(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6300846号

(P6300846)

(45) 発行日 平成30年3月28日(2018.3.28)

(24) 登録日 平成30年3月9日(2018.3.9)

(51) Int.Cl.

F 1

H01S 5/14 (2006.01)

H01S 5/14

H01S 5/022 (2006.01)

H01S 5/022

G02B 6/12 (2006.01)

G02B 6/12 301

請求項の数 12 外国語出願 (全 9 頁)

(21) 出願番号 特願2016-43106 (P2016-43106)

(22) 出願日 平成28年3月7日 (2016.3.7)

(65) 公開番号 特開2016-164986 (P2016-164986A)

(43) 公開日 平成28年9月8日 (2016.9.8)

審査請求日 平成28年4月15日 (2016.4.15)

(31) 優先権主張番号 15157905.9

(32) 優先日 平成27年3月6日 (2015.3.6)

(33) 優先権主張国 欧州特許庁 (EP)

(73) 特許権者 516280657

カリオパ・エンフェー

ベルギー・9052・ズウェイナルデ・

テクノロギーパルク・3

(74) 代理人 100146835

弁理士 佐伯 義文

(74) 代理人 100140534

弁理士 木内 敏二

(72) 発明者 マルティン・タサエール

中華人民共和国 518129 広東省深

▲チェン▼市龍崗区坂田 華為總部▲ベン

▼公樓

最終頁に続く

(54) 【発明の名称】 温度無依存レーザ

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体レーザであって、

レーザ放射を生成する利得領域と、

前記利得領域で生成された前記レーザ放射を反射する反射領域と、

前記利得領域で生成された前記レーザ放射を前記反射領域に導くための、および前記反射領域で反射された前記レーザ放射を前記利得領域に導くための導波路であって、前記利得領域、前記反射領域、および前記導波路が、前記半導体レーザの共振性空腔を規定し、前記導波路が、実質的にアサーマルである、導波路と

を備え、前記導波路が、導波路層と、前記導波路層の上部に配置される補償層と、前記導波路層と前記補償層との間に配置される平坦化酸化物層とを備え、前記補償層が、約1.8から約2.5の範囲の屈折率および1あたり $-0.5 \times 10^{-4}$ から $-2 \times 10^{-4}$ の範囲の負の温度係数を有する材料を備え、前記補償層の厚さが、前記導波路の有効屈折率nが温度にわたって実質的に一定であるように設定される、半導体レーザ。

10

## 【請求項 2】

前記導波路層が、窒化シリコンを備える、請求項1に記載の半導体レーザ。

## 【請求項 3】

前記導波路層が、約300nmから約400nmの範囲の厚さを有する、請求項2に記載の半導体レーザ。

## 【請求項 4】

前記補償層が、二酸化チタンを備える、請求項1から3のいずれか一項に記載の半導体レーザ。

【請求項5】

前記補償層が、約100nmから約250nmの範囲の、好ましくは、約150nmから約200nmの範囲の厚さを有する、請求項4に記載の半導体レーザ。

【請求項6】

前記平坦化酸化物層が、約30から約150nmの範囲の厚さを有する、請求項1に記載の半導体レーザ。

【請求項7】

前記半導体レーザの前記反射領域が、実質的にアサーマルである、請求項1から6のいずれか一項に記載の半導体レーザ。 10

【請求項8】

前記反射領域が、リング共振器および/またはプラッギングレーディングを備える、請求項1から7のいずれか一項に記載の半導体レーザ。

【請求項9】

前記反射領域および前記導波路が、平面光波回路で実現される、請求項1から8のいずれか一項に記載の半導体レーザ。

【請求項10】

前記利得領域が、III-V利得チップによってもたらされる、請求項9に記載の半導体レーザ。 20

【請求項11】

前記平面光波回路が、前記III-V利得チップに縁で結合されるか、前記III-V利得チップに一体化される、請求項10に記載の半導体レーザ。

【請求項12】

前記平面光波回路が、前記III-V利得チップにエバネッセントに結合される、請求項10に記載の半導体レーザ。 20

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、温度無依存な、すなわち、アサーマルな、レーザに関する。特に、本発明は、温度無依存半導体レーザに関する。 30

【背景技術】

【0002】

シリコンフォトニクスは、広帯域センサおよび光ファイバ通信ネットワークのためのレーザなどの、広い用途範囲のために基盤技術プラットフォームとして急速に重要性を得ている。シリコンフォトニクスにより、高品質で、低成本なシリコン基板でCMOS互換ウェハスケール技術の使用を介してフォトニック機能を実現することが可能になる。しかしながら、純粋なパッシブシリコン導波路デバイスは、挿入損、チャネルクロストークを生じさせる位相雑音、および温度依存性の点で、依然として性能が制限されている。これは、二酸化ケイ素被覆とシリコンコアとの間の高い屈折率コントラスト、不均一なシリコン層厚、およびシリコンの大きな熱光学効果に起因する。 40

【0003】

今日のフォトニック部品のコストの大部分は、金型コストよりはむしろ、パッケージングから生じている。このことは、チップの温度が正確に管理される必要があり、さらに熱電冷却器(TEC)が部品設計に含まれる場合に、特に当てはまる。TECは、密封環境を必要とし、それらを使用する構成要素は、「ゴールドボックス」ハウジングに通常は封入される。フォトニクスが、短距離、例えば、メートル間でも支配的なリンク技術となるよう、本技術は、銅による解決策とコストの面で競争力を有する必要がある。このことは、プリント回路板に直接取り付けられるフォトニックチップなどの、低成本のパッケージング技術を必要とし、TECを確実に使用しないようにする。 50

## 【0004】

今日の光通信用途のための非冷却レーザの場合、低密度波長多重（CWDM）のチャネル間隔は、20nmに設定されている。これは、TECが無い場合、レーザ波長が温度の関数としてドリフトするからである。80から100nm超にわたって動作するフォトニクス機能を設計することは極めて困難である。したがって、CWDM用途のために利用可能な波長チャネルは4つのみである。Ethernetデータリンクが400Gbpsで4つ超の波長チャネルに発展しても、もはや充分ではない。例えば、1つの提案として、25Gbps技術および8つの波長チャネルを使用してチャネルごとに50Gbpsを得るためにPAM-4を使用することが挙げられる。

## 【0005】

費用効果的なアサーマルレーザが利用可能である場合、CWDMチャネル間隔は、10nmに減らすことができ、8チャネルCWDM、非冷却解決策が可能になる。

10

## 【0006】

したがって、実質的に温度無依存なレーザ、すなわち、実質的に温度に無関係な発光波長を有するレーザが必要となる。

## 【発明の概要】

## 【課題を解決するための手段】

## 【0007】

本発明の目的は、実質的に温度無依存なレーザを提供することである。

## 【0008】

この目的は、独立請求項の発明の主題によって実現される。さらなる実装態様は、従属請求項、明細書、および図面で提供される。

20

## 【0009】

第1の態様によれば、本発明は、半導体レーザに関し、半導体レーザは、レーザ放射を生成するための利得領域と、利得領域で生成されたレーザ放射を反射するための反射領域と、利得領域で生成されたレーザ放射を反射領域に、および／または反射領域内に誘導するための、ならびに反射領域で反射されたレーザ放射を利得領域に、および／または利得領域内に誘導するための導波路であって、利得領域、反射領域、および導波路は、半導体レーザの共振性空腔を規定し、導波路は、実質的にアサーマルである、導波路とを備える。

## 【0010】

30

第1の態様による半導体レーザの第1の可能な実装態様において、導波路は、導波路層と、導波路層の上部に配置された補償層とを備え、補償層は、約1.8から約2.5の範囲の屈折率および1あたり-0.5×10-4から-2×10-4の範囲の負の温度係数を有する材料を備える。

## 【0011】

本発明の第1の態様の第1の可能な実装態様による半導体レーザの第2の可能な実装態様において、補償層の厚さは、導波路の有効屈折率nが温度にわたって実質的に一定であるよう設定される。

## 【0012】

40

本発明の第1の態様の第1または第2の可能な実装態様による半導体レーザの第3の可能な実装態様において、導波路層は、窒化シリコンを備える。

## 【0013】

本発明の第1の態様の第3の可能な実装態様による半導体レーザの第4の可能な実装態様において、導波路層は、約300nmから約400nmの範囲の厚さを有する。

## 【0014】

本発明の第1の態様の第1から第4の実装態様のいずれか1つによる半導体レーザの第5の可能な実装態様において、補償層は、二酸化チタンを備える。

## 【0015】

本発明の第1の態様の第5の実装態様による半導体レーザの第6の可能な実装態様において、補償層は、約100nmから約250nmの範囲の、好ましくは、約150nmから約200nmの範囲の

50

(導波路層に対して垂直方向に) 厚さを有する。

【0016】

本発明の第1の態様の第1から第6の実装態様のいずれか1つによる半導体レーザの第7の可能な実装態様において、半導体レーザは、導波路層と補償層との間に配置される平坦化酸化物層をさらに備える。平坦化酸化物層は、導波路層上に補償層をパターン形成することにより容易にする効果を有する。

【0017】

本発明の第1の態様の第7の実装態様の第8の可能な実装態様において、平坦化酸化物層は、約30から約150nmの範囲の厚さを有する。

【0018】

そのような本発明の第1の態様の第9の可能な実装態様または本発明の第1から第8の実装態様のいずれか1つにおいて、半導体レーザの反射領域は、実質的にアサーマルである。

【0019】

そのような本発明の第1の態様の第10の可能な実装態様または本発明の第1から第9の実装態様のいずれか1つにおいて、反射領域は、リング共振器および/またはプラッギングレーディングを備える。

【0020】

そのような本発明の第1の態様の第11の可能な実装態様または本発明の第1から第10の実装態様のいずれか1つにおいて、反射領域はおよび導波路は、平面光波回路で実現される。

【0021】

本発明の第1の態様の第11の実装態様の第12の可能な実装態様において、利得領域は、III-V利得チップによってもたらされる。

【0022】

本発明の第1の態様の第12の可能な実装態様の第13の可能な実装態様において、平面光波回路は、III-V利得チップで縁が結合されるか、またはIII-V利得チップに一体化される。

【0023】

本発明の第1の態様の第12の可能な実装態様の第14の可能な実装態様において、平面光波回路は、III-V利得チップにエバネッセントに結合される。

【0024】

本発明のさらなる実施形態は、以下の図面に関して説明される。

【図面の簡単な説明】

【0025】

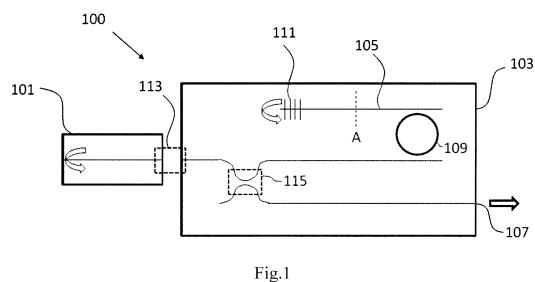

【図1】一実施形態によるアサーマルレーザの模式的な上面図である。

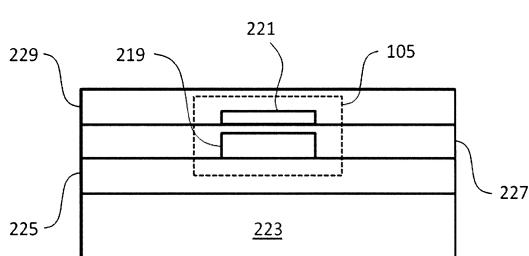

【図2】図1に示した線Aに沿った一実施形態によるアサーマルレーザの模式的な断面図である。

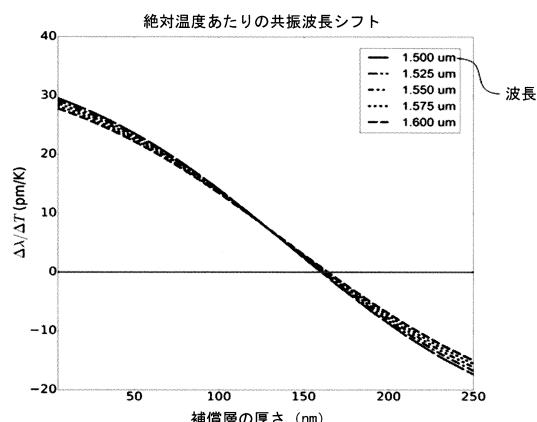

【図3】一実施形態によるアサーマルレーザの導波路の補償層の厚さに関する絶対温度あたりの共鳴波長シフトの依存度を示す図である。

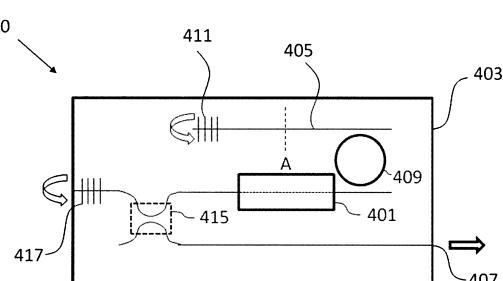

【図4】一実施形態によるアサーマルレーザの模式的な上面図である。

【発明を実施するための形態】

【0026】

以下の詳細な説明において、添付図面を参照し、添付図面は、本開示の一部を形成し、添付図面において、図示のために、本開示を実施することができる特定の態様が示される。他の態様を使用してもよく、構造的変更または論理的変更を、本開示の範囲から逸脱することなく行ってもよいことが理解されよう。したがって、以下の詳細な説明は、限定する意図はなく、本開示の範囲は、添付の特許請求の範囲によって定義される。

【0027】

説明する方法と関連する開示はまた、本方法を実行するよう構成される対応デバイスまたはシステムに当たはまり、逆も同様であることが理解されよう。例えば、特定の方法又

10

20

30

40

50

ステップが説明された場合、対応デバイスは、説明する方法ステップを実行するためのユニットを含むことができ、そのようなユニットが図面に明確に説明または示されていない場合もある。さらに、本明細書で説明するさまざまな例示的態様の特徴は、特記しない限り、互いに組み合わせることができることが理解されよう。

#### 【0028】

本明細書で説明するデバイスは、一体型光学チップを生成するために実現することができる。説明するデバイスは、集積回路を含むことができ、さまざまな技術により製造することができる。例えば、本回路は、論理集積回路、アナログ集積回路、混合信号集積回路、光学回路、および/またはメモリ回路を含むことができる。

#### 【0029】

以下の説明において、導波路を使用するデバイスが説明される。導波路は、特に、光学スペクトルで、電磁波を導く物理的構造である。一般的な種類の導波路には、光ファイバおよび方形導波路が含まれる。導波路は、例えば、平面、帯状、またはファイバ導波路などのその幾何学的形状、例えば、シングルモードまたはマルチモードなどのモード構造、例えば、段階的または勾配率分布などの屈折率分布、およびガラス、ポリマ、もしくは例えば半導体などの材料に従って分類することができる。

#### 【0030】

図1は、一実施形態による実質的に温度無依存な、すなわち、アサーマルレーザ100の模式的な上面図を示す。一実施形態において、アサーマルレーザ100は、半導体レーザとして実現される。

#### 【0031】

アサーマルレーザ100は、レーザ放射を生成するためにアクティブ利得領域101を備える。一実施形態において、利得領域101は、III-V利得チップによってもたらされる。図1のアサーマルレーザ実施形態100の利得領域101に示した矢印によって示されるように、利得領域101は、利得領域101で生成されるレーザ放射を反射するための高反射面を備えることができる。

#### 【0032】

さらに、アサーマルレーザ100は、利得領域101で生成されたレーザ放射を反射するためのパッシブ反射領域103を備える。一実施形態において、反射領域103は、平面光波回路で実現することができる。

#### 【0033】

一実施形態において、利得領域101で生成されたレーザ放射は、第1の結合領域113を介して、反射領域103に結合することができる。一実施形態において、反射領域103は、平面光波回路の形式であり、III-V利得チップの形式である利得領域101に縁で結合される。

#### 【0034】

さらに、アサーマルレーザ100は、利得領域101で生成されたレーザ放射を、反射領域103に、および/または反射領域103内に導くための、ならびに反射領域103で反射されたレーザ放射を利得領域101に導くための、導波路105を備える。図1に示す実施形態において、導波路105は、反射領域103の実質的に一部であり、特に、反射領域103の部分は、以下でより詳細に説明するように、リング共振器109および分布プラグ反射器111を含む。しかしながら、導波路105は、レーザ放射を導くためのアサーマルレーザ100の他の部品でも有利に実現することができるが当業者には明らかであろう。

#### 【0035】

利得領域101、反射領域103、および導波路105により、アサーマルレーザ100の共振性空腔が規定される。一実施形態において、反射領域103は、リング共振器109および分布プラググレーディング、すなわち、分布プラグ反射器111を備え、共振性空腔、すなわち、ファブリ・ペロー・レーザ空腔が、利得領域101の高反射面と分布プラグ反射器111との間に規定される。当業者には明らかであるように、図1に示すアサーマルレーザ100のレーザ発振波長は、リング共振器109および分布プラグ反射器111の反射特性によって本質的に判断される。一実施形態において、リング共振器109の複数の透過ピークの1つは、分布ブ

10

20

30

40

50

ラッゲ反射器111の阻止帯を使用することによって選択される。

【0036】

図1に示す実施形態において、レーザ放射は、利得領域101とリング共振器109との間の導波路105の一部に沿って設置される第2の結合領域115により、利得領域101、反射領域103、および導波路105によって規定される共振性空洞から引き出される。一実施形態において、第2の結合領域115は、導波路105のさらなる部分を介して、アサーマルレーザ100の出力面107に光学接続される。

【0037】

図2は、図1に示したアサーマルレーザ実施形態100の線Aに沿った模式的な断面図を示す。以下により詳細に説明するように、図2に示す実施形態において、導波路105は、実質的なアサーマル導波路105、および、したがって、実質的なアサーマル反射領域103をもたらす、導波路層219と、補償層221とによって本質的に規定される。

10

【0038】

一実施形態において、導波路層219および補償層221によって規定される導波路105が、シリコンウェハ223上に配置される。一実施形態において、導波路層219は、アンダークラッド酸化物層225により、シリコンウェハ223から分けられる。一実施形態において、導波路層219は、アンダークラッド酸化物層225の上部に堆積された平坦化酸化物層227の一部により、補償層221から分けられる。一実施形態において、オーバークラッド酸化物層229が、補償層221および平坦化酸化物層227の上部に堆積される。一実施形態において、平坦化酸化物層227は、導波路層219と補償層221との間に、約30から約150nmの範囲の厚さを有する。一実施形態において、図2の実施形態に示した層の構成は、CMOS処理に適合可能である。

20

【0039】

一実施形態において、導波路105の補償層221は、約1.8から約2.5の範囲の屈折率と、1あたり-0.5×10-4から-2×10-4の範囲の負の温度係数とを備える。一実施形態において、これらの特性を有する導波路105は、窒化シリコン(SiN)を備える導波路層219および/または二酸化チタン(TiO2)を備える補償層221によってもたらされる。

【0040】

図3は、5つの異なる波長(すなわち、1.5μmから1.6μmの範囲の波長)に対する窒化シリコン導波路層219の上部に配置されたチタン酸化物補償層221の厚さに関する一実施形態によるアサーマルレーザ100の絶対温度あたりの共鳴波長シフトの依存度を示す図を示す。この例において、窒化シリコン導波路層219は、約400nmの厚さと約800nmの幅を有し、一方、二酸化チタン層は、3μmの幅を有する。この例において、窒化シリコン導波路層219の場合、1550nmでの屈折率は、約2005であり、温度係数は、1あたり約5×10-5である。この例において、二酸化チタン補償層221の場合、1550nmでの屈折率は、約2,2であり、温度係数は、1あたり約-1×10-4である。

30

【0041】

図3から分かるように、約100nmから約250nmの範囲、好ましくは、約150nmから約200nmの範囲の(垂直方法の導波路層207に対する)(二酸化チタン)補償層221の厚さが、実質的なアサーマル導波路105を、したがって、実質的なアサーマルレーザ100をもたらす。さらなる実施形態において、補償層221の厚さは、導波路105の有効屈折率nが温度にわたって実質的に一定であるように設定される。

40

【0042】

図2に示した層、特に、導波路層219および補償層221の構成は、図4に示すアサーマルレーザ400のさらなる実施形態でのアサーマル導波路405として実現することができる。不要な繰り返しを避けるために、図4のアサーマルレーザ実施形態400の以下の説明は、図1のアサーマルレーザ実施形態100との相違点に焦点を当てる。先頭桁を変えてあるが(すなわち、"1"の代わりに"4")、図4および図1に示す同じ要素は、同じ参照符号により識別される。これらの同じ要素の詳細な説明のために、図1のアサーマルレーザ実施形態100の上記説明を参照する。

50

## 【0043】

図4に示すアサーマルレーザ実施形態400と、図1に示すアサーマルレーザ実施形態100との間の主な違いは、レーザ実施形態400において、利得領域401が、反射領域403にエバネッセントに結合されることである。すなわち、利得領域401は、利得領域401で生成されたレーザ放射が、反射領域403にエバネッセントに結合することができるよう、例えば、反射領域403の上部に配置される。図4に示す実施形態において、さらなる分布プラッグ反射器417を、反射領域403の一端に設けて、共振性空腔を規定することができる。さらなる実施形態において、別のリング共振器（図4では図示せず）を、分布プラッグ反射器417と組み合わせることができる。

## 【0044】

10

本明細書で説明するデバイスは、チップ、または集積回路、または特定用途向け集積回路（ASIC）内の光学回路として実現することができる。本発明は、デジタルおよび／またはアナログ電子および光学回路で実現することができる。

## 【0045】

本開示の特定の特徴または態様は、いくつかの実装態様または実施形態のただ1つのみに関して開示したであろうが、そのような特徴または態様は、任意の所与の、または特定の用途に対して所望され、有利である可能性があるような他の実装態様または実施形態の1つまたは複数の他の特徴または態様と組み合わせることができる。さらに、「含む」、「有する」、「伴う」という用語、またはそれらの他の変形形が、詳細な説明または特許請求の範囲のいずれかで使用される限り、そのような用語は、「備える」という用語と同様に包括的であることが意図される。「例示的」、「例え」、および「e.g.」という用語は、最良または最適ではなく、単に一例であることを意味する。「結合」および「接続」という用語は、派生語と共に使用される可能性がある。これらの用語は、それらが直接物理的または電気的に接觸しているか、またはそれらが互いに直接接觸していないかに関わらず、2つの要素が互いに協働または相互作用することを示すために使用された可能性があることを理解すべきである。

20

## 【0046】

特定の態様を本明細書で図示および説明してきたが、さまざまな代替および／または同等実装態様が、本開示の範囲から逸脱することなく、示し、説明した特定の態様と置き換え可能であることが当業者には明らかであろう。本出願は、本明細書で説明する特定の態様の任意の適応形態および変形形態を包含するように意図されている。

30

## 【0047】

添付の特許請求の範囲における要素は、対応する符号により特定の順序で記載されるが、そうでなければ、請求項の列挙は、それらの要素の一部または全てを実施するための特定の順序を意図しない限り、それらの要素は、その特定の順序で実施されることに限定されることを必ずしも意図しない。

## 【0048】

多くの代替例、修正例、および変更例が、上記の教示により、当業者に明らかであろう。当然、当業者は、本明細書で説明したものを超えて、本発明の用途が多数あることを容易に認識するであろう。本発明は、1つまたは複数の特定の実施形態を参照して説明してきたが、当業者は、本発明の範囲から逸脱すること無しに、多くの変形を行うことができるなどを認識するであろう。したがって、添付の特許請求の範囲およびそれらの同等物の範囲内で、本発明は、本明細書で特に説明した以外の方法で実施することができることを理解されたい。

40

## 【符号の説明】

## 【0049】

- 100 アサーマルレーザ

- 101 利得領域

- 103 反射領域

- 105 導波路

50

- 107 出力面

109 リング共振器

111 分布プラグ反射器

113 第1の結合領域

115 第2の結合領域

219 導波路層

221 補償層

223 シリコンウェハ

225 アンダークラッド酸化物層

227 平坦化酸化物層 10

400 アサーマルレーザ

401 利得領域

403 反射領域

405 アサーマル導波路

417 分布プラグ反射器

【図1】

Fig.1

【図2】

Fig.2

【図3】

【図4】

Fig.4

---

フロントページの続き

(72)発明者 マルコ・ランポニ

中華人民共和国 518129 広東省深 チェン 市龍崗区坂田 華為總部 ベン 公樓

(72)発明者 トム・コリンズ

中華人民共和国 518129 広東省深 チェン 市龍崗区坂田 華為總部 ベン 公樓

審査官 村井 友和

(56)参考文献 米国特許出願公開第2013/0243383(US, A1)

特開2011-253930(JP, A)

特表2009-542033(JP, A)

国際公開第2011/108617(WO, A1)

特開2002-190643(JP, A)

特開2000-352633(JP, A)

Jock Bovington et.al., Athermal laser design, OPTICS EXPRESS, Vol22 No.16, p19357-193

64

(58)調査した分野(Int.Cl., DB名)

H01S 5/00 - 5/50