(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6128901号

(P6128901)

(45) 発行日 平成29年5月17日(2017.5.17)

(24) 登録日 平成29年4月21日(2017.4.21)

(51) Int.Cl.

H04N 5/073 (2006.01)

F 1

H04N 5/073

A

請求項の数 13 (全 14 頁)

(21) 出願番号 特願2013-47135 (P2013-47135)

(22) 出願日 平成25年3月8日 (2013.3.8)

(65) 公開番号 特開2014-175870 (P2014-175870A)

(43) 公開日 平成26年9月22日 (2014.9.22)

審査請求日 平成28年3月4日 (2016.3.4)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】 映像処理装置及びその制御方法、タイミングジェネレータ、同期信号生成方法

## (57) 【特許請求の範囲】

## 【請求項 1】

入力映像信号をもとに出力映像信号を生成する映像処理装置であって、

前記出力映像信号の同期信号を挟む所定の期間に、前記入力映像信号の同期信号が生じたことを検出する検出手段と、

前記出力映像信号の同期信号を挟む所定の期間のうち前記出力映像信号の同期信号より前に、前記入力映像信号の同期信号が生じたことが前記検出手段により検出された場合、前記出力映像信号の同期信号の周期を長くするように補正する補正手段と、

前記補正手段により補正された周期で前記出力映像信号を出力する出力手段と、を備えることを特徴とする映像処理装置。

10

## 【請求項 2】

入力映像信号をもとに出力映像信号を生成する映像処理装置であって、

前記出力映像信号の同期信号を挟む所定の期間に、前記入力映像信号の同期信号が生じたことを検出する検出手段と、

前記出力映像信号の同期信号を挟む所定の期間のうち前記出力映像信号の同期信号より後に、前記入力映像信号の同期信号が生じたことが前記検出手段により検出された場合、前記出力映像信号の同期信号の周期を短くするように補正する補正手段と、

前記補正手段により補正された周期で前記出力映像信号を出力する出力手段と、を備えることを特徴とする映像処理装置。

## 【請求項 3】

20

前記入力映像信号の同期信号とは、前記入力映像信号から検出される垂直同期信号であり、前記出力映像信号の同期信号とは、前記出力映像信号の垂直同期信号であることを特徴とする請求項 1 または 2 に記載の映像処理装置。

**【請求項 4】**

前記補正手段は、前記検出手段が前記所定の期間のうち前記出力映像信号の同期信号より前に前記入力映像信号の同期信号を検出した場合、前記周期を長くするように補正することを特徴とする請求項 2 に記載の映像処理装置。

**【請求項 5】**

前記所定の期間において、前記出力映像信号の同期信号より前の期間と後の期間とで、それぞれ異なる長さの期間が設定されることを特徴とする請求項 1 乃至 4 のいずれか 1 項に記載の映像処理装置。 10

**【請求項 6】**

前記補正手段は、前記検出手段で検出された前記入力映像信号の同期信号が、前記出力映像信号の同期信号よりも前の期間であるか後の期間であるかにより、異なる補正幅で前記出力映像信号の同期信号の周期を補正することを特徴とする請求項 1 乃至 5 のいずれか 1 項に記載の映像処理装置。

**【請求項 7】**

前記検出手段は、前記所定の期間の前記出力映像信号の同期信号より前の期間と後の期間のそれを更に区切って複数の部分期間に分け、前記複数の部分期間のいずれに前記入力映像信号の同期信号が生じたかを検出し。 20

前記補正手段は、前記複数の部分期間のそれぞれに異なる補正幅を割り当て、前記検出手段により前記入力映像信号の同期信号の生じたことが検出された部分期間に割り当てられている補正幅で前記出力映像信号の同期信号の周期を補正することを特徴とする請求項 1 乃至 6 のいずれか 1 項に記載の映像処理装置。

**【請求項 8】**

前記補正手段は、隣接する垂直同期信号間に含まれる水平走査ライン数を増減することによって、前記出力映像信号の同期信号としての垂直同期信号の周期を補正することを特徴とする請求項 1 乃至 7 のいずれか 1 項に記載の映像処理装置。

**【請求項 9】**

前記補正手段は、隣接する水平同期信号間に含まれるビデオクロックの数を増減することによって、前記出力映像信号の同期信号としての垂直同期信号の周期を補正することを特徴とする請求項 1 乃至 7 のいずれか 1 項に記載の映像処理装置。 30

**【請求項 10】**

入力映像信号をもとに出力映像信号を生成する映像処理装置の制御方法であって、

前記出力映像信号の同期信号を挟む所定の期間に、前記入力映像信号の同期信号が生じたことを検出する検出工程と、

前記出力映像信号の同期信号を挟む所定の期間のうち前記出力映像信号の同期信号より前に、前記入力映像信号の同期信号が生じたことが前記検出工程により検出された場合、前記出力映像信号の同期信号の周期を長くするように補正する補正工程と、

前記補正工程で補正された周期で前記出力映像信号を出力する出力工程と、を有することを特徴とする映像処理装置の制御方法。 40

**【請求項 11】**

入力映像信号をもとに出力映像信号を生成する映像処理装置の制御方法であって、

前記出力映像信号の同期信号を挟む所定の期間に、前記入力映像信号の同期信号が生じたことを検出する検出工程と、

前記出力映像信号の同期信号を挟む所定の期間のうち前記出力映像信号の同期信号より後に、前記入力映像信号の同期信号が生じたことが前記検出工程により検出された場合、前記出力映像信号の同期信号の周期を短くするように補正する補正工程と、

前記補正工程で補正された周期で前記出力映像信号を出力する出力工程と、を有することを特徴とする映像処理装置の制御方法。 50

**【請求項 1 2】**

入力映像信号をもとに出力映像信号を生成する映像処理装置において、前記出力映像信号のための同期信号を生成するタイミングジェネレータであって、

前記出力映像信号のためのビデオクロックを第1のカウント値までカウントする毎に前記出力映像信号のための水平同期信号を出力する水平走査カウンタと、

前記水平同期信号を第2のカウント値までカウントする毎に、前記出力映像信号のための垂直同期信号を出力する垂直走査カウンタと、

前記出力映像信号の垂直同期信号を挟む所定の期間のうち、前記出力映像信号の垂直同期信号より前の期間に前記入力映像信号の垂直同期信号が到来した場合に前記第1または第2のカウント値のいずれかを増加させ、前記出力映像信号の垂直同期信号より後の期間に前記入力映像信号の垂直同期信号が到来した場合に前記第1または第2のカウント値のいずれかを減少させる周期補正手段と、を備え、

10

前記出力映像信号の垂直同期信号より前の期間と前記出力映像信号の垂直同期信号より後の期間とは互いに異なる長さの期間であることを特徴とするタイミングジェネレータ。

**【請求項 1 3】**

入力映像信号をもとに出力映像信号を生成する映像処理装置において、前記出力映像信号のための垂直同期信号を生成する方法であって、

水平走査カウンタが、前記出力映像信号のためのビデオクロックを第1のカウント値までカウントする毎に前記出力映像信号のための水平同期信号を生成し出力する工程と、

垂直走査カウンタが、前記水平同期信号を第2のカウント値までカウントする毎に、前記出力映像信号のための垂直同期信号を生成し出力する工程と、

20

周期補正手段が、前記出力映像信号の垂直同期信号を挟む所定の期間のうち、前記出力映像信号の垂直同期信号より前の期間に前記入力映像信号の垂直同期信号が到来した場合に前記第1または第2のカウント値のいずれかを増加させ、前記出力映像信号の垂直同期信号より後の期間に前記入力映像信号の垂直同期信号が到来した場合に前記第1または第2のカウント値のいずれかを減少させる周期補正工程と、を有し、

前記出力映像信号の垂直同期信号より前の期間と前記出力映像信号の垂直同期信号より後の期間とは互いに異なる長さの期間であることを特徴とする同期信号生成方法。

**【発明の詳細な説明】****【技術分野】**

30

**【0 0 0 1】**

本発明は、外部から映像データを入力して表示等の処理を行なう映像処理装置及びその制御方法、タイミングジェネレータ、同期信号生成方法に関する。

**【背景技術】****【0 0 0 2】**

T V 受信機やモニタディスプレイに代表される映像処理装置が普及している。T V 受信機はアナログ放送やデジタル放送を受信し、または外部入力インターフェースから映像データを入力して映像の表示を行なう。モニタディスプレイは、外部入力インターフェースからコンテンツを入力して映像の表示を行なう。

**【0 0 0 3】**

40

外部入力インターフェースにはP C やD V D レコーダなどの各種ソース機器を接続できる。インターフェース方式としては、H D M I 、D V I 、アナログR G B 、D 端子、S 端子、コンポジット信号等、各種の方式がある。装置内部では、各インターフェースのレシーバL S I でベースバンドのデジタル映像信号に変換した後に、映像処理L S I に入力する。ベースバンドのデジタル映像信号は、一般に垂直同期信号や水平同期信号のような同期信号と画素データを有しており、各信号のタイミングはS M P T E - 2 7 4 M 等の規格で規定されている。

**【0 0 0 4】**

入力映像信号をもとに出力映像信号を出力する際には、装置内部で生成した同期信号に合わせて映像信号を出力する場合がある。たとえば、L C D やプラズマ等のディスプレイ

50

に表示を行なう場合には、表示パネルのタイミング仕様に合わせた同期信号を用いて出力映像信号を生成し、表示することになる。また、拡大や縮小などを行なった場合にも、画面サイズに合わせたタイミング信号に載せ換えて表示が行なわれる。

#### 【0005】

ところが、入力映像信号と出力映像信号の同期信号の周期が異なると、画像の追越し・追越されによる表示乱れが生じる。出力周期が遅い場合はコマが飛んでしまい、速い場合は同じコマが複数回表示されてしまう。これにより、物体の動きがギクシャクするなどの表示乱れが起こる。同期ずれ補正を行なう方法としては、例えば下記のものがある。

#### 【0006】

(1) 垂直同期周波数が表示可能な所定の周波数範囲に収まるよう、ライン数の補間または間引きを行なう。入力の水平・垂直同期周期を検出し、補正された出力周期をMPUが設定する。また、垂直同期出力の位相を変更することで、フレームメモリ量を最小化する（特許文献1参照）。

10

(2) フレーム毎に入出力同期信号の時間間隔を測定し、その結果から入力同期信号と出力同期信号の近付く方向を検出して、ライン数の補間または間引きを行なう（特許文献2参照）。

(3) 出力同期信号の前後にウインドウパルスを発生し、ウインドウパルス内に参照信号が入った場合にのみフレームリセットを行なう（特許文献3参照）。

#### 【先行技術文献】

##### 【特許文献】

20

##### 【0007】

【特許文献1】特開2001-195023号公報

【特許文献2】特開2003-134414号公報

【特許文献3】特開2001-292336号公報

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0008】

しかしながら、上記の方法においては、安定且つ高速に同期ずれ補正を行なうには複雑なハードウェア資源が必要であるという課題があった。たとえば、(1)の方法では、入力周期の測定や補正周期の演算などをプロセッサで行なっており、複雑且つ高価なハードウェア資源を必要としていた。(2)の方法でも、過去の時間間隔を保持しておいて比較する必要があり、複雑なハードウェア資源が必要であった。

30

##### 【0009】

また、(3)の方法では、ハードウェア資源は簡素ではあるものの、制御時の周期の安定性と引き込み時間がトレードオフになるという課題があった。例えば、ウインドウパルスを狭くした場合は、フレームリセットが行なわれた場合の周期変動は少なくなるが、引き込みには長い時間が必要である。ウインドウパルスを広くした場合は、引き込みは短い時間で行なわれるが、フレームリセットが行なわれた場合の周期変動は大きくなってしまう。さらに、(1)～(3)の何れの例においても、出力信号の位相を制御するためには別の制御機構が必要であり、ハードウェア資源の複雑化を招いていた。

40

##### 【0010】

本発明は、上記の課題に鑑みてなされたものであり、簡素な構成で安定且つ高速な同期ずれ補正を可能にすることを目的とする。

##### 【課題を解決するための手段】

##### 【0011】

上記目的を達成するための本発明の一態様による映像処理装置は以下の構成を備える。すなわち、

入力映像信号をもとに出力映像信号を生成する映像処理装置であって、

前記出力映像信号の同期信号を挟む所定の期間に、前記入力映像信号の同期信号が生じたことを検出する検出手段と、

50

前記出力映像信号の同期信号を挟む所定の期間のうち前記出力映像信号の同期信号より

前に、前記入力映像信号の同期信号が生じたことが前記検出手段により検出された場合、

前記出力映像信号の同期信号の周期を長くするように補正する補正手段と、

前記補正手段により補正された周期で前記出力映像信号を出力する出力手段と、を備える。

#### 【発明の効果】

##### 【0012】

本発明によれば、簡素な構成で安定且つ高速な同期ずれ補正が可能になる。

#### 【図面の簡単な説明】

##### 【0013】

10

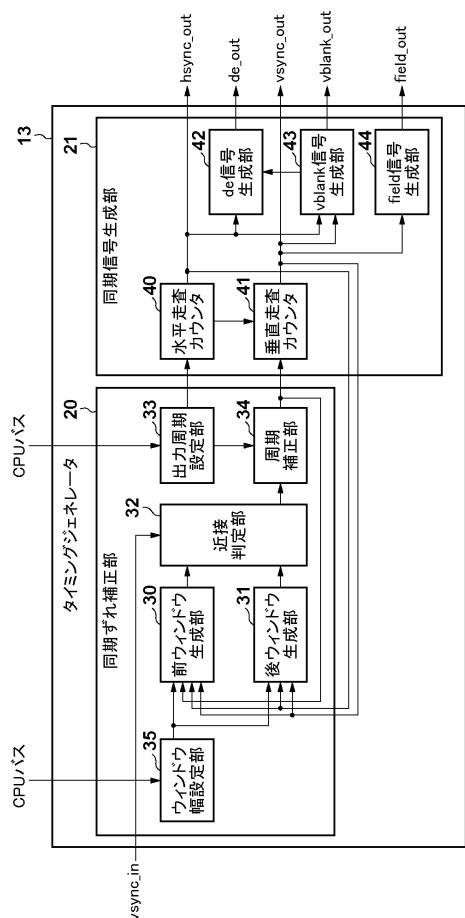

【図1】第一実施形態におけるタイミングジェネレータの構成を示すブロック図。

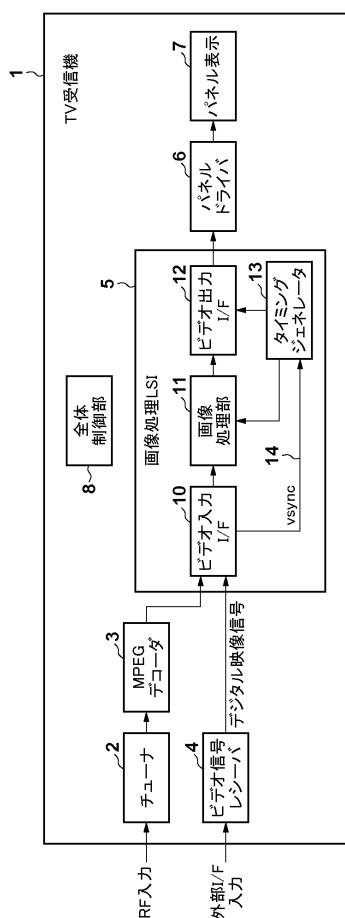

【図2】第一実施形態における映像処理装置の構成を示すブロック図。

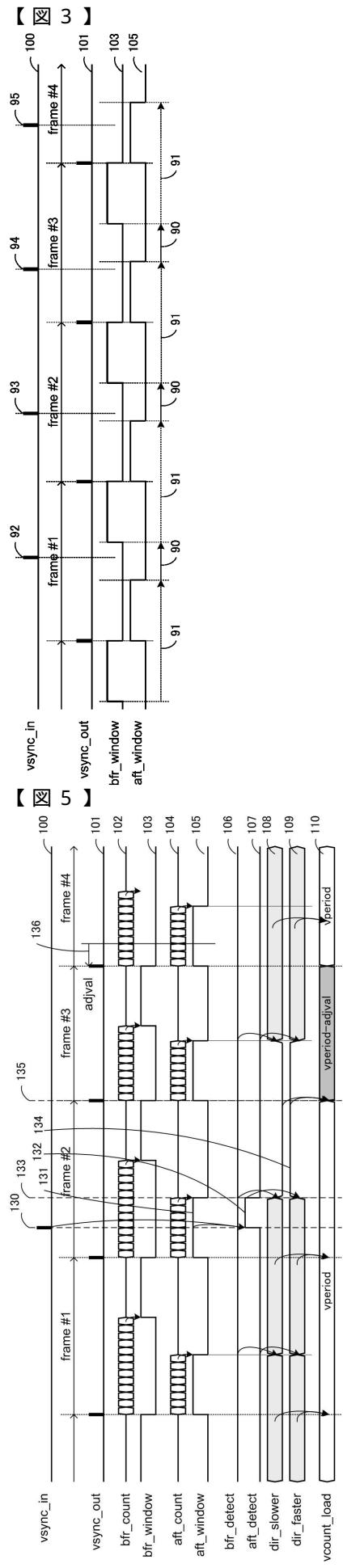

【図3】第一実施形態における入出力ロック期間のタイミングを示す図。

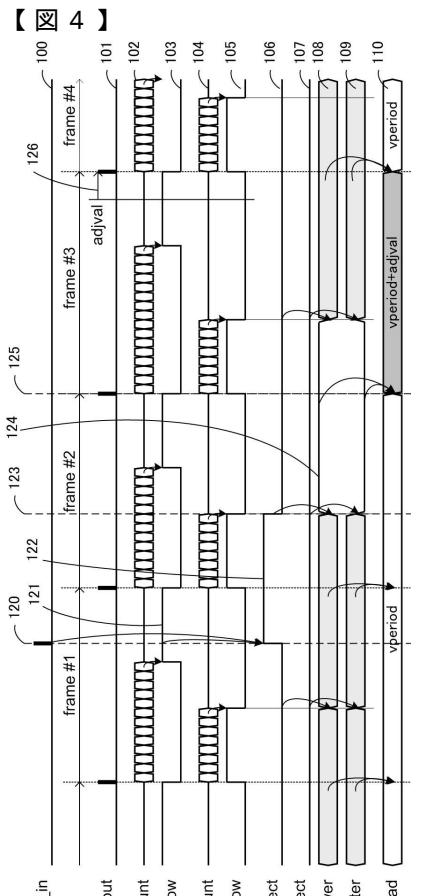

【図4】第一実施形態における同期ずれ補正の動作タイミングの例を示す図。

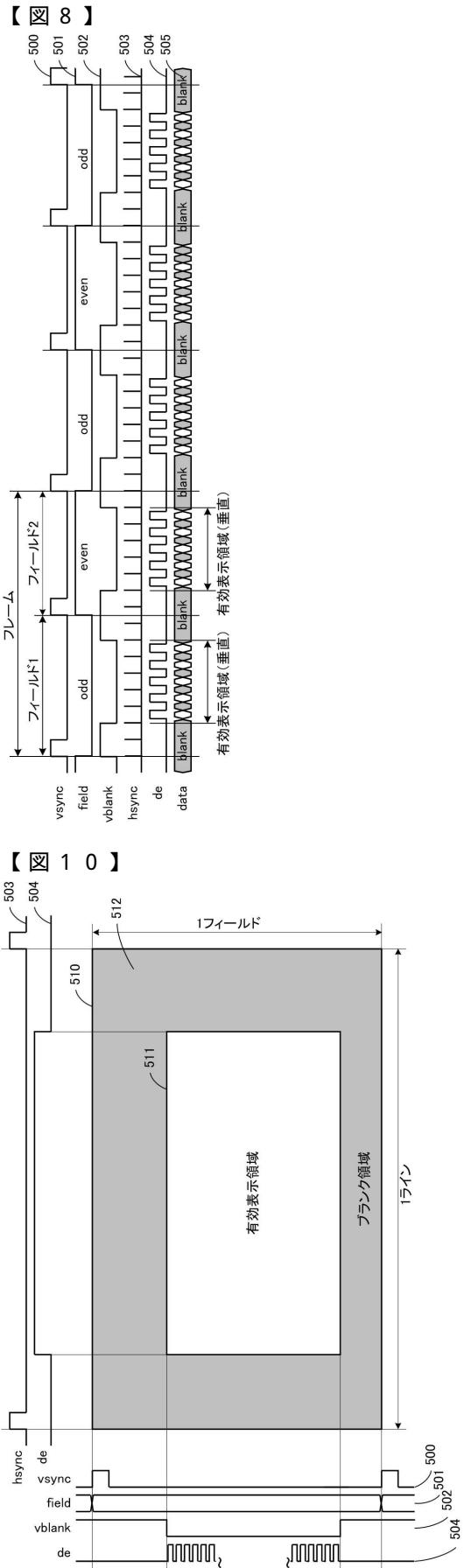

【図5】第一実施形態における同期ずれ補正の動作タイミングの例を示す図。

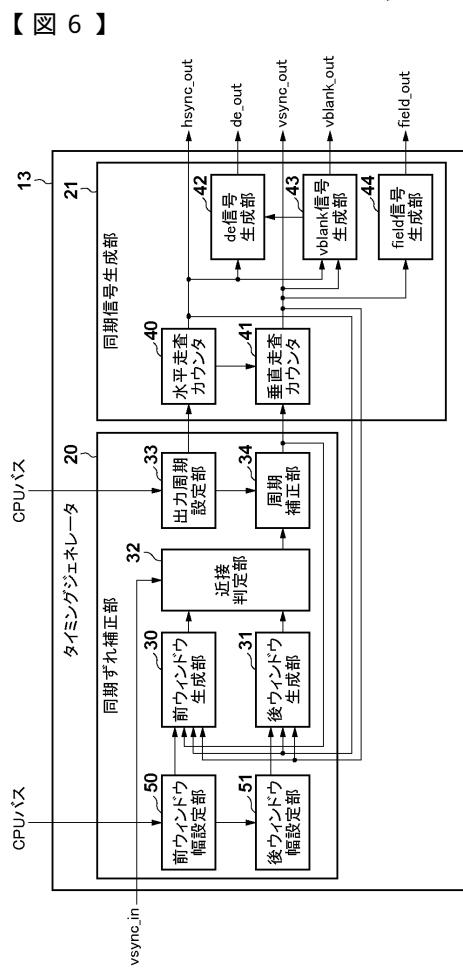

【図6】第二実施形態におけるタイミングジェネレータの構成を示すブロック図。

【図7】第二実施形態における同期ずれ補正の動作タイミングの例を示す図。

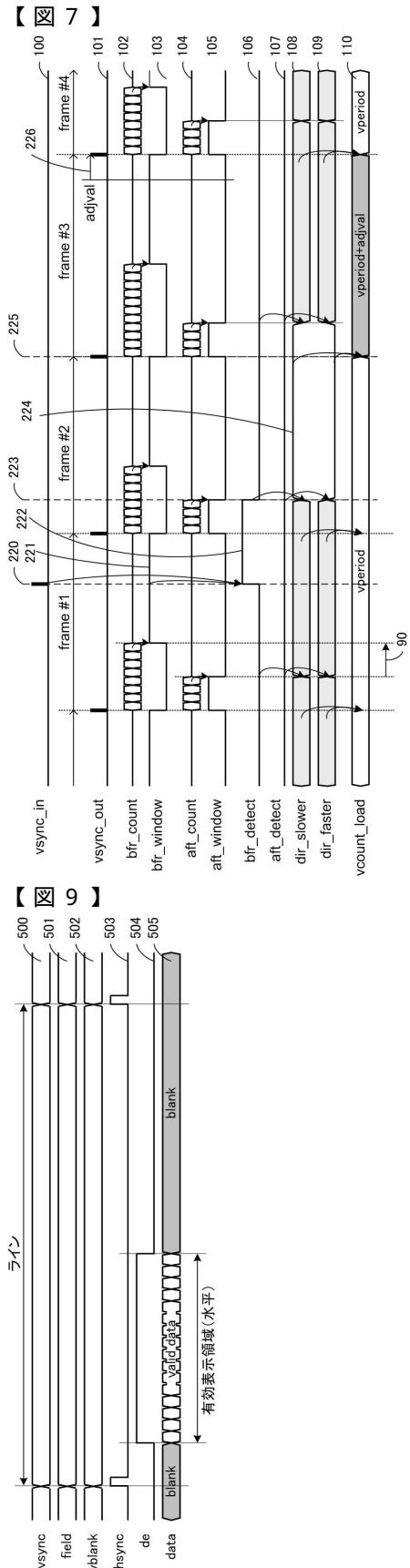

【図8】従来例におけるデジタル映像信号の垂直期間のタイミング例を示す図。

【図9】従来例におけるデジタル映像信号の水平期間のタイミング例を示す図。

【図10】従来例におけるデジタル映像信号と表示レイアウトの関係を示す図。

20

#### 【発明を実施するための形態】

##### 【0014】

以下、添付の図面を参照して、本発明をその好適な実施形態に基づいて詳細に説明する。なお、以下の実施形態において示す構成は一例に過ぎず、本発明は図示された構成に限定されるものではない。

##### 【0015】

30

#### [第一実施形態]

本実施形態では、垂直同期出力前後の所定のウインドウ期間に垂直同期入力があったことを検出し、検出されたウインドウの方向に応じて出力同期信号の周期を補正する例について説明する。

##### 【0016】

#### <表示装置の構成(図2)>

図2を用いて、第一実施形態による映像処理装置の構成を説明する。第一実施形態の映像処理装置は、入力映像信号としてのデジタル放送を受信して表示するTV受信機である。1はTV受信機の本体である。2はデジタルチューナであり、放送電波を入力し、復調されたストリームデータを出力する。3はデコーダであり、MPEG2等の方式で圧縮された映像データを伸張し、図8～図10により後述するようなベースバンドのデジタル映像データに変換して出力する。5は画像処理LSIであり、映像データに対して色や形状の補正を行ない、出力映像信号として出力する。6はパネルドライバであり、映像データ(出力映像信号)に従って、表示パネル7に表示するための駆動信号を出力する。7は映像データを表示する表示パネルであり、LCDやプラズマ、CRT、有機EL、SED等の方式で構成される。8は全体制御部であり、TV受信機1内の各部の制御を行なう。4はビデオ信号レシーバであり、装置の外部インタフェース経由で各種方式のビデオ信号を入力し、図8～図10により後述するようなベースバンドのデジタル映像データに変換して出力する。外部インタフェースの方式としては、HDMI、DVI、アナログRGB端子、D端子、S端子、コンポジットビデオ端子等がある。

40

##### 【0017】

画像処理LSI5において、10はビデオ入力インタフェースであり、デジタル映像データをLSIに入力する。11は画像処理部であり、映像データに対して各種の画像処理を行なう。13はタイミングジェネレータであり、映像データを出力するためのタイミン

50

グを生成する。12はビデオ出力インターフェースであり、出力タイミング信号に合わせて、デジタル映像データをLSIから出力する。タイミングジェネレータ13は、ビデオ入力インターフェース10から供給される入力同期信号(vsync)を用いて、入力されるデジタル映像信号とビデオ出力インターフェース12から出力されるデジタル映像信号の同期ずれ補正制御を行なう。

#### 【0018】

<ベースバンドのデジタル映像データの説明(図8～図10)>

本実施形態で用いられる映像信号の一例について、その信号構成と各信号のタイミングを図8～10を用いて説明する。

#### 【0019】

図8は、画面を構成するフレーム期間のタイミングを示す図である。500は垂直同期信号(vsync)であり、フィールドの開始タイミングを示す。501はフィールド信号(field)であり、奇数フィールド(odd)と偶数フィールド(even)の区別を示す。502は垂直ブランкиング信号(vblank)であり、垂直方向のブランク期間を示す。503は水平同期信号(hsync)であり、水平方向の走査線の開始タイミングを示す。504はデータタイナーブル信号(de)であり、水平方向の画素データが有効であることを示す。505は画素データ(data)であり、RGBやYCbCr色空間で表された色データを伝送する。垂直同期信号500のパルスで区切られた期間が1フィールドを構成する。インターレス映像データの場合は、奇数フィールドと偶数フィールドにより1フレームが構成される。

10

#### 【0020】

図9は、フィールド画面を構成する1ライン期間のタイミングを示す図である。500～505は図8で説明したものと同じ信号である。図中、水平同期信号のパルスで区切られた期間が1ラインを構成する。ライン内でデータタイナーブル信号504がアサートされている期間が有効表示領域である。有効表示領域の期間の画素データが表示に使用される。

20

#### 【0021】

図10は、図8と9のタイミング信号と表示画面のレイアウトの関係を示す図である。510は1フィールド期間の画面レイアウトである。中央の511は有効表示領域であり、パネル画面に表示される。512はブランク領域である。有効表示領域を識別するために同期信号が使用される。垂直方向は垂直同期信号500(vsync)、フィールド501(field)、垂直ブランкиング信号502(vblank)が、水平方向は水平同期信号503(hsync)、データタイナーブル信号504(de)が使用される。なお、垂直方向に関しては、垂直ブランкиング信号502を使用せずに、データタイナーブル信号504を用いて有効表示領域を識別することもできる。

30

#### 【0022】

<同期ずれ補正の仕組み(図3)>

図3は入出力同期信号とロック期間の関係を示すタイミング図である。図3を用いて本実施形態の同期ずれ補正の仕組みを説明する。100は入力映像データの垂直同期信号(vsync\_in)であり、例えば92～95のようなパルスが周期的に入力される。101は、タイミングジェネレータ13が生成する出力垂直同期信号(vsync\_out)である。103は前ウインドウ信号(bfr\_window)であり、出力垂直同期信号101の前の所定期間にわたってアサートされる。105は後ウインドウ信号(aft\_window)であり、出力垂直同期信号101の後の所定期間にわたってアサートされる。91はロック外れ期間であり、前ウインドウ信号103または後ウインドウ信号105がアサートされている期間である。90はロック期間であり、前ウインドウ信号103と後ウインドウ信号105の何れもアサートされていない期間である。

40

#### 【0023】

図3では、入出力の同期信号の周期が異なるために、位相が次第にずれていく様子が示されている。入力垂直同期信号パルス92と93はロック範囲内にあるので、補正を要し

50

ない状態にある。一方で、入力垂直同期信号パルス 94 と 95 はロック外れ期間に入っており、徐々に出力垂直同期信号に近寄っている。このまま時間が経過すると、やがて出力垂直同期信号に追い付き、追越してしまう。このような追い越しが発生すると、画像フレームの不連続による表示乱れが発生してしまう。そのため、入力垂直同期信号がロック外れ期間に位置する場合には、タイミングジェネレータ 13 がこれらフレームの出力同期信号に対して同期ずれ補正を行なう。

#### 【0024】

本実施形態の同期ずれ補正は、非ロック期間 91 に存在する入力垂直同期信号 100 をロック期間 90 に引き込むように動作する。入力垂直同期信号 100 がウインドウ信号にかかるタイミングにある場合は、その位置に応じて出力周期を変更することによって入出力の位相を調整する。入力垂直同期信号 100 がロック期間 90 に引き込まれている間は、所定の周期で同期信号を出力する。このようにすることで、入力垂直同期信号はロック期間 90 に位置するようになり、入出力の同期信号をほぼ一定の位相差に保つことができる。

10

#### 【0025】

以上のように動作することで、入出力間での画像コマの追越し・追越され、の発生を防ぐことができる。

#### 【0026】

<タイミングジェネレータの構成(図1)>

図1を用いて、タイミングジェネレータ 13 の構成及び同期信号生成の動作を説明する。21 は同期信号生成部であり、出力同期信号を生成して出力する。20 は同期ずれ補正部であり、入力垂直同期信号 100 に合わせて、同期信号生成部 21 の生成する出力垂直同期信号 101 のタイミングを補正する。

20

#### 【0027】

同期信号生成部 21 において、40 は水平走査カウンタであり、不図示のクロックジェネレータから供給される出力ビデオクロックをカウントして、第1のカウント値までカウントする毎に水平走査のタイミングを生成し、出力する。第1のカウント値は、後述する出力周期設定部 33 により設定される。41 は垂直走査カウンタであり、水平走査カウンタ 40 が出力する水平同期信号をカウントして、垂直走査のタイミングを生成する。垂直走査カウンタ 41 は、第2のカウント値まで水平同期信号をカウントする毎に、出力垂直同期信号 101 を生成し出力する。第2のカウント値は、後述する周期補正部 34 により設定された補正後の値(ライン数)である。

30

#### 【0028】

42 はデータイネーブル信号生成部であり、データイネーブル信号を生成して出力する。データイネーブル信号生成部 42 は、水平同期信号からの同期信号幅、バックポーチ幅、イネーブル期間幅をカウントし、データイネーブル信号をアサートする。すなわち、データイネーブル信号生成部 42 は、水平同期信号の先頭エッジから同期信号幅+バックポーチ幅の期間が経過した後、イネーブル期間幅の間にわたってデータイネーブル信号をアサートする。43 は垂直プランキング信号生成部であり、垂直プランキング信号を生成して出力する。垂直プランキング信号生成部 43 は、垂直同期信号からの同期信号幅、バックポーチ幅、イネーブル期間幅をカウントし、垂直プランキング信号をアサートする。すなわち、垂直プランキング信号生成部 43 は、垂直同期信号の先頭エッジから同期信号幅+バックポーチ幅の期間が経過した後のイネーブル期間を除く期間において垂直プランキング信号をアサートする。44 はフィールド信号生成部であり、奇数フィールドか偶数フィールドかを示すフィールド信号を生成して出力する。フィールド信号生成部 44 は、垂直同期信号の出力タイミングに合わせて、フィールド信号をトグルさせることで、奇数フィールドか偶数フィールドかを示す。

40

#### 【0029】

同期ずれ補正部 20 において、35 はウインドウ幅設定部であり、CPUバス経由で全体制御部 8 が有するCPU(不図示)により設定された検出ウインドウの幅の設定値を保

50

持する。30は前ウインドウ生成部であり、カウンタで構成されており、前ウインドウのタイミング(前ウインドウ信号103(bfr\_window))を生成する。前ウインドウ生成部30は、垂直同期信号出力のタイミングで、保持されている設定値(検出ウインドウ幅)を出力周期から差し引いた値をロードし、水平同期信号をカウントする。水平同期信号のカウントが終了した時点(カウント値が設定値に到達した時点)で前ウインドウ信号103(bfr\_window)をアサートし、次の垂直同期信号出力でネゲートする。

#### 【0030】

31は後ウインドウ生成部であり、カウンタで構成されており、後ウインドウのタイミング(後ウインドウ信号105(aft\_window))を生成する。後ウインドウ生成部31は、垂直同期信号出力のタイミングで保持されている設定値(検出ウインドウ幅)の値をロードし、水平同期信号をカウントする。後ウインドウ生成部31は、垂直同期信号出力を出力する時点で後ウインドウ信号105をアサートし、水平同期信号のカウントが終了した時点(カウント値が設定値に到達した時点)でネゲートする。

#### 【0031】

32は近接判定部であり、前ウインドウ信号103または後ウインドウ信号105がアサートされている期間内に入力垂直同期信号が検出されたか否かを判定し、入力垂直同期信号が検出されたウインドウに応じた補正方向信号を出力する。前ウインドウ信号103がアサートされている期間(前ウインドウ期間)に入力垂直同期信号が検出された場合は、出力周波数を遅くする方向への補正を指示する信号を周波数補正指示信号として出力する。後ウインドウ信号105がアサートされている期間(後ウインドウ期間)に入力垂直同期信号が検出された場合は、出力周波数を速くする方向への補正を指示する信号を周波数補正指示信号として出力する。33は出力周期設定部であり、CPUバス経由で設定された出力周期と補正幅の設定値を保持する。34は周期補正部であり、近接判定部32の出力する周波数補正指示信号に応じて、出力周期の値を補正して出力する。

#### 【0032】

<タイミングジェネレータの動作の説明(図4～図5)>

以下、図4、5のタイミング図を用いて、タイミングジェネレータ13による補正動作を説明する。

#### 【0033】

図4は、前ウインドウ期間で入力垂直同期信号を検出した様子を示すタイミング図である。図3と同様に、100は入力垂直同期信号(vsync\_in)、101は出力垂直同期信号(vsync\_out)、103は前ウインドウ信号(bfr\_window)、105は後ウインドウ信号(aft\_window)、である。102は前ウインドウカウンタ(bfr\_count)であり、出力垂直同期信号101から前ウインドウアサートまでのタイミングをカウントする。104は後ウインドウカウンタ(aft\_count)であり、出力垂直同期信号101から後ウインドウのネゲートまでのタイミングをカウントする。前ウインドウカウンタ102は前ウインドウ生成部30が実行するカウントを示し、後ウインドウカウンタ104は後ウインドウ生成部31が実行するカウントを示している。

#### 【0034】

また、近接判定部32は以下の信号を生成する。106は前ウインドウ検出信号(bfr\_detect)であり、前ウインドウ信号103のアサート中に入力垂直同期信号100が到来した場合にセットされる。107は後ウインドウ検出信号(aft\_detect)であり、後ウインドウ信号105のアサート中に入力垂直同期信号100が到来した場合にセットされる(図5を参照)。108は低速化要求信号(dir\_slower)、109は高速化要求信号(dir\_faster)であり、周期補正部34に対して補正の方向を示す。近接判定部32は、後ウインドウ期間が終了した時点で、前ウインドウ検出信号106と後ウインドウ検出信号107のいずれかがセットされているかを判定し、それに対応した要求信号をセットする。低速化要求信号108は、前ウインドウ検出信号106がセットされている場合にアサートされ、同期信号生成部21が出力する垂直同期信号の出力周波数を遅くする要求信号である。高速化要求信号109は、後ウインドウ検出信号107がセットされている場

10

20

30

40

50

合にアサートされ、同期信号生成部 21 が output する垂直同期信号の出力周波数を速くする要求信号である。

#### 【 0 0 3 5 】

周期補正部 34 は、垂直走査カウンタロード値 110 (vcount\_load) を output する。低速化要求信号 108 がアサートされている場合は「出力周期 (vperiod) + 補正幅 (adjval)」とする。こうして、垂直走査カウンタ 41 が垂直同期信号を output するまでにカウントするべきライン数を示す第 2 のカウント値を増加させ、垂直同期信号の周期を長くする。また、高速化要求信号 109 がアサートされている場合は「出力周期 (vperiod) - 補正幅 (adjval)」とする(図 5)。こうして、垂直走査カウンタ 41 が垂直同期信号を output するまでにカウントするべきライン数を示す第 2 のカウント値を減少させ、垂直同期信号の周期を短くする。低速化要求信号 108 及び高速化要求信号 109 のいずれもアサートされていない場合は、補正なしに「出力周期」を output する。10

#### 【 0 0 3 6 】

図 4 の例では、入力垂直同期信号パルス 120 が前ウインドウ期間 121 の間に到来しているので、前ウインドウ検出信号 106 がアサートされる(122)。後ウインドウ終了のタイミング 123 の時点で、低速化要求信号 108 がアサートされる(124)。そして、垂直走査カウンタ 41 のカウント終了タイミング 125において、「出力周期 + 補正幅」がロードされる。垂直走査カウンタ 41 は、ロードされた「出力周期 + 補正幅」だけ水平ラインをカウントすると出力垂直同期信号を output する。結果として、次のフレーム #3 では補正幅 (adjval) だけ垂直走査の周波数が遅くなるように変更され(126)、入出力の垂直同期信号がより離れるように補正される。20

#### 【 0 0 3 7 】

図 5 は、後ウインドウ期間で入力垂直同期信号を検出した様子を示すタイミング図である。図 5 の例では、入力垂直同期信号パルス 130 が後ウインドウ期間 131 の間に到来しているので、後ウインドウ検出信号 107 がアサートされる(132)。後ウインドウ期間の終了のタイミング 133 の時点で、高速化要求信号 109 がアサートされる(134)。垂直走査カウンタ 41 のカウント終了タイミング 135においては、「出力周期 - 補正幅」がロードされる。垂直走査カウンタ 41 は、ロードされた「出力周期 - 補正幅」だけ水平ラインをカウントすると出力垂直同期信号を output する。結果として、図 5 のフレーム #3 では垂直走査の周波数が補正幅 (adjval) だけ速くなるように変更され(136)、入出力の垂直同期信号がより離れるように補正される。30

#### 【 0 0 3 8 】

以上の動作により、入力垂直同期信号を output 垂直同期信号から離し、ロック期間の方向に近付けるように補正が行なわれる。この制御を、非ロック期間に入力垂直同期信号が存在しなくなるまで繰り返すことで、入力垂直同期信号をロック期間に引き込むことができる。

#### 【 0 0 3 9 】

以上説明したように、第一実施形態によれば、垂直同期信号出力前後の所定のウインドウ期間(非ロック期間)に入力垂直同期信号があったかを検出し、入力垂直同期信号が検出されたウインドウに応じて出力同期信号の周期が補正される。そのため、安定性と高速性を維持しながら同期ずれ補正の構成を簡素化できる。40

#### 【 0 0 4 0 】

##### [ 第二実施形態 ]

第二実施形態では、前ウインドウと後ウインドウとを異なった幅に設定できるようにした例について説明する。なお、第二実施形態における表示装置、TV 受信器の構成は、前述の第一実施形態(図 1)と同様である。

#### 【 0 0 4 1 】

##### < 第二実施形態によるタイミングジェネレータの構成(図 6) >

図 6 を用いて本実施形態のタイミングジェネレータ 13 の構成を説明する。なお、第一実施形態(図 1)と同様の構成要素には同一番号を付してある。第二実施形態の同期ずれ50

補正部 20 は、前ウインドウと後ウインドウの幅を独立に設定できる。50 は前ウインドウ幅設定部であり、CPUバスを介して設定された前ウインドウの幅の設定値を保持する。51 は後ウインドウ幅設定部であり、CPUバスを介して設定された後ウインドウの幅の設定値を保持する。このような構成によれば、ロック期間を所望のタイミングに配置することができる。例えば、出力垂直走査周期の前半分にロック期間を置きたい場合には、前ウインドウ幅を長くし、後ウインドウ幅を短く設定すればよい。また、出力垂直走査周期の後半分に置きたい場合には、前ウインドウ幅を短くし、後ウインドウ幅を長く設定すればよい。

#### 【0042】

<タイミングジェネレータの動作の説明(図7)>

10

図7は、前ウインドウで入力垂直同期信号を検出した様子を示すタイミング図である。図4や図5で説明したのと同様の信号のタイミングが図示されている。図7の例では、入力垂直同期信号100の入力垂直同期信号パルス220が、前ウインドウ信号103のアサートされている期間(前ウインドウ期間221)に到来しているので、前ウインドウ検出信号106がアサートされる(222)。そして、後ウインドウ信号105の終了のタイミング223の時点で、低速化要求信号108がアサートされる(224)。垂直走査カウンタ41のカウント終了タイミング225においては、「出力周期+補正幅」がロードされる。結果として、フレーム#3では垂直走査の周波数が遅く変更され、入出力の垂直同期信号がより離れるように補正される。後ウインドウ信号のアサート期間に入力垂直同期信号100のパルスが到来した場合も、第一実施形態同様に高速化要求信号109がアサートされ、入出力の垂直同期信号がより離れるように補正される。

20

#### 【0043】

以上の動作により、入力垂直同期信号をロック期間の方向に近付けるように補正が行なわれる。この制御を非ロック期間に入力垂直同期信号が存在しなくなるまで繰り返すことで、任意の位相に設定したロック期間に入力垂直同期信号を引き込むことができる。

#### 【0044】

以上説明したように、第二実施形態によれば、垂直同期信号入力の検出ウインドウを前後非対称の幅にして出力周期補正することで、簡素な構成で、同期ずれ補正に加えて出力位相制御を実現でき。

#### 【0045】

30

[他の実施形態]

なお、本発明は、上述の実施形態に限定されるものではなく、幅広く応用することが可能である。例えば、上記各実施形態においては、低速化要求信号108や高速化要求信号109に対して同一の補正幅(adjval)を用いたがこれに限られるものではなく、周波数を高速化する場合と低速化する場合で異なる値の補正幅を用いるようにしてもよい。

#### 【0046】

また、前ウインドウ期間や後ウインドウ期間を複数の部分に区切り、細分化された部分期間毎に異なる補正幅を割り当て、入力垂直同期信号が存在する部分期間に割り当てられている補正幅を用いるようにしてもよい。この場合、たとえば、出力垂直同期信号に近い部分期間ほど大きい補正幅を割り当てるにより、引き込み時間(入力垂直同期信号をロック期間へ移動させるための時間)をより短くすることができる。

40

#### 【0047】

また、上記各実施形態では隣接する垂直同期信号間の水平走査ライン数の増減によって周期補正を行なう例を説明したが、隣接する水平同期信号間を構成するクロックサイクル数の増減によって周期補正するようにしてもよい。すなわち、周期補正部34は、近接判定部32により低速化要求信号108がアサートされると、水平走査カウンタ40に「ロック時の水平周期+補正幅」を設定する。水平走査カウンタ40は、設定された「ロック時の水平周期+補正幅」だけビデオクロックをカウントすると、水平同期信号を出力する。垂直走査カウンタ41はこの水平同期信号をカウントして垂直同期信号を出力するため、結果として、垂直同期信号の出力が「補正幅」に応じて遅れる。同様に、周期補正部3

50

4は、近接判定部32により高速化要求信号109がアサートされると、水平走査カウンタ40に「ロック時の水平周期 - 補正幅」を設定する。水平走査カウンタ40は、設定された「ロック時の水平周期 - 補正幅」だけビデオクロックをカウントすると、水平同期信号を出力する。結果として、垂直走査カウンタ41による垂直同期信号の出力が「補正幅」に応じて早まる。

#### 【0048】

また、上記各実施形態において、低速化要求信号108や高速化要求信号109に対して別々の補正方法を用いるようにしてもよい。たとえば、低速化要求信号108に関しては、垂直同期信号間の水平ライン数を増加させ、高速化要求信号109では、水平同期信号間のクロックサイクル数を減少させるようにしてもよい。更に、上述した、細分化された部分期間毎に、上記の補正方法を設定するようにしてもよい。

10

#### 【0049】

なお、本発明は、複数の機器から構成されるシステムの1部として適用しても、1つの機器からなる装置の1部に適用してもよい。

#### 【0050】

また、本発明は、以下の処理を実行することによっても実現される。即ち、上述した実施形態の機能を実現するソフトウェア（プログラム）を、ネットワーク又は各種記憶媒体を介してシステム或いは装置に供給し、そのシステム或いは装置のコンピュータ（またはCPUやMPU等）がプログラムを読み出して実行する処理である。

【図1】

【図2】

---

フロントページの続き

(72)発明者 砂川 伸一

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 大室 秀明

(56)参考文献 特開2003-116110(JP,A)

特開2002-055643(JP,A)

特開2011-061323(JP,A)

(58)調査した分野(Int.Cl., DB名)

G09G 3/00 - 3/08

G09G 3/12

G09G 3/16

G09G 3/19 - 3/26

G09G 3/30

G09G 3/34

G09G 3/38 - 5/36

G09G 5/377 - 5/42

H04N 5/04 - 5/12

H04N 5/66 - 5/74