(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5939184号

(P5939184)

(45) 発行日 平成28年6月22日(2016.6.22)

(24) 登録日 平成28年5月27日(2016.5.27)

|               |           |

|---------------|-----------|

| (51) Int.Cl.  | F 1       |

| HO 1 L 27/146 | (2006.01) |

| HO 1 L 21/02  | (2006.01) |

| HO 1 L 21/768 | (2006.01) |

| HO 1 L 27/00  | (2006.01) |

| HO 4 N 5/374  | (2011.01) |

| HO 1 L        | 27/14     |

| HO 1 L        | 21/02     |

| HO 1 L        | 21/90     |

| HO 1 L        | 27/00     |

| HO 4 N        | 5/335     |

|               | 301 B     |

|               | 740       |

請求項の数 5 (全 16 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2013-60691 (P2013-60691)    |

| (22) 出願日  | 平成25年3月22日(2013.3.22)         |

| (65) 公開番号 | 特開2014-187166 (P2014-187166A) |

| (43) 公開日  | 平成26年10月2日(2014.10.2)         |

| 審査請求日     | 平成27年1月29日(2015.1.29)         |

|           |                                        |

|-----------|----------------------------------------|

| (73) 特許権者 | 000002185<br>ソニー株式会社<br>東京都港区港南1丁目7番1号 |

| (74) 代理人  | 100082131<br>弁理士 稲本 義雄                 |

| (74) 代理人  | 100121131<br>弁理士 西川 孝                  |

| (72) 発明者  | 藤井 宣年<br>東京都港区港南1丁目7番1号 ソニー株式会社内       |

| (72) 発明者  | 萩本 賢哉<br>東京都港区港南1丁目7番1号 ソニー株式会社内       |

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体装置の製造方法において、

電極および絶縁膜が露出された貼合せ面を有する 2 枚の基板のうち少なくとも一方の貼合せ面を覆う状態で、絶縁性薄膜を成膜し、

前記絶縁性薄膜を介して前記 2 枚の基板の貼合せ面同士を対向配置し、

前記 2 枚の基板の電極同士が前記絶縁性薄膜を介して電気的に接続される状態に位置合わせをして、前記 2 枚の基板を貼り合わせ、

貼り合わされた前記 2 枚の基板を、前記電極の成膜温度よりも高温で熱処理して、前記電極同士で狭持された絶縁性薄膜を、対応する電極それを構成する金属の結晶粒成長による変形・移動によって破壊し、前記電極同士を直接接触させる

製造方法。

## 【請求項 2】

前記 2 枚の基板の両方に、前記絶縁性薄膜を成膜する

請求項 1 に記載の製造方法。

## 【請求項 3】

前記 2 枚の基板の両方に、同じ材料からなる前記絶縁性薄膜を成膜する

請求項 1 または 2 に記載の製造方法。

## 【請求項 4】

原子層堆積法により前記絶縁性薄膜を成膜する

10

20

請求項1から3のいずれかに記載の製造方法。

【請求項5】

前記2枚の基板の貼合せ面は、平坦化処理によって形成されている

請求項1から4のいずれかに記載の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、半導体装置の製造方法に関し、特に、電極同士が電気的に接合された状態で2枚の基板を貼り合わせて構成される半導体装置の製造方法に関する。

【背景技術】

【0002】

従来、2次元構造の半導体装置の高集化は、微細プロセスの導入と実装密度の向上によって実現されてきたが、これらによる2次元構造の高集化には物理的な限界がある。そこで、さらなる半導体装置の小型化および画素の高密度化を実現するため、3次元構造の半導体装置が開発されている。例えば、特許文献1には、光電変換部を有するセンサ基板と周辺回路部を有する回路基板とを積層させて貼り合わせてなる3次元構造の半導体装置が提案されている。

【0003】

上述の3次元構造の半導体装置は、Cu電極と絶縁膜とを露出させた貼合せ面を有する基板を2枚用いて、貼合せ面を対向させた状態でCu電極同士を位置合わせし、さらに熱処理することにより、基板同士を貼り合わせて作製される。このようにCu電極を直接接合(Cu-Cu接合)することによって、基板を積層して貼り合わせてなる3次元構造の半導体装置がある(例えば、特許文献2乃至5参照)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2006-191081号公報

【特許文献2】特開2000-299379号公報

【特許文献3】特表2006-522461号公報

【特許文献4】特開2010-129576号公報

【特許文献5】特開2012-256736号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、上述した3次元構造の半導体装置は、製造工程中のCu電極同士の位置合わせにおいて生じるズレや、またはCu電極の形状や大きさの違い等により、Cu電極と絶縁膜との接合面が形成される。このCu電極と絶縁膜が接合される接合面においては、ボイドが発生する。そのため、接合面の貼合せ強度の低下による基板間の剥がれ等の問題点が生じる。

【0006】

本開示はこのような状況に鑑みてなされたものであり、2枚の基板を貼り合わせて電極同士を接合させた構成において、基板の接合面でのボイドの発生を防止して、基板間の貼合せ強度の向上が図られた3次元構造の半導体装置を提供できるようにするものである。

【課題を解決するための手段】

【0013】

本開示の第2の側面である製造方法は、半導体装置の製造方法において、電極および絶縁膜が露出された貼合せ面を有する2枚の基板のうち少なくとも一方の貼合せ面を覆う状態で、絶縁性薄膜を成膜し、前記絶縁性薄膜を介して前記2枚の基板の貼合せ面同士を対向配置し、前記2枚の基板の電極同士が前記絶縁性薄膜を介して電気的に接続される状態に位置合わせをして、前記2枚の基板を貼り合わせ、貼り合わされた前記2枚の基板を、

10

20

30

40

50

前記電極の成膜温度よりも高温で熱処理して、前記電極同士で狭持された絶縁性薄膜を、対応する電極それぞれを構成する金属の結晶粒成長による変形・移動によって破壊し、前記電極同士を直接接触させる。

【0016】

前記2枚の基板の両方に、前記絶縁性薄膜を成膜することができる。

【0017】

前記2枚の基板の両方に、同じ材料からなる前記絶縁性薄膜を成膜することができる。

【0018】

原子層堆積法により前記絶縁性薄膜を成膜することができる。

【0019】

前記2枚の基板の貼合せ面は、平坦化処理によって形成することができる。

10

【発明の効果】

【0020】

本開示によれば、2枚の基板を貼り合わせて電極同士を接続させた構成において、接合界面におけるボイドの発生を防止でき、これにより2枚の基板間の接合強度が増して信頼性の向上が図られた半導体装置を得ることが可能になる。

【図面の簡単な説明】

【0021】

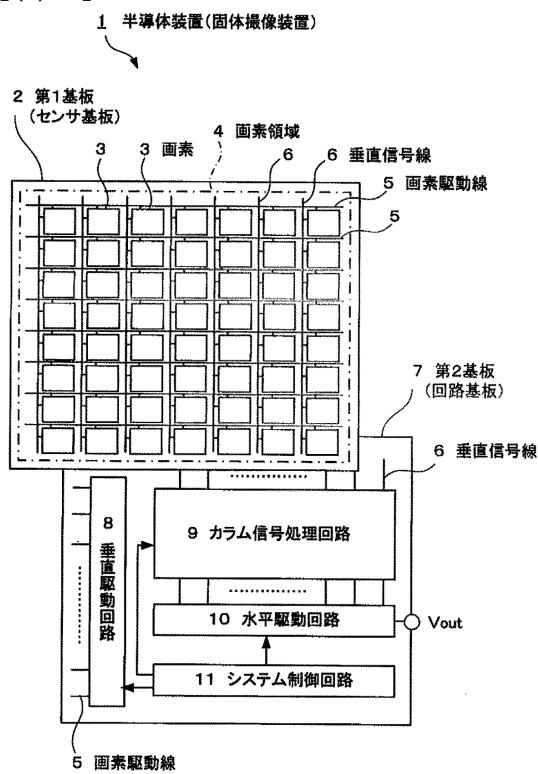

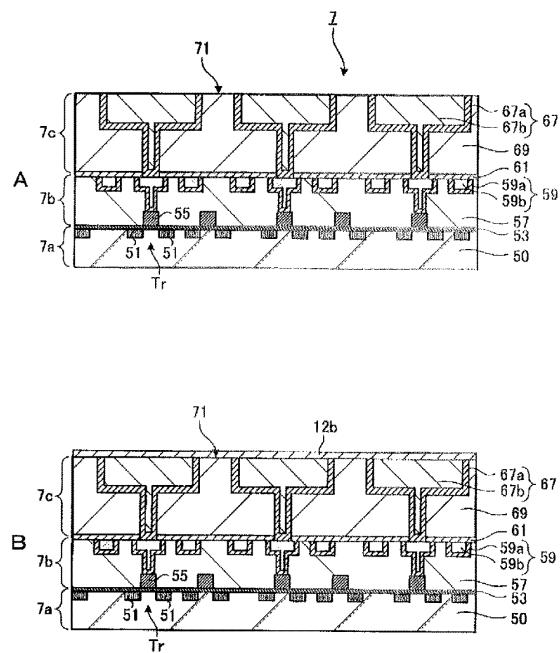

【図1】本開示が適用される半導体装置の一例を示す概略構成図である。

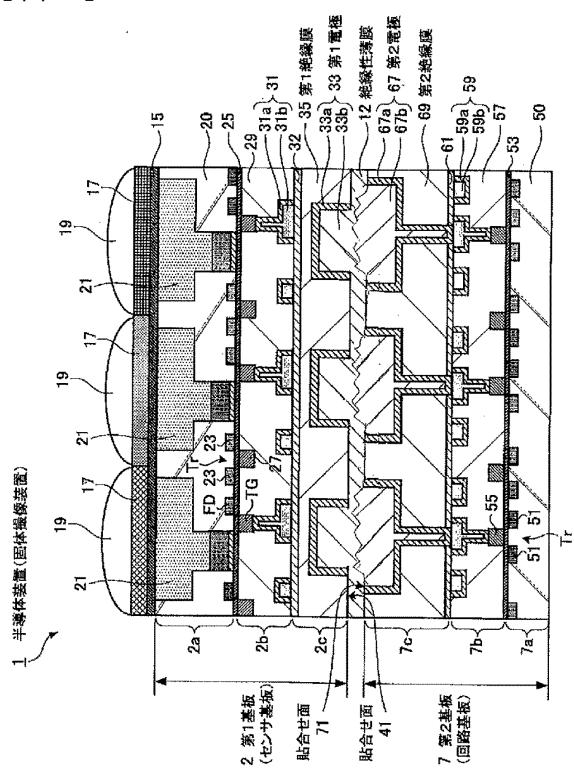

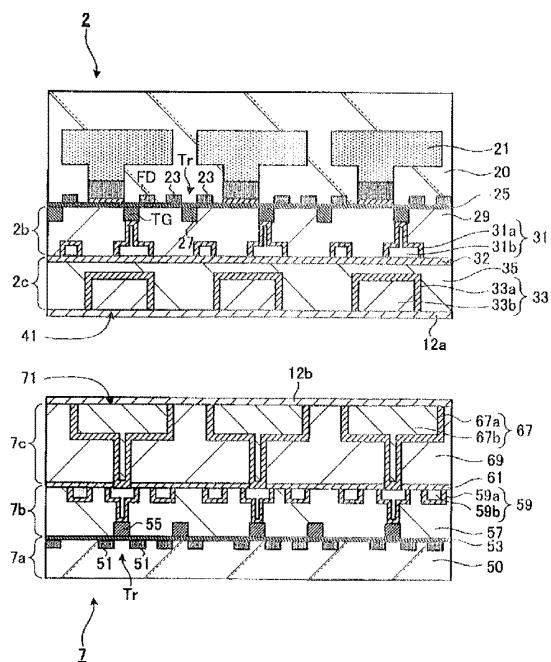

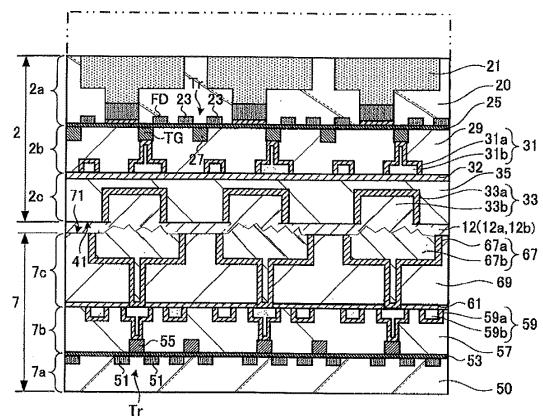

【図2】本実施形態の半導体装置の構成を示す要部断面図である。

20

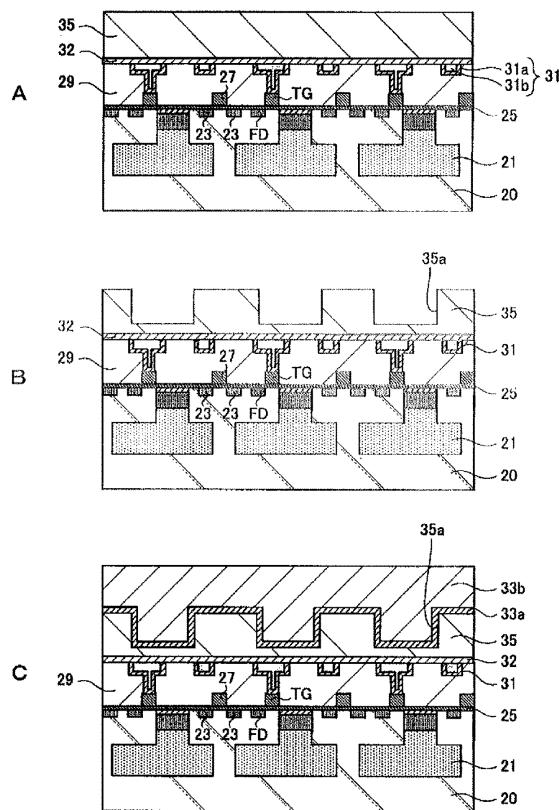

【図3】本実施形態の半導体装置の製造における第1基板（センサ基板）の作製手順（その1）を示す断面工程図である。

【図4】本実施形態の半導体装置の製造における第1基板（センサ基板）の作製手順（その2）を示す断面工程図である。

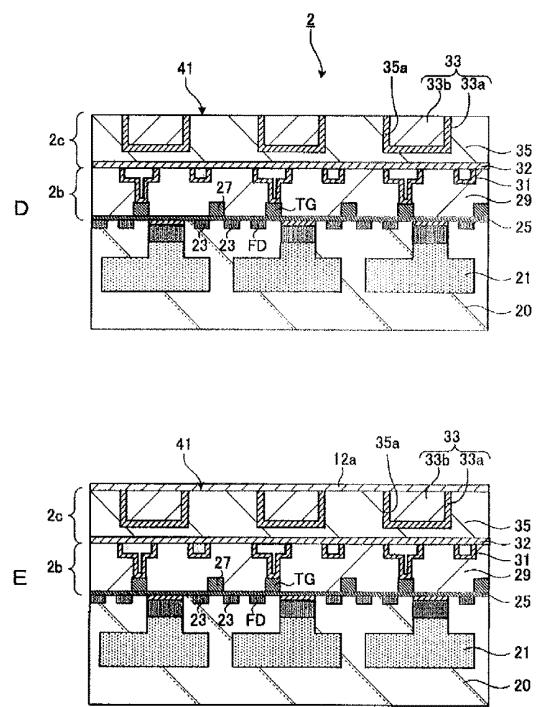

【図5】本実施形態の半導体装置の製造における第2基板（回路基板）の作製手順を示す断面工程図である。

【図6】本実施形態の半導体装置の製造における貼り合わせを示す断面図（その1）である。

【図7】本実施形態の半導体装置の製造における貼り合わせを示す断面図（その2）である。

30

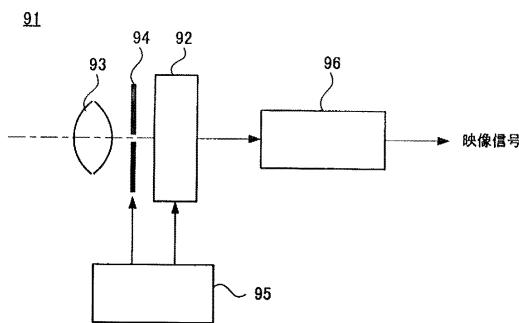

【図8】本開示を適用して得られた半導体装置を用いた電子機器の構成図である。

【発明を実施するための形態】

【0022】

以下、本開示の実施の形態を、図面に基づいて次に示す順に説明する。

1. 本実施形態の半導体装置の概略構成例

2. 本実施形態の半導体装置の構成

3. 本実施形態の半導体装置の製造における第1基板（センサ基板）の作製手順

4. 本実施形態の半導体装置の製造における第2基板（回路基板）の作製手順

5. 本実施形態の半導体装置の製造における基板の貼り合わせ手順

6. 本実施形態の半導体装置を用いた電子機器の一例

40

【0023】

1. 本実施形態の半導体装置の概略構成例

図1に、本開示が適用される半導体装置の一例として、固体撮像装置の概略構成を示す。

【0024】

この固体撮像装置1は、センサ基板としての第1基板2と、この第1基板2に対して積層された状態で貼り合せられた回路基板としての第2基板7とを含む、いわゆる3次元構造の半導体装置である。

【0025】

このうち、第1基板2には、光電変換部を含む複数の画素3が規則的に2次元配列され

50

た画素領域4が設けられている。この画素領域4には、複数の画素駆動線5が行方向に配線され、複数の垂直信号線6が列方向に配線されており、1つの画素3が1本の画素駆動線5と1本の垂直信号線6とに接続される状態で配置されている。これらの各画素3には、光電変換部と、フローティングディフュージョンと、複数のトランジスタ（いわゆるMOSトランジスタ）および容量素子等で構成された画素回路とが設けられている。なお、複数の画素で画素回路の一部を共有している場合もある。

【0026】

また、第2基板7には、第1基板2に設けられた各画素3を駆動するための垂直駆動回路8、カラム信号処理回路9、水平駆動回路10、およびシステム制御回路11などの周辺回路が設けられている。

10

【0027】

2. 本実施形態の半導体装置の構成

図2は、本実施形態の半導体装置の構成を示す要部断面図であり、図1における3画素分の断面図である。以下、この要部断面図に基づいて、本実施形態の半導体装置の詳細な構成を説明する。

【0028】

図2に示す半導体装置1は、絶縁性薄膜12を挟持する状態で第1基板2の貼合せ面41と第2基板7の貼合せ面71が対向配置されて、第1基板2と第2基板7とが貼り合わせられた3次元構造の固体撮像装置である。

20

【0029】

ここで、第1基板2は、半導体層2a、配線層2b、および電極層2cが、第2基板7とは反対側から順に積層されており、さらに電極層2cの表面が第2基板7に対する貼合せ面41として構成されている。一方、第2基板7は、半導体層7a、配線層7b、および電極層7cが、第1基板2の反対側から順に積層されており、さらに電極層7cの表面が第1基板2に対する貼合せ面71として構成されている。

【0030】

また、第1基板2における第2基板7と反対側の面には、保護膜15、カラーフィルタ層17、およびオンチップレンズ19が図示される順に積層されている。

【0031】

次に、第1基板2および第2基板7を構成する各層、および絶縁性薄膜12の詳細な構成を順次説明し、さらに、保護膜15、カラーフィルタ層17、およびオンチップレンズ19の構成を順次説明する。

30

【0032】

[半導体層2a(第1基板2側)]

第1基板2側の半導体層2aは、例えば単結晶シリコンからなる半導体基板20を薄膜化したものである。この半導体層2aにおいて、カラーフィルタ層17やオンチップレンズ19等が配置されている第1面側には、例えばn型不純物層（またはp型不純物層）からなる光電変換部21が画素毎に設けられている。一方、半導体層2aの第2面側には、n+型不純物層からなるフローティングディフュージョンFDおよびトランジスタTrのソース/ドレイン23、さらにはここでの図示を省略した他の不純物層などが設けられている。

40

【0033】

[配線層2b(第1基板2側)]

第1基板2において半導体層2a上に設けられた配線層2bは、半導体層2aとの界面側に、ゲート絶縁膜25を介して設けられた転送ゲートTGおよびトランジスタTrのゲート電極27、さらにはここでの図示を省略した他の電極を有している。これらの転送ゲートTGおよびゲート電極27は、層間絶縁膜29で覆われてあり、層間絶縁膜29に形成された溝パターン内には埋込配線31が設けられている。この埋込配線31は、溝パターンの内壁を覆うバリアメタル層31aと、バリアメタル層31aを介して溝パターンに埋め込まれた銅(Cu)からなる配線層31bにより構成されている。

50

## 【0034】

なお、以上のような配線層2bは、さらに積層された多層配線層として構成されていてもよい。

## 【0035】

## [電極層2c(第1基板2側)]

第1基板2において配線層2b上に設けられた電極層2cは、配線層2bとの界面側に、銅(Cu)に対する拡散防止絶縁膜32と、これに積層された第1絶縁膜35とを備えている。第1絶縁膜35は、例えばTEOS膜からなり、第1絶縁膜35に形成された溝パターン内には、埋込電極として第1電極33が設けられている。なおTEOS膜とは、TEOSガス(Tetra Ethoxy Silaneガス:組成Si(OCH<sub>3</sub>)<sub>4</sub>)を原料ガスとする化学気相成長法(Chemical Vapor Deposition:以下CVD法)により成膜された酸化シリコン膜である。

10

## 【0036】

そして、第1電極33は、溝パターンの内壁を覆うバリアメタル層33aと、バリアメタル層33aを介して溝パターンに埋め込まれた銅(Cu)からなる第1電極膜33bにより構成されている。また、少なくとも貼り合わせられる面となる電極層2cを形成する銅(Cu)は、貼り合わせ後の熱処理温度よりも低い温度で成膜されることが必要である。このような構成の電極層2cの表面が、第2基板7に対する第1基板2側の貼合せ面41となっている。貼合せ面41は、第1電極33および第1絶縁膜35が露出して構成されており、例えば化学的機械研磨(Chemical Mechanical Polishing:以下CMP)によって平坦化された状態となっている。

20

## 【0037】

なお、ここでの図示は省略したが、第1絶縁膜35に設けられた溝パターンの一部は、配線層2bに設けた埋込配線31に達しており、この溝パターン内部に埋め込まれた第1電極33が必要に応じて埋込配線31に接続された状態となっている。

## 【0038】

## [半導体層7a(第2基板7側)]

一方、第2基板7側の半導体層7aは、例えば単結晶シリコンからなる半導体基板50を薄膜化したものである。この半導体層7aにおいて、第1基板2側の表面層には、トランジスタTrのソース/ドレイン51、さらにはここでの図示を省略した不純物層などが設けられている。

30

## 【0039】

## [配線層7b(第2基板7側)]

第2基板7において半導体層7a上に設けられた配線層7bは、半導体層7aとの界面側に、ゲート絶縁膜53を介して設けられたゲート電極55、さらにはここでの図示を省略した他の電極を有している。これらのゲート電極55および他の電極は、層間絶縁膜57で覆われてあり、層間絶縁膜57に形成された溝パターン内には埋込配線59が設けられている。埋込配線59は、溝パターンの内壁を覆うバリアメタル層59aと、バリアメタル層59aを介して溝パターンに埋め込まれた銅(Cu)からなる配線層59bにより構成されている。

40

なお、以上のような配線層7bは、多層配線層構造としてもよい。

## 【0040】

## [電極層7c(第2基板7側)]

第2基板7において配線層7b上に設けられた電極層7cは、配線層7bとの界面側に、銅(Cu)に対する拡散防止絶縁膜61と、この上部に積層された第2絶縁膜69とを備えている。第2絶縁膜69は例えばTEOS膜からなり、第2絶縁膜69に形成された溝パターン内には、埋込電極として第2電極67が設けられている。第2電極67は、溝パターンの内壁を覆うバリアメタル層67aと、バリアメタル層67aを介して溝パターンに埋め込まれた銅(Cu)からなる第2電極膜67bにより構成されている。

## 【0041】

50

また、第1基板2とともに、少なくとも貼り合わせられる面となる電極層7cを形成する銅(Cu)は、貼り合わせ後の熱処理温度よりも低い温度で成膜されることが必要である。この第2電極67は、第1基板2側の第1電極33と対応するように配置され、絶縁性薄膜12を介した状態で第1基板2側の第1電極33と電気的に接続される。このような電極層7cの表面が、第1基板2に対する第2基板7側の貼合せ面71となっている。貼合せ面71は、第2電極67および第2絶縁膜69が露出して構成されており、例えばCMPによって平坦化された状態となっている。

#### 【0042】

##### [絶縁性薄膜12]

絶縁性薄膜12は、第1基板2側の貼合せ面41と第2基板7側の貼合せ面71との間に狭持されており、貼合せ面41および貼合せ面71の全面を覆っている。すなわち、第1基板2と第2基板7とは、この絶縁性薄膜12を介して貼り合わされる。貼り合わされた第1基板2と第2基板7を銅(Cu)の成膜温度よりも高い温度で熱処理することにより、銅(Cu)の結晶粒が移動し、絶縁性薄膜を破壊することが可能となる。このときの熱処理温度は、銅(Cu)の成膜温度との差が大きいほど絶縁性薄膜12を破壊することが可能である。すなわち、銅(Cu)の結晶粒成長がより大きくなる為である。また、絶縁性薄膜12は銅(Cu)の存在する箇所のみで破壊されるため、電極以外の部分は絶縁性を保つことができる。

#### 【0043】

上述のような絶縁性薄膜12は、例えば、酸化膜および窒化膜からなり、半導体に一般的に使用されている酸化膜および窒化膜が用いられる。ただし、前述のとおり、貼り合わせ後に銅(Cu)の結晶粒成長によって絶縁性薄膜12を破壊するため、絶縁性薄膜12の成膜時に銅(Cu)の結晶粒成長を促進してはいけない。そのため、この成膜は銅(Cu)の成膜を含む、接合面にくる電極形時の温度以下にする必要がある。絶縁性薄膜12の構成材料について詳しく説明する。

#### 【0044】

絶縁性薄膜12が酸化膜からなる場合は、例えば、酸化シリコン(SiO<sub>2</sub>)、酸化ハフニウム(HfO<sub>2</sub>)を用いる。

#### 【0045】

絶縁性薄膜12が窒化膜からなる場合は、例えば、窒化シリコン(SiN)を用いる。

#### 【0046】

また特に本実施形態では、絶縁性薄膜12を介した状態で、第1基板2側の第1電極33と第2基板7側の第2電極67とが貼り合わされた後に熱処理され、電極部分の絶縁性薄膜12が破壊されて、電極同士が直接接続されることが重要である。そのため、絶縁性薄膜12の膜厚は極めて薄い。その膜厚は、絶縁性薄膜12の材料により異なるものの、例えば、酸化シリコン(SiO<sub>2</sub>)、ハフニア(HfO<sub>2</sub>)等の酸化物や、その他のほとんどの材料において、およそ1nm以下が望ましい。これは、例えば銅(Cu)の成膜温度を150で行った後に400の熱処理をした場合に銅(Cu)の表面が結晶粒成長によって変化する量から決定される。ただし、絶縁性薄膜12の膜質および成膜温度と熱処理の温度差によっては、さらに厚い膜を用いることも可能である。このような方法で直接接觸された第1電極33と第2電極67との間は完全な導通状態となり電流が流れる。

#### 【0047】

なお、本実施形態の半導体装置1において、絶縁性薄膜12は、上述の一層の構造に限らず、同じ材料による積層構造であってもよく、また異なる材料による積層構造であってもよい。

#### 【0048】

##### [保護膜15、カラーフィルタ層17、オンチップレンズ19]

保護膜15は、第1基板2の光電変換部21を覆って設けられている。この保護膜15は、パッシベーション性を有する材料膜で構成され、例えば酸化シリコン膜、窒化シリコン膜、または酸窒化シリコン膜などが用いられる。

10

20

30

40

50

カラーフィルタ層 17 は、各光電変換部 21 に対応して 1 対 1 で設けられた各色のカラーフィルタで構成されている。各色のカラーフィルタの配列が限定されることはない。

オンチップレンズ 19 は、各光電変換部 21 およびカラーフィルタ層 17 を構成する各色のカラーフィルタに対応して 1 対 1 で設けられ、各光電変換部 21 に入射光が集光されるように構成されている。

#### 【0049】

##### [本実施形態の半導体装置の構成による効果]

上述のように構成された本実施形態の半導体装置 1 は、図 2 に示すように、絶縁性薄膜 12 を介して第 1 基板 2 と第 2 基板 7 とが貼り合わせられたことにより、第 1 基板 2 の貼合せ面 41 と第 2 基板 7 の貼合せ面 71 とが直接接することはない。したがって、これらの貼合せ面が直接接合された構成において接合界面に生じていたボイドの発生が防止される。これにより、2 枚の基板間の接合強度が増して信頼性の向上が図られた半導体装置を得ることが可能になる。

#### 【0050】

特に第 1 絶縁膜 35 および第 2 絶縁膜 69 が TEOS 膜からなる場合には、TEOS 膜表面に OH 基が多く存在するため、TEOS 膜からなる絶縁膜同士が直接接合する接合界面において、脱水縮合によるボイドが発生する。このように絶縁膜が TEOS 膜である場合においても、本実施形態の半導体装置 1 では、絶縁性薄膜 12 を介して基板を貼り合わせるので、TEOS 膜同士が直接接合することなく、脱水縮合によるボイドの発生を防止できる。これにより、2 枚の基板間の接合強度が増して信頼性の向上が図られた半導体装置を得ることが可能になる。

#### 【0051】

##### 3. 本実施形態の半導体装置の製造における第 1 基板（センサ基板）の作製手順

図 3 は上述した本実施形態の半導体装置の製造に用いる第 1 基板 2 の作製手順を示す断面工程図（その 1）であり、図 4 はこの図 3 に続く断面工程図（その 2）である。以下、これらの図に基づいて本実施形態に用いる第 1 基板 2（センサ基板）の作製手順を説明する。

#### 【0052】

図 3A に示すように、例えば単結晶シリコンからなる半導体基板 20 を用意する。この半導体基板 20 の所定深さに n 型不純物層からなる光電変換部 21 を形成し、さらに光電変換部 21 の表面層に、n<sup>+</sup> 型不純物層からなる電荷転送部や p<sup>+</sup> 型不純物層からなる正孔用の電荷蓄積部を形成する。また半導体基板 20 の表面層に、n<sup>+</sup> 型不純物層からなるフローティングディフュージョン FD、およびソース／ドレイン 23、さらにはここでの図示を省略した他の不純物層を形成する。

#### 【0053】

次に、半導体基板 20 上に、ゲート絶縁膜 25 を成膜し、さらにこの上部に転送ゲート TG およびゲート電極 27 を形成する。ここで、転送ゲート TG はフローティングディフュージョン FD と光電変換部 21 との間に形成され、ゲート電極 27 は、ソース／ドレイン 23 間に形成される。またこれと同一工程により、ここでの図示を省略した他の電極を形成する。

なお、ここまで工程は、通常の作製手順を適宜選択して行なってもよい。

#### 【0054】

その後、ゲート絶縁膜 25 上に、転送ゲート TG およびゲート電極 27 を覆う状態で、例えば酸化シリコンからなる層間絶縁膜 29 を成膜する。さらに層間絶縁膜 29 に溝パターンを形成し、この溝パターン内にバリアメタル層 31a を介して配線層 31b を埋め込んでなる埋込配線 31 を形成する。この埋込配線 31 は、必要箇所で転送ゲート TG に接続して形成される。またここでの図示は省略したが、一部の埋込配線 31 は、必要箇所でソース／ドレイン 23 に接続して形成される。以上により、埋込配線 31 を備えた配線層 2b を得る。なお、この埋込配線 31 の形成には、図 3B 以下を用いて説明する埋込配線技術を適用する。

10

20

30

40

50

## 【0055】

続いて、配線層2b上に、拡散防止絶縁膜32を成膜し、さらにこの上に第1絶縁膜35を成膜する。例えばTEOSガスを用いたCVD法により、TEOS膜からなる第1絶縁膜35を成膜する。その後、この第1絶縁膜35に、以下に説明する埋込配線技術を適用して、第1電極33を形成する。

## 【0056】

図3Bに示すように、第1絶縁膜35に溝パターン35aを形成する。ここでの図示は省略したが、溝パターン35aは、必要な箇所では埋込配線31に達する形状で形成される。

## 【0057】

図3Cに示すように、溝パターン35aの内壁を覆う状態でバリアメタル層33aを成膜し、この上部に溝パターン35aを埋め込む状態で第1電極膜33bを成膜する。バリアメタル層33aは、第1電極膜33bが第1絶縁膜35に拡散することを防ぐようなバリア性のある材料で構成され、一方、第1電極膜33bは銅(Cu)からなるが、これに限らず、導電性のある材料により構成される。

## 【0058】

図4Dに示すように、CMP法により、バリアメタル層33aが露出するまで第1電極膜33bを平坦化除去し、さらに、第1絶縁膜35が露出するまでバリアメタル層33aを平坦化除去する。これにより、溝パターン35a内にバリアメタル層33aを介して第1電極膜33bを埋め込んでなる第1電極33を形成する。以上により、第1電極33を備えた電極層2cを得る。

## 【0059】

以上の工程により、第1電極33と第1絶縁膜35とが露出された平坦な貼合せ面41を有する第1基板2が、センサ基板として作製される。なお、必要に応じて、貼合せ面41に対して、ウェット処理またはプラズマ処理による前処理を施しておく。

ここまで工程は、一般的な半導体装置の製造工程手順で行えばよく、また特に工程手順が限定されることではなく、適宜の手順で行うことができる。ただし、貼り合わせ面となる第1電極33の形成において、銅(Cu)の成膜温度は例えば100度に低くし、貼り合わせ後の熱処理温度(例えば400度)との温度差を可能な限り大きくする。本開示では、次の絶縁性薄膜の成膜が特徴的な工程となる。

## 【0060】

## [絶縁性薄膜の成膜手順]

図4Eに示すように、第1基板2における貼合せ面41の全面を覆う状態で、原子層堆積法(Atomic Layer Deposition: 以下ALD法)によって絶縁性薄膜12aを成膜する。

## 【0061】

ALD法の手順について、概略を説明する。

まず、成膜される薄膜の構成元素を含有する第1反応物と第2反応物とを準備する。成膜工程として、基板上に、第1反応物を含むガスを供給して吸着反応させる第1工程と、第2反応物を含むガス供給して吸着反応させる第2工程とがあり、この工程の間には不活性ガスを流して、未吸着の反応物をバージする。この成膜工程を1サイクル行なうことで原子層1層を堆積させ、繰り返すことにより所望膜厚の成膜をする。なお、第1工程と第2工程は、どちらを先に行なってもよい。

以上のような成膜方法がALD法であり、次のような特徴がある。

## 【0062】

ALD法は、上述のように、成膜工程のサイクルを繰り返して成膜する方法であり、このサイクル数の調整によって、成膜する膜厚を原子層単位で高精度に制御した成膜が可能である。このようなALD法を絶縁性薄膜12aの成膜に適用すると、極めて薄い絶縁性薄膜12aであっても膜厚制御性よく成膜できる。

## 【0063】

10

20

30

40

50

ALD法は、さらに約500℃以下の低温プロセスでの成膜が可能な方法である。さらにSiO<sub>2</sub>などでは室温での成膜も可能となっている。絶縁性薄膜12aの成膜時には、すでに電極層2cが形成されているため、電極層2cを構成する金属への耐熱性を考慮する必要があり、絶縁性薄膜12aの成膜には低温プロセスが要求される。そこで、このようなALD法を絶縁性薄膜12aの成膜に適用すると、低温プロセスにより電極層2cを劣化させることなく絶縁性薄膜12aを成膜できる。

#### 【0064】

ALD法は、上述のように、原子層を1層ずつ堆積させて成膜する方法である。このようなALD法を絶縁性薄膜12aの成膜に適用すると、CMPにより超平坦化された基板表面の凹凸を悪化させることなく、平坦かつ均一な絶縁性薄膜12aで貼合せ面41の全面を覆うことができる。10

#### 【0065】

以下に、一例として、酸化膜または窒化膜からなる絶縁性薄膜12aのALD法による成膜条件について、具体的に説明する。

#### 【0066】

絶縁性薄膜12aが酸化膜(SiO<sub>2</sub>、HfO<sub>2</sub>等)からなる場合、上述のALD法において、第1反応物をSi含有反応物またはHf含有反応物とし、第2反応物をO含有反応物とする。これらの反応物を供給して吸着反応させる工程を交互に繰り返すことによって、酸化膜(SiO<sub>2</sub>またはHfO<sub>2</sub>)からなる絶縁性薄膜12aを貼合せ面41上に成膜する。ここで、Si含有反応物は、例えば、シラン(SiH<sub>4</sub>)、ジクロロシラン(H<sub>2</sub>SiCl<sub>2</sub>)等のガス状で供給可能な物質を用いる。Hf含有反応物は、テトラキスジメチルアミノハフニウム(Hf[N(CH<sub>3</sub>)<sub>2</sub>]<sub>4</sub>等を用いる。O含有反応物は、水蒸気ガス、オゾンガス等を用いる。20

#### 【0067】

一方、絶縁性薄膜12aが窒化膜(SiN等)からなる場合、上述のALD法において、第1反応物をSi含有反応物とし、第2反応物をN含有反応物とする。これらの反応物を供給して吸着反応させる工程を交互に繰り返すことによって、窒化膜(SiN)からなる絶縁性薄膜12aを貼合せ面41上に成膜する。ここで、N含有反応物は、例えば、窒素ガスやアンモニアガス等を用いる。O含有反応物は、水蒸気ガス、オゾンガス等を用いる。30

#### 【0068】

以上により、第1基板2上に、貼合せ面41の全面を覆う状態で、極めて薄い均一な絶縁性薄膜12aを成膜する。

#### 【0069】

##### 4. 本実施形態の半導体装置の製造における第2基板(回路基板)の作製手順

図5は、上述した本実施形態の半導体装置の製造に用いる第2基板7の作製手順を説明するための断面工程図である。以下、この図に基づいて本実施形態に用いる第2基板7(回路基板)の作製手順を説明する。

#### 【0070】

図5Aに示すように、例えば単結晶シリコンからなる半導体基板50を用意する。この半導体基板50の表面層に、各導電型のソース/ドレイン51、およびここでの図示を省略した他の不純物層を形成する。これにより、半導体層7aを得る。40

#### 【0071】

次に、半導体層7aの上に、ゲート絶縁膜53を成膜し、さらにこの上部にゲート電極55を形成する。ゲート電極55は、ソース/ドレイン51間に形成される。また、これと同一工程で、ここでの図示を省略した他の電極を形成する。

#### 【0072】

続いて、ゲート絶縁膜53の上に、ゲート電極55を覆う状態で、例えば酸化シリコンからなる層間絶縁膜57を成膜する。この層間絶縁膜57の溝パターン内にバリアメタル層59aを介して配線層59bを埋め込んでなる埋込配線59を形成し、埋込配線59を50

備えた配線層 7 b を得る。ここで埋込配線 5 9 の形成は、上述した第 1 電極 3 3 の形成と同様に、埋込配線技術を適用して行なう。

【 0 0 7 3 】

その後、配線層 7 b 上に拡散防止絶縁膜 6 1 を介して、例えば T E O S 膜からなる第 2 絶縁膜 6 9 を積層させて成膜する。これにより、第 2 絶縁膜 6 9 の溝パターン内にバリアメタル層 6 7 a を介して第 2 電極膜 6 7 b を埋め込んでなる第 2 電極 6 7 を形成し、第 2 電極 6 7 を備えた電極層 7 c を得る。ここで第 2 電極 6 7 の形成は、上述した第 1 電極 3 3 の形成と同様にして行なう。

【 0 0 7 4 】

以上の工程により、第 2 電極 6 7 と第 2 絶縁膜 6 9 とが露出された平坦な貼合せ面 7 1 を有する第 2 基板 7 が、回路基板として作製される。

ここまで工程は、通常の工程手順で行えばよく、また特に工程手順が限定されることなく、適宜の手順で行なうことができる。ただし、貼り合わせ面となる第 2 電極 6 7 の形成において、銅 ( C u ) の成膜温度は例えば 100 度に低くし、貼り合わせ後の熱処理温度 ( 例えば 400 度 ) との温度差を可能な限り大きくする。本開示では、次の絶縁性薄膜の成膜、および基板の貼り合わせが特徴的な工程となる。

【 0 0 7 5 】

図 5 B に示すように、第 1 基板 2 側の絶縁性薄膜 1 2 a と同様にして、貼合せ面 7 1 の上に、 A L D 法により絶縁性薄膜 1 2 b を成膜する。

これにより、第 2 基板 7 上に、貼合せ面 7 1 の全面を覆う状態で、極めて薄い均一な絶縁性薄膜 1 2 b を成膜する。なお、絶縁性薄膜 1 2 b は、第 1 基板 2 側の絶縁性薄膜 1 2 a と異なる膜でもよいが、同じ膜でもよい。

【 0 0 7 6 】

5. 本実施形態の半導体装置の製造における基板の貼り合わせ手順

図 6 および図 7 を用いて、貼合せ面 4 1 上に絶縁性薄膜 1 2 a を成膜した第 1 基板 2 と、貼合せ面 7 1 上に絶縁性薄膜 1 2 b を成膜した第 2 基板 7 との貼り合わせ手順を説明する。

【 0 0 7 7 】

図 6 に示すように、絶縁性薄膜を介した状態で第 1 基板 2 の貼合せ面 4 1 と第 2 基板 7 の貼合せ面 7 1 とを対向配置させ、さらに、第 1 基板 2 の第 1 電極 3 3 と、第 2 基板 7 の第 2 電極 6 7 とが対応するように位置合わせする。図示した例では、第 1 電極 3 3 と第 2 電極 6 7 とが 1 : 1 で対応している状態を示したが、対応状態はこれに限定されることはない。

【 0 0 7 8 】

図 7 に示すように、第 1 基板 2 上の絶縁性薄膜 1 2 a と、第 2 基板 7 上の絶縁性薄膜 1 2 b とを対向させた状態で熱処理を行うことにより、絶縁性薄膜 1 2 a と絶縁性薄膜 1 2 b との間の接合をする。このような熱処理は、第 1 基板 2 および第 2 基板 7 に形成された素子や配線に影響のない範囲で、絶縁性薄膜 1 2 同士が十分に接合する温度および時間で行われる。さらにこのとき、銅 ( C u ) の結晶粒成長が発生し、第 1 電極 3 3 と第 2 電極 6 7 の間の絶縁性薄膜 1 2 を両側から破壊する。これにより、電極の銅 ( C u ) 同士が直接接触する。

【 0 0 7 9 】

例えば、第 1 電極 3 3 および第 2 電極 6 7 が、銅 ( C u ) を主とする材料で構成される場合、200 ~ 600 度で 15 分 ~ 5 時間程度の熱処理が行われる。このような熱処理は、加圧雰囲気下で行ってもよく、または、第 1 基板 2 と第 2 基板 7 とを両面側から押圧した状態で行ってもよい。一例として、400 度で 4 時間の熱処理を行うことで、絶縁性薄膜 1 2 を介した第 1 電極 3 3 と第 2 電極 6 7 との間の接続を行なう。これにより、絶縁性薄膜 1 2 a と絶縁性薄膜 1 2 b との間が接合され、第 1 基板 2 と第 2 基板 7 とが貼り合わせられる。ここで、銅 ( C u ) の成膜時の温度と熱処理の温度差が大きいほど、銅 ( C u ) の結晶粒成長を促進できるため、絶縁性薄膜 1 2 の破壊が容易になる。

10

20

30

40

50

## 【0080】

ここで、上述のように第1基板2および第2基板7の両方の貼合せ面41, 71上に絶縁性薄膜12a, 12bが成膜される場合は、その絶縁性薄膜12a, 12bが同じ材料であっても、異なる材料であってもよい。

## 【0081】

なお、本実施形態の半導体装置の製造方法では、第1基板2および第2基板7のうちどちらか一方の基板の貼合せ面のみに絶縁性薄膜を成膜してもよい。例えば、第1基板2の貼合せ面41上のみに絶縁性薄膜12aを成膜して、第1基板2側の絶縁性薄膜12aと第2基板7側の貼合せ面71との間の接合により、第1基板2と第2基板7を貼り合わせてもよい。

10

## 【0082】

以上のように、第1基板2と第2基板7とを貼り合わせた後、第1基板2側の半導体基板20を薄膜化して半導体層2aとし、光電変換部21を露出させる。また必要に応じて、第2基板7側の半導体層7aにおいて、半導体基板50を薄膜化してもよい。

## 【0083】

その後は図2に示すように、第1基板2における光電変換部21の露出面上に保護膜15を成膜し、さらに保護膜15上にカラーフィルタ層17およびオンチップレンズ19を形成し、半導体装置（固体撮像装置）1を完成させる。

## 【0084】

## [本実施形態の半導体装置の製造方法による効果]

20

上述のような本実施形態の半導体装置の製造方法では、第1基板2および第2基板7の上にそれぞれ絶縁性薄膜12a, 12bを成膜し、この絶縁性薄膜12a, 12bが成膜された面同士を接合することにより、第1基板2と第2基板7を貼り合わせている。このため、CMPにより平坦化処理された貼合せ面41, 71同士を直接接合する場合と比較して、絶縁性薄膜12a, 12bが成膜された面同士の接合によって、第1基板2と第2基板7を貼り合わせる本実施形態の半導体装置1は接合性がよい。なお、第1基板2の貼合せ面41上にのみ絶縁性薄膜12aを成膜した場合であっても、第1基板2側の絶縁性薄膜12aと第2基板7側の貼合せ面71との間の接合になり、貼合せ面41, 71同士を直接接合する場合よりも基板の接合性がよい。

## 【0085】

30

例えば、CMPにより平坦化処理された貼合せ面41, 71は、CMPの工程において貼合せ面41, 71を構成する第1絶縁膜35および第2絶縁膜69が含水する可能性がある。また、この貼合せ面41, 71を構成する第1絶縁膜35および第2絶縁膜69がTEOS膜からなる場合であれば、そのTEOS膜の成膜条件ゆえに、もともと含水率の高い膜として第1絶縁膜35および第2絶縁膜69が形成される。したがって、このような含水している貼合せ面41, 71同士を直接接合する場合、貼合せ後の熱処理において、脱ガスが接合界面に集中しボイドを形成する。しかしながら、本実施形態では、貼合せ面41, 71の全面を絶縁性薄膜12a, 12bで覆うことにより、脱ガスが接合界面に集中することを防止しボイドの発生を抑えることが可能である。

## 【0086】

40

特に、第1基板2の貼合せ面41上の絶縁性薄膜12aと第2基板7の貼合せ面71上の絶縁性薄膜12bが、同一材料膜で構成されている場合は、同一材料膜同士の接合となるので、より強固な接合が可能になる。これにより、基板の接合強度が増して信頼性の向上が図られた半導体装置を得ることができる。

## 【0087】

さらには、絶縁性薄膜12a, 12bの成膜をALD法により行なったことにより、次のような効果もある。

## 【0088】

まず、ALD法は原子層単位の成膜により膜厚制御性のよい方法なので、極めて薄い絶縁性薄膜を成膜できる。これにより、第1基板2側の第1電極33と第2基板7側の第2

50

電極 6 7 とが絶縁性薄膜 1 2 を介して対向配置された構造であっても、この絶縁性薄膜 1 2 が極めて薄い膜厚であるので、第 1 電極 3 3 と第 2 電極 6 7 との間の電気的な接続が可能となる。

【 0 0 8 9 】

次に、A L D 法は原子層単位の成膜により膜厚均一性のよい方法なので、C M P により平坦化された貼合せ面 4 1 , 7 1 の平坦性を維持して、均一な絶縁性薄膜 1 2 a , 1 2 b を第 1 基板 2 および第 2 基板 7 の上に成膜する。このような絶縁性薄膜 1 2 a , 1 2 b の成膜された平坦な接合面同士によって接合が図られるので、密着性に優れた接合が行なわれ、接合強度の向上した基板の接合が可能となる。

【 0 0 9 0 】

続いて、A L D 法は低温プロセスでの成膜をする方法なので、第 1 基板 2 側の電極層 2 c および第 2 基板 7 側の電極層 7 c を構成する金属が高熱により劣化することなく、第 1 基板 2 および第 2 基板 7 の上に絶縁性薄膜 1 2 a , 1 2 b を成膜できる。従って、本開示の要点である、銅 ( C u ) の結晶粒成長を貼り合わせ後の熱処理で促進する目的に適している。ここまで A L D 法による利点を記述したが、C V D 法による方法であっても、上述した利点を実現できるのであれば A L D 法による成膜にはこだわらない。さらに、ガスを用いた気相成長による成膜以外でも、例えば塗布方法などによる成膜であっても、本開示の原理を実現できる薄膜が形成出来れば良い。

【 0 0 9 1 】

最後に、A L D 法は原子層単位の成膜方法なので、成膜された絶縁性薄膜 1 2 a , 1 2 b は緻密な膜であって含水率が極めて低い。含水率の低い絶縁性薄膜 1 2 a , 1 2 b の成膜された接合面同士による接合となるので、接合面にボイドの発生する虞は全くない。

以上により、基板の接合強度が増して信頼性の向上が図られた半導体装置が得られる。

【 0 0 9 2 】

6 . 本実施形態の半導体装置を用いた電子機器の一例

上述の本実施形態で説明した本開示に係る半導体装置（固体撮像装置）は、例えばデジタルカメラやビデオカメラ等のカメラシステム、さらには撮像機能を有する携帯電話、あるいは撮像機能を備えた他の機器などの電子機器に適用することができる。

【 0 0 9 3 】

図 8 は、本開示に係る電子機器の一例として、固体撮像装置を用いたカメラの構成図を示す。本実施形態に係るカメラ 9 1 は、静止画像又は動画撮影可能なビデオカメラを例としたものである。このカメラ 9 1 は、固体撮像装置 9 2 と、固体撮像装置 9 2 の光電変換部に入射光を導く光学系 9 3 と、シャッタ装置 9 4 と、固体撮像装置 9 2 を駆動する駆動回路 9 5 と、固体撮像装置 9 2 の出力信号を処理する信号処理回路 9 6 とを有する。

【 0 0 9 4 】

固体撮像装置 9 2 は、上述した本実施形態で説明した構成の半導体装置（1）が適用される。光学系（光学レンズ）9 3 は、被写体からの像光（入射光）を固体撮像装置 9 2 の撮像面上に結像させる。これにより、固体撮像装置 9 2 内に、一定期間信号電荷が蓄積される。このような光学系 9 3 は、複数の光学レンズから構成された光学レンズ系としてもよい。シャッタ装置 9 4 は、固体撮像装置 9 2 への光照射期間および遮光期間を制御する。駆動回路 9 5 は、固体撮像装置 9 2 およびシャッタ装置 9 4 に駆動信号を供給し、供給した駆動信号（タイミング信号）により、固体撮像装置 9 2 の信号処理回路 9 6 への信号出力動作の制御、およびシャッタ装置 9 4 のシャッタ動作を制御する。すなわち、駆動回路 9 5 は、駆動信号（タイミング信号）の供給により、固体撮像装置 9 2 から信号処理回路 9 6 への信号転送動作を行う。信号処理回路 9 6 は、固体撮像装置 9 2 から転送された信号に対して、各種の信号処理を行う。信号処理が行われた映像信号は、メモリなどの記憶媒体に記憶され、或いは、モニタに出力される。

【 0 0 9 5 】

以上説明した本実施形態に係る電子機器によれば、センサ基板と回路基板とを積層させた信頼性の高い 3 次元構造の半導体装置 1 を固体撮像装置として用いたことにより、撮像

10

20

30

40

50

機能を有する電子機器の小型化および信頼性の向上を図ることが可能になる。

## 【符号の説明】

〔 0 0 9 7 〕

- 1 半導体装置 , 2 第 1 基板 (センサ基板) , 7 第 2 基板 (回路基板) , 1

2 絶縁性薄膜 , 3 3 第 1 電極 , 3 5 第 1 絶縁膜 , 4 1 , 7 1 貼合せ面 ,

6 7 第 2 電極 , 6 9 第 2 絶縁膜

【 図 1 】

【 図 2 】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

(72)発明者 青柳 健一

東京都港区港南1丁目7番1号 ソニー株式会社内

(72)発明者 香川 恵永

東京都港区港南1丁目7番1号 ソニー株式会社内

審査官 安田 雅彦

(56)参考文献 米国特許出願公開第2013/0009321(US, A1)

特開2010-066723(JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 27/14-148

H01L 21/02

H01L 21/768

H01L 23/522-532

H01L 27/00

H04N 5/335-378