(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5715063号

(P5715063)

(45) 発行日 平成27年5月7日(2015.5.7)

(24) 登録日 平成27年3月20日(2015.3.20)

(51) Int.Cl.

F 1

**G09G 3/30 (2006.01)**

G09G 3/30 G09G 3/20 G09G 3/20 G09G 3/20 G09G 3/20 G09G 3/20

3/30 6 1 2 E 6 1 1 A 6 2 1 J 6 1 1 H

請求項の数 8 (全 35 頁) 最終頁に続く

(21) 出願番号 特願2011-539859 (P2011-539859)

(86) (22) 出願日 平成21年12月8日 (2009.12.8)

(65) 公表番号 特表2012-511183 (P2012-511183A)

(43) 公表日 平成24年5月17日 (2012.5.17)

(86) 國際出願番号 PCT/CA2009/001769

(87) 國際公開番号 WO2010/066030

(87) 國際公開日 平成22年6月17日 (2010.6.17)

審査請求日 平成24年12月4日 (2012.12.4)

(31) 優先権主張番号 2,647,112

(32) 優先日 平成20年12月9日 (2008.12.9)

(33) 優先権主張国 カナダ(CA)

(31) 優先権主張番号 2,654,409

(32) 優先日 平成20年12月19日 (2008.12.19)

(33) 優先権主張国 カナダ(CA)

(73) 特許権者 507257080

イグニス・イノベイション・インコーポレーテッド

IGNIS INNOVATION IN

CORPORATED

カナダ オンタリオ ウォータールー バ

サースト ドライブ 50 ユニット 1

2

(74) 代理人 110001210

特許業務法人 Y K I 国際特許事務所

(74) 代理人 100080137

弁理士 千葉 昭男

最終頁に続く

(54) 【発明の名称】発光型表示装置用の低電力回路及び駆動方法

## (57) 【特許請求の範囲】

## 【請求項 1】

表示システムであって、

発光デバイスおよびスイッチ・トランジスタを含むピクセル回路であって、前記ピクセル回路をプログラミングするためのプログラミング電流と、前記ピクセル回路のプログラミングの促進のため及びエージングに対する補償のためのバイアス電流と、前記ピクセル回路の発光デバイスを駆動するための駆動電流とのうちの少なくとも1つを受けるように構成されるピクセル回路と、

前記ピクセル回路の前記スイッチ・トランジスタのゲート端子と接続されたアドレス線を介して前記スイッチ・トランジスタを駆動するためのゲート・ドライバと、

前記ピクセル回路へ結合されたデータ線とバイアス線と電源線とのうちの少なくとも1つへ時変電圧を供給するためのランプ電圧発生器と、

前記ランプ電圧発生器と直列に接続され、前記ランプ電圧発生器からの前記時変電圧を、前記プログラミング電流と前記バイアス電流と前記駆動電流とのうちの少なくとも1つに変換するキャパシタと、

前記ランプ電圧発生器の前記時変電圧の生成および前記ゲート・ドライバの動作を制御することにより、前記ピクセル回路のプログラミングおよび駆動を制御およびスケジューリングするためのコントローラと

を備え、

前記ピクセル回路は駆動トランジスタを更に備え、前記駆動トランジスタは、前記発光

10

20

デバイスが結合される第1のノードと、電源線との間に直列に結合され、

前記キャパシタは、前記駆動トランジスタのゲート端子が結合される第2のノードと、前記データ線との間に直列に結合され、

前記スイッチ・トランジスタは、前記第1のノードと前記第2のノードとの間に結合され、

前記コントローラは、前記ランプ電圧発生器および前記ゲート・ドライバを動作させるものであり、その動作において、

前記時変電圧は、前記スイッチ・トランジスタがオンの間のプログラミング・サイクル中に前記データ線へ供給されるランプ電圧であり、前記ランプ電圧は、前記キャパシタによりバイアス電流へと変換され、前記バイアス電流は、前記駆動トランジスタおよび前記スイッチ・トランジスタを通じて送られて、前記駆動トランジスタの前記ゲート端子を、前記駆動トランジスタの電気的特性の関数に応じて、バイアス電圧へと調節することを可能とするものであり、

前記プログラミング・サイクル中に、プログラミング電圧が前記データ線へ供給されて、ストレージ・エレメントとしての前記キャパシタが前記プログラミング電圧に従ってプログラミングされ、

駆動サイクル中に、前記駆動トランジスタが光を出力させるように前記発光デバイスを駆動している間に、基準電圧が前記データ線へ供給されて前記基準電圧に対しての前記キャパシタの参照が行われる、

表示システム。

10

20

#### 【請求項2】

請求項1に記載の表示システムであって、前記キャパシタは前記ピクセル回路内に位置するものであり、前記キャパシタは、前記データ線へ供給された電圧プログラミング情報を蓄積するための、前記ピクセル回路のストレージ・キャパシタとして作用し、また、前記キャパシタは、前記ランプ電圧発生器と関連し、前記時変電圧に従って、プログラミング・サイクル中に前記バイアス電流を印加するように、または駆動サイクル中に前記駆動電流を供給するように構成される容量性電流ドライバとして作用する、表示システム。

#### 【請求項3】

請求項1に記載の表示システムであって、前記ピクセル回路は電流プログラム型ピクセル回路であり、前記ランプ電圧発生器および前記キャパシタは、前記データ線を介して、前記プログラミング電流を前記ピクセル回路へ供給する、表示システム。

30

#### 【請求項4】

請求項1に記載の表示システムであって、前記キャパシタは、複数の層を有するインター・デジタル型キャパシタを含む、表示システム。

#### 【請求項5】

請求項4に記載の表示システムであって、

前記発光デバイスは、下部電極とOLED層とを有する有機発光ダイオード(OLED)デバイスを含み、

前記有機発光ダイオード・デバイスの前記下部電極は、前記インター・デジタル型キャパシタの第1層上に形成され、前記インター・デジタル型キャパシタの第2層は、前記有機発光ダイオード・デバイスの前記下部電極と相互接続される、

40

表示システム。

#### 【請求項6】

請求項5に記載の表示システムであって、前記有機発光ダイオード・デバイスの前記下電極は透明電極であり、前記キャパシタの前記複数の層は、前記透明電極上の前記OLED層からの光を覆うことなく、前記透明電極の下に設置される、表示システム。

#### 【請求項7】

発光デバイスと、前記発光デバイスを駆動するための駆動トランジスタと、前記駆動トランジスタおよび前記発光デバイスの双方と結合する第1ノードと、前記駆動トランジスタのゲート端子と結合する第2ノードと、前記第1ノードと前記第2ノードとの間に結合

50

されるスイッチ・トランジスタと、データ線と前記第2ノードとの間に結合されるストレージ・キャパシタとを含むピクセル回路を動作させる方法であって、

プログラミングのサイクル中に、前記データ線を介して前記ストレージ・キャパシタへ供給される時変電圧を充電し、前記スイッチ・トランジスタがオンにされているときに前記キャパシタが前記駆動トランジスタへ電気的に結合し、それにより、バイアス電流が、前記駆動トランジスタおよび前記スイッチ・トランジスタを通じて流れ且つ前記ストレージ・キャパシタを通って流れ、前記駆動トランジスタの前記ゲート端子を、前記駆動トランジスタの電気的特性の関数に応じて、バイアス電圧へと調節することを可能とするステップと、

前記プログラミングの動作中に、前記データ線へプログラミング電圧を印加して、前記プログラミング電圧に従って前記ストレージ・キャパシタをプログラミングするステップと、

駆動の動作中に、光を出力せるように前記駆動トランジスタが前記発光デバイスを駆動している間に、前記データ線へ基準電圧を印加して、前記基準電圧に対しての前記キャパシタの参照を行うステップと

を備える方法。

#### 【請求項 8】

請求項7に記載の方法であって、前記時変電圧は、基準電圧と前記プログラミング電圧との間で変化するものであり、且つランプ電圧発生器を介して供給されるものであり、

前記プログラミング・サイクルの最初の段階において、前記時変電圧が前記データ線へ供給されているときに、前記スイッチ・トランジスタをオンにするステップと、

前記プログラミング・サイクルの第2の段階において、前記プログラミング電圧が前記データ線で維持されているときに、前記スイッチ・トランジスタをオフにするステップとを備える方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

[0001] 本発明は、発光表示装置に関し、より具体的には、発光表示装置を駆動する方法及びシステムに関する。

##### 【背景技術】

##### 【0002】

[0002] エレクトロルミネッセンス表示装置は、携帯電話、携帯情報端末（PDA）などのような、多種多様なデバイス向けに開発されてきた。そのような表示装置としては、液晶表示装置（LCD）、電界放出表示装置（FED）、プラズマ表示パネル（PDP）、発光表示装置（LED）等が挙げられる。特に、非晶質シリコン（a-Si）、多結晶シリコン、有機体、又は他の駆動バックプレーンを備えたアクティブ・マトリックス有機発光ダイオード（AMOLED）表示装置は、実現可能な可撓性をもっての表示、低コストでの製造、高い解像度、及び広い視野角などの利点から、より一層魅力的になってきている。

##### 【0003】

[0003] 発光型表示装置（emissive display）を駆動するのに用いられる1つの方法は、電流を用いて直接ピクセルをプログラミングするものである（例えば、電流駆動型のOLEDデバイス）。しかしながら、OLEDの必要とするのは小電流であるが、大きい寄生容量と結合されると、AMOLED表示装置のプログラミングの整定時間を増加させる。更に、正確で一定の駆動電流を供給する外部ドライバを設計するのは困難である。高い開口率又はフィル・ファクタ（発光表示装置の面積と総ピクセル面積との比として定義される）を備え、高い表示品質を保証する高解像度の表示装置に対する需要がある。また、表示装置を有するデバイスのサイズ及び電力消費を低減することに対する需要がある。

##### 【0004】

10

20

30

40

50

[0004] 表示装置の寿命、画像の均一性、安定性、及び／又は歩留まりを改善することができ、高解像度で安定した低電力表示装置を提供することができる、表示システム及びその動作方法を提供することが求められている。

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0005】**

[0005] 本発明の1つの目的は、既存のシステムにおける不利な点の少なくとも1つを排除又は軽減する方法及びシステムを提供することである。

**【課題を解決するための手段】**

**【0006】**

[0006] 本発明の実施形態の1つの態様によれば、表示システムを駆動するドライバが提供され、ドライバは、時間変動(time-variant、時変)電圧に結合して時変電圧を電流に変換する変換器を含むものであり、電流を表示システムへ供給する双方向電流源と、時変電圧の発生を制御するコントローラとを含む。

**【0007】**

[0007] 本発明の実施形態の別の態様によればピクセル回路が提供され、ピクセル回路は、ピクセル電流を発光デバイスへ供給するトランジスタと、トランジスタに電気的に結合し、予め定められたタイミングで時変電圧に結合して時変電圧に基づいて電流を供給するストレージ・キャパシタ(storage capacitor)とを含む。

**【0008】**

[0008] 本発明の実施形態の更なる態様によれば、ピクセル回路を動作させる方法が提出され、方法は、プログラミング動作の第1のサイクルにおいて、ピクセル回路のストレージ・キャパシタであって、発光デバイスを駆動するための駆動トランジスタに電気的に結合されるストレージ・キャパシタへ供給された時変電圧を、基準電圧からプログラミング電圧に変化させるステップと、プログラミング動作の第2のサイクルにおいて、時変電圧をプログラミング電圧で維持するステップとを含む。

**【0009】**

[0009] 本発明の実施形態の更なる態様によれば、ピクセル回路を動作させる方法が提供され、方法は、プログラミング動作において、プログラミング・データを、データ線から、データ線に結合するトランジスタとストレージ・キャパシタとを含むピクセル回路へ供給するステップと、駆動動作において、発光デバイスをオンにする時変電圧を、電力供給線を通してピクセル回路のストレージ・キャパシタへ供給するステップとを含む。

**【0010】**

[0010] 本発明の実施形態の更なる態様によればピクセル回路が提供され、ピクセル回路は、電極及びOLED層を有する有機発光ダイオード(OLED)デバイスと、OLEDデバイスを動作させるための複数の層を有するインター・デジタル型キャパシタ(interdigitated capacitor)とを含み、OLEDデバイスは複数の層上に配置され、インター・デジタル型キャパシタの層の1つがOLEDの電極に相互接続される。

**【0011】**

[0011] 本発明のこれら及び他の特徴は、添付の図面を参照する以下の記載からより明白になるであろう。

**【図面の簡単な説明】**

**【0012】**

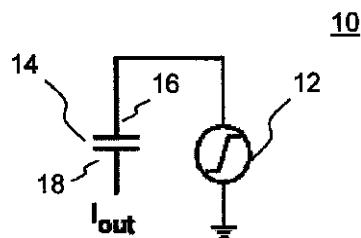

【図1】図1は、本開示の一実施形態による双方向電流源を示す。

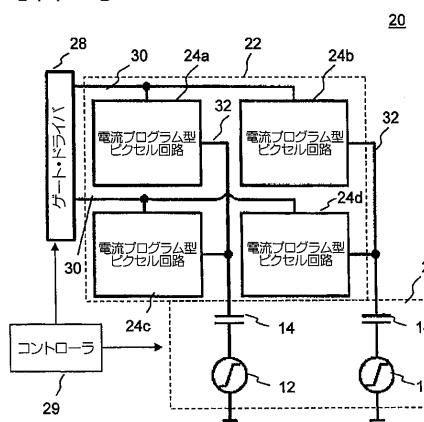

【図2】図2は、図1の双方向電流源を備えた表示システムの一例を示す。

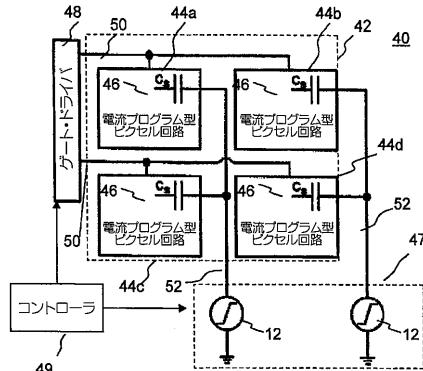

【図3】図3は、図1の双方向電流源を備えた表示システムの更なる一例を示す。

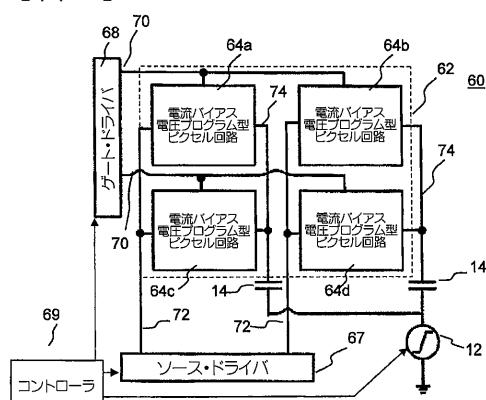

【図4】図4は、図1の双方向電流源を備えた表示システムの更なる一例を示す。

【図5】図5は、図1の双方向電流源を備えた表示システムの更なる一例を示す。

【図6A】図6Aは、図5の表示システムに適用可能な電流バイアス電圧プログラム型(current biased voltage programmed)ピクセル回路の一例を示す。

10

20

30

40

50

【図 6 B】図 6 B は、図 6 A のピクセル回路のタイミング図の一例を示す。

【図 7 A】図 7 A は、図 6 A のピクセル回路に関するシミュレーション結果を示す。

【図 7 B】図 7 B は、図 6 A のピクセル回路に関する更なるシミュレーション結果を示す。

【図 8 A】図 8 A は、電流バイアス電圧プログラム型ピクセル回路の更なる一例を示す。

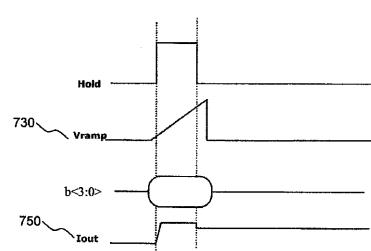

【図 8 B】図 8 B は、図 8 A のピクセル回路に関するタイミング図の一例を示す。

【図 8 C】図 8 C は、図 8 A のピクセル回路に関するタイミング図の別の例を示す。

【図 9 A】図 9 A は、電流バイアス電圧プログラム型ピクセル回路の更なる一例を示す。

【図 9 B】図 9 B は、図 9 A のピクセル回路に関するタイミング図の一例を示す。

【図 9 C】図 9 C は、図 9 A のピクセル回路に関するタイミング図の別の例を示す。

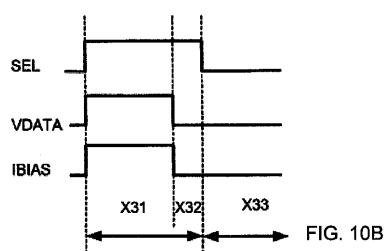

【図 10 A】図 10 A は、電流バイアス電圧プログラム型ピクセル回路の更なる一例を示す。

【図 10 B】図 10 B は、図 10 A のピクセル回路に関するタイミング図の一例を示す。

【図 11 A】図 11 A は、電流バイアス電圧プログラム型ピクセル回路の更なる一例を示す。

【図 11 B】図 11 B は、図 11 A のピクセル回路のタイミング図の一例を示す。

【図 12 A】図 12 A は、電流バイアス電圧プログラム型ピクセル回路を有する表示装置の一例を示す。

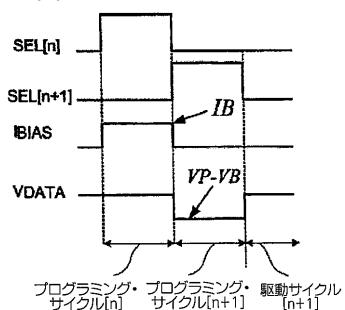

【図 12 B】図 12 B は、図 12 A の表示装置に関するタイミング図の一例を示す。

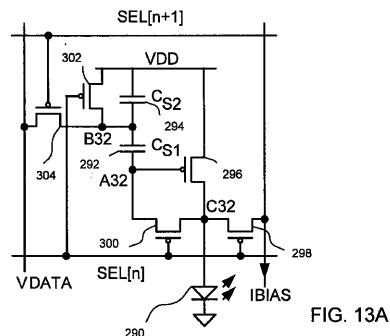

【図 13 A】図 13 A は、電流バイアス電圧プログラム型ピクセル回路を有する表示装置の一例を示す。

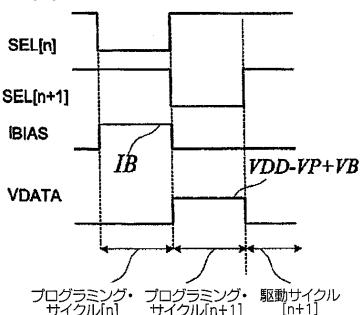

【図 13 B】図 13 B は、図 13 A の表示装置に関するタイミング図の一例を示す。

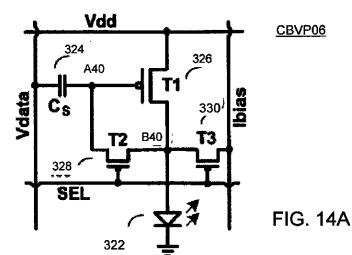

【図 14 A】図 14 A は、電流バイアス電圧プログラム型ピクセル回路の更なる一例を示す。

【図 14 B】図 14 B は、図 14 A のピクセル回路に関するタイミング図の一例を示す。

【図 15 A】図 15 A は、電流バイアス電圧プログラム型ピクセル回路の更なる一例を示す。

【図 15 B】図 15 B は、図 15 A のピクセル回路に関するタイミング図の一例を示す。

【図 16】図 16 は、電流バイアス電圧プログラム型ピクセル回路を有する表示システムの更なる一例を示す。

【図 17 A】図 17 A は、電圧バイアス電流プログラム型 (voltage biased current programmed) ピクセル回路の一例を示す。

【図 17 B】図 17 B は、図 17 A のピクセル回路に関するタイミング図の一例を示す。

【図 18 A】図 18 A は、電圧バイアス電流プログラム型ピクセル回路の更なる一例を示す。

【図 18 B】図 18 B は、図 18 A のピクセル回路に関するタイミング図の一例を示す。

【図 19】図 19 は、電圧バイアス電流プログラム型ピクセル回路を有する表示システムの一例を示す。

【図 20 A】図 20 A は、双方向電流源が適用されるピクセル回路の一例を示す。

【図 20 B】図 20 B は、双方向電流源が適用されるピクセル回路の別の例を示す。

【図 21 A】図 21 A は、図 20 A ~ 図 20 B のピクセル回路に対するタイミング図の一例を示す。

【図 21 B】図 21 B は、図 20 A ~ 図 20 B のピクセル回路に対するタイミング図の別の例を示す。

【図 22】図 22 は、異なるプログラミング電圧に対する 1 つのサブフレームにおける図 20 A ~ 図 20 B のピクセル回路に関するシミュレーション結果 (OLED 電流) を示すグラフを示す。

【図 23】図 23 は、図 20 A ~ 図 20 B のピクセル回路に関するシミュレーション結果 (平均電流) を示すグラフを示す。

【図 24】図 24 は、5.58 cm (2.2 インチ) QVGA パネルの電力消費及び OLE

10

20

30

40

50

E D に使用される電力消費を示すグラフを示す。

【図 2 5】図 2 5 は、ボトム・エミッショニ型表示装置を駆動するためのキャパシタの実装の一例を示す。

【図 2 6】図 2 6 は、ボトム・エミッショニ型ピクセルのレイアウトの一例を示す。

【図 2 7】図 2 7 は、トップ・エミッショニ型表示装置を駆動するためのキャパシタの実装の一例を示す。

【図 2 8】図 2 8 は、容量性駆動に基づくデジタル・アナログ変換器 (D A C) の一例を示す。

【図 2 9】図 2 9 は、図 2 8 の D A C に関するタイミング図の一例を示す。

【図 3 0】図 3 0 は、容量性駆動に基づくデジタル・アナログ変換器 (D A C) の別の例 10 を示す。

【図 3 1】図 3 1 は、図 3 0 の D A C に関するタイミング図の一例を示す。

**【発明を実施するための形態】**

**【0 0 1 3】**

[0012] 現在の好ましい実施形態の 1 又は複数が例として記載されている。特許請求の範囲において定義される本発明の範囲から逸脱することなく、多数の変形及び変更を行うことができる事が、当業者には明白となるであろう。

**【0 0 1 4】**

[0013] 本発明の実施形態は、限定するものではないが、例えば、非晶質シリコン、多結晶シリコン、金属酸化物、従来の C M O S 、有機体、ナノ結晶 / 微晶質半導体、又はそれらの組合せを含む様々な製造技術を使用して製造され得る表示システムを使用して説明する。表示システムは、トランジスタ、キャパシタ、及び発光デバイスを有し得るピクセルを含む。トランジスタは、非晶質 S i 、微晶質 / ナノ結晶 S i 、多結晶 S i 、有機 / ポリマー材料及び関連するナノコンポジット、半導体酸化物、又はそれらの組合せを含む、様々な材料、システム、並びに技術で実施され得る。キャパシタは、金属 - 絶縁体 - 金属、及び金属 - 絶縁体 - 半導体を含む、様々な構造を有することができる。例えば、発光デバイスは O L E D であり得るが、それに限定されない。表示システムは、A M O L E D 表示システムであり得るが、それに限定されない。

**【0 0 1 5】**

[0014] 本明細書では、「ピクセル回路」及び「ピクセル」は互換可能に使用されることがある。各トランジスタは、ゲート端子と 2 つの他の端子（第 1 及び第 2 の端子）とを有し得る。本明細書では、トランジスタの端子の一方、即ち、「第 1 の端子」（他方の端子、即ち、「第 2 の端子」）は、ドレイン端子（ソース端子）又はソース端子（ドレイン端子）に対応し得るが、それに限定されない。

**【0 0 1 6】**

[0015] 製造コストを低減するため、表示装置バックプレーンに使用される製造技術のほとんどは、1 つのみのタイプのトランジスタを提供する。各タイプのトランジスタは本質的に一方向電流源に適しているので、ピクセル回路及び / 又は周辺ドライバ回路が複雑になり、結果として、歩留まり、解像度、及び開口率が低下する。一方、全ての技術において容量が利用可能である。

**【0 0 1 7】**

[0016] 微分器 / 変換器を使用して時変電圧を電流に変換する電流駆動技術について記載する。本明細書では、キャパシタはランプ電圧を電流（例えば、D C 電流）に変換するために使用される。図 1 を参照すると、容量に基づいて開発された電流源が示されている。図 1 の電流源 1 0 は、正電流及び負電流を供給することができる双方向電流源である。電流源 1 0 は、時変電圧を発生させる電圧発生器 1 2 及び駆動キャパシタ 1 4 を含む。電圧発生器 1 2 は、駆動キャパシタ 1 4 の一方の端子 1 6 に結合される。ノード「 I o u t 」は、駆動キャパシタ 1 4 の他方の端子 1 8 に結合される。この例では、ランプ電圧は電圧発生器 1 2 により発生する。実施形態において、用語「容量性電流源」、「容量性電流源ドライバ」、「容量性ドライバ」、及び「電流源」は、互換可能に使用され得る。実施 40 50

形態において、用語「電圧発生器」及び「ランプ電圧発生器」は、互換可能に使用され得る。図1では、電流源10はランプ電圧発生器12を含むが、電流源10は、ランプ電圧を受け取る駆動キャパシタ14により形成されてもよい。

#### 【0018】

[0017] ノード「Iout」は仮想接地であると仮定する。ランプ電圧は駆動キャパシタ14の端子16に印加され、それにより、駆動キャパシタ14を通ってIoutに至る固定電流が得られる。 $i(t) = C \frac{dV_R(t)}{dt}$  ( $C$ : 容量、 $V_R(t)$ : ランプ電圧)。ランプの傾斜の振幅及び符号は制御可能(変更可能)であり、それにより出力電流の値及び方向を変えることができる。また、駆動キャパシタ14の量により電流値を変えることができる。その結果、容量性電流源10に基づくデジタル化された容量を使用して、単純且つ有効な電流モード型アナログ・デジタル変換器(ADC)を開発することができ、それにより小型で低電力のドライバが得られる。また、これにより、製造技術とは無関係に、パネルに簡単に一体化することができる簡単なソース・ドライバが提供され、それにより表示装置の歩留まり及び簡素性が改善され、システム・コストが大幅に低減される。

#### 【0019】

[0018] 一例では、容量性電流源10を使用して、プログラミング電流を電流プログラム型ピクセル(例えば、OLEDピクセル)へ供給することができる。別の例では、容量性電流源10を使用して、ピクセル(例えば、図8～図16の電圧バイアス電圧プログラム型ピクセル、及び図17～図19の電圧バイアス電流プログラム型ピクセル)のプログラミングを加速させるバイアス電流を供給することができる。更なる一例では、容量性電流源10を使用してピクセルを駆動することができる。容量性電流源10を用いた容量性駆動技術は、プログラミング/駆動の整定時間を改善するが、このことはより大型及び高解像度の表示装置に適しており、また結果として、後述するように、容量性電流源10を用いて低電力高解像度の発光型表示装置を実現することができる。容量性電流源10を用いた容量性駆動技術は、TFTのエージング(例えば、閾値電圧の変動)を補償し、結果として、後述するように、表示装置の均一性及び寿命を改善することができる。

#### 【0020】

[0019] 更なる一例では、容量性電流源10は、例えば、電流モード型ADCと共に使用し、入力電流をデジタル信号に変換する電流モード型アナログ・デジタル変換器(ADC)へ基準電流を供給することができる。更なる一例では、容量性駆動は、ランプ電圧及びキャパシタに基づいて電流を発生させるデジタル・アナログ変換器(DAC)に使用されてもよい。

#### 【0021】

[0020] 図2を参照すると、容量性ドライバ10を備えた統合型表示システムの一例が示されている。図2の統合型表示システム20は、列及び行の形で配列された複数のピクセル24a～24dを有するピクセル・アレイ22と、ピクセルを選択するゲート・ドライバ28と、プログラミング電流を選択されたピクセルへ供給するソース・ドライバ27とを含む。

#### 【0022】

[0021] ピクセル24a～24dは電流プログラム型ピクセル回路である。各ピクセルは、例えば、ストレージ・キャパシタ、駆動トランジスタ、スイッチ・トランジスタ(又は駆動及びスイッチング・トランジスタ)、並びに発光デバイスを含む。図2では、4つのピクセルが示されているが、ピクセル・アレイ22のピクセルの数は4つに限定されず、異なっていてもよいことが当業者には理解されるであろう。ピクセル・アレイ22は、電圧バイアス電圧プログラム型(CBVP)ピクセル(例えば、図8～図16)又は電圧バイアス電圧プログラム型(VBCP)ピクセル(例えば、図17～図19)を含むことができ、ピクセルは電流及び電圧に基づいて動作する。CBVP駆動技術及びVBCP駆動技術は、AMOLED表示装置での使用に適しており、ピクセルの整定時間を向上させる。

10

20

30

40

50

## 【0023】

[0022] 各ピクセルは、アドレス線30及びデータ線32に結合される。各アドレス線30は行内のピクセル間で共有される。各データ線32は列内のピクセル間で共有される。ゲート・ドライバ28は、アドレス線30を通してピクセル内のスイッチ・トランジスタのゲート端子を駆動する。ソース・ドライバ27は各列のための容量性ドライバ10を含む。容量性ドライバ10は対応する列のデータ線32に結合される。容量性ドライバ10はデータ線32を駆動する。コントローラ29は、表示アレイ22のプログラミング、校正、駆動、及び他の動作を制御およびスケジューリングするために提供される。コントローラ29は、ソース・ドライバ27及びゲート・ドライバ28の動作を制御する。各ランプ電圧発生器12は校正されることができる。表示システム20では、駆動キャパシタ14は、例えば、表示装置の縁部に実装される。10

## 【0024】

[0023] ランプ電圧の供給の開始時に、容量（駆動キャパシタ14）は電圧源として作用し、データ線32の電圧を調節する。データ線32の電圧が特定の適正電圧に達した後、データ線32は仮想接地（図1の「Iout」）として作用する。従って、この時点の後、容量は一定電流を供給する電流源として作用することになる。この二元性により高速で整定されるプログラミングがもたらされる。

## 【0025】

[0024] 図2では、ピクセルの駆動キャパシタ14及びストレージ・キャパシタは、別個に割り付けられる。しかしながら、駆動キャパシタ14は、図3に示されるようにピクセルのストレージ・キャパシタと共有されてもよい。20

## 【0026】

[0025] 図3を参照すると、図1の容量性ドライバ10を備えた統合型表示システムの別の例が示されている。図3の統合型表示システム40は、列及び行の形で配列された複数のピクセル44a～44dを有するピクセル・アレイ42を含む。ピクセル44a～44dは電流プログラム型ピクセル回路であり、図2のピクセル24a～24dと同じであり得る。図3では、4つのピクセルが示されているが、ピクセル・アレイ42内のピクセルの数は4つに限定されず、別の数でもよいことが当業者には理解されるであろう。各ピクセルは、例えば、ストレージ・キャパシタ、駆動トランジスタ、スイッチ・トランジスタ（又は駆動及びスイッチング・トランジスタ）、並びに発光デバイスを含む。例えば、ピクセル・アレイ42は図6Aのピクセルを含むことができ、ピクセルはプログラミング電圧及び電流バイアスに基づいて動作する。30

## 【0027】

[0026] 各ピクセルは、アドレス線50及びデータ線52に結合される。各アドレス線50は行内のピクセル間で共有される。ゲート・ドライバ48は、アドレス線50を通してピクセル内のスイッチ・トランジスタのゲート端子を駆動する。各データ線52は列内のピクセル間で共有され、列内の各ピクセルのキャパシタ46に結合される。列内の各ピクセルのキャパシタ46は、データ線52を通してランプ電圧発生器12に結合される。ソース・ドライバ47はランプ電圧発生器12を含む。ランプ電圧発生器12は各列に割り付けられる。コントローラ49は、表示アレイ42のプログラミング、校正、駆動、及び他の動作の制御およびスケジューリングのために提供される。コントローラ49は、ゲート・ドライバ48と、ランプ電圧発生器12を有するソース・ドライバ47とを制御する。表示システム40では、ピクセルのキャパシタ46は、ピクセルのストレージ・キャパシタとして作用し、また、駆動容量（図1のキャパシタ14）としても作用する。40

## 【0028】

[0027] 図4を参照すると、図1の容量性ドライバ10を備えた統合型表示システムの更なる一例を示す。図4の統合型表示システム60は、列及び行の形で配列された複数のピクセル64a～64dを有するピクセル・アレイ62を含む。図4では、4つのピクセルが示されているが、ピクセル・アレイ62内のピクセルの数は4つに限定されず、他の数としてもよいことが当業者には理解されるであろう。ピクセル64a～64dは、それ50

それがアドレス線 7 0、データ線 7 2、及び電流バイアス線 7 4 に結合する C B V P ピクセル回路である。ピクセル・アレイ 6 2 は図 8 ~ 図 16 の C B V P ピクセルを含むことができる。

### 【 0 0 2 9 】

[ 0028 ] 各アドレス線 7 0 は行内のピクセル間で共有される。ゲート・ドライバ 6 8 は、アドレス線 7 0 を通してピクセルのスイッチ・トランジスタのゲート端子を駆動する。各データ線 7 2 は、列のピクセル間で共有され、プログラミング・データを供給するためにソース・ドライバ 6 7 に結合する。ソース・ドライバ 6 7 はバイアス電圧（例えば、図 6 の V d d ）を更に供給することができる。各バイアス線 7 4 は列のピクセル間で共有される。駆動キャパシタ 1 4 は、各列に割り付けられ、バイアス線 7 4 及びランプ電圧発生器 1 2 に結合される。ランプ電圧発生器 1 2 は 1 つより多い列により共有される。コントローラ 6 9 は、表示アレイ 6 2 のプログラミング、校正、駆動、及び他の動作の制御およびスケジューリングのために提供される。コントローラ 6 9 は、ソース・ドライバ 6 7 、ゲート・ドライバ 6 8 、及びランプ電圧発生器 1 2 を制御する。表示システム 6 0 では、容量性電流源はパネルの周辺に簡単に置くことができ、それにより実装コストが低減される。図 4 では、ランプ電圧発生器 1 2 はソース・ドライバ 6 7 とは別個に示されている。しかしながら、ソース・ドライバ 6 7 はランプ電圧を供給することができる。

### 【 0 0 3 0 】

[ 0029 ] C B V P ピクセル回路を有する表示システムは、電圧を使用して様々なグレー・スケール（電圧プログラミング）を提供し、バイアスを使用して、プログラミングを加速させると共に、閾値電圧シフト及び O L E D 電圧シフトなどのようなピクセルの時間依存性パラメータを補償する。C B V P ピクセル回路を有する表示アレイを駆動するドライバは、ピクセル輝度データを電圧に変換する。C B V P 駆動方式に従って、オーバードライブ電圧が発生し、閾値電圧及び O L E D 電圧とは独立して駆動トランジスタに供給される。ピクセル素子（1又は複数）の特性（1又は複数）のシフト（例えば、表示装置の長時間動作による駆動トランジスタの閾値電圧のシフトや発光デバイスの劣化など）は、ストレージ・キャパシタに蓄積された電圧により、その電圧を駆動トランジスタのゲートに印加することにより、補償される。従って、ピクセル回路は、シフトの影響なしに発光デバイスを介して安定した電流を供給することができ、それにより表示装置の動作寿命が改善される。更に、回路が単純であるため、従来のピクセル回路よりも高い製品歩留まり、低い製造コスト、及び高い解像度が確実に得られる。ピクセル回路の整定時間は従来のピクセル回路よりもはるかに短いので、高精細度テレビジョンなどの大面積表示装置に適しているが、より小さい表示面積のものを除外するものではない。容量性駆動技術は、より大型且つ高解像度の表示装置に適したように整定時間を更に改善するために、C B V P 表示装置に適用可能である。

### 【 0 0 3 1 】

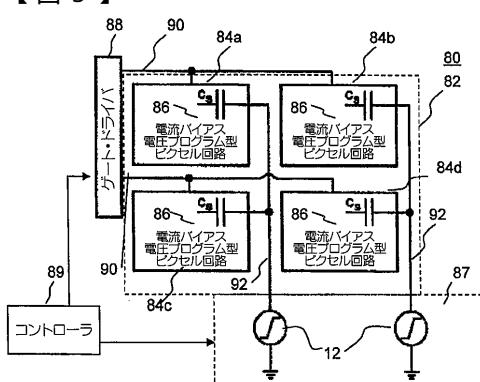

[ 0030 ] 容量性駆動技術は、C B V P 表示装置の電流バイアス線及び電圧データ線を共有する独特的の機会を提供する。図 5 を参照すると、図 1 の容量性ドライバ 1 0 を備えた統合型表示システムの更なる一例が示されている。図 5 の統合型表示システム 8 0 は、列及び行の形で配列された複数のピクセル 8 4 a ~ 8 4 d を有するピクセル・アレイ 8 2 を含む。ピクセル 8 4 a ~ 8 4 d は C B V P ピクセル回路であり、図 4 のピクセル 6 4 a ~ 6 4 d と同じであり得る。図 5 では、4 つのピクセルが示されているが、ピクセル・アレイ 8 2 内のピクセルの数は 4 つに限定されず、別の数としてもよいことが当業者には理解されるであろう。各ピクセルは、アドレス線 9 0 及び電圧データ / 電流バイアス線 9 2 に結合される。

### 【 0 0 3 2 】

[ 0031 ] 各アドレス線 9 0 は行のピクセル間で共有される。ゲート・ドライバ 8 8 は、アドレス線 9 0 を通してピクセルのスイッチ・トランジスタのゲート端子を駆動する。各電圧データ / 電流バイアス線 9 2 は、列のピクセル間で共有され、列の各ピクセルのキャパシタ 8 6 に結合される。列の各ピクセルのキャパシタ 8 6 は、電圧データ / 電流バイア

10

20

30

40

50

ス線 9 2 を通してランプ電圧発生器 1 2 に結合される。ソース・ドライバ 8 7 はランプ電圧発生器 1 2 を有する。ランプ電圧発生器 1 2 は各列に割り付けられる。コントローラ 8 9 は、表示アレイ 8 2 のプログラミング、校正、駆動、及び他の動作の制御およびスケジューリングのために提供される。コントローラ 8 9 は、ゲート・ドライバ 8 8 と、ランプ電圧発生器 1 2 を有するソース・ドライバ 8 7 を制御する。データ電圧及びバイアス電流は、電圧データ / 電流バイアス線 9 2 を介して搬送される。表示システム 8 0 では、ピクセルのキャパシタ 8 6 は、ピクセルのストレージ・キャパシタとして作用し、また、駆動容量（図 1 のキャパシタ 1 4 ）としても作用する。

## 【 0 0 3 3 】

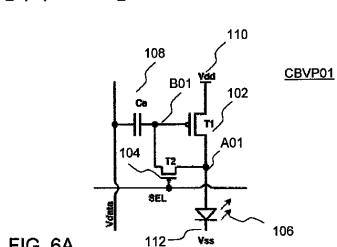

[ 0032 ] 図 6 A を参照すると、図 5 のピクセルに適用可能な C B V P ピクセル回路の一例が示されている。図 6 のピクセル回路 C B V P 0 1 は、駆動トランジスタ 1 0 2 、スイッチ・トランジスタ 1 0 4 、発光デバイス 1 0 6 、及びキャパシタ 1 0 8 を含む。図 6 A では、トランジスタ 1 0 2 及び 1 0 4 は p 型トランジスタであるが、当業者であれば、n 型トランジスタを有する C B V P ピクセルも図 5 のピクセルとして適用可能であることを理解するであろう。

## 【 0 0 3 4 】

[ 0033 ] 駆動トランジスタ 1 0 2 のゲート端子は B 0 1 でキャパシタ 1 0 8 に結合される。駆動トランジスタ 1 0 2 の第 1 及び第 2 の端子のうちの一方は電源 ( V d d ) 1 1 0 に結合され、他方はノード A 0 1 で発光デバイス 1 0 6 に結合される。発光デバイス 1 0 6 は電源 ( V s s ) 1 1 2 に結合される。スイッチ・トランジスタ 1 0 4 のゲート端子はアドレス線 S E L に結合される。スイッチ・トランジスタ 1 0 4 の第 1 及び第 2 の端子のうちの一方は駆動トランジスタ 1 0 2 のゲートに結合され、他方は A 0 1 で発光デバイス 1 0 6 及び駆動トランジスタ 1 0 2 に結合される。キャパシタ 1 0 8 は、データ線 V d a t a と駆動トランジスタ 1 0 2 のゲート端子との間に結合される。キャパシタ 1 0 8 はストレージ・キャパシタとして、容量性電流源（図 1 の 1 4 ）はドライバ・エレメントとして、作用する。

## 【 0 0 3 5 】

[ 0034 ] キャパシタ 1 0 8 は図 5 のキャパシタ 8 6 に対応する。アドレス線 S E L は、図 5 のアドレス線 9 0 に対応する。データ線 V d a t a は、図 5 の電圧データ / 電流バイアス線 9 2 に対応し、ランプ電圧発生器（図 1 の 1 2 ）に結合される。図 5 のソース・ドライバ 8 7 は、データ線 V d a t a に作用して、バイアス信号及びプログラミング・データ ( V p ) をピクセルに供給する。

## 【 0 0 3 6 】

[ 0035 ] 図 6 A では、ランプ電圧はバイアス電流を伝送するために使用され、ランプの初期電圧 ( V r e f 1 - V p ) は、図 6 B に示されているように、プログラミング電圧をピクセル回路 C B V P 0 1 へ送るために使用される。

## 【 0 0 3 7 】

[ 0036 ] 図 6 A 及び図 6 B を参照すると、ピクセル回路 C B V P 0 1 の動作サイクルはプログラミング・サイクル 1 2 0 及び駆動サイクル 1 2 6 を含む。駆動トランジスタ 1 0 2 に結合された電源 V d d は、プログラミング・サイクル 1 2 0 中は低レベルである。プログラミング・サイクル 1 2 0 の初期段階 1 2 2 では、ランプ電圧がデータ線 V d a t a に供給される。V d a t a の電圧は、( V r e f 1 - V p ) から V p へと移行する。ここで、V p はピクセルをプログラミングするためのプログラミング電圧であり、V r e f 1 は基準電圧である。初期段階 1 2 2 中、アドレス線 S E L は低電圧に設定されるので、スイッチ・トランジスタ 1 0 4 がオンになる。初期段階 1 2 2 中、キャパシタ 1 0 8 は電流源として作用する。ノード A 0 1 の電圧は V B T 1 へと移行する。ここで、V B は T 1 の特性の関数である ( T 1 : 駆動トランジスタ 1 0 2 ) 。ノード B 0 1 の電圧は V B T 1 + V r T 2 へと移行する。ここで、V r T 2 は T 2 の電圧降下である ( T 2 : スイッチ・トランジスタ 1 0 4 ) 。

## 【 0 0 3 8 】

10

20

30

40

50

[0037] 初期段階 122 後の次の段階 124 では、V<sub>data</sub> の電圧は V<sub>p</sub> のままであり、アドレス線 S<sub>EL</sub> は高レベルへと移行して、スイッチ・トランジスタ 104 がオフになる。段階 124 中は、キャパシタ 108 はストレージ・エレメントとして作用する。駆動サイクル 126 中、データ線 V<sub>data</sub> は V<sub>ref2</sub> へと移行し、フレームの残りの部分の間は V<sub>ref2</sub> にとどまる。

#### 【0039】

[0038] V<sub>ref1</sub> は、バイアス電流 I<sub>bias</sub> のレベルを定めるものであり、例えば、TFT、OLED、および表示装置の特性及び仕様に応じて決定される。V<sub>ref2</sub> は V<sub>ref1</sub> 及びピクセル特性の関数である。

#### 【0040】

[0039] 図 7A ~ 図 7B を参照すると、図 6B の動作を使用した図 6A のピクセル回路に関するシミュレーション結果を示すグラフが示されている。図 7A では、「V<sub>T</sub>」は駆動トランジスタ閾値 V<sub>T</sub> の変動を表し、「μ」は移動度 (cm<sup>2</sup>N.s) を表す。図 7A ~ 図 7B に示されているように、駆動トランジスタ閾値 V<sub>T</sub> 及び移動度の変動に関わらず、ピクセル電流は全てのグレー・スケールに対して安定している。

#### 【0041】

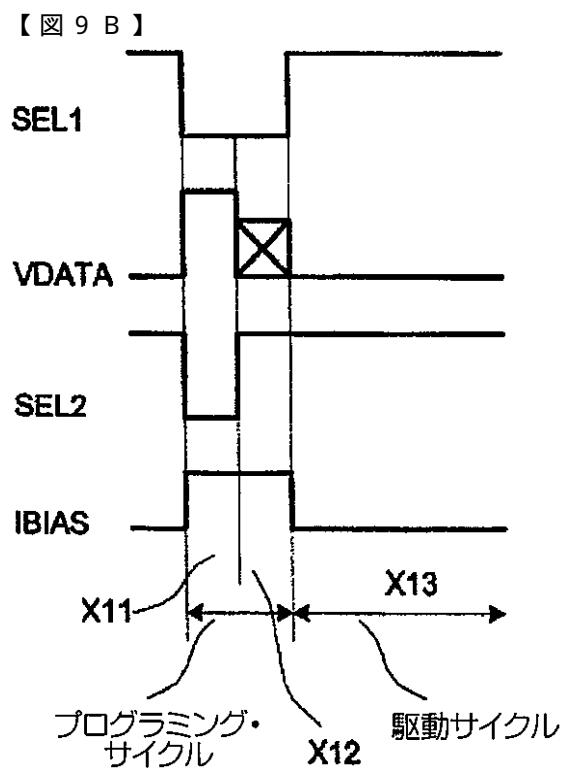

[0040] 図 8 ~ 図 16 を参照すると、図 2 ~ 図 5 のピクセル・アレイを形成し得る CB VP ピクセル回路の例が示されている。図 8 ~ 図 16 では、電流バイアス線 ('I<sub>bias</sub>' 又は 'IBIAS') は、対応するピクセルへバイアス電流を供給する。図 1 の容量性ドライバ 10 は、定バイアス電流を電流バイアス線へ供給し得る。CB VP ピクセル、表示システム、及び動作の例は、米国特許出願公開 US 2006/0125408 及び PCT 国際出願公開 WO 2009/127065 に開示されており、それらを参照により本明細書に組み込む。

#### 【0042】

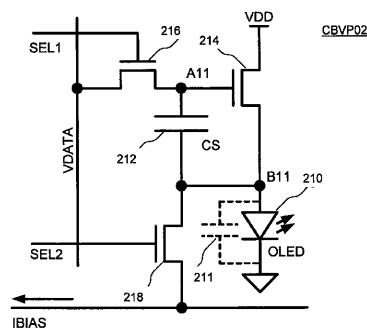

[0041] 図 8A のピクセル回路 CB VP 02 は、OLED 210、ストレージ・キャパシタ 212、駆動トランジスタ 214、並びにスイッチ・トランジスタ 216 及び 218 を含む。トランジスタ 214、216、及び 218 は n 型 TFT トランジスタである。当業者であれば、ピクセル回路 CB VP 02 に対して相補的であり p 型トランジスタを有する回路について理解するであろう。2 つの選択線 S<sub>EL</sub> 1 及び S<sub>EL</sub> 2、信号線 V<sub>DAT</sub>A、バイアス線 I<sub>BIA</sub>S、電圧供給線 V<sub>DD</sub>、及び共通接地 (common ground、コモン・グラウンド) は、ピクセル回路 CB VP 02 に結合される。図 8A では、共通接地は OLED の上部電極用である。共通接地はピクセル回路の一部ではなく、OLED 210 が形成される最終段階で形成される。トランジスタ 214 及び 216 並びにストレージ・キャパシタ 212 はノード A 11 に接続される。OLED 210、ストレージ・キャパシタ 212、並びにトランジスタ 214 及び 218 はノード B 11 に接続される。

#### 【0043】

[0042] 駆動トランジスタ 214 のゲート端子は、スイッチ・トランジスタ 216 及びキャパシタ 212 を介して信号線 V<sub>DAT</sub>A に接続される。駆動トランジスタ 214 の第 1 及び第 2 の端子のうちの一方は電圧供給線 V<sub>DD</sub> に接続され、他方は B 11 で OLED 210 のアノード電極に接続される。ストレージ・キャパシタ 212 は、駆動トランジスタ 214 のゲート端子と OLED 210 との間、即ち、A 11 と B 11 との間に接続される。スイッチ・トランジスタ 216 のゲート端子は第 1 の選択線 S<sub>EL</sub> 1 に接続される。スイッチ・トランジスタ 216 の第 1 及び第 2 の端子のうちの一方は信号線 V<sub>DAT</sub>A に接続され、他方は A 11 で駆動トランジスタ 214 のゲート端子に接続される。スイッチ・トランジスタ 218 のゲート端子は第 2 の選択線 S<sub>EL</sub> 2 に接続される。スイッチ・トランジスタ 218 の第 1 及び第 2 の端子のうちの一方は、B 11 で OLED 210 のアノード電極とストレージ・キャパシタ 212 とに接続され、他方はバイアス線 I<sub>BIA</sub>S に接続される。OLED 210 のカソード電極は共通接地に接続される。

#### 【0044】

[0043] ピクセル回路 CB VP 02 の動作は、複数のプログラミング・サイクルを有す

10

20

30

40

50

るプログラミング段階と、1つの駆動サイクルを有する駆動段階とを含む。プログラミング段階中、ノードB11は駆動トランジスタ214の負の閾値電圧に荷電され、ノードA11はプログラミング電圧VPに荷電される。

【0045】

[0044] その結果、駆動トランジスタ214のゲート・ソース電圧は次式のようになる。

。

【0046】

$$VGS = VP - (-VT) = VP + VT \quad (1)$$

【0047】

ここで、VGSは駆動トランジスタ214のゲート・ソース電圧を表し、VTは駆動トランジスタ214の閾値電圧を表す。この電圧は、駆動段階ではキャパシタ212に留まり、それにより、駆動段階において所望の電流がOLED210に流れる。

10

【0048】

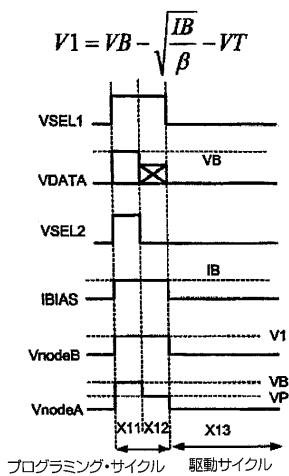

[0045] 図8Bを参照すると、図8Aのピクセル回路CBVP02に適用される1つの例示的な動作プロセスが示されている。図8Bでは、「VnodeB」は図8AのノードB11における電圧を表し、「VnodeA」は図8AのノードA11における電圧を表し、「VSEL1」は図8AのSEL1に対応し、「VSEL2」は図8AのSEL2に対応する。プログラミング段階は2つの動作サイクルX11、X12を有し、駆動段階は1つの動作サイクルX13を有する。

【0049】

[0046] 第1の動作サイクルX11：選択線SEL1及びSEL2は両方とも高レベルである。バイアス電流IBはバイアス線BIASを流れ、VDATAはバイアス電圧VBになる。

20

【0050】

[0047] その結果、ノードB11の電圧は次式のようである。

【0051】

【数1】

$$V_{nodeB} = VB - \sqrt{\frac{IB}{\beta}} - VT \quad (2)$$

30

【0052】

ここで、VnodeBはノードB11の電圧を表し、VTは駆動トランジスタ214の閾値電圧を表し、

は、 $ID_S = (VGS - VT)^2$ により与えられるTFTの電流-電圧(I-V)特性の係数を表す。ID\_Sは駆動トランジスタ214のドレイン・ソース電流を表す。

【0053】

[0048] 第2の動作サイクルX12：SEL2は低レベル、SEL1は高レベルであるとき、VDATAはプログラミング電圧VPとなる。OLED210の容量211が大きいため、前のサイクルで発生したノードB11の電圧はそのままである。

40

【0054】

[0049] 従って、駆動トランジスタ214のゲート・ソース電圧は次式のようになる。

【0055】

$$VGS = VP + VB + VT \quad (3)$$

【0056】

【数2】

$$\Delta VB = \sqrt{\frac{IB}{\beta}} - VB \quad (4)$$

【0057】

[0050] VBが(4)に基づいて適正に選ばれたとき、VBはゼロである。駆動トラ

50

ンジスタ 214 のゲート・ソース電圧、即ち、 $V_P + V_T$  は、ストレージ・キャパシタ 212 に蓄積される。

#### 【0058】

[0051] 第 3 の動作サイクル X13 : IBIAS は低レベルになり、SEL1 はゼロになる。ストレージ・キャパシタ 212 に蓄積された電圧は、駆動トランジスタ 214 のゲート端子に印加される。駆動トランジスタ 214 はオンである。駆動トランジスタ 214 のゲート・ソース電圧は、ストレージ・キャパシタ 212 に蓄積された電圧を上回るようになる。従って、OLED 210 を流れる電流は、駆動トランジスタの閾値電圧及び OLED の特性のシフトとは無関係になる。

#### 【0059】

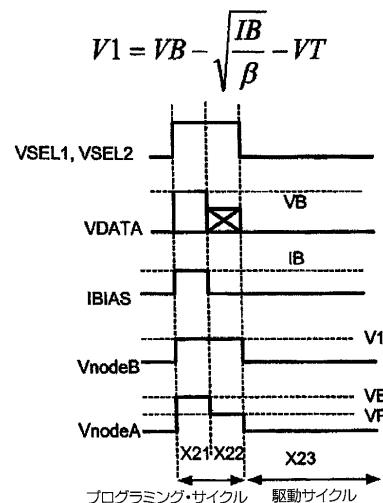

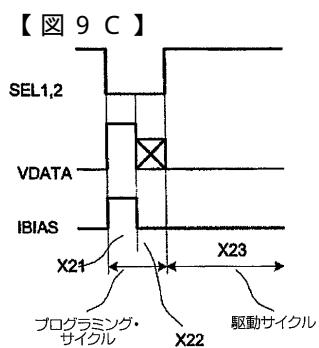

[0052] 図 8C を参照すると、図 8A のピクセル回路 CBVP02 に適用される更なる例示的な動作プロセスが示されている。図 8C では、「VnodeB」は図 8A のノード B11 の電圧を表し、「VnodeA」は図 8A のノード A11 の電圧を表し、「VSEL1」は図 8A の SEL1 に対応し、「VSEL2」は図 8A の SEL2 に対応する。プログラミング段階は 2 つの動作サイクル X21、X22 を有し、駆動段階は 1 つの動作サイクル X23 を有する。第 1 の動作サイクル X21 は図 8B の第 1 の動作サイクル X11 と同じである。第 3 の動作サイクル X23 は図 8B の第 3 の動作サイクル X13 と同じである。図 8C では、選択線 SEL1 及び SEL2 は同じタイミングを有する。従って、SEL1 と SEL2 は共通の選択線に接続され得る。

#### 【0060】

[0053] 第 2 の動作サイクル X22 : SEL1 及び SEL2 は高レベルである。スイッチ・トランジスタ 218 はオンである。IBIAS を流れるバイアス電流 IB はゼロである。

#### 【0061】

[0054] 駆動トランジスタ 214 のゲート・ソース電圧は、上述したように、 $VGS = V_P + V_T$  となることができる。駆動トランジスタ 214 のゲート・ソース電圧、即ち、 $V_P + V_T$  は、ストレージ・キャパシタ 212 に蓄積される。

#### 【0062】

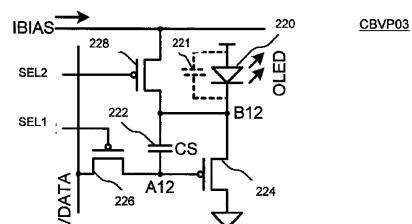

[0055] 図 9A のピクセル回路 CBVP03 は、図 8A のピクセル回路 CBVP02 に対して相補的であり、p 型トランジスタを有する。ピクセル回路 CBVP03 は、OLED 220、ストレージ・キャパシタ 222、駆動トランジスタ 224、並びにスイッチ・トランジスタ 226 及び 228 を含む。トランジスタ 224、226、及び 228 は p 型トランジスタである。2 つの選択線 SEL1 及び SEL2、信号線 VDATA、バイアス線 IBIAS、電圧供給線 VDD、及び共通接地はピクセル回路 CBVP03 に結合される。

#### 【0063】

[0056] トランジスタ 224 及び 226、並びにストレージ・キャパシタ 222 は A12 で接続される。OLED 220 のカソード電極、ストレージ・キャパシタ 222、並びにトランジスタ 224 及び 228 は、B12 で接続される。OLED カソードはピクセル回路 CBVP03 の他のエレメントに接続されるので、これにより任意の OLED 製造との統合が確実になされる。

#### 【0064】

[0057] 図 9B ~ 図 9C を参照すると、図 9A のピクセル回路 CBVP03 に適用される例示的な動作プロセスが示されている。図 9B は図 8B に対応する。図 9C は図 8C に対応する。図 9B ~ 図 9C の CBVP 駆動方式は、図 8B ~ 図 8C のものに似た IBIAS 及び VDATA を使用する。

#### 【0065】

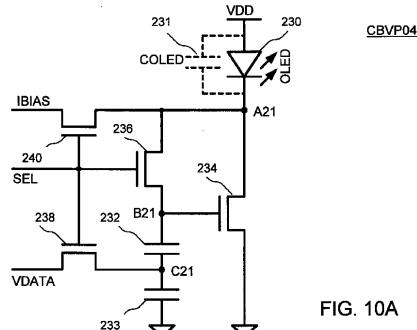

[0058] 図 10A のピクセル回路 CBVP04 は、OLED 230、ストレージ・キャパシタ 232 及び 233、駆動トランジスタ 234、並びにスイッチ・トランジスタ 236、238、及び 240 を含む。トランジスタ 234、236、238、及び 240 は

10

20

30

40

50

n型TFTトランジスタである。当業者であれば、ピクセル回路CBVP04に対して相補的であり、p型トランジスタを有する回路について理解するであろう。選択線SEL、信号線VDATA、バイアス線IBIAS、電圧線VDD、及び共通接地は、ピクセル回路CBVP04に結合される。OLED230、トランジスタ234、236及び、240は、ノードA21で接続される。ストレージ・キャパシタ232、並びにトランジスタ234及び236はノードB21で接続される。

## 【0066】

[0059] 駆動トランジスタ234の第1及び第2の端子のうちの一方は、A21でOLED230のカソード電極に接続され、他方は接地電位に接続される。ストレージ・キャパシタ232及び233は直列であり、駆動トランジスタ234のゲートと接地との間、即ち、B21と接地との間に接続される。スイッチ・トランジスタ236、238、及び240のゲート端子は選択線SELに接続される。スイッチ・トランジスタ236の第1及び第2の端子のうちの一方は、A21でOLED230及び駆動トランジスタ234に接続され、他方はB21で駆動トランジスタ234のゲート端子に接続される。スイッチ・トランジスタ238の第1及び第2の端子のうちの一方は信号線VDATAに接続され、他方はストレージ・キャパシタ232及び233を接続するC21に接続される。スイッチ・トランジスタ240の第1及び第2の端子のうちの一方はバイアス線IBIASに接続され、他方はA21でOLED230のカソード端子に接続される。OLED230のアノード電極はVDDに接続される。

## 【0067】

[0060] ピクセル回路CBVP04の動作は、複数のプログラミング・サイクルを有するプログラミング段階と、1つの駆動サイクルを有する駆動段階とを含む。プログラミング段階中、第1のストレージ・キャパシタ232は、プログラミング電圧VPに駆動トランジスタ234の閾値電圧を加えた値に荷電され、第2のストレージ・キャパシタ233はゼロに荷電される。

## 【0068】

[0061] その結果、駆動トランジスタ234のゲート・ソース電圧は次式のようになる。

## 【0069】

$$VGS = VP + VT \quad (5)$$

## 【0070】

ここで、VGSは駆動トランジスタ234のゲート・ソース電圧を表し、VTは駆動トランジスタ234の閾値電圧を表す。

## 【0071】

[0062] 図10Bを参照すると、図10Aのピクセル回路CBVP04に適用される1つの例示的な動作プロセスが示されている。プログラミング段階は2つの動作サイクルX31、X32を有し、駆動段階は1つの動作サイクルX33を有する。

## 【0072】

[0063] 第1の動作サイクルX31：選択線SELは高レベルである。バイアス電流IBはバイアス線IBIASを流れ、VDATAはVB - VPになる。ここで、VPはプログラミング電圧であり、VBは次式により与えられる。

## 【0073】

## 【数3】

$$VB = \sqrt{\frac{IB}{\beta}} \quad (6)$$

## 【0074】

[0064] その結果、第1のキャパシタ232に蓄積される電圧は次式のようになる。

## 【0075】

$$VC1 = VP + VT \quad (7)$$

10

20

30

40

50

## 【0076】

ここで、V<sub>C1</sub>は第1のストレージ・キャパシタ232に蓄積される電圧を表し、V<sub>T</sub>は駆動トランジスタ234の閾値電圧を表し、I<sub>DS</sub> = (V<sub>GS</sub> - V<sub>T</sub>)<sup>2</sup>により与えられるTFTの電流-電圧(I-V)特性の係数を表す。I<sub>DS</sub>は駆動トランジスタ234のドレイン・ソース電流を表す。

## 【0077】

[0065] 第2の動作サイクルX32: SELは高レベル、V<sub>DAT</sub>Aはゼロであるとき、IBIASはゼロになる。OLED230の容量231及びバイアス線IBIASの寄生容量が大きいので、前のサイクルで発生したノードB21の電圧及びノードA21の電圧は不变である。

10

## 【0078】

[0066] 従って、駆動トランジスタ234のゲート・ソース電圧は次式のように見出すことができる。

## 【0079】

$$V_{GS} = V_P + V_T \quad (8)$$

## 【0080】

ここで、V<sub>GS</sub>は駆動トランジスタ234のゲート・ソース電圧を表す。駆動トランジスタ234のゲート・ソース電圧はストレージ・キャパシタ232に蓄積される。

## 【0081】

[0067] 第3の動作サイクルX33: IBIASはゼロになる。SELはゼロになる。ノードC21の電圧はゼロになる。ストレージ・キャパシタ232に蓄積された電圧は、駆動トランジスタ234のゲート端子に印加される。駆動トランジスタ234のゲート・ソース電圧は、ストレージ・キャパシタ232に蓄積された電圧を上回るようになる。駆動トランジスタ234の電流が主にそのゲート・ソース電圧により定められることを考慮すると、OLED230を流れる電流は、駆動トランジスタ234の閾値電圧及びOLEDの特性のシフトとは無関係になる。

20

## 【0082】

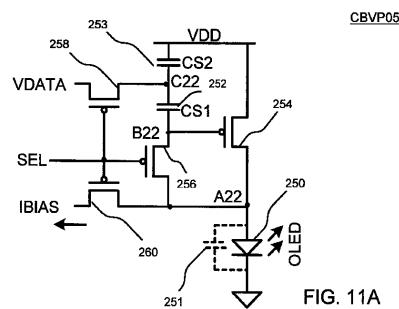

[0068] 図11Aのピクセル回路CBVP05は、図10Aのピクセル回路CBVP04に対して相補的であり、p型トランジスタを有する。ピクセル回路CBVP05は、OLED250、ストレージ・キャパシタ252及び253、駆動トランジスタ254、並びにスイッチ・トランジスタ256、258、及び260を含む。トランジスタ254、256、258、及び260はp型トランジスタである。2つの選択線SEL1及びSEL2、信号線V<sub>DAT</sub>A、バイアス線IBIAS、電圧供給線VDD、及び共通接地は、ピクセル回路CBVP05に結合される。共通接地は図8Aのものと同じであり得る。

30

## 【0083】

[0069] OLED250のアノード電極、トランジスタ254、256、及び260は、ノードA22で接続される。ストレージ・キャパシタ252、並びにトランジスタ254及び256は、ノードB22で接続される。スイッチ・トランジスタ258、並びにストレージ・キャパシタ252及び253は、ノードC22で接続される。

## 【0084】

40

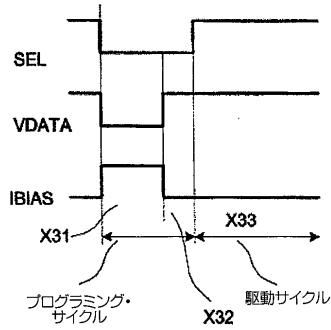

[0070] 図11Bを参照すると、図11Aのピクセル回路CBVP05が適用される1つの例示的な動作プロセスが示されている。図11Bは図10Bに対応する。図11Bに示されるように、図11BのCBVP駆動方式は、図10Bのものに類似したIBIAS及びV<sub>DAT</sub>Aを使用する。

## 【0085】

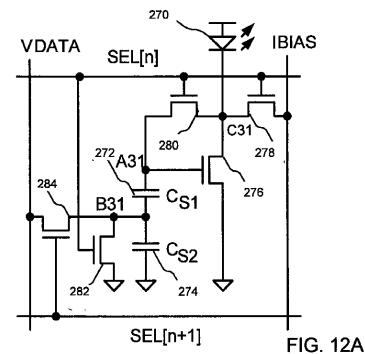

[0071] 図12AのCBVPピクセル回路を有する表示装置は、図10Aのピクセル回路CBVP04に基づくものであり、OLED270、ストレージ・キャパシタ272及び274、並びにトランジスタ276、278、280、282、及び284を含む。トランジスタ276は駆動トランジスタである。トランジスタ278、280、及び284はスイッチ・トランジスタである。トランジスタ276及び280、並びにストレージ

50

・キャパシタ 272 はノード A31 で接続される。トランジスタ 282 及び 284、並びにストレージ・キャパシタ 272 及び 274 は B31 で接続される。トランジスタ 278、280、及び 282 のゲート端子は、n 番目の行に対するアドレス線 SEL[n] に結合され、スイッチ・トランジスタ 284 のゲート端子は、(n+1) 番目の行に対するアドレス線 SEL[n+1] に結合される。トランジスタ 276、278、280、282 及び 284 は、n 型 TFT トランジスタである。当業者であれば、図 12A のピクセル回路に対して相補的であり、p 型トランジスタを有する回路について理解するであろう。当業者であれば、図 12A に適用される駆動技術は相補的なピクセル回路に適用可能であることを理解するであろう。図 12A では、2 つの行及び 1 つの列と関連したエレメントが示されている。図 12A の表示装置は、2 つより多い行及び 1 つより多い列を含み得る。

10

### 【0086】

[0072] 図 12B を参照すると、図 12A の表示装置に適用される 1 つの例示的な動作プロセスが示されている。図 12B では、「プログラミング・サイクル[n]」は、表示装置の行[n]に対するプログラミング・サイクルを表す。プログラミング時間は、2 つの連続する行(n 及び n+1) で共有される。n 番目の行のプログラミング・サイクル中、SEL[n] は高レベルであり、バイアス電流 IB はトランジスタ 278 及び 280 を流れている。ノード A31 の電圧は( IB / ) 1 / 2 + VT へと自己調節され、一方、ノード B31 の電圧はゼロであり、ここで、VT は、駆動トランジスタ 276 の閾値電圧を表し、は、IDS = (VGS - VT)<sup>2</sup> により与えられる TFT の電流 - 電圧(I-V)特性の係数を表し、IDS は駆動トランジスタ 276 のドレイン・ソース電流を表す。

20

### 【0087】

[0073] (n+1) 番目の行のプログラミング・サイクル中、V DATA は VP - VB へと変化する。その結果、ノード A31 の電圧は、VB = (IB / ) 1 / 2 である場合には VP + VT へと変化する。一定電流が全てのピクセルに用いられるので、IBIAS 線は一貫して適切な電圧を有し、結果として、線を事前に荷電する必要はなく、プログラミング時間がより短くなると共に電力消費がより低くなる。更に重要なことには、n 番目の行のプログラミング・サイクルの開始時に、ノード B31 の電圧は VP - VB からゼロへと変化する。従って、ノード A31 の電圧は( IB / ) 1 / 2 + VT へと変化し、これは、その最終値へと既に調節されているので、整定時間が速くなる。

30

### 【0088】

[0074] 図 13A の CBVP ピクセル回路を有する表示装置は、図 11 のピクセル回路 CBVP05 に基づくものであり、OLED 290、ストレージ・キャパシタ 292 及び 294、並びに p 型 TFT トランジスタ 296、298、300、302、及び 304 を有する。トランジスタ 296 は駆動トランジスタである。トランジスタ 298、300 及び 304 はスイッチ・トランジスタである。トランジスタ 296 及び 300、並びにストレージ・キャパシタ 292 はノード A32 で接続される。トランジスタ 302 及び 304、並びにストレージ・キャパシタ 292 及び 294 は B32 で接続される。トランジスタ 296、298、及び 200、並びに OLEDO 290 は C32 で接続される。トランジスタ 298、300、及び 302 のゲート端子は、n 番目の行に対するアドレス線 SEL[n] に結合され、スイッチ・トランジスタ 304 のゲート端子は、(n+1) 番目の行に対するアドレス線 SEL[n+1] に結合される。当業者であれば、図 13A のピクセル回路に対して相補的であり、n 型トランジスタを有する回路について理解するであろう。当業者であれば、図 13A に適用される駆動技術は相補的なピクセル回路に適用可能であることを理解するであろう。図 13A では、2 つの行及び 1 つの列と関連付けられたエレメントが示されている。図 13A の表示装置は、2 つより多い行及び 1 つより多い列を含むこともできる。駆動トランジスタ 296 は、OLED 290 のアノード電極と電圧供給線 VDD との間に接続される。

40

### 【0089】

50

[0075] 図13Bを参照すると、図13Aの表示装置に適用される1つの例示的な動作プロセスが示されている。図13Bは図12Bに対応する。図13BのCBVP駆動方式は、図12Bのものに類似したIBIAS及びVDATAを使用する。

#### 【0090】

[0076] 図14Aのピクセル回路CBVP06は、OLED322、ストレージ・キャパシタ324、駆動トランジスタ326、並びにスイッチ・トランジスタ328及び330を含む。トランジスタ326、328、及び330はp型TFTトランジスタである。当業者であれば、図14Aのピクセル回路に対して相補的であり、n型トランジスタを有する回路について理解するであろう。当業者であれば、図14Aに適用された駆動技術は相補的なピクセル回路に適用可能であることを理解するであろう。選択線SEL、信号線Vdata、バイアス線Ibias、及び電圧供給線Vddは、ピクセル回路CBVP06に接続される。バイアス線Ibiasは、寿命、電力、及びデバイスの性能及び均一性などのような表示装置の仕様に基づいて規定されるバイアス電流(Ibias)を供給する。

10

#### 【0091】

[0077] 駆動トランジスタ326の第1及び第2の端子のうちの一方は電圧供給線Vddに接続され、他方はノードB40でOLED322に接続される。キャパシタ324の一方の端子は信号線Vdataに接続され、他方の端子はノードA40で駆動トランジスタ326のゲート端子に接続される。スイッチ・トランジスタ328及び330のゲート端子は選択線SELに接続される。スイッチ・トランジスタ328はA40とB40の間に接続される。スイッチ・トランジスタ330はB40とバイアス線Ibiasの間に接続される。ピクセル回路CBVP06では、全ての空間的及び時間的な不均一性を補償するために、予め定められた固定電流(Ibias)がトランジスタ330を介して供給され、様々なグレー・スケールに対して必要な様々な電流レベルに電流を分割するために電圧プログラミングが使用される。

20

#### 【0092】

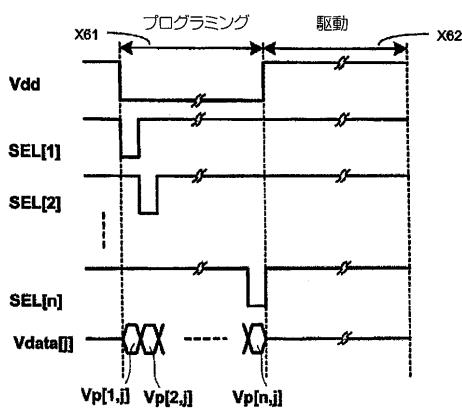

[0078] 図14Bを参照すると、図14Aのピクセル回路CBVP06に適用される1つの例示的な動作プロセスが示されている。動作プロセスは、プログラミング段階X61及び駆動段階X62を含む。図14BのVdata[j]は図14AのVdataに対応する。図14BのVp[k,j](k=1, 2, ..., n)はVdata[j]のk番目のプログラミング電圧を表す。ここで、「j」は列番号である。図14BのSEL[j](j=1, 2, ...)は、j番目の列に対する選択線(図14Aの「SEL」)を表す。

30

#### 【0093】

[0079] プログラミング・サイクルX61中、SELは低レベルなので、スイッチ・トランジスタ328及び330はオンである。バイアス電流Ibiasは、バイアス線Ibiasを通してピクセル回路CBVP06へ印加され、駆動トランジスタ326のゲート端子は、全ての電流が駆動トランジスタ326のソース・ドレイン間を流れることができるように、自己調節される。このサイクルでは、Vdataは、ピクセルのグレー・スケールに関連するプログラミング電圧を有する。駆動サイクルX62中、スイッチ・トランジスタ328及び330はオフであり、電流は駆動トランジスタ326及びOLED322を流れる。

40

#### 【0094】

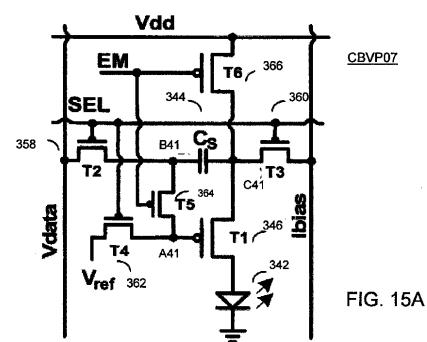

[0080] 図15Aのピクセル回路CBVP07は、OLED342、ストレージ・キャパシタ344、並びにトランジスタ346、358、360、362、364、及び366を含む。トランジスタ346、358、360、362、364、及び366は、p型TFTトランジスタである。当業者であれば、図15Aのピクセル回路に対して相補的であり、n型トランジスタを有する回路について理解するであろう。当業者であれば、図15Aに適用される駆動技術は相補的なピクセル回路に適用可能であることを理解するであろう。1つの選択線SEL、信号線Vdata、バイアス線Ibias、電圧供給線V

50

d d、基準電圧線 V r e f、及び発光 (emission) 信号線 E M は、ピクセル回路 C B V P 0 7 に接続される。バイアス線 I b i a s は、寿命、電力、及びデバイスの性能及び均一性などの表示装置の仕様に基づいて定められるバイアス電流 (I b i a s) を供給する。基準電圧線 V r e f は基準電圧 (V r e f) を供給する。基準電圧 V r e f は、バイアス電流 I b i a s と、グレー・スケール及び / 又はコントラスト比を含み得る表示装置の仕様とに基づいて決定され得る。信号線 E M は、ピクセル回路 C B V P 0 7 をオンにする発光信号 E M を供給する。ピクセル回路 C B V P 0 7 は、発光信号 E M に基づいて発光モードへと移行する。選択線 S E L は、トランジスタ 3 5 8、3 6 0、及び 3 6 2 のゲート端子に接続される。選択線 E M は、トランジスタ 3 6 4 及び 3 6 6 のゲート端子に接続される。トランジスタ 3 4 6 は駆動トランジスタである。トランジスタ 3 5 8、3 6 0、3 6 2、3 6 4、及び 3 6 6 は、スイッチング・トランジスタである。

10

#### 【 0 0 9 5 】

[0081] トランジスタ 3 6 2 の第 1 及び第 2 の端子のうちの一方は基準電圧線 V r e f に接続され、他方はノード A 4 1 でトランジスタ 3 4 6 のゲート端子に接続される。トランジスタ 3 6 4 の第 1 及び第 2 の端子のうちの一方は A 4 1 に接続され、他方は B 4 1 でキャパシタ 3 4 4 に接続される。トランジスタ 3 5 8 の第 1 及び第 2 の端子のうちの一方は V d a t a に接続され、他方は B 4 1 に接続される。トランジスタ 3 6 6 の第 1 及び第 2 の端子のうちの一方は V d d に接続され、他方は C 4 1 でキャパシタ 3 4 4 及びトランジスタ 3 4 6 に接続される。トランジスタ 3 6 0 の第 1 及び第 2 の端子のうちの一方は I b i a s に接続され、他方は C 4 1 でキャパシタ 3 4 4 及びトランジスタ 3 4 6 に接続される。トランジスタ 3 4 6 の第 1 及び第 2 の端子のうちの一方は O L E D 3 4 2 に接続され、他方は C 4 1 でキャパシタ 3 4 4 並びにトランジスタ 3 6 6 及び 3 6 0 に接続される。

20

#### 【 0 0 9 6 】

[0082] ピクセル回路 C B V P 0 7 では、予め定められた固定電流 (I b i a s) はトランジスタ 3 6 0 を通して供給され、一方、基準電圧 V r e f はトランジスタ 3 6 2 を介してトランジスタ 3 4 6 のゲート端子に印加され、プログラミング電圧 V P はトランジスタ 3 5 8 を介してストレージ・キャパシタ 3 4 4 の他方の端子 (即ち、ノード B 4 1) に印加される。ここで、トランジスタ 3 4 6 のソース電圧 (即ち、ノード C 4 1 の電圧) は、バイアス電流がトランジスタ 3 4 6 を流れることができ、結果として全ての空間的及び時間的な不均一性を補償することができるよう、自己調節される。また、様々なグレー・スケールに必要な様々な電流レベルに電流を分割するために電圧プログラミングが使用される。

30

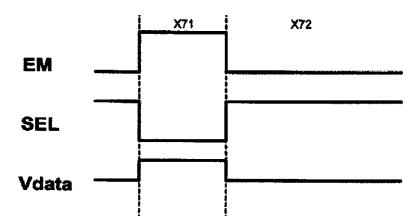

#### 【 0 0 9 7 】

[0083] 図 1 5 B を参照すると、図 1 5 A のピクセル回路 C B V P 0 7 に適用される 1 つの例示的な動作プロセスが示されている。動作プロセスは、プログラミング段階 X 7 1 及び駆動段階 X 7 2 を含む。プログラミング・サイクル X 7 1 中、S E L は低レベルなので、トランジスタ 3 5 8、3 6 0、及び 3 6 2 はオンであり、固定されたバイアス電流が I b i a s 線に印加され、トランジスタ 3 4 6 のソースは、全ての電流がトランジスタ 3 4 6 のソース・ドレン間を流れることができるように、自己調節される。このサイクルでは、V d a t a はピクセルのグレー・スケールに関連するプログラミング電圧を有し、キャパシタ 3 4 4 は、プログラミング電圧と、不整合を補償するために電流により発生する電圧とを蓄積する。駆動サイクル X 7 2 中、トランジスタ 3 5 8、3 6 0、及び 3 6 2 はオフであり、一方、トランジスタ 3 6 4 及び 3 6 6 は発光信号 E M によりオンとなる。この駆動サイクル X 7 2 中、トランジスタ 3 4 6 は O L E D 3 4 2 のための電流を供給する。

40

#### 【 0 0 9 8 】

[0084] 図 1 4 B では、表示装置全体がプログラミングされて点灯される (発光モードへと移行する)。対照的に、図 1 5 B では、発光線 E M を使用することによりプログラミング後に各行は点灯することができる。

50

## 【0099】

[0085] 図8～図15の上述の例では、各ピクセルのキャパシタは、ストレージ・キャパシタ及び図1の駆動キャパシタ14として作用し得る。上述の例では、図1の容量性電流源10はバイアス電流線へ一定電流を供給するために使用される。別の例では、容量性電流源10は表示装置の動作中にバイアス電流を調節することができる。

## 【0100】

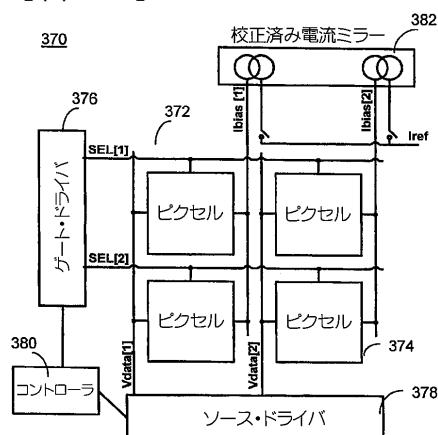

[0086] 図16を参照すると、CBVP駆動方式を実施するためのアレイ構造を有する表示システムの更なる一例が示されている。図16の表示システム370は、複数のピクセル374を有するピクセル・アレイ372、ゲート・ドライバ376、ソース・ドライバ378、及びコントローラ380を含む。コントローラ380は、表示アレイ372のプログラミング、校正、駆動、及び他の動作の制御およびスケジューリングのために提供され、これは、上述のようなCBVP駆動方式及び容量性駆動を含む。コントローラ380はドライバ376及び378を制御する。ピクセル回路374は、電流バイアス電圧プログラム型ピクセル（例えば、図8～図15のもの）であり、ここで、SEL[i]（i=1, 2, ...）は選択（アドレス）線（例えば、SEL）であり、Vdata[j]（j=1, 2, ...）は信号（データ）線（例えば、Vdata、VDATA）であり、Ibias[j]（j=1, 2, ...）はバイアス線（例えば、Ibias、IBIAS）である。ゲート・ドライバ376は、アドレス（選択）線（例えば、SEL[1]、SEL[2]、...）に作用する。ソース・ドライバ378は、データ線（例えば、Vdata[1]、Vdata[2]、...）に作用する。図15Aのピクセル回路CBVP07をピクセル回路374として使用するとき、ゲート・ドライバ376などのような表示装置の周辺のドライバが、各発光線EMを制御する。

10

20

## 【0101】

[0087] 表示システム370は、基準電流Irefを使用してバイアス線（例えば、Ibias[1]、Ibias[2]）に作用するための校正済み電流ミラー・ブロック382を含む。ブロック382は複数の校正済み電流ミラーを含み、それらのそれぞれが、対応するIbiasに対するものである。基準電流Irefは、スイッチを介して校正済み電流ミラー・ブロック382へ供給され得る。

## 【0102】

[0088] 図16では、電流ミラーは基準電流源を用いて校正される。パネルのプログラミング・サイクル中（例えば、図14BのX61、図15BのX71）、校正済み電流ミラー（ブロック382）はバイアス線Ibiasへ電流を供給する。これらの電流ミラーはパネルの縁部に作ることができる。図1の容量性ドライバ10が図16の基準電流Irefを発生させることもできる。

30

## 【0103】

[0089] ピクセル・エレメント（1又は複数）の特性（1又は複数）のシフト（例えば、表示装置の長時間の動作による駆動トランジスタの閾値電圧シフトや、発光デバイスの劣化）は、ストレージ・キャパシタに蓄積された電圧により、その電圧を駆動トランジスタのゲートへ印加することにより、補償される。従って、ピクセル回路は、シフトの影響もなく、発光デバイスを通じて安定した電流を供給することができ、それにより表示装置の動作寿命が改善される。更に、回路が単純であるため、従来のピクセル回路よりも、高い製品歩留まり、低い製造コスト、及び高い解像度が確実に得られる。上述のピクセル回路の整定時間は従来のピクセル回路よりもはるかに短いので、高精細度テレビジョンなどの大面積の表示装置に適しているが、小さい表示面積のものを除外するものではない。

40

## 【0104】

[0090] 図17～図19を参照すると、図2～図5のピクセル・アレイを形成し得るVBCPピクセル回路の例が示されている。VBCPピクセル、それらの表示システム、及び動作の例は、米国特許出願公開US2006/0125408及びPCT国際出願公開WO2009/127065に開示されており、それらを参照により本明細書に組み込むものとする。

50

## 【0105】

[0091] V B C P 駆動方式では、ピクセル電流は、ミラー・トランジスタのサイズを変更することなくスケールダウンされる。V B C P 駆動方式は、電流を使用して様々なグレー・スケールを提供し(電流プログラミング)、バイアスを使用して、プログラミングを加速させると共に、閾値電圧シフトなどのようなピクセルの時間依存性パラメータを補償する。駆動トランジスタの端子のうちの一方は仮想接地V G N Dに接続される。仮想接地の電圧を変えることにより、ピクセル電流が変化する。バイアス電流I Bはドライバ側でプログラミング電流I Pに加えられ、次に、バイアス電流は、仮想接地の電圧を変えることにより、ピクセル回路内のプログラミング電流から除去される。V B C P ピクセル回路を有する表示アレイを駆動するドライバは、ピクセル輝度データを電流に変換する。

10

## 【0106】

[0092] 容量性駆動技術は、より大型で高解像度の表示装置に適した整定時間を更に改善するために、V B C P 表示装置に適用可能である。図17～図19では、例えばバイアス電流I Bを供給するために図1の容量性ドライバ10が使用される場合に、データ線I D A T Aは、プログラミング電流I P及びバイアス電流I Bを対応するピクセルへ供給する。

## 【0107】

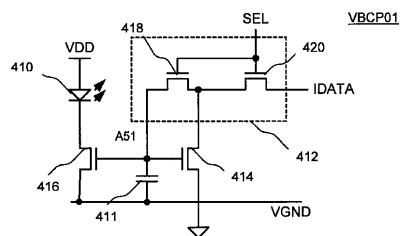

[0093] 図17Aのピクセル回路V B C P 01は、O L E D 410、ストレージ・キャパシタ411、スイッチ・ネットワーク412、並びにミラー・トランジスタ414及び416を含む。ミラー・トランジスタ414及び416は電流ミラーを形成し、トランジスタ414はプログラミング・トランジスタであり、トランジスタ416は駆動トランジスタである。スイッチ・ネットワーク412はスイッチ・トランジスタ418及び420を含む。トランジスタ414、416、418、及び420はn型T F Tトランジスタである。当業者であれば、ピクセル回路V B C P 01に対して相補的であり、p型トランジスタを有する回路について理解するであろう。選択線S E L、信号線I D A T A、仮想接地線V G N D、電圧供給線V D D、及び共通接地は、ピクセル回路V B C P 01に接続される。

20

## 【0108】

[0094] トランジスタ416の第1及び第2の端子のうちの一方はO L E D 410のカソード電極に接続され、他方はV G N Dに接続される。トランジスタ414のゲート端子、トランジスタ416のゲート端子、及びストレージ・キャパシタ411はノードA51で接続される。スイッチ・トランジスタ418及び420のゲート端子はS E Lに接続される。スイッチ・トランジスタ418の第1及び第2の端子のうちの一方はA51でトランジスタ416のゲート端子に接続され、他方はトランジスタ414に接続される。スイッチ・トランジスタ420の第1及び第2の端子のうちの一方はI D A T Aに接続され、他方はトランジスタ414に接続される。

30

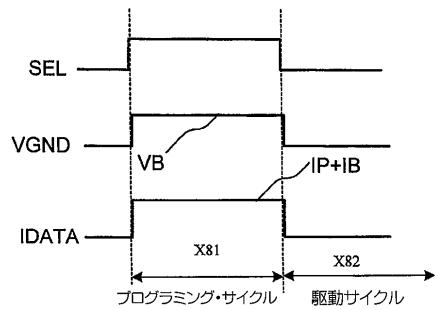

## 【0109】

[0095] 図17Bを参照すると、図17Aのピクセル回路V B C P 01に関する例示的な動作が示されている。図17A及び17Bを参照して、ピクセル回路V B C P 01に適用される電流スケーリング技術について詳細に説明する。ピクセル回路V B C P 01の動作は、プログラミング・サイクルX81及び駆動サイクルX82を有する。

40

## 【0110】

[0096] プログラミング・サイクルX81：S E Lは高レベルである。従って、スイッチ・トランジスタ418及び420はオンである。V G N Dはバイアス電圧V Bになる。電流(I B + I P)がI D A T Aを介して供給され、ここで、I Pはプログラミング電流を表し、I Bはバイアス電流を表す。(I B + I P)に等しい電流がスイッチ・トランジスタ418及び420を流れる。

## 【0111】

[0097] 駆動トランジスタ416のゲート・ソース電圧は次式のように自己調節される。

。

50

【0112】

【数4】

$$VGS = \sqrt{\frac{IP + IB}{\beta}} + VT \quad (9)$$

【0113】

ここで、 $V_T$  は駆動トランジスタ 416 の閾値電圧を表し、 $\beta$  は  $ID_S = (VGS - V_T)^2$  により与えられる TFT の電流 - 電圧 ( $I - V$ ) 特性の係数を表す。  $ID_S$  は駆動トランジスタ 416 のドレイン・ソース電流を表す。

【0114】

[0098] ストレージ・キャパシタ 411 に蓄積される電圧は次式のようである。

【0115】

【数5】

$$VCS = \sqrt{\frac{IP + IB}{\beta}} - VB + VT \quad (10)$$

【0116】

ここで、 $V_{CS}$  はストレージ・キャパシタ 411 に蓄積される電圧を表す。

【0117】

[0099] 駆動トランジスタ 416 の一方の端子は  $V_{GND}$  に接続されるので、プログラミング時間中に OLED 410 に流れる電流は次式の通りである。

【0118】

【数6】

$$I_{pixel} = IP + IB + \beta \cdot (VB)^2 - 2\sqrt{\beta} \cdot VB \cdot \sqrt{(IP + IB)} \quad (11)$$

【0119】

ここで、 $I_{pixel}$  は OLED 410 に流れるピクセル電流を表す。

【0120】

[00100]  $IB >> IP$  の場合、ピクセル電流  $I_{pixel}$  は次式のように記述することができる。

【0121】

【数7】

$$I_{pixel} = IP + (IB + \beta \cdot (VB)^2 - 2\sqrt{\beta} \cdot VB \cdot \sqrt{IB}) \quad (12)$$

【0122】

[00101]  $VB$  は次式のように適切に選択される。

【0123】

【数8】

$$VB = \sqrt{\frac{IB}{\beta}} \quad (13)$$

【0124】

[00102] ピクセル電流  $I_{pixel}$  はプログラミング電流  $IP$  と等しくなる。従って、プログラミング・サイクル中の不要な発光が避けられる。サイズ変更は不要なので、電流ミラー・ピクセル回路の 2 つのミラー・トランジスタ間のより良好な整合を達成することができる。

【0125】

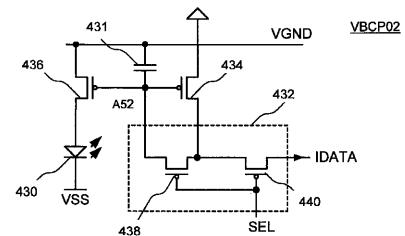

[00103] 図 18A のピクセル回路  $VBCP02$  は、図 17A のピクセル回路  $VBCP01$  に対して相補的であり、p 型トランジスタを有する。ピクセル回路  $VBCP02$  は、図 18B に示されるような  $VBCP$  駆動方式を用いる。ピクセル回路  $VBCP02$  は、O 50

L E D 430、ストレージ・キャパシタ431、スイッチ・ネットワーク432、並びにミラー・トランジスタ434及び436を含む。ミラー・トランジスタ434及び436は電流ミラーを形成し、トランジスタ434はプログラミング・トランジスタであり、トランジスタ436は駆動トランジスタである。スイッチ・ネットワーク432はスイッチ・トランジスタ438及び440を含む。トランジスタ434、436、438、及び440はp型TFTトランジスタである。選択線SEL、信号線DATA、仮想接地線V G N D、及び電圧供給線V S Sが、ピクセル回路V B C P 0 2に提供される。

#### 【0126】

[00104]トランジスタ436の第1及び第2の端子のうちの一方はV G N Dに接続され、他方はO L E D 430のカソード電極に接続される。トランジスタ434のゲート端子、トランジスタ436のゲート端子、ストレージ・キャパシタ431、及びスイッチ・ネットワーク432は、ノードA52で接続される。

10

#### 【0127】

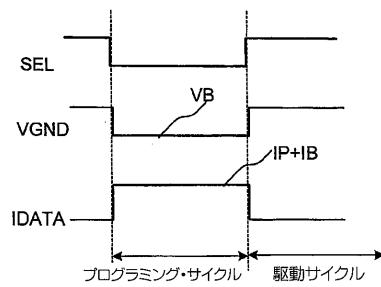

[00105]図18Bを参照すると、図18Aのピクセル回路V B C P 0 2に関する例示的な動作が示されている。図18Bは図17Bに対応する。図18BのV B C P駆動方式は、図17Bのものに似たI D A T A及びV G N Dを使用する。

#### 【0128】

[00106]図17A及び図18Aのピクセル回路V B C P 0 1及びV B C P 0 2に適用されるV B C P技術は、電流ミラー・タイプのピクセル回路以外の電流プログラム型ピクセル回路に適用可能である。

20

#### 【0129】

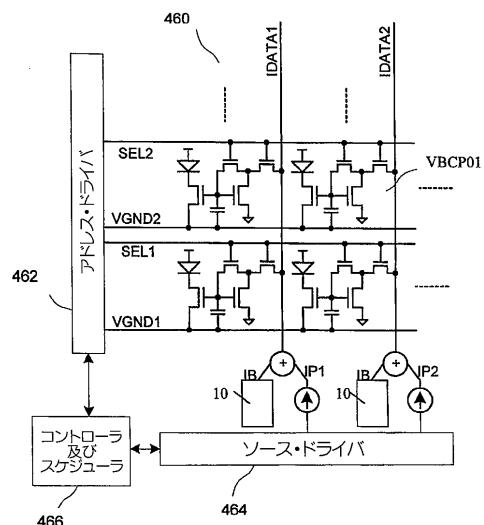

[00107]図19を参照すると、複数のV B C Pピクセル回路を有する表示システムが示されている。図19の表示アレイ460は図17Aのピクセル回路V B C P 0 1を含む。表示アレイ460は、記載されたV B C P駆動方式を適用可能な他の任意のピクセル回路を含んでもよい。図19では、4つのV B C Pピクセル回路が示されているが、表示アレイ460は、4つより多い、又は4つ未満のV B C Pピクセル回路を有してもよい。図19に示される「S E L 1」及び「S E L 2」は図17AのS E Lに対応する。図19に示される「V G N D 1」及び「V G N D 2」は図17AのV G N Dに対応する。図19に示される「I D A T A 1」及び「I D A T A 2」は図17AのI D A T Aに対応する。

#### 【0130】

[00108]I D A T A 1(又はI D A T A 2)は共通の列ピクセル間で共有され、S E L 1(又はS E L 2)及びV G N D 1(又はV G N D 2)はアレイ構造内の共通の行ピクセル間で共有される。S E L 1、S E L 2、V G N D 1、及びV G N D 2はアドレス・ドライバ462を介して駆動される。I D A T A 1及びI D A T A 2はソース・ドライバ464を介して駆動される。コントローラ及びスケジューラ466は、プログラミング、校正、駆動、及び表示アレイを動作させる他の動作の制御およびスケジューリングのために提供され、それは、上述のような、V B C P駆動方式および容量性駆動の制御及びスケジューリングを含む。

30

#### 【0131】

[00109]高解像度で安定した低電力の発光型表示装置を開発するための更なる技術について詳細に説明する。図20A～図20B及び図21A～図21Bの以下の例では、ピクセルの駆動サイクルにおいて図1の容量性電流源10が使用される。

40

#### 【0132】

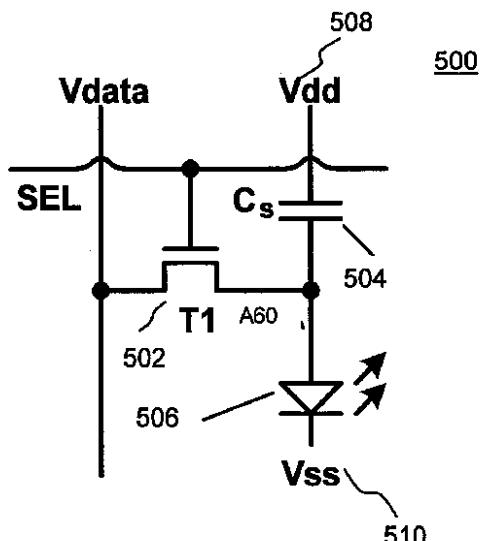

[00110]図20Aを参照すると、フレーム時間にわたって一定電流を供給することができるピクセル回路の一例が示されている。図20Aのピクセル回路500は、単一のスイッチ・トランジスタ(T1)502、ストレージ・キャパシタ504、及びO L E D 506を含む。キャパシタ504は電源V d d 508に結合される。O L E D 506は別の電源V s s 510に結合される。スイッチ・トランジスタ502のゲート端子はアドレス線S E Lに結合される。スイッチ・トランジスタ502の第1及び第2の端子のうちの一方はデータ線V d a t aに結合され、他方の端子はノードA60でキャパシタ504

50

及び O L E D 5 0 6 に結合される。

**【 0 1 3 3 】**

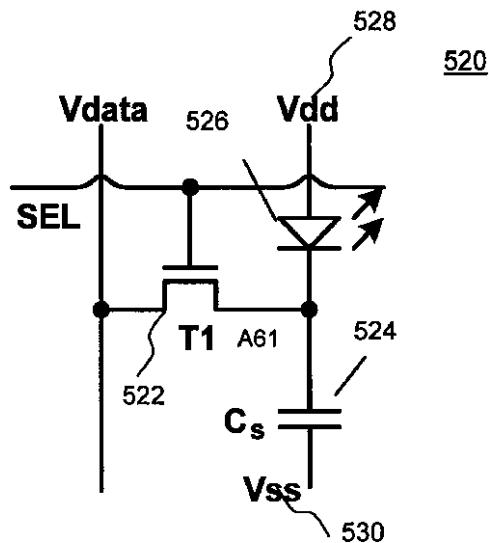

[ 00111 ] 図 2 0 B を参照すると、フレーム時間にわたって一定電流を供給することができるピクセル回路の別の例が示されている。図 2 0 B のピクセル回路 5 2 0 は、スイッチ・トランジスタ ( T 1 ) 5 2 2 、ストレージ・キャパシタ 5 2 4 、及び O L E D 5 2 6 を含む。キャパシタ 5 2 4 は電源 V d d 5 2 8 に結合される。O L E D 5 2 6 は別の電源 V s s 5 3 0 に結合される。スイッチ・トランジスタ 5 2 2 のゲート端子はアドレス線 S E L に結合される。スイッチ・トランジスタ 5 2 2 の第 1 及び第 2 の端子のうちの一方はデータ線 V d a t a に結合され、他方の端子はノード A 6 1 でキャパシタ 5 2 4 及び O L E D 5 2 6 に結合される。

10

**【 0 1 3 4 】**

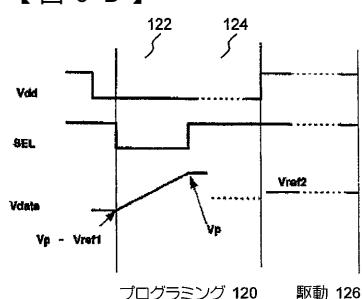

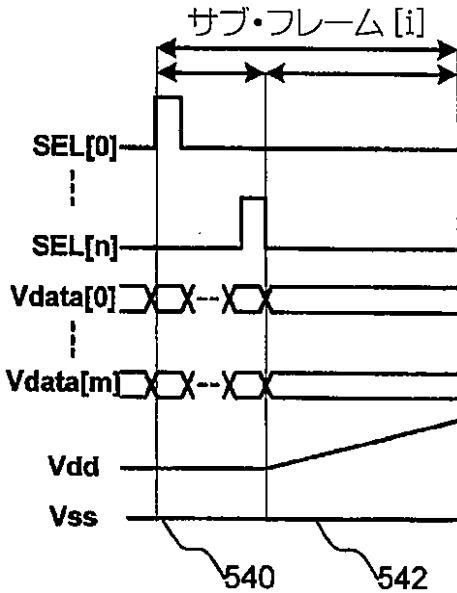

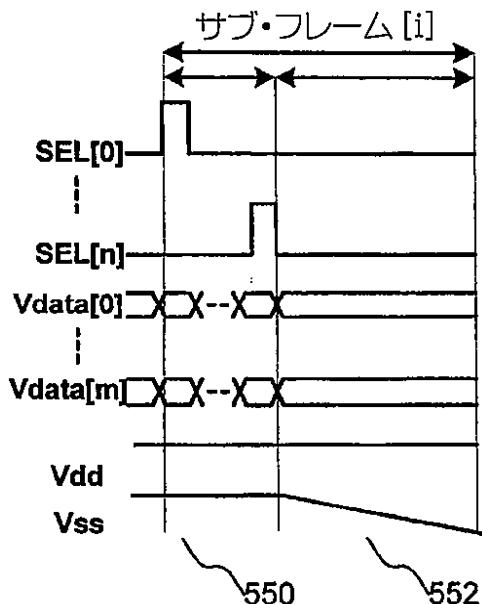

[ 00112 ] 図 2 1 A を参照すると、図 2 0 A ~ 図 2 0 B のピクセル回路に適用される波形の一例が示されている。図 2 1 A の S E L [ i ] ( i = 0 、 . . . 、 n ) は、 i 番目の行のアドレス線を表すものであり、図 2 0 A ~ 図 2 0 B の S E L に対応する。図 2 1 A の V d a t a [ j ] ( j = 0 、 . . . 、 m ) は、 j 番目の列のデータ線を表すものであり、図 2 0 A ~ 図 2 0 B の V d a t a に対応する。図 2 1 A の V d d は図 2 0 A ~ 図 2 0 B の V d d に対応し、図 2 1 A の V s s は図 2 0 A ~ 図 2 0 B の V s s s に対応する。図 2 1 A のフレーム時間は、プログラミング・サイクル 5 4 0 と駆動サイクル 5 4 2 とに分割される。プログラミング・サイクル 5 4 0 中、行はアドレス線 S E L [ i ] により連続的に選択され、選択された行のピクセルはプログラミング・データ V d a t a [ 0 ] ~ V d a t a [ m ] を用いてプログラムされる。プログラミング・サイクル 5 4 0 中、キャパシタと O L E D との間の接続ノード、例えば、 A 6 0 、 A 6 1 は、 V d a t a を通じてプログラミング電圧 ( V p ) へと荷電され、これは図 1 の I o u t として作用する。

20

**【 0 1 3 5 】**

[ 00113 ] 駆動サイクル 5 4 2 中、電源 V d d は、例えば、図 1 のランプ電圧発生器 1 2 からランプ電圧を V d d に印加することにより、増加する。一定電流がキャパシタ ( 5 0 4 、 5 2 4 ) を介して流れ。その結果、接続ノード、例えば、 A 6 0 、 A 6 1 は、荷電し始め、 O L E D がオンになるまで荷電する。次に、 C s V R / に等しい電圧が O L E D を流れる。ここで、「 V R 」はランプ電圧であり、「 」はランプ時間であり、「 C s 」はキャパシタ ( 5 0 4 、 5 2 4 ) の容量を表す。

30

**【 0 1 3 6 】**

[ 00114 ] 図 2 1 B を参照すると、図 2 0 A ~ 図 2 0 B のピクセル回路に適用される波形の別の例が示されている。図 2 1 B の S E L [ i ] ( i = 0 、 . . . 、 n ) は、 i 番目の行のアドレス線を表すものであり、図 2 0 A ~ 図 2 0 B の S E L に対応する。図 2 1 B の V d a t a [ j ] ( j = 0 、 . . . 、 m ) は、 j 番目の列のデータ線を表すものであり、図 2 0 A ~ 図 2 0 B の V d a t a に対応する。図 2 1 B の V d d は図 2 0 A ~ 図 2 0 B の V d d に対応し、図 2 1 B の V s s は図 2 0 A ~ 図 2 0 B の V s s に対応する。図 2 1 B のフレーム時間は、プログラミング・サイクル 5 5 0 と駆動サイクル 5 5 2 とに分割される。プログラミング・サイクル 5 5 0 中、行はアドレス線 S E L [ i ] により連続的に選択され、選択された行のピクセルはプログラミング・データ V d a t a [ 0 ] ~ V d a t a [ m ] を用いてプログラムされる。プログラミング・サイクル 5 5 0 中、キャパシタと O L E D との間の接続ノード、例えば、 A 6 0 、 A 6 1 は、 V d a t a を通じてプログラミング電圧 ( V p ) へと荷電され、これは図 1 の I o u t として作用する。

40

**【 0 1 3 7 】**

[ 00115 ] 駆動サイクル 5 5 2 中、電源 V s s は、例えば、図 1 のランプ電圧発生器 1 2 からランプ電圧を V s s に印加することにより、減少する。一定電流がキャパシタ ( 5 2 4 、 5 0 2 ) を通して流れ。その結果、接続ノード、例えば、 A 6 1 、 A 6 0 は放電し始め、 O L E D がオンになるまで放電する。次に、 C s V R / に等しい電圧が O L E D を通して流れ。

**【 0 1 3 8 】**

50

[00116] 図20A、図20B、図21A、及び図21Bに示されるように、この技術は、AMLCD表示装置に使用される駆動サイクルや駆動回路以上の駆動サイクルや駆動回路を必要としないので、結果として、表示装置のより短い駆動時間、より少ない電力消費、高い開口率及び安定性が得られ、従って、携帯電話やPDAを含む携帯デバイスに対する適用のコストが少なくなる。

#### 【0139】

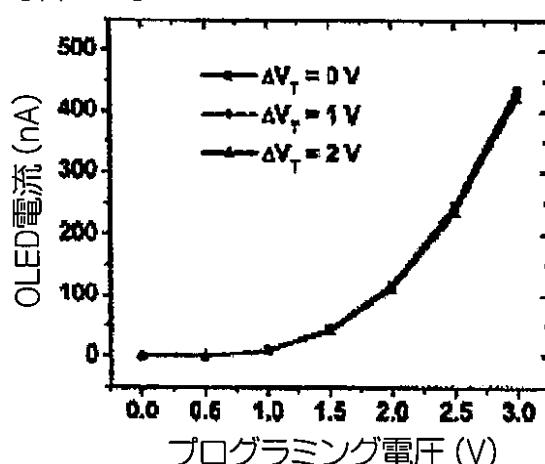

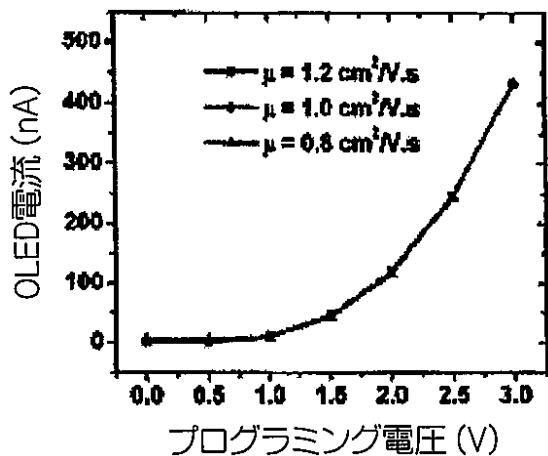

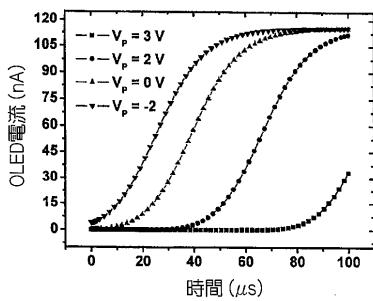

[00117] 図22を参照すると、様々なプログラミング電圧に対する1つのサブフレームでの図20A～図20Bのピクセル回路に関するシミュレーション結果(OLED電流)を示すグラフが示されている。図22では、「V<sub>p</sub>」はプログラミング電圧を表す。図22に示されるように、ピクセル電流は、プログラミング電圧(V<sub>p</sub>)が変化するにつれて時間により変調される。10

#### 【0140】

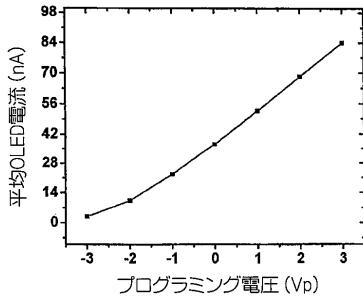

[00118] 図23を参照すると、図20A～図20Bのピクセル回路に関するシミュレーション結果(平均OLED電流)を示すグラフが示されている。図23のグラフは、ピクセルのI-V特性を示す。図23に示されるように、ピクセル電流は明らかにプログラミング電圧(V<sub>p</sub>)により制御される。

#### 【0141】

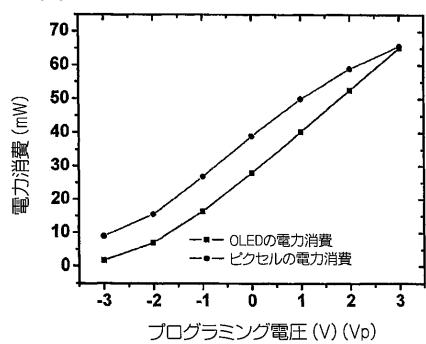

[00119] 図24を参照すると、5.58cm(2.2インチ)のクオーター・ビデオ・グラフィックス・アレイ(QVGA、Quarter Video Graphics Array)パネルの電力消費とOLEDに使用される電力消費とを示すグラフが示されている。図24に示されるように、パネル全体の電力消費はOLEDの電力消費に非常に近い。特に、容量性電圧全体がOLED(図20A～図20Bの506、536)へ行くので、電力消費は高電流レベルでOLEDの電力消費に近付く。ここで、断熱的な電荷共有を使用して、例えば、2つの隣接した行の間で電荷を共有することにより、ドライバ側の電力消費を改善することができる。20

#### 【0142】

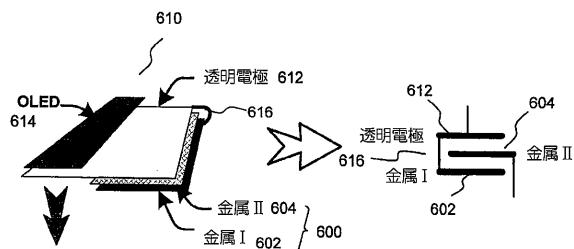

[00120] 図25を参照すると、ボトム・エミッション型表示装置を駆動するための大型キャパシタの実装の一例が示されている。図25に示されるキャパシタ600はインター・デジタル型(inter-digitated)キャパシタであり、図1の駆動キャパシタ10及び/又はピクセル回路のストレージ・キャパシタとして使用可能である。図20A～図20Bのキャパシタ504及び524は、インター・デジタル型キャパシタ600であり得る。インター・デジタル型キャパシタ600は、金属I層602及び金属II層604を含む。OLED装置610は、インター・デジタル型キャパシタ600上に形成され、少なくとも透明な下部電極612とOLED層614とを有する。OLED層614は下部電極612上に位置する。金属I層602は、相互接続線616を介してOLEDの下部電極612に結合される。金属I層602及び金属II層604は、OLED614からの光を妨げることなく下部電極612の下方に位置する。図25では、OLED層614は下部電極612の一側に配され、金属層602及び604は下部電極612の他側の下に配される。これにより、開口率を犠牲にすることなく大型キャパシタが得られる。30

#### 【0143】

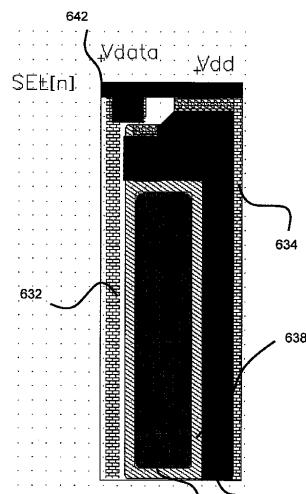

[00121] 図26を参照すると、180ppiの表示解像度に対して25%を超える開口率をもつボトム・エミッション型ピクセルのレイアウトの一例が示されている。図26では、図20Aに示されるピクセル回路に対する大容量を作り出すために複数の層が使用されている。ここで、キャパシタは、金属II 634と、それを挟むITO 638及び金属I 640との3つの層から作られる。金属層634及び640は図20Aのキャパシタ504を形成する。金属I層640は図25の602に対応し、金属II層634は図25の604に対応する。データ線632は、電圧を用いてピクセルをプログラミングするために使用される。OLEDバンク636は、OLEDがパターニングされたOLED電極に接触できるようにするための開口部である。選択線642は、プログラミングのためにピクセルへアクセスできるように選択トランジスタをオンにするために使用され4050

る。

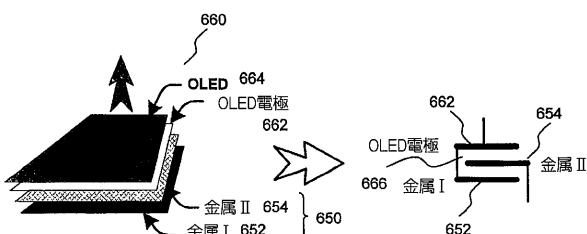

#### 【0144】

[00122] 図27を参照すると、トップ・エミッショニ型表示装置を駆動するための大型キャパシタの実装の一例が示されている。図27に示されるキャパシタ650はインター・デジタル型キャパシタであり、図1の駆動キャパシタ10及び／又はピクセル回路のストレージ・キャパシタとして使用可能である。図20A～図20Bのキャパシタ504及び524は、インター・デジタル型キャパシタ650であり得る。インター・デジタル型キャパシタ650は、金属I層652及び金属II層654を含む。OLED装置660は、インター・デジタル型キャパシタ650上に形成され、少なくとも下部電極662及びOLED層664を有する。OLED層664は下部電極662上に位置する。金属I電極層652は、相互接続線566を介してOLEDの下部電極662に結合される。これにより、表示解像度を犠牲にすることなく大型キャパシタが得られる。

10

#### 【0145】

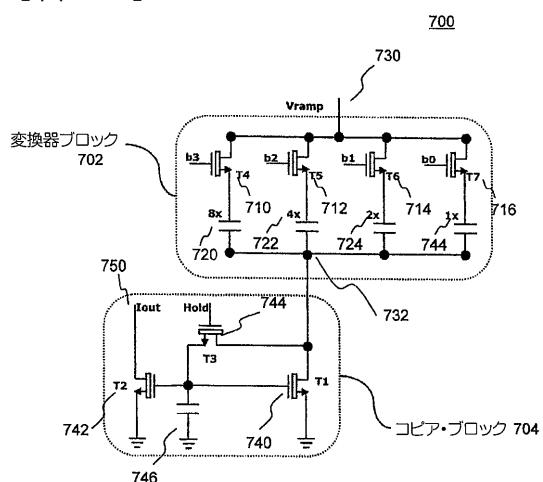

[00123] 容量性駆動に基づくデジタル・アナログ変換器(DAC)について詳細に説明する。図28～図29を参照すると、容量性駆動に基づくDAC及びその動作の一例が示されている。図28のDAC700は、変換器ブロック702及びコピア(copier)・ブロック704を含む。変換器ブロック702は、複数のトランジスタ及び複数のキャパシタを含む。図28では、スイッチ・トランジスタ710、712、714、及び716、並びにキャパシタ720、722、724、及び726は、変換器ブロック702の構成要素の一例として示されている。トランジスタ及びキャパシタは、V<sub>ramp</sub>ノード730とノード732との間に直列に結合される。キャパシタ720、722、724、及び726は異なるサイズにされる。V<sub>ramp</sub>ノード730は、ランプ電圧発生器、例えば、図1の12に結合され得る。変換器ブロック702は電流を発生させる。

20

#### 【0146】

[00124] コピア・ブロック704は、ノード732で変換器ブロック702に結合され、トランジスタ740、742、及び744、並びにキャパシタ746を含む。トランジスタ740は、変換器ブロック702により発生した電流を複製(コピー)する。トランジスタ742は、I<sub>out</sub>750を介して、ピクセル回路を含む外部回路へ電流を印加する。

#### 【0147】

[00125] 変換器ブロック702で電流を発生させている間、トランジスタ710、712、714、及び716は、対応するビット値b3～b0(b<3:0>)に基づいて、オン又はオフの何れかである。その結果、ランプ電圧V<sub>ramp</sub>が、ONスイッチ(トランジスタ)に接続されたキャパシタへ印加される。キャパシタは異なるサイズにされるので、それぞれ、デジタル測定基準で、対応するビットの値を表す電流を発生させる。例えば、b<3:0>が「1010」の場合、2つのキャパシタ(例えば、図28の720及び724)がランプ電圧(730)に接続される。その結果、8C×S+2C×Sに等しい電流が発生する。ここで、Cは単位キャパシタであり、Sはランプの傾斜である。キャパシタはランプを電流に変換する。合計の電流はトランジスタ740へ進み、トランジスタ740は、トランジスタ744がオンのときにこの電流をコピーする。

30

40

#### 【0148】

[00126] 図28の例では、変換器ブロック702により発生した電流はコピア・ブロック704を介して供給される。しかしながら、別の例では、変換器ブロック702は、ピクセル回路を含む外部回路に直接に接続され得る。

#### 【0149】

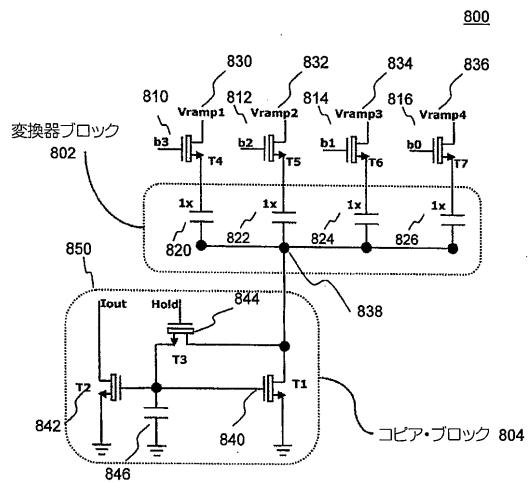

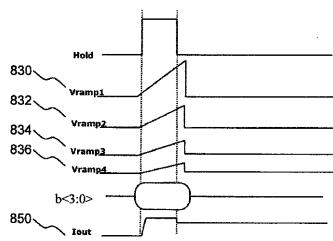

[00127] 図30～図31を参照すると、容量性駆動に基づくDAC及びその動作の別の例が示されている。図30のDAC800は、変換器ブロック802及びコピア・ブロック804を含む。変換器ブロック802は、スイッチ・トランジスタにそれぞれ結合する複数のキャパシタを含む。図30では、キャパシタ820、822、824、及び826が変換器ブロック802の構成要素の一例として示され、スイッチ・トランジスタ8

50

10、812、814、及び816はそれぞれ、キャパシタ820、822、824、及び826に結合される。トランジスタ810、812、814、及び816は、それぞれ、Vrampノード830、832、834、及び836に結合され、Vramp1、Vramp2、Vramp3、及びVramp4を受け取る。キャパシタ820、822、824、及び826は同じサイズを有し得る。Vrampノード830、832、834、及び836のそれぞれは、ランプ電圧発生器、例えば、図1の12に結合され得る。Vrampノード830、832、834、及び836のランプ電圧Vramp1、Vramp2、Vramp3、Vramp4は互いに異なる。変換器ブロック802は電流を発生させる。

## 【0150】

10

[00128] コピア・ブロック804はノード838で変換器ブロック802に結合され、トランジスタ840、842、及び844、並びにキャパシタ846を含む。トランジスタ840は、変換器ブロック802により発生した電流をコピーする。トランジスタ842は、Iout850を介して、ピクセル回路を含む外部回路へ電流を印加する。コピア・ブロック804は図28のコピア・ブロック704に対応する。

## 【0151】

[00129] 図30の例では、キャパシタをサイズ決めを行う代わりに、各キャパシタへ適用されるランプの傾斜が変えられる。回路の基本動作は図28のものと同じであるが、電流レベルは様々なランプの傾斜により定められる。例えば、b<3:0>が「1010」の場合、2つのキャパシタ（例えば、図30の820及び824）がランプ（例えば、図30の830及び834）に接続される。その結果、C×8S+C×2Sに等しい電流が発生する。ここで、Cはキャパシタであり、Sはランプの単位傾斜である。

20

## 【0152】

[00130] 本発明の上述の実施形態は、薄膜シリコン（例えば、a-Si、n-Si、μc-Si、ポリSi）及びそれに関連するSi集積回路CMOS技術、真空蒸着し溶液処理した有機体及びポリマー、並びに関連の無機／有機ナノコンポジット、並びに半導体酸化物（例えば、酸化インジウム、酸化亜鉛）を含む、様々な材料系のバックプレーン技術と関連した電力消費を低減することができる。更に、本発明の上述の実施形態により、低コストの駆動方式を使用して、より長寿命の要件に対して適用することが可能になる。また、本発明は、温度変化及び機械的応力の影響を受けにくい。

30

【図1】

FIG. 1

【図2】

【図3】

【図4】

【図5】

【図6A】

【図6 B】

【図7 A】

【図 7 B】

【図 8 A】

FIG. 8A

【図 8 B】

【図 8 C】

【図 9 A】

FIG. 9A

【図 10A】

FIG. 10A

【 図 1 0 B 】

【図11A】

CBVP05

【図11B】

【図12A】

FIG. 12A

【図12B】

【図 1 3 A】

FIG. 13A

【図13B】

【図 14A】

Vdd

FIG. 14A

【 図 1 4 B 】

【 図 1 5 A 】

【図15B】

FIG. 15B

【図16】

【図 17A】

FIG. 17A

【図 17B】

【図 18A】

FIG. 18A

【図 18B】

【図 19】

【図 20A】

FIG. 20A

【図 20B】

FIG. 20B

【図 21A】

【図 21B】

【図 22】

【図 23】

【図24】

【図25】

【図26】

FIG. 26

【図27】

【図28】

【図29】

FIG. 29

【図30】

【図31】

FIG. 31

---

フロントページの続き

(51)Int.Cl.

F I

|        |      |         |

|--------|------|---------|

| G 09 G | 3/20 | 6 4 2 A |

| G 09 G | 3/20 | 6 7 0 J |

| G 09 G | 3/20 | 6 2 3 C |

| G 09 G | 3/20 | 6 2 3 D |

| G 09 G | 3/20 | 6 4 1 C |

| G 09 G | 3/20 | 6 4 1 D |

(72)発明者 チャジ , ジー・レザ

カナダ国オンタリオ エヌ2ヴィ・2エス3 , ウォータールー , ケルソー・ドライブ 463

(72)発明者 ネイサン , アロキア

イギリス国ケンブリッジ シービー3・0ディーエル , ハンティンドン・ロード 189

審査官 山崎 仁之

(56)参考文献 特開平10-319908 (JP, A)

特開2001-350431 (JP, A)

特表2008-519305 (JP, A)

特開2006-154730 (JP, A)

特開2010-079159 (JP, A)

特開2007-065539 (JP, A)

特表2008-521033 (JP, A)

特開2004-341444 (JP, A)

(58)調査した分野(Int.Cl. , DB名)

G 09 G 3 / 30

G 09 G 3 / 20