(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7029961号**

**(P7029961)**

(45)発行日 令和4年3月4日(2022.3.4)

(24)登録日 令和4年2月24日(2022.2.24)

(51)国際特許分類

|         |                |         |       |

|---------|----------------|---------|-------|

| H 0 4 N | 5/374(2011.01) | H 0 4 N | 5/374 |

| H 0 4 N | 5/341(2011.01) | H 0 4 N | 5/341 |

F I

請求項の数 15 (全18頁)

|                   |                             |

|-------------------|-----------------------------|

| (21)出願番号          | 特願2017-560252(P2017-560252) |

| (86)(22)出願日       | 平成28年5月19日(2016.5.19)       |

| (65)公表番号          | 特表2018-516013(P2018-516013) |

|                   | A)                          |

| (43)公表日           | 平成30年6月14日(2018.6.14)       |

| (86)国際出願番号        | PCT/US2016/033354           |

| (87)国際公開番号        | WO2016/187469               |

| (87)国際公開日         | 平成28年11月24日(2016.11.24)     |

| 審査請求日             | 令和1年5月20日(2019.5.20)        |

| 審判番号              | 不服2021-3135(P2021-3135/J1)  |

| 審判請求日             | 令和3年3月9日(2021.3.9)          |

| (31)優先権主張番号       | 62/163,730                  |

| (32)優先日           | 平成27年5月19日(2015.5.19)       |

| (33)優先権主張国・地域又は機関 | 米国(US)                      |

|          |                                                                                                                                                                                                            |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (73)特許権者 | 514108838<br>マジック リープ, インコーポレイテッド<br>M a g i c L e a p , I n c .<br>アメリカ合衆国 フロリダ 33322,<br>プランテーション, ウエスト サンライズ<br>ブルバード 7500<br>7500 W S U N R I S E B L V D<br>, P L A N T A T I O N , F L 333<br>22 USA |

| (74)代理人  | 100078282<br>弁理士 山本 秀策                                                                                                                                                                                     |

| (74)代理人  | 100113413<br>弁理士 森下 夏樹                                                                                                                                                                                     |

| (74)代理人  | 100181674<br>弁理士 飯田 貴敏                                                                                                                                                                                     |

最終頁に続く

(54)【発明の名称】 セミグローバルシャッタイメージヤ

**(57)【特許請求の範囲】****【請求項1】**

画像センサであって、

複数のブロックに分割された2次元ピクセルアレイであって、前記複数のブロックのそれぞれは、少なくとも2つの異なる行および2つの異なる列において配列されたピクセルを備える、2次元ピクセルアレイと、

画像を捕捉するために前記複数のブロックを連続的に露出するシャッタであって、各ブロック内の全てのピクセルは、同期して露出される、シャッタと、

複数の読出回路を備える読出回路網であって、各読出回路は、前記複数のブロックのうちの1つに対応し、前記読出回路のそれぞれは、各対応するブロック内のピクセルからの前記画像の信号を受信および処理することが可能である、読出回路網とを備え、

前記2次元ピクセルアレイは、M個の行のピクセルを含み、Mは、100以上であり、各ブロックの高さは、M個の行の組み合わせられた高さの少なくとも20分の1であるが、M個の行の前記組み合わせられた高さの5分の1未満であり、

前記2次元ピクセルアレイは、N個の列を含み、Nは、100以上であり、各ブロックの幅は、N個の列のピクセルの組み合わせられた幅の少なくとも20分の1であるが、N個の列の前記組み合わせられた幅の5分の1未満である、画像センサ。

**【請求項2】**

前記ブロックのうちの少なくとも2つは、異なる数のピクセルを含む、請求項1に記載の

画像センサ。

**【請求項 3】**

前記ブロックの少なくとも 2 つは、異なる幾何学的形状を有する、請求項 1 に記載の画像センサ。

**【請求項 4】**

前記複数のブロックのそれぞれは、同数のピクセルを含む、請求項 1 に記載の画像センサ。

**【請求項 5】**

タイミング信号を前記ブロックのそれぞれに伝送するタイミング制御モジュールを備え、前記タイミング信号は、前記ブロックの露出のシーケンスを開始する、請求項 1 に記載の画像センサ。

10

**【請求項 6】**

前記読み出回路網は、前記信号を増幅する増幅器と、前記信号をデジタルデータに変換するアナログ / デジタルコンバータとを備える、請求項 1 に記載の画像センサ。

**【請求項 7】**

前記複数のブロックは、第 1 のブロックと、第 2 のブロックとを含み、

前記読み出回路網は、前記第 1 のブロックの露出が完了した直後にピクセルの前記第 1 のブロックから信号を読み出し、

前記第 2 のブロックの露出は、前記第 1 のブロックからの信号の読み出しが完了する前に開始する、請求項 1 に記載の画像センサ。

20

**【請求項 8】**

前記複数のブロックは、第 1 のブロックと、第 2 のブロックとを含み、

前記第 2 のブロックの露出と前記第 1 のブロックの露出との間に遅延が存在し、前記遅延は、前記第 2 のブロックがその露出を完了する前に前記第 1 のブロックの読み出しが可能にするために十分に長い、請求項 1 に記載の画像センサ。

**【請求項 9】**

前記シャッタは、電子的に制御される、請求項 1 に記載の画像センサ。

**【請求項 10】**

画像センサを用いて画像を捕捉する方法であって、

前記画像センサの 2 次元ピクセルアレイ画像面積を複数のブロックに分割することであって、前記複数のブロックのそれぞれは、少なくとも 2 つの異なる行および 2 つの異なる列において配列されたピクセルを備える、ことと、

30

前記画像を捕捉するために前記複数のブロックを連続的に露出することであって、各ブロック内の全てのピクセルは、同期して露出される、ことと、

複数の別個の読み出回路を用いて前記複数のブロックのそれからの前記画像の信号を読み出すことであって、各読み出回路は、前記複数のブロックのうちの 1 つに対応する、ことを含み、

前記 2 次元ピクセルアレイは、M 個の行のピクセルを含み、M は、100 以上であり、各ブロックの高さは、M 個の行の組み合わせられた高さの少なくとも 20 分の 1 であるが、M 個の行の前記組み合わせられた高さの 5 分の 1 未満であり、

前記 2 次元ピクセルアレイは、N 個の列を含み、N は、100 以上であり、各ブロックの幅は、N 個の列のピクセルの組み合わせられた幅の少なくとも 20 分の 1 であるが、N 個の列の前記組み合わせられた幅の 5 分の 1 未満である、方法。

40

**【請求項 11】**

タイミング信号を前記ブロックのそれぞれに伝送することを含み、前記タイミング信号は、前記ブロックの露出のシーケンスを開始する、請求項 10 に記載の方法。

**【請求項 12】**

前記複数のブロックの少なくとも第 1 のブロックおよび第 2 のブロックから信号を連続的に読み出すことを含む、請求項 10 に記載の方法。

**【請求項 13】**

ピクセルの前記第 1 のブロックからの信号は、前記第 1 のブロックの露出が完了した直後

50

に読み出され、

前記第2のブロックの露出は、前記第1のブロックからの信号の読出が完了する前に開始する、請求項12に記載の方法。

#### 【請求項14】

前記第2のブロックの露出と前記第1のブロックの露出との間に遅延が存在し、前記遅延は、前記第2のブロックがその露出を完了する前に前記第1のブロックの読出を可能にするだけ長い、請求項12に記載の方法。

#### 【請求項15】

デジタルカメラであって、

複数のブロックに分割される2次元ピクセルアレイを備える画像センサであって、前記複数のブロックのそれぞれは、少なくとも2つの異なる行および2つの異なる列において配列されたピクセルを備える、画像センサと、

光を前記画像センサに指向させるレンズと、

画像を捕捉するために前記複数のブロックを連続的に露出するシャッタであって、各ブロック内の全てのピクセルは、同期して露出される、シャッタと、

前記ブロックの露出のシーケンスのタイミングを制御するタイミング制御モジュールと、複数の読出回路を備える読出回路網であって、各読出回路は、前記複数のブロックのうちの1つに対応し、前記読出回路のそれぞれは、各対応するブロック内のピクセルからの前記画像の信号を受信および処理することが可能である、読出回路網と、

前記読出回路網の出力から前記画像を組み立てるカメラASICと

を備え、

前記2次元ピクセルアレイは、M個の行のピクセルを含み、Mは、100以上であり、各ブロックの高さは、M個の行の組み合わせられた高さの少なくとも20分の1であるが、M個の行の前記組み合わせられた高さの5分の1未満であり、

前記2次元ピクセルアレイは、N個の列を含み、Nは、100以上であり、各ブロックの幅は、N個の列のピクセルの組み合わせられた幅の少なくとも20分の1であるが、N個の列の前記組み合わせられた幅の5分の1未満である、デジタルカメラ。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

(関連出願への相互参照)

本出願は、2015年5月19日に出願された「SEMI-GLOBAL SHUTTER IMAGE」いう題名の米国仮特許出願第62/163,730号に対して優先権を主張する。上記文献は、その全体として参照することによって本明細書において援用される。

##### 【0002】

(発明の分野)

本開示は、デジタル撮像の分野に監視、特に、複数のピクセルブロックを連続的に捕捉するが、各ブロック内のピクセルは同期して捕捉され得る、セミグローバルシャッタimerジャに関する。

##### 【背景技術】

##### 【0003】

(発明の背景)

画像センサ(またはイメージャ)は、概して、画像を形成するために要求される情報を検出および伝達し得る画像捕捉デバイス(例えば、カメラ)の一部を指す。デジタルカメラでは、画像センサは、典型的には、その上で画像が捕捉されるシリコン半導体であり得る。構造的には、センサは、光子を捕捉し、それらを電子に変換する感光性ダイオード(すなわち、フォトサイト)のアレイから成ることができる。各フォトサイト内の電子の蓄積は、電子信号(例えば、電圧)に変換されることができ、これは、順に、画素またはピクセルを表すデジタルデータに変換されることができる。これらの要素またはピクセルは、次

10

20

30

40

50

いで、最終画像を組み立てるために使用されることがある。最終画像は、カメラのメモリ内に記憶され、ディスプレイ上で閲覧される、および／またはさらに操作されるように読み出されることができる。

#### 【0004】

理想的には、良好に設計された画像センサは、カメラが比較的に高速のフレームレートを有することを可能にし、これは、カメラが短い時間周期以内により多数の画像を捕捉すると同時に、結果画像におけるモーションアーチファクト等の望ましくない効果の量を最小限にすることによって画像品質を維持することを可能にする。

#### 【発明の概要】

#### 【課題を解決するための手段】

10

#### 【0005】

#### (発明の簡単な要約)

本開示は、概して、複数のピクセルブロックを連続的に捕捉および処理し、各ブロック内のピクセルが同期して捕捉され得る、セミグローバルシャッタイメージヤおよび機構に関する。画像センサのセンサ要素（またはピクセル）は、複数のピクセルブロックに分割されることができる。同一のブロック内の全てのピクセルは、同時に光に露出されることがある。その後、露出されたピクセルのブロックからのデータが依然として読み出されている間、別のピクセルのブロックが、露出されることができる。本プロセスは、全てのピクセルが露出され、読み出されるまで繰り返されることがある。これは、ピクセルの露出とピクセル内に捕捉される情報が分析されるときとの間の遅延を有意に低減させ、それによって、カメラのフレームレート（または速度）を増加させることができる。加えて、所与のセミグローバルシャッタ画像センサに対する最適な数のピクセルブロックを設定し、同時に各ピクセルブロック内の全てのピクセルを露出することによって、セミグローバルイメージヤはまた、ピクセルブロックの連続的露出によって引き起こされ得る、結果画像へのある形態の望ましくない歪み（例えば、モーションアーチファクト）を低減させることができる。

20

#### 【0006】

概して、画像センサが、複数のブロックに分割され、複数のブロックのそれぞれは、少なくとも2つの異なる行および2つの異なる列において配列されるピクセルを備える、2次元ピクセルアレイと、複数のブロックを連続的に露出し、各ブロック内の全てのピクセルは、同期して露出される、シャッタとを含み得る。シャッタは、例えば、電子的に制御され得る。ピクセルアレイは、種々の構成を有し得る。例えば、ピクセルアレイは、M個の行のピクセルを伴う長方形アレイを含み得、Mは、100以上であり、各ブロックの高さは、M個の行の組み合わせられた高さの少なくとも20分の1であるが、M個の行の組み合わせられた高さの5分の1未満である。別の実施例として、ピクセルアレイは、N個の列を伴う長方形アレイを含み得、Nは、100以上であり、各ブロックの幅は、N個の列のピクセルの組み合わせられた幅の少なくとも20分の1であるが、N個の列の組み合わせられた幅の5分の1未満である。ブロックのいくつかは、他の好適な配列および幾何学的形状における異なる数のピクセルを含み得る一方、ブロックのいくつかは、同数のピクセルを含み得る。

30

#### 【0007】

いくつかの変形例では、画像センサは、タイミング信号をブロックのそれぞれに伝送する、タイミング制御モジュールを含む、またはそれと併用するために構成され得、タイミング信号は、ブロックの露出のシーケンスを開始する。さらに、画像センサは、複数のブロック毎の別個の読み出し電子機器を含む、またはそれと併用するために構成され得、読み出し電子機器は、対応するブロック内のピクセルからの電子信号を受信および処理することが可能であり得る。そのような別個の読み出し電子機器は、例えば、電子信号を增幅する增幅器と、電子信号をデジタルデータに変換するアナログ／デジタルコンバータとを含み得る。さらに、画像センサの一変形例では、読み出し電子機器は、第1のブロックの露出が完了した直後にピクセルの第1のブロックから電子信号を読み出し得、第2のブロックの露出が、第1

40

50

のブロックからの電子信号の読み出しが完了する前に開始する。別の変形例では、第2のブロックの露出と第1のブロックの露出との間に遅延が存在し得、遅延は、第2のブロックがその露出を完了する前に第1のブロックの読み出しが可能にするために十分に長い。

#### 【0008】

概して、画像センサを用いて画像を捕捉する方法が、画像センサの2次元ピクセルアレイ画像面積を複数のブロックに分割することであって、複数のブロックのそれぞれは、少なくとも2つの異なる行および2つの異なる列において配列されるピクセルを備える、ことと、複数のブロックを連続的に露出することであって、各ブロック内の全てのピクセルは、同期して露出される、ことを含み得る。本方法は、M個の行のピクセルを含む2次元ピクセルアレイを伴う画像センサ等の種々の構成の画像センサを用いて使用され得、Mは、100以上であり、各ブロックの高さは、M個の行のピクセルの組み合わせられた高さの少なくとも20分の1であるが、M個の行の組み合わせられた高さの5分の1未満である。別の実施例として、本方法は、N個の列を含む2次元ピクセルアレイを伴う画像センサを用いて使用され得、Nは、100以上であり、各ブロックの幅は、N個の列のピクセルの組み合わせられた幅の少なくとも20分の1であるが、N個の列の組み合わせられた幅の5分の1未満である。

10

#### 【0009】

本方法は、タイミング信号をブロックのそれぞれに伝送することを含み得、タイミング信号は、ブロックの露出のシーケンスを開始する。本方法はまた、複数のブロックの少なくとも第1のブロックおよび第2のブロック内に配列される電子信号を連続的に読み出すことを含み得る。一変形例では、ピクセルの第1のブロックからの電子信号は、第1のブロックの露出が完了した直後に読み出され得、第2のブロックの露出が、第1のブロックからの電子信号の読み出しが完了する前に開始し得る。さらに、第2のブロックの露出と第1のブロックの露出との間に遅延が存在し得、遅延は、第2のブロックの露出が完了する前に第1のブロックの読み出しが可能にするために十分に長い。

20

#### 【0010】

概して、デジタルカメラが、複数のブロックに分割される2次元ピクセルアレイを含み、複数のブロックのそれぞれは、少なくとも2つの異なる行および少なくとも2つの異なる列において配列されるピクセルを含む、画像センサと、光を画像センサに指向させる、レンズと、複数のブロックを連続的に露出し、各ブロック内の全てのピクセルは、同期して露出される、シャッタと、ブロックの露出のシーケンスのタイミングを制御する、タイミング制御モジュールと、複数のブロック毎の読み出電子機器であって、対応するブロック内のピクセルからの電子信号を受信および/または処理することが可能である、読み出電子機器と、読み出電子機器の出力から画像を組み立てる、カメラ特定用途向け集積回路（ASIC）とを含み得る。

30

本願明細書は、例えば、以下の項目も提供する。

##### (項目1)

画像センサであって、

複数のブロックに分割された2次元ピクセルアレイであって、前記複数のブロックのそれぞれは、少なくとも2つの異なる行および2つの異なる列において配列されたピクセルを備える、2次元ピクセルアレイと、

40

前記複数のブロックを連続的に露出するシャッタであって、各ブロック内の全てのピクセルは、同期して露出される、シャッタと

を備える、画像センサ。

##### (項目2)

前記2次元ピクセルアレイは、M個の行のピクセルを含み、Mは、100以上であり、各ブロックの高さは、M個の行の組み合わせられた高さの少なくとも20分の1であるが、M個の行の前記組み合わせられた高さの5分の1未満である、項目1に記載の画像センサ。

##### (項目3)

50

前記 2 次元ピクセルアレイは、N 個の列を含み、N は、100 以上であり、各ブロックの幅は、N 個の列のピクセルの組み合わせられた幅の少なくとも 20 分の 1 であるが、N 個の列の前記組み合わせられた幅の 5 分の 1 未満である、項目 1 に記載の画像センサ。

(項目 4)

前記ブロックのうちの少なくとも 2 つは、異なる数のピクセルを含む、項目 1 に記載の画像センサ。

(項目 5)

前記ブロックのうちの少なくとも 2 つは、異なる幾何学的形状を有する、項目 1 に記載の画像センサ。

10

(項目 6)

前記複数のブロックのそれぞれは、同数のピクセルを含む、項目 1 に記載の画像センサ。

(項目 7)

タイミング信号を前記ブロックのそれぞれに伝送するタイミング制御モジュールを備え、前記タイミング信号は、前記ブロックの露出のシーケンスを開始する、項目 1 に記載の画像センサ。

(項目 8)

前記複数のブロックのそれぞれのための別個の読出電子機器を備え、前記読出電子機器は、対応するブロック内のピクセルからの信号を受信および処理することが可能である、項目 1 に記載の画像センサ。

20

(項目 9)

前記読出電子機器は、前記信号を増幅する増幅器と、前記信号をデジタルデータに変換するアナログ / デジタルコンバータとを備える、項目 8 に記載の画像センサ。

(項目 10)

前記複数のブロックは、第 1 のブロックと、第 2 のブロックとを含み、

前記読出電子機器は、前記第 1 のブロックの露出が完了した直後にピクセルの前記第 1 のブロックから信号を読み出し、

前記第 2 のブロックの露出は、前記第 1 のブロックからの信号の読出が完了する前に開始する、項目 8 に記載の画像センサ。

(項目 11)

30

前記複数のブロックは、第 1 のブロックと、第 2 のブロックとを含み、

前記第 2 のブロックの露出と前記第 1 のブロックの露出との間に遅延が存在し、前記遅延は、前記第 2 のブロックがその露出を完了する前に前記第 1 のブロックの読出を可能にするために十分に長い、項目 8 に記載の画像センサ。

(項目 12)

前記シャッタは、電子的に制御される、項目 1 に記載の画像センサ。

(項目 13)

画像センサを用いて画像を捕捉する方法であって、

前記画像センサの 2 次元ピクセルアレイ画像面積を複数のブロックに分割することであって、前記複数のブロックのそれぞれは、少なくとも 2 つの異なる行および 2 つの異なる列において配列されたピクセルを備える、ことと、

40

前記複数のブロックを連続的に露出することであって、各ブロック内の全てのピクセルは、同期して露出される、ことと

を含む、方法。

(項目 14)

前記 2 次元ピクセルアレイは、M 個の行のピクセルを含み、M は、100 以上であり、

各ブロックの高さは、M 個の行のピクセルの組み合わせられた高さの少なくとも 20 分の 1 であるが、M 個の行の前記組み合わせられた高さの 5 分の 1 未満である、項目 13 に記載の方法。

(項目 15)

50

前記 2 次元ピクセルアレイは、N 個の列を含み、N は、100 以上であり、各ブロックの幅は、N 個の列のピクセルの組み合わせられた幅の少なくとも 20 分の 1 であるが、N 個の列の前記組み合わせられた幅の 5 分の 1 未満である、項目 13 に記載の方法。

(項目 16)

タイミング信号を前記ブロックのそれぞれに伝送することを含み、前記タイミング信号は、前記ブロックの露出のシーケンスを開始する、項目 13 に記載の方法。

(項目 17)

前記複数のブロックの少なくとも第 1 のブロックおよび第 2 のブロックから信号を連続的に読み出すことを含む、項目 13 に記載の方法。

10

(項目 18)

ピクセルの前記第 1 のブロックからの信号は、前記第 1 のブロックの露出が完了した直後に読み出され、

前記第 2 のブロックの露出は、前記第 1 のブロックからの信号の読み出しが完了する前に開始する、項目 17 に記載の方法。

(項目 19)

前記第 2 のブロックの露出と前記第 1 のブロックの露出との間に遅延が存在し、前記遅延は、前記第 2 のブロックがその露出を完了する前に前記第 1 のブロックの読み出しが可能にするだけ長い、項目 17 に記載の方法。

(項目 20)

20

デジタルカメラであって、

複数のブロックに分割される 2 次元ピクセルアレイを備える画像センサであって、前記複数のブロックのそれぞれは、少なくとも 2 つの異なる行および 2 つの異なる列において配列されたピクセルを備える、画像センサと、

光を前記画像センサに指向させるレンズと、

前記複数のブロックを連続的に露出するシャッタであって、各ブロック内の全てのピクセルは、同期して露出される、シャッタと、

前記ブロックの露出のシーケンスのタイミングを制御するタイミング制御モジュールと、

前記複数のブロックのそれぞれのための別個の読み出電子機器であって、前記読み出電子機器は、対応するブロック内のピクセルからの信号を受信および処理することが可能である

30

読み出電子機器と、

前記読み出電子機器の出力から画像を組み立てるカメラ ASIC を備える、デジタルカメラ。

**【図面の簡単な説明】**

**【0011】**

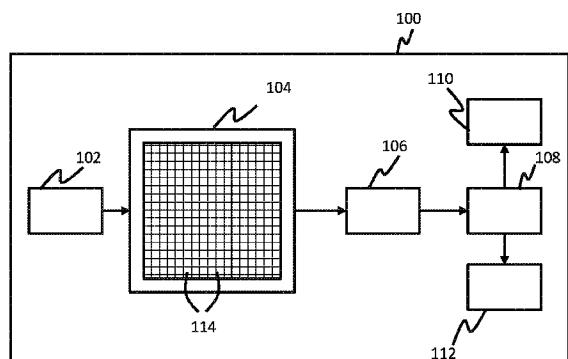

**【図 1】** 図 1 は、本開示のある実施形態による、デジタルカメラ 100 の例示的構成要素を図示する、ブロック図である。

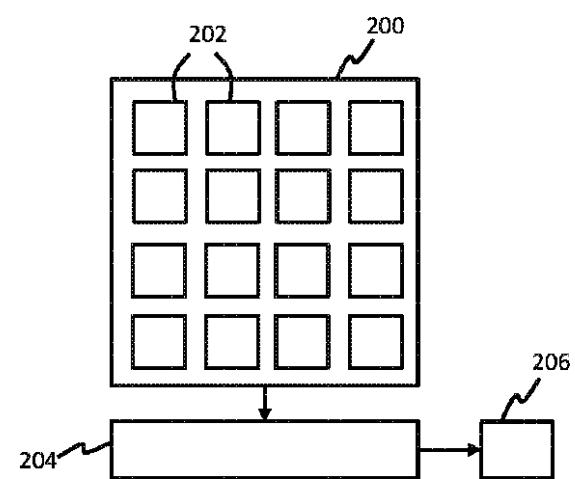

**【図 2】** 図 2 a は、グローバルシャッタを伴う CCD 画像センサ 200 の例示的構成要素を図示する、ブロック図である。図 2 b は、ローリングシャッタを伴う CMOS 画像センサ 210 の例示的構成要素を図示する、ブロック図である。

40

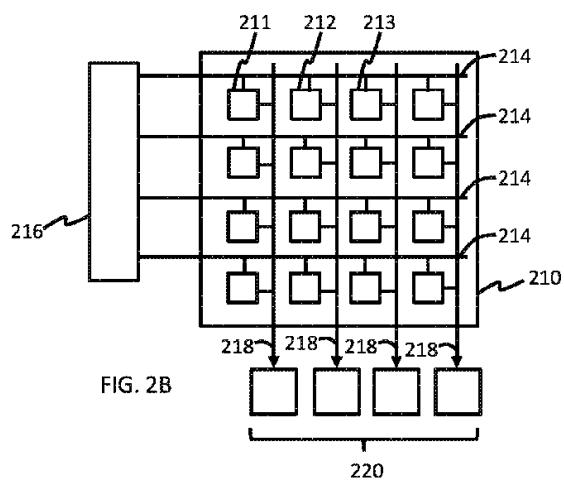

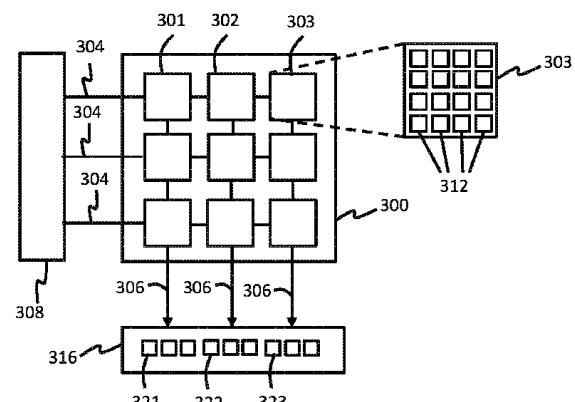

**【図 3】** 図 3 は、本開示のある実施形態による、セミグローバルシャッタを伴う画像センサ 300 の例示的構成要素を図示する、ブロック図である。

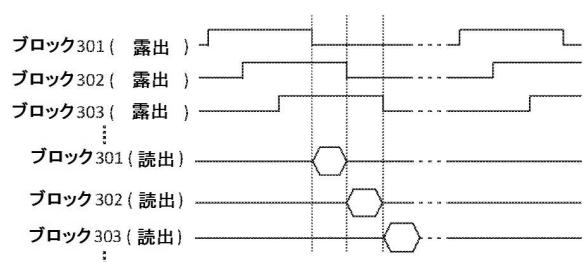

**【図 4】** 図 4 は、本開示のある実施形態による、図 3 のセミグローバルシャッタイメージヤにおけるブロックのうちの 3 つの露出および読み出の例示的タイムラインを図示する。

**【図 5】** 図 5 a - 5 c は、本開示のある実施形態による、種々のセミグローバルシャッタイメージヤに対して好適な種々のピクセルブロック構成を図示する。

**【発明を実施するための形態】**

**【0012】**

**(発明の詳細な説明)**

以下の好ましい実施形態の説明では、本明細書の一部を形成し、実践され得る具体的な実施

50

形態が例証として示される、付隨の図面を参照する。他の実施形態も、使用され得、構造的変更が、本開示の実施形態の範囲から逸脱することなく成され得ることを理解されたい。

#### 【 0 0 1 3 】

本明細書に使用されるように、用語「デジタルカメラ」は、画像センサを伴う任意のデジタル画像 / ビデオ捕捉デバイスを指し得る。用語「画像センサ」および「イメージヤ」は、1つ以上の画像を形成する情報を検出および伝達し得る、デジタルカメラにおける1つ以上の構成要素を説明するために同義的に使用されることができる。画像センサは、フォトサイト等のセンサ要素のアレイから成る画像面積を含むことができる。用語「フォトサイト」、「感光性ダイオード」、および「フォトダイオード」は、本文書において同義的に使用される。各センサ要素はまた、画像センサの「ピクセル」とも称され得る。用語「ブロック」および「ピクセルブロック」は、画像センサの複数のピクセルを含む画像面積内のある領域を指し得る。ピクセルの各ブロックは、本開示の実施形態による、任意のサイズおよび幾何学的形状であり得ることに留意されたい。好ましい実施形態では、ブロックは、連続的である、および / または面積と境界との最大実践比率を有することができる。用語「画像」、「結果画像」、および「最終画像」は、デジタルカメラの画像センサによって捕捉されるデジタル画像を指すように同義的に使用されることができる。画像は、独立画像またはビデオのフレームであり得る。

#### 【 0 0 1 4 】

本開示は、概して、複数のピクセルブロックを連続的に捕捉および処理し、各ブロック内のピクセルが同期して捕捉され得る、セミグローバルシャッタイメージヤおよび機構に関する。画像センサのセンサ要素（またはピクセル）は、複数のピクセルブロックに分割（または群化）されることができる。同一のブロック内の全てのピクセルは、同時に光に露出されることがある。露出は、集積要素に対する任意の好適な電気制御によって達成されることができる。例えば、これは、電荷表面を接地に結び付けることと、要素から読出ラッチへのC M O Sトランジスタを閉にすることとの組み合わせを伴うことができる。その後、露出されたピクセルのブロックからのデータが依然として読み出されている間、別のピクセルのブロックが、露出されることができる。本プロセスは、全てのピクセルが露出され、読み出されるまで繰り返されることができる。これは、ピクセルの露出とピクセル内に捕捉される情報が分析されるときとの間の遅延を有意に低減させることができる。加えて、所与の画像センサに対する最適な数のピクセルブロックを設定し、同時に各ピクセルブロック内の全てのピクセルを露出することによって、セミグローバルイメージヤはまた、ピクセルブロックの連続的露出によって引き起こされ得る、結果画像へのある形態の望ましくない歪み（例えば、モーションアーチファクト）を低減させることができる。

#### 【 0 0 1 5 】

図1は、本開示のある実施形態による、デジタルカメラ100の例示的構成要素を図示する、ブロック図である。デジタルカメラ100は、レンズ102と、画像センサ104と、アナログ / デジタル（A / D）コンバータ106と、カメラ特定用途向け集積回路（A S I C）108と、記憶デバイス110と、1つ以上の入力 / 出力（I / O）デバイス112とを含むことができる。カメラ100上のシャッタボタン（図1に図示せず）が押されると、光が、レンズ102を通過し、画像センサ104に到達することができる。画像センサ104は、光を捕捉することが可能なセンサ要素（例えば、フォトサイト）114の2次元アレイを含むことができる。あるタイプの画像センサ（例えば、C C Dセンサ）では、電荷が、捕捉された光の量に基づいて、各フォトサイト内に蓄積することができる。蓄積された電荷は、次いで、A / Dコンバータ106によってデジタル信号（例えば、デジタル数字）に変換されることができる。他のタイプの画像センサ（例えば、C M O Sセンサ）では、各フォトサイトは、どの程度光が露出の瞬間にピクセルに衝突しているかを読み取り、いずれの電荷も貯蔵することなくそれを電子信号に変換することができる。電子信号は、次いで、アナログ / デジタル（A / D）コンバータ106によってデジタル化され、次いで、カメラ特定用途向け集積回路（A S I C）108によって処理され、画像要素を形成することができる。

**【 0 0 1 6 】**

カメラ A S I C 1 0 8 が、画像センサ 1 0 4 のあらゆるフォトサイト 1 1 4 によって捕捉されるデータを具現化するデジタル信号の処理を終了すると、最終画像が、組み立てられることができる。画像を形成するプロセスは、結果画像から背景雑音を除去する随意のステップを含むことができる。画像は、記憶装置 1 1 0 内に記憶される、および / または I / O デバイス 1 1 2 を介して出力されることができる。記憶デバイス 1 1 0 は、限定ではないが、メモリカード、ハードドライブ、内部メモリ、およびクラウド記憶サービス等の外部記憶空間を含む、任意の好適な記憶デバイスであり得る。I / O デバイス 1 1 2 は、画像をデジタルカメラ 1 0 0 のディスプレイ（図 1 に図示せず）に出力する、またはこれをネットワークを経由して別のデバイスに伝送することができる。

10

**【 0 0 1 7 】**

図 1 は、図 1 に示されない他の構成要素を含み得る、デジタルカメラ 1 0 0 の例示的構成要素のいくつかのみを図示することを理解されたい。例えば、デジタルカメラ 1 0 0 はまた、フラッシュ、ズームおよび焦点モジュール、アンチエイリアシングフィルタ、バッテリ、ならびにデジタルカメラにおいて一般的に見出される他の構成要素を含むことができる。カメラ A S I C 1 0 8 は、カメラ A S I C 1 0 8 によって処理されないデジタルカメラの動作を実施するように設計される中央処理ユニット（C P U）に接続されることができる。

**【 0 0 1 8 】**

本開示の実施形態は、概して、図 1 に図示される画像センサ 1 0 4 および画像センサ 1 0 4 と関連付けられるシャッタ機構を対象とする。デジタルカメラ 1 0 0 におけるシャッタ機構は、画像がカメラ 1 0 0 によって取得されるとき、画像センサ 1 0 4 のセンサアレイの露出を制御することができる。シャッタ機構は、電子的、機械的、またはその両方の組み合わせであり得る。タイミング機構が、カメラに内蔵され、画像センサのピクセルに対する光露出時間を制御し、シャッタ機構に応じて、ピクセルが露出される順序を制御することができる。現在、殆どのデジタルカメラは、2つのタイプのシャッタ機構のうちの1つ、すなわち、グローバルシャッタまたはローリングシャッタのいずれかを採用している。以下の段落に説明されるように、これらの2つのタイプのシャッタ機構は、その個別の利点および欠点を有する。

20

**【 0 0 1 9 】**

グローバルシャッタは、典型的には、電荷結合素子（C C D）画像センサを伴うカメラにおいて見出されることがある。図 2 a は、グローバルシャッタを伴う C C D 画像センサ 2 0 0 の例示的構成要素を図示する、簡略化されたブロック図である。例証を目的として、C C D 画像センサ 2 0 0 は、 $4 \times 4$  の 2 次元ピクセルアレイ 2 0 2 を含むように示されるが、画像センサは、任意の構成において整合されるピクセル、または任意の好適な構成において配列されるピクセルの任意の数の列および行を含み得ることを理解されたい。実際に、C C D 画像センサが数百またはさらには数千のピクセルの行および / または列を有することは、珍しくはない。各ピクセルは、画像センサ 2 0 0 のフォトサイトに対応し、光子を捕捉することが可能であり得る。ピクセル 2 0 2 は、電子転送レジスタ 2 0 4 に接続されることができ、これは、順に、限定ではないが、増幅器および A / D コンバータを含み得る、読出電子機器 2 0 6 に接続されることができる。また、C C D 画像センサ 2 0 0 は、明確化を目的として図 2 a から省略される他の構成要素を含み得ることを理解されたい。

30

**【 0 0 2 0 】**

図 2 a のイメージ 2 0 0 のグローバルシャッタは、シャッタが「開」であるとき、光が事前判定された時間周期（シャッタ時間または露出時間）にわたってイメージ 2 0 0 の全センサアレイに到達し得るように動作することができる。その時間中、画像センサ 2 0 0 の全てのピクセル 2 0 2 は、並行して光を捕捉する（例えば、電荷を蓄積する）ことができる。シャッタが遮断されると、光は、もはやセンサに到達することはできず、ピクセルは、非アクティブな状態になり得る。C C D デジタルカメラにおけるグローバルシャッタ

40

50

タは、露出を制御するために、電子的に制御されることができる。

**【 0 0 2 1 】**

捕捉が完了した後、ピクセル内に収集された信号は、例えば、一度に 1 ピクセルずつ、電子転送レジスタ 204 に転送されることができ、そこから、それらは、読出電子機器 206 によって読み出され、処理されることができる。本プロセスは、信号を増幅することおよび／またはそれらをデジタルフォーマット（例えば、デジタル数字）に変換することを含むことができ、これは、結果画像を形成することができる。

**【 0 0 2 2 】**

デジタル撮像では、結果画像は、いくつかのキーポイントを含むことができ、これらは、画像の 1 つ以上の高度に位置特定可能かつ認識可能な特徴を含む、画像の小区分（例えば、 $5 \times 5$  または  $10 \times 10$  ピクセルブロック）によって定義されることができる。キーポイントは、未加工ピクセルのうちの 1 つ以上を処理することによって生産されることができる。各キーポイントは、これが連続的に取得される一連の画像の異なるフレームにおいて認識され得るようにキーポイントを記述する、記述子を含むことができる。カメラの移動およびこれが向いている方向は、異なるフレームからの種々のキーポイントを合致させることによって判定されることができる。本アプローチは、多くの場合、SLAM（同時位置特定およびマッピング）アルゴリズムを実装するときに使用される。

10

**【 0 0 2 3 】**

グローバルシャッタイメージヤによって採用される電子転送レジスタ 204 および読出電子機器 206 に対する本連続的電荷転送アプローチは、特に、画像センサが多数のピクセルを含む場合、イメージヤの各ピクセルからのデータが連続的に読み出される必要があるため、時間がかかり得る。それは、最後のピクセル（グローバルシャッタイメージヤ内の全ての他のピクセルとともに）の露出と、これらのピクセルが分析され得るとき（すなわち、全ての他のピクセルが分析された後）との間の遅延が有意であり得ることを意味し得る。言い換えると、これらの最後のピクセルから読み出された情報が最終的に処理されるとき、カメラと風景との間に相対的移動が存在した場合、これは、必ずしも、風景に対するカメラの現在の位置を正確に反映するわけではない。例えば、典型的なグローバルシャッタ CCD イメージヤが、全てのピクセル値を読み出し、画像のキーポイントを計算するために、露出間で約 15 ミリ秒かかる場合、最後のピクセルからの情報が分析されるまでに 15 ミリ秒の遅延が存在し得、これは、例えば、カメラの移動（または捕捉されている風景における移動）の判定に影響を及ぼし得る。これは、グローバルシャッタイメージヤの主要な欠点のうちの 1 つである。

20

**【 0 0 2 4 】**

グローバルシャッタは、全てのピクセルを同時に露出することによって、CCD 画像センサが画像全体を全く同一の瞬間に捕捉することを可能にするため、グローバルシャッタの利点のうちの 1 つは、結果画像が、通常、比較的に高い品質を有し得、モーションアーチファクト等の有意な望ましくない効果がないことである。全てのキーポイント（例えば、小ピクセルブロック）は、完全に保たれ、一連の連続的画像において容易に識別可能であり得る。

30

**【 0 0 2 5 】**

第 2 のタイプのシャッタ機構であるローリングシャッタは、典型的には、相補型金属酸化膜半導体（CMOS）画像センサを伴うデジタルカメラにおいて見出されることがある。グローバルシャッタとは対照的に、ローリングシャッタは、個々のピクセルまたは個々のピクセルの列／行が連続的に露出されることを可能にすることができる、したがって、第 1 のピクセル（または第 1 のピクセルの列／行）における情報は、次のピクセル（または次のピクセルの列／行）が光に露出されている間に読み出されることができる。CMOS 画像センサは、ピクセル（またはピクセルの列／行）を体系的に事前判定された順序でオン／オフにすることによって、本ローリング効果を達成することができる。

40

**【 0 0 2 6 】**

図 2 b は、ローリングシャッタを伴う CMOS 画像センサ 210 の例示的構成要素を図示

50

する、ブロック図である。例証を目的として、C M O S 画像センサ 2 1 0 は、 $4 \times 4$  の 2 次元ピクセルアレイを含むように示されるが、画像センサは、任意の構成において整合される、または任意の好適な構成において配列されるピクセルの任意の数の列および行を有し得ることを理解されたい。図 2 b の 2 次元ピクセルアレイの各ピクセル 2 1 1、2 1 2、2 1 3 は、光を電子信号に変換することが可能なフォトダイオードであり得る。画像センサ 2 1 0 にオーバーレイする導電性相互接続 2 1 4、2 1 8 のグリッドが、タイミングおよび読出信号を印加するために、ピクセルを行および列で接続することができる。特に、相互接続は、クロックおよびタイミング制御モジュール 2 1 6 から各ピクセル（または各ピクセルの行 / 列）にタイミング信号を伝送するために、行信号ライン（集合的に 2 1 4）を含むことができる。タイミング信号は、いつ各個々のピクセルまたはピクセルの行が光に露出されるか、また、いつ各ピクセルからの電子信号が読み出されるかを制御することができる。相互接続はまた、ピクセルからの信号を読み出し、さらなる処理のためにそれらを読出電子機器（集合的に 2 2 0）に伝送するために、垂直出力ライン（集合的に 2 1 8）を含むことができる。図 2 b に図示されるように、各出力ラインは、別個の読出電子機器 2 2 0 に接続されることができる。出力ライン毎の読出電子機器 2 2 0 は、例えば、増幅器および A / D コンバータを含むことができ、これらは、信号を増幅し、デジタルフォーマット（例えば、デジタル数字）に変換することができる。デジタル情報は、最終画像を組み立てるために使用されることができる。いくつかの C M O S センサでは、読出電子機器 2 2 0 の少なくともいくつかが、画像センサの個々のピクセル内に内蔵されることができる。また、図 2 b の C M O S 画像センサ 2 1 0 は、明確化を目的として図から省略される他の構成要素を含み得ることを理解されたい。

#### 【 0 0 2 7 】

C M O S センサ 2 1 0 の本アーキテクチャは、そのピクセル 2 1 2 のそれぞれ（または各ピクセルの行 / 列）が独立してオン / オフにされ、ピクセル（またはピクセルの行 / 列）からの信号が連続的に読み出されることを可能にする。動作時、クロックおよびタイミング制御モジュール 2 1 6 は、タイミング信号を個々のピクセル（または個々のピクセルの行 / 列）に送信し、その露出のタイミングを制御することができる。1 つのピクセルが露出されるとすぐに、その値が、読み出されることができる。事実上、露出と読出との間にいかなる遅延も存在しない。加えて、各ピクセル（またはピクセルの行 / 列）に関するシャッタリング効果は、全てのピクセルを横断してローリングベースで起こるようにプログラムされることができる。例えば、第 1 のピクセル 2 1 1 のピクセル値が読み出されているとき、第 2 のピクセル 2 1 2 は、その捕捉プロセスを終了することができる。同様に、第 2 のピクセル 2 1 2 のピクセル値が読み出されているとき、第 3 のピクセル 2 1 3 は、光を捕捉することができる。同様に、ある行のピクセルがともに露出され、読み出されているとき、次の行は、前の行がその読出を終了する前に光を捕捉し始めることができる。本質的に、全てのピクセル（またはピクセルの行）は、全ての他のピクセル（または次のピクセルの行）よりも少し後で読み出される。全てのピクセル（または行）読出は、例えば、1 マイクロ秒分の 1 だけその近傍に対して非対称にされることができる。したがって、殆どの場合、少なくとも 1 つのピクセルが、露出され、任意の個々のピクセルに対する露出と読出との間には、殆ど遅延が存在しない。これは、ローリングシャッタイメージャを伴うカメラが、ピクセルの少なくともいくつかに関して、ピクセルの露出とピクセルから読み出される情報の分析との間の遅延を低減させることを可能にする。低減は、特に、それらがグローバルシャッタイメージャによって処理される場合と比較して、最後に露出され、読み出されるピクセルに関して有意であり得る。

#### 【 0 0 2 8 】

しかしながら、ローリングシャッタは、個々のピクセル（または個々のピクセルの行 / 列）に対する露出時間をずらすため、異なるピクセルによって捕捉される情報は、時間内の異なる瞬間に捕捉されるであろう。捕捉されている風景内の物体とカメラとの間に相対的移動が存在する場合、結果画像は、異なるピクセルのずらされた露出に起因して、ウォブル、スキュー、スミア等の顕著なモーションアーチファクトを有し得る。これは、ローリ

10

20

30

40

50

ングシャッタイメージヤの欠点のうちの1つである。加えて、キーポイント内の全てのピクセルが同時に露出されるわけではないことの結果として、1つ以上のキーポイントが、認識できない程度に歪曲され得る。歪曲されたキーポイントは、もはや一連の連続的フレーム内の対応する特徴を識別することが可能ではなく、したがって、カメラのその独自の移動または捕捉されている物体の移動を追跡する能力に影響を及ぼし得る。

#### 【0029】

要するに、上記に議論されるシャッタ機構の両方が、有意な欠点を有し、すなわち、グローバルシャッタイメージヤは、ピクセル露出と分析との間に遅延を引き起こし得、ローリングシャッタイメージヤは、結果として生じる画像に望ましくない効果（例えば、歪み）を引き起こし得る。これらの短所を最小限にするために、以下の実施形態は、本明細書では「セミグローバルシャッタ」と称される、第3のタイプのシャッタ機構を伴う画像センサを開示する。セミグローバルシャッタは、ピクセル露出と分析との間の遅延を低減させる一方、ある形態の望ましくない歪みを低減させることができる。

10

#### 【0030】

具体的には、セミグローバルシャッタを伴う画像センサは、その2次元ピクセルアレイを複数のピクセルブロックに分割（または群化）し、各ブロックは、画像面積のある領域内に複数のピクセルを含むことができる。セミグローバルシャッタは、同一のブロック内の全てのピクセルが同時に露出され、群として読み出されることを可能にすることができる。したがって、セミグローバルシャッタは、少なくとも各ピクセルブロック内でモーションアーチファクトのない画像を捕捉することが可能であり得る。ブロックは、ローリングベースで露出され、読み出されることができる。つまり、1つのピクセルのブロックからのデータが読み出され、処理されている間、次のピクセルのブロックが、露出されることが可能。これは、ブロックが重複または連続的様式で露出されることを可能にすることができる、これは、グローバルシャッタイメージヤが典型的に悩まされる連続的露出間の遅延を有意に低減または排除することができる。これは、速度の利点を提供することができる。

20

#### 【0031】

加えて、セミグローバルシャッタは、多くの場合、ローリングシャッタイメージヤを用いて取得される画像と関連付けられ得るモーションアーチファクトの量を低減させることができる。種々の実施形態では、これは、ピクセルを、カメラの要件および／または意図される使用によるピクセルブロックの最適な数に分割することによって達成されることがある。上記に議論されるように、ローリングシャッタは、典型的には、1つのピクセルまたは1つのピクセルの行／列を一度に露出し、読み出すようにプログラムされる。多数のピクセル（またはピクセルの行）を伴う画像センサに関して、ローリング露出によって引き起こされる各ピクセルまたはピクセルの行の露出時間における差異は、実質的であり、最終画像において容易に気付くモーションアーチファクトをもたらし得る。セミグローバルシャッタは、複数のピクセルの行／列のブロックを通して一度にロールすることができる。実施例として、各ブロックが10行を有する場合、潜在的モーションアーチファクトの量は、一度に1行ずつピクセルを通してロールするローリングシャッタと比較して、約10分の1に効果的に低減され得る。理想的には、ピクセルブロックは、セミグローバルシャッタイメージヤを伴う任意の特定のカメラに関するフレームレートと画像品質との間のバランスを達成するように定義されることがある。

30

#### 【0032】

図3は、セミグローバルシャッタを伴う画像センサ300の例示的構成要素を図示する、ブロック図である。センサ300の画像面積は、 $3 \times 3$ レイアウトにおける9つのピクセルブロックに分割されることができる。例えば、上部の行は、ピクセルブロック301、302、303を含むことができる。各ブロックは、複数のピクセルを含むことができる。ブロック303の拡大図が、ブロック303が $4 \times 4$ アレイのピクセルを含むことを示す。本実施形態では、各ブロックは、同一の構成で配列される同数のピクセルを含むことができる。しかしながら、本開示は、そのように限定されず、他の実施形態では、ブロッ

40

50

クは、異なる数および／または配列のピクセルを含むことができる。ブロック内の全てのピクセル 312 は、光を電子信号に変換する事が可能なセンサ要素（すなわち、フォトサイト）であり得る。

#### 【 0033 】

いくつかのブロック信号ライン（集合的に 304）が、タイミング信号をクロックおよびタイミング制御モジュール 308 から 9 つのピクセルブロックのそれぞれに伝送することができる。タイミング信号は、いつ各ピクセルブロックが光に露出されるか、また、いつピクセルブロックからの電子信号が読み出されるかを制御することができる。3 つのブロック信号ラインのみが図 3 に示されているが、全てのピクセルブロックが、クロックおよびタイミング制御モジュール 308 に別個に接続され得、独立してトリガされ得ることを理解されたい。いくつかの出力ライン 306 が、処理のために電子信号を各ピクセルブロック内のピクセルから読み出電子機器 316 に伝送することができる。3 つの垂直ラインのみが、明確化を目的として図 3 に出力ライン 306 としてマーキングされる。しかしながら、全てのピクセルブロックが、読み出電子機器 316 に別個に接続され得、各ピクセルブロックからの信号が、並行して読み出され得ることを理解されたい。本実施形態における読み出電子機器 316 は、9 つのピクセルブロックのそれぞれから受信された信号を並行して処理するように設計されることができる。図示されるように、読み出電子機器 316 は、それぞれが 9 つのピクセルブロックのうちの 1 つからの信号の処理に関与する、9 つの別個のサブモジュールを含むことができる。例えば、サブモジュール 321、322、323 は、それぞれ、ピクセルブロック 301、302、303 から信号を読み出すことができる。各サブモジュールは、例えば、それぞれ、信号を増幅し、デジタルフォーマット（例えば、デジタル数字）に変換するための増幅器および A/D コンバータを含むことができる。デジタル情報は、最終画像を組み立てるために処理されることができる。また、図 3 のセミグローバルシャッタイメージヤ 300 は、明確化を目的として図から省略される他の構成要素を含み得ることを理解されたい。図 3 に図式的に示される例示的配列は、任意の好適な数のピクセルブロックおよびその個別のサブモジュールに拡張され得る。

10

#### 【 0034 】

動作時、セミグローバルシャッタは、ピクセルブロックをローリングベースで露出するようにプログラムされることができる。例えば、同一のピクセルブロック内で、全てのピクセルは、同時に露出されることができ、ピクセルブロック内の各ピクセルからの信号は、一度に 1 つのピクセルずつ読み出され、出力ラインのうちの 1 つを経由して読み出電子機器 316 内の対応するサブモジュールに転送されることができる。各ピクセルブロックは、読み出が完了するまで再び露出され得ない。しかしながら、第 1 のピクセルブロック 301 が読み出されている間、第 2 のピクセルブロック 302 が、露出されることができる。同様に、第 2 のピクセルブロック 302 内のピクセルからの信号が読み出されている間、第 3 のピクセルブロック 303 が、露出されることができる。異なるブロックの露出および読み出における本重複は、典型的には、グローバルシャッタイメージヤにおける露出間で起こる遅延を最小限にする、または排除することができる。

20

#### 【 0035 】

図 4 は、図 3 のセミグローバルシャッタイメージヤ 300 におけるピクセルブロック 301、302、303 の 3 つの露出（上部）および読み出（底部）の例示的タイムラインを図示する。図示されるように、各ブロック 301、302、303 の露出および読み出は、連続的であり得るが、連続的ブロックのトリガは、重複することができる。各ピクセルブロックは、その前のもののわずかに後に露出され、露出遅延が、現在のピクセルブロックがその露出を完了する前に 1 つ以上の先に露出されたピクセルブロックの読み出を可能にすることができる。実施例として、シーケンス内のピクセルブロック 302 の露出は、前のピクセルブロック（例えば、ピクセルブロック 301）に関する読み出時間が完了し得る前にトリガされ得る。同様に、ブロックピクセル 303 の露出は、ブロック 302 に関する読み出時間が完了し得る前にトリガされ得る。これは、イメージヤからの出力デジタル転送帯域幅の使用を増加させることができる。全てのピクセルブロック（図 4 のタイムラインに

30

40

50

示されない 6 つを含む) が露出および読み出のサイクルを完了すると、第 1 のブロック(すなわち、ブロック 301) は、いずれの遅延も伴わずに再び露出されることができる。

#### 【0036】

代替として、ピクセルブロックは、連続的にトリガされることができ、各ブロックは、事前のピクセルブロックがその露出を完了した後のみその露出を開始することができる。例えば、これは、モーションからの不明瞭化効果が積分時間の同じサブウィンドウを含まない場合があるため、コンピュータビジョン用途に対して好適であり得る。重複または連続的トリガが実装されるかにかかわらず、ピクセルブロックは、その露出時間が完了した直後に読み出されることができる。

#### 【0037】

ピクセルブロックの露出とピクセルブロック内のピクセルによって捕捉される情報の分析との間の遅延があまり存在しないため、セミグローバルシャッタイメージジャによって生成される情報は、ピクセルからの情報が分析され得る前に画像全体が読み出されることを要求するであろう、同一ピクセル分解能のグローバルシャッタイメージジャよりも、カメラおよび / または捕捉されている風景の場所および / または移動を反映する際に正確であり得る。セミグローバルシャッタイメージジャにおける 1 つの潜在的遅延が、同一のブロック内の個々のピクセルからの信号が読み出されるときに起こり得る。しかしながら、本遅延は、匹敵するグローバルシャッタイメージジャにおける遅延よりも有意に短くあり得る。例えば、グローバルシャッタイメージジャ上の遅延が最後に読み出されるピクセルに関して 15 ミリ秒である場合、同一のピクセル(または各ブロック内の最後のピクセルのいずれか)に関するセミグローバルシャッタイメージジャ上の遅延は、セミグローバルシャッタイメージジャが同一サイズの 10 個のピクセルブロックに分割される場合、わずか 1.5 ミリ秒である。故に、セミグローバルシャッタイメージジャを用いて捕捉される画像は、画像内のキーポイントを追跡するために使用されるもの等の機械可読画像に関して優り得る。

10

#### 【0038】

セミグローバルシャッタおよびローリングシャッタの両方が、風景全体のスナップショットを取得するのではなく、風景を横断して走査することによって画像を取得し得るが、セミグローバルシャッタは、いくつかの用途に関して、カメラと風景との間に相対的移動が存在しないとき、ローリングシャッタよりも良好な画像品質を達成することができる。これは、セミグローバルシャッタイメージジャにおけるピクセルブロックの数が、ローリングシャッタイメージジャにおけるピクセルまたは行の数よりもはるかに少なくあり得るためである。ピクセルをより少ないピクセルブロックに分割することによって、最終画像におけるモーションアーチファクトは、限定されることができる。ピクセルブロックの連続的露出によって影響を受け得る画像内の唯一の領域は、ブロック間の境界である。対照的に、ローリングシャッタは一度に 1 行ずつピクセルを通してロールするため、モーションアーチファクトは、ローリングシャッタイメージジャを伴うカメラによって取得される画像上の任意の場所に出現し得る。しかしながら、これらの画像は、画像内のキーポイントを追跡するために使用されるもの等の機械可読画像に対して好適であり得る。

20

#### 【0039】

実施例として、セミグローバルシャッタイメージジャの  $9 \times 9$  ピクセルアレイは、それぞれが 3 つのピクセルの行を含む 3 つのピクセルブロックに分割され、3 つのピクセルブロック間に 2 つの境界をもたらすことができる。同一の  $9 \times 9$  ピクセルアレイがローリングシャッタを使用して行毎に読み出される場合、9 つの行間に 8 つの境界が存在する。それは、セミグローバルシャッタイメージジャを用いて取得されるものよりも、ローリングシャッタイメージジャを用いて取得される画像内のモーションアーチファクトによって影響を受け得る有意により多くの面積に対応する。加えて、セミグローバルシャッタにおけるより少ない境界はまた、シャッタがピクセルブロックを通してロールするとき、より少ないキーポイントが認識できない程度に歪曲されるであろうことを意味し得る。

30

#### 【0040】

セミグローバルシャッタは、画像アレイを任意の好適な数のピクセルブロックに分割する

40

50

ことができ、各ピクセルブロックは、任意の好適な数のピクセルを有することができる。種々の実施形態では、不等サイズ、非コンパクト、または非連続的構成のものを含む、任意の配列のピクセルブロックが、可能である。好ましくは、ピクセルブロックの数は、匹敵するグローバルシャッタイメージヤよりも短いピクセル露出と分析との間の遅延を達成すること、および匹敵するローリングシャッタイメージヤよりも結果画像においてある形態の歪みを起こしにくいことの両方のために設定されることができる。例えば、セミグローバルシャッタイメージヤの  $1000 \times 1000$  ピクセル画像面積を 10 個のブロック（例えば、それぞれ、 $100 \times 1000$  ブロック）に分割することを所望し得る。これは、同一の  $1000 \times 1000$  ピクセル画像面積を伴うグローバルシャッタイメージヤと比較して、少なくともピクセルのいくつかに関して、ピクセル露出と分析との間の遅延を 10 分の 1 に低減させることができる。加えて、ローリングシャッタ効果（例えば、モーションアーチファクト）は、ローリングシャッタイメージヤの場合であろうような画像面積全体を通してではなく、ピクセルブロック間の境界においてのみ問題となり得る。

#### 【0041】

ピクセル露出と分析との間の短い遅延を要求するカメラに関して、画像面積を、それぞれがより少ないピクセルを含む多数のピクセルブロックに分割させるセミグローバルシャッタイメージヤを有することが、理想的であろう。対照的に、より短い遅延周期にわたって画像品質に有利である（例えば、ある形態の歪みを最小限にする）カメラに関して、少数のピクセルブロックを伴うセミグローバルシャッタイメージヤが、より望ましくあり得る。

#### 【0042】

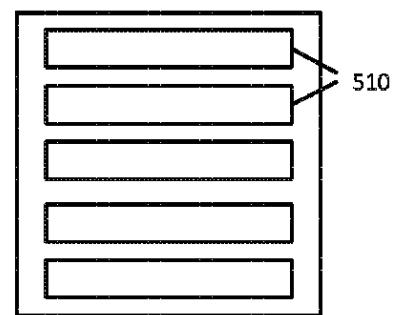

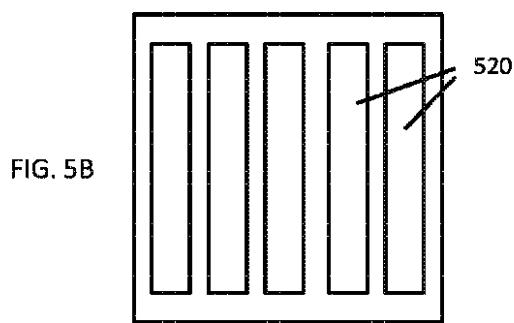

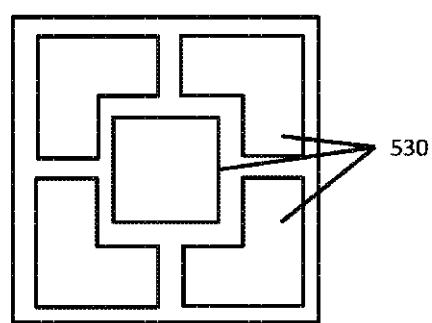

セミグローバルイメージヤは、任意の好適な幾何学的形状および配列のピクセルブロックを含み得る。図 3 は、例示的ブロックが同一サイズの正方形である一実施形態を図示するが、図 5 a - 5 c は、種々のセミグローバルシャッタイメージヤに対して好適なピクセルブロックの他の例示的分割を図示する。特に、図 5 a は、それぞれが同数のピクセルの行を含む、5 つの（または N 個の数の）長方形ピクセルブロック 510 に水平に分割される画像面積を図示する。図 5 b は、それぞれが同数のピクセルの列を有する、5 つの（または M 個の数の）ピクセルブロック 520 に垂直に分割される画像面積を図示する。図 5 c は、異なる形状および / またはサイズである 5 つのピクセルブロック 530 の構成を図示する。上記に議論されるように、ピクセルブロックの数および / または幾何学的形状は、ピクセルブロック間の面積が最小に保たれるように最適化されることができる。これは、ローリングシャッタイメージヤよりもセミグローバルシャッタイメージヤに対して有意な画像品質における利点を提供することができる。

#### 【0043】

一実施形態では、（例えば、図 3 に示されるように）比較的に高い分解能画像センサの画像面積を複数のピクセルブロックに分割する代わりに、セミグローバルシャッタは、複数の比較的に低い分解能イメージヤを同一の構成において組み立てることによって実装することができる（例えば、図 3 の各ブロックが、スタンドアロン低分解能イメージヤによって代用される）。これらの比較的に低い分解能イメージヤは、そのトリガを時間内ですらさせ、中央コントローラによって制御させることができる。各イメージヤは、ピクセルブロックあたりの伝送がイメージヤのサイズの逆関数であるようなピクセルクロックレートで個別に動作することができる。一実施形態では、低分解能イメージヤのためのウエハを切断するとき、個々のイメージヤのためのダイは、切断によって分離されない場合がある。

#### 【0044】

本開示の用途は、上記に言及される実施形態に限定されないことを理解されたい。当業者が、上記の説明に従って修正または置換を成すことが可能であり、それらの修正ならびに置換は全て、本開示の添付される請求項の範囲内に全て該当するものとする。

【図面】

【図 1】

【図 2 A】

【図 2 B】

【図 3】

10

20

30

40

50

【図 4】

【図 5 A】

10

【図 5 B】

【図 5 C】

20

30

40

50

---

フロントページの続き

(74)代理人 100181641

弁理士 石川 大輔

(74)代理人 230113332

弁護士 山本 健策

(72)発明者 ケーラー, エイドリアン

アメリカ合衆国 カリフォルニア 92103, サンディエゴ, ワシントン ストリート 302,

スイート ナンバー 150 - 7353

合議体

審判長 千葉 輝久

審判官 木方 庸輔

新井 寛