(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5436324号

(P5436324)

(45) 発行日 平成26年3月5日(2014.3.5)

(24) 登録日 平成25年12月20日(2013.12.20)

(51) Int.Cl.

F 1

|              |           |              |         |

|--------------|-----------|--------------|---------|

| G 11 C 19/28 | (2006.01) | G 11 C 19/28 | D       |

| G 11 C 19/00 | (2006.01) | G 11 C 19/00 | J       |

| G 09 G 3/20  | (2006.01) | G 09 G 3/20  | 6 2 1 F |

| G 09 G 3/36  | (2006.01) | G 09 G 3/20  | 6 2 2 E |

|              |           | G 09 G 3/20  | 6 2 1 D |

請求項の数 13 (全 24 頁) 最終頁に続く

(21) 出願番号

特願2010-107906 (P2010-107906)

(22) 出願日

平成22年5月10日(2010.5.10)

(65) 公開番号

特開2011-238312 (P2011-238312A)

(43) 公開日

平成23年11月24日(2011.11.24)

審査請求日

平成25年4月19日(2013.4.19)

(73) 特許権者 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

(74) 代理人 100088672

弁理士 吉竹 英俊

(74) 代理人 100088845

弁理士 有田 貴弘

(72) 発明者 飛田 洋一

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

審査官 後藤 彰

最終頁に続く

(54) 【発明の名称】シフトレジスタ回路

## (57) 【特許請求の範囲】

## 【請求項 1】

入力端子、第1および第2出力端子、第1および第2クロック端子と、

前記第1クロック端子に入力される第1クロック信号を前記第1出力端子に供給する第1トランジスタと、

前記第2クロック端子に入力される第2クロック信号を前記第2出力端子に供給する第2トランジスタと、

前記入力端子に入力される入力信号の活性化に応じて、前記第1トランジスタの制御電極が接続する第1ノードまたは前記第2トランジスタの制御電極が接続する第2ノードを充電する第3トランジスタと、

前記第1ノードと前記第2ノードとの間に接続された第4トランジスタと、

前記第1出力端子を放電する第5トランジスタと、

前記第2出力端子を放電する第6トランジスタと、

前記第1ノードを入力端、前記第5トランジスタの制御電極および前記第6トランジスタの制御電極が共に接続する第3ノードを出力端とするインバータとを備え、

前記第1クロック信号と前記第2クロック信号は同位相であり、且つ、特定の期間は前記第2クロック信号のみが活性化するように設定可能であることを特徴とするシフトレジスタ回路。

## 【請求項 2】

前記第4トランジスタの制御電極は、前記第2クロック信号の活性レベル以下の一定電

位の電源に接続されている

請求項 1 記載のシフトレジスタ回路。

**【請求項 3】**

入力端子、第 1 および第 2 出力端子、第 1 および第 2 クロック端子と、

前記第 1 クロック端子に入力される第 1 クロック信号を前記第 1 出力端子に供給する第 1 トランジスタと、

前記第 2 クロック端子に入力される第 2 クロック信号を前記第 2 出力端子に供給する第 2 トランジスタと、

前記入力端子に入力される入力信号の活性化に応じて、前記第 1 トランジスタの制御電極が接続する第 1 ノードまたは前記第 2 トランジスタの制御電極が接続する第 2 ノードを充電する第 3 トランジスタと、

前記第 1 ノードと前記第 2 ノードとの間に接続された第 4 トランジスタとを備え、

前記第 1 クロック信号と前記第 2 クロック信号は同位相であり、且つ、特定の期間は前記第 2 クロック信号のみが活性化するように設定可能であり、

前記第 4 トランジスタの制御電極は、前記入力端子に接続されていることを特徴とするシフトレジスタ回路。

**【請求項 4】**

前記第 2 出力端子が充電されるとき、前記第 4 トランジスタが前記第 1 ノードと前記第 2 ノードの間を電気的に分離する

請求項 1 から請求項 3 のいずれか記載のシフトレジスタ回路。

10

**【請求項 5】**

前記第 1 出力端子を放電する第 5 トランジスタと、

前記第 2 出力端子を放電する第 6 トランジスタとをさらに備え、

前記第 5 トランジスタの制御電極と前記第 6 トランジスタの制御電極とが互いに接続されている

請求項 3 記載のシフトレジスタ回路。

20

**【請求項 6】**

複数のシフトレジスタ回路が継続接続して成る多段のシフトレジスタ回路であって、

前記複数のシフトレジスタ回路のそれぞれは、

入力端子、第 1 および第 2 出力端子、並びに第 1 および第 2 クロック端子と、

30

前記第 1 クロック端子に入力される第 1 クロック信号を前記第 1 出力端子に供給する第 1 トランジスタと、

前記第 2 クロック端子に入力される第 2 クロック信号を前記第 2 出力端子に供給する第 2 トランジスタと、

前記入力端子に入力される入力信号の活性化に応じて、前記第 1 トランジスタの制御電極が接続する第 1 ノードを充電する第 3 トランジスタと、

前記入力信号の活性化に応じて、前記第 2 トランジスタの制御電極が接続する第 2 ノードを充電する第 4 トランジスタとを備え、

前記複数のシフトレジスタ回路のそれぞれにおいて、前記入力端子は自己の前段のシフトレジスタ回路の前記第 2 出力端子に接続されており、

40

前記第 1 クロック信号と前記第 2 クロック信号は同位相であり、且つ、前記複数のシフトレジスタ回路を信号が一巡する期間のうちの特定の期間は前記第 2 クロック信号のみが活性化するように設定可能である

ことを特徴とする多段のシフトレジスタ回路。

**【請求項 7】**

前記複数のシフトレジスタ回路のそれぞれは、

前記第 1 出力端子を放電する第 5 トランジスタと、

前記第 2 出力端子を放電する第 6 トランジスタとをさらに備え、

前記複数のシフトレジスタ回路のそれぞれにおいて、前記第 5 トランジスタの制御電極と前記第 6 トランジスタの制御電極とが互いに接続されている

50

請求項 6 記載の多段のシフトレジスタ回路。

【請求項 8】

第 1 および第 2 入力端子、第 1 および第 2 出力端子、並びに第 1 および第 2 クロック端子と、

互いに相補な第 1 および第 2 電圧信号がそれぞれ供給される第 1 および第 2 電圧信号端子と、

前記第 1 クロック端子に入力される第 1 クロック信号を前記第 1 出力端子に供給する第 1 トランジスタと、

前記第 2 クロック端子に入力される第 2 クロック信号を前記第 2 出力端子に供給する第 2 トランジスタと、

前記第 1 入力端子に入力される第 1 入力信号の活性化に応じて、前記第 1 トランジスタの制御電極が接続する第 1 ノードまたは前記第 2 トランジスタの制御電極が接続する第 2 ノードに、前記第 1 電圧信号を供給する第 3 トランジスタと、

前記第 2 入力端子に入力される第 2 入力信号の活性化に応じて、前記第 1 ノードまたは前記第 2 ノードに、前記第 2 電圧信号を供給する第 4 トランジスタと、

前記第 1 ノードと前記第 2 ノードとの間に接続された第 5 トランジスタとを備え、

前記第 1 クロック信号と前記第 2 クロック信号は同位相であり、且つ、特定の期間は前記第 2 クロック信号のみが活性化するように設定可能であることを特徴とするシフトレジスタ回路。

【請求項 9】

前記第 5 トランジスタの制御電極は、前記第 2 クロック信号の活性レベル以下の一定電位の電源に接続されている

請求項 8 記載のシフトレジスタ回路。

【請求項 10】

前記第 2 出力端子が充電されるとき、前記第 5 トランジスタが前記第 1 ノードと前記第 2 ノードの間を電気的に分離する

請求項 8 または請求項 9 記載のシフトレジスタ回路。

【請求項 11】

前記第 1 出力端子を放電する第 6 トランジスタと、

前記第 2 出力端子を放電する第 7 トランジスタとをさらに備え、

前記第 6 トランジスタの制御電極と前記第 7 トランジスタの制御電極とが互いに接続されている

請求項 8 から請求項 10 のいずれか記載のシフトレジスタ回路。

【請求項 12】

第 1 および第 2 入力端子、第 1 および第 2 出力端子、第 1 および第 2 クロック端子と、

互いに相補な第 1 および第 2 電圧信号がそれぞれ供給される第 1 および第 2 電圧信号端子と、

前記第 1 クロック端子に入力される第 1 クロック信号を前記第 1 出力端子に供給する第 1 トランジスタと、

前記第 2 クロック端子に入力される第 2 クロック信号を前記第 2 出力端子に供給する第 2 トランジスタと、

前記第 1 入力端子に入力される第 1 入力信号の活性化に応じて、前記第 1 トランジスタの制御電極が接続する第 1 ノードに前記第 1 電圧信号を供給する第 3 トランジスタと、

前記第 2 入力端子に入力される第 2 入力信号の活性化に応じて、前記第 1 ノードに前記第 2 電圧信号を供給する第 4 トランジスタと、

前記第 1 入力信号の活性化に応じて、前記第 2 トランジスタの制御電極が接続する第 2 ノードに前記第 1 電圧信号を供給する第 5 トランジスタと、

前記第 2 入力信号の活性化に応じて、前記第 2 ノードに前記第 2 電圧信号を供給する第 6 トランジスタとを備え、

前記第 1 クロック信号と前記第 2 クロック信号は同位相であり、且つ、特定の期間は前

10

20

30

40

50

記第2クロック信号のみが活性化するように設定可能であることを特徴とするシフトレジスタ回路。

**【請求項13】**

前記第1出力端子を放電する第7トランジスタと、

前記第2出力端子を放電する第8トランジスタとをさらに備え、

前記第7トランジスタの制御電極と前記第8トランジスタの制御電極とが互いに接続されている

請求項12記載のシフトレジスタ回路。

**【発明の詳細な説明】**

**【技術分野】**

10

**【0001】**

本発明は、走査線駆動回路に適用可能なシフトレジスタ回路に関するものであり、特に、部分表示機能を備える画像表示装置に使用され、同一導電型の電界効果トランジスタのみを用いて構成される走査線駆動回路に適用可能なシフトレジスタ回路に関するものである。

**【背景技術】**

**【0002】**

液晶表示装置等の画像表示装置（以下「表示装置」）では、複数の画素が行列状に配列された表示パネルの画素行（画素ライン）ごとにゲート線（走査線）が設けられ、表示信号の1水平期間の周期でそのゲート線を順次選択して駆動することにより表示画像の更新が行われる。そのように画素ラインすなわちゲート線を順次選択して駆動するためのゲート線駆動回路（走査線駆動回路）としては、表示信号の1フレーム期間で一巡するシフト動作を行うシフトレジスタを用いることができる。

20

**【0003】**

表示装置の分野においては、表示を画面の一部のみに限定する「部分表示」を行うことによって低消費電力化を図る技術が知られている。特に下記の特許文献1，2では、同一導電型の電界効果トランジスタのみで構成されるシフトレジスタが用いられている。表示装置に搭載するシフトレジスタを同一導電型のトランジスタのみで構成すると、表示装置の製造プロセスにおける工程数を少なくして製造コストの低減を図ることができる。

30

**【先行技術文献】**

**【特許文献】**

**【0004】**

**【特許文献1】**特開2008-140490号公報

**【特許文献2】**特開2008-58939号公報

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0005】**

ゲート線駆動回路としてのシフトレジスタは、1つの画素ラインすなわち1つのゲート線ごとに設けられた複数のシフトレジスタ回路が縦続接続（カスケード接続）して構成される。本明細書では説明の便宜上、ゲート線駆動回路を構成する複数のシフトレジスタ回路の各々を「単位シフトレジスタ」と称する。即ち、ゲート線駆動回路を構成する個々の単位シフトレジスタの出力信号は、ゲート線に供給されると共に、次段あるいは後段の単位シフトレジスタにも入力される。

40

**【0006】**

例えば特許文献1には、部分表示に対応可能な走査線駆動回路が開示されており、同文献の図3には、それを構成する単位シフトレジスタ（Ua）の回路構成が示されている。当該単位シフトレジスタ（Ua）は、走査線を駆動する走査信号（Y）と、次段の単位シフトレジスタに送られる転送信号（G）とを出力する。当該単位シフトレジスタ（Ua）において、転送信号（G）を生成する転送信号生成部（110A）は常に動作するが、転送信号（G）を生成する走査信号生成部（120A）は部分表示において表示が必要な

50

画素ラインの選択期間（表示有効期間）にのみ動作するように制御される。

**【0007】**

走査信号生成部（120A）は第1クロック端子（P）と走査信号出力端子（y）との間に接続した第1トランジスタ（121）を備える。転送信号生成部（110A）は、第2クロック端子（A）と転送信号出力端子（g）との間に接続した第2トランジスタ（111）を備える。第1および第2トランジスタ（121, 111）は、ゲートが互いに接続されており、共に同じタイミングでオン、オフが切り替わる。

**【0008】**

ここで、各単位シフトレジスタ（Ua）の第2クロック端子（A）に入力される第2クロック信号（YCK1 / YCK2）は常に一定周期で活性化するが、第1クロック端子（P）に入力される第1クロック信号（P1 / P2）は、表示有効期間にのみ一定周期で活性化され、その他の期間（表示無効期間）には非活性レベルに維持される。これにより、走査信号（Y）は表示有効期間のみに活性化される。その結果、一部の画素ラインのみが駆動されることになり、画面の部分的な表示（部分表示）が達成される。10

**【0009】**

ところで、特許文献1の図3の単位シフトレジスタ（Ua）においては、第2トランジスタ（111）のソース（転送信号出力端子（g））とゲートとの間には容量素子（113）が接続されている。この容量素子（113）は、転送信号（G）が活性化するときに第2トランジスタ（111）のゲートを昇圧し、第2トランジスタ（111）の駆動能力（電流を流す能力）を高める働きをする。第2トランジスタ（111）のゲートが充分に昇圧されれば、第2トランジスタ（111）は非飽和領域で動作し、転送信号（G）の活性レベルの電位はより高くなる。20

**【0010】**

上記したように、第1および第2トランジスタ（121, 111）はゲートが互いに接続されているので、第2トランジスタ（111）のゲートが昇圧されれば、第1トランジスタ（121）も同様に駆動能力が高くなる。ここでは、第1および第2トランジスタ（121, 111）のゲートが接続するノード（）を「ゲートノード」と称する。

**【0011】**

第1および第2トランジスタ（121, 111）は、それぞれゲート容量（ゲート・ソース間容量、ゲート・ドレイン間容量およびゲート・チャネル容量）を有する。表示有効期間においては、第1および第2トランジスタ（121, 111）がオンしたとき、第1クロック信号（P1 / P2）および第2クロック信号（YCK1 / YCK2）の活性化に応じて、転送信号出力端子（g）と走査信号出力端子（y）の両方が充電されるため、第1および第2トランジスタ（121, 111）のゲート容量は、どちらも上記の容量素子（113）と共にゲートノード（）を昇圧するように機能する。30

**【0012】**

しかし表示無効期間では、第2クロック信号（YCK1 / YCK2）は活性化されるが第1クロック信号（P1 / P2）が活性化されないので、第1および第2トランジスタ（121, 111）がオンしても、転送信号出力端子（g）が充電されるのみで走査信号出力端子（y）は充電されない。この場合、第2トランジスタ（111）のゲート容量はゲートノード（）を昇圧するように機能するが、第1トランジスタ（121）のゲート容量はそれを妨げるよう働く。これが原因でゲートノード（）の昇圧が不充分になると、表示無効期間における単位シフトレジスタ（Ua）の第2トランジスタ（111）の駆動能力が低下する。このことは単位シフトレジスタ（Ua）の高速動作化の妨げとなり、走査線駆動回路の動作マージンを低下させる原因となる。40

**【0013】**

第1トランジスタ（121）は、大きな負荷容量を持つゲート線を駆動するために高い駆動能力が必要とされ、ゲート幅が広く設定される。このため第1トランジスタ（121）のゲート容量は大きな値となり（ゲート容量はゲート幅とゲート長の積に比例する）、この問題が生じ易い。50

## 【0014】

本発明は以上のような課題を解決するためになされたものであり、部分表示機能を備える走査線駆動回路に適用できる単位シフトレジスタの駆動能力の向上および動作の高速化を図ることを目的とする。

## 【課題を解決するための手段】

## 【0015】

本発明の第1の局面に係るシフトレジスタ回路は、入力端子、第1および第2出力端子、第1および第2クロック端子と、前記第1クロック端子に入力される第1クロック信号を前記第1出力端子に供給する第1トランジスタと、前記第2クロック端子に入力される第2クロック信号を前記第2出力端子に供給する第2トランジスタと、前記入力端子に入力される入力信号の活性化に応じて、前記第1トランジスタの制御電極が接続する第1ノードまたは前記第2トランジスタの制御電極が接続する第2ノードを充電する第3トランジスタと、前記第1ノードと前記第2ノードとの間に接続された第4トランジスタと、前記第1出力端子を放電する第5トランジスタと、前記第2出力端子を放電する第6トランジスタと、前記第1ノードを入力端、前記第5トランジスタの制御電極および前記第6トランジスタの制御電極が共に接続する第3ノードを出力端とするインバータとを備え、前記第1クロック信号と前記第2クロック信号は同位相であり、且つ、特定の期間は前記第2クロック信号のみが活性化するように設定可能であるものである。10

## 【0016】

本発明の第2の局面に係る多段のシフトレジスタ回路は、複数のシフトレジスタ回路が継続接続して成る多段のシフトレジスタ回路であって、前記複数のシフトレジスタ回路のそれぞれは、入力端子、第1および第2出力端子、並びに第1および第2クロック端子と、前記第1クロック端子に入力される第1クロック信号を前記第1出力端子に供給する第1トランジスタと、前記第2クロック端子に入力される第2クロック信号を前記第2出力端子に供給する第2トランジスタと、前記入力端子に入力される入力信号の活性化に応じて、前記第1トランジスタの制御電極が接続する第1ノードを充電する第3トランジスタと、前記入力信号の活性化に応じて、前記第2トランジスタの制御電極が接続する第2ノードを充電する第4トランジスタとを備え、前記複数のシフトレジスタ回路のそれれにおいて、前記入力端子は自己の前段のシフトレジスタ回路の前記第2出力端子に接続されており、前記第1クロック信号と前記第2クロック信号は同位相であり、且つ、前記複数のシフトレジスタ回路を信号が一巡する期間のうちの特定の期間は前記第2クロック信号のみが活性化するように設定可能であるものである。20

## 【0017】

本発明の第3の局面に係るシフトレジスタ回路は、第1および第2入力端子、第1および第2出力端子、並びに第1および第2クロック端子と、互いに相補な第1および第2電圧信号がそれぞれ供給される第1および第2電圧信号端子と、前記第1クロック端子に入力される第1クロック信号を前記第1出力端子に供給する第1トランジスタと、前記第2クロック端子に入力される第2クロック信号を前記第2出力端子に供給する第2トランジスタと、前記第1入力端子に入力される第1入力信号の活性化に応じて、前記第1トランジスタの制御電極が接続する第1ノードまたは前記第2トランジスタの制御電極が接続する第2ノードに、前記第1電圧信号を供給する第3トランジスタと、前記第2入力端子に入力される第2入力信号の活性化に応じて、前記第1ノードまたは前記第2ノードに、前記第2電圧信号を供給する第4トランジスタと、前記第1ノードと前記第2ノードとの間に接続された第5トランジスタとを備え、前記第1クロック信号と前記第2クロック信号は同位相であり、且つ、特定の期間は前記第2クロック信号のみが活性化するように設定可能であるものである。40

## 【0018】

本発明の第4の局面に係るシフトレジスタ回路は、第1および第2入力端子、第1および第2出力端子、第1および第2クロック端子と、互いに相補な第1および第2電圧信号がそれぞれ供給される第1および第2電圧信号端子と、前記第1クロック端子に入力され50

る第1クロック信号を前記第1出力端子に供給する第1トランジスタと、前記第2クロック端子に入力される第2クロック信号を前記第2出力端子に供給する第2トランジスタと、前記第1入力端子に入力される第1入力信号の活性化に応じて、前記第1トランジスタの制御電極が接続する第1ノードに前記第1電圧信号を供給する第3トランジスタと、前記第2入力端子に入力される第2入力信号の活性化に応じて、前記第1ノードに前記第2電圧信号を供給する第4トランジスタと、前記第1入力信号の活性化に応じて、前記第2トランジスタの制御電極が接続する第2ノードに前記第1電圧信号を供給する第5トランジスタと、前記第2入力信号の活性化に応じて、前記第2ノードに前記第2電圧信号を供給する第6トランジスタとを備え、前記第1クロック信号と前記第2クロック信号は同位相であり、且つ、特定の期間は前記第2クロック信号のみが活性化するように設定可能であるものである。 10

#### 【発明の効果】

##### 【0019】

本発明に係るシフトレジスタ回路によれば、第2出力信号（シフト信号）を活性化する際、第2出力端子を充電する第2トランジスタの制御電極と、第1出力信号（ゲート線駆動信号）の第1出力端子を充電する第2トランジスタの制御電極との間が電気的に分離される。よって第1出力信号を活性化させる期間（表示有効期間）であるか否かに関わらず、第2トランジスタの駆動能力を高く維持できる。

#### 【図面の簡単な説明】

##### 【0020】

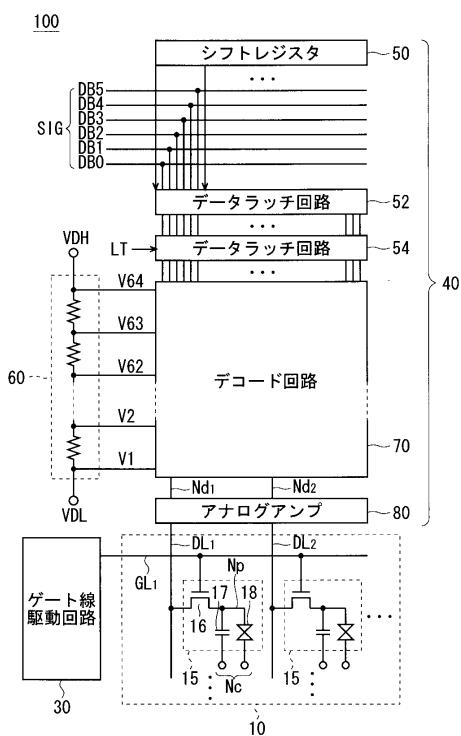

【図1】液晶表示装置の構成を示す概略ブロック図である。

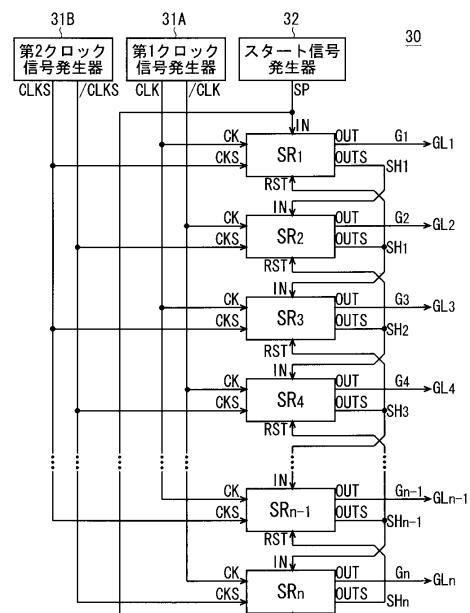

【図2】本発明の実施の形態に係るゲート線駆動回路の構成の構成を示す図である。

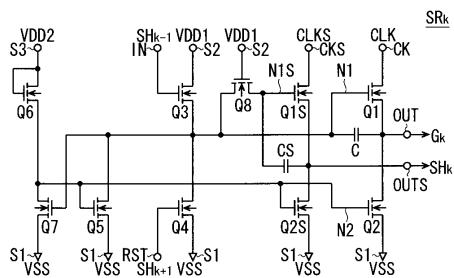

【図3】実施の形態に係る単位シフトレジスタの回路図である。

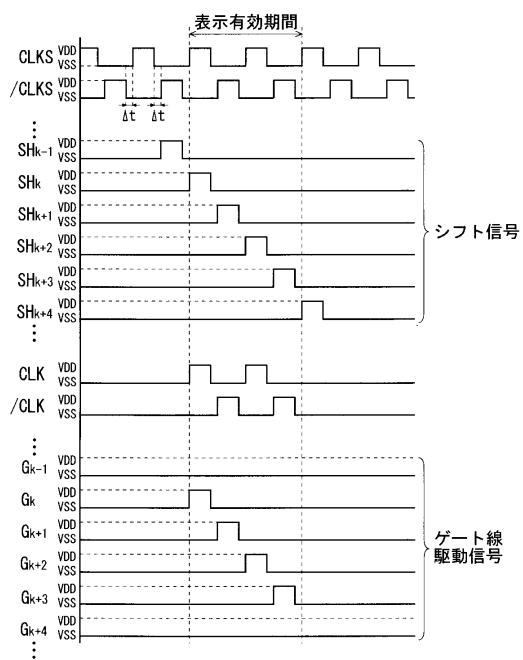

【図4】実施の形態に係るゲート線駆動回路の動作を示すタイミング図である。

【図5】実施の形態の第1の変更例に係る単位シフトレジスタの回路図である。

【図6】実施の形態の第2の変更例に係る単位シフトレジスタの回路図である。

【図7】実施の形態の第3の変更例に係る単位シフトレジスタの回路図である。

【図8】実施の形態の第4の変更例に係る単位シフトレジスタの回路図である。

【図9】実施の形態の第5の変更例に係る単位シフトレジスタの回路図である。

【図10】実施の形態の第6の変更例に係る単位シフトレジスタの回路図である。 30

#### 【発明を実施するための形態】

##### 【0021】

以下、本発明の実施の形態を、図面を参照しながら説明する。なお、説明が重複して冗長になるのを避けるため、各図において同一または相当する機能を有する要素には同一符号を付してある。

##### 【0022】

また、各実施の形態に用いられるトランジスタは、絶縁ゲート型電界効果トランジスタである。絶縁ゲート型電界効果トランジスタは、ゲート絶縁膜中の電界により半導体層内のドレイン領域とソース領域との間の電気伝導度が制御される。ドレイン領域およびソース領域が形成される半導体層の材料としては、ポリシリコン、アモルファスシリコン、ペンタセン等の有機半導体、単結晶シリコンあるいはIGZO (In-Ga-Zn-O) 等の酸化物半導体などを用いることができる。 40

##### 【0023】

よく知られているように、トランジスタは、それぞれ制御電極（狭義にはゲート（電極））と、一方の電流電極（狭義にはドレイン（電極）またはソース（電極））と、他方の電流電極（狭義にはソース（電極）またはドレイン（電極））とを含む少なくとも3つの電極を有する素子である。トランジスタはゲートに所定の電圧を印加することによりドレインとソース間にチャネルが形成されるスイッチング素子として機能する。トランジスタのドレインとソースは、基本的に同一の構造であり、印加される電圧条件によって互いにその呼称が入れ代わる。例えば、N型トランジスタであれば、相対的に電位（以下「レベ 50

ル」とも称する)の高い電極をドレイン、低い電極をソースと呼称する( P 型トランジスタの場合はその逆となる)。

#### 【 0 0 2 4 】

特に示さない限り、それらのトランジスタは半導体基板上に形成されるものであってもよく、またガラスなどの絶縁性基板上に形成される薄膜トランジスタ(TFT)であってもよい。トランジスタが形成される基板としては、単結晶基板あるいはSOI、ガラス、樹脂などの絶縁性基板であってもよい。

#### 【 0 0 2 5 】

本発明のゲート線駆動回路は、单一導電型のトランジスタのみを用いて構成される。例えばN型トランジスタは、ゲート・ソース間電圧が当該トランジスタのしきい値電圧よりも高いH(ハイ)レベルになると活性状態(オン状態、導通状態)となり、同しきい値電圧よりも低いL(ロー)レベルで非活性状態(オフ状態、非導通状態)となる。そのためN型トランジスタを用いた回路においては信号のHレベルが「活性レベル」、Lレベルが「非活性レベル」となる。また、N型トランジスタを用いて構成した回路の各ノードは、充電されてHレベルになることで、非活性レベルから活性レベルへの変化が生じ、放電されてLレベルになることで、活性レベルから非活性レベルへの変化が生じる。

#### 【 0 0 2 6 】

逆にP型トランジスタは、ゲート・ソース間電圧がトランジスタのしきい値電圧(ソースを基準として負の値)よりも低いLレベルになると活性状態(オン状態、導通状態)となり、同しきい値電圧よりも高いHレベルで非活性状態(オフ状態、非導通状態)となる。そのためP型トランジスタを用いた回路においては信号のLレベルが「活性レベル」、Hレベルが「非活性レベル」となる。また、P型トランジスタを用いて構成した回路の各ノードは、充電・放電の関係がN型トランジスタの場合と逆になり、充電されてLレベルになることで、非活性レベルから活性レベルへの変化が生じ、放電されてHレベルになることで、活性レベルから非活性レベルへの変化が生じる。

#### 【 0 0 2 7 】

本明細書では、非活性レベルから活性レベルへの変化を「プルアップ」、活性レベルから非活性レベルへの変化「プルダウン」と定義する。つまり、N型トランジスタを用いた回路では、LレベルからHレベルへの変化が「プルアップ」、HレベルからLレベルの変化が「プルダウン」と定義され、P型トランジスタを用いた回路では、HレベルからLレベルへの変化が「プルアップ」、LレベルからHレベルの変化が「プルダウン」と定義される。

#### 【 0 0 2 8 】

また本明細書においては、二つの素子間、二つのノード間あるいは一の素子とのノードとの間の「接続」とはその他の要素(素子やスイッチなど)を介しての接続であるが実質的に直接接続されているのと等価な状態を含むものとして説明する。例えば二つの素子がスイッチを介して接続している場合であっても、それらが直接接続されているときと同一に機能できるような場合には、その二つの素子が「接続している」と表現する。

#### 【 0 0 2 9 】

本発明においては、各々位相の異なるクロック信号(多相クロック信号)が用いられる。以下では説明の簡単のため、一のクロック信号の活性期間とその次に活性化するクロック信号の活性期間との間に一定の間隔を設けている(図4に示すt)。しかし本発明では各クロック信号の活性期間が実質的に重ならなければよく、上記の間隔は無くてもよい。例えば活性レベルをHレベルとすると、一のクロック信号の立ち下がり(HレベルからLレベルへの変化)タイミングとその次に活性化するクロック信号の立ち上がり(LレベルからHレベルへの変化)タイミングとが同時であってもよい。

#### 【 0 0 3 0 】

##### < 実施の形態 >

図1は、本発明に係る表示装置の構成を示す概略ブロック図であり、表示装置の代表例として液晶表示装置の全体構成を示している。なお、本発明は、液晶表示装置への適用に

10

20

30

40

50

限定されるものではなく、電気信号を光の輝度に変換する表示装置であるエレクトロルミネッセンス(EL)、有機EL、プラズマディスプレイ、電子ペーパ等の電気光学装置に広く適用可能である。

#### 【0031】

液晶表示装置100は、液晶アレイ部10と、ゲート線駆動回路(走査線駆動回路)30と、ソースドライバ40とを備える。後の説明により明らかになるが、本実施の形態に係るシフトレジスタは、ゲート線駆動回路30に搭載される。

#### 【0032】

液晶アレイ部10は、行列状に配設された複数の画素15を含む。画素の行(以下「画素ライン」とも称する)の各々にはそれぞれゲート線 $GL_1, GL_2\dots$ (総称「ゲート線 $GL$ 」)が配設され、また、画素の列(以下「画素列」とも称する)の各々にはそれぞれデータ線 $DL_1, DL_2\dots$ (総称「データ線 $DL$ 」)がそれぞれ設けられる。図1には、第1行の第1列および第2列の画素15、並びにこれに対応するゲート線 $GL_1$ およびデータ線 $DL_1, DL_2$ が代表的に示されている。10

#### 【0033】

各画素15は、対応するデータ線 $DL$ と画素ノード $N_p$ との間に設けられる画素スイッチ素子16と、画素ノード $N_p$ および共通電極ノード $N_c$ との間に並列に接続されるキャパシタ17および液晶表示素子18とを有している。画素ノード $N_p$ と共に電極ノード $N_c$ との間の電圧差に応じて、液晶表示素子18中の液晶の配向性が変化し、これに応答して液晶表示素子18の表示輝度が変化する。これにより、データ線 $DL$ および画素スイッチ素子16を介して画素ノード $N_p$ へ伝達される表示電圧によって、各画素の輝度をコントロールすることが可能となる。即ち、最大輝度に対応する電圧差と最小輝度に対応する電圧差との間の中間的な電圧差を、画素ノード $N_p$ と共に電極ノード $N_c$ との間に印加することによって、中間的な輝度を得ることができる。従って、上記表示電圧を段階的に設定することにより、階調的な輝度を得ることが可能となる。20

#### 【0034】

ゲート線駆動回路30は、所定の走査周期に基づき、ゲート線 $GL$ を順に選択して活性化させる。画素スイッチ素子16のゲート電極は、それぞれ対応するゲート線 $GL$ と接続される。特定のゲート線 $GL$ が選択されている間は、それに接続する各画素において、画素スイッチ素子16が導通状態になり画素ノード $N_p$ が対応するデータ線 $DL$ と接続される。そして、画素ノード $N_p$ へ伝達された表示電圧がキャパシタ17によって保持される。一般的に、画素スイッチ素子16は、液晶表示素子18と同一の絶縁体基板(ガラス基板、樹脂基板等)上に形成されるTFTで構成される。30

#### 【0035】

ソースドライバ40は、Nビットのデジタル信号である表示信号SIGによって段階的に設定される表示電圧を、データ線 $DL$ へ出力するためのものである。ここでは一例として、表示信号SIGは6ビットの信号であり、表示信号ビットDB0～DB5から構成されるものとする。6ビットの表示信号SIGに基づくと、各画素において、 $2^6 = 64$ 段階の階調表示が可能となる。さらに、R(Red)、G(Green)およびB(Blue)の3つの画素により1つのカラー表示単位を形成すれば、約26万色のカラー表示が可能となる。40

#### 【0036】

また、図1に示すように、ソースドライバ40は、シフトレジスタ50と、データラッシュ回路52, 54と、階調電圧生成回路60と、デコード回路70と、アナログアンプ80とから構成されている。

#### 【0037】

表示信号SIGにおいては、各々の画素15の表示輝度に対応する表示信号ビットDB0～DB5がシリアルに生成される。すなわち、各タイミングにおける表示信号ビットDB0～DB5は、液晶アレイ部10中のいずれか1つの画素15における表示輝度を示している。

#### 【0038】

10

20

30

40

50

シフトレジスタ 50 は、表示信号 S I G の設定が切り換わる周期に同期したタイミングで、データラッチ回路 52 に対して、表示信号ビット D B 0 ~ D B 5 の取り込みを指示する。データラッチ回路 52 は、シリアルに生成される表示信号 S I G を順に取り込み、1 つの画素ライン分の表示信号 S I G を保持する。

#### 【 0 0 3 9 】

データラッチ回路 54 に入力されるラッチ信号 L T は、データラッチ回路 52 に1つの画素ライン分の表示信号 S I G が取り込まれるタイミングで活性化する。データラッチ回路 54 はそれに応答して、そのときデータラッチ回路 52 に保持されている1つの画素ライン分の表示信号 S I G を取り込む。

#### 【 0 0 4 0 】

階調電圧生成回路 60 は、高電圧 V D H および低電圧 V D L の間に直列に接続された63 個の分圧抵抗で構成され、64 段階の階調電圧 V 1 ~ V 64 をそれぞれ生成する。

#### 【 0 0 4 1 】

デコード回路 70 は、データラッチ回路 54 に保持されている表示信号 S I G をデコードし、当該デコード結果に基づいて各デコード出力ノード N d<sub>1</sub>, N d<sub>2</sub>... ( 総称「デコード出力ノード N d 」) に出力する電圧を、階調電圧 V 1 ~ V 64 のうちから選択して出力する。

#### 【 0 0 4 2 】

その結果、デコード出力ノード N d には、データラッチ回路 54 に保持された1つの画素ライン分の表示信号 S I G に対応した表示電圧 ( 階調電圧 V 1 ~ V 64 のうちの1つ ) が同時に ( パラレルに ) 出力される。なお、図1においては、第1列目および第2列目のデータ線 D L<sub>1</sub>, D L<sub>2</sub> に対応するデコード出力ノード N d<sub>1</sub>, N d<sub>2</sub> が代表的に示されている。

#### 【 0 0 4 3 】

アナログアンプ 80 は、デコード回路 70 からデコード出力ノード N d<sub>1</sub>, N d<sub>2</sub>... に出力された各表示電圧に対応したアナログ電圧を電流増幅して、それぞれデータ線 D L<sub>1</sub>, D L<sub>2</sub>... に出力する。

#### 【 0 0 4 4 】

ソースドライバ 40 が、所定の走査周期に基づいて、一連の表示信号 S I G に対応する表示電圧を1画素ライン分ずつデータ線 D L へ繰り返し出力し、ゲート線駆動回路 30 がその走査周期に同期してゲート線 G L<sub>1</sub>, G L<sub>2</sub>... を順に駆動することにより、液晶アレイ部 10 に表示信号 S I G に基づいた画像の表示が成される。

#### 【 0 0 4 5 】

なお、図1には、ゲート線駆動回路 30 およびソースドライバ 40 が液晶アレイ部 10 と一体的に形成された液晶表示装置 100 の構成を例示したが、ゲート線駆動回路 30 と液晶アレイ部 10 とを一体的に形成し、ソースドライバ 40 については液晶アレイ部 10 の外部回路として設ける、あるいはゲート線駆動回路 30 およびソースドライバ 40 については、液晶アレイ部 10 の外部回路として設けることも可能である。

#### 【 0 0 4 6 】

図2は、ゲート線駆動回路 30 の構成を示す図である。このゲート線駆動回路 30 は、縦続接続 ( カスケード接続 ) した複数の単位シフトレジスタ S R<sub>1</sub>, S R<sub>2</sub>, S R<sub>3</sub>, S R<sub>4</sub> ... S R<sub>n</sub> で構成されるシフトレジスタから成っている ( 説明の便宜上、縦続接続する単位シフトレジスタ S R<sub>1</sub>, S R<sub>2</sub>... を「単位シフトレジスタ S R 」と総称する )。各単位シフトレジスタ S R は、1つの画素ラインすなわち1つのゲート線 G L ごとに設けられる。

#### 【 0 0 4 7 】

各単位シフトレジスタ S R は、入力端子 I N 、第1出力端子 O U T 、第2出力端子 O U T S 、リセット端子 R S T 、第1クロック端子 C K 、第2クロック端子 C K S を有している。第1出力端子 O U T は、対応するゲート線 G L に接続される。

#### 【 0 0 4 8 】

各単位シフトレジスタ S R の第1出力端子 O U T は、対応するゲート線 G L を駆動する

10

20

30

40

50

ためのゲート線駆動信号 G (第 1 出力信号) を出力するものである。ゲート線駆動信号 G はいわゆる垂直 (又は水平) 走査パルスとして機能する。

#### 【 0 0 4 9 】

各単位シフトレジスタ S R の第 2 出力端子 O U T S は、ゲート線駆動回路 3 0 における信号のシフト動作を規定するシフト信号 S H (第 2 出力信号) を出力するものである。各単位シフトレジスタ S R の入力端子 I N には、前段の単位シフトレジスタ S R が出力したシフト信号 S H が入力信号として供給される。但し、第 1 段目 (第 1 ステージ) の単位シフトレジスタ S R<sub>1</sub> の入力端子 I N には、画像信号の各フレーム期間の先頭に対応するスタートパルス S P が入力信号として供給される。

#### 【 0 0 5 0 】

また各単位シフトレジスタ S R のシフト信号 S H は、その前段の単位シフトレジスタ S R のリセット端子 R S T にも供給される。つまり各単位シフトレジスタ S R のリセット端子 R S T には、次段の単位シフトレジスタ S R が出力したシフト信号 S H がリセット信号として供給される。但し、最後段 (第 n ステージ) の単位シフトレジスタ S R<sub>n</sub> のリセット端子 R S T には上記のスタートパルス S P がリセット信号として供給される。

#### 【 0 0 5 1 】

各単位シフトレジスタ S R の第 1 クロック端子 C K には、第 1 クロック信号発生器 3 1 A が生成するクロック信号 C L K , / C L K のいずれかが供給される。図 2 の例では、奇数段の単位シフトレジスタ S R<sub>1</sub> , S R<sub>3</sub> , S R<sub>5</sub> … の第 1 クロック端子 C K にはクロック信号 C L K が供給され、偶数段の単位シフトレジスタ S R<sub>2</sub> , S R<sub>4</sub> , S R<sub>6</sub> … の第 1 クロック端子 C K には、クロック信号 / C L K が供給される。

#### 【 0 0 5 2 】

各単位シフトレジスタ S R の第 2 クロック端子 C K S には、第 2 クロック信号発生器 3 1 B が生成するクロック信号 C L K S , / C L K S のいずれかが供給される。図 2 の例では、奇数段の単位シフトレジスタ S R<sub>1</sub> , S R<sub>3</sub> , S R<sub>5</sub> … の第 2 クロック端子 C K S にはクロック信号 C L K S が供給され、偶数段の単位シフトレジスタ S R<sub>2</sub> , S R<sub>4</sub> , S R<sub>6</sub> … の第 2 クロック端子 C K S には、クロック信号 / C L K S が供給される。

#### 【 0 0 5 3 】

以下、説明の便宜のため、第 1 クロック信号発生器 3 1 A が生成するクロック信号 C L K , / C L K の各々を「第 1 クロック信号」、第 2 クロック信号発生器 3 1 B が生成する第 2 クロック信号 C L K S , / C L K S の各々を「第 2 クロック信号」と称する。

#### 【 0 0 5 4 】

第 1 クロック信号 C L K , / C L K は、互いに位相の異なる (活性期間が重ならない) 2 相のクロック信号である。第 1 クロック信号 C L K , / C L K は互いに逆相であり、表示装置の走査周期に同期したタイミングで交互に活性化するよう制御されている。

#### 【 0 0 5 5 】

第 2 クロック信号 C L K S , / C L K S もまた、互いに位相の異なる (活性期間が重ならない) 2 相のクロック信号であり、第 1 クロック信号 C L K , / C L K と同様に、表示装置の走査周期に同期したタイミングで交互に活性化するよう制御されている。第 1 クロック信号 C L K と第 2 クロック信号 C L K S は同位相であり、第 1 クロック信号 / C L K と第 2 クロック信号 / C L K S は同位相である。

#### 【 0 0 5 6 】

本実施の形態に係る各単位シフトレジスタ S R においては、第 1 クロック信号 C L K , / C L K は、ゲート線駆動信号 G を活性化させるための信号として用いられ、第 2 クロック信号 C L K S , / C L K S は、シフト信号 S H を活性化させるための信号として用いられる。

#### 【 0 0 5 7 】

第 2 クロック信号 C L K S , / C L K S は、各フレームにおいて常に一定周期 (2 水平走査期間に相当) で活性化されるが、第 1 クロック信号 C L K , / C L K は、表示が必要な画素ラインの選択期間 (表示有効期間) にのみ活性化される。つまり、部分表示が実行

10

20

30

40

50

されるとき、第1クロック信号 C L K , / C L K は、表示有効期間にのみ活性化され、その他の期間（表示無効期間）は非活性レベルに維持される。よって第1クロック信号 C L K , / C L K は、第2クロック信号 C L K S , / C L K S の波形の一部を取り出した波形の信号となる。なお、通常の全画面表示の場合には、第1クロック信号 C L K , / C L K も第2クロック信号 C L K S , / C L K S と同様に、常に一定周期で活性化される。

#### 【0058】

詳細は後述するが、ゲート線駆動回路 30 の単位シフトレジスタ S R の各々は、第2クロック信号 C L K S , / C L K S に同期して、入力端子 I N に入力される信号（スタートパルス S P あるいは前段のシフト信号 S H ）を時間的にシフトさせながら、次段の単位シフトレジスタ S R へと伝達するように動作する。その結果、各単位シフトレジスタ S R のシフト信号 S H は、S H<sub>1</sub>、S H<sub>2</sub>、S H<sub>3</sub>…と順番に活性化される。10

#### 【0059】

また各単位シフトレジスタ S R は、シフト信号 S H を活性化させる際、第1クロック信号 C L K , / C L K の活性化に応じてゲート線駆動信号 G も活性化させる。第1クロック信号 C L K と第2クロック信号 C L K S は同位相であり、また第1クロック信号 / C L K と第2クロック信号 / C L K S も同位相なので、ゲート線駆動信号 G<sub>1</sub> , G<sub>2</sub> , G<sub>3</sub>…は、それぞれシフト信号 S H<sub>1</sub> , S H<sub>2</sub> , S H<sub>3</sub>…と同じタイミングで活性化される。その結果、ゲート線 G L<sub>1</sub> , G L<sub>2</sub> , G L<sub>3</sub>…が順番に活性化される。但し、第1クロック信号 C L K , / C L K は表示有効期間にのみ活性化するので、部分表示が実行される場合、表示有効期間に対応するゲート線 G L のみが活性化されることになる。20

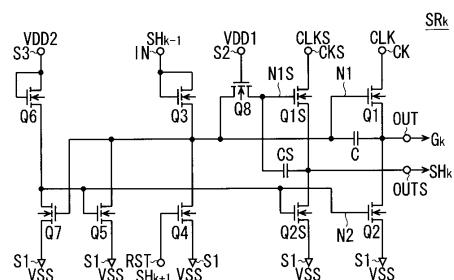

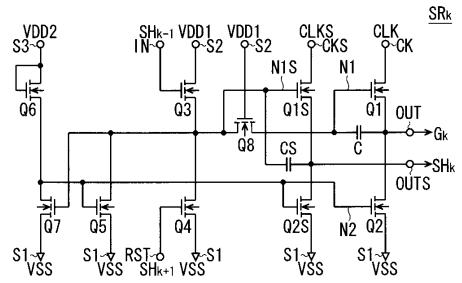

#### 【0060】

図 3 は、本発明の単位シフトレジスタ S R の構成を示す回路図である。ゲート線駆動回路 30 において、縦続接続した複数の単位シフトレジスタ S R の構成は実質的にどれも同じであるので、代表的に第 k 段目の単位シフトレジスタ S R<sub>k</sub> の構成について説明する。本実施の形態では、単位シフトレジスタ S R を構成するトランジスタは、全て同一導電型の電界効果トランジスタであるが、ここでは N 型 TFT を用いた例を示す。

#### 【0061】

図 3 の如く、単位シフトレジスタ S R<sub>k</sub> は、図 2 で示した入力端子 I N 、第1出力端子 O U T 、第2出力端子 O U T S 、第1クロック端子 C K 、第2クロック端子 C K S およびリセット端子 R S T の他に、低電位側電源電位（ロー側電源電位） V S S が供給される第1電源端子 S 1 、高電位側電源電位（ハイ側電源電位） V D D 1 , V D D 2 がそれぞれ供給される第2および第3電源端子 S 2 , S 3 を有している。ハイ側電源電位 V D D 1 , V D D 2 は、互いに同一レベルでもよい。30

#### 【0062】

以下の説明では、ロー側電源電位 V S S を回路の基準電位としているが（V S S = 0）、実使用では画素に書き込まれるデータの電圧を基準にして基準電位が設定され、例えばハイ側電源電位 V D D 1 , V D D 2 は 17 V 、ロー側電源電位 V S S は -12 V などと設定される。

#### 【0063】

単位シフトレジスタ S R<sub>k</sub> において、ゲート線駆動信号 G<sub>k</sub> の出力段は、ゲート線 G L<sub>k</sub> の選択期間かつ表示有効期間のときにゲート線駆動信号 G<sub>k</sub> を活性レベル（H レベル）にするトランジスタ Q 1 と、ゲート線 G L<sub>k</sub> の非選択期間にゲート線駆動信号 G<sub>k</sub> を非活性レベル（L レベル）に維持するためのトランジスタ Q 2 とから構成されている。40

#### 【0064】

トランジスタ Q 1 は、第1出力端子 O U T と第1クロック端子 C K との間に接続しており、第1クロック端子 C K に入力される第1クロック信号（C L K または / C L K ）を第1出力端子 O U T に供給することによりゲート線駆動信号 G<sub>k</sub> を活性化させる。またトランジスタ Q 2 は、第1出力端子 O U T と第1電源端子 S 1 との間に接続しており、第1出力端子 O U T を放電して電位 V S S にすることで、ゲート線駆動信号 G<sub>k</sub> を非活性レベルに維持する。ここで、トランジスタ Q 1 のゲート（制御電極）が接続するノードを「ノー

50

20

30

40

50

「ノード N 1」、トランジスタ Q 2 のゲートが接続するノードを「ノード N 2」とそれぞれ定義する。

**【 0 0 6 5 】**

トランジスタ Q 1 のゲート・ソース間（即ち第 1 出力端子 OUT とノード N 1 との間）には容量素子 C（昇圧容量）が設けられている。この容量素子 C は、第 1 出力端子 OUT とノード N 1 との間を容量結合し、第 1 出力端子 OUT のレベル上昇に伴うノード N 1 の昇圧効果を高めるためのものである。但し、容量素子 C は、トランジスタ Q 1 のゲート・チャネル間容量が充分大きい場合にはそれで置き換えることができ、その場合には省略してもよい。

**【 0 0 6 6 】**

シフト信号 SH<sub>k</sub> の出力段は、ゲート線 GL<sub>k</sub> の選択期間にシフト信号 SH<sub>k</sub> を活性レベル（H レベル）にするトランジスタ Q 1 S と、ゲート線 GL<sub>k</sub> の非選択期間にシフト信号 SH<sub>k</sub> を非活性レベル（L レベル）に維持するためのトランジスタ Q 2 S とから構成されている。

**【 0 0 6 7 】**

トランジスタ Q 1 S は、第 2 出力端子 OUTS と第 2 クロック端子 CKS との間に接続しており、第 2 クロック端子 CKS に入力される第 2 クロック信号（CLKS または /CLKS）を第 2 出力端子 OUTS に供給することによりシフト信号 SH<sub>k</sub> を活性化させる。またトランジスタ Q 2 S は、第 2 出力端子 OUTS と第 1 電源端子 S 1 との間に接続しており、第 2 出力端子 OUTS を放電して電位 VSS にすることで、シフト信号 SH<sub>k</sub> を非活性レベルに維持する。トランジスタ Q 2 S のゲートはノード N 2 に接続される。トランジスタ Q 1 S のゲートが接続するノードを「ノード N 1 S」と定義する。

**【 0 0 6 8 】**

本実施の形態の単位シフトレジスタ S R<sub>k</sub> では、ノード N 1 とノード N 1 S との間に、第 2 電源端子 S 2 に接続されたゲートを有するトランジスタ Q 8 が接続される。

**【 0 0 6 9 】**

トランジスタ Q 1 S のゲート・ソース間（即ち第 2 出力端子 OUTS とノード N 1 S との間）には容量素子 CS（昇圧容量）が設けられている。この容量素子 CS は、第 2 出力端子 OUTS とノード N 1 S との間を容量結合し、第 2 出力端子 OUTS のレベル上昇に伴うノード N 1 S の昇圧効果を高めるためのものである。但し、容量素子 CS は、トランジスタ Q 1 S のゲート・チャネル間容量が充分大きい場合にはそれで置き換えることができ、その場合には省略してもよい。

**【 0 0 7 0 】**

ノード N 1 と第 2 電源端子 S 2 との間にはトランジスタ Q 3 が接続しており、そのゲートは入力端子 IN に接続している。トランジスタ Q 3 は、入力端子 IN に供給される信号（入力信号）の活性化に応じてノード N 1 を充電するよう機能する。トランジスタ Q 3 のドレインは第 3 電源端子 S 3 に接続させてもよい。

**【 0 0 7 1 】**

ノード N 1 と第 1 電源端子 S 1 との間には、ゲートがリセット端子 RST に接続したトランジスタ Q 4 が接続される。トランジスタ Q 4 は、リセット端子 RST に供給される信号（リセット信号）の活性化に応じてノード N 1 を放電するよう機能する。またノード N 1 と第 1 電源端子 S 1 との間には、ゲートがノード N 2 に接続したトランジスタ Q 5 も接続されている。トランジスタ Q 5 は、ノード N 2 が活性レベル（H レベル）である期間、ノード N 1 を放電して当該ノード N 1 を非活性レベル（L レベル）に維持するよう機能する。

**【 0 0 7 2 】**

これらトランジスタ Q 3, Q 4, Q 5 から成る回路は、ノード N 1 を充放電することによってトランジスタ Q 1, Q 1 S（出力プルアップトランジスタ）を駆動する「プルアップ駆動回路」を構成している。

**【 0 0 7 3 】**

10

20

30

40

50

一方、ノードN2と第3電源端子S3との間には、ゲートが第3電源端子S3に接続したトランジスタQ6が接続される（即ちトランジスタQ6はダイオード接続されている）。ノードN2と第1電源端子S1との間には、ゲートがノードN1に接続したトランジスタQ7が接続される。

#### 【0074】

トランジスタQ7は、トランジスタQ6よりもオン抵抗が充分小さく（つまり駆動能力が大きく）設定される。よってトランジスタQ7のゲート（ノードN1）がHレベルになってトランジスタQ7がオンすると、ノードN2は放電されてLレベルになる。逆にノードN1のLレベルになりトランジスタQ7がオフすると、ノードN2はトランジスタQ6により充電されてHレベルになる。

10

#### 【0075】

つまりトランジスタQ6, Q7は、ノードN1を入力端、ノードN2を出力端とするレシオ型インバータを構成している。このインバータにおいて、トランジスタQ6は負荷素子、トランジスタQ7は駆動素子として機能する。当該インバータは、ノードN2を充放電することによってトランジスタQ2, Q2S（出カプルダウントランジスタ）を駆動する「プルダウン駆動回路」を構成している。

#### 【0076】

図3の単位シフトレジスタ $S_{R_k}$ の動作を説明する。説明の簡単のため、単位シフトレジスタ $S_{R_k}$ においては、第1クロック端子CKには第1クロック信号CLKが、第2クロック端子CKSには第2クロック信号CLKSが、それぞれ入力されているものとする（例えは図2における、単位シフトレジスタ $S_{R_1}$ ,  $S_{R_3}$ などがこれに該当する）。

20

#### 【0077】

また、第1電源端子S1に供給されるロー側電源電位VSSを基準電位（0[V]）と仮定する。そして第1クロック信号CLK, /CLK、第2クロック信号CLKS, /CLKSおよびスタートパルスSPのLレベル電位は全てVSS（0[V]）であると仮定する。また、第2電源端子S2に供給されるハイ側電源電位VDD1と第3電源端子S3に供給されるハイ側電源電位VDD2は互いに等しいと仮定し、その値をVDDとする。

#### 【0078】

さらに、第1クロック信号CLK, /CLK、第2クロック信号CLKS, /CLKSおよびスタートパルスSPのHレベル電位は全て等しく、それらの値もVDDとする。また各トランジスタのしきい値電圧は全て等しいと仮定し、その値をVthとする。

30

#### 【0079】

ここでは、表示有効期間における単位シフトレジスタ $S_{R_k}$ の動作を説明する。表示有効期間では、第1クロック信号CLK, /CLKが、第2クロック信号CLKS, /CLKSと同様に活性化する。

#### 【0080】

単位シフトレジスタ $S_{R_k}$ の初期状態として、ノードN1がLレベル（VSS）、ノードN2がHレベル（VDD - Vth）の状態を仮定する（以下、この状態を「リセット状態」と称す）。このときトランジスタQ1はオフ、トランジスタQ2はオンになっており、第1出力端子OUT（ゲート線駆動信号 $G_k$ ）はLレベル（VSS）である。またトランジスタQ8はオン状態なので、ノードN1SはノードN1と同じくLレベル（VSS）である。よってトランジスタQ1Sはオフ、トランジスタQ2Sはオンになっており、第2出力端子OUTS（シフト信号 $SH_k$ ）もLレベル（VSS）である。

40

#### 【0081】

その状態から、前段のシフト信号 $SH_{k-1}$ がHレベル（VDD）になると、当該単位シフトレジスタ $S_{R_k}$ ではトランジスタQ3がオンになる。このときノードN2はHレベルなのでトランジスタQ5もオンしているが、トランジスタQ3はトランジスタQ5よりもオン抵抗が充分小さく（駆動能力が充分大きく）設定されており、ノードN1の電位が上昇する。

#### 【0082】

50

それによりトランジスタQ7が導通し始め、ノードN2のレベルが下がる。するとトランジスタQ5の抵抗値が上がるためノードN1のレベルが急速に上昇し、トランジスタQ7は充分にオンになる。その結果ノードN2はLレベル( VSS )になる。応じてトランジスタQ5がオフになり、ノードN1はHレベル( VDD - Vth )になる。このようにノードN1がHレベル、ノードN2がLレベルになると(以下、この状態を「セット状態」称す)、トランジスタQ1はオン、トランジスタQ2がオフになる。

#### 【0083】

ノードN2がLレベルになったため、トランジスタQ2Sはオフになる。またノードN1がHレベルになったため、オン状態のトランジスタQ8を通してノードN1Sが充電されてHレベル( VDD - Vth )になる。よってトランジスタQ1Sはオンになる。

10

#### 【0084】

前段のシフト信号SH<sub>k-1</sub>がLレベルに戻ると、トランジスタQ3はオフになるが、トランジスタQ4, Q5もオフしているため、ノードN1, N1Sは高インピーダンス状態(フローティング状態)でHレベルに維持される。

#### 【0085】

表示有効期間なので、続いて第1クロック信号CLKが活性化する。第1クロック信号CLKがHレベル( VDD )になると、オン状態のトランジスタQ1を通して第1出力端子OUTが充電され、ゲート線駆動信号G<sub>k</sub>のレベルが上昇する。このとき、容量素子C並びにトランジスタQ1のゲート容量(ゲート・ドレイン間容量、ゲート・ソース間容量およびゲート・チャネル間容量)を介する結合のため、ノードN1の電位が昇圧される。そのため第1出力端子OUTのレベルが上昇しても、トランジスタQ1のゲート・ソース間電圧はしきい値電圧( Vth )よりも大きく保たれ、当該トランジスタQ1は低インピーダンスに維持される。

20

#### 【0086】

従って、ゲート線駆動信号G<sub>k</sub>は、第1クロック信号CLKの立ち上がりに追随して素早くHレベルになる。またこのときトランジスタQ1は非飽和領域で動作するため、ゲート線駆動信号G<sub>k</sub>のレベルはクロック信号CLKと同じ電位VDDまで上昇する。その結果、ゲート線GL<sub>k</sub>が選択状態になる。

#### 【0087】

第1クロック信号CLKがHレベルになると同時に、第2クロック信号CLKSもHレベル( VDD )になる。するとオン状態のトランジスタQ1Sを通して第2出力端子OUTSが充電され、シフト信号SH<sub>k</sub>のレベルが上昇する。このとき、容量素子CS並びにトランジスタQ1Sのゲート容量(ゲート・ドレイン間容量、ゲート・ソース間容量およびゲート・チャネル間容量)を介する結合のため、ノードN1Sの電位が昇圧される。そのため第2出力端子OUTSのレベルが上昇しても、トランジスタQ1Sのゲート・ソース間電圧はしきい値電圧( Vth )よりも大きく保たれ、当該トランジスタQ1Sは低インピーダンスに維持される。

30

#### 【0088】

従って、シフト信号SH<sub>k</sub>は、第2クロック信号CLKSの立ち上がりに追随して素早くHレベルになる。またこのときトランジスタQ1Sは非飽和領域で動作して第2出力端子OUTSを充電するため、シフト信号SH<sub>k</sub>のレベルは、第2クロック信号CLKSと同じ電位VDDまで上昇する。

40

#### 【0089】

ノードN1の昇圧とノードN1Sの昇圧は同時に起こるため、トランジスタQ8のゲートは2つの電流電極(ソース、ドレイン)よりも高くなる。従ってノードN1, N1Sが昇圧されるとき、トランジスタQ8はオフになり、ノードN1, N1S間は電気的に分離される。ノードN1Sは、接続されるトランジスタの数が少ないため、ノードN1から分離されると寄生容量が非常に小さくなる。よってノードN1Sは充分に昇圧され、シフト信号SH<sub>k</sub>の立ち上がり速度は充分に高速化される。

#### 【0090】

50

その後、第1クロック信号 C L K および第2クロック信号 C L K S が揃って L レベル ( V S S ) になる。すると、オン状態のトランジスタ Q 1 , Q 1 S を通して第1および第2出力端子 O U T , O U T S がそれぞれ放電され、ゲート線駆動信号 G k およびシフト信号 S H k は L レベル ( V S S ) になる。その結果、ゲート線 G L k は非選択状態に戻る。

#### 【 0 0 9 1 】

なお、先ほどシフト信号 S H k が活性化したとき、次段 ( 単位シフトレジスタ S R k+1 ) はセット状態になっているので、次に第2クロック信号 / C L K が活性化すると、次段のシフト信号 S H k+1 が H レベルになる。

#### 【 0 0 9 2 】

すると当該単位シフトレジスタ S R k では、トランジスタ Q 4 がオンするので、ノード N 1 , N 1 S が放電されて L レベル ( V S S ) になる。応じてトランジスタ Q 7 がオフするので、ノード N 2 はトランジスタ Q 6 により充電されて H レベル ( V D D - V t h ) になる。その結果、単位シフトレジスタ S R k はリセット状態に戻り、トランジスタ Q 1 , Q 1 S がオフ、トランジスタ Q 2 , Q 2 S がオンの状態になる。

10

#### 【 0 0 9 3 】

以降、次のフレーム期間に前段のシフト信号 S H k-1 が活性化されるまでは、単位シフトレジスタ S R k はリセット状態に維持される。トランジスタ Q 5 ~ Q 7 から成るハーフラッチ回路がノード N 1 , N 1 S を L レベル、ノード N 2 を H レベルに保持するからである。よってゲート線 G L k の非選択期間の間は、ゲート線駆動信号 G k およびシフト信号 S H k は、共に低インピーダンスで L レベルに維持される。

20

#### 【 0 0 9 4 】

上で説明した単位シフトレジスタ S R k を簡単に説明すると、以下のとおりである。すなわち、単位シフトレジスタ S R k は、入力端子 I N の信号 ( 入力信号 ) の活性化に応じてセット状態になる。セット状態ではトランジスタ Q 1 , Q 1 S がオン、トランジスタ Q 2 , Q 2 S がオフになる。よってこのとき第1クロック端子 C K の信号 ( 第1クロック信号 ) が活性化するとゲート線駆動信号 G k が活性レベルになり、第2クロック端子 C K S の信号 ( 第2クロック信号 ) が活性化するとシフト信号 S H k が活性レベルになる。そして、リセット端子 R S T の信号 ( リセット信号 ) が活性化するとリセット状態に戻り、その後はゲート線駆動信号 G k およびシフト信号 S H k を L レベルに維持する。

#### 【 0 0 9 5 】

30

表示有効期間においては、第1クロック信号 C L K , / C L K が第2クロック信号 C L K S , / C L K S と同様に活性化されるので、セット状態 ( トランジスタ Q 1 , Q 1 S がオン、トランジスタ Q 2 , Q 2 S がオフ ) となった単位シフトレジスタ S R k はゲート線駆動信号 G k とシフト信号 S H k を同時に活性化させる。

#### 【 0 0 9 6 】

これに対し、表示無効期間においては、第2クロック信号 C L K S , / C L K S のみが活性化され、第1クロック信号 C L K , / C L K が L レベルに維持される。そのため単位シフトレジスタ S R k がセット状態になっても、第1出力端子 O U T は充電されずゲート線駆動信号 G k は L レベルから変化しない。よって表示無効期間では、単位シフトレジスタ S R k はシフト信号 S H k のみを活性化させる。

40

#### 【 0 0 9 7 】

図 2 のゲート線駆動回路 3 0 では、各単位シフトレジスタ S R の入力端子 I N には前段のシフト信号 S H が入力されるので、ゲート線駆動信号 G が活性化されない期間が存在しても、シフト信号 S H のシフト動作は正常に行われ、シフト信号 S H 1 , S H 2 , S H 3 ... がこの順に活性化される。よって、部分表示を行われるとき、シフト信号 S H 1 , S H 2 , S H 3 ... はこの順に全て活性化され、ゲート線駆動信号 G 1 , G 2 , G 3 ... は表示有効期間 ( 表示が必要な画素ラインの選択期間 ) 内のものだけが活性化される。

#### 【 0 0 9 8 】

図 4 は、本実施の形態に係るゲート線駆動回路 3 0 の動作を示す信号波形図であり、第 k 行目から第 k + 3 行までの画素ラインでのみ表示を行う部分表示が実行されるときの例

50

を示している。

#### 【0099】

上記したように、第1クロック信号C L K , / C L Kは、表示有効期間にのみ、第2クロック信号C L K S , / C L K Sと同様に活性化される。例えば第k行目から第k+3行までの画素ラインでのみ表示を行う場合は、図4に示すように、第k行目の選択期間(シフト信号S H<sub>k</sub>の活性期間)の始めから第k+3行の選択期間(シフト信号S H<sub>k+3</sub>の活性期間)の終わりまで間、第1クロック信号C L K , / C L Kが第2クロック信号C L K S , / C L K Sと同期して活性化される。これにより、ゲート線駆動信号G<sub>k</sub> ~ G<sub>k+3</sub>が、それぞれゲート線G L<sub>k</sub> ~ G<sub>k+3</sub>の選択期間に活性化される。その他の行のゲート線駆動信号Gはフレーム期間内の全てを通して非活性レベルに維持される。

10

#### 【0100】

図示は省略するが、全画面表示の場合には、第1クロック信号C L K , / C L Kが常に第2クロック信号C L K S , / C L K Sと同様に活性化される。よってゲート線駆動信号G<sub>1</sub>, G<sub>2</sub>, G<sub>3</sub>...は、シフト信号S H<sub>1</sub>, S H<sub>2</sub>, S H<sub>3</sub>...と同じタイミングで、全てが順番に活性化される。

#### 【0101】

ここで表示無効期間の単位シフトレジスタS R<sub>k</sub>におけるトランジスタQ 8の動作に注目する。表示無効期間では、第1クロック端子C Kおよび第1出力端子O U TがLレベルのまま変化しないので、トランジスタQ 1のゲート容量および容量素子Cを介する結合によるノードN 1の昇圧は起こらない。よって第2出力端子O U T Sのレベル上昇に伴ってノードN 1 Sの電位がV D D - V t hから昇圧されるとき、ノードN 1の電位はV D D - V t hのまま変化しない。

20

#### 【0102】

つまりノードN 1 Sが昇圧されたとき、トランジスタQ 8のソース(ノードN 1)電位はV D D - V t h、ゲート電位はV D Dであり、ゲート・ソース間電圧はV t hとなる。この状態では、トランジスタQ 8にはサブスレッシュホールド電流である僅かな電流しか流れず、トランジスタQ 8は実質的にオフしている。つまりノードN 1 SからノードN 1への電流は殆ど流れず、ノードN 1 SとノードN 1の間が実質的に分離された状態となる。よってノードN 1 Sの寄生容量が小さくなり、表示有効期間のときと同様に、ノードN 1 Sは充分に昇圧される。

30

#### 【0103】

トランジスタQ 8のゲートに供給するハイ側電源電位V D D 1は、入力端子I Nに入力される前段のシフト信号S H<sub>k-1</sub>の活性レベル(第2クロック信号C L K S , / C L K Sの活性レベルに相当)の電位以下にすることが重要である。本実施の形態では、ハイ側電源電位V D D 1と前段のシフト信号S H<sub>k-1</sub>の活性レベルの電位が等しいと仮定し、その値をV D Dと定義した。トランジスタQ 8のゲート電位がV D Dより大きい場合は、表示無効期間にノードN 1 Sが昇圧されたとき、トランジスタQ 8がオフにならず、ノードN 1 SとノードN 1の間が分離されないので、上記の効果が得られない。

#### 【0104】

逆に、トランジスタQ 8のゲート電位がV D Dよりも低いと、その分だけトランジスタQ 8によって充電された後のノードN 1 Sの電位が低くなるので、これも好ましくない。従ってトランジスタQ 8のゲート電位は、V D Dを超えない範囲で、より高いことが好ましい。

40

#### 【0105】

このように本実施の形態に係る単位シフトレジスタS R<sub>k</sub>では、シフト信号S H<sub>k</sub>の活性化に応じてノードN 1 Sが昇圧されるとき、トランジスタQ 8がノードN 1, N 1 S間を分離する。よってノードN 1 Sは充分に昇圧されるので、シフト信号S H<sub>k</sub>の立ち上がり速度は充分に高速化される。この効果は、表示有効期間および表示無効期間のどちらの場合でも得られる。つまり表示無効期間であってもシフト信号S Hの立ち上がり速度は低下せず、ゲート線駆動回路30の動作マージンの低下を防止できる。

50

**【0106】**

本実施の形態では、ゲート線駆動回路30のシフトレジスタが2相のクロック信号を用いて駆動される例を示したが、もちろん3相以上のクロック信号を用いることも可能である。

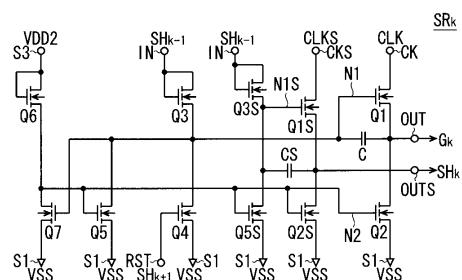

**【0107】****[第1の変更例]**

図3の単位シフトレジスタ $S R_k$ では、トランジスタ $Q_3$ のドレインを一定のハイ側電源電位 $V_{DD1}$ が供給される第2電源端子 $S_2$ に接続させたが、図5のように、それを前段のシフト信号 $S H_{k-1}$ が供給される入力端子 $I_N$ に接続させてもよい。これにより、トランジスタ $Q_3$ にハイ側電源電位 $V_{DD1}$ を供給するための配線を省略でき、回路レイアウトが容易になるという効果が得られる。10

**【0108】**

なお図3の構成では、図5に比べて単位シフトレジスタ $S R$ のそれぞれのシフト信号 $S H$ が駆動する負荷容量が低減され、各段のシフト信号 $S H$ の立ち上がり速度および立ち下がり速度が向上するという効果が得られる。

**【0109】****[第2の変更例]**

液晶表示装置などの走査線駆動回路には、非晶質シリコン( $a-Si$ )を用いて形成したトランジスタ( $a-Si$ トランジスタ)が広く使用されている。 $a-Si$ トランジスタは、ゲートが直流的にバイアスされるとしきい値電圧がシフトする特性があり、それが原因で走査線駆動回路の誤動作を引き起こす場合がある。20

**【0110】**

例えば図3の回路では、トランジスタ $Q_8$ のゲートが常に正バイアスされるので、トランジスタ $Q_8$ のしきい値電圧が正方向へシフトする。その場合、トランジスタ $Q_8$ のオン抵抗が高くなるため、ノード $N_{1S}$ の充電・放電の速度が低下することが懸念される。

**【0111】**

図6は本実施の形態の第2の変更例に係る単位シフトレジスタ $S R_k$ の回路図である。当該単位シフトレジスタ $S R_k$ は、図5の回路に対し、トランジスタ $Q_8$ のゲートを入力端子 $I_N$ に接続させると共に、ノード $N_2$ に接続したゲートを有しノード $N_{1S}$ と第1電源端子 $S_1$ との間に接続するトランジスタ $Q_{5S}$ を設けたものである。本変更例は図3の回路に対しても適用可能である。30

**【0112】**

図6の単位シフトレジスタ $S R$ では、ノード $N_1$ がHレベルになってトランジスタ $Q_8$ がノード $N_{1S}$ を充電する期間にのみ、当該トランジスタ $Q_8$ のゲートが正バイアスされる。つまりトランジスタ $Q_8$ のゲートは直流的にバイアスされないので、トランジスタ $Q_8$ のしきい値電圧のシフトを防止できる。

**【0113】**

但し、図3や図5の回路と異なり、トランジスタ $Q_8$ がノード $N_{1S}$ を放電することができないので、単位シフトレジスタ $S R$ がリセット状態のとき(ノード $N_2$ がHレベルのとき)にノード $N_{1S}$ を放電するトランジスタ $Q_{5S}$ が必要になる。そのため図3や図5に比べて必要なトランジスタの個数が1つ増える点に留意すべきである。40

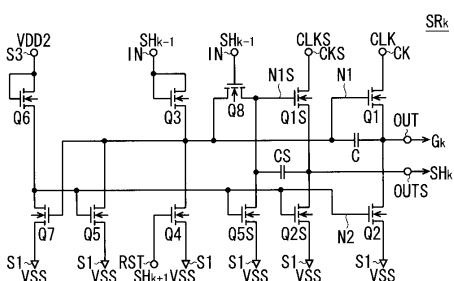

**【0114】****[第3の変更例]**

図7は、本実施の形態の第2の変更例に係る単位シフトレジスタ $S R_k$ の回路図である。当該単位シフトレジスタ $S R_k$ は、図5のトランジスタ $Q_8$ の代わりに、ノード $N_{1S}$ に接続するトランジスタ $Q_{3S}, Q_{5S}$ を設けたものである。トランジスタ $Q_{3S}$ は、ノード $N_{1S}$ と入力端子 $I_N$ との間に接続し、そのゲートは入力端子 $I_N$ に接続される。トランジスタ $Q_{5S}$ は、ノード $N_{1S}$ と第1電源端子 $S_1$ との間に接続し、そのゲートはノード $N_2$ に接続される。

**【0115】**1020304050

本変更例は図3の回路に対しても適用可能である。またトランジスタQ3Sのドレインは、第2電源端子S2または第3電源端子S3に接続させてもよい。

#### 【0116】

図6の単位シフトレジスタSRでは、前段のシフト信号SH<sub>k-1</sub>の活性化に応じてトランジスタQ3SがノードN1Sを充電し、ノードN2がHレベルになるとトランジスタQ5SがノードN1Sを放電する。つまりトランジスタQ3S, Q5Sの2つのトランジスタによって、図3や図5の回路におけるトランジスタQ8と同様の動作が行われる。

#### 【0117】

本変更例によれば、ノードN1, N1S間に完全に分離されているので、トランジスタQ1のゲート容量および容量素子CがノードN1Sの昇圧には影響しない。よって表示無効期間であってもシフト信号SH<sub>k</sub>の立ち上がり速度は低下せず、ゲート線駆動回路30の動作マージンの低下を防止できる。但し、図3や図5に比べて必要なトランジスタの個数が1つ増える点に留意すべきである。

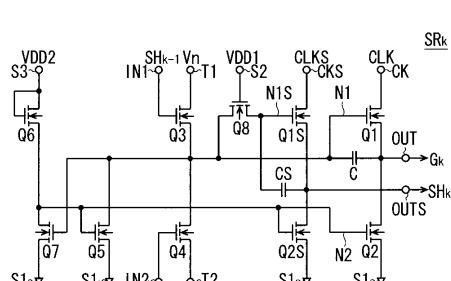

#### 【0118】

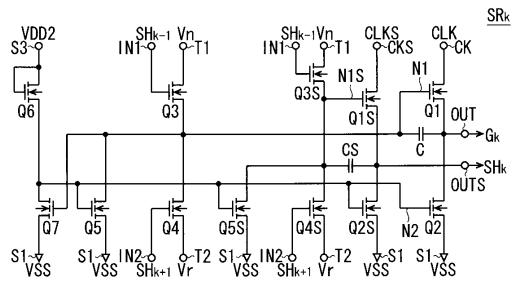

##### [第4の変更例]

本変更例では、信号のシフト方向を変更可能なシフトレジスタに本発明を適用する。そのようなシフトレジスタを用いて構成されたゲート線駆動回路30は、双方向の走査が可能である。前段から後段への方向（単位シフトレジスタSR<sub>1</sub>, SR<sub>2</sub>, SR<sub>3</sub>, …の順）に信号をシフトさせる動作を「順方向シフト」、後段から前段への方向（単位シフトレジスタSR<sub>n</sub>, SR<sub>n-1</sub>, SR<sub>n-2</sub>, …の順）に信号をシフトさせる動作を「逆方向シフト」と定義する。

#### 【0119】

図8は、本変更例に係る単位シフトレジスタSR<sub>k</sub>の回路図である。当該単位シフトレジスタSR<sub>k</sub>は、図3とほぼ同様の構成であるが、以下の点で異なっている。

#### 【0120】

すなわち、当該単位シフトレジスタSR<sub>k</sub>は、前段のシフト信号SH<sub>k-1</sub>を受ける第1入力端子IN1と、次段のシフト信号SH<sub>k+1</sub>を受ける第2入力端子IN2と、所定の第1および第2電圧信号Vn, Vrがそれぞれ供給される第1および第2電圧信号端子T1, T2とを備えている。トランジスタQ3は、ノードN1と第1電圧信号端子T1との間に接続され、そのゲートは第1入力端子IN1に接続される。トランジスタQ4は、ノードN1と第2電圧信号端子T2との間に接続され、そのゲートは第2入力端子IN2に接続される。

#### 【0121】

第1および第2電圧信号Vn, Vrは、信号のシフト方向（走査方向）を決定するための制御信号である。単位シフトレジスタSR<sub>k</sub>に順方向シフトを行わせる場合、第1電圧信号VnがHレベル、第2電圧信号VrがLレベルに設定される。また逆方向シフトを行わせる場合には、第1電圧信号VnがLレベル、第2電圧信号VrがHレベルに設定される。

#### 【0122】

第1電圧信号VnがHレベル、第2電圧信号VrがLレベルの場合、図8の単位シフトレジスタSR<sub>k</sub>は、図3の回路と等価になるので順方向シフトが可能になる。一方、第1電圧信号VnがLレベル、第2電圧信号VrがHレベルの場合は、図8の単位シフトレジスタSR<sub>k</sub>において、トランジスタQ3, Q4の機能が図3の回路とは逆になる。つまりトランジスタQ4がノードN1を充電するように機能し、トランジスタQ3がノードN1を放電するように機能する。その結果、逆方向シフトが可能になる。

#### 【0123】

##### [第5の変更例]

図3の回路では、トランジスタQ3のソース、トランジスタQ4, Q5のドレインおよびトランジスタQ7のゲートを全てノードN1に接続させたが、それらの1つ以上をノードN1Sに接続させてもよい。図9は、それら全てをノードN1Sに接続させた例を示し

10

20

30

40

50

ている。

**【0124】**

トランジスタQ3のソース、トランジスタQ4, Q5のドレインおよびトランジスタQ7のゲートをノードN1Sに接続させると、その分だけノードN1の寄生容量が低減されるため、ノードN1がより高い電位にまで昇圧されるようになり、トランジスタQ1の駆動能力が向上する。それによりゲート線駆動信号Gのレベル遷移の速度が速くなるため、ゲート線GLの高速駆動が可能になる。

**【0125】**

その反面、ノードN1Sの寄生容量は増加するため、シフト信号SHのレベル遷移の速度が低下する点に留意すべきである。トランジスタQ3のソース、トランジスタQ4, Q5のドレインおよびトランジスタQ7のゲートをそれぞれノードN1側, N1S側のどちらに接続させるかは、表示装置の特性を考慮して決定するとよい。10

**【0126】**

本変更例は、上記の各変更例の単位シフトレジスタSR(図5～図8)に対しても適用可能である。但し、図7のトランジスタQ3のソースは、ノードN1に接続させておく必要がある。図7の構成では、ノードN1, N1Sをそれぞれ個別のトランジスタで充電する必要があるからである。

**【0127】**

また図6、図7のトランジスタQ5のドレインは、ノードN1側に接続させておく必要がある。図6、図7の構成では、単位シフトレジスタSRがリセット状態のときにノードN1, N1Sを低インピーダンスでLレベルにするトランジスタが、それぞれ個別に必要だからである。20

**【0128】**

さらに図6、図7の回路では、トランジスタQ4ドレインとトランジスタQ7のゲートを同じ側に接続させる必要がある。図6、図7の構成では、トランジスタQ4がオンするときノードN1, N1S間が分離されているので、トランジスタQ4ドレインとトランジスタQ7のゲートが接続していなければ、トランジスタQ7をオフにすることができないからである。

**【0129】**

**[第6の変更例]**30

本変更例では、第3の変更例(図7)を、信号のシフト方向を変更可能なシフトレジスタ(第4の変更例(図8))に適用する。

**【0130】**

図10は、本実施の形態の第6の変更例に係る単位シフトレジスタSR<sub>k</sub>の回路図である。当該単位シフトレジスタSR<sub>k</sub>は、図8と同様に、前段のシフト信号SH<sub>k-1</sub>を受ける第1入力端子IN1と、次段のシフト信号SH<sub>k+1</sub>を受ける第2入力端子IN2と、第1および第2電圧信号VN, VRがそれぞれ供給される第1および第2電圧信号端子T1, T2とを備えている。

**【0131】**

当該単位シフトレジスタSR<sub>k</sub>の回路構成は、図7に対し、以下の点で異なっている。40

すなわち、トランジスタQ3は、ノードN1と第1電圧信号端子T1との間に接続され、そのゲートは第1入力端子IN1に接続される。トランジスタQ4は、ノードN1と第2電圧信号端子T2との間に接続され、そのゲートは第2入力端子IN2に接続される。トランジスタQ3Sは、ノードN1Sと第1電圧信号端子T1との間に接続され、そのゲートは第1入力端子IN1に接続される。さらに、第2入力端子IN2に接続したゲートを有し、ノードN1と第2電圧信号端子T2との間に接続したトランジスタQ4Sが設けられる。

**【0132】**

第1電圧信号VNがHレベル、第2電圧信号VRがLレベルの場合、図10の単位シフトレジスタSR<sub>k</sub>は、図7の回路と等価になるので順方向シフトが可能になる。但し、ノ50

ードN1Sの放電は、図7ではトランジスタQ5Sにより行われるが、図10の回路では主にトランジスタQ4Sによって行われる（トランジスタQ5Sは主に、リセット状態の間ノードN1Sを低インピーダンスでLレベルに維持する働きをする）。

### 【0133】

一方、第1電圧信号VnがLレベル、第2電圧信号VrがHレベルの場合は、図10の単位シフトレジスタSR<sub>k</sub>において、トランジスタQ3, Q4, Q3S, Q4Sの機能が順方向シフト時とは逆になる。つまりトランジスタQ4, Q4SがそれぞれノードN1, N1Sを充電するように機能し、トランジスタQ3, Q3SがそれぞれノードN1, N1Sを放電するように機能する。その結果、逆方向シフトが可能になる。

### 【0134】

なお、図10の回路において、トランジスタQ7のゲートはノードN1Sに接続させてもよい。

### 【符号の説明】

### 【0135】

10 液晶アレイ部、100 液晶表示装置、30 ゲート線駆動回路、31B 第2クロック信号発生器、31A 第1クロック信号発生器、31B 第2クロック信号発生器、32 スタート信号発生器、GL ゲート線、SR 単位シフトレジスタ、G ゲート線駆動信号、SH シフト信号、CLK, /CLK 第1クロック信号、CLKS, /CLKS 第2クロック信号。

【図1】

【図2】

【図3】

【図4】

【図5】

【図7】

【図6】

【図8】

【図9】

【図10】

---

フロントページの続き

(51)Int.Cl.

F I

G 09 G 3/20 611A

G 09 G 3/36

G 09 G 3/20 624B

(56)参考文献 特開2011-209714(JP,A)

特開2009-140608(JP,A)

特開2008-140490(JP,A)

特開2008-58939(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 11 C 19 / 28

G 11 C 19 / 00

G 09 G 3 / 20

G 09 G 3 / 36