(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5919087号

(P5919087)

(45) 発行日 平成28年5月18日(2016.5.18)

(24) 登録日 平成28年4月15日(2016.4.15)

|                        |                |

|------------------------|----------------|

| (51) Int.Cl.           | F 1            |

| HO 1 L 23/28 (2006.01) | HO 1 L 23/28 H |

| HO 1 L 23/50 (2006.01) | HO 1 L 23/28 A |

|                        | HO 1 L 23/50 R |

請求項の数 13 (全 40 頁)

(21) 出願番号 特願2012-108266 (P2012-108266)

(22) 出願日 平成24年5月10日 (2012.5.10)

(65) 公開番号 特開2013-235999 (P2013-235999A)

(43) 公開日 平成25年11月21日 (2013.11.21)

審査請求日 平成27年2月4日 (2015.2.4)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

東京都江東区豊洲三丁目2番24号

(74) 代理人 100080001

弁理士 筒井 大和

(74) 代理人 100113642

弁理士 菅田 篤志

(74) 代理人 100117008

弁理士 筒井 章子

(74) 代理人 100147430

弁理士 坂次 哲也

(72) 発明者 成田 博明

青森県北津軽郡鶴田町大字山道字小泉27

5番地 株式会社ルネサスハイコンボーネンツ内

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法および半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

以下の工程を含む半導体装置の製造方法：

(a) チップ搭載領域を囲む第1領域、前記第1領域を囲む導電性部材からなる四角形の保持枠、前記保持枠に連結保持され、前記チップ搭載領域を囲み、前記第1領域に配置された前記導電性部材からなる第1厚さの複数のリード、前記保持枠に連結保持された前記導電性部材からなる前記第1厚さよりも薄い第2厚さの吊りリード、および前記吊りリードに保持された前記導電性部材からなる前記第1厚さの識別用目印を有する単位フレームを複数配列したリードフレームを準備する工程；

(b) 第1主面、前記第1主面に設けられた複数のチップ領域、前記複数のチップ領域のうちの互いに隣り合うチップ領域間に設けられた切断領域、および前記第1主面とは反対側の第2主面を有する半導体ウエハを準備する工程；

(c) 前記半導体ウエハの前記第2主面に樹脂シートを貼り付ける工程；

(d) 前記工程(c)の後、前記切断領域に沿って前記半導体ウエハおよび前記樹脂シートを切断し、前記樹脂シートの一部を有する半導体チップを取得する工程；

(e) 前記工程(d)の後、ヒートステージの表面上に配置されたフレームテープの上面に前記リードフレームを固定し、前記リードフレームを構成する前記単位フレームの前記チップ搭載領域に前記樹脂シートの前記一部を介して前記半導体チップを配置し、前記半導体チップを前記フレームテープの前記上面に固定する工程；

(f) 前記工程(e)の後、前記半導体チップの複数の電極パッドと前記複数のリードの

10

20

表面とを複数の導電性ワイヤを介してそれぞれ電気的に接続する工程；

(g) 前記工程 (f) の後、前記半導体チップ、前記複数の導電性ワイヤ、前記複数のリードの前記表面および側面、前記吊りリード、前記識別用目印の表面および側面、ならびに前記フレームテープの前記上面を樹脂で封止し、前記樹脂シートの前記一部を封止体の一部として、前記封止体を形成する工程；

(h) 前記工程 (g) の後、前記封止体から前記フレームテープを剥離し、前記封止体の裏面から前記複数のリードの裏面および前記識別用目印の裏面を露出する工程；

(i) 前記工程 (h) の後、前記封止体、前記複数のリード、および前記吊りリードを切断し、個々の前記半導体装置を取得する工程、

ここで、前記工程 (a) において、前記識別用目印および前記吊りリードは、平面視において前記第1領域に配置され、前記チップ搭載領域には配置されていない。

#### 【請求項2】

請求項1記載の半導体装置の製造方法において、

前記保持枠は、互いに離間して第1方向に延在する第1保持部と第3保持部、および互いに離間して前記第1方向と直交する第2方向に延在する第2保持部と第4保持部により構成され、

前記第1保持部と前記第2保持部、前記第2保持部と前記第3保持部、前記第3保持部と前記第4保持部、前記第4保持部と前記第1保持部とがそれぞれ互いに連結し、

前記吊りリードは前記第1方向に沿って延在する第1部分と、前記第2方向に沿って延在する第2部分とから構成され、前記吊りリードの前記第1部分の一端が前記第4保持部に連結し、前記吊りリードの前記第2部分の一端が前記第1保持部に連結し、前記吊りリードの前記第1部分の他端と前記吊りリードの前記第2部分の他端とが前記識別用目印を保持している。

#### 【請求項3】

請求項1記載の半導体装置の製造方法において、

前記保持枠は、互いに離間して第1方向に延在する第1保持部と第3保持部、および互いに離間して前記第1方向と直交する第2方向に延在する第2保持部と第4保持部により構成され、

前記第1保持部と前記第2保持部、前記第2保持部と前記第3保持部、前記第3保持部と前記第4保持部、前記第4保持部と前記第1保持部とがそれぞれ互いに連結し、

前記吊りリードの一端が前記第1保持部に連結し、前記吊りリードの他端が前記識別用目印を保持している。

#### 【請求項4】

請求項1記載の半導体装置の製造方法において、

前記封止体の前記裏面から露出する前記識別用目印の前記裏面の平面視における形状は、円形または四角形である。

#### 【請求項5】

請求項1記載の半導体装置の製造方法において、

前記導電性部材は銅であり、前記複数のリードの前記裏面および前記識別用目印の前記裏面にはパラジウム膜が形成されている。

#### 【請求項6】

請求項1記載の半導体装置の製造方法において、

前記工程 (a) は、さらに以下の工程を含む：

(a1) 表面、および前記表面と反対側の裏面を有する前記導電性部材を準備する工程；

(a2) 前記導電性部材の前記表面に第1レジスト膜を塗布し、前記導電性部材の前記裏面に第2レジスト膜を塗布する工程；

(a3) 前記第1レジスト膜の一部領域および前記第2レジスト膜の一部領域にそれぞれ露光光を照射して、前記第1レジスト膜の前記一部領域および前記第2レジスト膜の前記一部領域を硬化させる工程；

(a4) 前記第1レジスト膜および前記第2レジスト膜に現像処理を施して、前記第1レ

10

20

30

40

50

ジスト膜の前記一部領域および前記第2レジスト膜の前記一部領域を前記導電性部材の前記表面および前記裏面にそれぞれ残す工程；

(a5) 前記第1レジスト膜の前記一部領域および前記第2レジスト膜の前記一部領域をマスクとして前記導電性部材をエッチングし、前記導電性部材を加工する工程；

(a6) 前記第1レジスト膜の前記一部領域および前記第2レジスト膜の一部領域を除去する工程。

ここで、前記導電性部材の前記表面側から透視したときに、前記第1レジスト膜の前記一部領域が覆う領域は前記第2レジスト膜の前記一部領域が覆う領域よりも広いが、前記第2レジスト膜の前記一部領域が覆う領域は全て前記第1レジスト膜の前記一部領域が覆う領域と重なる。

10

【請求項7】

請求項6記載の半導体装置の製造方法において、

前記工程(a5)では、前記導電性部材の前記表面側から透視したときに、前記第1レジスト膜の前記一部領域と前記第2レジスト膜の前記一部領域とが重なって形成されている領域では、前記導電性部材はエッチングされず、

前記導電性部材の前記表面側から透視したときに、前記第1レジスト膜の前記一部領域は形成されているが、前記第2レジスト膜の前記一部領域は形成されていない領域では、前記導電性部材は前記表面側に一部を残して、前記裏面側から厚さ方向にエッチングされる。

20

【請求項8】

請求項6記載の半導体装置の製造方法において、

前記工程(a5)では、前記識別用目印が形成される領域では、前記導電性部材の前記表面側から透視したときに、前記第1レジスト膜の前記一部領域と前記第2レジスト膜の前記一部領域とが重なって形成されており、前記導電性部材はエッチングされず、

前記吊りリードが形成される領域では、前記導電性部材の前記表面側から透視したときに、前記第1レジスト膜の前記一部領域は形成されているが、前記第2レジスト膜の前記一部領域は形成されておらず、前記導電性部材は前記表面側に一部を残して、前記裏面側から厚さ方向にエッチングされる。

【請求項9】

請求項8記載の半導体装置の製造方法において、

30

前記識別用目印の前記第1厚さは、前記吊りリードの前記第2厚さの半分である。

【請求項10】

樹脂封止された半導体装置であって、

前記半導体装置は、

半導体チップと、

前記半導体チップの裏面を封止する樹脂シートと、

前記半導体チップの周囲に設けられた導電性部材からなる複数のリードと、

前記半導体チップの複数の電極パッドと前記複数のリードとをそれぞれ電気的に接続する複数の導電性ワイヤと、

前記複数のリードのうち1個のリードの傍に設けられた前記導電性部材からなる識別用目印と、

40

前記識別用目印に連結する吊りリードと、

前記半導体チップ、前記複数のリードの表面および側面の一部、前記複数の導電性ワイヤ、前記識別用目印の表面および側面、ならびに前記吊りリードの表面、裏面、および側面の一部を樹脂により封止する封止体と、

を有し、

前記封止体の裏面に、前記複数のリードの裏面および前記識別用目印の裏面が露出しており、

前記封止体の前記裏面は、前記複数のリードで取り囲まれた第1領域と、前記第1領域を除く第2領域と、を有し、

50

前記識別用目印および前記吊りリードは、平面視において前記第2領域に配置され、前記第1領域には配置されていない。

**【請求項11】**

請求項10記載の半導体装置において、

前記封止体は、さらに前記裏面の反対側の表面および前記裏面と前記表面との間の側面を有し、

前記吊りリードは、さらに一端部と他端部とを有し、

前記識別用目印は、前記一端部と前記他端部との間の前記吊りリードに設置され、

前記吊りリードの前記一端部の一部は、前記封止体の前記側面から露出している。

**【請求項12】**

10

請求項10記載の半導体装置において、

前記導電性部材は銅であり、前記封止体の前記裏面から露出する前記複数のリードの前記裏面および前記識別用目印の前記裏面にはパラジウム膜が形成されている。

**【請求項13】**

請求項10記載の半導体装置において、

前記複数のリードのインデックスを前記識別用目印によって認識する。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は半導体装置の製造技術および半導体装置に関し、例えばパッケージの裏面にリードを有する半導体装置の製造に好適に利用できるものである。

20

**【背景技術】**

**【0002】**

樹脂封止された半導体装置の特性選別においては、複数のリード（外部接続端子、外部端子、端子）のなかからインデックス（識別番号、通し番号、指標）として1番目のリードと定められた1pin（1ピン）の位置を認識する必要がある。

**【0003】**

例えば特開2008-288304号公報（特許文献1）には、モールド樹脂の下面から露出する周辺部の吊りリードの先端部を補強端子部として構成し、1つの補強端子部を、他の補強端子部とはモールド樹脂から露出する形状が異なるものとすることにより、1pinを認識する技術が開示されている。

30

**【0004】**

また、特開2011-091145号公報（特許文献2）には、樹脂パッケージの裏面に露出するアイランドのコーナー部の一部を切り欠くことで、アイランドの露出形状が位置認識マークとして利用される技術が開示されている。

**【0005】**

また、特開2006-229263号公報（特許文献3）には、樹脂封止体の裏面から複数の吊りリードの一部を露出させ、そのうちの1本を樹脂封止体の向きを認識するためのインデックスとして用いる技術が開示されている。

**【0006】**

40

また、特開2003-332513号公報（特許文献4）には、封止体の表面側の対角線方向に沿った2つのコーナー部に切り欠き部を設け、これら切り欠き部から、円形の平面形状を有する認識マークが設けられた吊りリードの一部を露出する技術が開示されている。

**【0007】**

また、特開2004-327903号公報（特許文献5）には、リードの一面をハーフエッティング面、他面を非ハーフエッティング面とし、非ハーフエッティング面と外側側面とを樹脂から露出させ、これ以外を樹脂中にして樹脂封止した半導体装置が開示されている。

**【先行技術文献】**

**【特許文献】**

50

## 【0008】

【特許文献1】特開2008-288304号公報

【特許文献2】特開2011-091145号公報

【特許文献3】特開2006-229263号公報

【特許文献4】特開2003-332513号公報

【特許文献5】特開2004-327903号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0009】

樹脂封止された半導体装置（半導体パッケージ）においては、その裏面から露出する複数のリードのなかから1個のリードを「1pin」と定めている。この1pinは、半導体装置の向きの識別、または検査時において複数のリードの各々を識別する役割を担う。そのため、外観から容易に1pinを認識できることが必要である。しかし、パーツフィーダ方式の特性選別を採用する場合、タプレスパッケージでは1pinの位置認識ができないという課題が生じていた。

## 【0010】

その他の課題と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

## 【課題を解決するための手段】

## 【0011】

一実施の形態によれば、吊りリードに連結され、樹脂封止体の裏面に露出する識別用目印を形成し、この識別用目印によって樹脂封止体の裏面に露出する複数のリードのなかから1pinの位置認識を行う。

## 【発明の効果】

## 【0012】

一実施の形態によれば、タプレスパッケージにおいて1pinの位置認識を容易に行うことができる。

## 【図面の簡単な説明】

## 【0013】

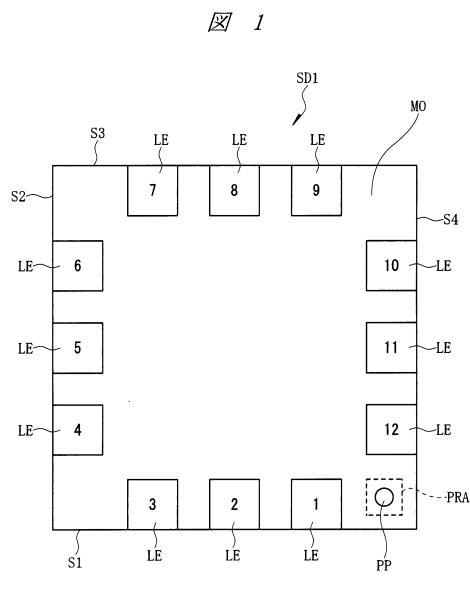

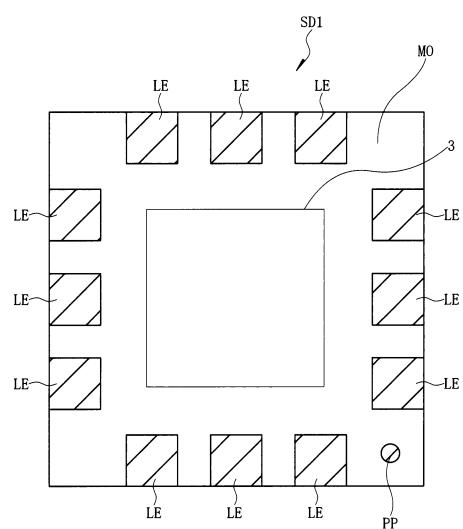

【図1】一実施の形態による半導体装置の裏面を示す要部平面図である。

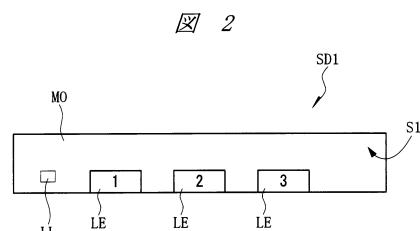

【図2】一実施の形態による半導体装置の1番目のインデックスが付されたリード（1pin）が配置された外側側面を示す要部側面図である。

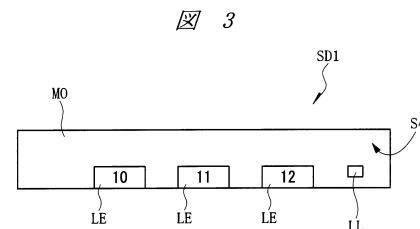

【図3】一実施の形態による半導体装置の最終番目のインデックスが付されたリードが配置された外側側面を示す要部側面図である。

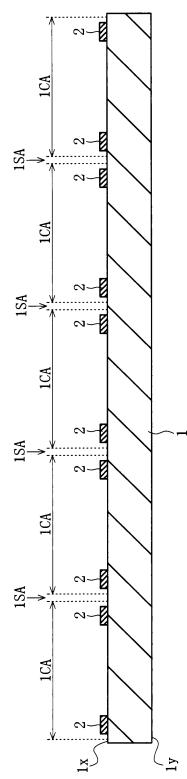

【図4】一実施の形態によるウエハ準備工程における半導体装置の要部断面図である。

【図5】一実施の形態による樹脂シート貼り付け工程における半導体装置の要部断面図である。

【図6】一実施の形態によるダイシングテープ工程における半導体装置の要部断面図である。

【図7】一実施の形態によるウエハダイシング工程における半導体装置の要部断面図である。

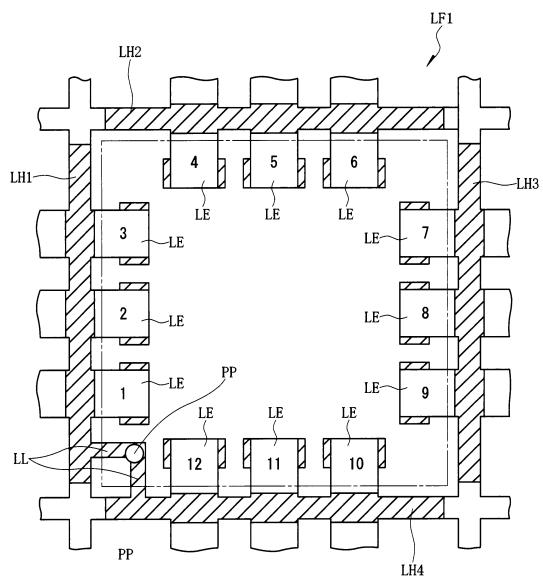

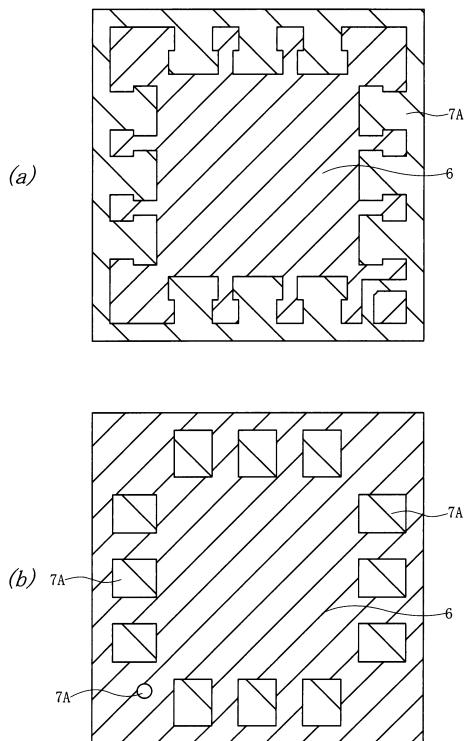

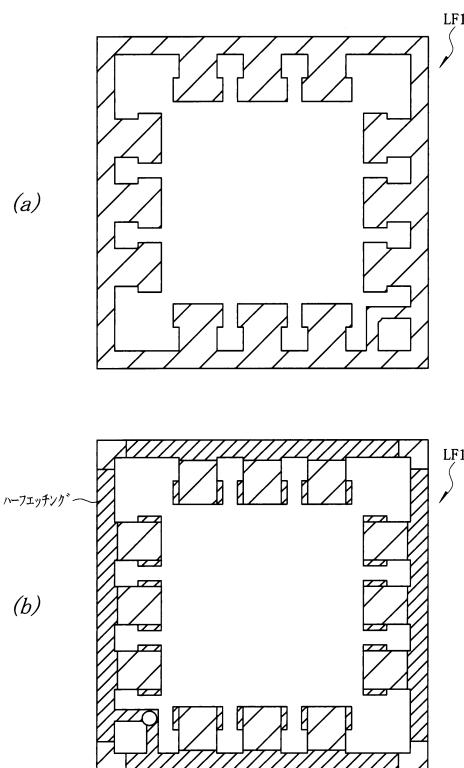

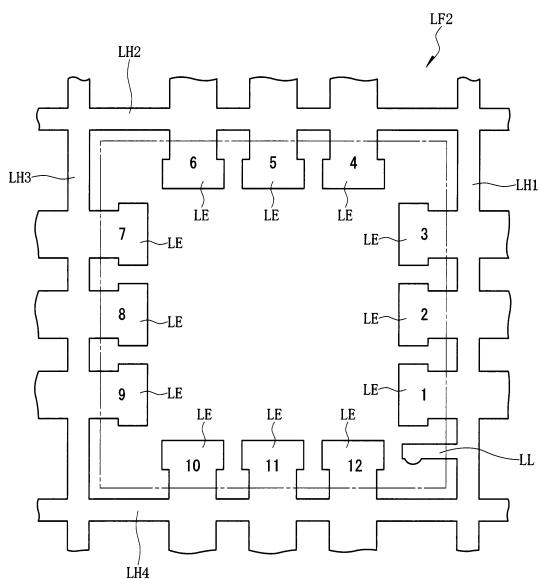

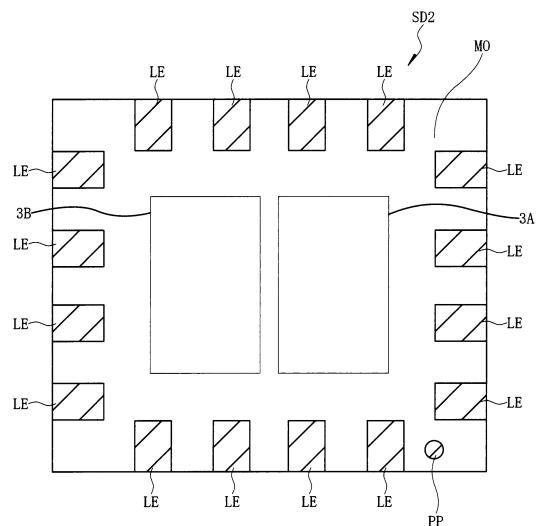

【図8】一実施の形態によるリードフレームの表面を示す要部平面図である。

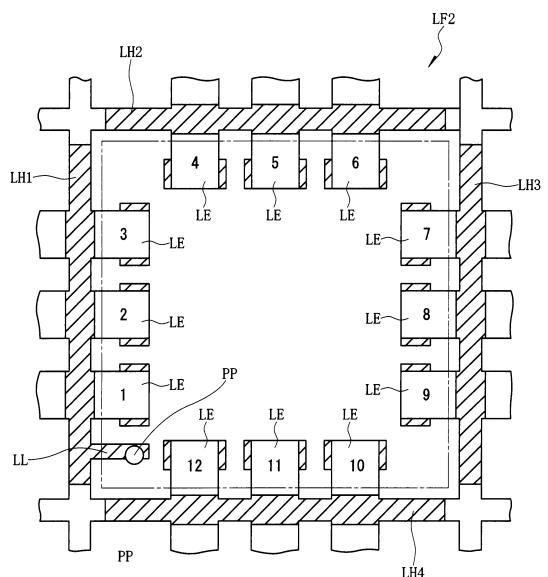

【図9】一実施の形態によるリードフレームの裏面を示す要部平面図である。

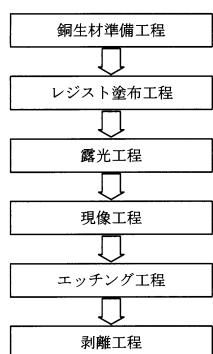

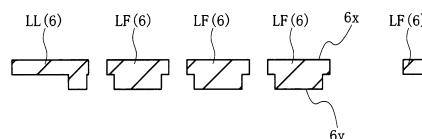

【図10】一実施の形態によるリードフレームの製作方法を説明する工程図である。

【図11】(a)および(b)はそれぞれ、一実施の形態によるリードフレームの製作工程におけるリードフレームの表面および裏面を示す要部平面図である。

【図12】一実施の形態によるリードフレームの製作工程におけるリードフレームの断面を示す要部断面図である。

【図13】(a)および(b)はそれぞれ、図11および図12に続く、図11(a)および(b)と同じ個所の要部平面図である。

10

20

30

40

50

【図14】図11および図12に続く、図12と同じ箇所の要部断面図である。

【図15】(a)および(b)はそれぞれ、図13および14に続く、図11(a)および(b)と同じ箇所の要部平面図である。

【図16】図13および図14に続く、図12と同じ箇所の要部断面図である。

【図17】(a)および(b)はそれぞれ、図15および16に続く、図11(a)および(b)と同じ箇所の要部平面図である。

【図18】図15および図16に続く、図12と同じ箇所の要部断面図である。

【図19】(a)および(b)はそれぞれ、図17および18に続く、図11(a)および(b)と同じ箇所の要部平面図である。

【図20】図17および図18に続く、図12と同じ箇所の要部断面図である。

10

【図21】(a)および(b)はそれぞれ、図19および20に続く、図11(a)および(b)と同じ箇所の要部平面図である。

【図22】図19および図20に続く、図12と同じ箇所の要部断面図である。

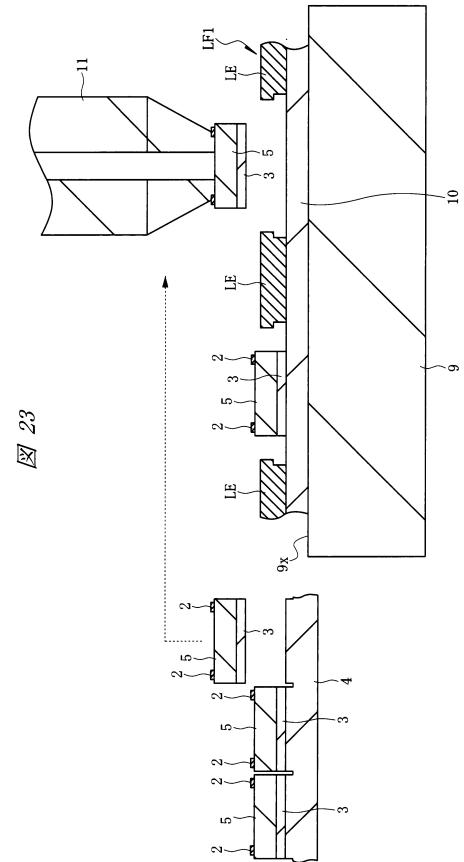

【図23】一実施の形態によるダイボンディング工程における半導体装置の要部断面図である。

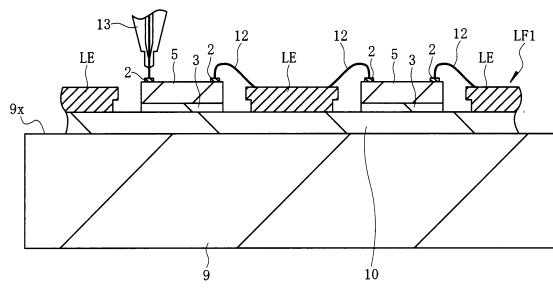

【図24】一実施の形態によるワイヤボンディング工程における半導体装置の要部断面図である。

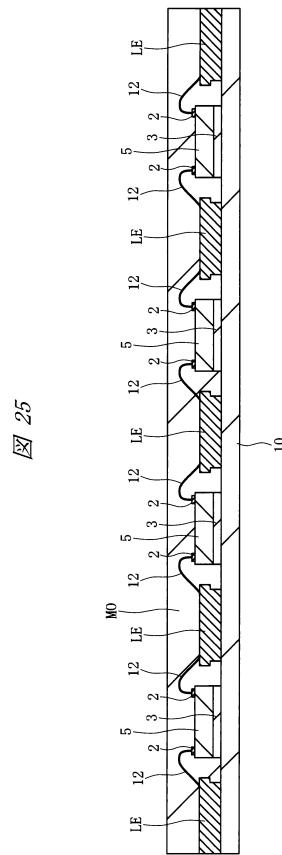

【図25】一実施の形態によるモールド工程における半導体装置の要部断面図である。

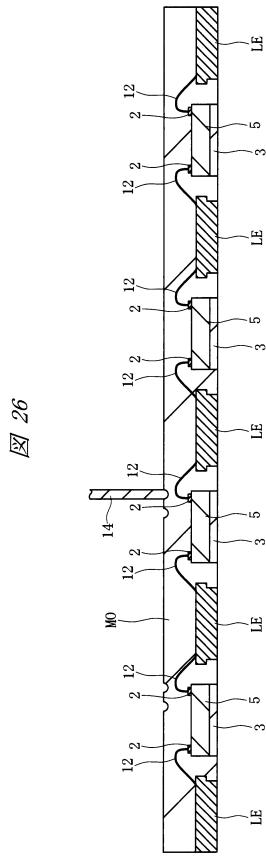

【図26】一実施の形態によるレーザーマーク工程における半導体装置の要部断面図である。

20

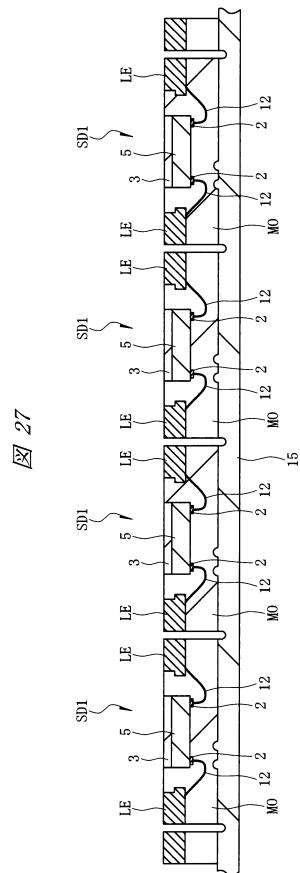

【図27】一実施の形態によるパッケージダイシング工程における半導体装置の要部断面図である。

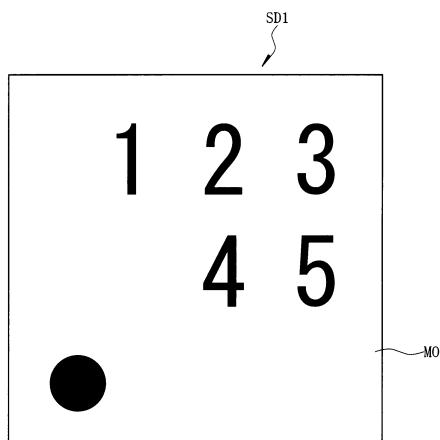

【図28】一実施の形態による半導体装置の表面を示す要部平面図である。

【図29】一実施の形態による半導体装置の裏面を示す要部平面図である。

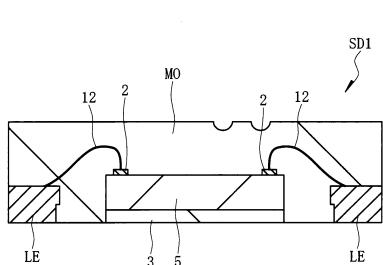

【図30】一実施の形態による半導体装置の断面を示す要部断面図である。

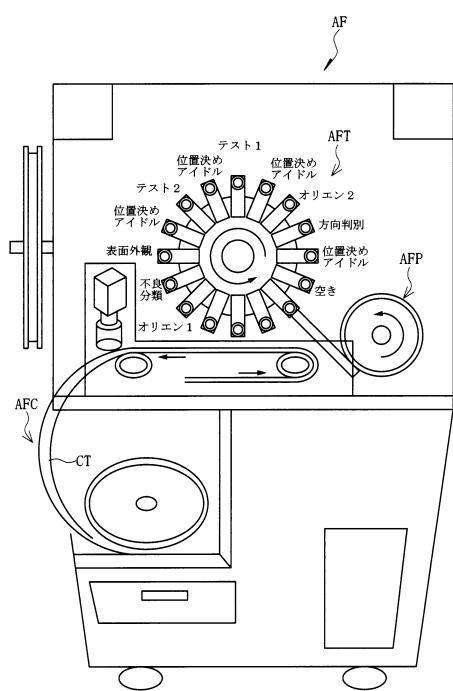

【図31】一実施の形態による自動部品供給装置を説明する概略図である。

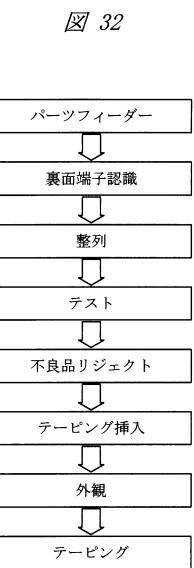

【図32】一実施の形態によるパーツフィーダー方式の特性選別を説明する工程図である。

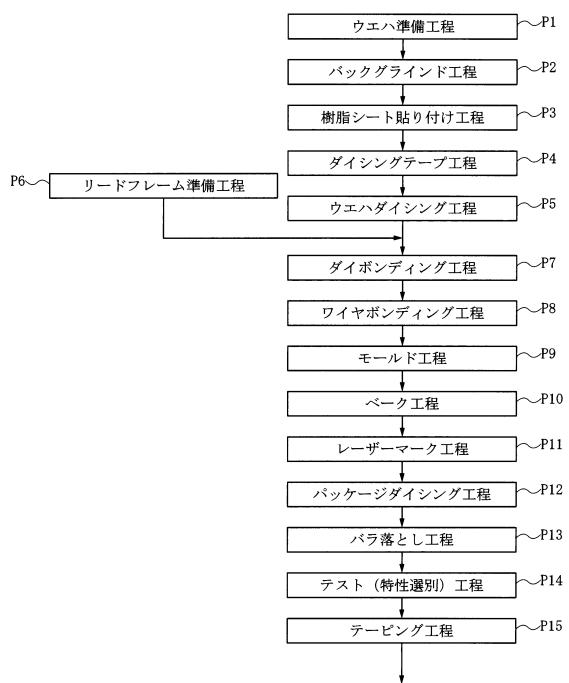

【図33】一実施の形態による半導体装置の製造方法を説明する工程図である。

【図34】一実施の形態の第1変形例によるリードフレームの表面を示す要部平面図である。

30

【図35】一実施の形態の第1変形例によるリードフレームの裏面を示す要部平面図である。

【図36】一実施の形態の第2変形例による半導体装置の断面を示す要部断面図である。

【図37】一実施の形態の第2変形例による半導体装置の裏面を示す要部平面図である。

【図38】一実施の形態の第3変形例による半導体装置の裏面を示す要部平面図である。

【図39】一実施の形態の第3変形例による半導体装置の1番目のインデックスが付されたリード(1pin)が配置された外側側面を示す要部側面図である。

【図40】一実施の形態の第3変形例による半導体装置の最終番目のインデックスが付されたリードが配置された外側側面を示す要部側面図である。

40

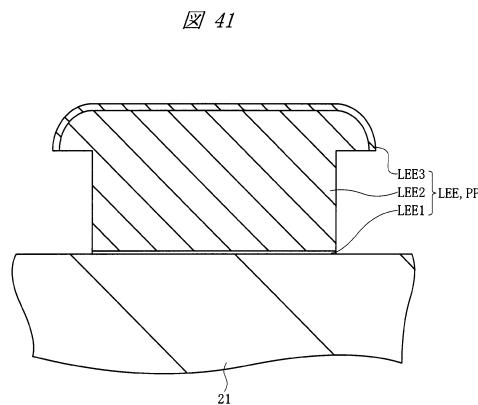

【図41】一実施の形態の第3変形例による1個のリードを拡大して示すリードの要部断面図である。

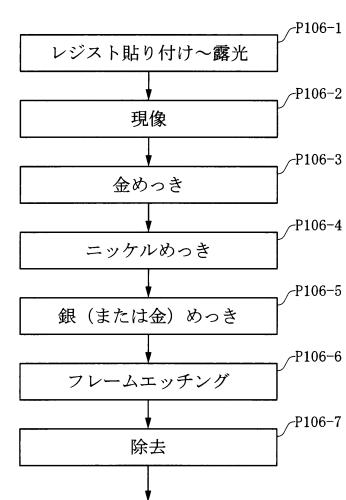

【図42】一実施の形態の第3変形例による複数のリードを有する基材の製造方法を説明する工程図である。

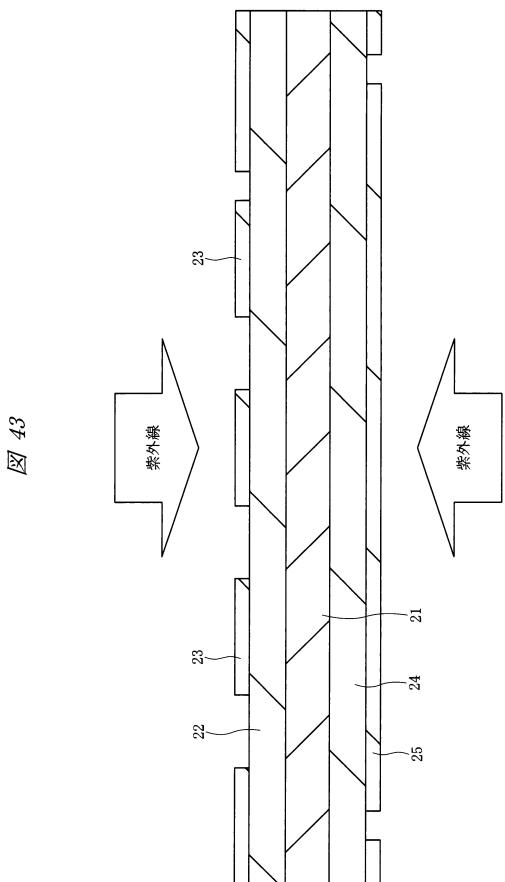

【図43】一実施の形態の第3変形例による複数のリードを有する基材の製造方法を説明する製造工程中における基材の要部断面図である。

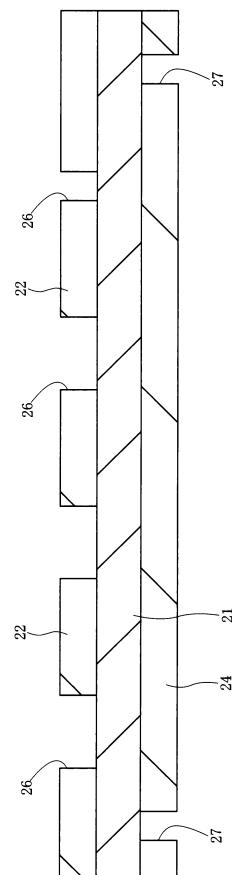

【図44】図43に続く、図43と同じ箇所の要部断面図である。

【図45】図44に続く、図43と同じ箇所の要部断面図である。

【図46】図45に続く、図43と同じ箇所の要部断面図である。

【図47】図46に続く、図43と同じ箇所の要部断面図である。

50

【図48】図47に続く、図43と同じ箇所の要部断面図である。

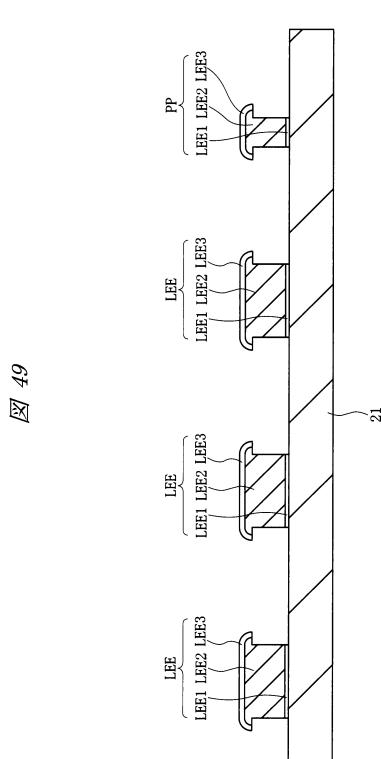

【図49】図48に続く、図43と同じ箇所の要部断面図である。

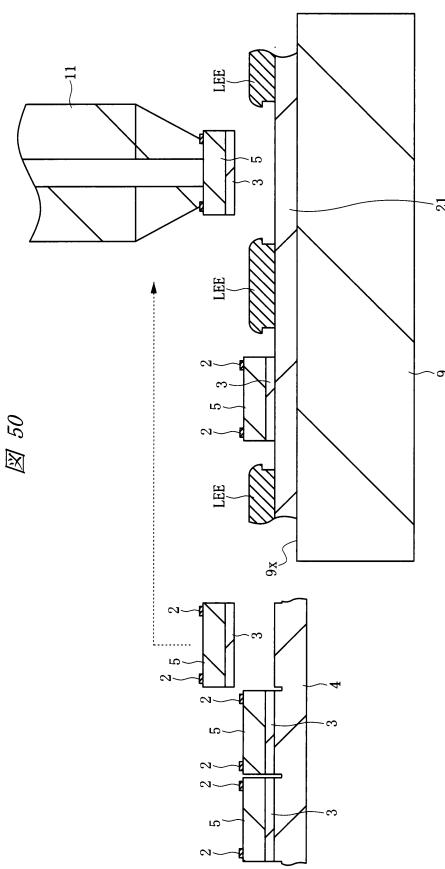

【図50】一実施の形態の第3変形例によるダイボンディング工程における半導体装置の要部断面図である。

【図51】一実施の形態の第3変形例によるワイヤボンディング工程における半導体装置の要部断面図である。

【図52】一実施の形態の第3変形例によるモールド工程における半導体装置の要部断面図である。

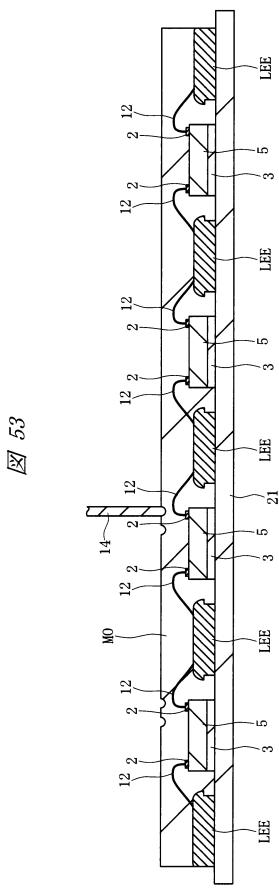

【図53】一実施の形態の第3変形例によるレーザーマーク工程における半導体装置の要部断面図である。

10

【図54】一実施の形態の第3変形例によるパッケージダイシング工程における半導体装置の要部断面図である。

【図55】一実施の形態の第3変形例による半導体装置の裏面を示す要部平面図である。

【図56】一実施の形態の第3変形例による半導体装置の断面を示す要部断面図である。

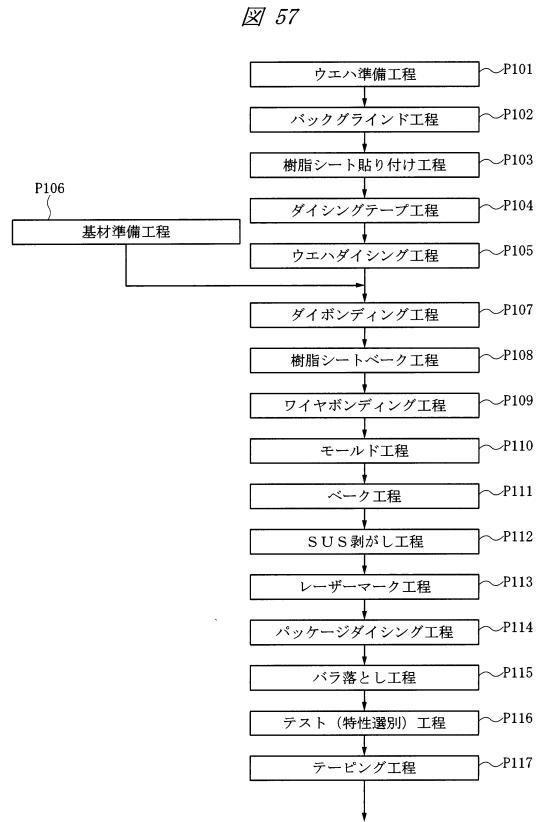

【図57】一実施の形態の第3変形例による半導体装置の製造方法を説明する工程図である。

【図58】本発明者らによって検討されたQFNの一例であるタブレスパッケージの裏面の要部平面図である。

【図59】本発明者らによって検討されたQFNの一例であるタブレスパッケージの第1変形例の裏面の要部平面図である。

20

【図60】本発明者らによって検討されたQFNの一例であるタブレスパッケージの第2変形例の裏面の要部平面図である。

【図61】本発明者らによって検討されたQFNの他の例であるタブ有りパッケージの裏面の要部平面図である。

#### 【発明を実施するための形態】

##### 【0014】

以下の実施の形態において、便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。

##### 【0015】

30

また、以下の実施の形態において、要素の数等（個数、数値、量、範囲等を含む）に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良い。さらに、以下の実施の形態において、その構成要素（要素ステップ等も含む）は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

##### 【0016】

40

また、以下の実施の形態において、タブレスパッケージとは、半導体チップを搭載する基材（タブ、アイランド）がなく、半導体チップを封止する樹脂封止体の裏面（下面、底面）に上記基材が露出しない樹脂パッケージを言う。

##### 【0017】

また、以下の実施の形態で用いる図面においては、平面図であっても図面を見易くするためにハッチングを付す場合もある。また、以下の実施の形態を説明するための全図において、同一機能を有するものは原則として同一の符号を付し、その繰り返しの説明は省略する。以下、本実施の形態を図面に基づいて詳細に説明する。

##### 【0018】

（詳細な課題）

50

リードフレームに搭載された半導体チップを樹脂からなる封止体によって封止した半導体パッケージの一種にQFN (Quad Flat Non-leaded package) がある。

【0019】

QFNは、封止体の中央部に半導体チップを配置し、半導体チップの周囲に複数のリードを配置し、封止体の内部において半導体チップの表面に形成された複数の電極パッドと複数のリードの表面とを複数のボンディングワイヤを介してそれぞれ電気的に接続し、複数のリードの裏面を封止体の裏面から露出する構造となっている。そして、封止体の裏面から露出した複数のリードのそれぞれの裏面を配線基板の電極（フットプリント）に半田付けすることによって、半導体パッケージは実装される。このQFNは、複数のリードが封止体の側面から横方向に延びるQFP (Quad Flat Package) に比べて、実装面積が小さくなるという利点を備えている。

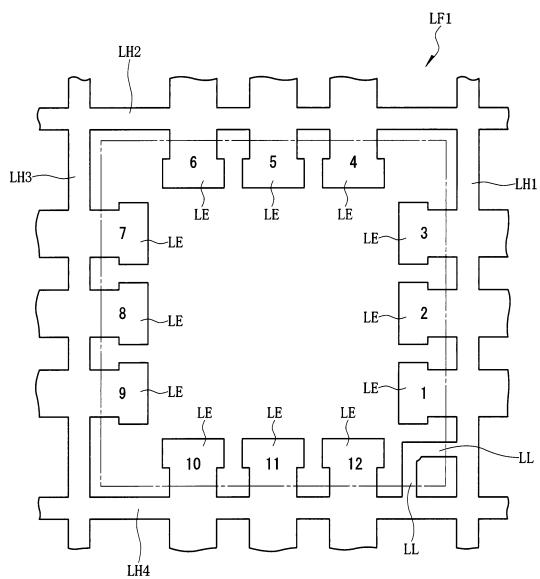

【0020】

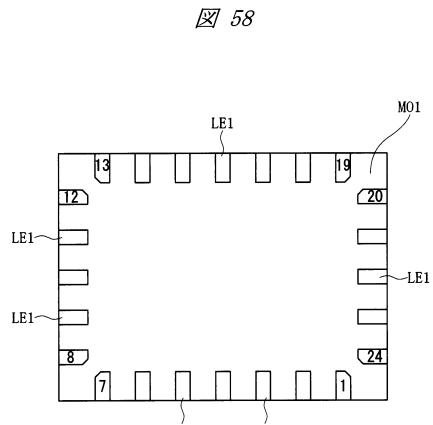

図58に、QFNの一例であるタブレスパッケージの裏面の要部平面図を示す。封止体MO1の外周部の裏面には、複数（24個）のリードLE1の裏面がそれぞれ露出している。図58中に示す数字は各リードLE1のインデックス（識別番号、通し番号、指標）であり、インデックス1に該当するリードLE1を「1pin」と言う。

【0021】

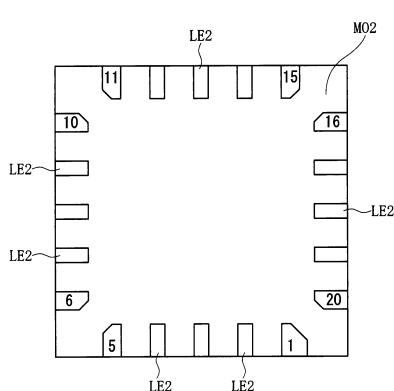

図59に、QFNの一例であるタブレスパッケージの第1変形例の裏面の要部平面図を示す。封止体MO2の外周部の裏面には、複数（20個）のリードLE2の裏面がそれぞれ露出している。前述の図58と同様に、図59中に示す数字は各リードLE2のインデックスであり、インデックス1に該当するリードLE2を「1pin」と言う。

【0022】

封止体MO2から露出した1pinの裏面における封止体MO2の外周に沿った方向の幅が、封止体MO2から露出した他のリードLE2の裏面における封止体MO2の外周に沿った幅よりも大きく形成されている。すなわち、この1pinの封止体MO2の裏面から露する形状は、他のリードLE2の封止体MO2の裏面から露する形状とは相違しており、これにより、1pinを認識することができる。

【0023】

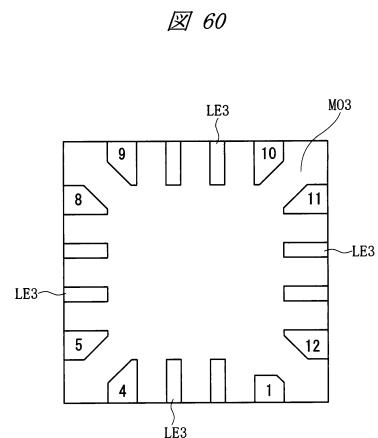

図60に、QFNの一例であるタブレスパッケージの第2変形例の裏面の要部平面図を示す。封止体MO3の外周部の裏面には、複数（16個）のリードLE3の裏面がそれぞれ露出している。前述の図58と同様に、図60中に示す数字は各リードLE3のインデックスであり、インデックス1に該当するリードLE3を「1pin」と言う。

【0024】

封止体MO3から露出した1pinの裏面における封止体MO3の外周に沿った方向と封止体MO3の裏面上で直交する方向の長さが、封止体MO3から露出した他のリードLE3の裏面における封止体MO3の外周に沿った方向と封止体MO3の裏面上で直交する方向の長さよりも短く形成されている。すなわち、この1pinの封止体MO3の裏面から露する形状は、他のリードLE2の封止体MO3の裏面から露する形状とは相違しており、これにより、1pinを認識することができる。

【0025】

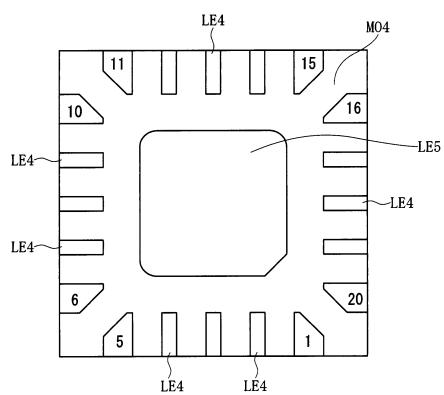

図61に、QFNの他の例であるタブ有りパッケージの裏面の要部平面図を示す。封止体MO4の外周部の裏面には、複数（20個）のリードLE4の裏面がそれぞれ露出している。さらに、封止体MO4の中央部の裏面には、1個の四角形のタブ（アイランド）LE5が露出している。前述の図58と同様に、図61中に示す数字は各リードLE4のインデックスであり、インデックス1に該当するリードLE4を「1pin」と言う。封止体MO4の裏面から露しているタブLE5の1つの角部に切り欠け部を形成することにより、1pinを認識することができる。

【0026】

ところで、このようなパッケージ構造を有する半導体装置の特性選別においては、従来トレイ方式の特性選別またはプローバー方式の特性選別を採用していた。

10

20

30

40

50

**【0027】**

しかしながら、トレイ方式の特性選別は、個々の半導体装置（半導体パッケージ）をトレイに詰めるため、作業に長時間を要していた。また、プローバー方式の特性選別は、品種切り替えなどに時間がかかるためフレキシビリティが不足していた。さらに、トレイ方式の特性選別およびプローバー方式の特性選別では、検査装置による特性選別の後に、別途半導体装置を梱包する梱包装置が必要であった。

**【0028】**

そこで、本発明者らは、パーツフィーダー方式の特性選別の採用を検討した。パーツフィーダー方式の特性選別は、トレイ方式の特性選別よりも作業時間が短縮でき、かつ品種切り替えも容易に行えるという利点を有している。さらに、半導体装置の検査および梱包も一台の装置において連続して行うことができる。10

**【0029】**

ところが、パーツフィーダー方式の特性選別では、ダイシングにより個片化された複数の半導体装置が一旦バラバラになるため、検査時には 1 pin を認識して、半導体装置の向きを揃える必要がある。なお、トレイ方式の特性選別では、ダイシングにより個片化された複数の半導体装置を、例えばコレットを用いて個々にトレイに詰めるため、1 pin の識別は不要であった。また、プローバー方式の特性選別では、ダイシングにより個片化された複数の半導体装置を固定リング（C リング）に貼り付けたまま検査を行うため、1 pin の識別は不要であった。

**【0030】**

しかし、前述の図 58 に示したタプレスパッケージでは、1 pin の認識ができない。20

**【0031】**

また、前述の図 59 および図 60 に示したタプレスパッケージでは、1 pin の認識は可能ではあるが、配線基板の電極を 1 pin の形状に合わせる必要があるため、1 pin の形状を変更するには顧客の許可が必要となる。さらに、前述の図 59 および図 60 に示したタプレスパッケージでは、1 pin の形状変更による面積の増減は数 % 程度であるため、半導体装置のサイズが、例えば 1 辺が 2 mm 程度と小さくなると画像認識が難しくなり、1 pin の正確な認識ができなくなる恐れがあった。

**【0032】**

また、前述の図 61 に示したタブ有りパッケージでも、同様に、半導体装置のサイズが、例えば 1 辺が 2 mm 程度と小さくなると画像認識が難しくなり、1 pin の正確な認識ができなくなる恐れがあった。30

**【0033】**

本実施の形態では、吊りリードにより保持した識別用目印を形成し、この識別用目印を封止体の裏面から露出させることにより、特に、タプレスパッケージにおいて 1 pin の位置認識を容易に行うことができる技術を開示する。

**【0034】**

（実施の形態）

半導体装置

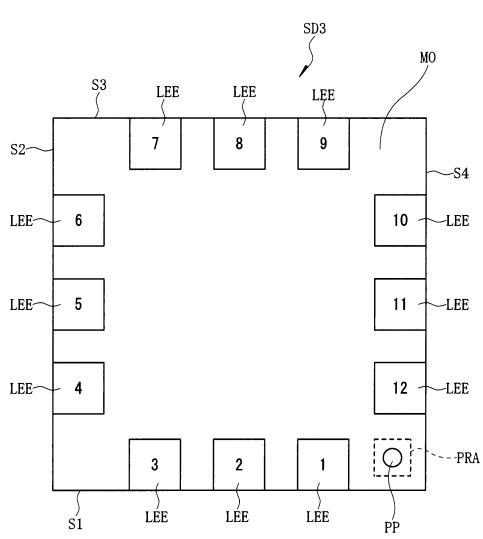

本実施の形態 1 による半導体装置の構造を図 1 ~ 図 3 を用いて説明する。ここでは、1 2 個のリード（外部接続端子、外部端子、端子）を備えるタプレスパッケージを例示する。40

**【0035】**

図 1 は半導体装置の裏面を示す要部平面図、図 2 は半導体装置の 1 pin (インデックス 1 のリード) が配置された外側側面を示す要部側面図、図 3 は半導体装置の最終番目のインデックスが付されたリード (インデックス 12 のリード) が配置された外側側面を示す要部側面図である。

**【0036】**

半導体装置（半導体パッケージ）SD 1 の平面視における形状は四角形であり、表面（上面）、裏面（下面、底面）、および 4 つの側面（第 1 側面 S 1、第 2 側面 S 2、第 3 側50

面 S 3、および第 4 側面 S 4 ) を有する。

【 0 0 3 7 】

半導体装置 S D 1 は、例えば半導体チップ、半導体チップの周囲に設けられた複数のリード (外部接続端子、外部端子、端子) L E 、半導体チップの表面に設けられた複数の電極パッド (ボンディングパッド、表面電極) と複数のリード L E の表面 (上面) とをそれぞれ電気的に接続する複数の導電性ワイヤから構成されている。そして、半導体チップ、複数のリード L E の一部 (表面 (上面) と、側面の一部) 、および複数の導電性ワイヤは樹脂封止体 (封止体) M O によって封止されている。従って、樹脂封止体 M O も平面視における形状は四角形であり、所定の厚さを持って、表面 (上面) 、表面と反対側の裏面 (下面、底面) を有している。

10

【 0 0 3 8 】

図 1 に示すように、樹脂封止体 M O の裏面には、複数のリード L E の裏面 (下面、実装面) が露出する。ここでは 12 個のリード L E を有する半導体装置 S D 1 を例示しているので、樹脂封止体 M O の裏面には 12 個のリード L E の裏面が露出している。樹脂封止体 M O の 4 つの角部のうち、1 つの角部に最も近いリード L E の 1 個をインデックス 1 と定め、これを基準にして、連続して樹脂封止体 M O の外周部の裏面に配置された複数のリード L E に、順次インデックス (識別番号、通し番号、指標) が付けられている。インデックス 1 に該当するリード L E を「 1 p i n 」と言う。

【 0 0 3 9 】

半導体装置 S D 1 では、第 1 側面 S 1 に沿ってインデックス 1 、 2 および 3 のリード L E が配置され、第 2 側面 S 2 に沿ってインデックス 4 、 5 および 6 のリード L E が配置され、第 3 側面 S 3 に沿ってインデックス 7 、 8 および 9 のリード L E が配置され、第 4 側面 S 4 に沿ってインデックス 10 、 11 および 12 のリード L E が配置されている。図 1 中にリード L E と重ねて付した数字がインデックスである。

20

【 0 0 4 0 】

さらに、 1 p i n に最も近い樹脂封止体 M O の角部には、 1 p i n に隣接して画像認識エリア P R A が設けられており、この画像認識エリア P R A において、樹脂封止体 M O の裏面に識別用目印 P P の裏面 (下面) が露出している。この識別用目印 P P は、後に説明する吊りリードに保持されており、 12 個のリード L E と同一の導電性部材からなる。上記導電性部材は、例えば銅 ( C u ) であり、樹脂封止体 M O の裏面から露出する 12 個のリード L E の裏面および識別用目印 P P の裏面には、例えばパラジウム ( P d ) 膜が形成されている。

30

【 0 0 4 1 】

また、図 2 および図 3 に示すように、樹脂封止体 M O の側面にも、 12 個のリード L E の側面の他部が露出する。図 2 および図 3 中にリード L E と重ねて付した数字がインデックスである。図 2 に示すように、第 1 側面 S 1 にはインデックス 1 、 2 および 3 のリード L E の側面の他部が露出し、図 3 に示すように、第 4 側面 S 4 にはインデックス 10 、 11 および 12 のリード L E の側面の他部が露出する。また、側面図は省略するが、第 1 側面 S 1 および第 4 側面 S 4 と同様に、第 2 側面 S 2 にはインデックス 4 、 5 および 6 のリード L E の側面の他部が露出し、第 3 側面 S 3 にはインデックス 7 、 8 および 9 のリード L E の側面の他部が露出する。

40

【 0 0 4 2 】

さらに、上記識別用目印 P P を保持する吊りリード L L は、 1 p i n が露出する樹脂封止体 M O の第 1 側面 S 1 に露出しており、 1 p i n の傍に 1 p i n と離間して位置する。同様に、上記識別用目印 P P を保持する吊りリード L L は、第 4 側面 S 4 にも露出しており、最終番目のインデックスが付されたリード L E (インデックス 12 のリード L E ) の傍に、このリード L E と離間して位置する。

【 0 0 4 3 】

識別用目印 P P は、画像認識により検知することができる。画像認識では、画像を 2 値化することにより識別用目印 P P の有無を判断する。例えば半導体装置 S D 1 の裏面の複

50

数のリード L E が形成されていない四隅の領域（画像認識エリア P R A およびこれと同一面積を有する他の三隅の領域）を抜き出して画像認識を行い、ピクセルの違いを判断する。ピクセルの違いが 15 % 以上あれば、反射の有るところ（識別用目印 P P の有るところ）と反射の無いところ（識別用目印 P P の無いところ）を判断することが可能であるので、画像認識において画像処理する領域（画像認識エリア P R A ）に対する識別用目印 P P の平面面積は 15 % 以上とすることが好ましい。

#### 【 0 0 4 4 】

このように、1 p i n の傍に識別用目印 P P を設けることにより、1 p i n の位置識別が容易となる。従って、1 p i n を認識して半導体装置 S D 1 の向きを揃えることができる、半導体装置 S D 1 の検査において、パーツフィーダー方式の特性選別を採用することができる。

10

#### 【 0 0 4 5 】

##### 半導体装置の製造方法

次に、本実施の形態による半導体装置の製造方法を図 4 ~ 図 3 3 を用いて工程順に説明する。ここでは、12 個のリード（外部接続端子、外部端子、端子）を備えるタブレスパッケージを例示する。

#### 【 0 0 4 6 】

図 4 ~ 図 7 は半導体装置の製造方法を説明する製造工程中における半導体装置の要部断面図である。図 8 はリードフレームの表面を示す要部平面図、図 9 はリードフレームの裏面を示す要部平面図である。図 10 ~ 図 2 2 はリードフレームの製作工程を説明する図である。図 2 3 ~ 図 2 7 は半導体装置の製造方法を説明する製造工程中における半導体装置の要部断面図である。図 2 8 は半導体装置の表面を示す要部平面図、図 2 9 は半導体装置の裏面を示す要部平面図、図 3 0 は半導体装置の断面を示す要部断面図である。図 3 1 は自動部品供給装置を説明する概略図である。図 3 2 はパーツフィーダー方式の特性選別を説明する工程図である。図 3 3 は半導体装置の製造方法を説明する工程図である。

20

#### 【 0 0 4 7 】

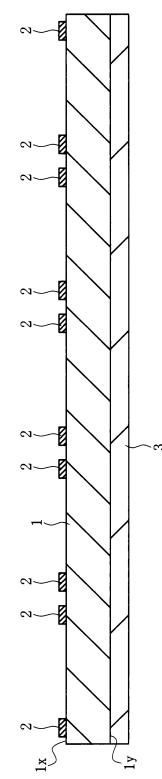

##### < ウエハ準備工程 P 1 >

図 4 に示すように半導体ウエハ 1 を準備する。半導体ウエハ 1 は単結晶シリコンからなり、その直径は、例えば 200 mm または 300 mm、その厚さ（第 1 の厚さ）は、例えば 0.7 mm 以上（製造工程への投入時の値）である。半導体ウエハ 1 は、第 1 主面（表面）1 x、第 1 主面 1 x にマトリックス状に区画形成された複数のチップ領域 1 C A、複数のチップ領域 1 C A のうちの互いに隣り合うチップ領域 1 C A 間に形成された切断領域（スクライブ領域、ダイシング領域、ダイシングライン）1 S A、および第 1 主面 1 x とは反対側の第 2 主面（裏面）1 y を有している。

30

#### 【 0 0 4 8 】

半導体ウエハ 1 の第 1 主面 1 x の各チップ領域 1 C A には、これに限定されないが、複数の半導体素子と、絶縁層と配線層とをそれぞれ複数段積み重ねた多層配線層と、この多層配線層を覆うようにして形成された表面保護膜とから構成される集積回路が形成されている。上記絶縁層は、例えば酸化シリコン（SiO<sub>2</sub>）膜で形成されている。上記配線層は、例えばアルミニウム（Al）、タンゲステン（W）、または銅などの金属膜で形成されている。上記表面保護膜は、例えば酸化シリコン膜または窒化シリコン（Si<sub>3</sub>N<sub>4</sub>）膜等の無機絶縁膜および有機絶縁膜を積み重ねた多層膜で形成されている。また、半導体ウエハ 1 の第 1 主面 1 x の各チップ領域 1 C A には、上記複数の半導体素子と電気的に接続された複数の電極パッド（ボンディングパッド、表面電極）2 が各チップ領域 1 C A の各辺に沿って配置されている（図 4 には、複数の電極パッド 2 のうちの一部を記載）。これら複数の電極パッド 2 は、上記多層配線層のうちの最上層の配線からなり、上記表面保護膜にそれぞれの電極パッド 2 に対応して形成された開口部により露出している。

40

#### 【 0 0 4 9 】

##### < バックグラインド工程 P 2 >

半導体ウエハ 1 の第 1 主面 1 x 側に集積回路を覆う保護テープ（バックグラインドテー

50

プ)を貼り付けた後、半導体ウエハ1の第2主面1yを、研削材(例えば粗さ360)を用いて粗研削することにより、半導体ウエハ1の厚さを所定の厚さまで薄くする。続いて半導体ウエハ1の第2主面1yを、先に使用した研削材よりも目の粗さが細かい研削材(例えば粗さ1500または2000)を用いて仕上げ研削することにより、粗研削時に生じた半導体ウエハ1の第2主面1yの歪みを除去する(バックグラインド)。さらに、仕上げ研削時に生じた半導体ウエハ1の第2主面1yの研磨スジを、例えばスピンドルチ法、CMP(Chemical Mechanical Polishing)法などにより除去する(ストレスリリーフ)。上記バックグラインドおよび上記ストレスリリーフを終えた時点での半導体ウエハ1の厚さ(第2の厚さ)は、例えば0.13mmである。なお、上記ストレスリリーフは全ての半導体ウエハ1に対して行う必要はなく、半導体チップに要求される強度に応じて行う。

#### 【0050】

<樹脂シート貼り付け工程P3>

図5に示すように、半導体ウエハ1の第2主面1yに、フィルム状の樹脂シート(接着シート、接着フィルム、封止材)3を貼り付ける。樹脂シート3は、半導体装置SD1として完成した後において、半導体チップの裏面を保護する封止材として機能する。樹脂シート3は、例えば熱硬化型であり、フィラー(SiO<sub>2</sub>の粒)を含有するエポキシ系樹脂からなる。その厚さは、例えば20~30μmであり、25μmを中心値とする周辺範囲が好適である。また、そのフィラー含有量は、例えば60wt%である。その後、樹脂シート3が貼り付けられた半導体ウエハ1に対して熱処理を施す。

#### 【0051】

<ダイシングテープ工程P4>

図6に示すように、ダイシングテープ4を準備する。なお、図示はしないが、ダイシングテープ4の周縁部には、平面視において環状のフレームが貼り付けられている。ダイシングテープ4は、例えばポリオリフィンを基材とし、その厚さは、例えば90μmである。また、ダイシングテープ4の上面(半導体ウエハ1が固定される面)には、図示はしないが、接着層が形成されている。接着層は、例えばアクリル系UV硬化型の粘着剤であり、例えばUV照射前は200g/25mm、UV照射後は10~20g/25mmの粘着力を有している。

#### 【0052】

次に、ダイシングテープ4の上面と半導体ウエハ1の第2主面1yとを対向させて、両者を樹脂シート3を介して貼り付ける。これにより、ダイシングテープ4の上面に、樹脂シート3を介して半導体ウエハ1が固定される。

#### 【0053】

<ウエハダイシング工程P5>

図7に示すように、例えばダイヤモンド微粒を貼り付けた極薄の円形刃を用いて、半導体ウエハ1を切断領域1SAに沿って縦、横に切断する。同時に、樹脂シート3も半導体ウエハ1の切断領域1SAに沿って縦、横に切断する。半導体ウエハ1は半導体チップ5に個片化されるが、個片化された後も半導体チップ5はダイシングテープ4を介してフレームに固定されているため、整列した状態を維持している。また、前の製造工程である樹脂シート貼り付け工程P3において、半導体ウエハ1の第2主面1yに樹脂シート3が強く接着されているので、半導体チップ5が樹脂シート3から剥がれて、半導体チップ5の飛散等の問題も生じることはない。

#### 【0054】

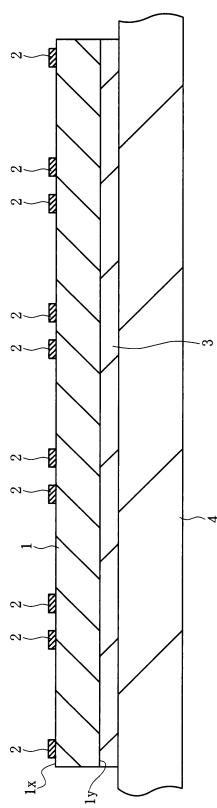

<リードフレーム準備工程P6>

図8および図9に示すように、リードフレームLF1を準備する。リードフレームLF1は、表面(上面)、表面と反対側の裏面(下面)とを有し、例えば銅などの導電性部材からなる。リードフレームLF1は、半導体製品1つ分に該当し、チップ搭載領域を囲む四角形の保持枠(保持部)に12個のリードLEおよび吊りリードLLを有する単位フレームが複数配列した構成となっている。図8および図9には単位フレームに該当するリードフレームLF1を示す。

10

20

30

40

50

ドフレームLF1の一部を示している。

【0055】

チップ搭載領域を囲む保持枠は、互いに離間して第1方向に延在する2つの第1保持部LH1と第3保持部LH3、互いに離間して第1方向と直交する第2方向に延在する2つの第2保持部LH2と第4保持部LH4により構成される。そして、単位フレームの中央部(チップ搭載領域)を囲むように、12個のリードLEが配置されている。12個のリードLEには、インデックス(識別番号、通し番号、指標)が付けられており、単位フレームの1つの角部を選択し、この角部に最も近いリードLEの1つをインデックス1と定める。そして、これを基準として、連続して単位フレームの周囲に配置されたリードLEに、順次インデックスが付けられている。インデックス1に該当するリードLEが、前述したように「1pin」である。図8および図9中にリードLEと重ねて付した数字がインデックスである。

【0056】

また、これら12個のリードLEは第1保持部LH1、第2保持部LH2、第3保持部LH3、または第4保持部LH4に連結保持されている。例えば、インデックス1、2、および3に該当するリードLEは第1保持部LH1に連結保持され、インデックス4、5、および6に該当するリードLEは第2保持部LH2に連結保持され、インデックス7、8、および9に該当するリードLEは第3保持部LH3に連結保持され、インデックス10、11、および12に該当するリードLEは第4保持部LH4に連結保持されている。

【0057】

さらに、吊りリードLLは、第1方向に沿って延在する第1部分と、第2方向に沿って延在する第2部分とから構成される。吊りリードLLの第2部分の一端は第1保持部LH1と第4保持部LH4とが交差する角部とインデックス1のリードLE(1pin)との間の第1保持部LH1に連結し、吊りリードLLの第1部分の一端は上記角部とインデックス12のリードLE(最終番目のインデックスが付されたリードLE)との間の第4保持部LH4とに連結する。そして、吊りリードLLの第1部分の他端と吊りリードLLの第2部分の他端とが識別用目印PPを保持している。

【0058】

リードフレームLF1の表面は平坦であるが、リードフレームLF1の裏面の一部には、リードフレームLF1を厚さを約半分の厚さに加工するハーフエッチングが施されており(例えば図9に示すハッチングを付した部分)、リードフレームLF1の裏面は平坦ではない。リードフレームLF1のハーフエッチングが施されていない部分の厚さは、例えば0.125mmである。

【0059】

12個のリードLEにおいては、後のモールド工程において、樹脂封止体の裏面から露出するリードLEの一部を除いて、リードLEの裏面側からハーフエッチングが施されている。ハーフエッチングが施されたリードLEの他部は、後のモールド工程において、樹脂封止体により封止される。その厚さは、例えば0.065mmである。

【0060】

また、第1保持部LH1と第4保持部LH4とに繋がる吊りリードLLでは、吊りリードLLの裏面側からハーフエッチングが施されている。この吊りリードLLに保持され、ハーフエッチングが施されていない導電性部材が、後のモールド工程において、その裏面が樹脂封止体の裏面から露出する識別用目印PPとなる。ハーフエッチングが施された吊りリードLLは、後のモールド工程において、樹脂封止体により封止される。その厚さは、例えば0.065mmである。

【0061】

また、保持部においては、第1保持部LH1と第2保持部LH2とが交差する角部、第2保持部LH2と第3保持部LH3とが交差する角部、第3保持部LH3と第4保持部LH4とが交差する角部、第4保持部LH4と第1保持部LH1とが交差する角部を除いて、第1保持部LH1、第2保持部LH2、第3保持部LH3、および第4保持部LH4に

10

20

30

40

50

は、これらの裏面側からハーフエッティングが施されている。ハーフエッティングが施された第1保持部LH1、第2保持部LH2、第3保持部LH3、および第4保持部LH4の厚さは、例えば0.065mmである。

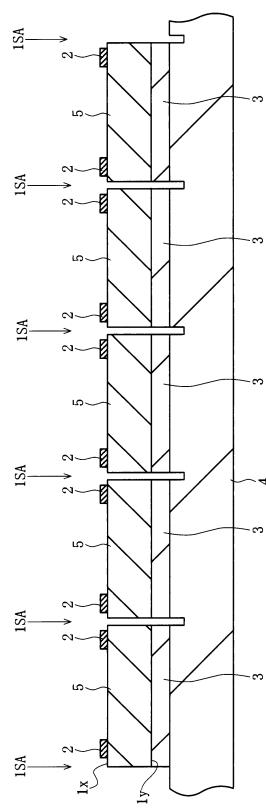

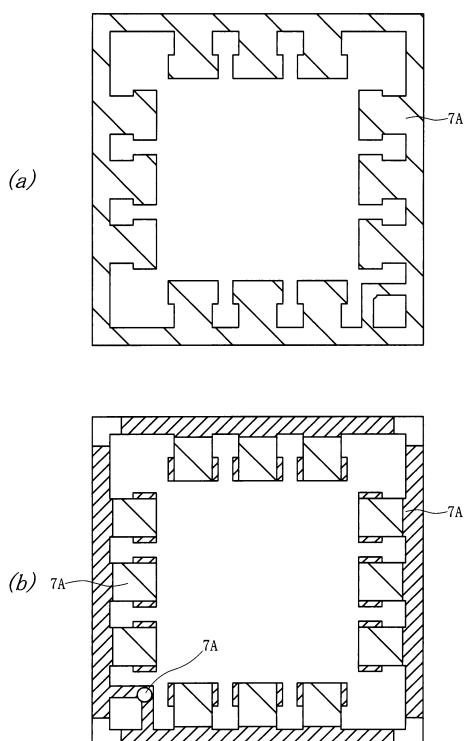

#### 【0062】

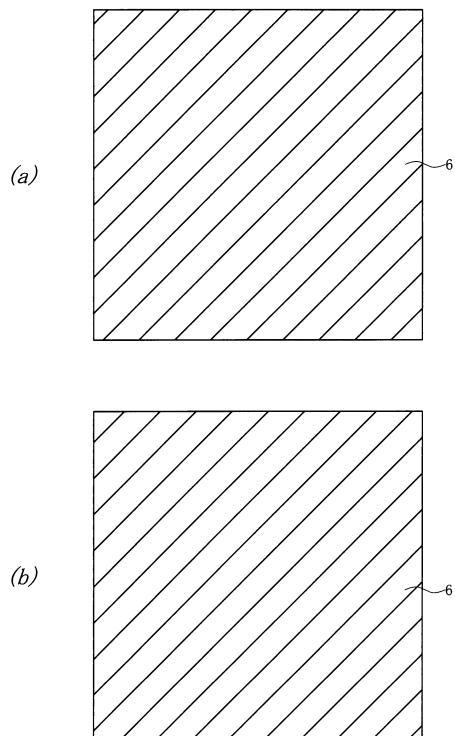

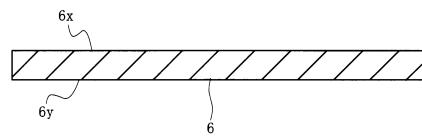

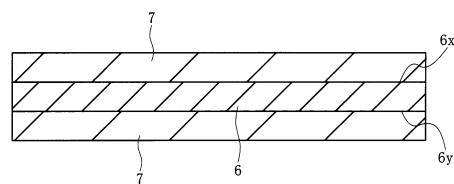

次に、リードフレームLF1の製作工程について図10～図22を用いて説明する。図10はリードフレームLF1の製作方法を説明する工程図である。図11(a)、図13(a)、図15(a)、図17(a)、図19(a)、および図21(a)はリードフレームLF1の表面を示す要部平面図、図11(b)、図13(b)、図15(b)、図17(b)、図19(b)、および図21(b)はリードフレームLF1の裏面を示す要部平面図である。図12、図14、図16、図18、図20、および図22はリードフレームLF1の断面を示す要部断面図である。

10

#### 【0063】

- ・P6-(1)銅生材準備工程

図11および図12に示すように、導電性部材、例えば銅生材6を準備する。銅生材6は、表面(上面)6xと、表面6xと反対側の裏面(下面)6yとを有し、その厚さは、例えば0.125mmである。

#### 【0064】

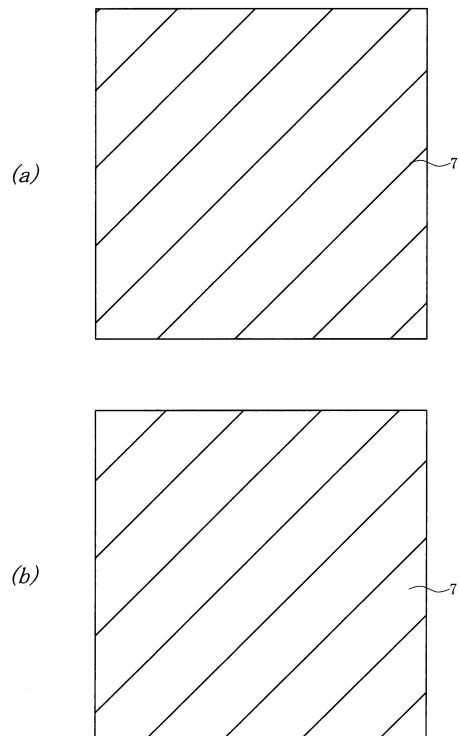

- ・P6-(2)レジスト塗布工程

図13および図14に示すように、銅生材6の表面6xおよび裏面6yにそれぞれレジスト膜7を塗布する。

20

#### 【0065】

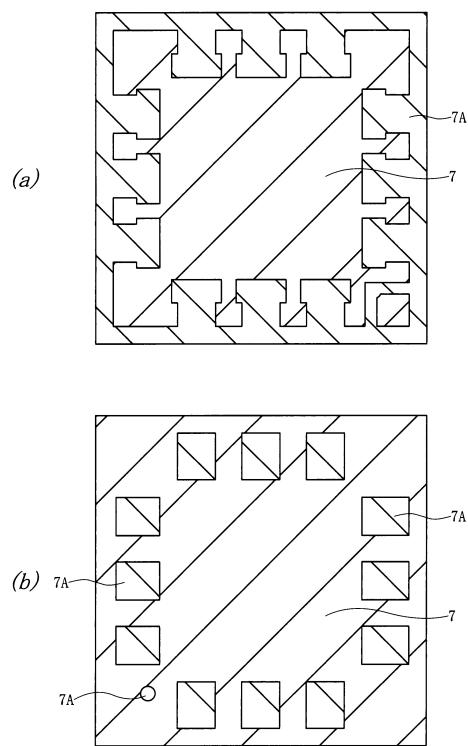

- ・P6-(3)露光工程

図15および図16に示すように、レジスト膜7を残す領域(リードフレームが形成される領域)に銅生材6の表面6x側および裏面6y側からそれぞれ露光(UV(Ultra Violet)光)を照射して、レジスト膜7を硬化させる。図16中、レジスト膜7の硬化部分を符号7Aで示す。

#### 【0066】

- ・P6-(4)現像工程

図17および図18に示すように、レジスト膜7, 7Aに現像処理を施して、硬化したレジスト膜7Aを銅生材6の表面6xおよび裏面6yに残す。銅生材6の表面6xに形成されたレジスト膜7Aの形状と、銅生材6の裏面6yに形成されたレジスト膜7Aの形状とは互いに異なっている。その異なる領域がハーフエッティングが施される領域となる。

30

#### 【0067】

すなわち、銅生材6の表面6x側から透視したときに、銅生材6の表面6xに形成されたレジスト膜7Aが覆う領域は、銅生材6の裏面6yに形成されたレジスト膜7Aが覆う領域よりも広いが、銅生材6の裏面6yに形成されたレジスト膜7Aが覆う領域は全て銅生材6の表面6xに形成されたレジスト膜7Aが覆う領域と重なる。

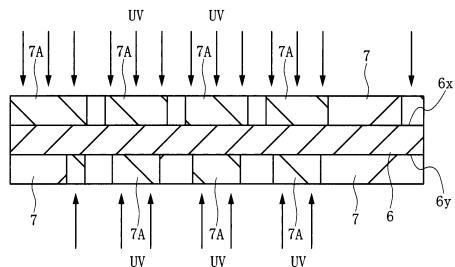

#### 【0068】

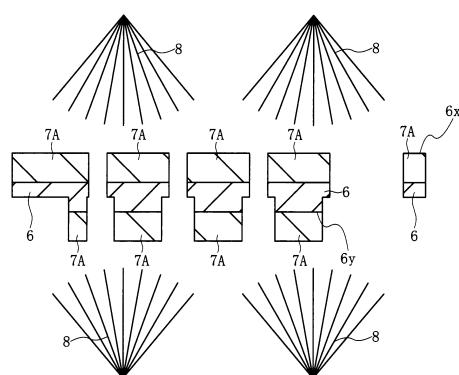

- ・P6-(5)エッティング工程

図19および図20に示すように、銅生材6の表面6x側および裏面6y側からそれぞれ溶解液8を銅生材6にスプレーして、レジスト膜7Aに覆われていない銅生材6をエッティングする。表面6xおよび裏面6yともにレジスト膜7Aが形成されていない領域の銅生材6は厚さ方向に全てエッティングされる。一方、表面6xにはレジスト膜7Aは形成されているが裏面6yにはレジスト膜7Aが形成されていない領域の銅生材6は、裏面6yから厚さ方向に約半分がエッティング(ハーフエッティング)される。

40

#### 【0069】

すなわち、銅生材6の表面6x側から透視したときに、銅生材6の表面6xに形成されたレジスト膜7Aと銅生材6の裏面6yに形成されたレジスト膜7Aとが重なっている領域では、銅生材6はエッティングされない。しかし、銅生材6の表面6x側から透視したときに、銅生材6の表面6xにレジスト膜7Aは形成されているが、銅生材6の裏面6yに

50

レジスト膜 7 A は形成されていない領域では、銅生材 6 は表面 6 x 側に一部を残して、裏面 6 y 側から厚さ方向にエッティングされる。

【 0 0 7 0 】

従って、識別用目印 P P が形成される領域では、銅生材 6 の表面 6 x 側から透視したときに、銅生材 6 の表面 6 x に形成されたレジスト膜 7 A と銅生材 6 の裏面 6 y に形成されたレジスト膜 7 A とが重なっており、銅生材 6 はエッティングされない。しかし、吊りリード L L が形成される領域では、銅生材 6 の表面 6 x 側から透視したときに、銅生材 6 の表面 6 x にレジスト膜 7 A は形成されているが、銅生材 6 の裏面 6 y にレジスト膜 7 A は形成されておらず、銅生材 6 は表面 6 x 側に一部を残して、裏面 6 y 側から厚さ方向にエッティングされる。

10

【 0 0 7 1 】

・ P 6 - ( 6 ) 剥離工程

図 2 1 および図 2 2 に示すように、レジスト膜 7 A を除去することにより、リードフレーム L F 1 が完成する。

【 0 0 7 2 】

なお、本実施の形態では、平面視における識別用目印 P P の形状を円形としたが、これに限定されるものではなく、例えば四角形であってもよい。

【 0 0 7 3 】

次に、リードフレーム L F 1 にめっき処理を施して、リードフレーム L F 1 の表面および裏面に、例えばパラジウム膜（図示は省略）をめっき法により形成する。

20

【 0 0 7 4 】

< ダイポンディング工程 P 7 >

ダイシングテープ 4 の下面側から紫外線を照射して、ダイシングテープ 4 の上面に形成された接着層の接着力を、例えば 10 ~ 20 g / 25 mm 程度に低下させることにより、接着層を硬化させる。これにより、各半導体チップ 5 がダイシングテープ 4 から剥がれやすくなる。

【 0 0 7 5 】

次に、図 2 3 に示すように、リードフレーム L F 1 の裏面と、熱源を有するヒートステージ 9 の表面（上面）9 x とを対向させて、ヒートステージ 9 の表面 9 x 上にフレームテープ 1 0 を介してリードフレーム L F 1 を配置する。ヒートステージ 9 は、例えばステンレス（SUS 430）などの導電性部材から成り、例えば 40 ~ 80 °C に加熱されている。

30

【 0 0 7 6 】

次に、半導体チップ 5 の表面を円筒コレット 1 1 によって吸着し、保持した後、半導体チップ 5 をダイシングテープ 4 から引き剥がしてピックアップする。ダイシングテープ 4 の上面に形成された接着層の接着力が弱められているので、薄く強度が低下している半導体チップ 5 であっても確実にピックアップすることができる。半導体チップ 5 の裏面には、樹脂シート 3 が接着している。

【 0 0 7 7 】

次に、ピックアップされた半導体チップ 5 は、フレームテープ 1 0 の所定のチップ搭載領域に搬送される。続いて、半導体チップ 5 の裏面に接着している樹脂シート 3 を介して、フレームテープ 1 0 のチップ搭載領域に半導体チップ 5 を配置し、熱（例えば 40 ~ 80 °C）を加えることで、フレームテープ 1 0 のチップ搭載領域に半導体チップ 5 を固定する。

40

【 0 0 7 8 】

< ワイヤポンディング工程 P 8 >

図 2 4 に示すように、半導体チップ 5 の表面の縁辺に配置された複数の電極パッド 2 と、チップ搭載領域の周囲に位置する複数のリード L E の表面とを、例えば熱圧着に超音波振動を併用したネイルヘッドポンディング法（ボールポンディング法）により、複数の導電性ワイヤ 1 2 を用いてそれぞれ電気的に接続する。具体的には、導電性ワイヤ 1 2 の先

50

端をアーク放電により溶融して表面張力でボールを形成し、それをキャピラリ（円筒状の接続治具）13により電極パッド2およびリードL Eの表面に、例えば120kHzの超音波振動を加えながら熱圧着する。

【0079】

また、主として、正ポンディング方式（半導体チップ5の電極パッド2と導電性ワイヤ12の一部を接続した後に、リードL Eと導電性ワイヤ12の他部を接続する方式）を用いるが、逆ポンディング方式（リードL Eと導電性ワイヤ12の一部を接続した後に、半導体チップ5の電極パッド2と導電性ワイヤ12の他部を接続する方式）を用いても良い。

【0080】

<モールド工程P9>

図25に示すように、複数の半導体チップ5が搭載されたリードフレームL F 1およびフレームテープ10を金型成型機にセットし、温度を上げて液状化した封止樹脂を金型成型機に圧送して流しこみ、フレームテープ10の半導体チップ等が搭載された面側を封止樹脂で封入して、1つの樹脂封止体（封止体）MOを形成する。樹脂封止体MOは、低応力化を図ることを目的として、例えばフェノール系硬化剤、シリコーンゴム、および多数のフィラー（例えばシリカ）などが添加されたエポキシ系の熱硬化性絶縁樹脂からなる。

【0081】

<ベーク工程P10>

例えば175の温度で5時間の熱処理（ポストキュアベーク）を施す。この熱処理は、例えばエア（Air）ベークである。これにより、複数の半導体チップ5、複数のリードL Eのそれぞれの一部（表面と、側面の一部）、複数の導電性ワイヤ12、および識別用目印PPの一部（表面（上面）と、側面）などが樹脂封止体MOによって封止される。樹脂封止体MOの厚さは、例えば300μmである。

【0082】

<レーザーマーク工程P11>

図26に示すように、フレームテープ10を除去した後、レーザー14を用いて樹脂封止体MOの上面に品名などを捺印する。

【0083】

<パッケージダイシング工程P13>

図27に示すように、ダイシングテープ15を準備する。続いて、ダイシングテープ15の上面に、複数の半導体チップ5、複数のリードL Eのそれぞれの一部（表面と、側面の一部）、および複数の導電性ワイヤ12などを被覆した樹脂封止体MOを固定する。

【0084】

次に、例えばダイヤモンド微粒を貼り付けた極薄の円形刃を用いて、樹脂封止体MOの裏面側から樹脂封止体MO、複数のリードL E、および吊りリードL Lをスクライプ領域に沿って縦、横に切断する。樹脂封止体MOは半導体装置（半導体パッケージ）SD1に個片化されるが、個片化された後も半導体装置SD1はダイシングテープ15を介して固定されているため、整列した状態を維持している。続いて、樹脂封止体MOを切断する際に発生した屑などを除去するために、半導体装置SD1を洗浄する。

【0085】

<バラ落とし工程P14>

図28～図30に示すように、ダイシングテープ15を除去することにより、個々の半導体装置SD1に分ける。図28に示すように、半導体装置SD1の表面には、レーザマークが印字されている。また、図29に示すように、半導体装置SD1の裏面には、12個のリードL Eのそれぞれの裏面、および半導体チップ5の裏面に貼られた樹脂シート3が露出している。従って、半導体チップ5の裏面は、樹脂シート3に保護されている。また、半導体装置SD1の側面には、12個のリードの側面の一部が樹脂封止体MOから露出している。なお、樹脂シート3は樹脂封止体MOと区別して視認することが難しいため、後述する1pinの位置認識では樹脂シート3は認識されない。

10

20

30

40

50

## 【0086】

個々に分けられた複数の半導体装置 S D 1 は、後の工程において検査され、良品と判断された半導体装置 S D 1 のみが梱包される。本実施の形態では、図 3 1 に示す自動部品供給装置 A F を用いて検査および梱包を行う。従って、複数の半導体装置 S D 1 は、自動部品供給装置 A F のパーツフィーダー部 A F P にバラバラの状態で投入される。パーツフィーダー部 A F P に投入された複数の半導体装置 S D 1 は、自動部品供給装置 A F において、順次検査され（テスト（特性選別）工程 P 1 5）、良品と判断された半導体装置 S D 1 は梱包される（テーピング工程 P 1 6）。

## 【0087】

< テスト（特性選別）工程 P 1 5 >

10

図 3 2 に示すパーツフィーダー方式の特性選別の工程に従って、半導体装置 S D 1 を自動部品供給装置 A F のパーツフィーダー部 A F P から検査部 A F T に搬送し、製品規格に沿って選別する。自動部品供給装置 A F のパーツフィーダー部 A F P にバラバラに投入した複数の半導体装置 S D 1 を一個ずつ自動部品供給装置 A F の検査部 A F T へ搬送する。

## 【0088】

検査部 A F T では、まず、半導体装置 S D 1 の形状および面積を判別して、樹脂封止体 M O から露出している 1 2 個のリード L E および識別用目印 P P を認識し、識別用目印 P P から 1 p i n の位置認識を行う。続いて、1 p i n の位置を基に半導体装置 S D 1 を 90°、180°、または -90° 回転させて、整列させる。続いて、半導体装置 S D 1 のテスト（特性選別）を行う。テストにおいて不良と判断された半導体装置 S D 1 は取り除かれる。

20

## 【0089】

< テーピング工程 P 1 6 >

テストにおいて良と判断された半導体装置 S D 1 を自動部品供給装置 A F のテーピング部 A F C において、キャリアテープ C T に収納する。その後、キャリアテープ C T に収納された半導体装置 S D 1 の外観、例えばレーザマークおよび傷の有無等が検査される。その後、例えばキャリアテープ C T をリールに巻き取り、防湿された袋にリールを収納し、この状態で出荷する。

## 【0090】

このように、本実施の形態 1 によれば、識別用目印 P P により 1 p i n の位置を容易に認識できることから、タブレスパッケージであってもパーツフィーダ方式の特性選別を採用することができる。

30

## 【0091】

（実施の形態の第 1 変形例）

前述した実施の形態では、例えば前述の図 8 および図 9 に示したように、識別用目印 P P は、第 1 方向に延在する第 1 保持部 L H 1 と第 2 方向に延在する第 4 保持部 L H 4 とが交差する角部とインデックス 1 のリード L E ( 1 p i n ) との間の第 1 保持部 L H 1 に連結し、上記角部とインデックス 1 2 のリード L E との間の第 4 保持部 L H 4 に連結した吊りリード L L に保持されている。しかし、第 1 方向に延在する第 1 保持部 L H 1 または第 2 方向に延在する第 4 保持部 L H 4 のどちらか一方に連結する吊りリードによって識別用目印 P P を保持しても良い。

40

## 【0092】

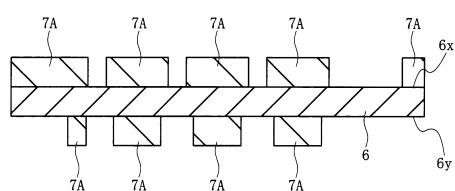

リードフレームの第 1 変形例を図 3 4 および図 3 5 を用いて説明する。図 3 4 はリードフレームの表面を示す要部平面図、図 3 5 はリードフレームの裏面を示す要部平面図である。

## 【0093】

図 3 4 および図 3 5 に示すように、リードフレーム L F 2 は、前述の図 8 および図 9 に示したリードフレーム L F 1 と同様に、第 1 保持部 L H 1 、第 2 保持部 L H 2 、第 3 保持部 L H 3 、および第 4 保持部 L H 4 を有し、単位フレームの中央部（チップ搭載領域）を囲むように、1 2 個のリード L E が配置されている。また、1 2 個のリード L E には、イ

50

ンデックス（識別番号、通し番号、指標）が付けられており、インデックス1に該当するリードL Eが1 p i nである。また、1 p i nの傍に1 p i nと離間して、後のモールド工程において、その裏面が樹脂封止体の裏面から露出する識別用目印P Pが形成されている。図34中に、リードL Eと重ねて付した数字がインデックスである。

【0094】

しかし、このリードフレームL F 2では、識別用目印P Pは、第1保持部L H 1と第4保持部L H 4とが交差する角部とインデックス1のリードL E（1 p i n）との間の第1保持部L H 1のみに繋がる吊りリードL Lに保持されている。すなわち、吊りリードL Lの一端が第1保持部L H 1に連結し、吊りリードL Lの他端が識別用目印P Pを保持している。

10

【0095】

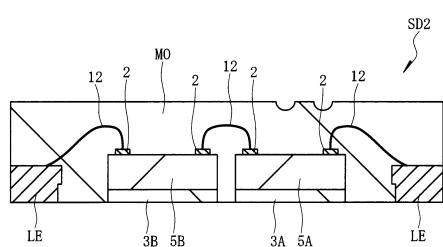

（実施の形態の第2変形例）

前述した実施の形態では、例えば前述の図30に示したように、1個の半導体チップを樹脂封止する構成の半導体装置S D 1を例示したが、2個または3個の半導体チップを樹脂封止する構成の半導体装置にも、本実施の形態は適用することができる。

【0096】

半導体装置の第2変形例の構造を図36および図37を用いて説明する。図36は半導体装置の断面を示す要部断面図、図37は半導体装置の裏面を示す要部平面図である。

【0097】

図36に示すように、半導体装置（半導体パッケージ）S D 2は、2個の半導体チップ5 A, 5 B、半導体チップ5 A, 5 Bのそれぞれの裏面に形成された樹脂シート（接着接着シート、接着フィルム、封止材）3 A, 3 B、半導体チップ5 A, 5 Bの周囲に設けられた複数のリードL E、および半導体チップ5 A, 5 Bのそれぞれの表面に配置された複数の電極パッド（ボンディングパッド）と複数のリードL Eとを電気的に接続する複数の導電性ワイヤ1 2から構成されている。半導体チップ5 A, 5 B、樹脂シート3 A, 3 Bの側面、複数のリードL Eのそれぞれの一部（表面（上面）と、側面の一部）、および複数の導電性ワイヤ1 2は樹脂封止体（封止体）M Oによって封止されている。

20

【0098】

また、図37に示すように、樹脂封止体M Oの下面からは半導体チップ5 A, 5 Bのそれぞれの裏面は露出しておらず、半導体チップ5 A, 5 Bのそれぞれの裏面に接着された樹脂シート3 A, 3 B、複数のリードL Eのそれぞれの他部（裏面（下面、実装面））、および識別用目印P Pの裏面が露出した構造となっている。なお、樹脂シート3は樹脂封止体M Oと区別して視認することが難しいため、1 p i nの位置認識では樹脂シート3は認識されない。

30

【0099】

（実施の形態の第3変形例）

前述した実施の形態では、半導体装置のリード（外部接続端子、外部端子、端子）をリードフレームにより形成したが、電解めっき法により形成したリードを用いても良い。

【0100】

半導体装置

40

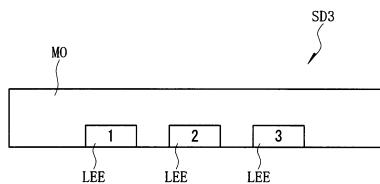

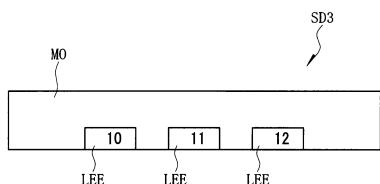

半導体装置の第3変形例の構造を図38～図40を用いて説明する。ここでは、12個の電解めっき法により形成したリード（外部接続端子、外部端子、端子）を備えるタブレスパッケージを例示する。

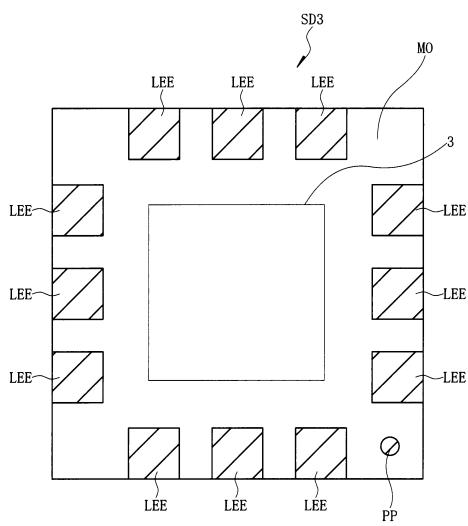

【0101】

図38は半導体装置の裏面を示す要部平面図、図39は半導体装置の1 p i n（インデックス1のリード）が配置された外側側面を示す要部側面図、図40は半導体装置の最終番目のインデックスが付されたリード（インデックス12のリード）が配置された外側側面を示す要部側面図である。

【0102】

図38に示すように、前述の図1に示した半導体装置（半導体パッケージ）S D 1と同

50

様に、電解めっき法により形成したリード L E E を用いた半導体装置（半導体パッケージ）S D 3 も、その裏面（下面、底面）には、複数のリード L E E の裏面（下面、実装面）が露出する。ここでは 12 個のリード L E E を有する半導体装置 S D 3 を例示しているので、樹脂封止体 M O の裏面には 12 個のリード L E E の裏面が露出している。

#### 【0103】

そして、1 p i n に最も近い樹脂封止体 M O の角部には、1 p i n に隣接して画像認識エリア P R A が設けられており、この画像認識エリア P R A において、樹脂封止体 M O の裏面に識別用目印 P P の裏面が露出している。この識別用目印 P P は、複数のリード L E E と同じ製造工程において形成され、12 個のリード L E E と同一の導電性部材からなる。なお、図 3 9 および図 4 0 に示すように、樹脂封止体 M O の側面には、12 個のリード L E E の側面の一部のみが露出する。 10

#### 【0104】

このように、電解めっき法により形成したリードを採用した半導体装置 S D 3 においても、1 p i n の傍に識別用目印 P P を設けることができる。これにより、1 p i n を認識して半導体装置 S D 3 の向きを揃えることができるので、半導体装置 S D 3 の検査において、パーツフィーダー方式の特性選別を採用することができる。

#### 【0105】

##### 半導体装置の製造方法

次に、半導体装置の第 3 変形例の製造方法を図 4 1 ~ 図 5 7 を用いて工程順に説明する。ここでは、電解めっき法により形成した 12 個のリード（外部接続端子、外部端子、端子）を備えるタプレスパッケージを例示する。 20

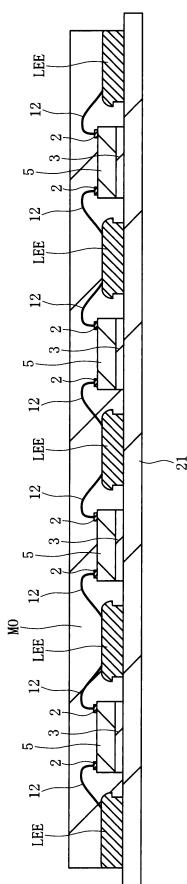

#### 【0106】

図 4 1 は 1 個のリードを拡大して示すリードの要部断面図である。図 4 2 は複数のリードを有する基材の製造方法を説明する工程図、図 4 3 ~ 図 4 9 は複数のリードを有する基材の製造方法を説明する製造工程中における基材の要部断面図、図 5 0 ~ 図 5 4 は半導体装置の製造方法を説明する製造工程中における半導体装置の要部断面図である。図 5 5 は半導体装置の裏面を示す要部平面図、図 5 6 は半導体装置の断面を示す要部断面図である。図 5 7 は半導体装置の製造方法を説明する工程図である。

#### 【0107】

ここでは、12 個の電解めっき法により形成したリードを備える半導体装置の製造方法について説明するが、これに限定されるものではなく、例えば 20 個または 24 個のリードを有する半導体装置の製造方法にも適用することができる。 30

#### 【0108】

<ウエハ準備工程 P 1 0 1 >から<ウエハダイシング工程 P 1 0 5 >までは、前述した半導体装置 S D 1 の製造方法の<ウエハ準備工程 P 1 >から<ウエハダイシング工程 P 5 >と同様であるので、ここでの説明は省略する。従って、<基板準備工程 P 1 0 6 >以降の工程について、以下に説明する。

#### 【0109】

##### <基材準備工程 P 1 0 6 >

まず、リード L E E および識別用目印 P P の形状について説明する。 40

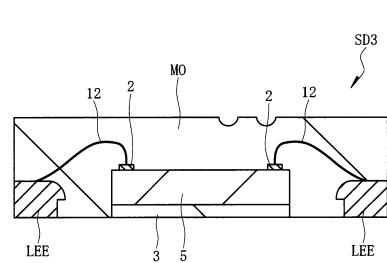

#### 【0110】

図 4 1 に示すように、リード L E E および識別用目印 P P は、例えば電解めっき法により金 (A u) 膜 L E E 1、ニッケル (N i) 膜 L E E 2、および銀 (A g) 膜 L E E 3（または金膜）を下から順次形成した積層膜により構成され、ニッケル膜 L E E 2 がひさし状に張り出した迫り出し部を有するマッシュルーム形状を有している。リード L E E および識別用目印 P P の表面（上面）は、母基板 2 1 の上面よりも高い位置にあるが、電解めっき法により形成するリード L E E および識別用目印 P P は、導電性基板（金属板）をパターニングすることで形成されたリードフレームの一部からなるリードの厚さの約半分以下の厚さで形成することができる。また、リード L E E および識別用目印 P P の形状をマッシュルーム形状とすることにより、後の製造工程であるモールド工程（P 1 1 0 ）にお 50

いて、リード LEE および識別用目印 PP のアンカー効果が期待できる。リード LEE および識別用目印 PP を構成する金膜 LEE 1 の厚さは、例えば 0.03 μm、ニッケル膜 LEE 2 B の厚さは、例えば 60 μm、銀膜 LEE 3 (または金膜) の厚さは、例えば 3 μm である。

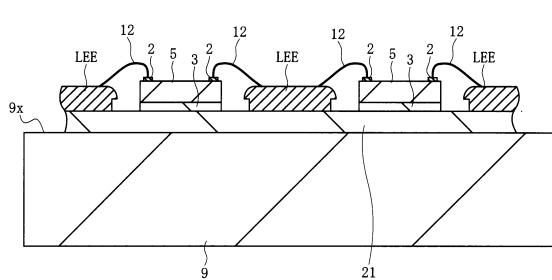

【0111】

次に、図 42～図 49 を用いて複数のリード LEE が形成された基材の製造方法について説明する。図 42 は複数のリードを有する基材の製造方法を説明する工程図、図 43～図 49 は複数のリードを有する基材の製造方法を説明する製造工程中における基材の要部断面図である。

【0112】

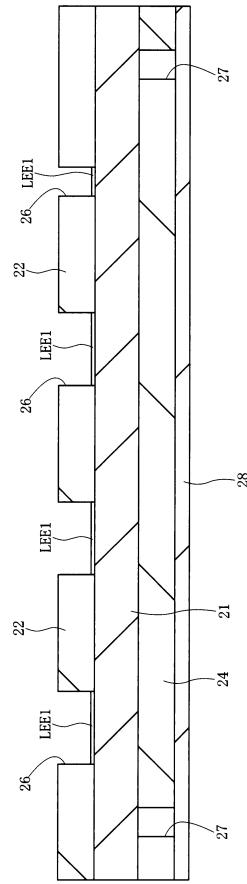

(P106-1: レジスト貼り付け工程～露光工程)

図 43 に示すように、母基板 21 の上面 (表面) にレジスト膜 22 を塗布した後、このレジスト膜 22 に、所定のパターンが形成されたフィルムマスク 23 を介して紫外線を露光する。同様に、母基板 21 の上面と反対側の下面 (裏面) にレジスト膜 24 を塗布した後、このレジスト膜 24 に、所定のパターンが形成されたフィルムマスク 25 を介して紫外線を露光する。

【0113】

(P106-2: 現像工程)

図 44 に示すように、フィルムマスク 23, 25 を除去した後に現像処理を施して、母基板 21 の上面に塗布されたレジスト膜 22 および母基板 21 の下面に塗布されたレジスト膜 24 をそれぞれパターニングする。これにより、母基板 21 の上面に塗布されたレジスト膜 22 に複数のリード LEE および識別用目印 PP を形成するための複数のリード用の穴 26 を形成し、母基板 21 の下面に塗布されたレジスト膜 24 に複数のガイド用の穴 27 を形成する。

【0114】

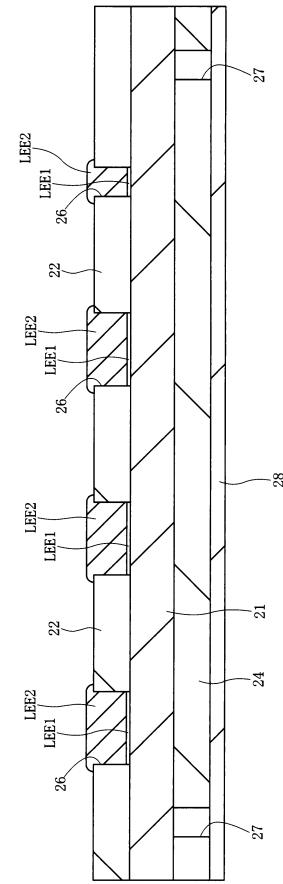

(P106-3: 金めっき工程)

図 45 に示すように、母基板 21 の下面に形成されたレジスト膜 24 の表面を保護フィルム 28 で覆った後、電解めっき法により母基板 21 の上面に形成された複数のリード用の穴 26 の底部にそれぞれ金膜 LEE 1 を形成 (堆積) する。金膜 LEE 1 の厚さは、例えば 0.03 μm である。

【0115】

(P106-4: ニッケルめっき工程)

図 46 に示すように、さらに、電解めっき法により母基板 21 の上面に形成された複数のリード用の穴 26 の内部に、金膜 LEE 1 に接続してニッケル膜 LEE 2 をそれぞれ形成 (堆積) する。このニッケル膜 LEE 2 は、複数のリード用の穴 26 の内部のみでなく、レジスト膜 22 の表面にも拡がって形成されるので、オーバーハング (底のようにはみ出した部位) を有するマッシュルーム形状に形成される。ニッケル膜 LEE 2 の厚さは、例えば 60 μm である。

【0116】

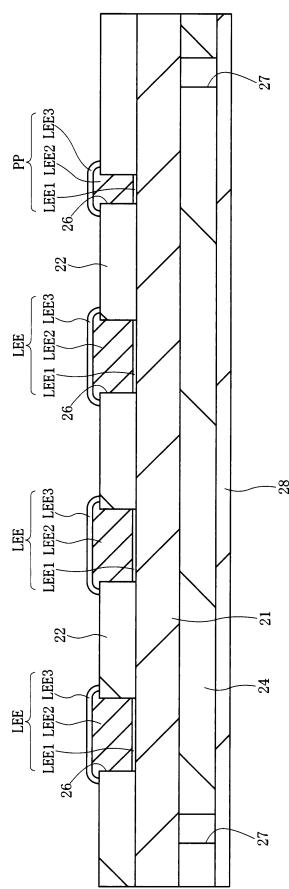

(P106-5: 銀 (または金) めっき工程)

図 47 に示すように、さらに、電解めっき法により母基板 21 の上面に形成された複数のニッケル膜 LEE 2 の表面に、ニッケル膜 LEE 2 に接続して銀膜 LEE 3 (または金膜) をそれぞれ形成 (堆積) する。銀膜 LEE 3 (または金膜) の厚さは、例えば 3 μm である。なお、本実施の形態では、金膜 LEE 1、ニッケル膜 LEE 2、および銀膜 LEE 3 (または金膜) を電解めっき法により形成することについて説明したが、無電解めっき法により形成してもよい。ただし、これらめっき膜の形成速度 (堆積速度) を考慮した場合には、電解めっき法を用いることが好ましい。

【0117】

(P106-6: フレームエッティング工程)

図 48 に示すように、母基板 21 の下面に形成されたレジスト膜 24 の表面を覆う保護

10

20

30

40

50

フィルム28を除去した後、レジスト膜24をマスクとして母基板21をエッチングする。これにより、レジスト膜24に形成されたガイド用の穴27に対応して母基板21の外枠29を形成する。

【0118】

(P106-7:除去工程)

図49に示すように、レジスト膜22, 24を除去し、余分な母基板21の一部を除去することにより、複数のリードLEEおよび識別用目印PPを有する母基板21が略完成する。

【0119】

<ダイポンディング工程P107>

10

ダイシングテープ4の下面側から紫外線を照射して、ダイシングテープ4の上面に形成された接着層の接着力を、例えば10~20g/25mm程度に低下させることにより、接着層を硬化させる。これにより、各半導体チップ5がダイシングテープ4から剥がれやすくなる。

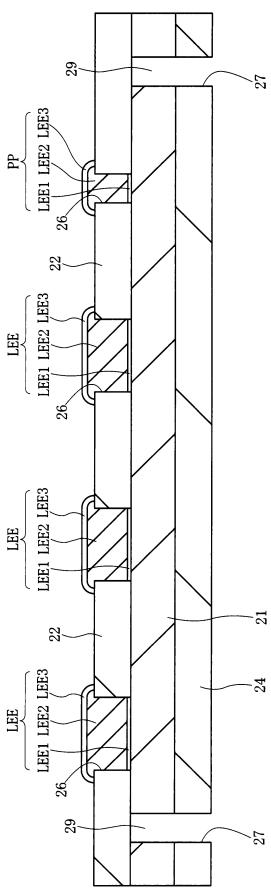

【0120】

次に、図50に示すように、母基板21の下面と、熱源を有するヒートステージ9の表面(上面)9xとを対向させて、ヒートステージ9の表面9x上に複数のリードLEEを有する母基板21を配置する。ヒートステージ9は、例えばステンレス(SUS430)などの導電性部材から成り、例えば40~80に加熱されている。ヒートステージ9の表面9x上に配置された母基板21にヒートステージ9の熱が伝わり、母基板21はヒートステージ9の温度と同等の温度に加熱されている。

20

【0121】

次に、半導体チップ5の表面を円筒コレット11によって吸着し、保持した後、半導体チップ5をダイシングテープ4から引き剥がしてピックアップする。半導体チップ5の裏面には、樹脂シート3が接着している。ピックアップされた半導体チップ5は、フレームテープ10の所定のチップ搭載領域に搬送される。

【0122】

次に、半導体チップ5の裏面に接着している樹脂シート3を介して、母基板21の上面のチップ搭載領域に半導体チップ5を配置し、熱(例えば40~80)を加えることでの、母基板21の上面のチップ搭載領域に半導体チップ5を固定する。

30

【0123】

<樹脂シートベーク工程P108>

次に、複数の半導体チップ5が貼り付けられた母基板21に対して、圧力を加えることなく例えば150で60分程度の熱処理を施す。この熱処理は、例えばベーク炉(複数の半導体チップ5が貼り付けられた母基板21を収納する加熱された室内)を用いたエア(Air)ベークである。これにより、樹脂シート3の硬化反応を促進させて、樹脂シート3を介した半導体チップ5と母基板21との接着力が強くなり、また、樹脂シート3の硬度が高くなる。

【0124】

<ワイヤボンディング工程P109>

40

図51に示すように、半導体チップ5の表面の縁辺に配置された複数の電極パッド2と、母基板21の上面のチップ搭載領域の周囲に位置する複数のリードLEEの表面とを、例えば熱圧着に超音波振動を併用したネイルヘッドボンディング法(ボールボンディング法)により、複数の導電性ワイヤ12を用いてそれぞれ電気的に接続する。

【0125】

主として、正ボンディング方式(半導体チップ5の電極パッド2と導電性ワイヤ12の一部を接続した後に、リードLEEと導電性ワイヤ12の他部を接続する方式)を用いるが、逆ボンディング方式(リードLEEと導電性ワイヤ12の一部を接続した後に、半導体チップ5の電極パッド2と導電性ワイヤ12の他部を接続する方式)を用いても良い。

【0126】

50

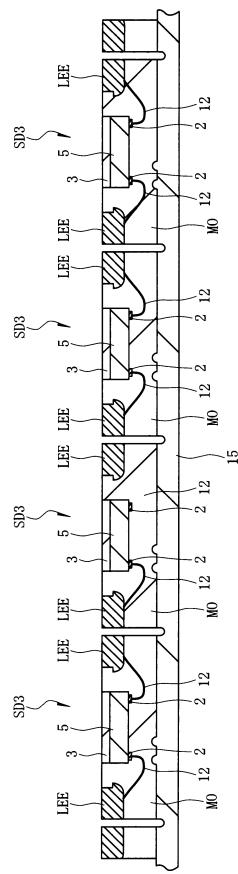

## &lt; モールド工程 P 1 1 0 &gt;

図 5 2 に示すように、複数の半導体チップ 5 が搭載された母基板 2 1 を金型成型機にセットし、温度を上げて液状化した封止樹脂を金型成型機に圧送して流し込み、母基板 2 1 の上面側を封止樹脂で封入して、1 つの樹脂封止体（封止体）M O を形成する。樹脂封止体 M O は、低応力化を図ることを目的として、例えばフェノール系硬化剤、シリコーンゴム、および多数のフィラー（例えばシリカ）などが添加されたエポキシ系の熱硬化性絶縁樹脂からなる。

## 【 0 1 2 7 】

## &lt; ベーク工程 P 1 1 1 &gt;

例えば 1 7 5 の温度で 5 時間の熱処理（ポストキュアベーク）を施す。この熱処理は 10 、例えばエア（A i r）ベークである。これにより、複数の半導体チップ 5 、複数のリード L E E のそれぞれの一部（表面と、側面の一部）、複数の導電性ワイヤ 1 2 、および識別用目印 P P の一部（表面（上面）と、側面）などが樹脂封止体 M O によって封止される。樹脂封止体 M O の厚さは、例えば 3 0 0  $\mu\text{m}$  である。

## 【 0 1 2 8 】

## &lt; S U S 剥がし工程 P 1 1 2 &gt;

樹脂封止体 M O から母基板 2 1 を折り曲げながら引き剥がす。これにより、樹脂封止体 M O の裏面（下面）から樹脂シート 3 および複数のリード L E E のそれぞれの他部（裏面（下面、実装面））および認識用目印 P P の裏面（下面）を露出させる。母基板 2 1 を引き剥がした後も、半導体チップ 5 の裏面には樹脂シート 3 が接着している。 20

## 【 0 1 2 9 】

## &lt; レーザーマーク工程 P 1 1 3 &gt;

図 5 3 に示すように、レーザー 1 4 を用いて樹脂封止体 M O の上面に品名などを捺印する。

## 【 0 1 3 0 】

## &lt; パッケージダイシング工程 P 1 1 4 &gt;

図 5 4 に示すように、ダイシングテープ 1 5 を準備する。続いて、ダイシングテープ 1 5 の上面に、複数の半導体チップ 5 、複数のリード L E E のそれぞれの一部（表面と、側面の一部）、および複数の導電性ワイヤ 1 2 などを被覆した樹脂封止体 M O を固定する。 30

## 【 0 1 3 1 】

次に、例えばダイヤモンド微粒を貼り付けた極薄の円形刃を用いて、樹脂封止体 M O の裏面側から樹脂封止体 M O 、複数のリード L E E 、および吊りリード L L をスクライブ領域に沿って縦、横に切断する。樹脂封止体 M O は半導体装置（半導体パッケージ）S D 3 に個片化されるが、個片化された後も半導体装置 S D 3 はダイシングテープ 1 5 を介して固定されているため、整列した状態を維持している。続いて、樹脂封止体 M O を切断する際に発生した屑などを除去するために、半導体装置 S D 3 を洗浄する。

## 【 0 1 3 2 】

## &lt; バラ落とし工程 P 1 1 5 &gt;

図 5 5 および図 5 6 に示すように、ダイシングテープ 1 5 を除去することにより、個々の半導体装置 S D 3 に分ける。半導体装置 S D 3 の表面には、レーザマークが印字されている。また、半導体装置 S D 3 の裏面には、1 2 個のリード L E E のそれぞれの裏面、および半導体チップ 5 の裏面に貼られた樹脂シート 3 が露出している。従って、半導体チップ 5 の裏面は、樹脂シート 3 に保護されている。また、半導体装置 S D 3 の側面には、1 2 個のリード L E E の側面の一部が樹脂封止体 M O から露出している。なお、樹脂シート 3 は樹脂封止体 M O と区別して視認することが難しいため、1 p i n の位置認識では樹脂シート 3 は認識されない。 40

## 【 0 1 3 3 】

個々に分けられた複数の半導体装置 S D 3 は、前述した半導体装置 S D 1 と同様に、前述の図 3 1 に示す自動部品供給装置 A F を用いて検査および梱包を行う。従って、複数の半導体装置 S D 1 は、自動部品供給装置 A F のパーツフィーダー部 A F P にバラバラの状 50

態で投入される。

【0134】

そして、前述した半導体装置 S D 1 の製造方法と同様に、<テスト(特性選別)工程 P 1 1 6 >および<テーピング工程 P 1 1 7 >を経て、良品と判断された半導体装置 S D 3 は出荷される。

【0135】

このように、電解めっき法により形成したリードを採用した半導体装置 S D 3 においても、識別用目印 P P により 1 p i n の位置を容易に認識できることから、タブレスパッケージであってもパーツフィーダ方式の特性選別を採用することができる。

【0136】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【符号の説明】

【0137】

|             |                                |    |

|-------------|--------------------------------|----|

| 1           | 半導体ウエハ                         |    |

| 1 C A       | チップ領域                          |    |

| 1 S A       | 切断領域(スクライブ領域、ダイシング領域、ダイシングライン) |    |

| 1 x         | 第1主面(表面)                       |    |

| 1 y         | 第2主面(裏面)                       | 20 |

| 2           | 電極パッド(ボンディングパッド、表面電極)          |    |

| 3, 3 A, 3 B | 樹脂シート(接着シート、接着フィルム、封止材)        |    |

| 4           | ダイシングテープ                       |    |

| 5, 5 A, 5 B | 半導体チップ                         |    |

| 6           | 銅(Cu)生材                        |    |

| 6 x         | 表面(上面)                         |    |

| 6 y         | 裏面(下面)                         |    |

| 7           | レジスト膜                          |    |

| 7 A         | レジスト膜(硬化部分)                    |    |

| 8           | 溶解液                            | 30 |

| 9           | ヒートステージ                        |    |

| 9 x         | 表面(上面)                         |    |

| 10          | フレームテープ                        |    |

| 11          | 円筒コレット                         |    |

| 12          | 導電性ワイヤ                         |    |

| 13          | キャピラリ(円筒状の接続治具)                |    |

| 14          | レーザー                           |    |

| 15          | ダイシングテープ                       |    |

| 21          | 母基板                            |    |

| 22          | レジスト膜                          | 40 |

| 23          | フィルムマスク                        |    |

| 24          | レジスト膜                          |    |

| 25          | フィルムマスク                        |    |

| 26          | リード用の穴                         |    |

| 27          | ガイド用の穴                         |    |

| 28          | 保護フィルム                         |    |

| 29          | 外枠                             |    |

| A F         | 自動部品供給装置                       |    |

| A F C       | テーピング部                         |    |

| A F P       | パーツフィーダー部                      | 50 |

AFT 検査部

CT キャリアテープ

LE リード(外部接続端子、外部端子、端子)

LE1, LE2, LE3, LE4 リード(外部接続端子、外部端子、端子)

LE5 タブ(アイランド)

LEE リード(外部接続端子、外部端子、端子)

LEE1 金(Au)膜

LEE2 ニッケル(Ni)膜

LEE3 銀(Ag)膜

LF1, LF2 リードフレーム

10

LH1 第1保持部

LH2 第2保持部

LH3 第3保持部

LH4 第4保持部

LL 吊りリード

MO 樹脂封止体(封止体)

MO1, MO2, MO3, MO4 封止体

PP 識別用目印

PRA 画像認識エリア

S1 第1側面

20

S2 第2側面

S3 第3側面

S4 第4側面

SD1, SD2, SD3 半導体装置(半導体パッケージ)

【図1】

【図2】

【図3】

【図4】

図4

【図5】

図5

【図6】

図6

【図7】

図7

【図8】

図8

【図9】

図9

【図10】

図10

【図11】

図11

【図12】

図12

【図13】

図13

【図14】

図14

【図15】

図15

【図16】

図16

【図17】

図17

【図18】

図18

【図19】

図19

【図20】

図20

【図21】

図21

【図22】

図22

【図23】

【図24】

図24

【図25】

【図26】

【図27】

【図28】

図28

【図29】

図29

【図30】

図30

【図31】

図31

【図32】

【図33】

図33

【図34】

図34

【図35】

図35

【図36】

図36

【図37】

図37

【図38】

図38

【図39】

図39

【図40】

図40

【図41】

図41

【図42】

図42

【図43】

図43

【図44】

図44

【図45】

図45

【図46】

図46

【図47】

図47

【図48】

図48

【図 49】

図 49

【図 50】

図 50

【図 51】

図 51

【図 52】

図 52

【図53】

【図55】

【図54】

【図56】

【図57】

【図58】

【図59】

【図60】

【図 61】

図 61

---

フロントページの続き

審査官 松田 直也

(56)参考文献 特開2008-153710(JP, A)

特開2005-294443(JP, A)

国際公開第2001/035460(WO, A1)

特開2010-080914(JP, A)

特開2002-231871(JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 23/28 - 23/31

H01L 23/50

H01L 21/301

H01L 21/78