【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第6部門第2区分

【発行日】平成17年4月7日(2005.4.7)

【公開番号】特開2003-344866(P2003-344866A)

【公開日】平成15年12月3日(2003.12.3)

【出願番号】特願2002-151322(P2002-151322)

【国際特許分類第7版】

G 02 F 1/1343

G 02 F 1/1368

G 09 F 9/30

H 01 L 21/336

H 01 L 29/786

【F I】

G 02 F 1/1343

G 02 F 1/1368

G 09 F 9/30 3 3 8

H 01 L 29/78 6 1 2 C

H 01 L 29/78 6 1 2 Z

【手続補正書】

【提出日】平成16年4月30日(2004.4.30)

【手続補正1】

【補正対象書類名】明細書

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【書類名】明細書

【発明の名称】表示装置及びその製造方法

【特許請求の範囲】

【請求項1】

表示素子と、

第1の走査線と、

第2の走査線と、

データ信号線と、

第1導電型の第1及び第2の出力配線層を有し、前記第1の出力配線層が前記データ信号線に接続され、前記第1の走査線に印加される電圧に応じて導通状態又は非導通状態に保持されるスイッチング素子と、

第1の電極と、前記第2の走査線を共有する第2の電極とを有する保持容量とを有し、

前記スイッチング素子の第2の出力配線層が、前記表示素子に接続され、かつ、当該第2の出力配線層と異なる第2導電型の半導体膜を含む前記保持容量の第1の電極に接続されている

表示装置。

【請求項2】

前記スイッチング素子が導通状態に保持されている時に、前記保持容量は、前記スイッチング素子を介して前記データ信号線から充電され、

前記スイッチング素子が非導通状態に保持されている時に、前記保持容量は、前記表示素子に電圧を印加する

請求項1に記載の表示装置。

**【請求項 3】**

前記スイッチ素子の前記第2の出力配線層と、前記保持容量の前記第1の電極とは、導電性物質により接続されている

請求項1に記載の表示装置。

**【請求項 4】**

前記スイッチ素子の前記第2の出力配線層と、前記保持容量の前記第1の電極とは、前記スイッチ素子の前記第2の出力配線層に到達するコンタクトホールと、前記保持容量の前記第1の電極に到達するコンタクトホールとに充填された導電性物質により接続されている

請求項3に記載の表示装置。

**【請求項 5】**

前記スイッチ素子の前記第2の出力配線層と、前記保持容量の前記第1の電極とは、前記スイッチ素子の前記第2の出力配線層、及び前記保持容量の前記第1の電極に到達するコンタクトホールに充填された導電性物質により接続されている

請求項3に記載の表示装置。

**【請求項 6】**

前記スイッチ素子の前記第2の出力配線層と、前記保持容量の前記第1の電極とを接続する前記導電性物質は、前記データ信号線に用いる導電性物質と同じである

請求項1に記載の表示装置。

**【請求項 7】**

前記保持容量の一部または全部は、前記データ信号線と前記第2の走査線が重なっている領域に、前記データ信号線と前記第2の走査線の間に形成される

請求項1に記載の表示装置。

**【請求項 8】**

複数の前記第1と第2の走査線と、複数の前記データ信号線と、行列状に配列された複数の画素と、前記複数の画素を駆動する駆動回路とを含む表示装置であって、

各画素を駆動する前記駆動回路は、第1導電型の第1及び第2の出力配線層を有し、前記第1の出力配線層が前記データ信号線に接続され、前記第1の走査線に印加される電圧に応じて導通状態又は非導通状態に保持されるスイッチング素子と、

第1の電極と、前記第2の走査線を共有する第2の電極とを有する保持容量と

を有し、

前記スイッチング素子の第2の出力配線層が、前記表示素子に接続され、かつ、当該第2の端子と異なる第2導電型の半導体膜を含む前記保持容量の第1の電極に接続されている

表示装置。

**【請求項 9】**

前記スイッチング素子は、多結晶シリコンを半導体層とする薄膜トランジスタである

請求項8に記載の表示装置。

**【請求項 10】**

並列に配置する導電性の第1の走査線と第2の走査線と、前記第1の走査線と第2の走査線とを覆う第1の絶縁膜と、前記第1の絶縁膜を覆う半導体膜とを形成し、

前記第1の走査線及び第2の走査線と対向する前記半導体膜の第1のチャネル領域と第2のチャネル領域をそれぞれ保護する第1の保護マスクと第2の保護マスクとを形成し、

前記第1の保護マスクと第2の保護マスクが形成されている状態で、前記半導体膜において、前記第1の走査線を含むスイッチング素子を形成するスイッチング素子領域と、前記第2の走査線を含む保持容量を形成する保持容量領域とに、それぞれ第1導電型の不純物と第2の導電型の不純物を注入する

表示装置の製造方法。

**【請求項 11】**

前記スイッチング素子領域と前記保持容量領域にそれぞれ第1導電型の不純物と第2の

導電型の不純物が注入された半導体膜と、前記第1と第2の保護マスクとを覆うように、第2の絶縁膜を形成し、

前記第2の絶縁膜に、前記第1の走査線の両側の第1導電型半導体領域に到達する第1のコンタクトホールと第3のコンタクトホールとを形成し、

前記第2の絶縁膜に、前記第2の走査線の片側の第2導電型の半導体領域に到達する第2のコンタクトホールとを形成し、

前記第1と第2のコンタクトホールに導電性物質を充填し、前記第1の走査線の片側の第1導電型の半導体領域と、前記第2の走査線の片側の第2導電型の半導体領域とを接続し、

前記第3のコンタクトホールに導電性物質を充填し、データ信号線を形成する請求項10に記載の表示装置の製造方法。

#### 【請求項12】

前記第1のコンタクトホールは、前記第2のコンタクトホールと同じコンタクトホールである

請求項11に記載の表示装置の製造方法。

#### 【請求項13】

前記第1と第2のコンタクトホールに堆積された導電性物質は、前記第3のコンタクトホールに堆積された導電性物質と同じ材料である

請求項11に記載の表示装置の製造方法。

#### 【請求項14】

半導体膜と、前記半導体膜を覆う絶縁膜と、前記絶縁膜に並列に配置する導電性の第1の走査線と第2の走査線とを形成し、

前記半導体膜における前記第1の走査線を含むスイッチング素子を形成するスイッチング素子領域と、前記第2の走査線を含む保持容量を形成する保持容量領域とに、前記第1の走査線と第2の走査線側から、それぞれ第1導電型の不純物と第2導電型の不純物を注入する

表示装置の製造方法。

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

本発明は、表示装置およびその製造方法に関し、具体的には、液晶表示装置およびその製造方法に関する。

##### 【0002】

##### 【従来の技術】

液晶表示装置は、薄型で低消費電力であるという特徴を生かして、ノート型パーソナルコンピュータ、カーナビゲーション用の表示装置、携帯情報端末（Personal Digital Assistant：PDA）、携帯電話等に広く用いられている。この液晶表示装置には、大きく分けて、バックライトからの光を制御して表示を行なう透過型と、太陽光などの外光を反射して表示を行なう反射型、また、最近は、その両者の特徴を併せ持つ併用型と呼ばれる表示装置がある。

これらの表示装置は、その用途から低消費電力が求められ、そのため、バックライトの利用効率を最大限に上げるように、高開口率が求められる。また、併用型においては、同一画素に透過部と反射部を形成し、画素内に多機能を盛り込むため、出来る限り有効にスペースを使う必要がある。

##### 【0003】

液晶表示装置で画像を表示する時は、走査線から各画素に設けられたスイッチング素子、例えば、TFT（Thin Film Transistor）に走査パルスを印加し、ON/OFFして、表示画素を選択する。そして、画像信号に応じた信号がデータ線に印加され、TFTのソースとドレインを介して、液晶を挟む電極に印加して、液晶に入射された光を変調させ、画像を表示する。

画像信号に応じた電圧を各画素に書き込んだ後、次の書き込み動作までの期間内に、液晶の電極に印加された電圧による電荷は、液晶やスイッチング素子を通じてリークして変化する。表示画質を保証するためには、その印加された電圧を保持する必要がある。そこで、液晶表示装置では、通常、そのリーク量と比較して十分な補助容量（CS）が形成されている。

#### 【0004】

図1は、従来の液晶表示装置の等価回路図の一例を示し、図2は、図1に示された液晶表示装置の構成の平面図を示す。

図1は、 $2 \times 3$ 画素の等価回路を示す。該等価回路において、1画素は、液晶素子及びそれを挟んでいる電極と、スイッチング素子であるトランジスタTrと、及び補助容量CSとを含む。Cc11...Cc16は、液晶素子とそれを挟んでいる表示電極と共に通電極とからなる液晶コンデンサーの容量を示し、CS1...CS6は、各画素の補助容量の容量値を示す。

#### 【0005】

複数の走査線WLn-1、WLn、WLn+1は並列に配置され、例えばTFTからなるトランジスタTr1、Tr4、または、Tr2、Tr5、またはTr3、Tr6のゲート電極とそれぞれ接続しており、各トランジスタのON/OFFを制御し、画素を選択する。

並列に配置されたデータ信号線BLn-1、BLn、BLn+1からは、画像信号に応じた電圧を各画素に印加する。データ信号線BLn-1、BLn、BLn+1は、トランジスタTr1、Tr2、Tr3、または、Tr4、Tr5、Tr6の例えばソース領域と接続しており、走査線WLn-1、WLn、またはWLn+1により選択された画素に対して、補助容量CSに充電しながら、液晶素子両側の電極に電圧を印加し、液晶素子に入射された光を変調させ、画像を表示する。

#### 【0006】

図2は透明基板上に形成された走査線とデータ信号線及び1画素の構成図を示している。図2に示すように、補助容量線CSLn-1が一方の電極として、その上に補助容量CS1が形成されている。コンタクトホールH1に堆積された導電性材料を介して、トランジスタTr1の片方の不純物領域、例えばソース領域はデータ信号線BLn-1と接続している。また、コンタクトホールH2とH3に堆積された導電性材料を介して、トランジスタTr1の他方の不純物領域、例えばドレイン領域は補助容量CS1の他方の例えば半導体からなる電極、及び図示せぬ上層のITO電極に接続している。

#### 【0007】

通常、トランジスタTr1、...、Tr6はNチャネル型の薄膜トランジスタTFTを用いている。即ち、ゲート電極の両側の半導体薄膜に、燐(P)などを注入したN型のソースとドレイン不純物領域が形成され、ゲート電極(走査線)にしきい値以上の正電圧を印加すると、ソースとドレインの間にN型の反転層からなるNチャネルが形成され、ソースとドレインは導通される。即ち、トランジスタがON状態である。逆に、ゲート電極(走査線)にしきい値以下の電圧を印加した場合、ソースとドレインを導通するチャネルが形成されず、トランジスタがOFF状態である。

また、補助容量CS1は、通常、最も大きい容量が形成できる、半導体層/絶縁膜/金属のMOS構造により形成されている。図2において、例えば、補助容量線CSLn-1(金属)、トランジスタTr1を構成するゲート絶縁膜、及び上記燐などを注入したN型の半導体膜によって、補助容量CS1が形成される。以下、このようなMOS容量をN型MOS構造とする。

#### 【0008】

補助容量電極を一定電位にしておく場合には、補助容量部分はN型MOS構造にすることが一般的である。

また、補助容量用電極を対向電極と同位相で振るコモン反転駆動の場合には、補助容量CSを形成する半導体膜はイントリニシック状態では、十分な容量が形成されないため、

半導体層をメタル化、即ち、高濃度に燐（N+化）やボロン（P+化）を含有させることが一般的である。

#### 【0009】

以上の従来の方法では、高濃度に燐（N+化）やボロン（P+化）の注入は一回だけで済み、製造上コストダウンが可能であった。

しかしながら、以上の構造では独立の補助容量線が必要であるので、開口率の低下を招くという問題がある。

そこで、補助容量線を前段又は後段の走査線（ゲート線）と兼ねるCSオングート構造が提唱されている。

#### 【0010】

図3は、従来の液晶表示装置の他の例を示し、図3(A)は、該液晶表示装置の等価回路図であり、(B)は、該液晶表示装置の構成の平面図を示す。図3(A)と(B)において、図1と同じ構成成分に同じ符号を用いて表わす。また、重複する説明を適宜省略する。

図3(A)は、 $2 \times 2$ 画素の等価回路を示している。図3(A)において、図1に示された補助容量線CSLn-1、CSn、CSn+1の代わりに、補助容量CS1、CS4、CS2、CS5がそれぞれ直接に走査線WLn-1、WLn、WLn+1に接続している。

図3(B)は透明基板上に形成された走査線とデータ信号線及び1画素の構成を示している。図2に示された補助容量線CSLn-1の代わりに、補助容量CS1が走査線WLnに重ねて形成されている。

#### 【0011】

この場合も、通常、トランジスタTr1、…、Tr5はNチャネル型の薄膜トランジスタTFTを用いている。また、補助容量CS1もN型MOS容量である。即ち、トランジスタTr1、…、Tr5は、ゲート電極（走査線）にしきい値以上の正電圧を印加すると、トランジスタをON（オン）状態にし、ゲート電極にしきい値以下の電圧を印加すると、トランジスタをOFF（オフ）状態にする。

また、補助容量CS1は、図3(B)に示すように、走査線WLn（金属）、トランジスタTr1を構成するゲート絶縁膜、及び燐などを注入したN型の半導体膜によって、補助容量CS1が形成される。

このようなCSオングート構造にすれば、独立の補助容量線を形成する必要がないため、開口率が向上する利点がある。

#### 【0012】

##### 【発明が解決しようとする課題】

NMOSトランジスタTr1をオフ状態に保つため、通常、走査線WLn-1、WLn、…の電位は0V~-6V程度に設定されれば良い。しかも、液晶表示装置において、1画面を表示する期間内にトランジスタTr1がほとんどOFF状態に保持され、即ち、走査線電位は0V以下に保持されている。

しかし、図3に示すようなCSオングート構造では、例えば、後段の走査線（ゲート線）WLnと補助容量CS1を形成する場合、以上のような電位が印加される状態では、走査線/ゲート絶縁膜/N型の半導体膜で形成されたN型MOS構造では十分な容量が得られない。

図4は、N型MOS構造の容量-電圧特性を示すグラフである。

図3(B)に示す走査線WLn-1、WLnに例えば-2Vを印加して、Tr1をOFF状態にした場合、CS1はTr1がON状態の間に充電されたので、CS1の半導体電極は走査線WLn-1、WLnより高電位であり、CS1に印加されたゲート電圧は負電圧となる。これによって、多数キャリア電子が該半導体膜の表面から排斥され、半導体膜の表面に空乏層（又／及び反転層）が形成されるので、CS1の絶縁層が厚くなるのに相当し、容量値が小さい。

この傾向は図4に示されている。走査電位が約1.5V程度以下で使用される場合、N

型MOS容量では、常に小さい容量しか確保できない。

補助容量CS1の容量を上げるために、補助容量CS1の半導体膜電極に高濃度に燐(N+化)やボロン(P+化)を注入する必要がある。そうすることによって、工程増加や不良発生による歩留り落ちなどの問題が発生する。

#### 【0013】

図5～図7は従来の液晶表示装置の製造工程の一例を示す。

図5(A)では、ガラス基板101上に走査線となるゲート電極(走査線)102aと102bを形成する。材料は、Ta、Cr、Mo、Ti、Alなどの金属が用いられ、フォトレジスト工程を経てウェットエッティングやドライエッティングによりパターン形成される。

図5(B)では、ゲート電極102aと102b上にゲート絶縁膜103および半導体層104aを形成する。ゲート絶縁膜103には、たとえば、シリコン窒化膜やシリコン酸化膜、他にゲート電極を陽極酸化した陽極酸化膜などがある。また、半導体膜としては、アモルファス・シリコン膜やアモルファス・シリコン膜を結晶化したポリシリコン膜、または、直接形成したポリシリコン膜などが使用される。

#### 【0014】

図5(C)では、半導体膜104aの上部に保護絶縁膜105を形成する。この保護絶縁膜105には、シリコン窒化膜やシリコン酸化膜などが使用される。

図5(D)では、ゲート電極102aと102bを遮光マスクとして自己整合的に、レジスト107aと107bを形成する。その後、保護絶縁膜105をウェットエッティング、または、ドライエッティングにより除去する。その後、残りの保護絶縁膜105aと105bをマスクとして、燐(P)などを低濃度でドープする。半導体膜の注入された部分(領域)は104bと記する。半導体膜104bはn<sup>-</sup>型半導体である。

#### 【0015】

図6(A)では、画素トランジスタでLCD領域を形成する部分を覆うような形状のレジスト108を形成する。その後、補助容量形成部分に残留の保護絶縁膜105bを除去するため、ウェットエッティング、または、ドライエッティングを行なう。

その後、高濃度に燐などを注入し、半導体層104bを金属化する。半導体膜104bの金属化された部分は104cと記する。

ここでは、図示していないが、第2のドープ種(ボロンなど)を注入する部分について、フォトレジスト工程、注入工程を行なう。その後、必要に応じてドープした元素を活性化するための熱処理を行なう。

#### 【0016】

通常、このウェットエッティングまたは、ドライエッティングは、半導体層104bとはエッティング選択性があるプロセスにより行われるが、半導体層104bにピンホールなどがある場合には、下地のゲート絶縁膜103がエッティングされ、その部分は、非常に耐圧が悪くなり、電流リーク経路となって点欠陥などの不良原因となる。また、保護絶縁膜105bを除去するための工程が増加し、コストアップ要因となる。

#### 【0017】

図6(B)では、素子分離を行なうために、ゲート電極102aと102bの外側の半導体層104bをフォトリソグラフィ、ドライエッティングなどの手段を用いて除去する。

図6(C)では、シリコン窒化膜やシリコン酸化膜などにより、層間絶縁膜109を形成する。その後、フォトリソグラフィ、ウェットエッティングなどの手段を用いてコンタクトホール110aと110bを形成する。

#### 【0018】

図7(A)では、データ信号線111aと111bおよび画素電極との接続金属112として、AlやTa、Wなどの金属を堆積し、その後、フォトリソグラフィ、ドライエッティングなどの手段を用いて除去し、パターンを形成する。

図7(B)では、第2の層間絶縁膜113をシリコン窒化膜やシリコン酸化膜などにより形成する。また、この層に平坦化効果を持たせるために、感光性有機膜や感光性SOG

(スピンオングラス)膜などを用いても良い。ここでも、画素電極114とのコンタクトホールを形成しておく。その後、ITOやIXOなど透明導電膜を用いて、画素電極114を形成する。

#### 【0019】

その後、図示はしていないが、別に用意した対応カラーフィルタ基板と本TFT基板を重ね合わせ、液晶層を挟んで組立工程を行ない、さらに偏光板などを貼り付けることにより液晶表示装置を完成する。

このように、従来の製造方法では、補助容量構造を完成させるために、特別な工程が必要になり、コストアップの要因となり、また、欠陥の原因となるリーク電流が増加する。従来は、このような工程増加や不良発生による歩留り落ちが発生するという問題がある。

#### 【0020】

以上は、走査線(ゲート電極)を半導体層の下部に形成するボトムゲート型トランジスタでの従来例であり、走査線(ゲート電極)を半導体層の上部に形成するトップゲート型トランジスタについても製造方法上に問題が生じる。

図8と図9は、トップゲート型トランジスタ構造を有する液晶表示装置の製造方法の従来例を示す。

図8(A)に示すように、ガラス基板121上に下地層122と半導体層123aを成膜する。下地層122には、たとえば、シリコン窒化膜やシリコン酸化膜を使用する。また、半導体膜123aとしては、アモルファス・シリコン膜やアモルファス・シリコン膜を結晶化したポリシリコン膜、または、直接形成したポリシリコン膜などが使用される。

#### 【0021】

図8(B)に示すように、素子分離を行なう領域を確保するために、半導体層123aの一部を、フォトリソグラフィ、ドライエッチングなどの手段を用いて除去する。

そして、半導体膜123a上に、ゲート絶縁膜124を形成する。ゲート絶縁膜124には、たとえば、シリコン窒化膜やシリコン酸化膜などがある。

続いて、トランジスタTFTを形成する領域および補助容量を形成する領域において、ゲート電極125a、125bを形成する。

次に、ゲート電極125a、125bを注入マスクとして自己整合的に、燐などを低濃度でドープする。半導体膜の注入された部分はn<sup>-</sup>型半導体であり、123bと記する。

#### 【0022】

図8(C)に示すように、画素トランジスタTFTでLD領域を形成する領域を覆うような形状のレジスト126を形成する。他の領域に高濃度に燐などを注入し、半導体層123bを金属化する。半導体膜123bの金属化された部分は123cと記する。

また、ここでは、図示していないが、第2のドープ種(ボロンなど)を注入する部分に応じて、フォトレジスト工程、注入工程を行なう。その後、必要に応じてドープした元素を活性化するための熱処理を行なう。

#### 【0023】

図9(A)においては、シリコン窒化膜やシリコン酸化膜などにより、層間絶縁膜127を形成する。その後、フォトリソグラフィ、ウェットエッチングなどの手段を用いてコンタクトホール128aと128bを形成する。

図9(B)では、データ信号線129aと129bおよび画素電極132との接続金属130として、A1やTa、Wなどの金属を堆積し、その後、フォトリソグラフィ、ドライエッチングなどの手段を用いて除去し、パターンを形成する。

続いて、第2の層間絶縁膜131をシリコン窒化膜やシリコン酸化膜などにより形成する。また、この層に平坦化効果を持たせるために、感光性有機膜や感光性SOG(スピンオングラス)膜などを用いても良い。ここでも、画素電極132とのコンタクトホールを形成しておく。その後、ITOやIXOなど透明導電膜を用いて、画素電極132を形成する。

その後、図示していないが、別に用意した対応カラーフィルタ基板と本TFT基板を重ね合わせ、液晶層を挟んで組立工程を行ない、さらに偏光板などを貼り付けることにより

液晶表示装置を完成する。

【0024】

図8(B)と(C)に示すように、以上の構造では、補助容量を形成する領域に、ゲート電極125bが形成されたので、その下部の半導体膜123aに不純物を注入できなく、金属化することが出来ない問題がある。従来の方法の範囲において、この問題を解決するには、初期段階でマスクを形成して注入を行なった後にマスクを除去する工程を増やすか、或は、図1に示したような独立した補助容量線を形成する必要がある。

【0025】

本発明は、上記の課題を鑑みてなされ、その目的は、高い開口率と大容量の補助容量を含んだ表示装置、及び製造工程を増やすことなくその表示装置を製造する方法を提供することにある。

【0026】

【課題を解決するための手段】

本発明に係わる表示装置は、表示素子と、第1の走査線と、第2の走査線と、データ信号線と、第1導電型の第1及び第2の出力配線層を有し、前記第1の出力配線層が前記データ信号線に接続され、前記第1の走査線に印加される電圧に応じて導通状態又は非導通状態に保持されるスイッチング素子と、第1の電極と、前記第2の走査線を共有する第2の電極とを有する保持容量とを有し、前記スイッチング素子の第2の出力配線層が、前記表示素子に接続され、かつ、当該第2の出力配線層と異なる第2導電型の半導体膜を含む前記保持容量の第1の電極に接続されている。

【0027】

前記スイッチング素子が導通状態に保持されている時に、前記保持容量は、前記スイッチング素子を介して前記データ信号線から充電され、前記スイッチング素子が非導通状態に保持されている時に、前記保持容量は、前記表示素子に電圧を印加する。

【0028】

また、前記スイッチ素子の前記第2の出力配線層と、前記保持容量の前記第1の電極とは、導電性物質により接続されている。

具体的に、前記スイッチ素子の前記第2の出力配線層と、前記保持容量の前記第1の電極とは、前記スイッチ素子の前記第2の出力配線層に到達するコンタクトホールと、前記保持容量の前記第1の電極に到達するコンタクトホールとに堆積された導電性物質により接続されている。

或は、前記スイッチ素子の前記第2の出力配線層と、前記保持容量の前記第1の電極とは、前記スイッチ素子の前記第2の出力配線層、及び前記保持容量の前記第1の電極に到達するコンタクトホールに堆積された導電性物質により接続されている。

【0029】

好適に、前記スイッチ素子の前記第2の出力配線層と、前記保持容量の前記第1の電極とを接続する前記導電性物質は、前記データ信号線に用いる導電性物質と同じである。

又、好適に、前記保持容量の一部または全部は、前記データ信号線と前記第2の走査線が重なっている領域に、前記データ信号線と前記第2の走査線の間に形成される。

【0030】

本発明に係わる表示装置は、複数の前記第1と第2の走査線と、複数の前記データ信号線と、行列状に配列された複数の画素と、前記複数の画素を駆動する駆動回路とを含む表示装置であって、各画素を駆動する前記駆動回路は、第1導電型の第1及び第2の出力配線層を有し、前記第1の出力配線層が前記データ信号線に接続され、前記第1の走査線に印加される電圧に応じて導通状態又は非導通状態に保持されるスイッチング素子と、第1の電極と、前記第2の走査線を共有する第2の電極とを有する保持容量とを有し、前記スイッチング素子の第2の出力配線層が、前記表示素子に接続され、かつ、当該第2の出力配線層と異なる第2導電型の半導体膜を含む前記保持容量の第1の電極に接続されている。

好適に、前記スイッチング素子は、多結晶シリコンを半導体層とする薄膜トランジスタ

である。

#### 【 0 0 3 1 】

本発明に係わる表示装置の製造方法は、並列に配置する導電性の第1の走査線と第2の走査線と、前記第1の走査線と第2の走査線とを覆う第1の絶縁膜と、前記第1の絶縁膜を覆う半導体膜とを形成し、前記第1の走査線と第2の走査線と対向する前記半導体膜の第1のチャネル領域と第2のチャネル領域をそれぞれ保護する第1の保護マスクと第2の保護マスクと形成し、前記第1の保護マスクと第2の保護マスクが形成されている状態で、前記半導体膜において、前記第1の走査線を含むスイッチング素子を形成するスイッチング素子領域と、前記第2の走査線を含む保持容量を形成する保持容量領域とに、それぞれ第1導電型の不純物と第2導電型の不純物を注入する。

#### 【 0 0 3 2 】

本発明に係わる表示装置の製造方法では、前記スイッチング素子領域と前記保持容量領域にそれぞれ第1導電型の不純物と第2導電型の不純物が注入された半導体膜と、前記第1と第2の保護マスクとを覆うように、第2の絶縁膜を形成し、前記第2の絶縁膜に、前記第1の走査線の両側の第1導電型半導体領域に到達する第1のコンタクトホールと第3のコンタクトホールとを形成し、前記第2の絶縁膜に、前記第2の走査線の片側の第2導電型の半導体領域に到達する第2のコンタクトホールとを形成し、前記第1と第2のコンタクトホールに導電性物質を堆積し、前記第1の走査線の片側の第1導電型の半導体領域と、前記第2の走査線の片側の第2導電型の半導体領域とを接続し、前記第3のコンタクトホールに導電性物質を堆積し、データ信号線を形成する。

#### 【 0 0 3 3 】

好ましくは、前記第1のコンタクトホールは、前記第2のコンタクトホールと同じコンタクトホールである。

また、好ましくは、前記第1と第2のコンタクトホールに堆積された導電性物質は、前記第3のコンタクトホールに堆積された導電性物質と同じ材料である。

#### 【 0 0 3 4 】

また、本発明に係わる表示装置の製造方法は、半導体膜と、前記半導体膜を覆う絶縁膜と、前記絶縁膜に並列に配置する導電性の第1の走査線と第2の走査線とを形成し、前記半導体膜における前記第1の走査線を含むスイッチング素子を形成するスイッチング素子領域と、前記第2の走査線を含む保持容量を形成する保持容量領域とに、前記第1の走査線と第2の走査線側から、それぞれ第1導電型の不純物と第2導電型の不純物を注入する。

#### 【 0 0 3 5 】

上記の本発明によれば、半導体膜において、トランジスタのソース・ドレイン領域の導電型（言わばソース・ドレイン間のチャネルの導電型）を、補助容量を形成する半導体膜領域の導電型と異ならしめている。トランジスタのソース・ドレイン領域、及びチャネルの導電型がN型の場合、補助容量を形成する半導体膜領域をP型にする。そうすることによって、NチャネルのトランジスタをOFF状態にする走査線電圧（ゼロ又は負電圧）を、P型MOS構造の補助容量に印加すると、大きい容量が得られる。また、トランジスタのソース・ドレイン領域、及びチャネルの導電型がP型の場合、補助容量を形成する半導体膜領域をN型にすれば、同じ効果を奏する。

また、以上の構成を形成するために、不純物を注入する時に、異なるタイプの不純物を注入し分けるだけで十分なので、製造工程を増やすことはない。

さらに、以上の構成で十分な容量が得られるので、半導体膜の補助容量形成領域に不純物を注入する時に、走査線と対向する半導体膜のチャネル形成領域を保護するマスクを、エッチングにより除去する必要がないので、欠陥を生じる要因が減る。

#### 【 0 0 3 6 】

##### 【 発明の実施の形態 】

以下、液晶表示装置を例として、本発明の表示装置及びその製造方法の実施の形態について、添付の図面を参照して述べる。

## 第1の実施形態

図10(A)と(B)は、本実施形態に係わる液晶表示装置の等価回路及びその構成を示す図である。図10(A)の回路配置図は図3(A)に示された従来例と同様である、ただし、図10(A)において、補助容量PCS1、PCS2、PCS4、PCS5が有する半導体膜の導電型は、トランジスタNTr1、NTr2、NTr4、NTr5の導電型と異なる。この例では、トランジスタNTr1、NTr2、NTr4、NTr5がNチャネル型TFTで形成されており、補助MOS容量がP型MOS構造により形成されている。即ち、補助MOS容量が走査線(金属)、ゲート絶縁膜、及びP型の半導体膜により形成されている。

また、この導電型を入れ替えて、トランジスタをPチャネル型TFTで、補助容量をN型MOS構造で形成しても良い。

### 【0037】

図10(A)は、 $2 \times 2$ 画素の等価回路を示す。図10(A)において、複数の走査線WL<sub>n-1</sub>、WL<sub>n</sub>、WL<sub>n+1</sub>が並列に配置され、例えばNチャネル型TFTからなるトランジスタNTr1とNTr4、または、NTr2とNTr5のゲート電極とそれぞれ接続しており、各トランジスタのON/OFFを制御し、動作する画素を選択する。

走査線/ゲート絶縁膜/P型の半導体膜から形成されたP型MOS構造の補助容量PCS1、PCS2、PCS4、及びPCS5がそれぞれ直接に走査線WL<sub>n-1</sub>、WL<sub>n</sub>、WL<sub>n+1</sub>に接続している。

また、並列に配置されて、画像信号に応じた電圧を各画素に印加するデータ信号線BL<sub>n-1</sub>、BL<sub>n</sub>、BL<sub>n+1</sub>は、トランジスタNTr1、NTr2、または、NTr4、NTr5の一方の不純物領域、例えば、ソース領域と接続しており、走査線WL<sub>n-1</sub>、WL<sub>n</sub>、またはWL<sub>n+1</sub>により選択された画素に対して、P型MOS構造の補助容量PCSを充電しながら、液晶素子の電極に電圧を印加し、液晶に入射された光を変調させ、画像を表示する。

### 【0038】

図10(B)は、透明基板上に形成された走査線とデータ信号線及び1画素の構成の平面図である。図10(B)において、図10(A)に示したP型MOS補助容量PCS1が走査線WL<sub>n</sub>の上に不図示のゲート絶縁膜を介して形成されている。

コンタクトホールH1に充填された導電性材料を介して、Nチャネル型トランジスタNTr1の一方の不純物領域、例えばソース領域はデータ信号線BL<sub>n-1</sub>と接続している。また、コンタクトホールH2とH3に充填された導電性材料を介して、Nチャネル型トランジスタNTr1の他方の不純物領域、例えばドレイン領域は補助容量PCS1の半導体膜及び図示せぬ上層のITO電極に接続している。

### 【0039】

図11は図10(B)に示される画素構造を模式的断面図にしたものであり、図10(B)では、データ信号線から補助容量に至る半導体層パターンに沿った断面図になっている。ただし、TFTトランジスタ部分は、紙面の関係上、トランジスタが直列に並んだダブルゲート構造では図示されておらず、シングルゲート構造となっている。

図11において、不図示の透明基板上に走査線1aと1b(WL<sub>n-1</sub>とWL<sub>n</sub>)が形成され、それを覆うようにゲート絶縁膜2が形成されており、ゲート絶縁膜2の上に半導体膜3, 4, 5, 6が成膜され、TFTトランジスタ及び補助容量が形成される。

該半導体膜において、3は、例えば高濃度の燐(P)が注入されたN<sup>+</sup>半導体領域、4は例えば高濃度のボロン(B)が注入されたP<sup>+</sup>半導体領域である。半導体膜5の中央は不純物を注入していない、いわゆるiタイプ(真性半導体)の半導体膜であり、その両側は低濃度の例えば燐(P)が注入したLDD領域である。半導体膜5はTFTトランジスタのチャネル領域を構成し、図11の例には、これはNチャネルである。6も不純物が注入されていない、いわゆるiタイプの半導体膜である。

7aと7bは、その下のiタイプの半導体膜5と6が不純物注入されないように形成されたストップ膜であり、8は層間絶縁層である。

## 【0040】

層間絶縁層8において、N<sup>+</sup>半導体領域3、P<sup>+</sup>半導体領域4の上方に、コンタクトホールが形成されており、コンタクトホール内の導電材料が、N<sup>+</sup>半導体領域3とP<sup>+</sup>半導体領域4を接続する接続電極10を形成し、また、データ信号線9を形成する。

ゲート電極1a、ゲート絶縁膜2、及び半導体膜4と5がNチャネル型のTFTトランジスタを構成する。一方、ゲート電極1b、ゲート絶縁膜2、及び半導体膜4と6がPチャネル型のトランジスタを構成する、そのPチャネル型トランジスタの容量は補助容量として用いる。

## 【0041】

N<sup>+</sup>半導体領域3とP<sup>+</sup>半導体領域4の導通は、両者を直接に接続する場合は、N<sup>+</sup>半導体領域3とP<sup>+</sup>半導体領域4の間にPN結合が生じ、電位のロスが生じる。そこで、N<sup>+</sup>半導体領域3からP<sup>+</sup>半導体領域4への接続を金属を介して行われることが望ましい。本実施形態では、N<sup>+</sup>型半導体3に接続するコンタクトホールと、P<sup>+</sup>型半導体4に接続するコンタクトホールに金属を充填し接続電極10を形成し、両者を接続している。

接続電極10の材料は、データ信号線9に使用する材料であることが望ましい。データ信号線9と同一金属を用いれば、接続のための特別な工程が必要なくなるため、安価に製造することが可能となる。

接続のための金属としてほかには、画素電極(図7と図9)を用いることも可能である。

しかし、コンタクトホールは必ずしも必要ではなく、N<sup>+</sup>型半導体3とP<sup>+</sup>型半導体4の直上に金属層を形成してもよい。

## 【0042】

図12(A)、(B)と(C)は、図10(A)が示している本実施形態の液晶表示装置において、走査線WL<sub>n-1</sub>、WL<sub>n</sub>、及びWL<sub>n+1</sub>に印加する走査線電圧のタイミングチャートを示す。図12(A)において、V<sub>dd</sub>とV<sub>ssg</sub>は、それぞれ各画素のTFTトランジスタをON状態、及びOFF状態にする電圧である。ここで、一例として、V<sub>dd</sub>=13V、V<sub>ssg</sub>=-2V。

図12(B)では、破線は共通電極の電位、折れ線は画素電位の変化のタイミングを表わす。

図12(A)、(B)と(C)に示すように、画像を表示する時は、各走査線WL<sub>n-1</sub>、WL<sub>n</sub>、WL<sub>n+1</sub>、…が順次ハイレベル電圧信号(V<sub>dd</sub>)を各画素のトランジスタNT<sub>r1</sub>、NT<sub>r4</sub>、NT<sub>r2</sub>、NT<sub>r5</sub>に出力してONさせて、各画素を動作させる。

1画面を表示するには、各画素が一回しか動作せず、そのため、走査線電圧がV<sub>dd</sub>となる期間は、V<sub>ssg</sub>となる期間と比べて遙か短く、各トランジスタは1画面を表示する期間内にほとんどOFF状態に保持されている。即ち、該表示期間の殆どの部分に、WL<sub>n-1</sub>、WL<sub>n</sub>、及びWL<sub>n+1</sub>に-2Vの電圧を印加している。

これによって、図10と図11に示された、例えば、P型MOS補助容量PCS1は、その金属の電極(走査線)に、殆どの時間内に、-2Vの電圧を印加することになる。

## 【0043】

一方、補助容量PCS1の他方のP型半導体膜を含む電極については、トランジスタNT<sub>r1</sub>がON状態の場合は、トランジスタNT<sub>r1</sub>のソース・ドレインを介して、データ信号線BL<sub>n-1</sub>からのハイレベル信号が補助容量PCS1を充電しながら、液晶両側電極に電圧を印加する。補助容量PCS1が充電されると、その半導体膜電極の電位がV<sub>ssg</sub>より高くなる。また、トランジスタNT<sub>r1</sub>がOFF状態の場合は、トランジスタNT<sub>r1</sub>のソースとドレインが遮断され、データ信号線BL<sub>n-1</sub>からの信号が液晶と補助容量PCS1に電圧を供給せず、補助容量PCS1が液晶の両側の電極に電圧を供給する。

図12(B)に画素電位が図示されているように、補助容量PCS1の半導体膜の電位

(画素電位と同じである)が徐々に下がったり、上がったりしているが、常に  $V_{SSG}$  よりは高い。そうすると、補助容量 PCS1 の金属側(走査線側)から半導体膜までの電圧  $V_g$  は常に負電圧である。

#### 【0044】

図4のグラフについて既に説明したように、このような電圧  $V_g$  を走査線(金属)/ゲート絶縁膜/N型の半導体膜からなるN型MOS容量に印加すると、N型半導体の多数キャリアが電子であるので、負の走査線電圧(又は電圧  $V_g$ )では、多数キャリアが該半導体膜の表面から排斥され、空乏層(又/及び反転層)が形成されるので、補助容量の絶縁層が厚くなるのに相当し、図4に示されたように、得られる容量値は小さい。

図13は、P型MOS構造の容量-電圧特性を示すグラフである。

走査線(金属)/ゲート絶縁膜/P型の半導体膜からなるP型MOS容量において、P型半導体の多数キャリアがホールであるので、負の走査線電圧(又は、電圧  $V_g$ )では、P型半導体膜の表面で空乏層が形成されず、逆に多数キャリアが集まる。これによって、図13に示されたように、大きい容量値が得られる。

従って、本実施形態によって、通常の駆動条件の使用範囲(走査線電圧が  $V_{SSG}$  となる期間)において十分な容量が形成されている。

#### 【0045】

このように、通常画素トランジスタをNチャネル型で形成している場合には、補助容量はP型MOS容量で形成する必要があり、画素トランジスタをPチャネル型で形成している場合には、補助容量はN型MOS容量で形成することが望ましい。

本実施の形態では、補助容量を次段の走査線(ゲート線)WLnとで形成しているが、前段の走査線(ゲート線)WLn-2でもかまわない。

補助容量を形成している走査線WLnがハイレベルになったとき、従来では、画素電位が大幅にシフトしていたが、本実施形態のようなP型MOS容量にすることにより、走査線WLnがハイレベルになった時に、図12(B)に示すように、P型MOS容量が実効的に減少し、シフト量が減少する。これにより表示品質が向上する。

#### 【0046】

図14(A)と(B)は、本実施形態に係わる液晶表示装置の製造方法を示す。本実施形態の製造方法は、図5、図6、及び図7に示した従来の方法において、図6(A)に示した従来の製造方法の工程を変えたものである。

図5(D)の工程に続いて、図14(A)において、TFTトランジスタ近傍に燐の高濃度注入を行い、 $N^+$ 型半導体領域3を形成し、半導体層を金属化する。その時、補助容量近傍では、燐の高濃度注入を行わないように、レジスト11bが形成されている。このため、燐の高濃度注入を行った後に、補助容量の近傍は、図5(D)の工程と同じように、 $N^-$ 型半導体領域4aである。

また、従来行ってきた補助容量上の保護絶縁膜を除去する工程が不要となる。

図14(B)では、補助容量近傍のレジストパターン11bを除去し、補助容量の近傍に高濃度のボロンの注入を行い、 $P^+$ 型半導体領域4bを形成する。その時、TFTトランジスタ近傍では、ボロンの高濃度注入を行わないように、レジスト11cを形成している。

その後、必要に応じてドープした元素を活性化するための熱処理を行う。

#### 【0047】

以上に説明したように、本実施形態に係わる液晶表示装置は、第1の導電型の素子と、第2の導電型のMOS構造を含む。このような2種類の導電型の素子を用いれば、表示画素領域、若しくは、その外側領域、若しくは、その両方にCMOS型の駆動回路や論理回路を形成することが可能である。

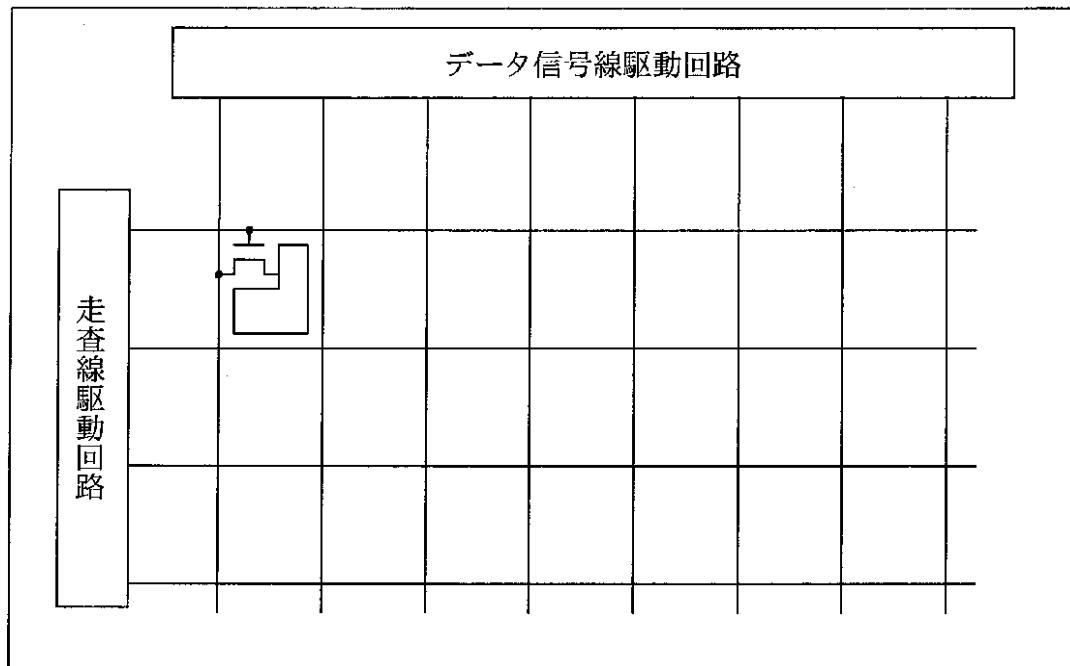

図15は、各画素がこのようなCMOSにより駆動される表示装置の構成の一例を示す。図15において、並列に配列した複数の走査線と複数のデータ信号線がそれぞれ走査線駆動回路とデータ信号線駆動回路によって駆動され、行列状に配列された各画素が、例えば、NチャネルTFTと、P型MOS容量により構成された駆動回路により駆動される。

また、そのような回路を有する液晶表示装置においては、本実施形態のような方法が、特別な工程の増加無しに構成することが可能となるため、最も適した構成例となる。例えば、高移動度を有するポリシリコン膜を半導体として用いているポリシリコントランジスタ液晶表示装置などで使用されることが望ましい。

#### 【0048】

本実施形態によれば、通常の駆動条件の使用範囲（走査線電圧がV<sub>SSG</sub>となる期間）において、補助容量に十分な容量が得られる。また、補助容量がCSオンゲート構造で形成できるので、高い開口率が得られる。

また、本実施形態の液晶装置製造方法によれば、半導体層がエッチングにさらされる工程が減るため、欠陥などが減少する。

#### 【0049】

##### 第2の実施形態

本実施形態は、本発明の液晶表示装置の他の構成例を示す。

図16と図17は、本実施形態に係わる液晶表示装置の構成の平面図と模式的断面図である。

図16と図17に示された液晶表示装置は、基本的に図10(B)と図11に示された構成と同じである。従って、本実施形態について、重複する説明を適宜省略し、また、図16と図17において、図10(B)と図11と同じ構成成分に同じ符号を用いる。

図16と図10(B)、及び図17と図11の違いは、図10(B)に示されたN<sup>+</sup>型半導体3とP<sup>+</sup>型半導体4を接続するコンタクトホールH2とH3は、図16に一つのコンタクトホールH4になっている。図11に示された2つのコンタクトホールに導電性物質を充填して形成された接続電極10は、図17において、同一のコンタクトホールに充填した導電材料で形成された接続電極30になっている。

#### 【0050】

N<sup>+</sup>型半導体3とP<sup>+</sup>型半導体4を接続するコンタクトは、両導電型にまたがる同一のコンタクトホールであることが望ましい。コンタクトホールを1つにすることにより画素内の領域を有效地に活用でき、開口率を向上する。

#### 【0051】

##### 第3の実施形態

本実施形態は、本発明の液晶表示装置の他の構成例を示す。

図18は、本実施形態に係わる液晶表示装置の構成の平面図である。

図18において、図16と図11と同じ構成成分に同じ符号を用いる。

図18と図11、図16の違いは、図18において、補助容量PCS1の一部がデータ信号線BLn-1の下部に配置されている。

この場合には、必要な補助容量を形成するのに必要な領域が、もともと光が透過しない領域、例えば、金属領域（ここではデータ信号線）に形成されているため、透過率のロスが少くなり、大きな開口率を確保することが可能となる。

この場合、トランジスタ構造は、ボトムゲート型でも、トップゲート型でも形成可能である。

#### 【0052】

図18に示されたボトムゲート構造において、データ信号線BLn-1の下部に補助容量PCS1を形成する場合、半導体層上に保護絶縁膜が残るため、信号線・半導体膜間の結合容量が減少する。これにより、クロストークなど表示品質が向上する。

また、信号線下の電極とのカップリング容量が減少するため、トータルの信号線容量が減少し、信号線電位のナマリが減少して表示品質の向上が図れる。

#### 【0053】

##### 第4の実施形態

以上、ボトムゲート型のトランジスタ構造を例として説明してきたが、本発明はトップゲート型のトランジスタ構造にも適用できる。

図19は、本実施形態に係わるトップゲート構造の液晶表示装置の構成の1例の断面図

である。

図19の液晶表示装置においては、不図示の透明基板に形成された不図示の下地層に半導体膜43, 44, 45, 46が成膜され、その半導体膜の上にゲート絶縁膜42が形成され、さらにその上に走査線41aと41b(WLn-1とWLn)と層間絶縁膜48が形成される。これにより、TFTトランジスタ及び補助容量が形成される。

43はN<sup>+</sup>半導体領域、44はP<sup>+</sup>半導体領域である。半導体膜45の中央はiタイプの半導体膜であり、その両端はLDD領域である。半導体膜45はTFTトランジスタのチャネル領域を構成し、図19には、これはNチャネルである。46もiタイプの半導体膜である。

#### 【0054】

46も不純物が注入されていない、いわゆるiタイプの半導体膜である。層間絶縁層48において、N<sup>+</sup>半導体領域43、P<sup>+</sup>半導体領域44、コンタクトホールが形成されており、コンタクトホール内の導電材料が、N<sup>+</sup>半導体領域43とP<sup>+</sup>半導体領域44を接続する接続電極50を形成し、また、データ信号線49を形成する。

ゲート電極41a、ゲート絶縁膜42、及び半導体膜44と45がNチャネル型のTFTトランジスタを構成する。一方、ゲート電極41b、ゲート絶縁膜42、及び半導体膜44と46がPチャネル型のトランジスタを構成する、そのPチャネル型トランジスタの容量は補助容量として用いる。

以上示した構造は、図10(B)に示される構造を模式断面図にしたものである。また、図16に対応する構造でもかまわない。

また、画素トランジスタは、NチャネルでもPチャネルでもかまわない。

#### 【0055】

図20(A)と(B)は、本実施形態に係わるトップゲート構造を有する液晶表示装置の製造方法を示す。本実施形態の製造方法は、図8と図9に示した従来の製造方法において、図8(C)に示した従来の製造方法の工程を変えたものである。

図8(B)の工程に続いて、図20(A)において、TFTトランジスタ領域で、チャネル領域45両側のLDD領域を覆うような形状のレジスト47aを形成する。そして、TFTトランジスタ近傍に燐の高濃度注入を行ない、N<sup>+</sup>型半導体領域43を形成し、半導体層を金属化する。

#### 【0056】

その時、補助容量近傍では、燐の高濃度注入を行なわないように、レジスト47bが形成されている。このため、燐の高濃度注入を行なった後に、補助容量の近傍は、図8(B)と同じように、N<sup>-</sup>型半導体領域44aである。

図20(B)では、補助容量近傍のレジスト47bを除去し、補助容量の近傍に高濃度のボロンの注入を行ない、P<sup>+</sup>型半導体領域44bを形成する。その時、TFTトランジスタ近傍では、ボロンの高濃度注入を行なわないように、レジスト47cが形成されている。

その後、必要に応じてドープした元素を活性化するための熱処理を行なう。

#### 【0057】

本実施形態は、第1、2の実施形態と同じ効果を有する。

#### 【0058】

以上、本発明を好ましい実施の形態に基づき説明したが、本発明は以上に説明した実施の形態に限られるものではなく、本発明の要旨を逸脱しない範囲で、種々の改変が可能である。

以上の実施例では、液晶表示装置を例として説明したが、他の駆動方法が類似する表示装置にも応用できる。

#### 【0059】

##### 【発明の効果】

本発明によれば、従来出来なかったスイッチングトランジスタと補助容量の構造が可能となり、補助容量が増大し、開口率が向上する。

本発明に係わる表示装置を製造するに当たって、工程数の増加なし、若しくは少ない工程数で、有効な補助容量を形成することが可能となる。

また、半導体層表面がウェットエッティングやドライエッティングにさらされる回数が減少するため、半導体層 - 補助容量用ゲート電極間のリーク電流などの欠陥発生率を抑制することが可能となり、歩留まりが向上する。

本発明により、非透過領域が減少し、大幅な開口率の向上が可能となる。また、それに伴い、バックライト輝度を低減することが可能となり、消費電力を低減することが可能となる。

#### 【図面の簡単な説明】

##### 【図 1】

従来の表示装置の一例の等価回路を示す。

##### 【図 2】

図 1 に示す従来の表示装置の構成の平面図を示す。

##### 【図 3】

(A) は、従来のボトムゲート構造を有する表示装置の他例の等価回路を示し、(B) は、該表示装置の構成の平面図を示す。

##### 【図 4】

図 3 に示された従来の表示装置において、補助容量の電圧 - 容量特性の測定結果を示すグラフである。

##### 【図 5】

(A) ~ (D) は、図 3 に示された従来の表示装置の製造方法を説明する断面図である。

##### 【図 6】

図 5 に続いて、(A) ~ (C) は、図 3 に示された従来の表示装置の製造方法を説明する断面図である。

##### 【図 7】

図 6 に続いて、(A) と (B) は、図 3 に示された従来の表示装置の製造方法を説明する断面図である。

##### 【図 8】

(A) ~ (C) は、従来のトップゲート構造を有する表示装置の製造方法を説明する断面図である。

##### 【図 9】

図 8 に続いて、(A) と (B) は、従来のトップゲート構造を有する表示装置の製造方法を説明する断面図である。

##### 【図 10】

(A) は、本発明の第 1 の実施形態に係わる表示装置の等価回路を示し、(B) は、該表示装置の構成の平面図を示す。

##### 【図 11】

本発明の第 1 の実施形態に係わる表示装置の構造を示す断面図である。

##### 【図 12】

(A) ~ (C) は、本発明の第 1 の実施形態に係わる表示装置において、走査線信号及び画素電位のタイミングチャートである。

##### 【図 13】

本発明の第 1 の実施形態に係わる表示装置において、補助容量の電圧 - 容量特性の測定結果を示すグラフである。

##### 【図 14】

(A) と (B) は、本発明の第 1 の実施形態に係わる表示装置の製造方法を説明する断面図である。

##### 【図 15】

本発明の第 1 の実施形態に係わる表示装置における駆動回路を示す図である。

**【図 16】**

本発明の第2の実施形態に係わる表示装置の構成の平面図を示す。

**【図 17】**

本発明の第2の実施形態に係わる表示装置の構成の断面図である。

**【図 18】**

本発明の第3の実施形態に係わる表示装置の構成の平面図を示す。

**【図 19】**

本発明の第4の実施形態に係わる表示装置の構成の断面図である。

**【図 20】**

(A)と(B)は、本発明の第4の実施形態に係わる表示装置の製造方法を説明する断面図である。

**【符号の説明】**

1 a、1 b … 走査線、2 … ゲート絶縁膜、3 … N<sup>+</sup>型半導体膜、4、4 b … P<sup>+</sup>型半導体膜、4 a … N<sup>-</sup>型半導体膜、5 … チャネル領域、6 … i型半導体膜、7 a、7 b … ストッパ絶縁膜、8 … 層間絶縁膜、9 … データ信号線、10 … 接続電極、11 a、11 b、11 c … レジスト、30 … 接続電極、40 … 下地層、41 a、41 b … 走査線、42 … ゲート絶縁膜、43 … N<sup>+</sup>型半導体膜、44、44 b … P<sup>+</sup>型半導体膜、44 a … N<sup>-</sup>型半導体膜、45 … チャネル領域、46 … i型半導体膜、48 … 層間絶縁膜、49 … データ信号線、50 … 接続電極、47 a、47 b、47 c … レジスト、101 … ガラス基板、102 a、102 b … 走査線、103 … ゲート絶縁膜、104 a、104 b、104 c … 半導体膜、105、105 a、105 b … 保護絶縁膜、107 a、107 b … レジスト、108 … レジスト、109 … 層間絶縁膜、110 a、110 b … コンタクトホール、111 a、111 b … データ信号線、112 … 接続金属、113 … 第2の層間絶縁膜、114 … 画素電極、121 … ガラス基板、122 … 下地層、123 a、123 b、123 c … 半導体膜、124 … ゲート絶縁膜、125 a、125 b … ゲート電極(走査線)、126 … レジスト、127 … 層間絶縁膜、128 a、128 b … コンタクトホール、129 a、129 b … データ信号線、130 … 接続金属、131 … 第2の層間絶縁膜、132 … 画素電極、WL … 走査線、BL … データ信号線、CSL … 補助容量線、CS, PCS … 補助容量、Tr, NT r … トランジスタ、Cc1 … 液晶素子容量、H1、H2, H3、H4 … コンタクトホール。

**【手続補正2】**

【補正対象書類名】図面

【補正対象項目名】図15

【補正方法】変更

【補正の内容】

【図15】