(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5835736号

(P5835736)

(45) 発行日 平成27年12月24日(2015.12.24)

(24) 登録日 平成27年11月13日(2015.11.13)

(51) Int.Cl.

F 1

H02M 7/49 (2007.01)

H02M 7/501 (2007.01)H02M 7/49

H02M 7/501

請求項の数 2 (全 10 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2012-110382 (P2012-110382)  |

| (22) 出願日  | 平成24年5月14日 (2012.5.14)        |

| (65) 公開番号 | 特開2013-240161 (P2013-240161A) |

| (43) 公開日  | 平成25年11月28日 (2013.11.28)      |

| 審査請求日     | 平成26年10月17日 (2014.10.17)      |

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000006013<br>三菱電機株式会社<br>東京都千代田区丸の内二丁目7番3号 |

| (74) 代理人  | 100094916<br>弁理士 村上 啓吾                     |

| (74) 代理人  | 100073759<br>弁理士 大岩 増雄                     |

| (74) 代理人  | 100127672<br>弁理士 吉澤 憲治                     |

| (74) 代理人  | 100088199<br>弁理士 竹中 岳生                     |

| (72) 発明者  | 坂下 友一<br>東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内       |

最終頁に続く

(54) 【発明の名称】電力変換装置

## (57) 【特許請求の範囲】

## 【請求項 1】

それぞれ直流電圧源を有してこの直流電圧源からの直流電力を交流電力に変換する複数の単相インバータを備え、これらの各単相インバータを順次直列に接続して上記各単相インバータによる各発生電圧の総和を出力する電力変換器と、この電力変換器の出力電圧を制御する制御装置と、を備えた電力変換装置において、

上記各単相インバータの内、最も小さい直流電圧を生じる上記直流電圧源で動作する単相インバータの交流出力側に上記電力変換器の出力電流を検出する電流検出手段を配置し、上記電流検出手段の一端を制御 GND に接続したことを特徴とする電力変換装置。

## 【請求項 2】

上記複数の単相インバータの内、最も小さい直流電圧を生じる直流電圧源を有する単相インバータは、ハーフブリッジ型のものであり、このハーフブリッジ型の単相インバータを構成する 2 つの直流電圧源の中性点に上記電流検出手段を配置したことを特徴とする請求項 1 に記載の電力変換装置。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

この発明は、インバータから負荷に流れる出力電流を安価かつ精度良く検出可能な電力変換装置に関するものである。

## 【背景技術】

10

20

**【0002】**

モータを負荷とする可変速度駆動装置として PWM インバータが多く採用されている。そして、PWM インバータのスイッチング素子として MOSFET や IGBT 等の高速スイッチング素子が使用され、高いスイッチング周波数とすることで波形改善の向上が図られている。

**【0003】**

このような PWM インバータの制御特性は、電流検出器の検出精度に大きく依存し、一般的には、ホール CT が適用される。この場合に、ホール CT で検出する電流は、PWM インバータを構成するスイッチング素子のオン / オフで発生する数百ボルト /  $\mu$ s の電圧変化 ( $dV/dt$ ) に起因して、数 kHz の周波数で変動するようなスイッチングノイズを含む電流であり、そのスイッチングノイズが検出精度に大きく影響を与える。10

**【0004】**

このようなスイッチング素子のオン / オフで発生する電圧変化 ( $dV/dt$ ) に起因したスイッチングノイズの影響を最小限に抑制するため、従来技術では、電流検出器で得られる検出電流について、所定の周期毎に、この周期より十分短い時間間隔で複数回のサンプリングを行い、サンプリングして得られた各サンプル値の平均値を求め、この平均値を電流検出値として制御装置に取り込んでモータの速度制御を行うようにした方法が提案されている（例えば、下記の特許文献 1 参照）。

**【先行技術文献】****【特許文献】**

20

**【0005】****【特許文献 1】特開平 9 - 23658 号公報****【発明の概要】****【発明が解決しようとする課題】****【0006】**

しかし、このような検出方法では、上記の検出電流に含まれるスイッチングノイズの影響を小さくするほどの大きな平均化処理が必要となるため、その処理に時間がかかり、高速・高応答が要求されるモータの可変速度駆動装置に採用することが困難であるという問題があった。

**【0007】**

30

この発明は、上記のような問題点を解消するために成されたものであって、それぞれ直流電圧源を有してこの直流電圧源からの直流電力を交流電力に変換する複数の単相インバータを順次直列に接続して各単相インバータによる各発生電圧の総和を出力する電力変換器を採用し、スイッチングノイズの影響を受けることなく、安価でかつ精度良い電流検出が可能な電力変換装置を得ることを目的としている。

**【課題を解決するための手段】****【0008】**

この発明に係る電力変換装置は、それぞれ直流電圧源を有してこの直流電圧源からの直流電力を交流電力に変換する複数の単相インバータを備え、これらの各単相インバータを順次直列に接続して上記各単相インバータによる各発生電圧の総和を出力する電力変換器と、この電力変換器の出力電圧を制御する制御装置とを備え、上記各単相インバータの内、最も小さい直流電圧を生じる上記直流電圧源で動作する単相インバータの交流出力側に上記電力変換器の出力電流を検出する電流検出手段を配置し、上記電流検出手段の一端を制御 GND に接続したことを特徴としている。40

**【発明の効果】****【0009】**

この発明の電力変換装置は、最も小さい直流電圧を生じる直流電圧源で動作する単相インバータの交流出力側の直近に電流検出器を配置し、この電流検出手段の一端を制御 GND に接続しているため、単相インバータのスイッチング素子のオン / オフで発生する電圧変化 ( $dV/dt$ ) に起因したスイッチングノイズのみならず、コモンモードノイズの影

50

響が小さくなり、電力変換装置の出力電流を精度良く検出することができる。さらに、電流検出器として安価なシャント抵抗などを使用することができるため、低価格で実現可能となる。

【図面の簡単な説明】

【0010】

【図1】この発明の実施の形態1における電力変換装置が備える電力変換器の部分を示す構成図である。

【図2】この発明の実施の形態1における電力変換装置が備える制御装置の構成図である。

【図3】この発明の実施の形態1における制御装置のAD変換器の出力の説明図である。

10

【図4】この発明の実施の形態1における制御装置のゲート駆動信号分配部の動作の説明図である。

【図5】この発明の実施の形態1における各単相インバータの制御動作の説明図である。

【図6】この実施の形態1において、各単相インバータの出力電圧と電力変換器全体の出力電圧との関係を示す波形図である。

【図7】この発明の実施の形態2における電力変換装置が備える電力変換器の部分を示す構成図である。

【発明を実施するための形態】

【0011】

実施の形態1.

20

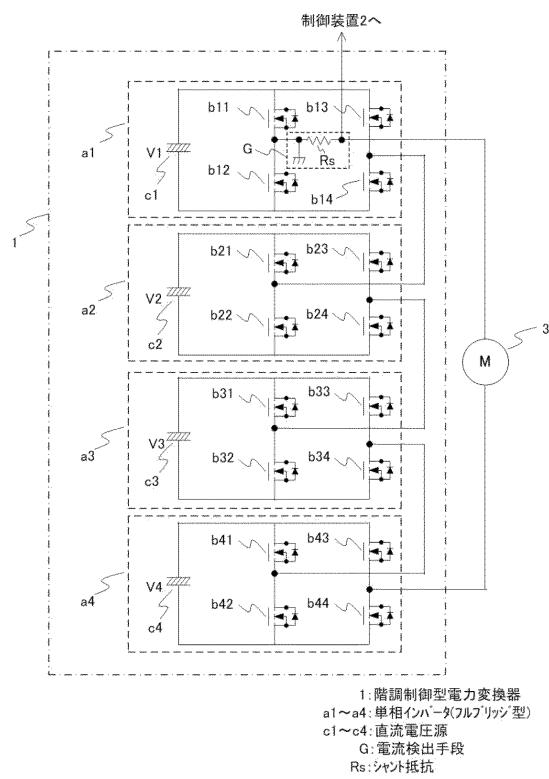

図1は、この発明の実施の形態1における電力変換装置が備える電力変換器の部分を示す構成図である。

【0012】

この実施の形態1の電力変換装置は、それぞれ異なる直流電圧V1～V4を発生する絶縁された直流電圧源c1～c4を有する4つの単相インバータa1～a4を備えている。そして、これらの各単相インバータa1～a4の交流出力側を順次直列に接続することにより、各単相インバータa1～a4による各発生電圧の総和を出力する電力変換器1が構成されている。以下、この構成の電力変換器1を階調制御型電力変換器1と称する。なお、各直流電圧源c1～c4に対しては、図示しないバッテリや太陽電池、AC/DCコンバータなどの別の直流電圧源から直流電力が供給される。

30

【0013】

この階調制御型電力変換器1を構成する各単相インバータa1～a4は、ダイオードを逆並列に接続した4つのMOSFET等の自己消弧型の半導体スイッチング素子b1(b11、…、b14)～b4(b41、…、b44)をフルブリッジ型に構成してなり、直流電圧源c1～c4からの直流電力を交流電力に変換して、負荷としてのモータ3に電力が供給される。この場合、各単相インバータa1～a4の直流電圧源c1～c4で発生する各直流電圧V1, V2, V3, V4は、1:2:4:8のように、2の累乗比の電圧比となるように予め設定されている。

【0014】

なお、この実施の形態1の階調制御型電力変換器1は、4つの単相インバータa1～a4を備えているが、単相インバータの数は4つに限定されるものではなく、2以上であればこの発明を適用可能である。また、自己消弧型の半導体スイッチング素子b1(b11、…、b14)～b4(b41、…、b44)として、ここではMOSFETを示しているが、これに限らずIGBT、GCT、GTO、トランジスタ等の半導体スイッチング素子を適用することができる。

40

【0015】

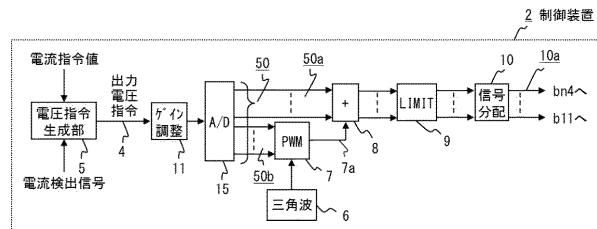

図2は、この発明の実施の形態1における電力変換装置が備える制御装置の構成図である。

【0016】

制御装置2は、ゲート駆動信号10aによって階調制御型電力変換器1の各単相インバ

50

ータ a 1 ~ a 4 の各スイッチング素子 b 1 ( b 1 1, . . . , b 1 4 ) ~ b 4 ( b 4 1, . . . , b 4 4 ) をオン / オフ駆動することによりその出力電圧を制御するものであり、電圧指令生成部 5 、ゲイン調整手段 1 1 、 A D 変換器 1 5 、三角波発生部 6 、 P W M 制御部 7 、信号加算部 8 、リミッタ 9 、およびゲート駆動信号分配部 1 0 を備える。

#### 【 0 0 1 7 】

電圧指令生成部 5 は、後述の電流検出手段 G で検出された電流と、モータ 3 を適切に動作させるために外部から与えられる電流指令値との偏差を求め、この偏差に基づいてこの偏差を小さくして零になるようにフィードバック制御するためのアナログの出力電圧指令 4 を生成する。

#### 【 0 0 1 8 】

このアナログの出力電圧指令 4 は、ゲイン調整手段 1 1 で適切な信号レベルに調整された後、 A D 変換器 1 5 でデジタル値に変換されて出力される。この場合のデジタル値に変換後の出力電圧指令 5 0 を、以下、デジタル電圧指令値 5 0 と称する。

#### 【 0 0 1 9 】

次に、上記構成の制御装置 2 における動作について説明する。なお、図 1 に示した階調制御型電力変換器 1 は、 n = 4 、すなわち 4 つの単相インバータ a 1 ~ a 4 を備えて構成されているが、図 2 ~ 図 5 を用いた以下の説明では、 n は 2 以上の自然数として、その個数を特定せずに一般化して説明することとする。

#### 【 0 0 2 0 】

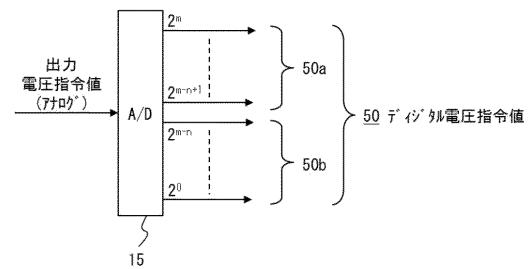

制御装置 2 の A D 変換器 1 5 によって、電圧指令生成部 5 からの出力電圧指令値（アナログ値） 4 がデジタル電圧指令値 5 0 に変換されるが、その際、図 3 に示すように、このデジタル電圧指令値 5 0 を、上位ビットからなる整数部 5 0 a と下位ビットからなる小数部 5 0 b とに分割する。デジタル電圧指令値 5 0 の上位ビットからなる整数部 5 0 a は、基本出力レベルとして生成されるもので、この整数部 5 0 a のビット数が、直列接続された各単相インバータ a 1 ~ a n の個数 n と等しくなるように、前段のゲイン調整手段 1 1 で調整しておく。

#### 【 0 0 2 1 】

これにより、上位 n ビットを整数部 5 0 a 、それより下位の下位ビットを小数部 5 0 b とし、整数部 5 0 a を信号加算部 8 へ、小数部 5 0 b を P W M 制御部 7 へそれぞれ出力する。 P W M 制御部 7 は、小数部 5 0 b を三角波発生部 6 からの三角波をキャリア波として比較し、 P W M 電圧指令 7 a を出力する。

#### 【 0 0 2 2 】

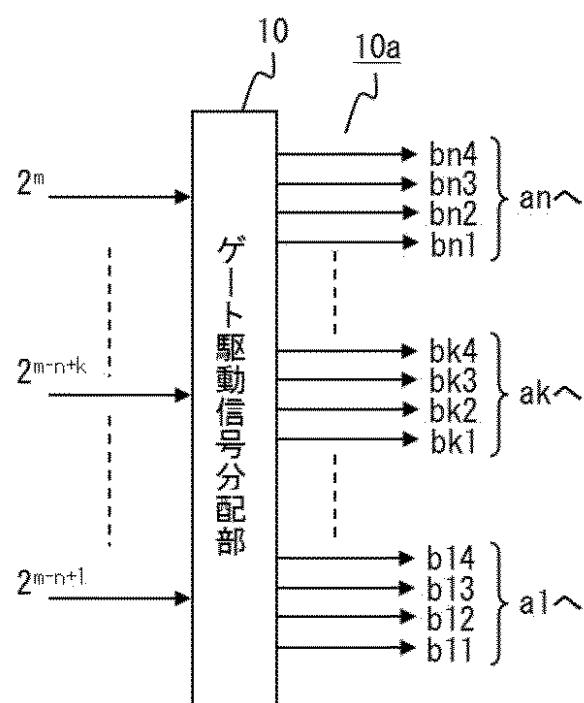

出力された P W M 電圧指令 7 a は、信号加算部 8 において上述の整数部 5 0 a の最下位ビットに加算される。加算結果はリミッタ 9 によって  $\pm 2^{m-n+k}$  ( $k = 1 \sim n$ ) の範囲に制限されてゲート駆動信号分配部 1 0 に入力される。ゲート駆動信号分配部 1 0 は、図 4 に示すように、階調制御型電力変換器 1 を構成する各単相インバータ a 1 ~ a n の半導体スイッチング素子 b 1 ( b 1 1 ~ b 1 4 ) ~ b n ( b n 1 ~ b n 4 ) への各ゲート駆動信号 1 0 a を生成する。

#### 【 0 0 2 3 】

この場合、 A D 変換器 1 5 の分解能を示すビット数を m とすると、整数部 5 0 a は  $2^{m-n+1} \sim 2^m$  、小数部 5 0 b は  $2^0 \sim 2^{m-n}$  のビットとなる。そして、直流電圧源 c 1 ~ c n の中で電圧が最低である直流電圧源 c 1 の電圧を 1 レベルとした基本出力レベルが整数部 5 0 a として決定される。また、小数部 5 0 b に基づいて生成された P W M 電圧指令 7 a は、基本出力レベルを示す整数部 5 0 a の最下位ビット  $2^{m-n+1}$  と等価であるため、信号加算部 8 において最下位ビット  $2^{m-n+1}$  に加算される。これにより、出力電圧の 1 レベルを P W M 制御することになる。

#### 【 0 0 2 4 】

また、 A D 変換器 1 5 のビット数 m の内、整数部 5 0 a のビット数は、階調制御型電力変換器 1 の構成で決まっているため、小数部 5 0 b に必要なビット数により A D 変換器 1 5 のビット数 m を決定する。すなわち、小数部 5 0 b が入力される P W M 制御部 7 が要求

する分解能から A D 変換器 1 5 の分解能を決定する。これにより、要求される制御が信頼性良く、かつ高速に実現することができる。

#### 【 0 0 2 5 】

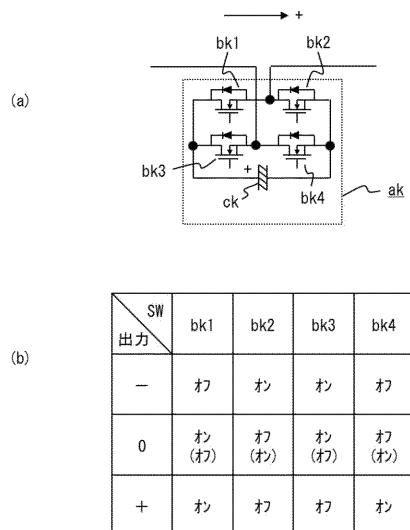

次に、ゲート駆動信号分配部 1 0 からのゲート駆動信号 1 0 a による各単相インバータ  $a_k$  ( $k ; 1 \sim n$ ) の制御について、図 5 を参照して説明する。

#### 【 0 0 2 6 】

ゲート駆動信号分配部 1 0 では、 $2_{m-n+k}$  のビットの入力信号から、例えば図 5 ( a ) に示す、ある一つの単相インバータ  $a_k$  に関し、その各半導体スイッチング素子  $b_k$   $1 \sim b_k 4$  に対するゲート駆動信号 1 0 a を生成する。また、ゲート駆動信号分配部 1 0 への入力信号には電圧極性が付随しており、図 5 ( b ) に示すように、入力信号 “ 0 ” か “ 1 ” の内、“ 0 ” の場合には出力 0 、“ 1 ” の場合には、電圧極性により正電圧 “ + ” あるいは負電圧 “ - ” を出力するように、オン / オフする半導体スイッチング素子  $b_k 1 \sim b_k 4$  を選択する。

10

#### 【 0 0 2 7 】

例えば、出力 “ 0 ” では、半導体スイッチング素子  $b_k 1$  および  $b_k 3$  を共にオンし、残りの半導体スイッチング素子  $b_k 2$  および  $b_k 4$  を共にオフする。あるいは半導体スイッチング素子  $b_k 2$  および  $b_k 4$  を共にオンし、残りの半導体スイッチング素子  $b_k 1$  および  $b_k 3$  を共にオフする。

#### 【 0 0 2 8 】

また、正電圧 “ + ” を出力するには、半導体スイッチング素子  $b_k 1$  および  $b_k 4$  をオンし、残りの半導体スイッチング素子  $b_k 2$  および  $b_k 3$  を共にオフする。一方、負電圧 “ - ” を出力するには、半導体スイッチング素子  $b_k 2$  および  $b_k 3$  を共にオンし、残りの半導体スイッチング素子  $b_k 1$  および  $b_k 4$  を共にオフする。

20

#### 【 0 0 2 9 】

以上のようにしてゲート駆動信号分配部 1 0 で生成されるゲート駆動信号 1 0 a によって、階調制御型電力変換器 1 内の各単相インバータ  $a_1 \sim a_n$  の直流電圧源  $c_1 \sim c_n$  の直流電圧  $V_1 \sim V_n$  を切り替えて各単相インバータ  $a_1 \sim a_n$  の出力電圧を制御する。

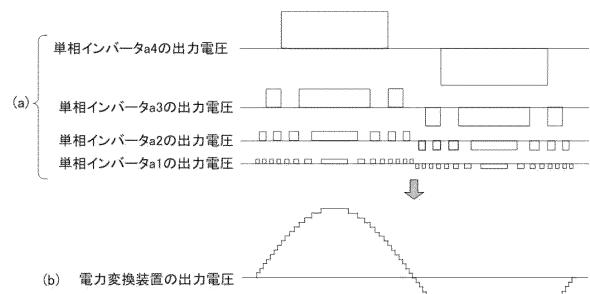

#### 【 0 0 3 0 】

これにより、例えば  $n = 4$  の場合において、各単相インバータ  $a_1 \sim a_4$  からは、それぞれ図 6 ( a ) に示すような出力電圧が得られ、これらの全ての単相インバータ  $a_1 \sim a_4$  の出力の総和が、図 6 ( b ) に示すように、モータ 3 へ供給する出力電圧として決定される。この場合、正弦波電圧を出力電圧目標にする場合、各単相インバータ  $a_1 \sim a_4$  の出力電圧の総和による階調制御型電力変換器 1 全体の出力電圧は、各単相インバータ  $a_1 \sim a_4$  の各出力レベルの内の 1 レベル分を P W M 制御した多レベルの電圧となり、歪の小さい波形出力が可能となる。

30

#### 【 0 0 3 1 】

この実施の形態 1 では、電圧指令生成部 5 から出力されるアナログの電圧指令値を A D 変換器 1 5 でデジタル値に変換した後のデジタル電圧指令値 5 0 について、上位ビットと下位ビットに分割するのみで整数部 5 0 a と小数部 5 0 b の抽出を行うため、各単相インバータ  $a_1 \sim a_4$  に対するゲート駆動信号を高速で生成でき、P W M 制御を合成した多レベル出力を実現する制御の高速化が図れる。また、制御装置 2 内に C P U 回路を不要にできるため、安価で高速制御が可能となる。また、整数部 5 0 a の最下位ビットに P W M 電圧指令 7 a を加算することにより、出力レベルの 1 レベル分を P W M 制御した多レベルの電圧の出力制御が容易に実現できる。また、各単相インバータ  $a_1 \sim a_4$  の直流電圧源  $c_1 \sim c_4$  の電圧比を、1 : 2 : 4 : 8 のように、2 の累乗比の電圧比となるようにしているので、多レベルの電圧出力が容易に得られる。また、A D 変換器 1 5 から出力されるデジタル電圧指令値 5 0 の整数部 5 0 a のビット数を、直列接続される複数の単相インバータ  $a_1 \sim a_4$  の個数に等しくすることで、制御が容易になり、制御装置 2 の回路構成の簡素化、および制御の高速化がさらに促進できる。

40

#### 【 0 0 3 2 】

なお、上記の説明では、直流電圧源 c 1 ~ c 4 の電圧比は 2 の累乗比としているが、これに限定されるものではなく、2 の累乗比以外でも良く、電圧が最低である直流電圧源 c 1 の電圧を 1 レベルとして電圧比が整数であればよい。これにより、電力変換装置全体の出力電圧は、各出力レベルの 1 レベル分を PWM 制御した多レベルの電圧となり、歪の小さい波形出力が同様に可能となる。この場合、出力可能な出力電圧レベルに応じて整数部 50 a のビット数が決定され、各単相インバータ a 1 ~ a 4 に対応する信号に変換されてからゲート駆動信号分配部 10 に入力される。

#### 【 0 0 3 3 】

この実施の形態 1 の特徴は、階調制御型電力変換器 1 を構成する各単相インバータ a 1 ~ a 4 の内、最も小さい直流電圧 V 1 を生じる直流電圧源 c 1 で動作する単相インバータ a 1 の交流出力側に、階調制御型電力変換器 1 の出力電流を検出する電流検出手段 G が配置されていることである。10

#### 【 0 0 3 4 】

すなわち、この電流検出手段 G は、上下アームのスイッチング素子 b 1 1、b 1 2 の接続点に近接して当該接続点とモータ 3 への電力出力経路との間に配置されたシャント抵抗 R s を備え、かつ、このシャント抵抗 R s の一端が制御 GND に接続されて構成されている。

#### 【 0 0 3 5 】

このように、この実施の形態 1 では、階調制御型電力変換器 1 を構成する各単相インバータ a 1 ~ a 4 の内、最も小さい直流電圧 V 1 の直流電圧源 c 1 を有する単相インバータ a 1 の交流出力側の直近に電流検出手段 G としてのシャント抵抗 R s を配置しているので、単相インバータ a 1 を構成するスイッチング素子 b 1 ( b 1 1、・・・、b 1 4 ) のオン / オフで発生する電圧変化 ( dV / dt ) に起因したスイッチングノイズの影響が低減され、かつ、シャント抵抗 R s の一端を制御 GND に接続していることによりコモンモードノイズの影響も小さくなる。このため、従来の PWM インバータを前提として電流検出を行う場合よりも電流検出精度が高くなる。また、シャント抵抗 R s を使用することができるため、安価な電流検出手段 G を構成することができる。20

#### 【 0 0 3 6 】

なお、実施の形態 1 では、電流検出手段 G として安価なシャント抵抗 R s を用いているが、ホール CT などの別の電流検出手段を適用することも可能である。また、この実施の形態 1 では、複数の単相インバータ a 1 ~ a 4 の出力電圧パルスの組合せによって交流波形を得る場合を示したが、直流電圧が最も小さい直流電圧源 c 1 を有する単相インバータ a 1 を PWM 制御して交流波形を得るようにしてよい。30

#### 【 0 0 3 7 】

例えば、階調制御型電力変換器 1 を 2 つの単相インバータで構成し、直流電圧が小さい単相インバータを PWM 制御し、直流電圧が大きい単相インバータは半周期毎に 1 パルスを出力することによって交流波形を得るような構成でも、インバータ動作時のスイッチングノイズの影響を小さくでき、かつ、コモンモードノイズの影響を小さくすることができる。

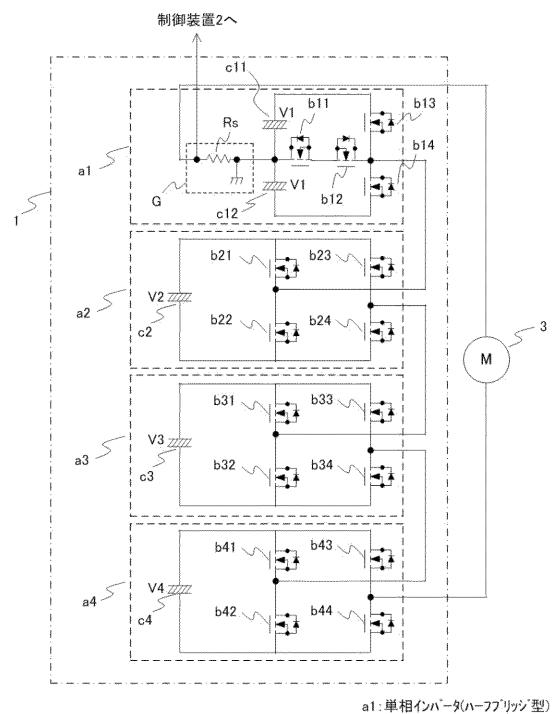

#### 【 0 0 3 8 】

実施の形態 2 。

図 7 は、この発明の実施の形態 2 における電力変換装置が備える階調制御型電力変換器の部分を示す構成図であり、図 1 に示した実施の形態 1 と対応もしくは相当する構成部分には同一の符号を付す。

#### 【 0 0 3 9 】

上記の実施の形態 1 では、4 つの単相インバータ a 1 ~ a 4 の全てがフルブリッジ型の構成のものであるに対し、この実施の形態 2 では、これらの単相インバータ a 1 ~ a 4 の内、最も小さい直流電圧 V 1 を生じる直流電圧源 c 1 1、c 1 2 を有する単相インバータ a 1 をハーフブリッジ型の構成にしたものである。すなわち、このハーフブリッジ型の構成の単相インバータ a 1 は、直流電圧 V 1 を生じる 2 つの電解コンデンサからなる直流電4050

圧源 c 1 1、c 1 2 を有するとともに、4 つの半導体スイッチング素子 b 1 1 ~ b 1 4 を備えて構成されている。

**【 0 0 4 0 】**

そして、この実施の形態 2 では、この最も小さい直流電圧 V 1 を生じる直流電圧源 c 1 1、c 1 2 で動作するハーフブリッジ型の単相インバータ a 1 の交流出力側に、階調制御型電力変換器 1 の出力電流を検出する電流検出手段 G が配置されている。

**【 0 0 4 1 】**

すなわち、この電流検出手段 G は、互いに直列に接続された 2 つの直流電圧源 c 1 1、c 1 2 の中性点に近接して当該中性点とモータ 3 への電力出力経路との間に配置されたシャント抵抗 R s を備え、かつ、このシャント抵抗 R s の一端が制御 G N D に接続されて構成されている。10

**【 0 0 4 2 】**

この構成によれば、シャント抵抗 R s の接続箇所が直流の中性点電位に固定されるため、この単相インバータ a 1 の回路内部の電位が高周波で変化することではなく、コモンモードノイズの影響を低減することができる。

**【 0 0 4 3 】**

以上のように、実施の形態 2 による電力変換装置では、階調制御型電力変換器 1 を構成する単相インバータ a 1 ~ a 4 の内、ハーフブリッジ型の単相インバータ a 1 の 2 直列の直流電圧源 c 1 1、c 1 2 の中性点の直近に、電流検出手段 G としてのシャント抵抗 R s を配置した構成としたので、単相インバータ a 1 を構成するスイッチング素子 b 1 ( b 1 1、. . . 、b 1 4 ) のオン / オフで発生する電圧変化 ( d V / d t ) に起因したスイッチングノイズを低減することができる。さらに、シャント抵抗 R s の電位が 2 つの直流電圧源 c 1 1、c 1 2 の中性点電位に固定されるため、コモンモードノイズの影響を低減することができる。また、シャント抵抗 R s を使用することができるため、安価な電流検出手段 G を構成することができる。20

**【 0 0 4 4 】**

なお、この実施の形態 2 についても、電流検出手段 G として安価なシャント抵抗 R s を用いているが、ホール C T などの別の電流検出手段を適用することも可能である。

**【 0 0 4 5 】**

また、この発明は上記の各実施の形態 1、2 の構成のみに限定されるものではなく、この発明の趣旨を逸脱しない範囲で各種の変形や応用を加えることができ、また、各実施の形態 1、2 の構成を適宜組み合わせることも可能である。30

**【 符号の説明 】**

**【 0 0 4 6 】**

1 階調制御型電力変換器、2 制御装置、3 モータ、

a 1 ~ a 4 単相インバータ、

b 1 1 ~ b 1 4 , b 2 1 ~ b 2 4 , b 3 1 ~ b 3 4 , b 4 1 ~ b 4 4 半導体スイッチング素子、

c 1 ~ c 4 , c 1 1 , c 1 2 直流電圧源、G 電流検出手段、

R s シャント抵抗。40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

(72)発明者 内山 研吾

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

審査官 梶木澤 昌司

(56)参考文献 特開2005-080414 (JP, A)

特開2011-155786 (JP, A)

特開2011-142740 (JP, A)

特開2010-148157 (JP, A)

特開平09-023658 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H02M 7/49

H02M 7/501