(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7336217号

(P7336217)

(45)発行日 令和5年8月31日(2023.8.31)

(24)登録日 令和5年8月23日(2023.8.23)

(51)国際特許分類

F I

H 0 4 N 25/773 (2023.01) H 0 4 N 25/773

H 0 4 N 25/10 (2023.01) H 0 4 N 25/10

請求項の数 22 (全18頁)

(21)出願番号 特願2019-45134(P2019-45134)

(22)出願日 平成31年3月12日(2019.3.12)

(65)公開番号 特開2020-150377(P2020-150377)

A)

(43)公開日 令和2年9月17日(2020.9.17)

審査請求日 令和4年3月14日(2022.3.14)

(73)特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74)代理人 110003281

弁理士法人大塚国際特許事務所

小川 武志

東京都大田区下丸子3丁目30番2号

(72)発明者 キヤノン株式会社内

鈴木 明

審査官

最終頁に続く

(54)【発明の名称】 情報処理装置、撮像素子、撮像装置、及び情報処理方法

## (57)【特許請求の範囲】

## 【請求項1】

複数の画素を有し、前記複数の画素がそれぞれ、光子の入射に応じてパルス信号を出力するセンサ手段と、前記パルス信号の数をカウントしてカウント値を生成するカウント手段と、を有する撮像素子から前記複数の画素の前記カウント値を順次取得し、該取得したカウント値に基づく信号値を補正する補正手段を有し、

前記カウント手段は、前記カウント値が所定値に達した場合に、カウント値をリセットした後カウントを継続し、

前記補正手段は、隣接する画素のカウント値に基づく信号値に基づいて、前記信号値のうち、カウント値をリセットした後カウントを継続して得られたカウント値に基づく信号値を補正することを特徴とする情報処理装置。

## 【請求項2】

前記補正手段は、前記複数の画素から順次取得したカウント値に基づく信号値を補正するか否かを、隣接する画素のカウント値に基づいて判断することを特徴とする請求項1に記載の情報処理装置。

## 【請求項3】

前記補正手段は、前記複数の画素から順次入力する第1のカウント値と、前記第1のカウント値を出力した画素に隣接する画素から出力された第2のカウント値が、予め決められた第1の条件を満たしてから、予め決められた第2の条件を満たすまでの第1の間、前記第1のカウント値に基づく信号値に前記所定値に基づく第1の信号値を加えることを特

徴とする請求項 1 に記載の情報処理装置。

【請求項 4】

前記カウント手段は、複数のビット数のバイナリカウンタであって、

前記補正手段は、前記第 1 の間、前記第 1 のカウント値に最上位ビットとして 1 を付加することで前記第 1 の信号値を補正することを特徴とする請求項 3 に記載の情報処理装置。

【請求項 5】

前記補正手段は、前記第 1 の間を除いて、前記第 1 のカウント値に最上位ビットとして 0 を付加することで前記第 1 の信号値を補正することを特徴とする請求項 3 または 4 に記載の情報処理装置。

【請求項 6】

10

前記カウント手段は、複数のビット数のバイナリカウンタであって、

前記複数の画素は、第 1 のビット数のカウント値を出力する前記カウント手段を有する画素と、前記第 1 のビット数よりも多い第 2 のビット数のカウント値を出力する前記カウント手段を有する画素とを含み、

前記第 2 のビット数のカウント値が入力された場合、前記補正手段は、当該カウント値に基づく信号値を補正しないことを特徴とする請求項 3 乃至 5 のいずれか 1 項に記載の情報処理装置。

【請求項 7】

前記第 1 の条件は、前記第 1 のカウント値と前記第 2 のカウント値との差が予め決められた第 1 の閾値より大きく、且つ、前記第 2 のカウント値が予め決められた第 2 の閾値より大きいことを特徴とする請求項 3 乃至 6 のいずれか 1 項に記載の情報処理装置。

20

【請求項 8】

前記第 2 の条件は、前記第 1 のカウント値と前記第 2 のカウント値との差が前記第 1 の閾値より大きく、且つ、前記第 2 のカウント値が、前記第 2 の閾値より小さい予め決められた第 3 の閾値より小さいことを特徴とする請求項 7 に記載の情報処理装置。

【請求項 9】

前記複数の画素は、複数の色のカラーフィルタによってそれぞれ覆われ、前記隣接する画素は、近傍の同色の画素であることを特徴とする請求項 2 に記載の情報処理装置。

【請求項 10】

前記複数の画素は、複数の色のカラーフィルタによってそれぞれ覆われ、

30

前記補正手段は、隣接する異なる色の画素との輝度比に基づいて、前記取得したカウント値が、カウント値をリセットした後カウントを継続して得られたカウント値であるかどうかを判断することを特徴とする請求項 1 に記載の情報処理装置。

【請求項 11】

前記センサ手段は、アバランシェフォトダイオードを含むことを特徴とする請求項 1 乃至 10 のいずれか 1 項に記載の情報処理装置。

【請求項 12】

前記カウント手段は、カウント値が最大値に達した場合に、前記カウント値を 0 にリセットした後カウントを継続することを特徴とする請求項 1 乃至 11 のいずれか 1 項に記載の情報処理装置。

40

【請求項 13】

複数の画素を有し、前記複数の画素がそれぞれ、

光子の入射に応じてパルス信号を出力するセンサ手段と、

前記パルス信号の数をカウントするカウント手段と、を有し、

前記カウント手段は、複数のビット数のバイナリカウンタであって、カウント値が所定値に達した場合に、カウント値をリセットした後カウントを継続し、

前記複数の画素は、複数の色のカラーフィルタによってそれぞれ覆われ、前記複数の色それぞれについて、予め決められた数の画素ごとに、他の画素よりもビット数の多いカウント値を出力する前記カウント手段を有することを特徴とする撮像素子。

【請求項 14】

50

複数の画素を有し、前記複数の画素がそれぞれ、

光子の入射に応じてパルス信号を出力するセンサ手段と、

前記パルス信号の数をカウントするカウント手段と、を有し、

前記カウント手段は、カウント値が所定値に達した場合に、カウント値をリセットした後カウントを継続することを特徴とする像素子と、

請求項 1 乃至 1 2 のいずれか 1 項に記載の情報処理装置と

を有することを特徴とする撮像装置。

【請求項 1 5】

前記カウント手段は、複数のビット数のバイナリカウンタであって、

前記複数の画素は、複数の色のカラーフィルタによってそれぞれ覆われ、前記複数の色の内、第 1 の色のカラーフィルタに対応する画素の前記カウント手段は、前記第 1 の色以外のカラーフィルタに対応する画素の前記カウント手段よりも、ビット数の多いカウント値を出力することを特徴とする請求項 1 4 に記載の撮像装置。

10

【請求項 1 6】

前記カウント手段は、複数のビット数のバイナリカウンタであって、

前記複数の画素は、複数の色のカラーフィルタによってそれぞれ覆われ、前記複数の色それぞれについて、予め決められた数の画素ごとに、他の画素よりもビット数の多いカウント値を出力する前記カウント手段を有することを特徴とする請求項 1 4 に記載の撮像装置。

20

【請求項 1 7】

複数のマイクロレンズを更に有し、

前記複数のマイクロレンズそれぞれに対し、2 つの前記画素を配置したことを特徴とする請求項 1 4 に記載の撮像装置。

【請求項 1 8】

前記センサ手段は、アバランシェフォトダイオードを含むことを特徴とする請求項 1 4 乃至 1 7 のいずれか 1 項に記載の撮像装置。

30

【請求項 1 9】

前記カウント手段は、カウント値が最大値に達した場合に、前記カウント値を 0 にリセットしてカウントを継続することを特徴とする請求項 1 4 乃至 1 8 のいずれか 1 項に記載の撮像装置。

【請求項 2 0】

複数の画素を有し、前記複数の画素がそれぞれ、光子の入射に応じてパルス信号を出力するセンサ手段と、前記パルス信号の数をカウントしてカウント値を生成するカウント手段と、を有する像素子から、取得手段が、前記複数の画素の前記カウント値を順次取得する取得工程と、

補正手段が、前記取得したカウント値に基づく信号値を補正する補正工程と、を有し、

前記カウント手段は、前記カウント値が所定値に達した場合に、カウント値をリセットした後カウントを継続し、

前記補正工程では、隣接する画素のカウント値に基づく信号値に基づいて、前記信号値のうち、カウント値をリセットした後カウントを継続して得られたカウント値に基づく信号値を補正することを特徴とする情報処理方法。

40

【請求項 2 1】

コンピュータを、請求項 1 乃至 1 2 のいずれか 1 項に記載の情報処理装置の各手段として機能させるためのプログラム。

【請求項 2 2】

請求項 2 1 に記載のプログラムを記憶したコンピュータが読み取り可能な記憶媒体。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、情報処理装置、像素子、撮像装置、及び情報処理方法に関する。

50

## 【背景技術】

## 【0002】

従来、スイッチングノイズや浮遊容量などに起因するS/N比の劣化を無くすことができる撮像素子の技術として、画素内でデジタル信号に変換する技術があった。

## 【0003】

例えば、特許文献1では入射したフォトン(光子)に応じて発生するパルスを計数手段によりカウントするしくみを画素内に備えた撮像素子が開示されている。

## 【0004】

また、特許文献2では、時分割フォトンカウンティングを用いた場合の露光設定の最適化を実現できる撮像素子およびカメラシステムが開示されている。

10

## 【先行技術文献】

## 【特許文献】

## 【0005】

## 【文献】特開平7-67043号公報

特開2011-71958号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0006】

しかしながら、上述の特許文献に開示された従来技術では、フォトンを計数するカウンタが画素内にあるため、高いダイナミックレンジを得るためにビット数を増やすと画素が大きくなり、小型化、高精細化が困難になってしまい、配線量の増加や電力の増加などコストアップの要因となる。

20

## 【0007】

本発明は上記問題点を鑑みてなされたものであり、画素内のカウンタのビット数を増やすことなく、ダイナミックレンジを拡大することを目的とする。

## 【課題を解決するための手段】

## 【0008】

上記目的を達成するために、本発明の情報処理装置は、複数の画素を有し、前記複数の画素がそれぞれ、光子の入射に応じてパルス信号を出力するセンサ手段と、前記パルス信号の数をカウントしてカウント値を生成するカウント手段と、を有する撮像素子から前記複数の画素の前記カウント値を順次取得し、該取得したカウント値に基づく信号値を補正する補正手段を有し、前記カウント手段は、前記カウント値が所定値に達した場合に、カウント値をリセットした後カウントを継続し、前記補正手段は、隣接する画素のカウント値に基づく信号値に基づいて、前記信号値のうち、カウント値をリセットした後カウントを継続して得られたカウント値に基づく信号値を補正する。

30

## 【発明の効果】

## 【0009】

本発明によれば、画素内のカウンタのビット数を増やすことなく、ダイナミックレンジを拡大することができる。

40

## 【図面の簡単な説明】

## 【0010】

## 【図1】第1及び第2の実施形態における撮像装置の概略構成を示すブロック図。

## 【図2】第1及び第2の実施形態におけるフォトンカウント型撮像素子に関する説明図。

## 【図3】第1の実施形態における各画素のカウンタのビット数の一例を示す図。

## 【図4】入射光量とカウント値との関係を示す図。

## 【図5】第1の実施形態における任意の行のカウント値及び補正後の画素値の一例を示す図。

## 【図6】第1の実施形態における撮像信号処理回路に含まれる補正回路の構成例を示す図。

## 【図7】第1の実施形態におけるカウント値と検出結果との関係を説明するための図。

## 【図8】第1の実施形態における各部の信号を示すタイミングチャート。

50

【図9】変形例2における画素配列例を示す図。

【図10】第2の実施形態における処理を示すフローチャート。

【発明を実施するための形態】

【0011】

以下、添付図面を参照して実施形態を詳しく説明する。尚、以下の実施形態は特許請求の範囲に係る発明を限定するものでなく、また実施形態で説明されている特徴の組み合わせの全てが発明に必須のものとは限らない。実施形態で説明されている複数の特徴うち二つ以上の特徴が任意に組み合わされてもよい。また、同一若しくは同様の構成には同一の参照番号を付し、重複した説明は省略する。

【0012】

<第1の実施形態>

以下、本発明の第1の実施形態による撮像素子および信号処理装置について説明する。

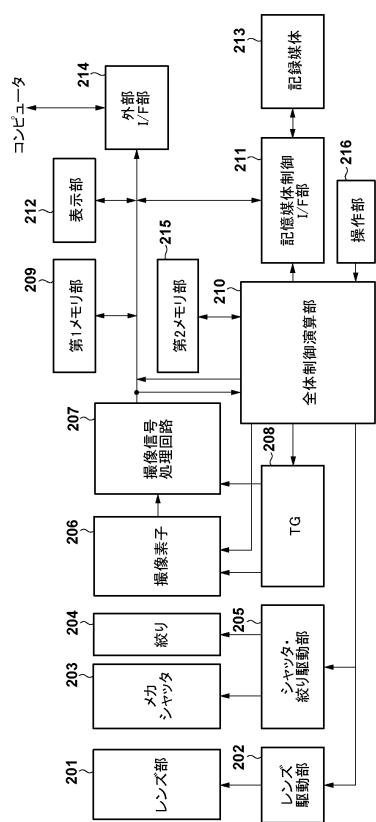

【0013】

図1は、第1の実施形態における撮像装置の概略構成を示すブロック図である。図1において、レンズ部201は、ズームレンズを含む複数枚のレンズにより構成され、レンズ駆動部202の制御により、Wide端からTele端まで、焦点距離を変化させることができる。

【0014】

メカニカルシャッタ(以下、「メカシャッタ」と記す。)203と、その後段の絞り204(光量調節部材)は、撮像素子206へ入射する光の照射時間を機械的に制御する露光量調整機構である。メカシャッタ203及び絞り204は、シャッタ・絞り駆動部205によって駆動制御される。

【0015】

ズームレンズを含むレンズ部201を通った被写体像は、メカシャッタ203及び絞り204により適切な露光量に調整され、撮像素子206に結像される。撮像素子206内の複数の画素に結像した被写体像は、撮像素子206内で2次元のデジタルデータに変換され、撮像信号処理回路207に送られる。なお、撮像素子206の詳細については後述する。

【0016】

撮像信号処理回路207は、本実施形態におけるカウント数の補正処理を行うと共に、補正した信号に対して、各種の画像処理を行う。画像処理は例えば、ノイズを軽減するローパスフィルタ処理やシェーディング補正処理、WB調整処理などを含む。更に、キズ補正処理やダークシェーディング補正処理、黒引き処理等の各種の補正、圧縮等を行って画像データを生成する。

【0017】

全体制御演算部210は、撮像装置全体の制御と各種演算を行う。タイミング発生部(以下、「TG」と記す。)208は、全体制御演算部210からの制御信号に基づき、撮像素子206を駆動させるための駆動パルスを発生させる。第1メモリ部209は、画像データを一時的に記憶する。

【0018】

記録媒体制御インターフェース(I/F)部211は、半導体メモリ等の着脱可能な記憶媒体である記録媒体213に対して画像データの記録及び読み出しを行う。表示部212は、画像データ等の表示を行う。外部インターフェース(I/F)部214は、外部コンピュータ等と通信を行う為のインターフェースである。

【0019】

第2メモリ部215は、全体制御演算部210での演算結果や撮影条件等の各種パラメータを記憶する。操作部216によりユーザーが設定した撮像装置の駆動条件に関する情報は、全体制御演算部210に送られ、これらの情報に基づいて撮像装置全体の制御が行われる。

【0020】

10

20

30

40

50

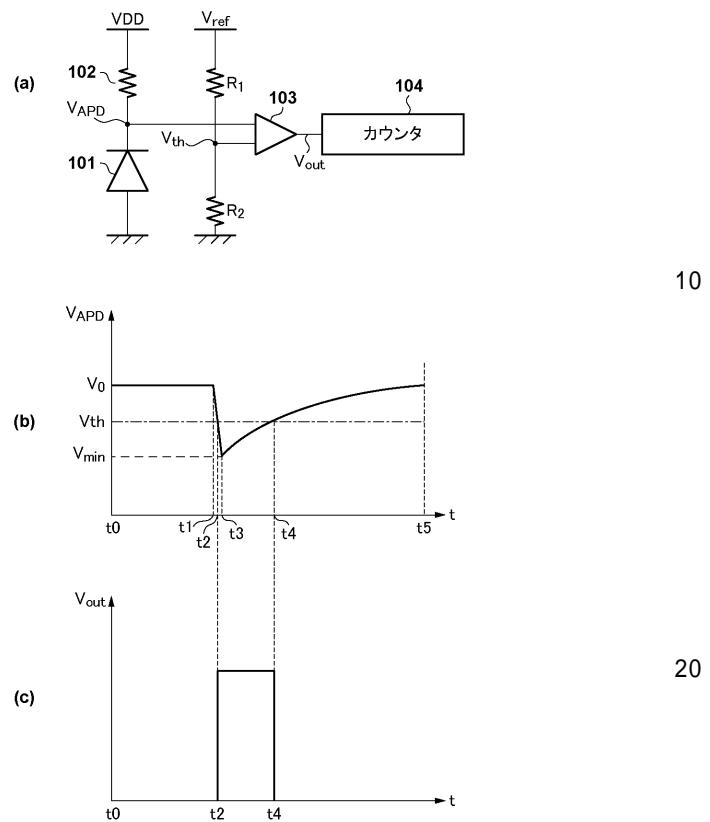

図2は、本実施形態における撮像素子206における各画素の概略構成を示す回路図であり、光子の入射に応じてパルス信号を出力するセンサ部と、出力されたパルス信号の数をカウントするカウンタを有する。本実施形態の撮像素子206は、アバランシェフォトダイオード(APD)をガイガーモードで動作させた際に発生するアバランシェ現象を利用して、入射したフォトン(光子)の数そのものを計測してデジタル信号として出力するものとする。このようなガイガーモードで動作させるアバランシェフォトダイオードは、SPAD(Single Photon Avalanche Diode)と呼ばれている。

#### 【0021】

APDをガイガーモードで動作させる時、例えばAPDに1つのフォトンが入射するとアバランシェ現象によって観測可能なレベルの電流が発生する。この電流をパルス信号に変換し、そのパルス信号の数をカウントすることで、入射するフォトンの個数を直接計測することが可能となる。そのため、RTSノイズが発生せず、S/N比の向上が期待されている。

10

#### 【0022】

ここで、本実施形態におけるSPADを用いたフォトンカウンティング型の撮像素子206の動作概要について、図2を用いて説明する。図2(a)は、SPADをガイガーモードで動作させる撮像素子206の単位画素(以下、「画素」と呼ぶ。)の等価回路を示している。画素は、アバランシェフォトダイオード(APD)101、クエンチ抵抗R102、コンパレータ103、抵抗R1, R2等により構成される。

20

#### 【0023】

APD101のアノード端はGNDに接続されており、カソード端はクエンチ抵抗R102に接続されている。そして、クエンチ抵抗R102を介して、電圧VDDから逆バイアス電圧が印加される。このとき電圧VDDとGNDの電圧差はAPD101をガイガーモードにする為に降伏電圧以上となるように設定する。

#### 【0024】

図2(b)はフォトン入射待機状態からアバランシェ現象が発生し、また元のフォトン入射待機状態に戻るまでのAPD101のカソード端の電圧V<sub>APD</sub>の推移を示している。時刻t0からt1の期間はフォトン入射待機状態であり、時刻t1でAPD101にフォトンが入射するとアバランシェ現象が発生する。アバランシェ現象が発生すると電流が流れで電圧V<sub>APD</sub>が低下してアバランシェ現象が止まり(時刻t3)、また元のフォトン入射待機状態に戻る(時刻t5)。

30

#### 【0025】

図2(a)に示すようにコンパレータ103の一方の入力端子にはAPD101のカソード端の電圧V<sub>APD</sub>が、もう一方の入力端子には基準電圧V<sub>ref</sub>を抵抗R1と抵抗R2とで分圧した参照電圧V<sub>th</sub>が入力されている。参照電圧V<sub>th</sub>は、上記で説明したフォトンが入射した際の電圧V<sub>APD</sub>の変化が検出できるように、V<sub>0</sub>とV<sub>min</sub>の間の電位に設定する。

#### 【0026】

コンパレータ103は、電圧V<sub>APD</sub>がV<sub>th</sub>より小さくなり、再び電圧V<sub>APD</sub>がV<sub>th</sub>より大きくなるまでの期間(電圧V<sub>APD</sub>がV<sub>th</sub>レベルを往復した期間)にパルス信号を1つ出力する。

40

#### 【0027】

図2(c)は、図2(b)に示すようにAPD101のカソード端の電圧V<sub>APD</sub>が推移した場合のコンパレータ103の出力V<sub>out</sub>を示している。時刻t2に電圧V<sub>APD</sub>がV<sub>th</sub>より小さくなり、時刻t4に再びV<sub>APD</sub>がV<sub>th</sub>より大きくなるため、t2~t4の期間にパルス信号が一つ出力される。

#### 【0028】

このコンパレータ103にカウンタ104を接続しておけば、入射したフォトンの数をカウントすることができる。従って、フォトン入射待機状態からアバランシェ現象の発生、アバランシェ現象の停止、また元のフォトン入射待機状態へ戻るサイクルを繰り返すこ

50

とで、A P D 1 0 1 に入射したフォトンの数を計測することができる。予め決められた時間、カウンタ 1 0 4 により計数されたカウント値を出力することで、画素信号を直接デジタル値で読み出すことができる。

【 0 0 2 9 】

このように、各画素からデジタル値として取得することができるため、スイッチングノイズや浮遊容量などに起因する S / N 比の劣化無く、転送することができる。

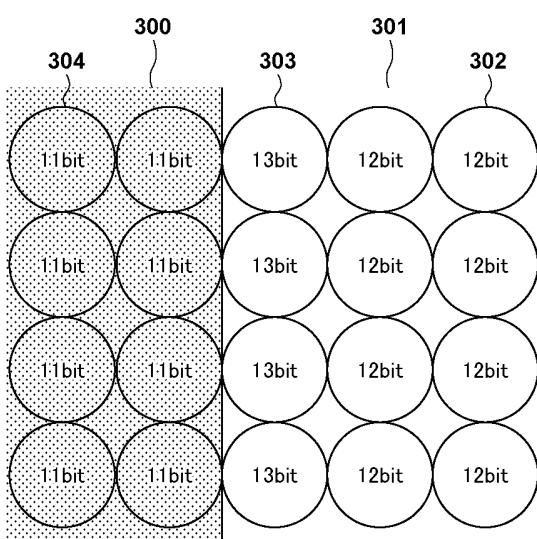

【 0 0 3 0 】

図 3 は、本実施形態における各画素のカウンタ 1 0 4 のビット数の一例を示す。本実施形態では、カウンタ 1 0 4 は複数のビット数のバイナリカウンタであって、ビット数はその構成により変更することができる。線よりも左側が遮光されているオプティカルブラック ( O\_B ) 領域 3 0 0 、右側が露光される露光領域 3 0 1 である。画素 3 0 4 は O\_B 領域 3 0 0 の画素で、カウンタ 1 0 4 のビット数は 1 1 ビット分、すなわち、 $2^{11}$  の値までカウントすることができる。画素 3 0 3 は O\_B 領域 3 0 0 に隣接した露光領域 3 0 1 の画素で、カウンタ 1 0 4 のビット数は 1 3 ビットで、 $2^{13}$  の値までカウントすることができる。そして、画素 3 0 2 は O\_B 領域 3 0 0 に隣接していない露光領域 3 0 1 の画素で、カウンタ 1 0 4 のビット数は 1 2 ビットで、 $2^{12}$  の値までカウントすることができる。

10

【 0 0 3 1 】

第 1 の実施形態では、後述するように、O\_B 領域 3 0 0 に隣接していない画素 3 0 2 の 1 2 ビットの画素値を、撮像信号処理回路 2 0 7 に含まれる補正回路において 1 3 ビットの画素値に補正することを想定している。なお、露光領域 3 0 1 の画素のうち、O\_B 領域 3 0 0 に隣接した画素 3 0 3 が 1 3 ビットである理由は、補正回路が、先に読み出された隣接する画素値を用いて補正をする構成を有しているためである。画素 3 0 3 の前に読み出される O\_B 領域 3 0 0 の画素 3 0 4 を用いて、画素 3 0 3 が最大値 C M A X を超えているかどうかを判断できないため、補正せずに 1 3 ビットの画素値が得られるように、1 3 ビットとしている。

20

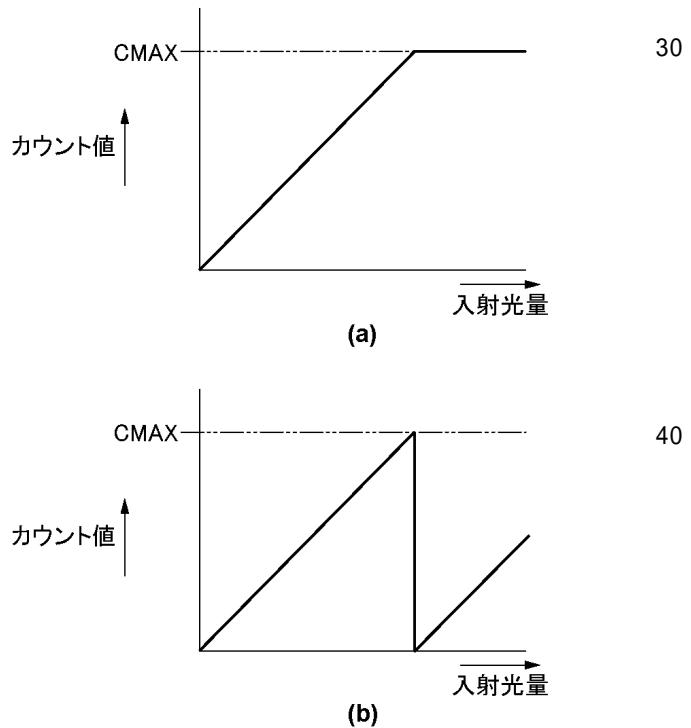

【 0 0 3 2 】

図 4 は、撮像素子への入射光量と、撮像素子の出力（カウント値）との関係を示したグラフである。ここでは比較のために、従来例のグラフを図 4 ( a ) に、本実施形態のグラフを図 4 ( b ) に示している。

30

【 0 0 3 3 】

図 4 ( a ) に示すように、従来は、入射光量が増加し、カウント値が最大値 C M A X に達すると、それ以上光が入射してもカウント値は変化しなくなる。

【 0 0 3 4 】

これに対し、本実施形態では、図 4 ( b ) に示すように、カウント値が最大値 C M A X に達した場合に、カウンタが停止せずに 0 に戻り、カウントし続けることを特徴としている。このように最大値 C M A X 後に 0 に戻してカウントが継続されたカウント値は、撮像信号処理回路 2 0 7 に含まれる補正回路により後述する手法で補正されて、画素値となる。

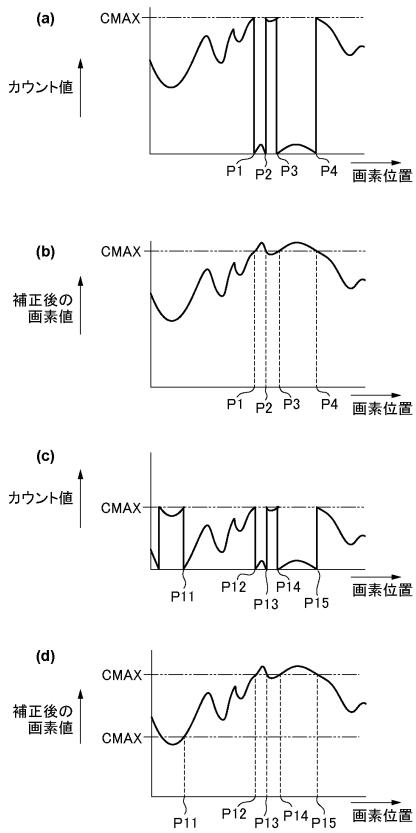

【 0 0 3 5 】

次に、図 5 ( a ) を参照して、図 3 に示すビット数で、図 4 ( b ) に示すようにカウントを行う場合に、撮像素子 2 0 6 の露光領域 3 0 1 の画素 3 0 2 及び 3 0 3 から得られる画素信号について説明する。

40

【 0 0 3 6 】

図 5 ( a ) において、縦軸は撮像素子 2 0 6 の任意の行における出力値、すなわちカウンタ 1 0 4 から出力されるカウント値を示し、横軸は水平方向の画素位置を示している。

【 0 0 3 7 】

P 1 ~ P 2 , P 3 ~ P 4 は、カウント値が最大値 C M A X を超えてしまった画素の範囲を示している。画素位置 P 1 及び P 3 の直前の画素において最大値 C M A X であった信号が、画素の範囲 P 1 ~ P 2 , P 3 ~ P 4 ではゼロ近傍で変化している。このような画素の範囲 P 1 ~ P 2 , P 3 ~ P 4 のカウント値に対し、補正回路により補正する。

【 0 0 3 8 】

50

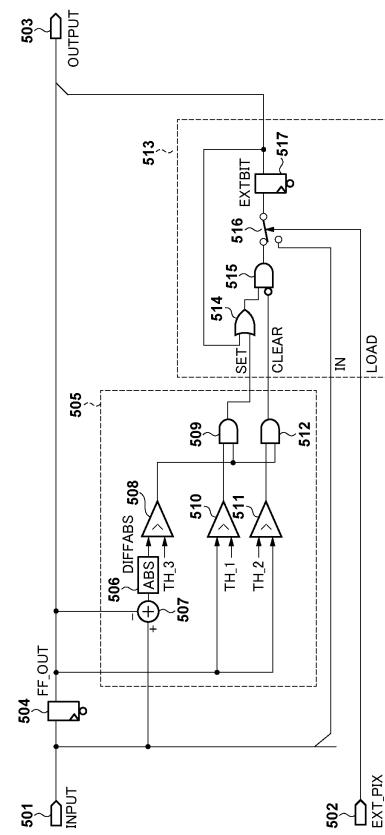

図6は、第1の実施形態における撮像信号処理回路207に含まれる補正回路の回路図である。撮像素子206から読み出されたカウント値は、端子501から、1サイクルに1画素分ずつ順次入力される。なお、撮像素子206と補正回路との間は、データ圧縮を含むプロトコルで接続されているが、補正回路の内部では、1サイクルに1画素分のカウント値がすべて13ビット(ビット0～12)で転送される。従って、画素302の12ビットのカウント値のビット12、及び、画素304の11ビットのカウント値のビット11及びビット12には、0が挿入されている。

#### 【0039】

端子501から入力されたカウント値は、遅延素子504に取り込まれ、1サイクル遅延される。そして、遅延素子504により1サイクル遅延されて出力されるのと同じタイミングで、次の画素のカウント値が入力される。以降、順次カウント値が入力され、遅延素子504により1サイクル遅延されて出力される。また、端子501から入力されたカウント値の内、付加されたビット12(最上位ビット)の値が、スイッチ516の一方の端子bに出力される。10

#### 【0040】

また、画素303のカウント値が入力される間、1となる信号EXT\_PIXが補正回路内で生成されて、端子502から入力される。信号EXT\_PIXが0の場合、スイッチ516は端子aを選択し、信号EXT\_PIXが1の場合、スイッチ516は端子bを選択する。従って、信号EXT\_PIXが1の場合、端子bに入力された画素303のビット12の値が選択され、それ以外の場合に、端子aに入力される論理積回路515の出力が選択されて、後段の遅延素子517に送られることになる。20

#### 【0041】

検出回路505は、カウント値が、その最大値MAXを超えてカウントし直された値であるかどうかを検出するための回路である。また、補正回路513は、カウント値が、最大値MAXを超えてカウントし直された値である場合に、そのカウント値に付加されたビット12(最上位ビット)に1を設定することにより補正し、それ以外の場合に0を設定する回路である。以下、検出回路505及び補正回路513について、詳細に説明する。

#### 【0042】

検出回路505において、減算器507は、現サイクルのカウント値(以下、「現カウント値」と呼ぶ。)から、遅延素子504により1サイクル遅延されたカウント値(以下、「遅延カウント値」と呼ぶ。)を減算し、絶対値化部506は、得られた差を正の値にする。そして、第1の比較部508は、絶対値化部506の出力が閾値TH\_3を超えているかどうかを比較により判定する。30

#### 【0043】

また、第2の比較部510は、遅延カウント値が閾値TH\_1を超えているかどうかを比較により判定し、第3の比較部511は、遅延カウント値が閾値TH\_2を下回っているかどうかを比較により判定する。

#### 【0044】

論理積回路509は、第1の比較部508と第2の比較部510の比較結果が共に真である場合に真を出力する。また、論理積回路512は、第1の比較部508と第3の比較部511の比較結果が共に真である場合に真を出力する。40

#### 【0045】

次に、補正回路513の動作について説明する。論理和回路514は、遅延素子517の出力と論理積回路509との論理和を取って、論理積回路515に出力する。論理積回路515は、論理積回路509の出力と、論理積回路512の反転入力との論理積を出力する。

#### 【0046】

スイッチ516は、上述したように、信号EXT\_PIXが0の場合、端子aを選択し、信号EXT\_PIXが1の場合、端子bを選択して、遅延素子517に出力する。遅延50

素子 517 は、入力した信号を 1 サイクル遅延させて出力する。

【0047】

遅延素子 517 から出力された値は、出力 503 のビット 12 として、遅延カウント値のビット 0 からビット 11 と束ねられて出力される。

【0048】

上記構成を有する補正回路では、論理積回路 509 の出力が真となるサイクルでは、論理積回路 512 の出力は必ず偽となり、その反転入力である真の信号が論理積回路 515 の一方の端子に入力される。従って、論理積回路 515 により、遅延素子 517 の出力と論理積回路 509 との論理和である真が後段に伝わるため、スイッチ 516 の端子 a が選択されている場合、次のサイクルでの遅延素子 517 の出力は真となる。

10

【0049】

また、論理積回路 512 の出力が真となる場合は、論理積回路 509 の出力は必ず偽となる。この場合、論理積回路 515 には、論理積回路 512 の反転入力である偽が入力されるため、論理和回路 514 の出力に関わらず、その出力は必ず偽となり、次のサイクルでの遅延素子 517 の出力は偽となる。

【0050】

また、画素 303 のカウント値が入力されるタイミングで、スイッチ 516 のコントロール端子に、端子 502 から入力される信号 EXT\_PIX が 1 となると、入力 501 の画素 303 のカウント値のビット 12 の値へ切り替わる。このため、次のサイクルでの遅延素子 517 の出力は、入力 501 のビット 12 の値となる。

20

【0051】

更に、第 1 の比較部 508 の比較結果が偽、即ち、信号間の差が小さい場合、論理積回路 509 と論理積回路 512 の出力は偽となり、論理積回路 515 には、論理積回路 512 の反転入力である偽が入力される。そのため、論理和回路 514 により、遅延素子 517 の出力が、論理積回路 515 の出力となり、1 サイクル前の遅延素子 517 の出力が保持されることとなる。

【0052】

このように、補正回路に入力される 13 ビットのカウント値に対し、条件に応じてビット 12 に 1、または 0 を設定することにより、12 ビットの画素から 13 ビットの信号を得ることが可能となる。

30

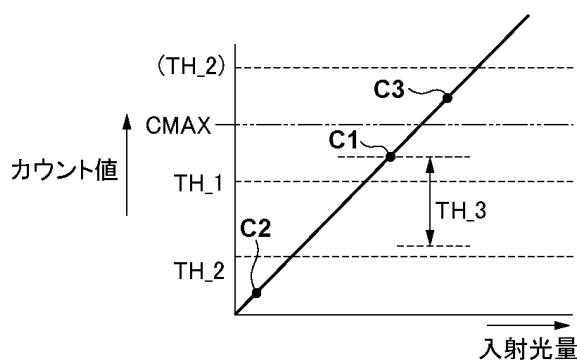

【0053】

ここで、図 7 を用いて、第 1 ~ 第 3 の比較部 508, 510, 511 それぞれの閾値 TH\_3, TH\_1, TH\_2 と、検出回路 505 における検出結果について説明する。図 7 において、横軸が入射光量、縦軸が撮像素子 206 の出力（カウント値）を示している。

【0054】

図 7 に示すように、遅延カウント値が C1、現カウント値が C2 であって、第 1 の比較部 508 の閾値 TH\_3 が図に示す範囲を有する場合、絶対値化部 506 の出力は、閾値 TH\_3 を超えているため、第 1 の比較部 508 の出力は真となる。このように、連続して入力するカウント値間の差が予め決められた閾値 TH\_3 を超える場合、最大値 CMAX を超えた事を示す条件 1 を満たすものとする。

40

【0055】

ここで、上記の様に判断する理由について簡単に説明する。撮像素子 206 がカラーの場合、同色の画素が離散的に存在するため、折り返しによる偽色が発生する事を防ぐ目的で光学的なローパスフィルタが撮像素子表面に張り付けられている。更に、光学的に隣接画素との間にクロストークが発生するなどのさまざまな要因により、隣接画素は一定の相関を持っているため、隣接画素の差が一定以上となる事はほぼ無い。

【0056】

従って、光学的なローパスフィルタなどの特性を考慮して閾値 TH\_3 を設定し、設定された閾値 TH\_3 を超えた場合、最大値 CMAX を超えたと考えることができる。そのため、条件 1 として、隣接画素との差が閾値 TH\_3 を超えることとしている。

50

## 【0057】

また、遅延カウント値 C 1 は、閾値 TH\_1 を超えているため（条件 2）、第 2 の比較部 510 の出力が真、論理積回路 509 の出力も真となり、更に、論理和回路 514 の出力も真となる。また、遅延カウント値 C 1 は、閾値 TH\_2 を超えているため第 3 の比較部 511 の出力は偽となり、論理積回路 512 の結果も偽となる。これにより、論理積回路 515 の出力は真となり、遅延素子 517 により 1 サイクル遅延されて、現カウント値のビット 12 に 1 が設定される。ビット 12 に 1 が設定されると、現カウント値 C 2 はカウント値 C 3 に変換されることになる。

## 【0058】

ここで、閾値 TH\_1 及び閾値 TH\_2 は、最大値 CMAX から所定量大きいか、または、小さい値を検出できるような値に設定される。なお、閾値 TH\_2 に関しては、最大値 CMAX を超えると、カウント値を 0 に戻してカウントを継続するため、ビット 12 が 0 である値を実際の比較に用いる閾値 TH\_2 としている。

10

## 【0059】

一方、遅延カウント値が C 2、現カウント値が C 1 であった場合、絶対値化部 506 の出力は、閾値 TH\_3 を超えているため、第 1 の比較部 508 の出力は真となる。また、カウント値 C 2 は、閾値 TH\_2 を下回っているため（条件 3）、第 3 の比較部 511 の出力が真、論理積回路 512 の出力も真となり、その反転入力である偽が論理積回路 515 に出力される。これにより、論理和回路 514 の出力に関わらず、論理積回路 515 の出力は偽となり、遅延素子 517 により 1 サイクル遅延されて、現カウント値のビット 12 に 0 が設定される。ビット 12 に 0 が設定されると、現カウント値 C 1 は変換されること無く、そのままの値で補正回路から出力される。

20

## 【0060】

このように、ビット 12 の値が補正回路 513 によって 1 または 0 に設定されると、次の検出回路 505 による信号値の大幅な変更の検出、または端子 502 からの信号 EXT\_PIX として 1 が入力することが無い限り、設定された値を保持する。

## 【0061】

上記のように図 6 の回路図で実現しているアルゴリズムを整理すると、

条件 1：隣接画素との差の絶対値が TH\_3 より大きい。

条件 2：遅延カウント値が TH\_1 より大きい。

30

条件 3：遅延カウント値が TH\_2 より小さい。

条件 4：画素 303 のカウント値が入力された。

として、

処理条件 1：条件 1 及び条件 2 が満たされた場合には、ビット 12 を 1 に設定

処理条件 2：条件 1 及び条件 3 が満たされた場合には、ビット 12 を 0 に設定

処理条件 3：条件 4 が満たされた場合には、画素 303 のビット 12 の値を設定

処理条件 4：いずれも満たされない場合には、設定されているビット 12 の値を保持という動作となる。

## 【0062】

図 5 (b) は、上述した処理を行う補正回路を用いて、図 5 (a) に示す信号のカウン

40

ト値の最大値 CMAX を超えた部分の信号を補正した状態の信号である。画素の範囲 P1

～P2、P3～P4 が最大値 CMAX よりも上に持ち上がっていることが分かる。

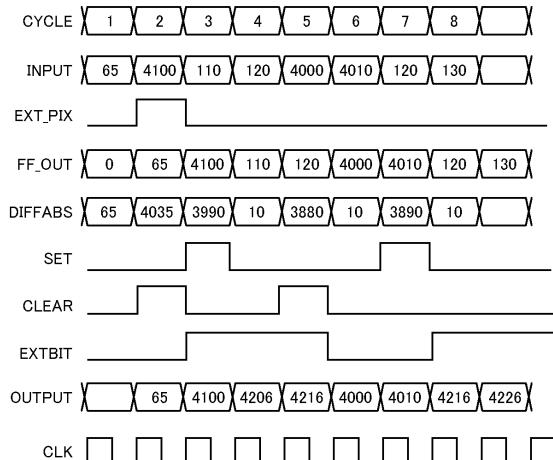

## 【0063】

次に、図 8 のタイミングチャートを参照して、図 6 に示す補正回路における各部の信号について具体的に説明する。

## 【0064】

図 8 において、CYCLE は、サイクル数を示している。INPUT は、入力端子 501 から入力される信号、EXT\_PIX は入力端子 502 から入力される信号、FF\_OUT は遅延素子 504 の出力、DIFFABS は絶対値化部 506 の出力である。また、SET は論理積回路 509 の出力、CLEAR は論理積回路 512 の出力、EXTBI

50

T は遅延素子 517 の出力、O U T P U T は出力端子 503 の出力、C L K は遅延素子 504, 517 及び上位回路ブロックと共有しているクロック信号である。

#### 【0065】

なお、初期値として、補正回路 513 の出力として 0 が出力されるように、遅延素子 517 には 0 を設定しておく。

#### 【0066】

1 サイクル目は、O B 領域 300 の画素 304 の 11 ビットの信号で、有効な情報としてはビット 10 までで、ビット 11 およびビット 12 には必ず 0 が入っている。これより先に I N P U T に入力された信号が無い場合、D I F F A B S は偽となり、S E T 及び C L E A R の値はともに偽となる。また、初期値として遅延素子 517 に 0 が設定されているため、この値が保持され、その結果、2 サイクル目の O U T P U T は 65 となる。10

#### 【0067】

2 サイクル目に画素 303 のカウント値である、ビット 12 が 1 である値 4100 が I N P U T に入力すると、E X T \_ P I X が 1 なので条件 4 を満たし、次の 3 サイクル目の E X T B I T は 1 が出力される。これに従い、3 サイクル目の O U T P U T の値は 4100 となる。

#### 【0068】

3 サイクル目で I N P U T に入力されるのは 110 という小さい値だが、E X T \_ P I X は 0 なので、入力されたカウント値のビット 12 ではなく、S E T 及び C L E A R の値により E X T B I T が変化する。隣接画素の F F \_ O U T の値 4100 との差である D I F F A B S の値は 4035 で、閾値 TH\_3 より大きく、F F \_ O U T の値 4100 が閾値 TH\_1 及び TH\_2 より大きいため、S E T は 1 、C L E A R は 0 になる。これにより、次のサイクルの E X T B I T は 1 となる。その結果、4 サイクル目の O U T P U T の値は、ビット 12 が 1 の値である 4206 として出力される。20

#### 【0069】

次の 4 サイクル目の I N P U T は 120 という小さい値が入ってきているが、D I F F A B S が閾値 TH\_3 を超えていないため、S E T 及び C L E A R は共に 0 になる。これにより、次の 5 サイクル目の E X T B I T は 4 サイクル目の値を保持して 1 のままとなり、O U T P U T の値は 4216 となる。

#### 【0070】

5 サイクル目で、I N P U T に 4000 という非常に大きな値が入力されると、D I F F A B S も 3880 と大きくなり、閾値 TH\_3 を超える。一方、F F \_ O U T は 4 サイクル目で入力した 120 で閾値 TH\_1 及び TH\_2 より小さいため、S E T は 0 、C L E A R は 1 となる。これにより、論理和回路 514 の出力に関わらず、論理積回路 515 の出力が偽となって、次のサイクルの E X T B I T が 0 となる。その結果、6 サイクル目の O U T P U T の値は、ビット 12 が 0 の値である 4000 となる。30

#### 【0071】

以降、入力した I N P U T 及び E X T \_ P I X の値に応じた処理を繰り返す。

#### 【0072】

このように、遅延素子 504 の F F \_ O U T は、3 ~ 6 サイクル目にかけて 4100 、 110 、 120 、 4000 と急激な変化をしている。しかしながら、E X T B I T を合成した補正結果の O U T P U T で見ると、4100 、 4206 、 4216 、 4000 という、急激ではない振幅の変化に留まっている。40

#### 【0073】

以上、一例として、12 ビット画素から 13 ビットの信号を得る方法を説明したが、本発明はカウンタ 104 のビット数により制限されるものでは無く、12 ビットや 13 ビット以外のビット数であっても構わない。

#### 【0074】

上記の通り第 1 の実施形態によれば、画素内のカウンタのビット数を超えた信号を得ることができる。

## 【0075】

また、第1の実施形態では、1サイクル前に入力された信号との比較により、カウント値が最大値C MAXを超えているかどうかを判断したが、本発明はこれに限られるものでは無い。例えば、上下に隣接する画素から得られるカウント値と比較したり、1フレーム前の対応する画素から得られるカウント値と比較するようにしても良く、その場合、画素303のような補正不要の画素を配置しない構成とすることも可能である。

## 【0076】

また、カラーフィルタに覆われたカラー撮像素子の場合は、同色画素の相関が高いことから、参照画素として近傍の同色の画素を用いて検出してもよい。または、輝度に対して色相や彩度の空間周波数が低い事から、周囲の色（色の異なる画素との間の輝度比）と着目画素の色の違いを検出することで、カウント値が最大値C MAXを超えてカウントし直された値であるかどうかを検出しても良い。

10

## 【0077】

また、上述した例では、条件2および条件3として遅延カウント値を閾値と比較して判断しているが、現カウント値を閾値と比較してもよい。

## 【0078】

更に、第1の実施形態の図3のOB領域300に隣接した画素303はビット数が多いが、フィルタの透過率を低く構成するか、APD101の光電変換の感度を低く構成して、最大値C MAXに達成しにくくして、補正回路で係数を掛けて補正してもよい。

20

## 【0079】

また、第1の実施形態における各画素のカウンタ104のトランジスタ部分は、全画素共通設計で配線層によりビット数の多い画素と少ない画素を構成してもよい。

## 【0080】

また、上述した第1の実施形態では、撮像素子206として、SPADを用いたフォトカウンティングタイプの撮像素子について説明したが、これに限られるものでは無く、フォトカウンティングタイプの撮像素子であれば、本発明を適用可能である。例えば、CMOSを用いたフォトカウンティングタイプの撮像素子に用いてもよい。

20

## 【0081】

## &lt;変形例1&gt;

上述した例では、12ビットのカウント値から13ビットのカウント値を得る場合について説明したが、11ビットのカウント値から13ビットのカウント値を得ることもできる。

30

## 【0082】

図5(c)は、カウンタ104から得られる11ビットのカウント値、図5(d)は、図5(c)に示す11ビットのカウント値から13ビットの画素値を得る場合の映像信号とカウント値の最大値C MAXとの関係を示す図である。図5(c)に示す例では、画素位置P11で最大値C MAXを超えた後に、画素位置P12, P14で再び最大値C MAXを超えており、画素の範囲P11～P12で最大値C MAXを超えて補正した部分が図5(d)の画素の範囲P11～P12で示すような波形となり、更に最大値C MAXを超えた部分が、画素の範囲P12～P13, P14～P15となる。このように11ビット画素から13ビット信号を得る場合は、最大値C MAXを2回超えることがあるが、第1の実施形態と同様の考え方で補正することが可能である。

40

## 【0083】

## &lt;変形例2&gt;

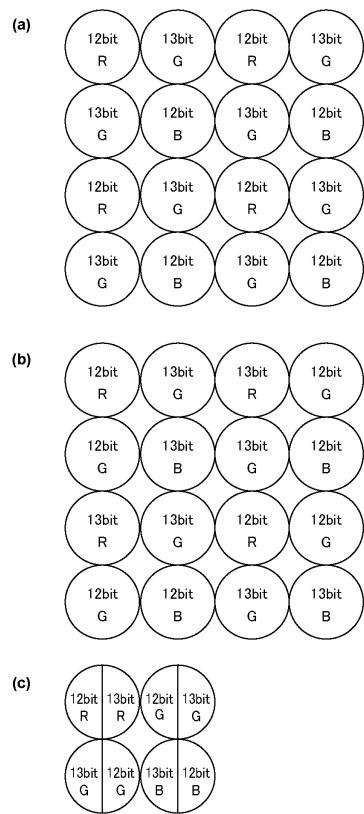

図9は画素配置の例を示している。図9(a)はカラーフィルタに覆われた撮像素子であり、緑色画素（第1の色の画素）に13ビット、赤色と青色画素（第1の色以外の画素）に12ビットが割り当てられている。青色は緑色に対して光量が少ない傾向にあるためビット数を少なくしている。仮に最大値C MAXを超えてても、第1の実施形態で上述した補正回路により補正可能である。

## 【0084】

50

図9 (b) は、それぞれの色に対して13ビット画素と12ビット画素を配置している。同じ色の画素を参照して補正する場合に一定の間隔で13ビット画素が入る構成である。

【0085】

図9 (c) は、1つのマイクロレンズに対して2つの画素を配置した例を示している。このような画素とすることで瞳分離された像を得ることが可能となる。同じマイクロレンズを共有した画素として異なるビットを持った画素とすることができる。

【0086】

<第2の実施形態>

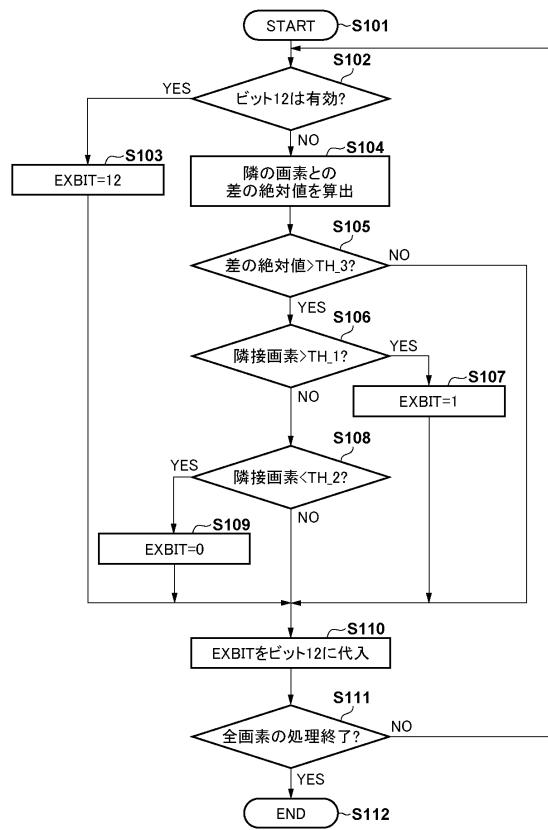

次に、図10を参照して、本発明の第2の実施形態における撮像信号処理について説明する。第2の実施形態では、コンピュータプログラムにより、カウント値が、カウント値の最大値C MAXを超えてカウントし直された値であるかどうかの検出と、ビットの補正とを行う。なお、第2の実施形態においても、12ビットのカウント値を13ビットに補正する場合について説明する。なお、以下の説明において、閾値TH\_1、TH\_2、TH\_3は、図7に示すものと同じとする。

10

【0087】

S101で処理を開始すると、S102で着目画素のビット12に有効な値が入っているかどうかを調べる。第1の実施形態では、端子502からEXT\_PIX信号が入力されるが、第2の実施形態では、配列中の位置などで決まっている。ビット12に有効な値(1)が入っていればS103へ、そうでなければS104に進む。S103の処理は、上述した処理条件3に対応する。

20

【0088】

S103では、着目画素のビット12の値(1)を変数EXTBITとして記憶する。変数EXTBITは第1の実施形態の遅延素子517の出力に相当する変数で、最終出力に添付されるものである。

【0089】

一方、S102でビット12に有効な値が入っていない場合はS104に進み、隣接画素との差の絶対値を算出する。

【0090】

そして、S105で差の絶対値が閾値TH\_3よりも大きいかどうかを判別する。差の絶対値が閾値TH\_3よりも大きい場合は条件1を満たしているのでS106へ進み、次の条件を満たしているかどうかを調べる。差の絶対値が閾値TH\_3以下の場合はS110に進む。この処理は、上述した処理条件4に対応する。

30

【0091】

S106では、隣接画素が閾値TH\_1よりも大きいかどうかを調べる。隣接画素がTH\_1よりも大きい場合は条件2を満たしたことになるのでS107へ進み、EXTBITに1を代入する。この処理は、上述した処理条件1に対応する。

【0092】

隣接画素が閾値TH\_1以下の場合は引き続きS108で次の条件を調べる。S108では隣接画素が閾値TH\_2よりも小さいかどうかを調べる。隣接画素が閾値TH\_2よりも小さい場合は条件3を満たすのでS109へ進み、EXTBITに0を代入する。この処理は、上述した処理条件2に対応する。隣接画素が閾値TH\_2よりも小さくない場合は、そのままS110へ進む。この処理は、上述した処理条件4に対応する。

40

【0093】

上記の処理により、S103、S105、S107、S108、S109のいずれかの後に、S110へ進む。S110では、変数EXTBITの値を着目画素のビット12に代入する。

【0094】

そして、S111において、全ての画素について処理を終えたかどうかを判断し、終えていなければ着目画素の位置を移動しながら、各行毎に、全画素に対して図10のフローチャートを実施する。なお、図10のフローチャートで参照している隣接画素は補正前の

50

画素なので、処理済みの画素は別のメモリなどに格納される事を想定している。

【0095】

上記の通り第2の実施形態によれば、コンピュータプログラムによる処理により、第1の実施形態と同様の効果を得ることができる。

【0096】

なお、上記処理は、撮像信号処理回路207で行っても良いし、全体制御演算部210により行ってもよい。また、撮像装置から、カウント値を補正せずに output し、外部の情報処理装置がこのカウント値を入力して行ってもよい。

【0097】

<他の実施形態>

10

また、本発明は、上述の実施形態の1以上の機能を実現するプログラムを、ネットワーク又は記憶媒体を介してシステム又は装置に供給し、そのシステム又は装置のコンピュータにおける1つ以上のプロセッサーがプログラムを読み出し実行する処理でも実現可能である。また、1以上の機能を実現する回路(例えば、A S I C)によっても実現可能である。

【0098】

発明は上記実施形態に制限されるものではなく、発明の精神及び範囲から離脱することなく、様々な変更及び変形が可能である。従って、発明の範囲を公にするために請求項を添付する。

【符号の説明】

【0099】

20

101：アバランシェフォトダイオード、103：コンパレータ、104：カウンタ、

206：差有象素子、207：撮像信号処理回路、210：全体制御演算部、214：外部インターフェース部、505：検出回路、513：補正部

30

40

50

【図面】

【図 1】

【図 2】

【図 3】

【図 4】

【図 5】

【図 6】

10

20

30

40

【図 7】

【図 8】

50

【図9】

【図10】

10

20

30

40

50

---

フロントページの続き

- (56)参考文献 特開2008-256700 (JP, A)

米国特許出願公開第2017/0230596 (US, A1)

- (58)調査した分野 (Int.Cl., DB名)

H04N 25/00 - 25/79