(19)日本国特許庁(JP)

## (12)公開特許公報(A)

(11)公開番号

特開2024-166313

(P2024-166313A)

(43)公開日 令和6年11月28日(2024.11.28)

## (51)国際特許分類

|        |                  |        |        |         |

|--------|------------------|--------|--------|---------|

| H 01 L | 29/786 (2006.01) | H 01 L | 29/78  | 6 1 8 B |

| H 01 L | 21/8234(2006.01) | H 01 L | 29/78  | 6 1 7 M |

| H 01 L | 27/088 (2006.01) | H 01 L | 27/06  | 1 0 2 A |

| H 10 B | 12/00 (2023.01)  | H 01 L | 27/088 | E       |

| H 10 B | 99/00 (2023.01)  | H 01 L | 27/088 | 3 3 1 E |

審査請求 有 請求項の数 3 O L (全77頁) 最終頁に続く

|                   |                                                                    |

|-------------------|--------------------------------------------------------------------|

| (21)出願番号          | 特願2024-156675(P2024-156675)                                        |

| (22)出願日           | 令和6年9月10日(2024.9.10)                                               |

| (62)分割の表示         | 特願2023-106946(P2023-106946)<br>の分割<br>原出願日 平成22年12月22日(2010.12.22) |

| (31)優先権主張番号       | 特願2009-293982(P2009-293982)                                        |

| (32)優先日           | 平成21年12月25日(2009.12.25)                                            |

| (33)優先権主張国・地域又は機関 | 日本国(JP)                                                            |

|         |                                                |

|---------|------------------------------------------------|

| (71)出願人 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (72)発明者 | 小山 潤<br>神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内        |

| (72)発明者 | 山崎 舜平<br>神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内       |

## (54)【発明の名称】 半導体装置

## (57)【要約】

【課題】複雑な作製工程を必要とせず、消費電力を抑え

ることができる記憶装置、当該記

憶装置を用いた半導体装置の提供を目的の一つとする。

【解決手段】インバータまたはクロックドインバータな

どの、入力された信号の位相を反

転させて出力する位相反転素子を用いた記憶素子内に、

データを保持するための容量素子

と、当該容量素子における電荷の蓄積及び放出を制御す

るスイッチング素子とを設ける。

上記スイッチング素子には、酸化物半導体をチャネル形

成領域に含むトランジスタを用い

る。位相反転素子への電源電圧の印加を停止する場合、

データを容量素子に記憶させるこ

とで、位相反転素子への電源電圧の供給を停止しても、

容量素子においてデータを保持さ

せる。

【選択図】図 1

10

**【特許請求の範囲】****【請求項 1】**

第1のトランジスタと、第2のトランジスタと、第1の絶縁膜と、第1の導電膜と、第2の導電膜と、を有し、

前記第1のトランジスタは、シリコン膜にチャネル形成領域を有し、

前記第2のトランジスタは、酸化物半導体膜にチャネル形成領域を有し、

前記第1の絶縁膜は、前記第1のトランジスタのゲート電極の上方に位置する領域を有し、

前記シリコン膜は、前記第1のトランジスタのソース電極またはドレイン電極の一方として機能する領域を有する第3の導電膜と接する領域を有し、

前記シリコン膜は、前記第1のトランジスタのソース電極またはドレイン電極の他方として機能する領域を有する第4の導電膜と接する領域を有し、

前記酸化物半導体膜は、前記第2のトランジスタのソース電極またはドレイン電極の一方として機能する領域を有する第5の導電膜と接する領域を有し、

前記第3の導電膜は、前記第1の絶縁膜の上方に位置する領域を有する第2の絶縁膜の上面と接する領域を有し、

前記第4の導電膜は、前記第2の絶縁膜の上面と接する領域を有しつつ前記第3の導電膜と同材料を有し、

前記第5の導電膜は、前記第2の絶縁膜の上面と接する領域を有しつつ前記第3の導電膜と同材料を有し、

前記第2のトランジスタのゲート電極は、前記第1の絶縁膜の上面と接する領域を有し、

前記第1の導電膜は、前記第1の絶縁膜の上面と接する領域を有しつつ前記第2のトランジスタのゲート電極と同材料を有し、

前記第1の導電膜は、前記第5の導電膜と重なる領域を有し、

前記第2の導電膜は、前記第1の絶縁膜の上面と接する領域を有しつつ前記第2のトランジスタのゲート電極と同材料を有し、

前記第2の導電膜は、前記第4の導電膜と接する領域を有し、

断面視において、前記第1のトランジスタのチャネル形成領域は、前記酸化物半導体膜と重ならない半導体装置。

**【請求項 2】**

請求項1において、

前記第2のトランジスタのゲート電極は、モリブデンを有する半導体装置。

**【請求項 3】**

請求項1または請求項2において、

前記酸化物半導体膜は、In-Oである半導体装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、記憶装置、及び当該記憶装置を用いた半導体装置、電子機器に関する。

**【背景技術】****【0002】**

絶縁表面上に形成される半導体膜を用いたトランジスタは、半導体装置にとって必要不可欠な半導体素子である。トランジスタの製造には基板の耐熱温度という制約があるため、比較的低温での成膜が可能なアモルファスシリコン、レーザ光または触媒元素を用いた結晶化により得られるポリシリコンなどを活性層に有するトランジスタが、半導体表示装置に用いられるトランジスタの主流となっている。

**【0003】**

近年では、ポリシリコンや微結晶シリコンによって得られる高い移動度と、アモルファスシリコンによって得られる均一な素子特性とを兼ね備えた新たな半導体材料として、酸化

10

20

30

40

50

物半導体と呼ばれる、半導体特性を示す金属酸化物に注目が集まっている。金属酸化物は様々な用途に用いられており、例えば、よく知られた金属酸化物である酸化インジウムは、液晶表示装置などで透明電極材料として用いられている。半導体特性を示す金属酸化物としては、例えば、酸化タンゲステン、酸化錫、酸化インジウム、酸化亜鉛などがあり、このような半導体特性を示す金属酸化物をチャネル形成領域に用いるトランジスタが、既に知られている（特許文献1及び特許文献2）。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2007-123861号公報

10

【特許文献2】特開2007-96055号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

ところで、記憶装置の一つであるレジスタは、一般的に、インバータ、クロックドインバータなどの論理素子と、スイッチング素子とで構成される論理回路である。メインメモリとして用いられているRAM(Random Access Memory)よりも遙かに高速で動作可能であることから、レジスタは、プロセッサにおいて、演算処理や、プログラムの実行状態の保持などのために、一時的にデータを保持するのに用いられている。

【0006】

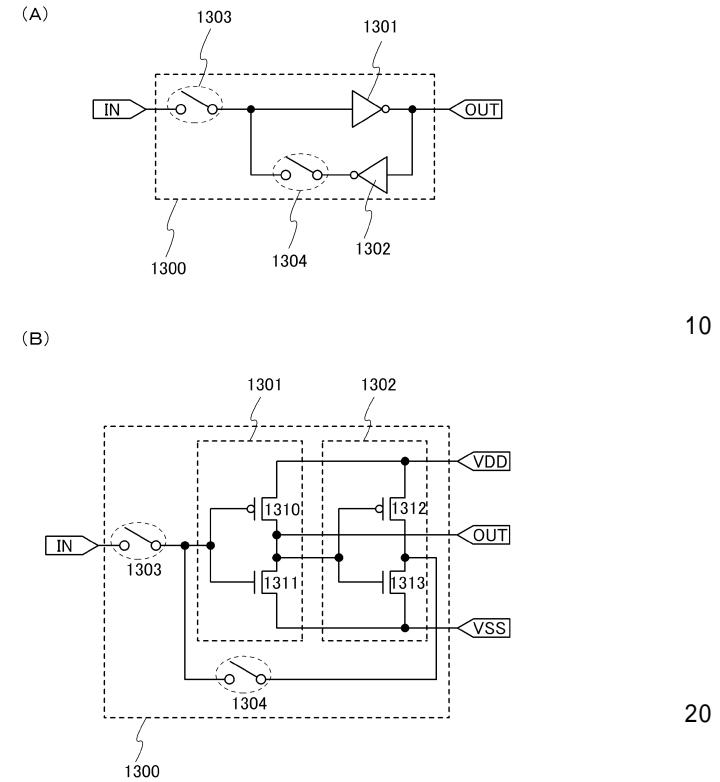

図16(A)に、インバータを用いたレジスタの構成する記憶素子の一つを示す。図16(A)に示すレジスタ1300は、インバータ1301、インバータ1302、スイッチング素子1303、スイッチング素子1304を有する。そして、インバータ1301の入力端子への信号INの入力は、スイッチング素子1303により制御されている。インバータ1301の出力端子の電位は、信号OUTとして、後段の回路に与えられる。また、インバータ1301の出力端子はインバータ1302の入力端子に接続されており、インバータ1302の出力端子は、スイッチング素子1304を介してインバータ1301の入力端子に接続されている。

【0007】

スイッチング素子1303を介して入力された信号INの電位は、スイッチング素子1303がオフ、スイッチング素子1304がオンになることで、レジスタ1300内で保持される。

【0008】

図16(A)に示したレジスタ1300の、より具体的な回路構成を、図16(B)に示す。図16(B)に示すレジスタ1300は、インバータ1301、インバータ1302、スイッチング素子1303、スイッチング素子1304を有しており、これら回路素子の接続構成は図16(A)と同じである。

【0009】

インバータ1301は、ゲート電極が互いに接続されたpチャネル型トランジスタ1310と、nチャネル型トランジスタ1311とを有している。そして、ハイレベルの電源電位VDDが与えられているノードと、ローレベルの電源電位VSSが与えられているノード間において、pチャネル型トランジスタ1310と、nチャネル型トランジスタ1311とは、直列に接続されている。また、同様に、インバータ1302は、ゲート電極が互いに接続されたpチャネル型トランジスタ1312と、nチャネル型トランジスタ1313とを有している。そして、ハイレベルの電源電位VDDが与えられているノードと、ローレベルの電源電位VSSが与えられているノード間において、pチャネル型トランジスタ1312と、nチャネル型トランジスタ1313とは、直列に接続されている。

【0010】

図16(B)に示すインバータ1301は、pチャネル型トランジスタ1310のゲート電極と、nチャネル型トランジスタ1311のゲート電極に与えられる電位の高さに従つ

20

30

40

50

て、一方がオフ、他方がオンとなるように動作する。よって、電源電位 VDD が与えられているノードと、電源電位 VSS が与えられているノードとの間の電流は、理想的には、0 になるはずである。しかし、実際には、オフのはずのトランジスタに僅かなオフ電流が流れているため、上記ノード間の電流は、完全に 0 にはならない。インバータ 1302 についても同様の現象が生じるため、レジスタ 1300 には、データの書き込みが行われていない保持の状態でも、消費電力が発生する。

#### 【0011】

例えば、トランジスタのサイズにもよるが、バルクのシリコンを用いて作製されたインバータの場合、室温下、ノード間の電圧が約 3V の状態にて、1 pA 程度のオフ電流が生じる。図 16 (A)、図 16 (B) に示す記憶素子には、インバータ 1301 とインバータ 1302 の、2 つのインバータが設けられているので、2 pA 程度のオフ電流が生じる。そして、記憶素子数が約 10<sup>7</sup> 個程度であるレジスタの場合、オフ電流はレジスタ全体で 20 μA となる。そして、レジスタが設けられた IC チップの温度が上昇すれば、消費電力はさらに大きくなり、レジスタだけでオフ電流が数 mA に達する。

10

#### 【0012】

そこで、消費電力を抑えるため、レジスタへの電源電位の供給を停止するという一つの方法が提案されている。レジスタは電源電位の供給が途絶えるとデータを消失してしまう揮発性の記憶装置であるため、その方法では、レジスタに長時間データを保持する必要がある場合に、レジスタ周辺に配置された不揮発性の記憶装置に上記データを一時的に移す。しかし、これらの不揮発性の記憶装置は、主に磁気素子や強誘電体が用いられているため、作製工程が複雑である。

20

#### 【0013】

また、長時間の電源停止を行う際には、データをハードディスク、フラッシュメモリ等の記憶装置に移してから電源停止を行うこともできるが、それらの記憶装置はデータを元に戻すのに時間を必要とするため、短時間の電源停止には適さない。

30

#### 【0014】

上述の課題に鑑み、本発明は、複雑な作製工程を必要とせず、消費電力を抑えることができる記憶装置、当該記憶装置を用いた半導体装置、電子機器の提供を目的の一つとする。特に、短時間の電源停止により消費電力を抑えることができる記憶装置、当該記憶装置を用いた半導体装置、電子機器の提供を目的の一つとする。

30

#### 【課題を解決するための手段】

#### 【0015】

インバータまたはクロックドインバータなどの、入力された信号の位相を反転させて出力する論理素子（以下、位相反転素子と呼ぶ）を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積及び放出を制御するスイッチング素子とを設ける。そして、上記スイッチング素子には、酸化物半導体をチャネル形成領域に含むトランジスタを用いる。

30

#### 【0016】

具体的に、記憶素子は、2 つの位相反転素子と、容量素子と、当該容量素子における電荷の蓄積及び放出を制御するスイッチング素子とを少なくとも有する。記憶素子に入力されたデータを含む信号は、第 1 の位相反転素子の入力端子に与えられる。第 1 の位相反転素子の出力端子は、第 2 の位相反転素子の入力端子に接続されている。第 2 の位相反転素子の出力端子は、第 1 の位相反転素子の入力端子に接続されている。第 1 の位相反転素子の出力端子または第 2 の位相反転素子の入力端子の電位が、信号として後段の記憶素子、あるいは他の回路に出力される。

40

#### 【0017】

上記位相反転素子は、ゲート電極が互いに接続された少なくとも 1 つの p チャネル型トランジスタと、少なくとも 1 つの n チャネル型トランジスタとが、第 1 のノードと、第 2 のノードの間ににおいて、直列に接続された構成を有する。

40

#### 【0018】

50

そして、容量素子は、記憶素子に入力された信号のデータを必要に応じて記憶できるよう に、上記スイッチング素子を介して、上記信号の電位が与えられるノードに接続されて いる。

#### 【 0 0 1 9 】

第1のノードと、第2のノードの間に電源電圧が与えられている状態において、第1の位 相反転素子の入力端子にデータを含む信号が入力されると、第1の位相反転素子及び第2 の位相反転素子によって、そのデータが保持される。第1のノードと第2のノード間への 電源電圧の印加を停止する場合、電源電圧の印加を停止する前に、上記スイッチング素子 をオンにして、信号のデータを容量素子に記憶させる。上記構成により、位相反転素子への 電源電圧の印加を停止しても、記憶素子にデータを保持させることが可能である。

10

#### 【 0 0 2 0 】

そして、上記スイッチング素子に用いられるトランジスタのチャネル形成領域は、高純度 化された酸化物半導体を含んでいるため、オフ電流が著しく低いという特性を有している。

#### 【 0 0 2 1 】

酸化物半導体は、微結晶シリコンまたは多結晶シリコンによって得られる高い移動度と、 非晶質シリコンによって得られる均一な素子特性とを兼ね備えた、半導体特性を示す金属 酸化物である。そして、電子供与体（ドナー）となる水分または水素などの不純物が低減 されて高純度化された酸化物半導体（purified OS）は、i型（真性半導体）又はi型に限りなく近い（実質的にi型）半導体である。具体的には、二次イオン質量分 析法（SIMS：Secondary Ion Mass Spectrometry）により測定した、酸化物半導体に含まれる水素濃度の値が、 $5 \times 10^{19} / \text{cm}^3$ 以下、好ましくは $5 \times 10^{18} / \text{cm}^3$ 以下、より好ましくは $5 \times 10^{17} / \text{cm}^3$ 以下、さら に好ましくは $1 \times 10^{16} / \text{cm}^3$ 未満となるように、酸化物半導体に含まれる水分または水素などの不純物を除去する。上記構成により、ホール効果測定により測定できる酸化物半導体膜のキャリア密度を、 $1 \times 10^{14} \text{ cm}^{-3}$ 未満、好ましくは $1 \times 10^{12} \text{ cm}^{-3}$ 未満、さらに好ましくは測定限界以下の $1 \times 10^{11} \text{ cm}^{-3}$ 未満とすることが可能 である。即ち、酸化物半導体膜のキャリア密度を、限りなくゼロに近づけることができる。ま た、バンドギャップは2eV以上、好ましくは2.5eV以上、より好ましくは3eV以上である。よって、水分または水素などの不純物濃度が十分に低減されて高純度化された 酸化物半導体膜を用いることにより、トランジスタのオフ電流を下げることができる。

20

#### 【 0 0 2 2 】

ここで、酸化物半導体膜中及び導電膜中の、水素濃度の分析について触れておく。酸化物 半導体膜中及び導電膜中の水素濃度測定は、二次イオン質量分析法（SIMS：Secondary Ion Mass Spectrometry）で行う。SIMS分析は、その原理上、試料表面近傍や、材質が異なる膜との積層界面近傍のデータを正確に得るこ とが困難であることが知られている。そこで、膜中における水素濃度の厚さ方向の分布を SIMSで分析する場合、対象となる膜が存在する範囲において、値に極端な変動が無く、ほぼ一定の値が得られる領域における平均値を、水素濃度として採用する。また、測定 の対象となる膜の厚さが小さい場合、隣接する膜内の水素濃度の影響を受けて、ほぼ一定 の値が得られる領域を見いだせない場合がある。この場合、当該膜が存在する領域における、水素濃度の極大値または極小値を、当該膜中の水素濃度として採用する。さらに、当 該膜の存在する領域において、極大値を示す山型のピーク、極小値を示す谷型のピークが 存在しない場合、変曲点の値を水素濃度として採用する。

30

#### 【 0 0 2 3 】

なお、スパッタ等で成膜された酸化物半導体膜中には、不純物である水分または水素が多 量に含まれていることが判明している。水分または水素はドナー準位を形成しやすいため 、酸化物半導体にとって不純物である。そこで、本発明の一態様では、酸化物半導体膜 中の水分または水素などの不純物を低減するために、酸化物半導体膜に対して、減圧雰 囲気下、窒素や希ガスなどの不活性ガス雰囲気下、酸素ガス雰囲気下、又は超乾燥エア（C

40

50

R D S (キャビティリングダウンレーザー分光法) 方式の露点計を用いて測定した場合の水分量が 20 ppm (露点換算で -55 ) 以下、好ましくは 1 ppm 以下、好ましくは 10 ppb 以下の空気) 霧囲気下で加熱処理を行う。上記加熱処理は、500 以上 850 以下 (若しくはガラス基板の歪点以下)、好ましくは 550 以上 750 以下の温度範囲で行うのが望ましい。なお、この加熱処理は、用いる基板の耐熱温度を超えないものとする。水分または水素の加熱処理による脱離の効果については、T D S (Thermal Desorption Spectroscopy; 升温脱離ガス分析) により確認済みである。

#### 【0024】

加熱処理は、炉での熱処理またはラピッドサーマルアニール法 (RTA 法) を用いる。RTA 法は、ランプ光源を用いる方法と、加熱されたガス中に基板を移動させて短時間の熱処理を行う方法がある。RTA 法を用いると熱処理に要する時間を 0.1 時間よりも短くすることもできる。

#### 【0025】

具体的に、上述した加熱処理により高純度化された酸化物半導体膜を活性層として用いたトランジスタは、非常に低いオフ電流を示す。具体的には、例えば、チャネル幅 (W) が  $1 \times 10^6 \mu\text{m}$  でチャネル長 (L) が  $10 \mu\text{m}$  の素子であっても、ソース電極とドレイン電極間の電圧 (ドレイン電圧) が 1 V から 10 V の範囲における、オフ電流 (ゲート電極とソース電極間の電圧を 0 V 以下としたときのドレイン電流) を、半導体パラメータアライザの測定限界以下、すなわち  $1 \times 10^{-13} \text{ A}$  以下とすることができる。よって、オフ電流をトランジスタのチャネル幅で除した数値に相当するオフ電流密度は、 $100 \text{ zA}/\mu\text{m}$  以下である。さらに、保持容量の電荷を保持するためのスイッチング素子として、高純度化された酸化物半導体膜を有するゲート絶縁膜の厚さが  $100 \text{ nm}$  のトランジスタを用いて、保持容量の単位時間あたりの電荷量の推移から当該トランジスタのオフ電流を測定したところ、トランジスタのソース電極とドレイン電極間の電圧が 3 V の場合に、 $10 \text{ zA}/\mu\text{m}$  乃至  $100 \text{ zA}/\mu\text{m}$  という、さらに低いオフ電流密度が得られることが分かった。したがって、本発明の一態様に係る記憶装置では、高純度化された酸化物半導体膜を活性層として用いたトランジスタのオフ電流密度を、 $100 \text{ zA}/\mu\text{m}$  以下、好ましくは  $10 \text{ zA}/\mu\text{m}$  以下、更に好ましくは  $1 \text{ zA}/\mu\text{m}$  以下にすることができる。従って、高純度化された酸化物半導体膜を活性層として用いたトランジスタは、オフ電流が、結晶性を有するシリコンを用いたトランジスタに比べて著しく低い。

#### 【0026】

また、高純度化された酸化物半導体を用いたトランジスタは、オフ電流の温度依存性がほとんど現れない。その要因のひとつは、酸化物半導体中で電子供与体 (ドナー) となる不純物を除去して、酸化物半導体が高純度化することによって、導電型が限りなく真性型に近づき、フェルミ準位が禁制帯の中央に位置することである。また、他の要因として、酸化物半導体のエネルギーギャップが 3 eV 以上であり、熱励起キャリアが極めて少ないとが挙げられる。さらに、ソース電極及びドレイン電極が縮退した状態にあることも、温度依存性が現れない要因となっている。トランジスタの動作は、縮退したソース電極から酸化物半導体に注入されたキャリアによるものがほとんどであり、キャリア密度には温度依存性がないので、オフ電流の温度依存性がみられないと考えられる。

#### 【0027】

上記構成を有するトランジスタを、容量素子に蓄積された電荷を保持するためのスイッチング素子として用いることで、容量素子からの電荷のリーク電流を防ぐことができるため、電源電圧の印加がない場合でも、データを消失させずに保持することができる。そして、容量素子においてデータを保持している期間は、位相反転素子への電源電圧の供給を行わなくても良いので、位相反転素子に用いられているトランジスタのオフ電流に起因する無駄な消費電力を削減することができ、記憶装置、延いては記憶装置を用いた半導体装置全体の、消費電力を低く抑えることが可能となる。

#### 【0028】

10

20

30

40

50

なお、位相反転素子に用いられるトランジスタには、酸化物半導体以外の、非晶質、微結晶、多結晶、または単結晶の、シリコン、またはゲルマニウムなどの半導体を用いることができる。また、上記トランジスタは、薄膜の半導体膜を用いていても良いし、バルクの半導体基板を用いていても良い。酸化物半導体膜を用いたpチャネル型トランジスタを作製することができれば、記憶素子内の全てのトランジスタの活性層に酸化物半導体膜を用い、プロセスを簡略化することもできる。

#### 【0029】

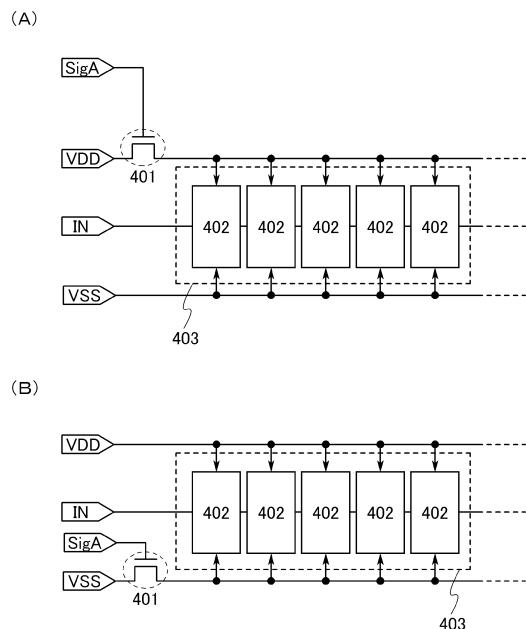

また、本発明の一態様では、記憶素子への電源電圧の供給を、酸化物半導体をチャネル形成領域に含むトランジスタを用いて制御しても良い。上述したように、酸化物半導体をチャネル形成領域に含むトランジスタは、3.0～3.5eVという、シリコンの約3倍程度の大きなバンドギャップを有している。よって、酸化物半導体をチャネル形成領域に含むトランジスタは高耐圧性を有するため、記憶素子への電源電圧の供給を上記トランジスタで制御することで、半導体装置の信頼性を高めることができる。10

#### 【0030】

なお、酸化物半導体は、四元系金属酸化物であるIn-Sn-Ga-Zn-O系酸化物半導体や、三元系金属酸化物であるIn-Ga-Zn-O系酸化物半導体、In-Sn-Zn-O系酸化物半導体、In-Al-Zn-O系酸化物半導体、Sn-Ga-Zn-O系酸化物半導体、Al-Ga-Zn-O系酸化物半導体、Sn-Al-Zn-O系酸化物半導体や、二元系金属酸化物であるIn-Zn-O系酸化物半導体、Sn-Zn-O系酸化物半導体、Al-Zn-O系酸化物半導体、Zn-Mg-O系酸化物半導体、Sn-Mg-O系酸化物半導体、In-Mg-O系酸化物半導体、In-Ga-O系酸化物半導体や、In-O系酸化物半導体、Sn-O系酸化物半導体、Zn-O系酸化物半導体などを用いることができる。なお、本明細書においては、例えば、In-Sn-Ga-Zn-O系酸化物半導体とは、インジウム(In)、錫(Sn)、ガリウム(Ga)、亜鉛(Zn)を有する金属酸化物、という意味であり、その化学量論的組成比は特に問わない。また、上記酸化物半導体は、珪素を含んでいてもよい。20

#### 【0031】

或いは、酸化物半導体は、化学式 $InM_3(ZnO)_m$ ( $m > 0$ )で表記することができる。ここで、Mは、Ga、Al、Mn及びCoから選ばれた一又は複数の金属元素を示す。30

#### 【発明の効果】

#### 【0032】

消費電力を抑えることができる記憶装置、当該記憶装置を用いた半導体装置を提供することができる。

#### 【図面の簡単な説明】

#### 【0033】

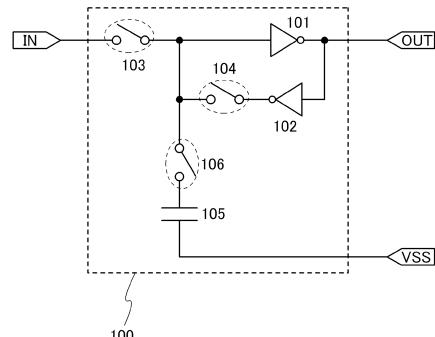

【図1】記憶素子の回路図。

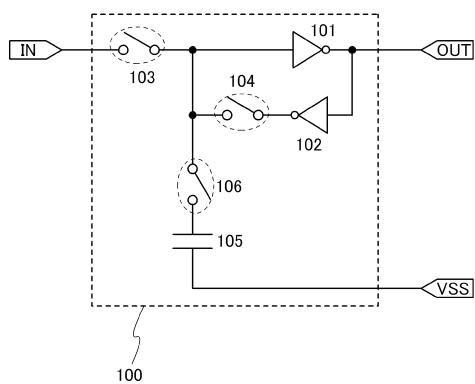

【図2】記憶素子の回路図。

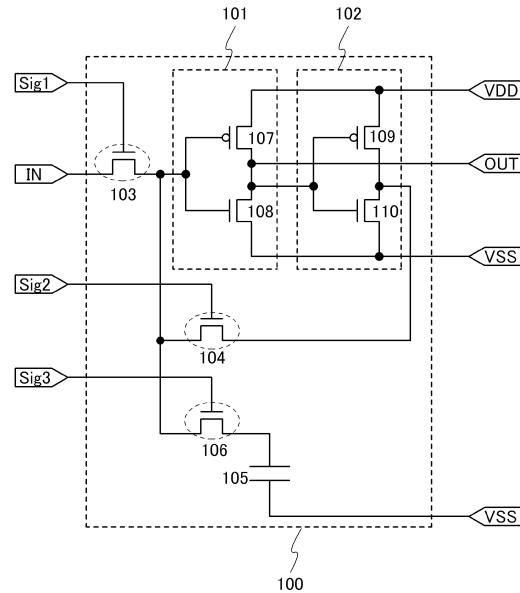

【図3】記憶素子の回路図。

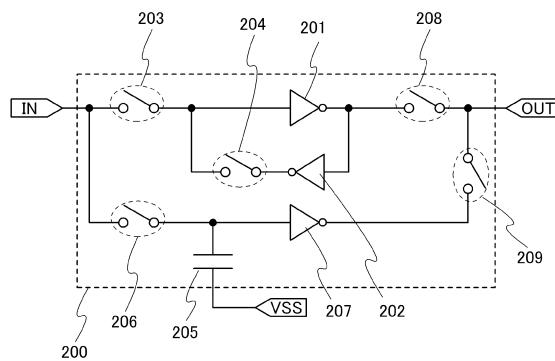

【図4】記憶素子の回路図。

【図5】記憶素子の回路図。

【図6】記憶素子の回路図。

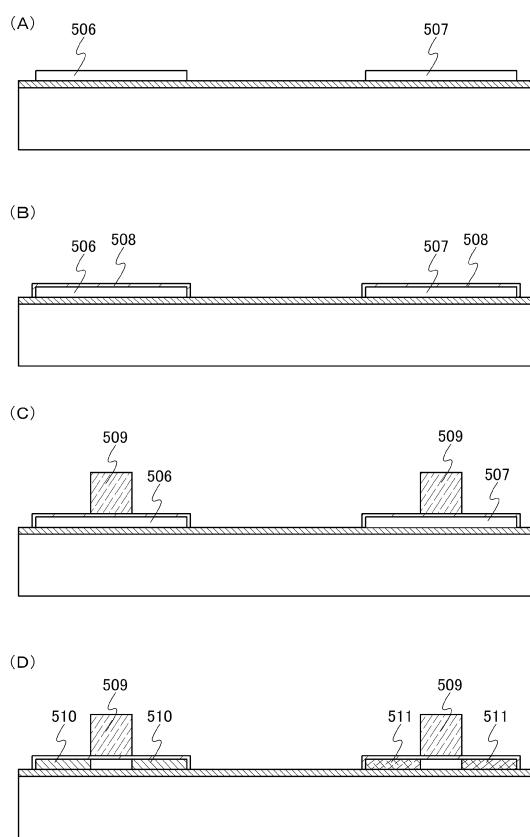

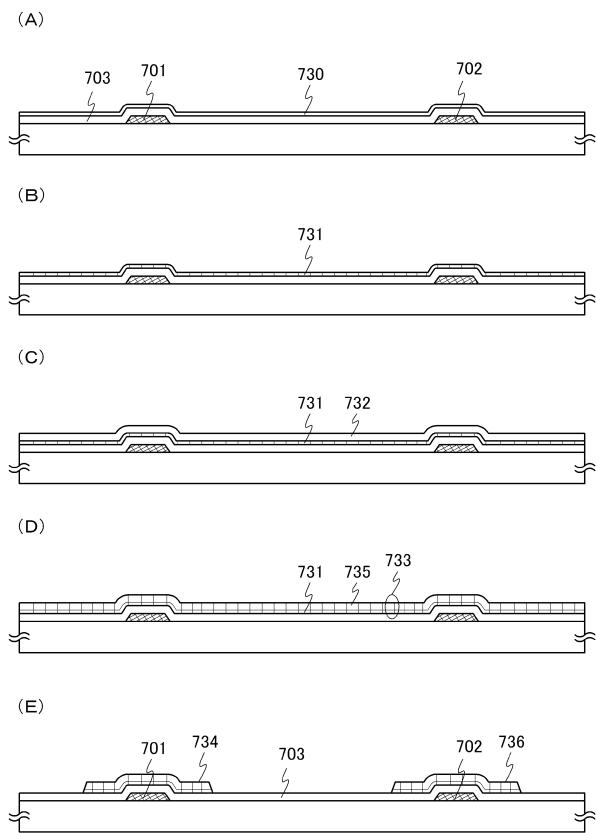

【図7】記憶装置の作製方法を示す図。

【図8】記憶装置の作製方法を示す図。

【図9】記憶装置の作製方法を示す図。

【図10】記憶装置の作製方法を示す図。

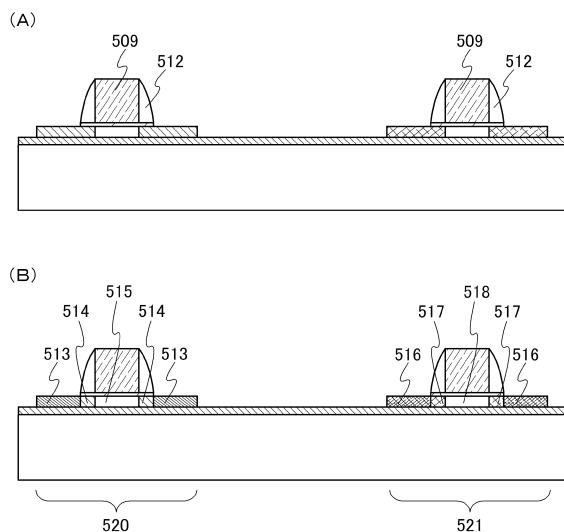

【図11】記憶装置の作製方法を示す図。

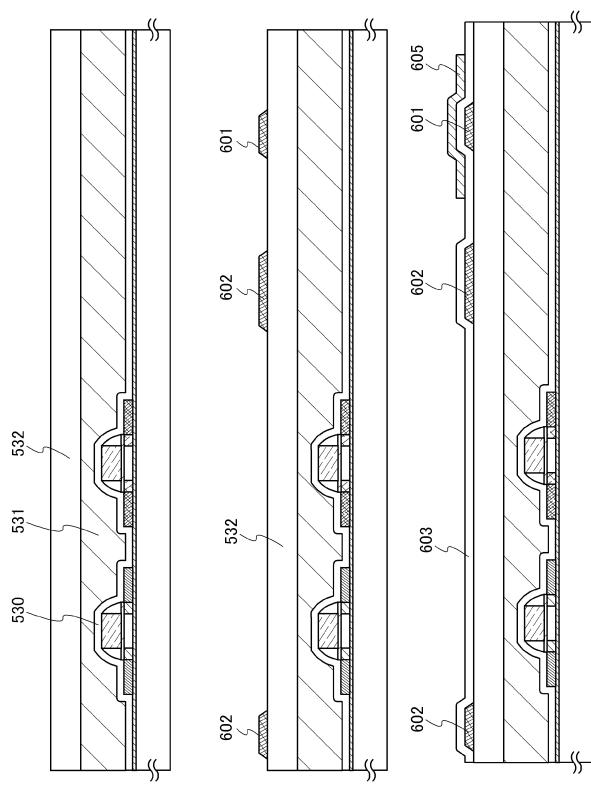

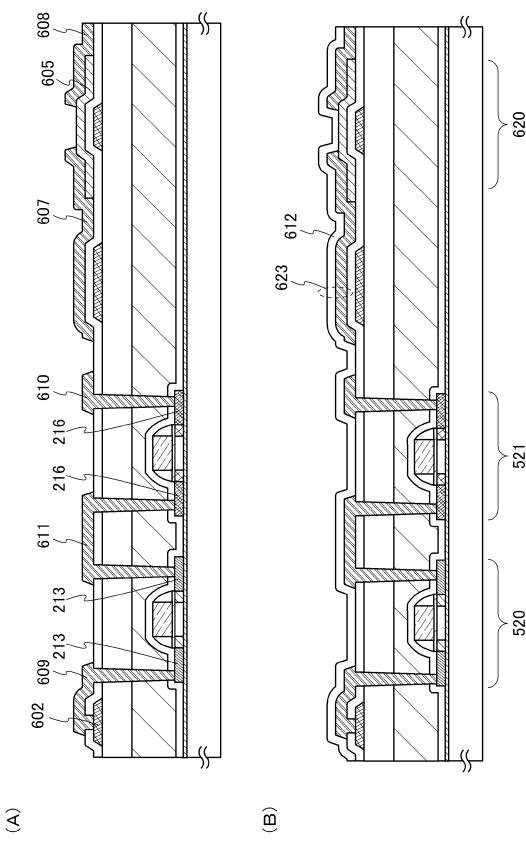

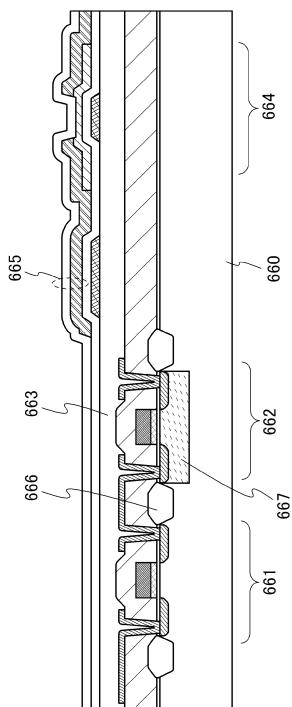

【図12】記憶装置の断面図。

【図13】記憶装置の構成を示す図。

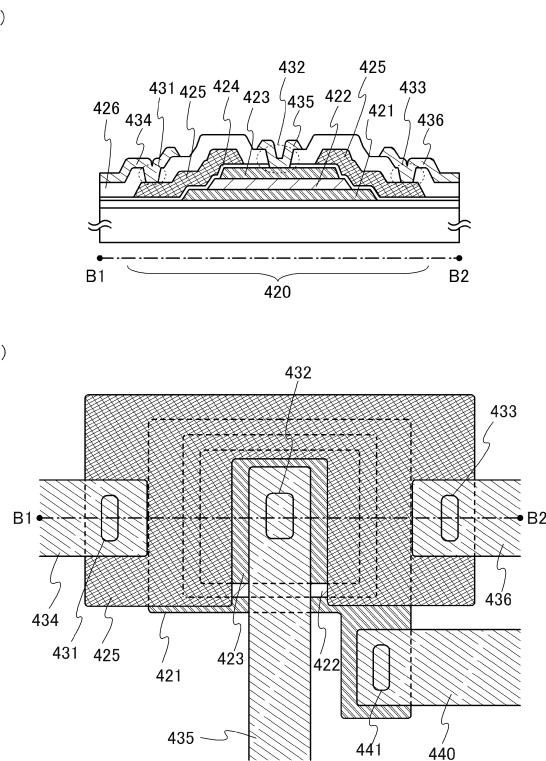

【図14】トランジスタの上面図及び断面図。

10

20

30

40

50

【図15】記憶装置の作製方法を示す図。

【図16】従来の記憶素子の回路図。

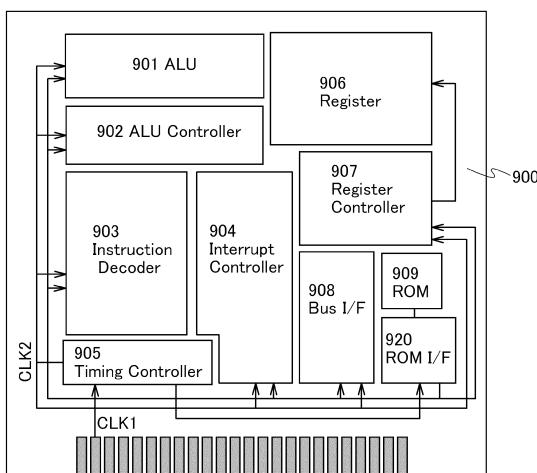

【図17】記憶装置を用いたCPUのブロック図。

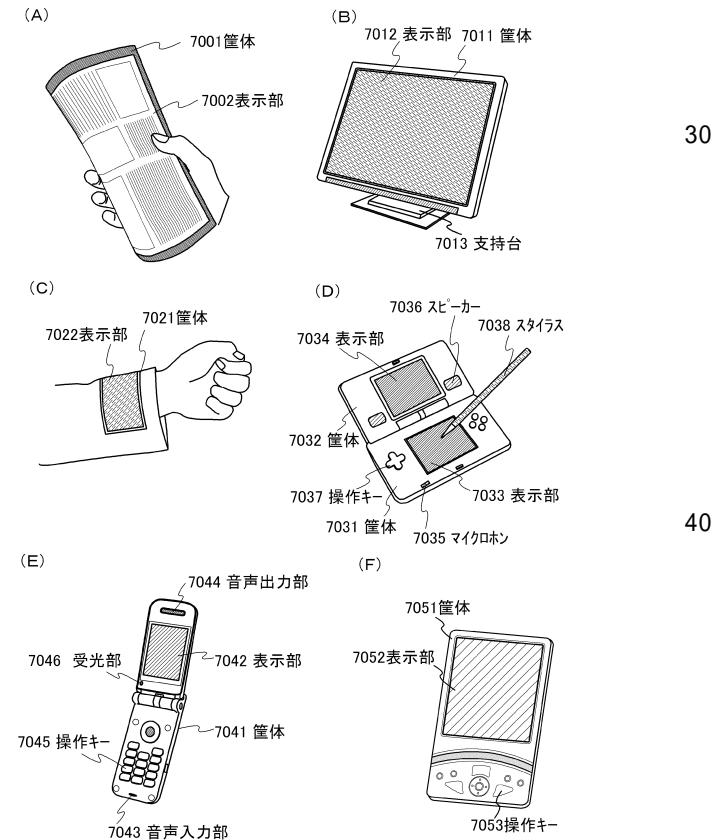

【図18】電子機器の構成を示す図。

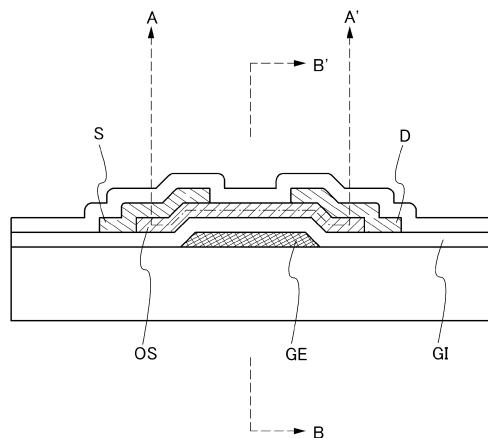

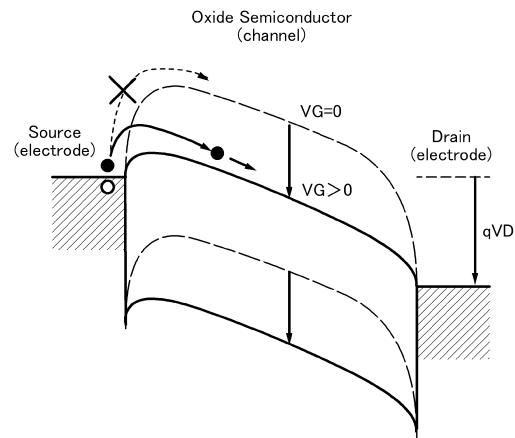

【図19】酸化物半導体を用いたトランジスタの断面図。

【図20】図19に示すA-A'断面におけるエネルギー・バンド図(模式図)。

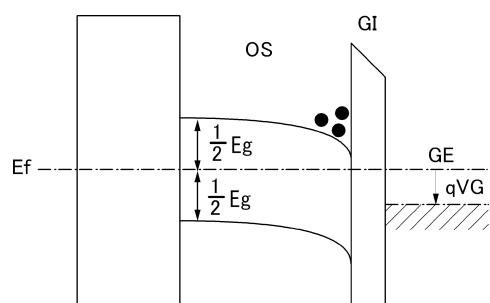

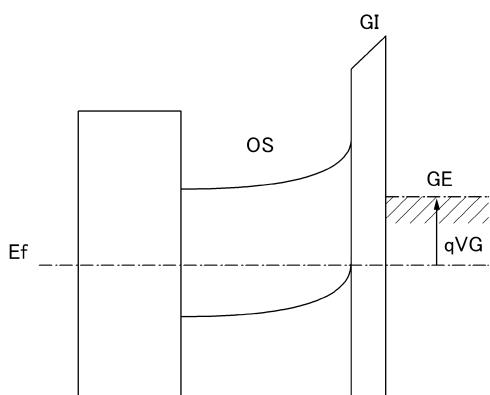

【図21】(A)ゲート電極(GE)に正の電圧( $V_G > 0$ )が印加された状態を示し、(B)ゲート電極(GE)に負の電圧( $V_G < 0$ )が印加された状態を示す図。

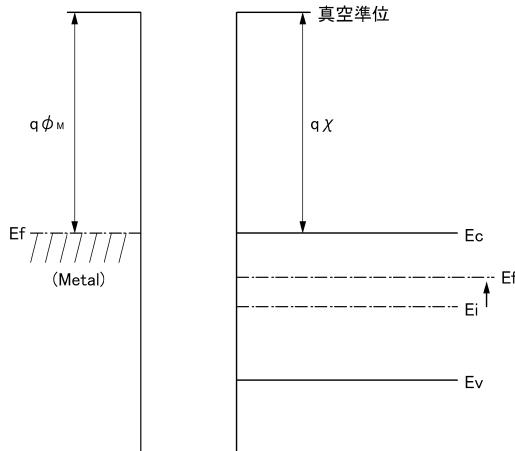

【図22】真空準位と金属の仕事関数( $M$ )、酸化物半導体の電子親和力( )の関係を示す図。 10

【図23】記憶装置の断面図。

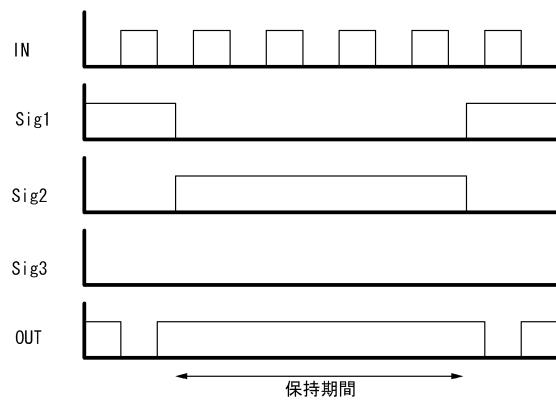

【図24】記憶装置の動作を示すタイミングチャート。

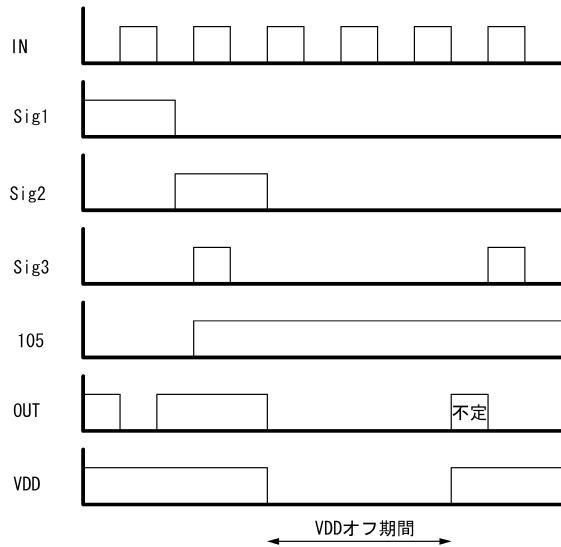

【図25】記憶装置の動作を示すタイミングチャート。

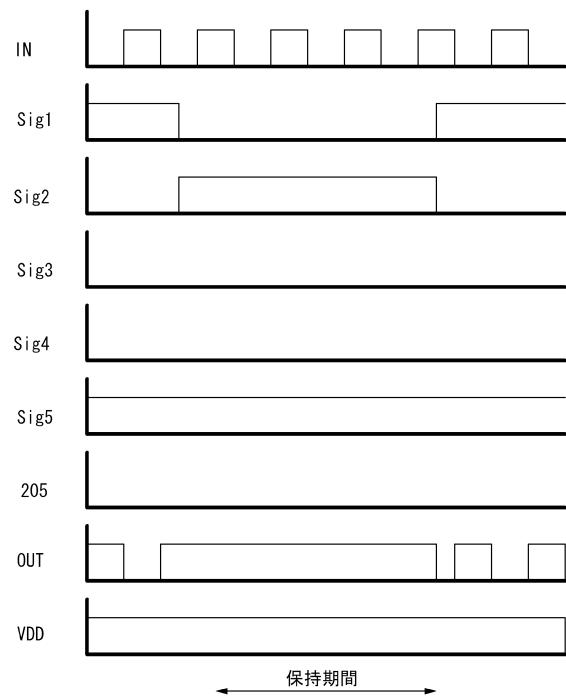

【図26】記憶装置の動作を示すタイミングチャート。

【図27】記憶装置の動作を示すタイミングチャート。

【図28】記憶装置の動作を示すタイミングチャート。

【図29】記憶装置の動作を示すタイミングチャート。

【発明を実施するための形態】

#### 【0034】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明は、以下に示す実施の形態の記載内容に限定して解釈されるものではない。 20

#### 【0035】

なお、マイクロプロセッサ、画像処理回路、DSP(Digital Signal Processor)、マイクロコントローラを含むLSI(Large Scale Integrated Circuit)などの集積回路や、RFタグ、半導体表示装置など、記憶装置を用いることができるありとあらゆる半導体装置が、本発明の範疇に含まれる。また、半導体表示装置には、液晶表示装置、有機発光素子(OLED)に代表される発光素子を各画素に備えた発光装置、電子ペーパー、DMD(Digital Micro mirror Device)、PDP(Plasma Display Panel)、FED(Field Emission Display)など、半導体膜を用いた回路素子を駆動回路に有している半導体表示装置が、その範疇に含まれる。 30

#### 【0036】

##### (実施の形態1)

本発明の一態様に係る記憶装置は、1ビットのデータを記憶することができる記憶素子を、単数または複数有する。図1に、本発明の記憶装置が有する記憶素子の、回路図の一例を示す。図1に示す記憶素子100は、入力された信号の位相を反転させて出力する第1の位相反転素子101及び第2の位相反転素子102と、スイッチング素子103と、スイッチング素子104と、容量素子105と、容量用スイッチング素子106とを、少なくとも有する。 40

#### 【0037】

記憶素子100に入力されたデータを含む信号INは、スイッチング素子103を介して第1の位相反転素子101の入力端子に与えられる。第1の位相反転素子101の出力端子は、第2の位相反転素子102の入力端子に接続されている。第2の位相反転素子102の出力端子は、スイッチング素子104を介して、第1の位相反転素子101の入力端子に接続されている。第1の位相反転素子101の出力端子または第2の位相反転素子102の入力端子の電位が、信号OUTとして後段の記憶素子、或いは他の回路に出力される。

#### 【0038】

なお、図1では、第1の位相反転素子101及び第2の位相反転素子102としてインバータを用いる例を示しているが、第1の位相反転素子101または第2の位相反転素子102として、インバータの他に、クロックドインバータを用いることもできる。

#### 【0039】

容量素子105は、記憶素子100に入力された信号INのデータを必要に応じて記憶できるように、スイッチング素子103及び容量用スイッチング素子106を介して、記憶素子100の入力端子、すなわち信号INの電位が与えられるノードに接続されている。具体的に、容量素子105は、一対の電極間に誘電体を有するコンデンサであり、その一方の電極は、容量用スイッチング素子106を介して第1の位相反転素子101の入力端子に接続され、他方の電極は、ローレベルの電源電位VSS、グラウンドなどの固定電位が与えられているノードに接続されている。10

#### 【0040】

また、容量用スイッチング素子106は、高純度化された酸化物半導体をチャネル形成領域に有するトランジスタを用いている。

#### 【0041】

なお、記憶素子100は、必要に応じて、ダイオード、抵抗素子、インダクタンスなどの他の回路素子を、さらに有していても良い。

#### 【0042】

次いで、図1で示した記憶素子の、より具体的な回路図の一例を、図2に示す。図2に示す記憶素子100は、第1の位相反転素子101と、第2の位相反転素子102と、スイッチング素子103と、スイッチング素子104と、容量素子105と、容量用スイッチング素子106とを有しており、これら回路素子の接続構成は図1と同じである。20

#### 【0043】

そして、図2において第1の位相反転素子101は、ゲート電極が互いに接続されたpチャネル型トランジスタ107と、nチャネル型トランジスタ108とが、ハイレベルの電源電位VDDが与えられる第1のノードと、ローレベルの電源電位VSSが与えられる第2のノードの間において、直列に接続された構成を有する。具体的に、pチャネル型トランジスタ107のソース電極が、電源電位VDDの与えられる第1のノードに接続され、nチャネル型トランジスタ108のソース電極が、電源電位VSSの与えられる第2のノードに接続される。また、pチャネル型トランジスタ107のドレイン電極と、nチャネル型トランジスタ108のドレイン電極とが接続されており、上記2つのドレイン電極の電位は、第1の位相反転素子101の出力端子の電位とみなすことができる。また、pチャネル型トランジスタ107のゲート電極、及びnチャネル型トランジスタ108のゲート電極の電位は、第1の位相反転素子101の入力端子の電位とみなすことができる。30

#### 【0044】

また、図2において第2の位相反転素子102は、ゲート電極が互いに接続されたpチャネル型トランジスタ109と、nチャネル型トランジスタ110とが、ハイレベルの電源電位VDDが与えられる第1のノードと、ローレベルの電源電位VSSが与えられる第2のノードの間において、直列に接続された構成を有する。具体的に、pチャネル型トランジスタ109のソース電極が、電源電位VDDの与えられる第1のノードに接続され、nチャネル型トランジスタ110のソース電極が、電源電位VSSの与えられる第2のノードに接続される。また、pチャネル型トランジスタ109のドレイン電極と、nチャネル型トランジスタ110のドレイン電極とが接続されており、上記2つのドレイン電極の電位は、第2の位相反転素子102の出力端子の電位とみなすことができる。また、pチャネル型トランジスタ109のゲート電極、及びnチャネル型トランジスタ110のゲート電極の電位は、第2の位相反転素子102の入力端子の電位とみなすことができる。40

#### 【0045】

また、図2では、スイッチング素子103としてトランジスタを用いている場合を例示しており、該トランジスタは、そのゲート電極に与えられる信号Sig1によりスイッチングが制御される。また、スイッチング素子104としてトランジスタを用いている場合を50

例示しており、該トランジスタは、そのゲート電極に与えられる信号 Sig 2 によりスイッチングが制御される。

【0046】

なお、図2では、スイッチング素子103と、スイッチング素子104が、それぞれトランジスタを一つだけ有する構成を示しているが、本発明はこの構成に限定されない。本発明の一態様では、スイッチング素子103またはスイッチング素子104が、トランジスタを複数有していても良い。スイッチング素子103またはスイッチング素子104が、スイッチング素子として機能するトランジスタを複数有している場合、上記複数のトランジスタは並列に接続されても良いし、直列に接続されても良いし、直列と並列が組み合わされて接続されても良い。

10

【0047】

また、図2では、容量用スイッチング素子106として、酸化物半導体をチャネル形成領域に有するトランジスタを用いており、該トランジスタは、そのゲート電極に与えられる信号 Sig 3 によりスイッチングが制御される。容量用スイッチング素子106に用いるトランジスタは、高純度化された酸化物半導体をチャネル形成領域に有するため、そのオフ電流は、上述したとおり著しく低い。

【0048】

そして、図2では、容量用スイッチング素子106がトランジスタを一つだけ有する構成を示しているが、本発明はこの構成に限定されない。本発明の一態様では、容量用スイッチング素子106が、トランジスタを複数有していても良い。容量用スイッチング素子106が、スイッチング素子として機能するトランジスタを複数有している場合、上記複数のトランジスタは並列に接続されても良いし、直列に接続されても良いし、直列と並列が組み合わされて接続されても良い。

20

【0049】

なお、本明細書において、トランジスタが直列に接続されている状態とは、第1のトランジスタのソース電極とドレイン電極のいずれか一方のみが、第2のトランジスタのソース電極とドレイン電極のいずれか一方のみに接続されている状態を意味する。また、トランジスタが並列に接続されている状態とは、第1のトランジスタのソース電極とドレイン電極のいずれか一方が、第2のトランジスタのソース電極とドレイン電極のいずれか一方に接続され、第1のトランジスタのソース電極とドレイン電極の他方が第2のトランジスタのソース電極とドレイン電極の他方に接続されている状態を意味する。

30

【0050】

また、本発明の一態様では、少なくとも、容量用スイッチング素子106においてスイッチング素子として用いられるトランジスタが、高純度化された酸化物半導体をチャネル形成領域に有していれば良い。よって、第1の位相反転素子101、第2の位相反転素子102、スイッチング素子103、またはスイッチング素子104に用いられるトランジスタは、酸化物半導体以外の、非晶質、微結晶、多結晶、または単結晶の、シリコン、またはゲルマニウムなどの半導体を用いることができる。また、上記トランジスタは、薄膜の半導体膜を用いていても良いし、バルクの半導体基板を用いていても良い。酸化物半導体膜を用いたpチャネル型トランジスタを作製することが可能であれば、記憶素子内の全てのトランジスタの活性層に酸化物半導体膜を用い、プロセスを簡略化することもできる。

40

【0051】

また、本明細書において接続とは電気的な接続を意味しており、電流、電圧または電位が、供給可能、或いは伝送可能な状態に相当する。従って、接続している状態とは、直接接続している状態を必ずしも指すわけではなく、電流、電圧または電位が、供給可能、或いは伝送可能であるように、配線、抵抗、ダイオード、トランジスタなどの回路素子を介して間接的に接続している状態も、その範疇に含む。

【0052】

また、回路図上は独立している構成要素どうしが接続しているように図示されている場合であっても、実際には、例えば配線の一部が電極としても機能する場合など、一の導電膜

50

が、複数の構成要素の機能を併せ持っているだけの場合もある。本明細書において接続とは、このような、一の導電膜が、複数の構成要素の機能を併せ持っている場合も、その範疇に含める。

#### 【0053】

また、トランジスタが有するソース電極とドレイン電極は、トランジスタの極性及び各電極に与えられる電位の高低差によって、その呼び方が入れ替わる。一般的に、nチャネル型トランジスタでは、低い電位が与えられる電極がソース電極と呼ばれ、高い電位が与えられる電極がドレイン電極と呼ばれる。また、pチャネル型トランジスタでは、低い電位が与えられる電極がドレイン電極と呼ばれ、高い電位が与えられる電極がソース電極と呼ばれる。本明細書では、便宜上、ソース電極とドレイン電極とが固定されているものと仮定して、トランジスタの接続関係を説明する場合があるが、実際には上記電位の関係に従ってソース電極とドレイン電極の呼び方が入れ替わる。10

#### 【0054】

次いで、図1に示す記憶素子の動作の一例について説明する。

#### 【0055】

まず、データの書き込み時において、スイッチング素子103はオン、スイッチング素子104はオフ、容量用スイッチング素子106はオフとする。そして、第1のノードに電源電位VDDを与え、第2のノードに電源電位VSSを与えることで、第1のノードと第2のノード間に電源電圧が印加される。記憶素子100に与えられる信号INの電位は、スイッチング素子103を介して第1の位相反転素子101の入力端子に与えられるので、第1の位相反転素子101の出力端子は、信号INの位相が反転した電位になる。そして、スイッチング素子104をオンにし、第1の位相反転素子101の入力端子と第2の位相反転素子102の出力端子とを接続することで、第1の位相反転素子101及び第2の位相反転素子102にデータが書き込まれる。20

#### 【0056】

次いで、入力されたデータの保持を、第1の位相反転素子101及び第2の位相反転素子102によって行う場合、スイッチング素子104をオン、容量用スイッチング素子106をオフの状態にしたままで、スイッチング素子103をオフにする。スイッチング素子103をオフにすることで、入力されたデータは、第1の位相反転素子101及び第2の位相反転素子102によって保持される。このとき、第1のノードに電源電位VDDを与え、第2のノードに電源電位VSSを与えることで、第1のノードと第2のノード間に電源電圧が印加されている状態を維持する。30

#### 【0057】

そして、第1の位相反転素子101の出力端子の電位には、第1の位相反転素子101及び第2の位相反転素子102によって保持されているデータが反映されている。よって、上記電位を読み取ることで、データを記憶素子100から読み出すことができる。

#### 【0058】

なお、データの保持時における消費電力を削減するために、入力されたデータの保持を、容量素子105において行う場合、まず、スイッチング素子103はオフ、スイッチング素子104はオン、容量用スイッチング素子106はオンとする。そして、容量用スイッチング素子106を介して、第1の位相反転素子101及び第2の位相反転素子102によって保持されているデータの値に見合った量の電荷が容量素子105に蓄積されることで、容量素子105へのデータの書き込みが行われる。容量素子105にデータが記憶された後、容量用スイッチング素子106をオフにすることで、容量素子105に記憶されたデータは保持される。容量用スイッチング素子106をオフにした後は、第1のノードと第2のノードとに、例えば電源電位VSSを与えて等電位とすることで、第1のノードと第2のノード間の電源電圧の印加を停止する。なお、容量素子105にデータが記憶された後は、スイッチング素子104をオフにしても良い。40

#### 【0059】

このように、入力されたデータの保持を容量素子105において行う場合は、第1のノードと第2のノード間に電源電圧の印加を停止する。50

ドと第2のノード間に電源電圧を印加する必要がないので、第1の位相反転素子101が有するpチャネル型トランジスタ107及びnチャネル型トランジスタ108、或いは、第2の位相反転素子102が有するpチャネル型トランジスタ109及びnチャネル型トランジスタ110を介して、第1のノードと第2のノードの間に流れるオフ電流を限りなく0にすることができる。したがって、データの保持時における記憶素子のオフ電流に起因する消費電力を大幅に削減することができ、記憶装置、延いては記憶装置を用いた半導体装置全体の、消費電力を低く抑えることが可能となる。

#### 【0060】

また、容量用スイッチング素子106に用いられているトランジスタは、高純度化された酸化物半導体をチャネル形成領域に用いているので、そのオフ電流密度を、 $100\text{ zA}/\mu\text{m}$ 以下、好ましくは $10\text{ zA}/\mu\text{m}$ 以下、更に好ましくは $1\text{ zA}/\mu\text{m}$ 以下にすることができる。よって、高純度化された酸化物半導体膜を活性層として用いたトランジスタはオフ電流が、結晶性を有するシリコンを用いたトランジスタに比べて著しく低い。その結果、上記トランジスタを用いた容量用スイッチング素子106がオフである時、容量素子105に蓄積された電荷は殆ど放電しないため、データは保持される。10

#### 【0061】

また、容量素子105に記憶されているデータを読み出す場合は、スイッチング素子103をオフとする。そして、再び、第1のノードに電源電位VDDを与えて、第2のノードに電源電位VSSを与えることで、第1のノードと第2のノード間に電源電圧を印加する。そして、容量用スイッチング素子106をオンにすることで、データが反映された電位を有する信号OUTを、記憶素子100から読み出すことができる。20

#### 【0062】

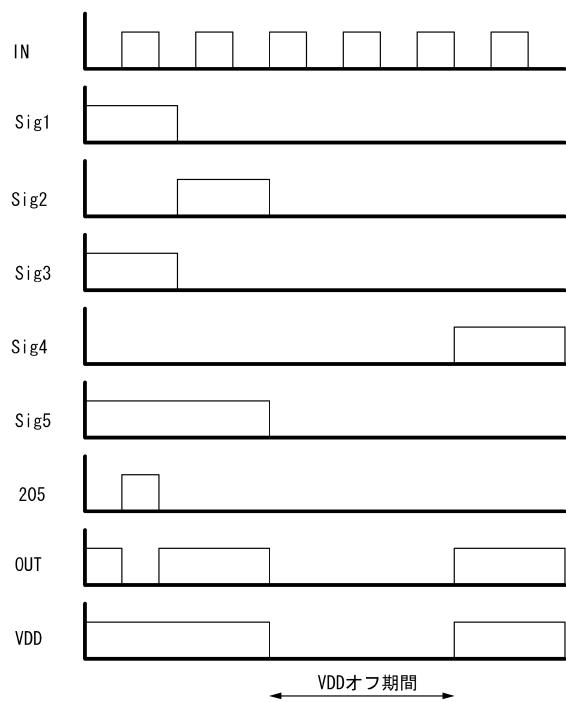

次いで、図2に示した回路において、電源電位VDDの供給を停止しない場合のタイミングチャートの一例を図24に示す。信号Sig1がローレベルになり、信号Sig2はハイレベルになることによって、信号INが遮断され、帰還ループができ、状態が保持できる。信号Sig1が再びハイレベルになり、信号Sig2がローレベルになると、信号INが入り、第1の位相反転素子101を介して出力される。このとき、信号Sig3はローレベルとする。

#### 【0063】

図25は、図2の回路の電源電位VDDの供給を停止する場合のタイミングチャートの一例である。信号Sig1がローレベルになり、信号Sig2はハイレベルになることによって、信号INが遮断され、帰還ループができ、状態が保持できる。この後、信号Sig3をハイレベルにすることによって容量素子105に記憶がなされる（図25ではハイレベル）。その後、電源電位VDDの供給が停止しても、容量素子105の電位は保持される。その後、電源電位VDDが供給され、信号Sig3が再度ハイレベルになると、容量素子105の電位が第1の位相反転素子101を介して出力される（図25ではローレベル）。

#### 【0064】

##### （実施の形態2）

本実施の形態では、本発明の記憶装置が有する記憶素子の、別の一例について説明する。40

図3に、本実施の形態の記憶素子の回路図を、一例として示す。

#### 【0065】

図3に示す記憶素子200は、入力された信号の位相を反転させて出力する第1の位相反転素子201、第2の位相反転素子202及び第3の位相反転素子207と、スイッチング素子203と、スイッチング素子204と、スイッチング素子208と、スイッチング素子209と、容量素子205と、容量用スイッチング素子206とを、少なくとも有する。

#### 【0066】

記憶素子200に入力されたデータを含む信号INは、スイッチング素子203を介して第1の位相反転素子201の入力端子に与えられる。第1の位相反転素子201の出力端

10

20

30

40

50

子は、第2の位相反転素子202の入力端子に接続されている。第2の位相反転素子202の出力端子は、スイッチング素子204を介して、第1の位相反転素子201の入力端子に接続されている。第1の位相反転素子201の出力端子または第2の位相反転素子202の入力端子の電位は、スイッチング素子208を介して、信号OUTとして後段の記憶素子、或いは他の回路に出力される。

#### 【0067】

容量素子205は、記憶素子200に入力された信号INのデータを必要に応じて記憶できるように、容量用スイッチング素子206を介して、記憶素子200の入力端子、すなわち信号INの電位が与えられるノードに接続されている。具体的に、容量素子205は、一対の電極間に誘電体を有するコンデンサであり、その一方の電極は、容量用スイッチング素子206を介して信号INの電位が与えられるノードに接続され、他方の電極は、ローレベルの電源電位VSS、グラウンドなどの固定電位が与えられているノードに接続されている。10

#### 【0068】

また、容量素子205の上記一方の電極は、第3の位相反転素子207の入力端子に接続される。第3の位相反転素子207の出力端子の電位は、スイッチング素子209を介して、信号OUTとして後段の記憶素子、或いは他の回路に出力される。

#### 【0069】

なお、図3では、第1の位相反転素子201、第2の位相反転素子202及び第3の位相反転素子207としてインバータを用いる例を示しているが、第1の位相反転素子201、第2の位相反転素子202または第3の位相反転素子207として、インバータの他に、クロックドインバータを用いることもできる。20

#### 【0070】

また、容量用スイッチング素子206は、高純度化された酸化物半導体をチャネル形成領域に有するトランジスタを用いている。

#### 【0071】

なお、記憶素子200は、必要に応じて、ダイオード、抵抗素子、インダクタンスなどの他の回路素子を、さらに有していても良い。

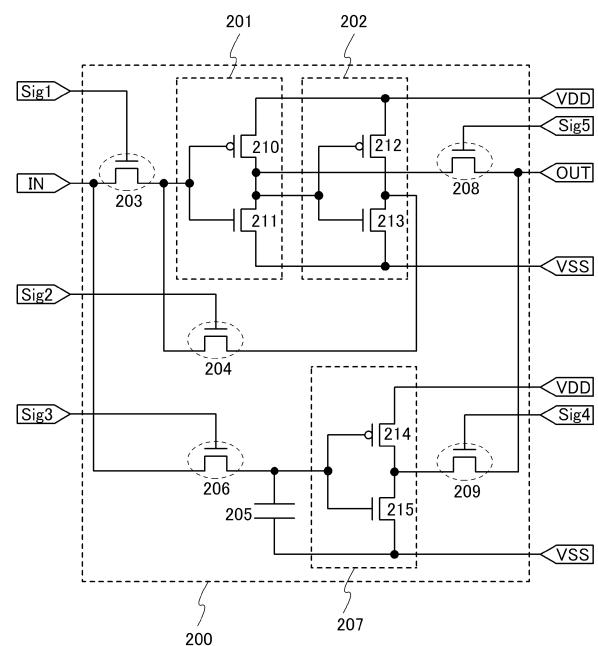

#### 【0072】

次いで、図3で示した記憶素子の、より具体的な回路図の一例を、図4に示す。図4に示す記憶素子200は、第1の位相反転素子201、第2の位相反転素子202、第3の位相反転素子207、スイッチング素子203、スイッチング素子204、スイッチング素子208、スイッチング素子209、容量素子205、容量用スイッチング素子206を少なくとも有しており、これら回路素子の接続構成は図3と同じである。30

#### 【0073】

そして、図4において第1の位相反転素子201は、ゲート電極が互いに接続されたpチャネル型トランジスタ210と、nチャネル型トランジスタ211とが、ハイレベルの電源電位VDDが与えられる第1のノードと、ローレベルの電源電位VSSが与えられる第2のノードの間において、直列に接続された構成を有する。具体的に、pチャネル型トランジスタ210のソース電極が、電源電位VDDの与えられる第1のノードに接続され、nチャネル型トランジスタ211のソース電極が、電源電位VSSの与えられる第2のノードに接続される。また、pチャネル型トランジスタ210のドレイン電極と、nチャネル型トランジスタ211のドレイン電極とが接続されており、上記2つのドレイン電極の電位は、第1の位相反転素子201の出力端子の電位とみなすことができる。また、pチャネル型トランジスタ210のゲート電極、及びnチャネル型トランジスタ211のゲート電極の電位は、第1の位相反転素子201の入力端子の電位とみなすことができる。40

#### 【0074】

また、図4において第2の位相反転素子202は、ゲート電極が互いに接続されたpチャネル型トランジスタ212と、nチャネル型トランジスタ213とが、ハイレベルの電源電位VDDが与えられる第1のノードと、ローレベルの電源電位VSSが与えられる第250

のノードの間において、直列に接続された構成を有する。具体的に、p チャネル型トランジスタ 212 のソース電極が、電源電位 VDD の与えられる第 1 のノードに接続され、n チャネル型トランジスタ 213 のソース電極が、電源電位 VSS の与えられる第 2 のノードに接続される。また、p チャネル型トランジスタ 212 のドレイン電極と、n チャネル型トランジスタ 213 のドレイン電極とが接続されており、上記 2 つのドレイン電極の電位は、第 2 の位相反転素子 202 の出力端子の電位とみなすことができる。また、p チャネル型トランジスタ 212 のゲート電極、及び n チャネル型トランジスタ 213 のゲート電極の電位は、第 2 の位相反転素子 202 の入力端子の電位とみなすことができる。

#### 【 0075 】

また、図 4において第 3 の位相反転素子 207 は、ゲート電極が互いに接続された p チャネル型トランジスタ 214 と、n チャネル型トランジスタ 215 とが、ハイレベルの電源電位 VDD が与えられる第 3 のノードと、ローレベルの電源電位 VSS が与えられる第 4 のノードの間において、直列に接続された構成を有する。具体的に、p チャネル型トランジスタ 214 のソース電極が、電源電位 VDD の与えられる第 3 のノードに接続され、n チャネル型トランジスタ 215 のソース電極が、電源電位 VSS の与えられる第 4 のノードに接続される。また、p チャネル型トランジスタ 214 のドレイン電極と、n チャネル型トランジスタ 215 のドレイン電極とが接続されており、上記 2 つのドレイン電極の電位は、第 3 の位相反転素子 207 の出力端子の電位とみなすことができる。また、p チャネル型トランジスタ 214 のゲート電極、及び n チャネル型トランジスタ 215 のゲート電極の電位は、第 3 の位相反転素子 207 の入力端子の電位とみなすことができる。

10

20

30

40

#### 【 0076 】

なお、上記第 1 のノードと第 3 のノードは、電気的に接続された一つのノードであっても良い。また、上記第 2 のノードと第 4 のノードも、電気的に接続された一つのノードであっても良い。

#### 【 0077 】

また、図 4 では、スイッチング素子 203 としてトランジスタを用いている場合を例示しており、該トランジスタは、そのゲート電極に与えられる信号 Sig 1 によりスイッチングが制御される。また、スイッチング素子 204 としてトランジスタを用いている場合を例示しており、該トランジスタは、そのゲート電極に与えられる信号 Sig 2 によりスイッチングが制御される。また、スイッチング素子 209 としてトランジスタを用いている場合を例示しており、該トランジスタは、そのゲート電極に与えられる信号 Sig 4 によりスイッチングが制御される。

30

#### 【 0078 】

なお、図 4 では、スイッチング素子 203、スイッチング素子 204、スイッチング素子 209 が、それぞれトランジスタを一つだけ有する構成を示しているが、本発明はこの構成に限定されない。本発明の一態様では、スイッチング素子 203、スイッチング素子 204、またはスイッチング素子 209 が、トランジスタを複数有していても良い。スイッチング素子 203、スイッチング素子 204、またはスイッチング素子 209 が、スイッチング素子として機能するトランジスタを複数有している場合、上記複数のトランジスタは並列に接続されても良いし、直列に接続されても良いし、直列と並列が組み合わされて接続されても良い。

40

#### 【 0079 】

また、図 4 では、容量用スイッチング素子 206 として、酸化物半導体をチャネル形成領域に有するトランジスタを用いており、該トランジスタは、そのゲート電極に与えられる信号 Sig 3 によりスイッチングが制御される。容量用スイッチング素子 206 に用いるトランジスタは、高純度化された酸化物半導体をチャネル形成領域に有するため、そのオフ電流は、上述したとおり著しく低い。

#### 【 0080 】

そして、図 4 では、容量用スイッチング素子 206 がトランジスタを一つだけ有する構成を示しているが、本発明はこの構成に限定されない。本発明の一態様では、容量用スイッ

50

チング素子 206 が、トランジスタを複数有していても良い。容量用スイッチング素子 206 が、スイッチング素子として機能するトランジスタを複数有している場合、上記複数のトランジスタは並列に接続されても良いし、直列に接続されても良いし、直列と並列が組み合わされて接続されても良い。

#### 【0081】

また、本発明の一態様では、少なくとも、容量用スイッチング素子 206 においてスイッチング素子として用いられるトランジスタが、高純度化された酸化物半導体をチャネル形成領域に有していれば良い。よって、第1の位相反転素子 201、第2の位相反転素子 202、第3の位相反転素子 207、スイッチング素子 203、スイッチング素子 204、スイッチング素子 208、スイッチング素子 209 に用いられるトランジスタは、酸化物半導体以外の、非晶質、微結晶、多結晶、または単結晶の、シリコン、またはゲルマニウムなどの半導体を用いることができる。また、上記トランジスタは、薄膜の半導体膜を用いていても良いし、バルクの半導体基板を用いていても良い。酸化物半導体膜を用いた p チャネル型トランジスタを作製することが可能であれば、記憶素子内の全てのトランジスタの活性層に酸化物半導体膜を用い、プロセスを簡略化することもできる。10

#### 【0082】

次いで、図3に示す記憶素子の動作の一例について説明する。

#### 【0083】

まず、データの書き込み時において、スイッチング素子 203 はオン、スイッチング素子 204 はオフ、スイッチング素子 208 はオフ、スイッチング素子 209 はオフ、容量用スイッチング素子 206 はオンとする。そして、第1のノードに電源電位 VDD を与え、第2のノードに電源電位 VSS を与えることで、第1のノードと第2のノード間に電源電圧が印加される。記憶素子 200 に与えられる信号 IN の電位は、スイッチング素子 203 を介して第1の位相反転素子 201 の入力端子に与えられるので、第1の位相反転素子 201 の出力端子は、信号 IN の位相が反転した電位になる。そして、スイッチング素子 204 をオンにし、第1の位相反転素子 201 の入力端子と第2の位相反転素子 202 の出力端子とを接続することで、第1の位相反転素子 201 及び第2の位相反転素子 202 にデータが書き込まれる。20

#### 【0084】

また、データの書き込み時では、容量用スイッチング素子 206 を介して、信号 IN のデータの値に見合った量の電荷が容量素子 205 に蓄積されることで、容量素子 205 にもデータが書き込まれる。30

#### 【0085】

なお、データの書き込み時において、第3のノードと第4のノード間に電源電圧を印加する必要はない。よって、例えば、第3のノードと第4のノードとに、例えば電源電位 VSS を与えて等電位とする。

#### 【0086】

次いで、入力されたデータの保持を、第1の位相反転素子 201 及び第2の位相反転素子 202 によって行う場合、スイッチング素子 204 をオン、スイッチング素子 208 をオフ、スイッチング素子 209 をオフにした状態で、スイッチング素子 203 をオフ、容量用スイッチング素子 206 をオフにする。スイッチング素子 203 をオフにすることで、入力されたデータは、第1の位相反転素子 201 及び第2の位相反転素子 202 によって保持される。このとき、第1のノードに電源電位 VDD を与え、第2のノードに電源電位 VSS を与えることで、第1のノードと第2のノード間に電源電圧が印加されている状態を維持する。40

#### 【0087】

また、容量用スイッチング素子 206 をオフにすることで、容量素子 205 に書き込まれたデータも、保持される。

#### 【0088】

そして、第1の位相反転素子 201 の出力端子の電位には、第1の位相反転素子 201 及50

び第2の位相反転素子202によって保持されているデータが反映されている。よって、スイッチング素子208をオンにして上記電位を読み取ることで、データを記憶素子200から読み出すことができる。

#### 【0089】

なお、データの保持時における消費電力を削減するために、入力されたデータの保持を、容量素子205のみにおいて行う場合は、第1のノードと第2のノードとに、例えば電源電位VSSを与えて等電位として、第1のノードと第2のノード間の電源電圧の印加を停止する。第1のノードと第2のノード間の電源電圧の印加を停止すると、第1の位相反転素子201及び第2の位相反転素子202において保持されているデータは消えるが、容量素子205に書き込まれたデータは、そのまま保持される。

10

#### 【0090】

このように、入力されたデータの保持を容量素子205において行う場合は、第1のノードと第2のノード間に電源電圧を印加する必要がないので、第1の位相反転素子201が有するpチャネル型トランジスタ210及びnチャネル型トランジスタ211、或いは、第2の位相反転素子202が有するpチャネル型トランジスタ212及びnチャネル型トランジスタ213を介して、第1のノードと第2のノードの間に流れるオフ電流を、限りなく0にすることができる。したがって、保持時における記憶素子のオフ電流に起因する消費電力を大幅に削減することができ、記憶装置、延いては記憶装置を用いた半導体装置全体の、消費電力を低く抑えることが可能となる。

20

#### 【0091】

また、入力されたデータの保持を容量素子205において行う場合、第3のノードと第4のノード間に電源電圧を印加する必要がない。よって、第3の位相反転素子207が有するpチャネル型トランジスタ214及びnチャネル型トランジスタ215を介して、第3のノードと第4のノードの間に流れるオフ電流を限りなく0にすることができる。したがって、保持時における記憶素子のオフ電流に起因する消費電力を大幅に削減することができ、記憶装置、延いては記憶装置を用いた半導体装置全体の、消費電力を低く抑えることが可能となる。

30

#### 【0092】

また、容量用スイッチング素子206に用いられているトランジスタは、高純度化された酸化物半導体をチャネル形成領域に用いているので、そのオフ電流密度を、 $100\text{zA}/\mu\text{m}$ 以下、好ましくは $10\text{zA}/\mu\text{m}$ 以下、更に好ましくは $1\text{zA}/\mu\text{m}$ 以下にすることができる。よって、高純度化された酸化物半導体膜を活性層として用いたトランジスタは、オフ電流が、結晶性を有するシリコンを用いたトランジスタに比べて著しく低い。その結果、上記トランジスタを用いた容量用スイッチング素子206がオフである時、容量素子205に蓄積された電荷は殆ど放電しないため、データは保持される。

30

#### 【0093】

なお、容量素子205に記憶されているデータを読み出す場合は、第3のノードに電源電位VDDを与え、第4のノードに電源電位VSSを与えることで、第3のノードと第4のノード間に電源電圧を印加する。第3のノードと第4のノード間に電源電圧が与えられると、第3の位相反転素子207の出力端子には、入力端子の電位の位相が反転した電位が与えられる。なお、第3の位相反転素子207の入力端子には、容量素子205に蓄積されている電荷量に見合った高さの電位が与えられるので、その出力端子の電位にはデータが反映される。よって、スイッチング素子209をオンにすることで、データが反映された電位を有する信号OUTを、記憶素子200から読み出すことができる。

40

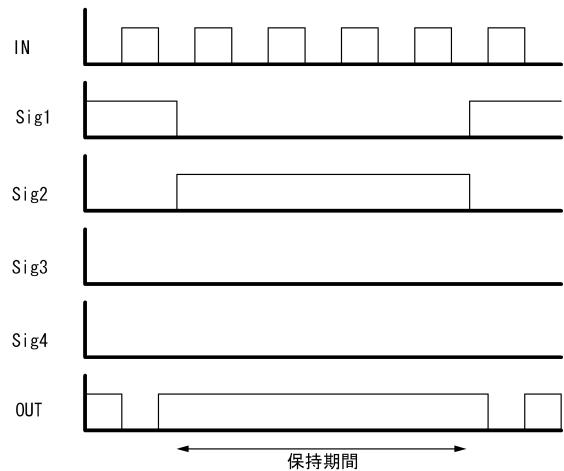

#### 【0094】

図26は、図4の回路の電源電位VDDの供給を停止しない場合のタイミングチャートの一例である。信号Sig1がローレベルになり、信号Sig2はハイレベルになることによつて、信号INが遮断され、帰還ループができ、状態が保持できる。信号Sig1が再びハイレベルになり、信号Sig2がローレベルになると、信号INが入り、第1の位相反転素子201を介して出力される。このとき信号Sig3、信号Sig4はローレベル

50

であり、信号 Sig 5 はハイレベルである。

**【 0 0 9 5 】**

図 27 は、図 4 の回路の電源電位 VDD の供給を停止する場合のタイミングチャートの一例である。信号 Sig 1 がローレベルになり、信号 Sig 2 はハイレベルになることによって、信号 IN が遮断され、帰還ループができ、状態が保持できる。一方、信号 Sig 3 をハイレベルにすることによって容量素子 205 に記憶がなされる（図 27 ではローレベル）。その後、電源電位 VDD の供給が停止しても容量素子 205 の電位は保持される。その後、電源電位 VDD が供給され、信号 Sig 5 がローレベル、信号 Sig 3 がローレベル、信号 Sig 4 がハイレベルになると、容量素子 205 の電位が第 3 の位相反転素子 207 を介して出力される（図 27 ではハイレベル）。

10

**【 0 0 9 6 】**

本実施の形態は、上記実施の形態と適宜組み合わせて実施することが可能である。

**【 0 0 9 7 】**

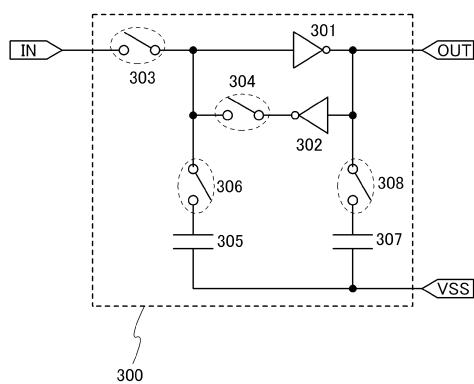

**(実施の形態 3 )**

本実施の形態では、本発明の記憶装置が有する記憶素子の、別の一例について説明する。図 5 に、本実施の形態の記憶素子の回路図を、一例として示す。

**【 0 0 9 8 】**

図 5 に示す記憶素子 300 は、入力された信号の位相を反転させて出力する第 1 の位相反転素子 301 及び第 2 の位相反転素子 302 と、スイッチング素子 303 と、スイッチング素子 304 と、容量素子 305 と、容量用スイッチング素子 306 と、容量素子 307 と、容量用スイッチング素子 308 とを、少なくとも有する。

20

**【 0 0 9 9 】**

記憶素子 300 に入力されたデータを含む信号 IN は、スイッチング素子 303 を介して第 1 の位相反転素子 301 の入力端子に与えられる。第 1 の位相反転素子 301 の出力端子は、第 2 の位相反転素子 302 の入力端子に接続されている。第 2 の位相反転素子 302 の出力端子は、スイッチング素子 304 を介して、第 1 の位相反転素子 301 の入力端子に接続されている。第 1 の位相反転素子 301 の出力端子または第 2 の位相反転素子 302 の入力端子の電位は、信号 OUT として後段の記憶素子、或いは他の回路に出力される。

30

**【 0 1 0 0 】**

容量素子 305 は、記憶素子 300 に入力された信号 IN のデータを必要に応じて記憶できるように、スイッチング素子 303 及び容量用スイッチング素子 306 を介して、記憶素子 300 の入力端子、すなわち信号 IN の電位が与えられるノードに接続されている。具体的に、容量素子 305 は、一対の電極間に誘電体を有するコンデンサであり、その一方の電極は、容量用スイッチング素子 306 を介して第 1 の位相反転素子 301 の入力端子に接続され、他方の電極は、ローレベルの電源電位 VSS、グラウンドなどの固定電位が与えられているノードに接続されている。

30

**【 0 1 0 1 】**

容量素子 307 は、容量素子 305 と同様に、記憶素子 300 に入力された信号 IN のデータを必要に応じて記憶できるように、スイッチング素子 303、第 1 の位相反転素子 301 及び容量用スイッチング素子 308 を介して、記憶素子 300 の入力端子、すなわち信号 IN の電位が与えられるノードに接続されている。具体的に、容量素子 307 は、一対の電極間に誘電体を有するコンデンサであり、その一方の電極は、容量用スイッチング素子 308 を介して第 1 の位相反転素子 301 の出力端子に接続され、他方の電極は、ローレベルの電源電位 VSS、グラウンドなどの固定電位が与えられているノードに接続されている。

40

**【 0 1 0 2 】**

なお、図 5 では、第 1 の位相反転素子 301、第 2 の位相反転素子 302 としてインバータを用いる例を示しているが、第 1 の位相反転素子 301 または第 2 の位相反転素子 302 として、インバータの他に、クロックドインバータを用いることもできる。

50

**【 0 1 0 3 】**

また、容量用スイッチング素子 306 及び容量用スイッチング素子 308 は、高純度化された酸化物半導体をチャネル形成領域に有するトランジスタを用いている。

**【 0 1 0 4 】**

なお、記憶素子 300 は、必要に応じて、ダイオード、抵抗素子、インダクタンスなどの他の回路素子を、さらに有しても良い。

**【 0 1 0 5 】**

次いで、図 5 で示した記憶素子の、より具体的な回路図の一例を、図 6 に示す。図 6 に示す記憶素子 300 は、第 1 の位相反転素子 301、第 2 の位相反転素子 302、スイッチング素子 303、スイッチング素子 304、容量素子 305、容量用スイッチング素子 306、容量素子 307、容量用スイッチング素子 308 を少なくとも有しており、これら回路素子の接続構成は図 5 と同じである。10

**【 0 1 0 6 】**

そして、図 6 において第 1 の位相反転素子 301 は、ゲート電極が互いに接続された p チャネル型トランジスタ 309 と、n チャネル型トランジスタ 310 とが、ハイレベルの電源電位 VDD が与えられる第 1 のノードと、ローレベルの電源電位 VSS が与えられる第 2 のノードの間ににおいて、直列に接続された構成を有する。具体的に、p チャネル型トランジスタ 309 のソース電極が、電源電位 VDD の与えられる第 1 のノードに接続され、n チャネル型トランジスタ 310 のソース電極が、電源電位 VSS の与えられる第 2 のノードに接続される。また、p チャネル型トランジスタ 309 のドレイン電極と、n チャネル型トランジスタ 310 のドレイン電極とが接続されており、上記 2 つのドレイン電極の電位は、第 1 の位相反転素子 301 の出力端子の電位とみなすことができる。また、p チャネル型トランジスタ 309 のゲート電極、及び n チャネル型トランジスタ 310 のゲート電極の電位は、第 1 の位相反転素子 301 の入力端子の電位とみなすことができる。20

**【 0 1 0 7 】**

また、図 6 において第 2 の位相反転素子 302 は、ゲート電極が互いに接続された p チャネル型トランジスタ 311 と、n チャネル型トランジスタ 312 とが、ハイレベルの電源電位 VDD が与えられる第 1 のノードと、ローレベルの電源電位 VSS が与えられる第 2 のノードの間ににおいて、直列に接続された構成を有する。具体的に、p チャネル型トランジスタ 311 のソース電極が、電源電位 VDD の与えられる第 1 のノードに接続され、n チャネル型トランジスタ 312 のソース電極が、電源電位 VSS の与えられる第 2 のノードに接続される。また、p チャネル型トランジスタ 311 のドレイン電極と、n チャネル型トランジスタ 312 のドレイン電極とが接続されており、上記 2 つのドレイン電極の電位は、第 2 の位相反転素子 302 の出力端子の電位とみなすことができる。また、p チャネル型トランジスタ 311 のゲート電極、及び n チャネル型トランジスタ 312 のゲート電極の電位は、第 2 の位相反転素子 302 の入力端子の電位とみなすことができる。30

**【 0 1 0 8 】**

また、図 6 では、スイッチング素子 303 としてトランジスタを用いている場合を例示しており、該トランジスタは、そのゲート電極に与えられる信号 Sig 1 によりスイッチングが制御される。また、スイッチング素子 304 としてトランジスタを用いている場合を例示しており、該トランジスタは、そのゲート電極に与えられる信号 Sig 2 によりスイッチングが制御される。40

**【 0 1 0 9 】**

なお、図 6 では、スイッチング素子 303、スイッチング素子 304 が、それぞれトランジスタを一つだけ有する構成を示しているが、本発明はこの構成に限定されない。本発明の一態様では、スイッチング素子 303 またはスイッチング素子 304 が、トランジスタを複数有しても良い。スイッチング素子 303 またはスイッチング素子 304 が、スイッチング素子として機能するトランジスタを複数有している場合、上記複数のトランジスタは並列に接続されていても良いし、直列に接続されていても良いし、直列と並列が組み合わされて接続されていても良い。50

## 【 0 1 1 0 】

また、図6では、容量用スイッチング素子306として、酸化物半導体をチャネル形成領域に有するトランジスタを用いており、該トランジスタは、そのゲート電極に与えられる信号Sig3によりスイッチングが制御される。容量用スイッチング素子306に用いるトランジスタは、高純度化された酸化物半導体をチャネル形成領域に有するため、そのオフ電流は、上述したとおり著しく低い。

## 【 0 1 1 1 】

また、図6では、容量用スイッチング素子308として、酸化物半導体をチャネル形成領域に有するトランジスタを用いており、該トランジスタは、そのゲート電極に与えられる信号Sig4によりスイッチングが制御される。容量用スイッチング素子308に用いるトランジスタは、高純度化された酸化物半導体をチャネル形成領域に有するため、そのオフ電流は、上述したとおり著しく低い。

10

## 【 0 1 1 2 】

そして、図6では、容量用スイッチング素子306または容量用スイッチング素子308がトランジスタを一つだけ有する構成を示しているが、本発明はこの構成に限定されない。本発明の一態様では、容量用スイッチング素子306または容量用スイッチング素子308が、トランジスタを複数有していても良い。容量用スイッチング素子306または容量用スイッチング素子308が、スイッチング素子として機能するトランジスタを複数有している場合、上記複数のトランジスタは並列に接続されていても良いし、直列に接続されていても良いし、直列と並列が組み合わされて接続されていても良い。

20

## 【 0 1 1 3 】

また、本発明の一態様では、少なくとも、容量用スイッチング素子306または容量用スイッチング素子308において、スイッチング素子として用いられるトランジスタが、高純度化された酸化物半導体をチャネル形成領域に有していれば良い。よって、第1の位相反転素子301、第2の位相反転素子302、スイッチング素子303、スイッチング素子304に用いられるトランジスタは、酸化物半導体以外の、非晶質、微結晶、多結晶、または単結晶の、シリコン、またはゲルマニウムなどの半導体を用いることができる。また、上記トランジスタは、薄膜の半導体膜を用いていても良いし、バルクの半導体基板を用いていても良い。酸化物半導体膜を用いたpチャネル型トランジスタを作製することが可能であれば、記憶素子内の全てのトランジスタの活性層に酸化物半導体膜を用い、プロセスを簡略化することもできる。

30

## 【 0 1 1 4 】

次いで、図5または図6に示す記憶素子の動作の一例について説明する。

## 【 0 1 1 5 】

まず、データの書き込み時において、スイッチング素子303はオン、スイッチング素子304はオフ、容量用スイッチング素子306はオフ、容量用スイッチング素子308はオフとする。そして、第1のノードに電源電位VDDを与えることなく、第2のノードに電源電位VSSを与えることで、第1のノードと第2のノード間に電源電圧が印加される。記憶素子300に与えられる信号INの電位は、スイッチング素子303を介して第1の位相反転素子301の入力端子に与えられるので、第1の位相反転素子301の出力端子は、信号INの位相が反転した電位になる。そして、スイッチング素子304をオンにし、第1の位相反転素子301の入力端子と第2の位相反転素子302の出力端子とを接続することで、第1の位相反転素子301及び第2の位相反転素子302にデータが書き込まれる。

40

## 【 0 1 1 6 】

次いで、入力されたデータの保持を、第1の位相反転素子301及び第2の位相反転素子302によって行う場合、スイッチング素子304をオン、容量用スイッチング素子306をオフ、容量用スイッチング素子308をオフの状態にしたままで、スイッチング素子303をオフにする。スイッチング素子303をオフにすることで、入力されたデータは、第1の位相反転素子301及び第2の位相反転素子302によって保持される。このとき、第1のノードに電源電位VDDを与えることなく、第2のノードに電源電位VSSを与えること

50

で、第1のノードと第2のノード間に電源電圧が印加されている状態を維持する。

【0117】

そして、第1の位相反転素子301の出力端子の電位には、第1の位相反転素子301及び第2の位相反転素子302によって保持されているデータが反映されている。よって、上記電位を読み取ることで、データを記憶素子300から読み出すことができる。

【0118】

なお、データの保持時における消費電力を削減するために、入力されたデータの保持を、容量素子305、容量素子307において行う場合は、スイッチング素子303をオフ、スイッチング素子304をオン、容量用スイッチング素子306をオン、容量用スイッチング素子308をオンとする。そして、容量用スイッチング素子306を介して、第1の位相反転素子301及び第2の位相反転素子302に保持されているデータの値に見合った量の電荷が、容量素子305に蓄積されることで、容量素子305へのデータの書き込みが行われる。また、容量用スイッチング素子308を介して、第1の位相反転素子301及び第2の位相反転素子302に保持されているデータの値に見合った量の電荷が、容量素子307に蓄積されることで、容量素子307へのデータの書き込みが行われる。なお、容量素子305が有する一対の電極間の電圧と、容量素子307が有する一対の電極間の電圧は、その極性が逆になる。

【0119】

容量素子305にデータが記憶された後、容量用スイッチング素子306をオフにすることで、容量素子305に記憶されたデータは保持される。また、容量素子307にデータが記憶された後、容量用スイッチング素子308をオフにすることで、容量素子307に記憶されたデータは保持される。容量用スイッチング素子306、容量用スイッチング素子308をオフにした後は、第1のノードと第2のノードとに、例えば電源電位VSSを与えて等電位とすることで、第1のノードと第2のノード間の電源電圧の印加を停止する。

【0120】

このように、入力されたデータの保持を容量素子305及び容量素子307において行う場合は、第1のノードと第2のノード間に電源電圧を印加する必要がないので、第1の位相反転素子301が有するpチャネル型トランジスタ309及びnチャネル型トランジスタ310、或いは、第2の位相反転素子302が有するpチャネル型トランジスタ311及びnチャネル型トランジスタ312を介して、第1のノードと第2のノードの間に流れるオフ電流を、限りなく0にすることができる。したがって、保持時における記憶素子のオフ電流に起因する消費電力を大幅に削減することができ、記憶装置、延いては記憶装置を用いた半導体装置全体の、消費電力を低く抑えることが可能となる。

【0121】

また、容量用スイッチング素子306及び容量用スイッチング素子308に用いられているトランジスタは、高純度化された酸化物半導体をチャネル形成領域に用いているので、そのオフ電流密度を、 $100\text{ zA}/\mu\text{m}$ 以下、好ましくは $10\text{ zA}/\mu\text{m}$ 以下、更に好ましくは $1\text{ zA}/\mu\text{m}$ 以下にすることができる。よって、高純度化された酸化物半導体膜を活性層として用いたトランジスタは、オフ電流が、結晶性を有するシリコンを用いたトランジスタに比べて著しく低い。その結果、上記トランジスタを用いた容量用スイッチング素子306がオフである時、容量素子305に蓄積された電荷は殆ど放電しないため、データは保持される。また、上記トランジスタを用いた容量用スイッチング素子308がオフである時、容量素子307に蓄積された電荷は殆ど放電しないため、データは保持される。

【0122】

なお、容量素子305及び容量素子307に記憶されているデータを読み出す場合は、第1のノードに電源電位VDDを与え、第2のノードに電源電位VSSを与えることで、第1のノードと第2のノード間に電源電圧を印加する。この状態で、容量用スイッチング素子306をオンとする。第1のノードと第2のノード間に電源電圧が与えられると、第1

10

20

30

40

50

の位相反転素子 301 の出力端子には、入力端子の電位の位相が反転した電位が与えられる。なお、第 1 の位相反転素子 301 の入力端子には、容量素子 305 に蓄積されている電荷量に見合った高さの電位が与えられるので、その出力端子の電位にはデータが反映される。また、容量用スイッチング素子 308 をオンにすることで、容量素子 305 に蓄積されている電荷量に見合った高さの電位が、第 1 の位相反転素子 301 の出力端子に与えられる。よって、データが反映された電位を有する信号 OUT を、記憶素子 300 から読み出すことができる。

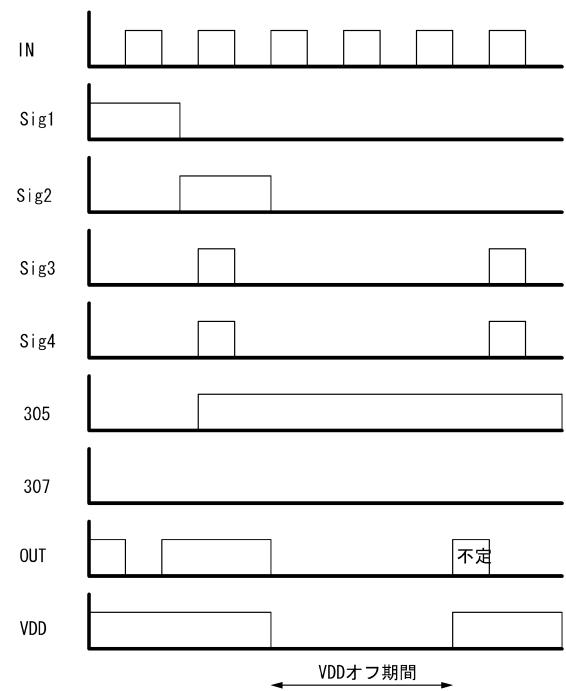

#### 【 0123 】

図 28 は、図 6 の回路の電源電位 VDD の供給を停止しない場合のタイミングチャートの一例である。信号 Sig 1 がローレベルになり、信号 Sig 2 はハイレベルになることによって、信号 IN が遮断され、帰還ループができ、状態が保持できる。信号 Sig 1 が再びハイレベルになり、信号 Sig 2 がローレベルになると、信号 IN が入り、第 1 の位相反転素子 301 を介して出力される。このとき信号 Sig 3、信号 Sig 4 はローレベルとする。

#### 【 0124 】

図 29 は、図 6 の回路の電源電位 VDD の供給を停止する場合のタイミングチャートの一例である。信号 Sig 1 がローレベルになり、信号 Sig 2 はハイレベルになることによって、信号 IN が遮断され、帰還ループができ、状態が保持できる。この後、信号 Sig 3、信号 Sig 4 をハイレベルにすることによって容量素子 305、容量素子 307 に記憶がなされる。その後、電源電位 VDD の供給が停止しても容量素子 305、容量素子 307 の電位は保持される（図 29 では容量素子 305 がハイレベル、容量素子 307 はローレベル）。その後、電源電位 VDD が供給され、信号 Sig 3、信号 Sig 4 が再度ハイレベルになると、容量素子 305 の電位が第 1 の位相反転素子 301 を介して出力され、容量素子 307 の電位が出力される（図 29 では共にローレベル）。

#### 【 0125 】

本実施の形態は、上記実施の形態と適宜組み合わせて実施することが可能である。

#### 【 0126 】

##### ( 実施の形態 4 )

本発明の一態様に係る半導体装置は、シリコンを用いたトランジスタと、酸化物半導体を用いたトランジスタとを有する。シリコンを用いたトランジスタは、シリコンウェハ、SOI (Silicon on Insulator) 基板、絶縁表面上のシリコン薄膜などを用いて形成することができる。

#### 【 0127 】

SOI 基板は、例えば、スマートカット（登録商標）に代表される UNIBOND（登録商標）、ELTRAN（Epitaxial Layer Transfer）（登録商標）、誘電体分離法、PACE（Plasma Assisted Chemical Etching）法などの方法や、SIMOX（Separation by Implanted Oxygen）法などを用いて作製することができる。

#### 【 0128 】

絶縁表面を有する基板上に形成されたシリコンの半導体膜は、公知の技術により結晶化しても良い。公知の結晶化方法としては、レーザ光を用いたレーザ結晶化法、触媒元素を用いる結晶化法がある。或いは、触媒元素を用いる結晶化法とレーザ結晶化法とを組み合わせて用いることもできる。また、石英のような耐熱性に優れている基板を用いる場合、電熱炉を使用した熱結晶化方法、赤外光を用いたランプアニール結晶化法、触媒元素を用いる結晶化法、950 度の高温アニール法を組み合わせた結晶法を用いても良い。

#### 【 0129 】

また、上記方法を用いて作製される半導体素子を、プラスチックなどの可撓性を有する基板上に移すことで、半導体装置を形成しても良い。転写には、様々な方法を用いることができる。例えば、基板と半導体素子の間に金属酸化膜を設け、該金属酸化膜を結晶化により脆弱化して半導体素子を剥離し、移す方法、基板と半導体素子の間に水素を含む非晶質

10

20

30

40

50

珪素膜を設け、レーザ光の照射またはエッティングにより該非晶質珪素膜を除去することで基板と半導体素子とを剥離し、移す方法、半導体素子が形成された基板を機械的に削除または溶液やガスによるエッティングで除去することで半導体素子を基板から切り離し、移す方法等が挙げられる。

#### 【 0 1 3 0 】

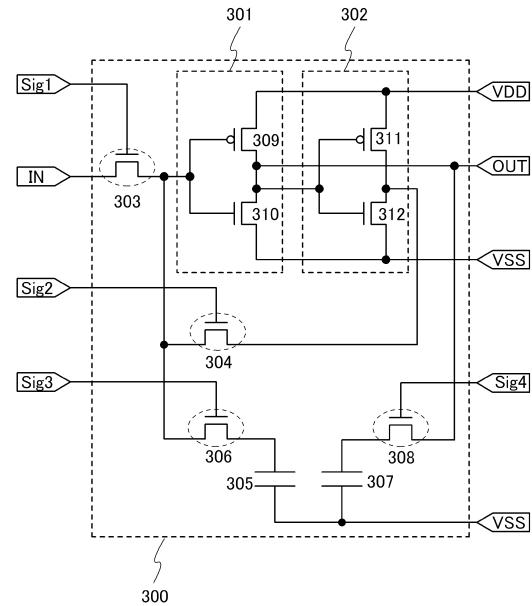

本実施の形態では、SOI (Silicon on Insulator) 基板を用いて、シリコンを有するトランジスタを作製した後、酸化物半導体を有するトランジスタを作製する場合を例に挙げて、半導体装置の構造及びその作製方法について説明する。

#### 【 0 1 3 1 】

まず、図7(A)に示すように、ボンド基板500を洗浄した後、ボンド基板500の表面に絶縁膜501を形成する。 10

#### 【 0 1 3 2 】

ボンド基板500として、シリコンの単結晶半導体基板を用いることができる。また、ボンド基板500として、結晶格子に歪みを有するシリコン、シリコンに対しゲルマニウムが添加されたシリコングルマニウムなどの半導体基板を用いていても良い。

#### 【 0 1 3 3 】

なお、ボンド基板500に用いられる単結晶半導体基板は、結晶軸の方向が基板内において揃っていることが望ましいが、点欠陥、線欠陥、面欠陥などの格子欠陥が完璧に排除された完全結晶である必要はない。

#### 【 0 1 3 4 】

ボンド基板500の形状は円形に限定されず、円形以外の形状に加工されていても良い。例えば、後に貼り合わせるベース基板503の形状が一般的に矩形状であること、及び縮小投影型露光装置などの露光装置の露光領域が矩形であること等を考慮し、ボンド基板500が矩形となるように、その形状を加工しても良い。ボンド基板500の形状の加工は、市販の円形状の単結晶半導体基板を切断することで、行うことができる。 20

#### 【 0 1 3 5 】

絶縁膜501は、単数の絶縁膜を用いたものであっても、複数の絶縁膜を積層して用いたものであっても良い。絶縁膜501の厚さは、後に不純物が含まれる領域が除去されることを考慮して、15nm以上500nm以下とするなど良い。

#### 【 0 1 3 6 】

絶縁膜501を構成する膜には、酸化珪素膜、窒化珪素膜、酸化窒化珪素膜、窒化酸化珪素膜、酸化ゲルマニウム、窒化ゲルマニウム膜、酸化窒化ゲルマニウム膜、窒化酸化ゲルマニウム膜などの珪素またはゲルマニウムを組成に含む絶縁膜を用いることができる。また、酸化アルミニウム、酸化タンタル、酸化ハフニウムなどの金属の酸化物でなる絶縁膜、窒化アルミニウムなどの金属の窒化物でなる絶縁膜、酸化窒化アルミニウム膜などの金属の酸化窒化物でなる絶縁膜、窒化酸化アルミニウム膜などの金属の窒化酸化物でなる絶縁膜を用いることもできる。 30

#### 【 0 1 3 7 】

本実施の形態では、ボンド基板500を熱酸化することによって形成された酸化珪素を、絶縁膜501として用いる例を示す。なお、図7(A)では、絶縁膜501がボンド基板500の全面を覆うように形成されているが、絶縁膜501は、ボンド基板500の少なくとも一面に形成されればよい。 40

#### 【 0 1 3 8 】

なお、本明細書において酸化窒化物とは、その組成として、窒素よりも酸素の含有量が多い物質であり、また、窒化酸化物とは、その組成として、酸素よりも窒素の含有量が多い物質をいう。

#### 【 0 1 3 9 】

また、ボンド基板500の表面を熱酸化することにより絶縁膜501を形成する場合、熱酸化は、含有水分量が低い酸素を用いるドライ酸化、酸素雰囲気中に塩化水素などのハロゲンを含むガスを添加する熱酸化、などを用いることができる。また、水素を酸素で燃焼

させて水を作るパイロジェニック酸化、高純度純水を100度以上に加熱した水蒸気を用いて酸化を行う水蒸気酸化などのウェット酸化を、絶縁膜501の形成に用いても良い。

#### 【0140】

ベース基板503にアルカリ金属若しくはアルカリ土類金属などの半導体装置の信頼性を低下させる不純物を含むような基板を用いる場合、ベース基板503からの分離後に形成される半導体膜に、上記不純物が拡散することを防止できるようなバリア膜を、少なくとも1層以上、絶縁膜501が有することが好ましい。バリア膜として用いることが出来る絶縁膜には、窒化珪素膜、窒化酸化珪素膜、窒化アルミニウム膜、または窒化酸化アルミニウム膜などが挙げられる。バリア膜として用いる絶縁膜は、例えば厚さ15nm～300nmの膜厚で形成することが好ましい。また、バリア膜とボンド基板500との間に、酸化珪素膜や酸化窒化珪素膜などの、バリア膜より窒素の含有率の低い絶縁膜を形成しても良い。窒素の含有率の低い絶縁膜の厚さは、5nm以上200nm以下とすれば良い。

10

#### 【0141】

酸化珪素を絶縁膜501として用いる場合、絶縁膜501はシランと酸素、TEOS（テトラエトキシシラン）と酸素等の混合ガスを用い、熱CVD、プラズマCVD、常圧CVD、バイアスECR CVD等の気相成長法によって形成することができる。この場合、絶縁膜501の表面を酸素プラズマ処理で緻密化しても良い。また、窒化珪素を絶縁膜501として用いる場合、シランとアンモニアの混合ガスを用い、プラズマCVD等の気相成長法によって形成することができる。

20

#### 【0142】

また、有機シランガスを用いて化学気相成長法により作製される酸化珪素を、絶縁膜501として用いても良い。有機シランガスとしては、珪酸エチル（TEOS：化学式Si(OCH<sub>3</sub>)<sub>4</sub>）、テトラメチルシラン（TMS：化学式Si(CH<sub>3</sub>)<sub>4</sub>）、テトラメチルシクロテトラシロキサン（TMCTS）、オクタメチルシクロテトラシロキサン（OMCTS）、ヘキサメチルジシラザン（HMDS）、トリエトキシシラン（SiH(OCH<sub>3</sub>)<sub>3</sub>）、トリスジメチルアミノシラン（SiH(N(CH<sub>3</sub>)<sub>2</sub>)<sub>3</sub>）等のシリコン含有化合物を用いることができる。

20

#### 【0143】

ソースガスに有機シランを用いることで、プロセス温度が350℃以下で、平滑な表面を有する酸化珪素膜を形成することができる。また、熱CVD法で、加熱温度が200℃以上500℃以下で形成されるLTO（低温酸化物、low temperature oxide）を用いることができる。LTOの形成には、シリコンソースガスにモノシラン（SiH<sub>4</sub>）またはジシラン（Si<sub>2</sub>H<sub>6</sub>）などを用い、酸素ソースガスに二酸化窒素（NO<sub>2</sub>）などを用いることができる。

30

#### 【0144】

例えば、ソースガスにTEOSとO<sub>2</sub>を用いて、酸化珪素膜でなる絶縁膜501を形成する場合、TEOSの流量15sccm、O<sub>2</sub>の流量750sccm、成膜圧力100Pa、成膜温度300℃、RF出力300W、電源周波数13.56MHzとすれば良い。

30

#### 【0145】

なお、有機シランを用いて形成された酸化珪素膜、または低温で成膜した窒化酸化珪素膜などの、比較的低温で成膜された絶縁膜は、表面にOH基を多く有する。OH基は水分子と水素結合することでシラノール基を形成して、ベース基板と絶縁膜とを低温で接合する。そして、最終的には共有結合であるシロキサン結合が、ベース基板と絶縁膜との間に形成される。よって、上記の有機シランを用いて形成された酸化珪素膜、または比較的低温で成膜されたLTOなどの絶縁膜は、Smart Cutなどで用いられているOH基が存在しない或いは非常に少ない熱酸化膜よりも、低温での接合に向いていると言える。

40

#### 【0146】

絶縁膜501は、平滑で親水性の接合面をボンド基板500の表面に形成するための膜である。そのため、絶縁膜501の平均粗さRaが0.7nm以下、より好ましくは、0.4nm以下が好ましい。また、絶縁膜501の厚さは5nm以上500nm以下であり、

50

より好ましくは 10 nm 以上 200 nm 以下とすれば良い。

#### 【0147】

次に図 7 (B) に示すように、ボンド基板 500 に、電界で加速されたイオンであるイオンビームを、矢印で示すように絶縁膜 501 を介してボンド基板 500 に照射し、ボンド基板 500 の表面から一定の深さの領域に、微小ボイドを有する脆化層 502 を形成する。例えば、脆化層は、結晶構造が乱されることで局所的に脆弱化された層を意味し、その状態は脆化層を形成する手段によって異なる。なお、ボンド基板の一表面から脆化層までの領域も多少脆弱化される場合があるが、脆化層は後に分断される領域及びその付近の層を指す。

#### 【0148】

脆化層 502 が形成される領域の深さは、イオンビームの加速エネルギーとイオンビームの入射角によって調節することができる。イオンの平均侵入深さとほぼ同じ深さの領域に脆化層 502 が形成される。イオンを注入する深さで、ボンド基板 500 から後に分離される半導体膜 504 の厚さが決定される。脆化層 502 が形成される深さは例えば 50 nm 以上 500 nm 以下とすることができ、好ましくは 50 nm 以上 200 nm 以下とするといい。

#### 【0149】

イオンをボンド基板 500 に注入するには、質量分離を伴わないイオンドーピング法で行なうことがタクトタイムを短縮するという点で望ましいが、本発明は質量分離を伴うイオン注入法を用いていても良い。

#### 【0150】

ソースガスに水素 ( $H_2$ ) を用いる場合、水素ガスを励起して  $H^+$ 、 $H_2^+$ 、 $H_3^+$  を生成することができる。ソースガスから生成されるイオン種の割合は、プラズマの励起方法、プラズマを発生させる雰囲気の圧力、ソースガスの供給量などを調節することで、変化させることができる。イオンドーピング法でイオン注入を行う場合、イオンビームに、 $H^+$ 、 $H_2^+$ 、 $H_3^+$  の総量に対して  $H_3^+$  が 50 % 以上、より好ましくは 80 % 以上含まれていることが好ましい。 $H_3^+$  の割合を 80 % 以上とすることで、イオンビームに含まれる  $H_2^+$  イオンの割合が相対的に小さくなるため、イオンビームに含まれる水素イオンの平均侵入深さのばらつきが小さくなるので、イオンの注入効率が向上し、タクトタイムを短縮することができる。

#### 【0151】

また、 $H_3^+$  は  $H^+$ 、 $H_2^+$  に比べて質量が大きい。そのため、イオンビームにおいて、 $H_3^+$  の割合が多い場合と、 $H^+$ 、 $H_2^+$  の割合が多い場合とでは、ドーピングの際の加速電圧が同じであっても、前者の場合の方が、ボンド基板 500 の浅い領域に水素を注入することができる。また前者の場合、ボンド基板 500 に注入される水素の、厚さ方向における濃度分布が急峻となるため、脆化層 502 の厚さ自体も薄くすることができる。

#### 【0152】

水素ガスを用いて、イオンドーピング法でイオン注入を行う場合、加速電圧 10 kV 以上 200 kV 以下、ドーズ量  $1 \times 10^{16} \text{ ions/cm}^2$  以上  $6 \times 10^{16} \text{ ions/cm}^2$  以下とすることで、イオンビームに含まれるイオン種及びその割合、絶縁膜 501 の膜厚にもよるが、脆化層 502 をボンド基板 500 の深さ 50 nm 以上 500 nm 以下の領域に形成することができる。

#### 【0153】

例えば、ボンド基板 500 が単結晶シリコン基板であり、絶縁膜 501 が厚さ 100 nm の熱酸化膜で形成されている場合、ソースガスである 100 % 水素ガスの流量が 50 sccm、ビーム電流密度  $5 \mu A/cm^2$ 、加速電圧 50 kV、ドーズ量  $2.0 \times 10^{16} \text{ atoms/cm}^2$  の条件では、ボンド基板 500 から厚さ 146 nm 程度の半導体膜を分離することができる。なお、水素をボンド基板 500 に添加する際の条件が同じであっても、絶縁膜 501 の膜厚をより大きくすることで、半導体膜の膜厚をより小さくすることができる。

10

20

30

40

50

## 【0154】

イオンビームのソースガスにヘリウム(He)を用いることもできる。ヘリウムを励起して生成されるイオン種は、He<sup>+</sup>が殆どであるため、質量分離を伴わないイオンドーピング法でも、He<sup>+</sup>を主たるイオンとしてボンド基板500に注入することができる。よって、イオンドーピング法で、効率良く、微小な空孔を脆化層502に形成することができる。ヘリウムを用いて、イオンドーピング法でイオン注入を行う場合、加速電圧10kV以上200kV以下、ドーズ量 $1 \times 10^{16}$  ions/cm<sup>2</sup>以上 $6 \times 10^{16}$  ions/cm<sup>2</sup>以下とすることができます。

## 【0155】

ソースガスに塩素ガス(Cl<sub>2</sub>ガス)、フッ素ガス(F<sub>2</sub>ガス)などのハロゲンガスを用いることもできる。10

## 【0156】

なお、イオンドーピング法でボンド基板500にイオン注入を行う場合、イオンドーピング装置内に存在する不純物がイオンと共に被処理物に注入されるため、絶縁膜501の表面近傍にS、Ca、Fe、Mo等の不純物が存在する可能性がある。よって、絶縁膜501の表面近傍の最も不純物が多いと考えられる領域を、エッチングや、研磨などにより除去しておいても良い。具体的には、絶縁膜501の表面から10nm~100nm、より望ましくは30~70nm程度の深さまでの領域を除去すれば良い。ドライエッチングだと、反応性イオンエッチング(RIE: Reactive Ion Etching)法、例えは、ICP(Inductively Coupled Plasma)エッティング法、ECR(Electron Cyclotron Resonance)エッティング法、平行平板型(容量結合型)エッティング法、マグネットロンプラズマエッティング法、2周波プラズマエッティング法またはヘリコン波プラズマエッティング法などを用いることができる。例えは、窒化酸化珪素膜の表面近傍をICPエッティング法で除去する場合、エッティングガスであるCHF<sub>3</sub>の流量を7.5sccm、Heの流量を100sccm、反応圧力5.5Pa、下部電極の温度70、コイル型の電極に投入するRF(13.56MHz)電力475W、下部電極(バイアス側)に投入する電力300W、エッティング時間10sec程度とすることで、表面から50nm程度の深さまでの領域を除去することができる。20

## 【0157】

エッティングガスとして、フッ素系ガスであるCHF<sub>3</sub>の他に、Cl<sub>2</sub>、BCl<sub>3</sub>、SiCl<sub>4</sub>、CCl<sub>4</sub>などの塩素系ガス、CF<sub>4</sub>、SF<sub>6</sub>、NF<sub>3</sub>などのフッ素系ガス、O<sub>2</sub>を適宜用いることができる。また用いるエッティングガスにHe以外の不活性気体を添加しても良い。例えは、添加する不活性元素として、Ne、Ar、Kr、Xeから選ばれた一種または複数種の元素を用いることができる。また窒化酸化珪素膜の表面近傍をウェットエッティングで除去する場合、フッ化水素アンモニウム、フッ化アンモニウム等を含む水溶液を、エッチャントとして用いれば良い。また研磨は、化学的機械的研磨(CMP: Chemical Mechanical Polishing)または液体ジェット研磨などにより、行うことができる。30

## 【0158】

脆化層502の形成後に、絶縁膜501の表面近傍における汚染の著しい領域を、エッティングまたは研磨などにより除去することで、ベース基板503上に形成される半導体膜504に混入する不純物の量を抑えることができる。また、最終的に形成される半導体装置では、不純物の影響により、しきい値電圧の変動、リーク電流の増加などのトランジスタの電気的特性の低下及び信頼性の低下が生じるのを防ぐことができる。40

## 【0159】

上記不純物の除去には、原子ビーム若しくはイオンビームの照射処理、プラズマ処理、若しくはラジカル処理で行うことができる。原子ビーム若しくはイオンビームを利用する場合には、アルゴン等の不活性ガス中性原子ビーム若しくは不活性ガスイオンビームを用いることができる。50

**【 0 1 6 0 】**

次に、図7(C)に示すように、絶縁膜501を間に挟むように、ボンド基板500とベース基板503を貼り合わせる。

**【 0 1 6 1 】**

なお、ベース基板503とボンド基板500との貼り合わせを行う前に、貼り合わせに係る表面、すなわち本実施の形態では、ボンド基板500上に形成された絶縁膜501とベース基板503の表面に、絶縁膜501とベース基板503の接合強度を向上させるための表面処理を施すことが好ましい。

**【 0 1 6 2 】**

表面処理としては、ウェット処理、ドライ処理、またはウェット処理およびドライ処理の組み合わせが挙げられる。異なるウェット処理、または異なるドライ処理を組み合わせて行っても良い。ウェット処理としては、オゾン水を用いたオゾン処理（オゾン水洗浄）、メガソニック洗浄などの超音波洗浄、または2流体洗浄（純水や水素添加水等の機能水を窒素等のキャリアガスとともに吹き付ける方法）、塩酸と過酸化水素水を用いた洗浄などが挙げられる。ドライ処理としては、不活性ガス中性原子ビーム処理、不活性ガスイオンビーム処理、紫外線処理、オゾン処理、プラズマ処理、バイアス印加プラズマ処理、またはラジカル処理などが挙げられる。上記のような表面処理を行うことで、貼り合わせに係る表面の親水性および清浄度を高め、その結果、接合強度を向上させることができる。

**【 0 1 6 3 】**

貼り合わせは、ベース基板503と、ボンド基板500上の絶縁膜501とを密着させた後、重ね合わせたベース基板503とボンド基板500の一部に、 $1\text{ N}/\text{cm}^2$ 以上 $500\text{ N}/\text{cm}^2$ 以下、好ましくは $11\text{ N}/\text{cm}^2$ 以上 $20\text{ N}/\text{cm}^2$ 以下程度の圧力を加える。圧力を加えると、その部分からベース基板503と絶縁膜501とが接合を開始し、最終的には密着した面全体に接合があよぶ。

**【 0 1 6 4 】**

接合はファンデルワールス力や水素結合を用いて行われているため、室温でも強固な接合が形成される。なお、上記接合は低温で行うことが可能であるため、ベース基板503は様々なものを用いることが可能である。例えばベース基板503としては、アルミニノシリケートガラス、バリウムホウケイ酸ガラス、アルミニノホウケイ酸ガラスなどの電子工業用に使われる各種ガラス基板の他、石英基板、セラミック基板、サファイア基板などの基板を用いることが出来る。さらにベース基板503として、シリコン、ガリウムヒ素、インジウムリンなどの半導体基板などを用いることができる。或いは、ステンレス基板を含む金属基板をベース基板503として用いても良い。なお、ベース基板503として用いるガラス基板は、熱膨張係数が $25 \times 10^{-7}/$ 以上 $50 \times 10^{-7}/$ 以下（好ましくは、 $30 \times 10^{-7}/$ 以上 $40 \times 10^{-7}/$ 以下）であり、歪み点が580以上680以下（好ましくは、600以上680以下）である基板を用いることが好ましい。また、ガラス基板として無アルカリガラス基板を用いると、不純物による半導体装置の汚染を抑えることができる。

**【 0 1 6 5 】**

ガラス基板としては、液晶パネルの製造用に開発されたマザーガラス基板を用いることができる。マザーガラスとしては、例えば、第3世代( $550\text{ mm} \times 650\text{ mm}$ )、第3.5世代( $600\text{ mm} \times 720\text{ mm}$ )、第4世代( $680\text{ mm} \times 880\text{ mm}$ または、 $730\text{ mm} \times 920\text{ mm}$ )、第5世代( $1100\text{ mm} \times 1300\text{ mm}$ )、第6世代( $1500\text{ mm} \times 1850\text{ mm}$ )、第7世代( $1870\text{ mm} \times 2200\text{ mm}$ )、第8世代( $2200\text{ mm} \times 2400\text{ mm}$ )などのサイズの基板が知られている。大面積のマザーガラス基板をベース基板503として用いてSOI基板を製造することで、SOI基板の大面積化が実現できる。マザーガラス基板のような大型の基板をベース基板503として用いることで、SOI基板の大面積化が実現できる。SOI基板の大面積化が実現すれば、1枚の基板から製造されるIC、LSI等のチップ数が増加するので、生産性を飛躍的に向上させることができる。

10

20

30

40

50

## 【 0 1 6 6 】

ベース基板 503 として使用することができる基板に大きな制限はないが、少なくとも、後の加熱処理に耐えうる程度の耐熱性を有していることが必要となる。例えば、フュージョン法やフロート法で作製されるガラス基板を用いることができる。ガラス基板としては、後の加熱処理の温度が高い場合には、歪み点が 730 以上のものを用いると良い。また、ガラス基板には、例えば、アルミノシリケートガラス、アルミノホウケイ酸ガラス、バリウムホウケイ酸ガラスなどのガラス材料が用いられている。なお、一般に、酸化ホウ素と比較して酸化バリウム (BaO) を多く含ませることで、より実用的な耐熱ガラスが得られる。このため、B<sub>2</sub>O<sub>3</sub> より BaO を多く含むガラス基板を用いることが好ましい。なお、シュリンクに起因する貼り合わせの不良を回避するために、接合を行う前に、ベース基板 503 に予め加熱処理を施しておいても良い。

10

## 【 0 1 6 7 】

また、ベース基板 503 上に絶縁膜を形成しておいても良い。ベース基板 503 は、その表面に絶縁膜が必ずしも形成されていなくとも良いが、ベース基板 503 の表面に絶縁膜を形成しておくことで、ベース基板 503 からボンド基板 500 に、アルカリ金属やアルカリ土類金属などの不純物が入り込むのを防ぐことができる。またベース基板 503 の表面に絶縁膜を形成しておく場合、ベース基板 503 上の絶縁膜が絶縁膜 501 と接合するので、ベース基板 503 として用いることができる基板の種類がさらに広がる。プラスチック等の可撓性を有する合成樹脂からなる基板は耐熱温度が一般的に低い傾向にあるが、後の半導体素子の作製工程における処理温度に耐え得るのであれば、ベース基板 503 上に絶縁膜を形成する場合において、ベース基板 503 として用いることが可能である。プラスチック基板として、ポリエチレンテレフタレート (PET) に代表されるポリエチル、ポリエーテルスルホン (PES)、ポリエチレンナフタレート (PEN)、ポリカーボネート (PC)、ポリエーテルエーテルケトン (PEEK)、ポリスルホン (PSF)、ポリエーテルイミド (PEI)、ポリアリレート (PAR)、ポリブチレンテレフタレート (PBT)、ポリイミド、アクリロニトリルブタジエンスチレン樹脂、ポリ塩化ビニル、ポリプロピレン、ポリ酢酸ビニル、アクリル樹脂などが挙げられる。ベース基板 503 上に絶縁膜を形成する場合、絶縁膜 501 と同様に、該絶縁膜の表面に表面処理を行ってから貼り合わせを行うと良い。

20

## 【 0 1 6 8 】

ベース基板 503 にボンド基板 500 を貼り合わせた後、ベース基板 503 と絶縁膜 501 との接合界面での結合力を増加させるための加熱処理を行うことが好ましい。この処理温度は、脆化層 502 に亀裂を発生させない温度とし、200 以上 400 以下の温度範囲で処理することができる。また、この温度範囲で加熱しながら、ベース基板 503 にボンド基板 500 を貼り合わせることで、ベース基板 503 と絶縁膜 501 と間ににおける接合の結合力を強固にすることができます。

30

## 【 0 1 6 9 】

なお、ボンド基板 500 とベース基板 503 とを貼り合わせるときに、接合面がゴミなどにより汚染されてしまうと、汚染部分は接合されなくなる。接合面の汚染を防ぐために、ボンド基板 500 とベース基板 503 との貼り合わせは、気密な処理室内で行うことが好ましい。また、ボンド基板 500 とベース基板 503 とを貼り合わせるとき、処理室内を  $5.0 \times 10^{-3}$  Pa 程度の減圧状態とし、接合処理の雰囲気を清浄にするようにしても良い。

40

## 【 0 1 7 0 】

次いで、加熱処理を行うことで、脆化層 502 において隣接する微小ボイドどうしが結合して、微小ボイドの体積が増大する。その結果、図 7 (D) に示すように、脆化層 502 においてボンド基板 500 の一部である半導体膜 504 が、ボンド基板 500 から分離する。絶縁膜 501 はベース基板 503 に接合しているので、ベース基板 503 上にはボンド基板 500 から分離された半導体膜 504 が固定される。半導体膜 504 をボンド基板 500 から分離するための加熱処理の温度は、ベース基板 503 の歪み点を越えない温度

50

とする。

#### 【0171】

この加熱処理には、RTA (Rapid Thermal Anneal) 装置、抵抗加熱炉、マイクロ波加熱装置を用いることができる。RTA装置には、GRTA (Gas Rapid Thermal Anneal) 装置、LRTA (Lamp Rapid Thermal Anneal) 装置を用いることができる。GRTA装置を用いる場合は、加熱温度550以上650以下、処理時間0.5分以上60分以内とすることができる。抵抗加熱装置を用いる場合は、加熱温度200以上650以下、処理時間2時間以上4時間以内とすることができる。

#### 【0172】

また、上記加熱処理は、マイクロ波などの高周波による誘電加熱を用いて行っても良い。誘電加熱による加熱処理は、高周波発生装置において生成された周波数300MHz乃至3THzの高周波をボンド基板500に照射することで行うことができる。具体的には、例えば、2.45GHzのマイクロ波を900W、14分間照射することで、脆化層内の隣接する微小ボイドどうしを結合させ、最終的にボンド基板500を脆化層において分断させることができる。

10

#### 【0173】

抵抗加熱を有する縦型炉を用いた加熱処理の具体的な処理方法を説明する。ボンド基板500が貼り付けられたベース基板503を、縦型炉のポートに載置し、該ポートを縦型炉のチャンバーに搬入する。ボンド基板500の酸化を抑制するため、まずチャンバー内を排気して真空状態とする。真空度は、 $5 \times 10^{-3}$ Pa程度とする。真空状態にした後、窒素をチャンバー内に供給して、チャンバー内を大気圧の窒素雰囲気にする。この間、加熱温度を200に上昇させる。

20

#### 【0174】

チャンバー内を大気圧の窒素雰囲気にした後、温度200で2時間加熱する。その後、1時間かけて400に温度上昇させる。加熱温度400の状態が安定したら、1時間かけて600に温度上昇させる。加熱温度600の状態が安定したら、600で2時間加熱処理する。その後、1時間かけて、加熱温度400まで下げ、10分～30分間に後に、チャンバー内からポートを搬出する。大気雰囲気下で、ポート上に並べられたボンド基板500、及び半導体膜504が貼り付けられたベース基板503を冷却する。

30

#### 【0175】

上記の抵抗加熱炉を用いた加熱処理は、絶縁膜501とベース基板503との結合力を強化するための加熱処理と、脆化層502を分割させる加熱処理が連続して行われる。この2つの加熱処理を異なる装置で行う場合は、例えば、抵抗加熱炉において、処理温度200、処理時間2時間の加熱処理を行った後、貼り合わされたベース基板503とボンド基板500を炉から搬出する。次いで、RTA装置で、処理温度600以上700以下、処理時間1分から数時間以内程度の加熱処理を行い、ボンド基板500を脆化層502で分断させる。

#### 【0176】

なお、ボンド基板500の周辺部は、ベース基板503と接合していないことがある。これは、ボンド基板500の周辺部が面取りされている、或いは周辺部が曲率を有しているため、ベース基板503と絶縁膜501とが密着しない、または、ボンド基板500の周辺部では脆化層502が分割しにくいなどの理由によるものと考えられる。また、その他の理由として、ボンド基板500を作製する際に行われるCMPなどの研磨が、ボンド基板500の周辺部で不十分であり、中央部に比べて周辺部では表面が荒れていることが挙げられる。また、ボンド基板500を移送する際に、キャリア等でボンド基板500の周辺部に傷が入ってしまった場合、該傷も、周辺部がベース基板503に接合しにくい理由になると考えられる。そのため、ベース基板503には、ボンド基板500よりもサイズの小さい半導体膜504が貼り付けられる。

40

#### 【0177】

50

なお、ボンド基板 500 を分離させる前に、ボンド基板 500 に水素化処理を行うようにしても良い。水素化処理は、例えば、水素雰囲気中において 350 ℃、2 時間程度行う。

#### 【0178】

なお、ベース基板 503 と複数のボンド基板 500 とを貼り合わせる場合、該複数のボンド基板 500 が異なる結晶面方位を有していても良い。半導体中における多数キャリアの移動度は、結晶面方位によって異なる。よって、形成する半導体素子に適した結晶面方位を有するボンド基板 500 を、適宜選択して半導体膜 504 を形成すればよい。例えば半導体膜 504 を用いて n 型の半導体素子を形成するならば、{100} 面を有する半導体膜 504 を形成することで、該半導体素子における多数キャリアの移動度を高めることができる。また、例えば半導体膜 504 を用いて p 型の半導体素子を形成するならば、{110} 面を有する半導体膜 504 を形成することで、該半導体素子における多数キャリアの移動度を高めることができる。そして、半導体素子としてトランジスタを形成するならば、チャネルの向きと結晶面方位とを考慮し、半導体膜 504 の貼り合わせの方向を定めるようとする。

#### 【0179】

次に、半導体膜 504 の表面を研磨により平坦化しても良い。平坦化は必ずしも必須ではないが、平坦化を行うことで、後に形成される半導体膜 506 及び半導体膜 507 とゲート絶縁膜の界面の特性を向上させることができる。具体的に研磨は、CMP または液体ジエット研磨などにより、行うことができる。半導体膜 504 の厚さは、上記平坦化により薄膜化される。上記平坦化は、エッチングする前の半導体膜 504 に施しても良いが、後にエッチングにより形成される半導体膜 506 及び半導体膜 507 に施しても良い。

#### 【0180】

また研磨ではなく、半導体膜 504 の表面をエッチングすることでも、半導体膜 504 の表面を平坦化することができる。エッチングには、反応性イオンエッチング (RIE : R e a c t i v e I o n E t c h i n g) 法、例えば ICP (I n d u c t i v e l y C o u p l e d P l a s m a) エッティング法、ECR (E l e c t r o n C y c l o t r o n R e s o n a n c e) エッティング法、平行平板型 (容量結合型) エッティング法、マグネットロンプラズマエッティング法、2 周波プラズマエッティング法またはヘリコン波プラズマエッティング法等のドライエッティング法を用いれば良い。

#### 【0181】

例えば ICP エッティング法を用いる場合、エッティングガスである塩素の流量 40 sccm ~ 100 sccm、コイル型の電極に投入する電力 100 W ~ 200 W、下部電極 (バイアス側) に投入する電力 40 W ~ 100 W、反応圧力 0.5 Pa ~ 1.0 Pa とすれば良い。例えば、エッティングガスである塩素の流量 100 sccm、反応圧力 1.0 Pa、下部電極の温度 70 ℃、コイル型の電極に投入する RF (13.56 MHz) 電力 150 W、下部電極 (バイアス側) に投入する電力 40 W、エッティング時間 25 sec ~ 27 sec とすることで、半導体膜 504 を 50 nm 乃至 60 nm 程度にまで薄膜化することができる。エッティングガスには、塩素、塩化硼素、塩化珪素または四塩化炭素などの塩素系ガス、四弗化炭素、弗化硫黄または弗化窒素などのフッ素系ガス、酸素などを適宜用いることができる。

#### 【0182】

上記エッティングにより、後に形成される半導体素子にとって最適となる膜厚まで半導体膜 504 を薄膜化できるのみならず、半導体膜 504 の表面を平坦化することができる。

#### 【0183】

なお、ベース基板 503 に密着された半導体膜 504 は、脆化層 502 の形成、脆化層 502 における分断によって、結晶欠陥が形成されている、または、その表面の平坦性が損なわれている。そこで、本発明の一態様では、結晶欠陥を低減、および平坦性を向上するために、半導体膜 504 の表面に形成されている自然酸化膜などの酸化膜を除去する処理を行った後、半導体膜 504 にレーザ光の照射を行う。

#### 【0184】

10

20

30

40

50

本発明実施の形態では、フッ化水素の濃度が0.5wt%のDHFに半導体膜504を10秒間さらすことで酸化膜を除去する。

#### 【0185】

レーザ光の照射は、半導体膜504を部分溶融させる程度のエネルギー密度で行うことが好ましい。完全溶融させると、液相となった半導体膜504で無秩序な核発生が起こるために、半導体膜504が再結晶化された際に微結晶が生成し、結晶性が低下するからである。部分溶融させることで、半導体膜504では、溶融されていない固相部分から結晶成長が進行する、いわゆる縦成長が起こる。縦成長による再結晶化によって、半導体膜504の結晶欠陥が減少され、結晶性が回復される。なお、半導体膜504が完全溶融状態であるとは、半導体膜504が絶縁膜501との界面まで溶融され、液体状態になっていることをいう。他方、半導体膜504が部分溶融状態であるとは、上層が溶融して液相であり、下層が固相である状態をいう。

10

#### 【0186】

このレーザ光の照射には、半導体膜504を部分的に溶融させるためにパルス発振でレーザ光の照射を行うことが望ましい。例えば、パルス発振の場合は、繰り返し周波数1MHz以下、パルス幅10n秒以上500n秒以下である。例えば、繰り返し周波数10Hz～300Hz、パルス幅25n秒、波長308nmのXeClエキシマレーザを用いることができる。

20

#### 【0187】

レーザ光は、半導体に選択的に吸収される固体レーザの基本波または第2高調波であることが望ましい。具体的には、例えば、波長が250nm以上700nm以下の範囲のレーザ光を用いることができる。また、レーザ光のエネルギーは、レーザ光の波長、レーザ光の表皮深さ、半導体膜504の膜厚などを考慮して決定することができる。例えば、半導体膜504の厚さが120nm程度で、レーザ光の波長が308nmのパルス発振レーザを用いる場合は、レーザ光のエネルギー密度を600mJ/cm<sup>2</sup>～700mJ/cm<sup>2</sup>とすれば良い。

20

#### 【0188】

パルス発振のレーザとして、例えばArレーザ、Krレーザ、エキシマレーザ、CO<sub>2</sub>レーザ、YAGレーザ、Y<sub>2</sub>O<sub>3</sub>レーザ、YVO<sub>4</sub>レーザ、YLFレーザ、YAlO<sub>3</sub>レーザ、ガラスレーザ、ルビーレーザ、アレキサンドライトレーザ、Ti：サファイアレーザ、銅蒸気レーザまたは金蒸気レーザを用いることができる。

30

#### 【0189】

本実施の形態では、レーザ光の照射は、半導体膜504の膜厚が146nm程度の場合、次のように行うことができる。レーザ光のレーザ発振器として、XeClエキシマレーザ（波長：308nm、パルス幅：20n秒、繰り返し周波数30Hz）を用いる。光学系により、レーザ光の断面を0.4mm×120mmの線状に整形する。レーザ光の走査速度を0.5mm/秒とし、レーザ光を半導体膜504に照射する。レーザ光の照射により、図7(E)に示すように、結晶欠陥が修復された半導体膜505が形成される。

#### 【0190】

なお、レーザ光の照射は、希ガスまたは窒素雰囲気のような不活性雰囲気、または減圧雰囲気で行うことが好ましい。上記雰囲気中でレーザ光を照射するには、気密性のあるチャンバー内でレーザ光を照射し、このチャンバー内の雰囲気を制御すればよい。チャンバーを用いない場合は、レーザ光の被照射面に窒素ガスなど不活性ガスを吹き付けることで不活性雰囲気でのレーザ光の照射を実現することができる。不活性雰囲気または減圧雰囲気においてレーザ光の照射を行うことで、大気雰囲気で行う場合よりも、自然酸化膜の発生をより抑え、レーザ光照射後に形成される半導体膜505にひび割れが生じる、またはピッチ縞が発生するのを抑え、半導体膜505の平坦性を向上させることができ、レーザ光の使用可能なエネルギー範囲を広くすることができる。

40

#### 【0191】

光学系により、レーザ光は、エネルギー分布を均一にし、かつ断面の形状を線状にするこ

50

とが好ましい。このことにより、スループット良く、かつレーザ光の照射を均一に行うことができる。レーザ光のビーム長は、ベース基板 503 の 1 辺より長くすることで、1 回の走査で、ベース基板 503 に貼り付けられた全ての半導体膜 504 にレーザ光を照射することができる。レーザ光のビーム長がベース基板 503 の 1 辺より短い場合は、複数回の走査で、ベース基板 503 に貼り付けられた全ての半導体膜 504 にレーザ光を照射することができるような、長さにすればよい。

#### 【0192】

希ガスまたは窒素雰囲気のような不活性雰囲気、または減圧雰囲気にて、レーザ光を照射するには、気密性のあるチャンバー内でレーザ光を照射し、このチャンバー内の雰囲気を制御すればよい。チャンバーを用いない場合は、レーザ光の被照射面に窒素ガスなど不活性ガスを吹き付けることで不活性雰囲気でのレーザ光の照射を実現することができる。不活性雰囲気または減圧雰囲気においてレーザ光の照射を行うことで、大気雰囲気で行う場合よりも、自然酸化膜の発生をより抑え、レーザ光照射後に形成される半導体膜 505 にひび割れが生じる、またはピッチ縞が発生するのを抑え、半導体膜 505 の平坦性を向上させることができ、レーザ光の使用可能なエネルギー範囲を広くすることができる。

10

#### 【0193】

レーザ光を照射する前に、ドライエッチングにより半導体膜 504 の表面を平坦化している場合、ドライエッチングにより半導体膜 504 の表面付近で結晶欠陥などの損傷が生じていることがある。しかし上記レーザ光の照射により、ドライエッチングにより生じる損傷をも補修することが可能である。

20

#### 【0194】

次にレーザ光を照射した後に、半導体膜 505 の表面をエッチングしても良い。レーザ光の照射後に半導体膜 505 の表面をエッチングする場合は、必ずしもレーザ光の照射を行う前に半導体膜 504 の表面をエッチングする必要はない。また、レーザ光の照射を行う前に半導体膜 504 の表面をエッチングした場合は、必ずしもレーザ光の照射後に半導体膜 505 の表面をエッチングする必要はない。或いは、レーザ光の照射後、レーザ光の照射前に、半導体膜 505 の表面をエッチングするようにしても良い。

#### 【0195】

上記エッチングにより、後に形成される半導体素子にとって最適となる膜厚まで半導体膜 505 を薄膜化できるのみならず、半導体膜 505 の表面を平坦化することができる。

30

#### 【0196】

レーザ光を照射した後、半導体膜 505 に 500 以上 650 以下の加熱処理を行うことが好ましい。この加熱処理によって、レーザ光の照射で回復されなかった、半導体膜 505 の欠陥の消滅、半導体膜 505 の歪みの緩和をすることができる。この加熱処理には、RTA (Rapid Thermal Anneal) 装置、抵抗加熱炉、マイクロ波加熱装置を用いることができる。RTA 装置には、GRTA (Gas Rapid Thermal Anneal) 装置、LRTA (Lamp Rapid Thermal Anneal) 装置を用いることができる。例えば、抵抗加熱炉を用いた場合は、600 で 4 時間加熱するとよい。

40

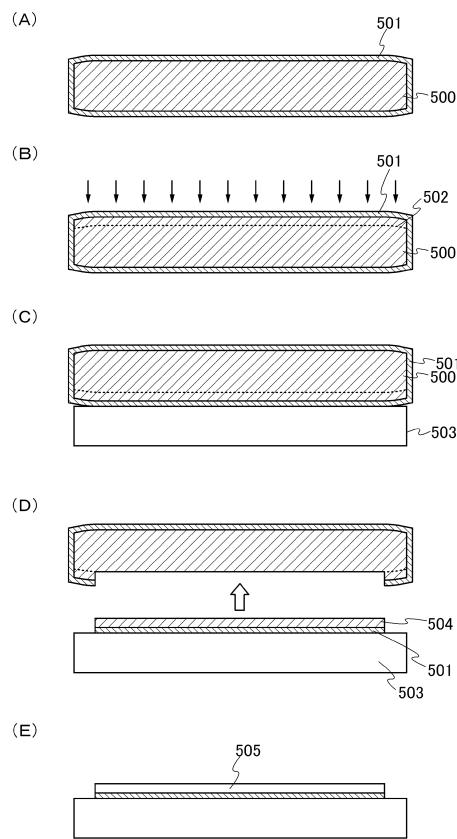

#### 【0197】

次に、図 8 (A) に示すように、半導体膜 505 を部分的にエッチングすることで、半導体膜 505 から島状の半導体膜 506 と半導体膜 507 を形成する。半導体膜 505 をさらにエッチングすることで、半導体膜 505 の端部において接合の強度が不十分である領域を、除去することができる。なお、本実施の形態では、一つの半導体膜 505 をエッチングすることで半導体膜 506 と半導体膜 507 を形成しているが、形成される半導体膜の数はこれに限定されない。

#### 【0198】

なお、半導体膜 505 が分離された後のボンド基板 500 は、その表面を平坦化することで、再度、半導体膜 505 を分離させることができる。

#### 【0199】

50

具体的には、ボンド基板 500 の主に端部に残存した絶縁膜 501 を、エッティングなどにより除去する。絶縁膜 501 が酸化珪素、酸化窒化珪素、または窒化酸化珪素で形成されている場合、フッ酸を用いたウェットエッティングを用いることが出来る。

#### 【0200】

次に、半導体膜 505 の分離によりボンド基板 500 の端部に形成された凸部と、水素を過剰に含んでいる、残存した脆化層を除去する。ボンド基板 500 のエッティングには、ウェットエッティングを用いることが好ましく、エッティング液には、水酸化テトラメチルアンモニウム (tetramethylammonium hydroxide、略称：TMH) 溶液を用いることができる。

#### 【0201】

次に、ボンド基板 500 の表面を研磨する。研磨は、CMP を用いることができる。ボンド基板 500 の表面を平滑化するため、 $1 \mu\text{m} \sim 10 \mu\text{m}$  程度研磨することが望ましい。研磨後は、ボンド基板 500 表面に研磨粒子などが残るため、フッ酸などを用いた RCA 洗浄を行う。

#### 【0202】

ボンド基板 500 を再利用することで、半導体基板の材料コストを削減することができる。

#### 【0203】

半導体膜 506 と半導体膜 507 には、閾値電圧を制御するために、硼素、アルミニウム、ガリウムなどの p 型不純物、若しくはリン、砒素などの n 型不純物を添加しても良い。閾値電圧を制御するための不純物の添加は、パターニングする前の半導体膜に対して行っても良いし、パターニング後に形成された半導体膜 506 と半導体膜 507 に対して行っても良い。また、閾値電圧を制御するための不純物の添加を、ボンド基板に対して行っても良い。若しくは、不純物の添加を、閾値電圧を大まかに調整するためにボンド基板に対して行った上で、閾値電圧を微調整するために、パターニング前の半導体膜に対して、またはパターニングにより形成された半導体膜 506 及び半導体膜 507 に対して行っても良い。

#### 【0204】

次に図 8 (B) に示すように、半導体膜 506 と半導体膜 507 を覆うように、ゲート絶縁膜 508 を形成する。ゲート絶縁膜 508 は、高密度プラズマ処理を行うことにより半導体膜 506 と半導体膜 507 の表面を酸化または窒化することで形成することができる。高密度プラズマ処理は、例えば He、Ar、Kr、Xe などの希ガスと酸素、酸化窒素、アンモニア、窒素、水素などの混合ガスとを用いて行う。この場合プラズマの励起をマイクロ波の導入により行うことで、低電子温度で高密度のプラズマを生成することができる。このような高密度のプラズマで生成された酸素ラジカル ( $\text{O}_\text{H}$  ラジカルを含む場合もある) や窒素ラジカル ( $\text{N}_\text{H}$  ラジカルを含む場合もある) によって、半導体膜の表面を酸化または窒化することにより、 $1 \sim 20 \text{ nm}$ 、望ましくは $5 \sim 10 \text{ nm}$  の絶縁膜が半導体膜に接するように形成される。この $5 \sim 10 \text{ nm}$  の絶縁膜をゲート絶縁膜 508 として用いる。例えば、亜酸化窒素 ( $\text{N}_2\text{O}$ ) を Ar で $1 \sim 3$  倍 (流量比) に希釈して、 $10 \sim 30 \text{ Pa}$  の圧力にて $3 \sim 5 \text{ kW}$  のマイクロ波 ( $2.45 \text{ GHz}$ ) 電力を印加して半導体膜 506 と半導体膜 507 の表面を酸化若しくは窒化させる。この処理により $1 \text{ nm} \sim 10 \text{ nm}$  (好ましくは $2 \text{ nm} \sim 6 \text{ nm}$ ) の絶縁膜を形成する。さらに亜酸化窒素 ( $\text{N}_2\text{O}$ ) とシリコン ( $\text{SiH}_4$ ) を導入し、 $10 \sim 30 \text{ Pa}$  の圧力にて $3 \sim 5 \text{ kW}$  のマイクロ波 ( $2.45 \text{ GHz}$ ) 電力を印加して気相成長法により酸化窒化シリコン膜を形成してゲート絶縁膜を形成する。固相反応と気相成長法による反応を組み合わせることにより界面準位密度が低く絶縁耐圧の優れたゲート絶縁膜を形成することができる。

#### 【0205】

上述した高密度プラズマ処理による半導体膜の酸化または窒化は固相反応で進むため、ゲート絶縁膜 508 と半導体膜 506 及び半導体膜 507 との界面準位密度をきわめて低くすることができる。また高密度プラズマ処理により半導体膜 506 及び半導体膜 507 を

10

20

30

40

50

直接酸化または窒化することで、形成される絶縁膜の厚さのばらつきを抑えることが出来る。また半導体膜が結晶性を有する場合、高密度プラズマ処理を用いて半導体膜の表面を固相反応で酸化させることにより、結晶粒界においてのみ酸化が速く進んでしまうのを抑え、均一性が良く、界面準位密度の低いゲート絶縁膜を形成することができる。高密度プラズマ処理により形成された絶縁膜を、ゲート絶縁膜の一部または全部に含んで形成されるトランジスタは、特性のばらつきを抑えることができる。

#### 【0206】

或いは、半導体膜506と半導体膜507を熱酸化させることで、ゲート絶縁膜508を形成するようにしても良い。また、プラズマCVD法またはスパッタリング法などを用い、酸化珪素、窒化酸化珪素、酸化窒化珪素、窒化珪素、酸化ハフニウム、酸化アルミニウムまたは酸化タンタルを含む膜を、単層で、または積層させることで、ゲート絶縁膜508を形成しても良い。10

#### 【0207】

次に、図8(C)に示すように、ゲート絶縁膜508上に導電膜を形成した後、該導電膜を所定の形状に加工(パターニング)することで、半導体膜506と半導体膜507の上方に電極509を形成する。導電膜の形成にはCVD法、スパッタリング法等を用いることが出来る。導電膜は、タンタル(Ta)、タンゲステン(W)、チタン(Ti)、モリブデン(Mo)、アルミニウム(Al)、銅(Cu)、クロム(Cr)、ニオブ(Nb)等を用いることが出来る。また上記金属を主成分とする合金を用いても良いし、上記金属を含む化合物を用いても良い。または、半導体膜に導電性を付与するリン等の不純物元素をドーピングした、多結晶珪素などの半導体を用いて形成しても良い。20

#### 【0208】

2つの導電膜の組み合わせとして、1層目に窒化タンタルまたはタンタルを、2層目にタンゲステンを用いることが出来る。上記例の他に、窒化タンゲステンとタンゲステン、窒化モリブデンとモリブデン、アルミニウムとタンタル、アルミニウムとチタン等が挙げられる。タンゲステンや窒化タンタルは、耐熱性が高いため、2層の導電膜を形成した後の工程において、熱活性化を目的とした加熱処理を行うことができる。また、2層の導電膜の組み合わせとして、例えば、n型を付与する不純物がドーピングされた珪素とニッケルシリサイド、n型を付与する不純物がドーピングされた珪素とタンゲステンシリサイド等も用いることが出来る。30

#### 【0209】

また、本実施の形態では電極509を単層の導電膜で形成しているが、本実施の形態はこの構成に限定されない。電極509は積層された複数の導電膜で形成されていても良い。3つ以上の導電膜を積層する3層構造の場合は、モリブデン膜とアルミニウム膜とモリブデン膜の積層構造を採用するとよい。

#### 【0210】

なお電極509を形成する際に、マスクを用いずに、液滴吐出法を用いて選択的に電極509を形成しても良い。

#### 【0211】

なお液滴吐出法とは、所定の組成物を含む液滴を細孔から吐出または噴出することで所定のパターンを形成する方法を意味し、インクジェット法などがその範疇に含まれる。40

#### 【0212】

また電極509は、導電膜を形成後、ICP(Inductively Coupled Plasma)または誘導結合型プラズマエッチャリング法を用い、エッチャリング条件(コイル型の電極層に印加される電力量、基板側の電極層に印加される電力量、基板側の電極温度等)を適宜調節することにより、所望のテーパー形状を有するようにエッチャリングすることができる。また、テーパー形状は、マスクの形状によっても角度等を制御することができる。なお、エッチャリング用ガスとしては、塩素、塩化硼素、塩化珪素もしくは四塩化炭素などの塩素系ガス、四弗化炭素、弗化硫黄もしくは弗化窒素などのフッ素系ガス又は酸素を適宜用いることができる。50

## 【0213】

次に図8(D)に示すように、電極509をマスクとして一導電型を付与する不純物元素を半導体膜506、半導体膜507に添加する。本実施の形態では、半導体膜506にn型を付与する不純物元素(例えばリンまたはヒ素)を、半導体膜507にp型を付与する不純物元素(例えばボロン)を添加する。なお、p型を付与する不純物元素を半導体膜507に添加する際、n型の不純物が添加される半導体膜506はマスク等で覆い、p型を付与する不純物元素の添加が選択的に行われるようとする。逆にn型を付与する不純物元素を半導体膜506に添加する際、p型の不純物が添加される半導体膜507はマスク等で覆い、n型を付与する不純物元素の添加が選択的に行われるようとする。或いは、先に半導体膜506及び半導体膜507にp型もしくはn型のいずれか一方を付与する不純物元素を添加した後、一方の半導体膜のみに選択的により高い濃度でp型もしくはn型のうちの他方を付与する不純物元素のいずれか一方を添加するようにしても良い。上記不純物の添加により、半導体膜506に不純物領域510、半導体膜507に不純物領域511が形成される。

## 【0214】

次に、図9(A)に示すように、電極509の側面にサイドウォール512を形成する。サイドウォール512は、例えば、ゲート絶縁膜508及び電極509を覆うように新たに絶縁膜を形成し、垂直方向を主体とした異方性エッティングにより、新たに形成された該絶縁膜を部分的にエッティングすることで、形成することが出来る。上記異方性エッティングにより、新たに形成された絶縁膜が部分的にエッティングされて、電極509の側面にサイドウォール512が形成される。なお上記異方性エッティングにより、ゲート絶縁膜508も部分的にエッティングしても良い。サイドウォール512を形成するための絶縁膜は、LPCVD法、プラズマCVD法、スパッタリング法等により、珪素膜、酸化珪素膜、酸化窒化珪素膜、窒化酸化珪素膜や、有機樹脂などの有機材料を含む膜を、単層または積層して形成することができる。本実施の形態では、膜厚100nmの酸化珪素膜をプラズマCVD法によって形成する。またエッティングガスとしては、CHF<sub>3</sub>とヘリウムの混合ガスを用いることができる。なお、サイドウォール512を形成する工程は、これらに限定されるものではない。

## 【0215】

次に、図9(B)に示すように、電極509及びサイドウォール512をマスクとして、半導体膜506、半導体膜507に一導電型を付与する不純物元素を添加する。なお、半導体膜506、半導体膜507には、それぞれ先の工程で添加した不純物元素と同じ導電型の不純物元素をより高い濃度で添加する。なお、p型を付与する不純物元素を半導体膜507に添加する際、n型の不純物が添加される半導体膜506はマスク等で覆い、p型を付与する不純物元素の添加が選択的に行われるようとする。逆にn型を付与する不純物元素を半導体膜506に添加する際、p型の不純物が添加される半導体膜507はマスク等で覆い、n型を付与する不純物元素の添加が選択的に行われるようとする。

## 【0216】

上記不純物元素の添加により、半導体膜506に、一対の高濃度不純物領域513と、一対の低濃度不純物領域514と、チャネル形成領域515とが形成される。また、上記不純物元素の添加により、半導体膜507に、一対の高濃度不純物領域516と、一対の低濃度不純物領域517と、チャネル形成領域518とが形成される。高濃度不純物領域513、高濃度不純物領域516はソース領域又はドレイン領域として機能し、低濃度不純物領域514、低濃度不純物領域517はLDD(Lightly Doped Drain)領域として機能する。なお、LDD領域は必ずしも設ける必要はなく、ソース領域又はドレイン領域として機能する不純物領域だけ形成しても良い。或いは、ソース領域とドレイン領域のいずれか一方の側にのみ、LDD領域を形成しても良い。

## 【0217】

なお、シリコンを用いたトランジスタの場合、ソース領域とドレイン領域が、それぞれソース電極、ドレイン電極として機能する。

## 【0218】

半導体膜507上に形成されたサイドウォール512と、半導体膜506上に形成されたサイドウォール512は、キャリアが移動する方向における幅が同じになるように形成しても良いが、該幅が異なるように形成しても良い。 $p$ 型トランジスタとなる半導体膜507上のサイドウォール512の幅は、 $n$ 型トランジスタとなる半導体膜506上のサイドウォール512の幅よりも長くすると良い。なぜならば、 $p$ 型トランジスタにおいてソース領域及びドレイン領域を形成するために注入されるボロンは拡散しやすく、短チャネル効果を誘起しやすいためである。 $p$ 型トランジスタにおいて、サイドウォール512の幅より長くすることで、ソース領域及びドレイン領域に高濃度のボロンを添加することが可能となり、ソース領域及びドレイン領域を低抵抗化することができる。

10

## 【0219】

次に、ソース領域及びドレイン領域をさらに低抵抗化するために、半導体膜506、半導体膜507をシリサイド化することで、シリサイド層を形成しても良い。シリサイド化は、半導体膜に金属を接触させ、加熱処理、GRTA法、LRTA法等により、半導体膜中の珪素と金属とを反応させて行う。シリサイド層としては、コバルトシリサイド若しくはニッケルシリサイドを用いれば良い。半導体膜506、半導体膜507の厚さが薄い場合には、この領域の半導体膜506、半導体膜507の底部までシリサイド反応を進めても良い。シリサイド化に用いる金属の材料として、チタン(Ti)、ニッケル(Ni)、タンゲステン(W)、モリブデン(Mo)、コバルト(Co)、ジルコニウム(Zr)、ハフニウム(Hf)、タンタル(Ta)、バナジウム(V)、ネオジム(Nd)、クロム(Cr)、白金(Pt)、パラジウム(Pd)等を用いることができる。また、レーザ照射やランプなどの光照射によってシリサイドを形成しても良い。

20

## 【0220】

上述した一連の工程により、 $n$ チャネル型トランジスタ520と、 $p$ チャネル型トランジスタ521が形成される。

## 【0221】

図9(B)に示す工程まで終了したら、次いで、 $n$ チャネル型トランジスタ520、 $p$ チャネル型トランジスタ521上に、酸化物半導体を用いたトランジスタを作製する。

30

## 【0222】

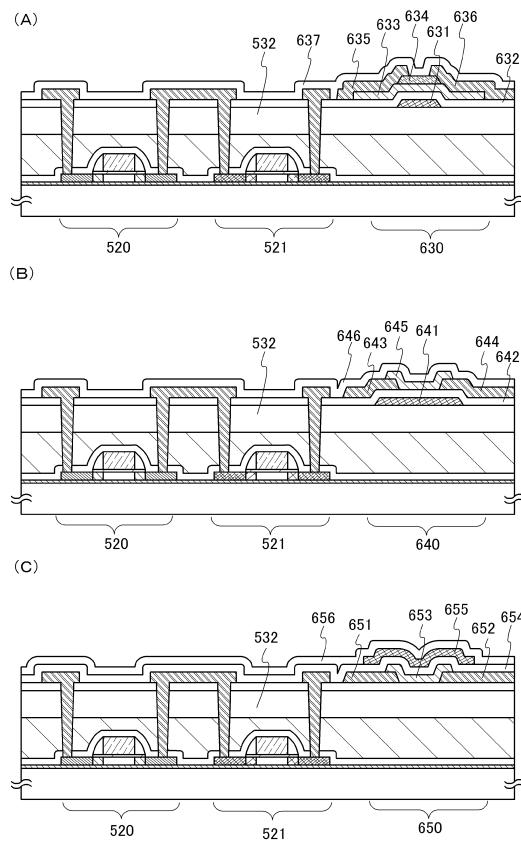

まず、図10(A)に示すように、 $n$ チャネル型トランジスタ520、 $p$ チャネル型トランジスタ521を覆うように絶縁膜530を形成する。絶縁膜530を設けることで、加熱処理の際に電極509の表面が酸化されるのを防ぐことが出来る。具体的に絶縁膜530として、窒化珪素、窒化酸化珪素、酸化窒化珪素、窒化アルミニウム、酸化アルミニウム、酸化珪素などを用いるのが望ましい。本実施の形態では、膜厚50nm程度の酸化窒化珪素膜を、絶縁膜530として用いる。

40

## 【0223】

次に、図10(B)に示すように、 $n$ チャネル型トランジスタ520、 $p$ チャネル型トランジスタ521を覆うように、絶縁膜530上に絶縁膜531、絶縁膜532を形成する。絶縁膜531、絶縁膜532は、後の作製工程における加熱処理の温度に耐えうる材料を用いる。具体的に、絶縁膜531、絶縁膜532は、例えば、酸化珪素、窒化珪素、窒化酸化珪素、酸化窒化珪素、窒化アルミニウム、窒化酸化アルミニウムなどの無機の絶縁膜を用いることができる。

40

## 【0224】

なお、本実施の形態では、絶縁膜530上に絶縁膜531、絶縁膜532を積層しているが、絶縁膜530上に形成する絶縁膜は単層の絶縁膜であっても良いし、3層以上の絶縁膜が積層されていても良い。

## 【0225】

絶縁膜532は、その表面をCMP法などにより平坦化させても良い。

## 【0226】

次いで、図10(B)に示すように、絶縁膜532上に、ゲート電極601、電極602

50

を形成する。

### 【 0 2 2 7 】

ゲート電極 6 0 1、電極 6 0 2 の材料は、モリブデン、チタン、クロム、タンタル、タングステン、ネオジム、スカンジウム等の金属材料、これら金属材料を主成分とする合金材料を用いた導電膜、或いはこれら金属の窒化物を、単層で又は積層で用いることができる。なお、後の工程において行われる加熱処理の温度に耐えうるのであれば、上記金属材料としてアルミニウム、銅を用いることも出来る。アルミニウムまたは銅は、耐熱性や腐食性の問題を回避するために、高融点金属材料と組み合わせて用いると良い。高融点金属材料としては、モリブデン、チタン、クロム、タンタル、タングステン、ネオジム、スカンジウム等を用いることができる。

10

### 【 0 2 2 8 】

例えば、二層の積層構造を有するゲート電極 6 0 1、電極 6 0 2 として、アルミニウム膜上にモリブデン膜が積層された二層の積層構造、銅膜上にモリブデン膜を積層した二層構造、銅膜上に窒化チタン膜若しくは窒化タンタル膜を積層した二層構造、または、窒化チタン膜とモリブデン膜とを積層した二層構造とすることが好ましい。3層の積層構造を有するゲート電極 6 0 1、電極 6 0 2 としては、アルミニウム膜、アルミニウムとシリコンの合金膜、アルミニウムとチタンの合金膜またはアルミニウムとネオジムの合金膜を中間層とし、タングステン膜、窒化タングステン膜、窒化チタン膜またはチタン膜を上下層として積層した構造とすることが好ましい。

20

### 【 0 2 2 9 】

また、ゲート電極 6 0 1、電極 6 0 2 に酸化インジウム、インジウム錫酸化物、酸化インジウム酸化亜鉛合金、酸化亜鉛、酸化亜鉛アルミニウム、酸窒化亜鉛アルミニウム、または酸化亜鉛ガリウム等の透光性を有する酸化物導電膜を用いることもできる。

### 【 0 2 3 0 】

ゲート電極 6 0 1、電極 6 0 2 の膜厚は、10 nm ~ 400 nm、好ましくは100 nm ~ 200 nmとする。本実施の形態では、タングステンターゲットを用いたスパッタ法により150 nmのゲート電極用の導電膜を形成した後、該導電膜をエッチングにより所望の形状に加工（パターニング）することで、ゲート電極 6 0 1、電極 6 0 2 を形成する。なお、形成されたゲート電極の端部がテーパー形状であると、上に積層するゲート絶縁膜の被覆性が向上するため好ましい。なお、レジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

30

### 【 0 2 3 1 】

次いで、図 10 ( C ) に示すように、ゲート電極 6 0 1、電極 6 0 2 上に、ゲート絶縁膜 6 0 3 を形成する。ゲート絶縁膜 6 0 3 は、プラズマ C V D 法又はスパッタリング法等を用いて、酸化珪素膜、窒化珪素膜、酸化窒化珪素膜、窒化酸化珪素膜、酸化アルミニウム膜、窒化アルミニウム膜、酸化窒化アルミニウム膜、窒化酸化アルミニウム膜、酸化ハフニウム膜または酸化タンタル膜を単層で又は積層させて形成することができる。ゲート絶縁膜 6 0 3 は、水分や、水素などの不純物を極力含まないことが望ましい。スパッタリング法により酸化珪素膜を成膜する場合には、ターゲットとしてシリコンターゲット又は石英ターゲットを用い、スパッタガスとして酸素又は、酸素及びアルゴンの混合ガスを用いる。

40

### 【 0 2 3 2 】

不純物を除去することにより i 型化又は実質的に i 型化された酸化物半導体（高純度化された酸化物半導体）は界面準位、界面電荷に対して極めて敏感であるため、高純度化された酸化物半導体とゲート絶縁膜 6 0 3 との界面は重要である。そのため高純度化された酸化物半導体に接するゲート絶縁膜 ( G I ) は、高品質化が要求される。

### 【 0 2 3 3 】

例えば、μ 波 ( 2 . 4 5 G H z ) を用いた高密度プラズマ C V D は、緻密で絶縁耐圧の高い高品質な絶縁膜を形成できるので好ましい。高純度化された酸化物半導体と高品質ゲー

50

ト絶縁膜とが密接することにより、界面準位を低減して界面特性を良好なものとすることができますからである。

#### 【0234】

もちろん、ゲート絶縁膜として良質な絶縁膜を形成できるものであれば、スパッタリング法やプラズマCVD法など他の成膜方法を適用することができる。また、成膜後の熱処理によってゲート絶縁膜の膜質、ゲート絶縁膜と酸化物半導体との界面特性が改善される絶縁膜であっても良い。いずれにしても、ゲート絶縁膜としての膜質が良好であることは勿論のこと、ゲート絶縁膜と酸化物半導体との界面準位密度を低減し、良好な界面を形成できるものであれば良い。

#### 【0235】

バリア性の高い材料を用いた絶縁膜と、窒素の含有比率が低い酸化珪素膜、酸化窒化珪素膜などの絶縁膜とを積層させた構造を有するゲート絶縁膜603を形成しても良い。この場合、酸化珪素膜、酸化窒化珪素膜などの絶縁膜は、バリア性の高い絶縁膜と酸化物半導体膜の間に形成する。バリア性の高い絶縁膜として、例えば窒化珪素膜、窒化酸化珪素膜、窒化アルミニウム膜、または窒化酸化アルミニウム膜などが挙げられる。バリア性の高い絶縁膜を用いることで、水分または水素などの雰囲気中の不純物、或いは基板内に含まれるアルカリ金属、重金属などの不純物が、酸化物半導体膜内、ゲート絶縁膜603内、或いは、酸化物半導体膜と他の絶縁膜の界面とその近傍に入り込むのを防ぐことができる。また、酸化物半導体膜に接するように窒素の含有比率が低い酸化珪素膜、酸化窒化珪素膜などの絶縁膜を形成することで、バリア性の高い絶縁膜が直接酸化物半導体膜に接するのを防ぐことができる。

#### 【0236】

例えば、第1のゲート絶縁膜としてスパッタリング法により膜厚50nm以上200nm以下の窒化珪素膜( $\text{SiN}_y$ ( $y > 0$ ))を形成し、第1のゲート絶縁膜上に第2のゲート絶縁膜として膜厚5nm以上300nm以下の酸化珪素膜( $\text{SiO}_x$ ( $x > 0$ ))を積層して、膜厚100nmのゲート絶縁膜603としても良い。ゲート絶縁膜603の膜厚は、トランジスタに要求される特性によって適宜設定すればよく350nm乃至400nm程度でもよい。

#### 【0237】

本実施の形態では、スパッタ法で形成された膜厚50nmの窒化珪素膜上に、スパッタ法で形成された膜厚100nmの酸化珪素膜を積層させた構造を有する、ゲート絶縁膜603を形成する。

#### 【0238】

なお、ゲート絶縁膜603に水素、水酸基及び水分がなるべく含まれないようにするためには、成膜の前処理として、スパッタリング装置の予備加熱室でゲート電極601、電極602が形成されたベース基板503を予備加熱し、ベース基板503に吸着した水分または水素などの不純物を脱離し排気することが好ましい。なお、予備加熱の温度は、100以上400以下、好ましくは150以上300以下である。なお、予備加熱室に設ける排気手段はクライオポンプが好ましい。なお、この予備加熱の処理は省略することもできる。

#### 【0239】

次いで、ゲート絶縁膜603上に膜厚2nm以上200nm以下、好ましくは膜厚3nm以上50nm以下、さらに好ましくは膜厚3nm以上20nm以下の酸化物半導体膜を形成する。酸化物半導体膜は、酸化物半導体をターゲットとして用い、スパッタ法により成膜する。また、酸化物半導体膜は、希ガス(例えばアルゴン)雰囲気下、酸素雰囲気下、又は希ガス(例えばアルゴン)及び酸素混合雰囲気下においてスパッタ法により形成することができる。

#### 【0240】

なお、酸化物半導体膜をスパッタ法により成膜する前に、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、ゲート絶縁膜603の表面に付着している塵埃を除去

10

20

30

40

50

することが好ましい。逆スパッタとは、ターゲット側に電圧を印加せずに、アルゴン雰囲気下で基板側に R F 電源を用いて電圧を印加して基板近傍にプラズマを形成して表面を改質する方法である。なお、アルゴン雰囲気に代えて窒素、ヘリウムなどを用いてもよい。また、アルゴン雰囲気に酸素、亜酸化窒素などを加えた雰囲気で行ってもよい。また、アルゴン雰囲気に塩素、四フッ化炭素などを加えた雰囲気で行ってもよい。

#### 【 0 2 4 1 】

酸化物半導体膜は、上述したような酸化物半導体を用いることができる。

#### 【 0 2 4 2 】

本実施の形態では、In (インジウム)、Ga (ガリウム)、及びZn (亜鉛)を含む金属酸化物ターゲットを用いたスパッタ法により得られる膜厚 30 nm の In - Ga - Zn - O 系非単結晶膜を、酸化物半導体膜として用いる。上記ターゲットとして、例えば、各金属の組成比が In : Ga : Zn = 1 : 1 : 0 . 5 、 In : Ga : Zn = 1 : 1 : 1 、または In : Ga : Zn = 1 : 1 : 2 である金属酸化物ターゲットを用いることができる。また、SiO<sub>2</sub> を 2 重量 % 以上 10 重量 % 以下含むターゲットを用いて成膜を行ってもよい。また、In、Ga、及びZn を含む金属酸化物ターゲットの充填率は 90 % 以上 100 % 以下、好ましくは 95 % 以上 99 . 9 % である。充填率の高い金属酸化物ターゲットを用いることにより、成膜した酸化物半導体膜は緻密な膜となる。

10

#### 【 0 2 4 3 】

本実施の形態では、減圧状態に保持された処理室内に基板を保持し、処理室内の残留水分を除去しつつ水素及び水分が除去されたスパッタガスを導入し、上記ターゲットを用いてベース基板 503 上に酸化物半導体膜を成膜する。成膜時に、基板温度を 100 以上 600 以下、好ましくは 200 以上 400 以下としても良い。基板を加熱しながら成膜することにより、成膜した酸化物半導体膜に含まれる不純物濃度を低減することができる。また、スパッタリングによる損傷が軽減される。処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて処理室を排気すると、例えば、水素原子、水 (H<sub>2</sub>O) など水素原子を含む化合物（より好ましくは炭素原子を含む化合物も）等が排気されるため、当該処理室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減できる。

20

30

#### 【 0 2 4 4 】

成膜条件の一例としては、基板とターゲットの間との距離を 100 mm、圧力 0 . 6 Pa 、直流 (DC) 電源 0 . 5 kW、酸素（酸素流量比率 100 %）雰囲気下の条件が適用される。なお、パルス直流 (DC) 電源を用いると、成膜時に発生するパーティクルと呼ばれる塵埃が軽減でき、膜厚分布も均一となるために好ましい。

40

#### 【 0 2 4 5 】

なお、酸化物半導体膜に水素、水酸基及び水分がなるべく含まれないようにするために、成膜の前処理として、スパッタリング装置の予備加熱室でゲート絶縁膜 603 までが形成されたベース基板 503 を予備加熱し、ベース基板 503 に吸着した水分または水素などの不純物を脱離し排気することが好ましい。なお、予備加熱の温度は、100 以上 400 以下、好ましくは 150 以上 300 以下である。なお、予備加熱室に設ける排気手段はクライオポンプが好ましい。なお、この予備加熱の処理は省略することもできる。またこの予備加熱は、絶縁膜 612 の成膜前に、ソース電極 607 及びドレイン電極 608 、配線 609 ~ 配線 611 まで形成したベース基板 503 にも同様に行ってもよい。

#### 【 0 2 4 6 】

スパッタリング法にはスパッタ用電源に高周波電源を用いる R F スパッタリング法と、DC スパッタリング法があり、さらにパルス的にバイアスを与えるパルス DC スパッタリング法もある。R F スパッタリング法は主に絶縁膜を成膜する場合に用いられ、DC スパッタリング法は主に金属膜を成膜する場合に用いられる。

#### 【 0 2 4 7 】

50

また、材料の異なるターゲットを複数設置できる多元スパッタ装置もある。多元スパッタ装置は、同一チャンバーで異なる材料膜を積層成膜することも、同一チャンバーで複数種類の材料を同時に放電させて成膜することもできる。

#### 【 0 2 4 8 】

また、チャンバー内部に磁石機構を備えたマグнетロンスパッタリング法を用いるスパッタ装置や、グロー放電を使わずマイクロ波を用いて発生させたプラズマを用いる E C R スパッタリング法を用いるスパッタ装置がある。

#### 【 0 2 4 9 】

また、スパッタリング法を用いる成膜方法として、成膜中にターゲット物質とスパッタガス成分とを化学反応させてそれらの化合物薄膜を形成するリアクティブスパッタリング法や、成膜中に基板にも電圧をかけるバイアススパッタリング法もある。

10

#### 【 0 2 5 0 】

ゲート絶縁膜 6 0 3 及び酸化物半導体膜を大気に触れさせることなく連続的に形成してもよい。大気に触れさせることなく連続成膜することで、界面が、水やハイドロカーボンなどの、大気成分や大気中に浮遊する不純物元素に汚染されることなく各積層界面を形成することができるので、トランジスタ特性のばらつきを低減することができる。

#### 【 0 2 5 1 】

次いで、図 1 0 ( C ) に示すように、酸化物半導体膜をエッチングなどにより所望の形状に加工（パターニング）し、ゲート絶縁膜 6 0 3 上のゲート電極 6 0 1 と重なる位置に、島状の酸化物半導体膜 6 0 5 を形成する。

20

#### 【 0 2 5 2 】

島状の酸化物半導体膜 6 0 5 を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

#### 【 0 2 5 3 】

なお、島状の酸化物半導体膜 6 0 5 を形成するためのエッチングは、ドライエッティングでもウェットエッティングでもよく、両方を用いてもよい。ドライエッティングに用いるエッティングガスとしては、塩素を含むガス（塩素系ガス、例えば塩素 ( C l 2 ) 、塩化硼素 ( B C l 3 ) 、塩化珪素 ( S i C l 4 ) 、四塩化炭素 ( C C l 4 ) など）が好ましい。また、フッ素を含むガス（フッ素系ガス、例えば四弗化炭素 ( C F 4 ) 、六弗化硫黄 ( S F 6 ) 、三弗化窒素 ( N F 3 ) 、トリフルオロメタン ( C H F 3 ) など）、臭化水素 ( H B r ) 、酸素 ( O 2 ) 、これらのガスにヘリウム ( H e ) やアルゴン ( A r ) などの希ガスを添加したガス、などを用いることができる。

30

#### 【 0 2 5 4 】

ドライエッティング法としては、平行平板型 R I E ( R e a c t i v e I o n E t c h i n g ) 法や、 I C P ( I n d u c t i v e l y C o u p l e d P l a s m a : 誘導結合型プラズマ ) エッティング法を用いることができる。所望の加工形状にエッティングできるように、エッティング条件（コイル型の電極に印加される電力量、基板側の電極に印加される電力量、基板側の電極温度等）を適宜調節する。

40

#### 【 0 2 5 5 】

ウェットエッティングに用いるエッティング液としては、磷酸と酢酸と硝酸を混ぜた溶液、アンモニア過水（31重量%過酸化水素水：28重量%アンモニア水：水 = 5 : 2 : 2）などを用いることができる。また、 I T O - 0 7 N （関東化学社製）を用いてもよい。また、ウェットエッティング後のエッティング液はエッティングされた材料とともに洗浄によって除去される。その除去された材料を含むエッティング液の廃液を精製し、含まれる材料を再利用してもよい。当該エッティング後の廃液から酸化物半導体膜に含まれるインジウム等の材料を回収して再利用することにより、資源を有効活用し低コスト化を図ることができる。

#### 【 0 2 5 6 】

なお、次工程の導電膜を形成する前に逆スパッタを行い、島状の酸化物半導体膜 6 0 5 及びゲート絶縁膜 6 0 3 の表面に付着しているレジスト残渣などを除去することが好ましい

50

。

### 【 0 2 5 7 】

次いで、減圧雰囲気下、窒素や希ガスなどの不活性ガス雰囲気下、酸素ガス雰囲気下、又は超乾燥エア（C R D S（キャビティリングダウンレーザー分光法）方式の露点計を用いて測定した場合の水分量が 2 0 p p m（露点換算で - 5 5 ）以下、好ましくは 1 p p m 以下、好ましくは 1 0 p p b 以下の空気）雰囲気下において、酸化物半導体膜 6 0 5 に加熱処理を施す。酸化物半導体膜 6 0 5 に加熱処理を施すことによって、酸化物半導体膜 6 0 5 中の水分または水素を脱離させることができる。具体的には、3 0 0 以上 8 5 0 以下（若しくはガラス基板の歪点以下の温度）、好ましくは 5 5 0 以上 7 5 0 以下で加熱処理を行えば良い。例えば、6 0 0 、3 分間以上 6 分間以下程度で行えればよい。加熱処理には R T A 法を用いれば、短時間に脱水化または脱水素化が行えるため、ガラス基板の歪点を超える温度でも処理することができる。或いは、基板温度が 4 5 0 に達した状態で、1 時間程度、加熱処理を行うようにしても良い。

10

### 【 0 2 5 8 】

本実施の形態では、加熱処理装置の一つである電気炉を用い、酸化物半導体膜 6 0 5 に対して、窒素雰囲気下において、基板温度が 6 0 0 に達した状態で 6 分間、加熱処理を行った後、大気に触れることなく、水分または水素の再混入を防ぐ。

20

### 【 0 2 5 9 】

なお、加熱処理装置は電気炉に限らず、抵抗発熱体などの発熱体からの熱伝導または熱輻射によって、被処理物を加熱する装置を備えていてもよい。例えば、G R T A ( G a s R a p i d T h e r m a l A n n e a l ) 装置、L R T A ( L a m p R a p i d T h e r m a l A n n e a l ) 装置等の R T A ( R a p i d T h e r m a l A n n e a l ) 装置を用いることができる。L R T A 装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光（電磁波）の輻射により、被処理物を加熱する装置である。G R T A 装置は、高温のガスを用いて加熱処理を行う装置である。気体には、アルゴンなどの希ガス、または窒素のような、加熱処理によって被処理物と反応しない不活性気体が用いられる。

20

### 【 0 2 6 0 】

例えば、加熱処理として、6 5 0 ~ 7 0 0 の高温に加熱した不活性ガス中に基板を移動させて入れ、数分間加熱した後、基板を移動させて高温に加熱した不活性ガス中から出す G R T A を行ってもよい。G R T A を用いると短時間での高温加熱処理が可能となる。

30

### 【 0 2 6 1 】

なお、加熱処理においては、窒素、またはヘリウム、ネオン、アルゴン等の希ガスに、水分または水素などが含まれないことが好ましい。または、加熱処理装置に導入する窒素、またはヘリウム、ネオン、アルゴン等の希ガスの純度を、6 N ( 9 9 . 9 9 9 9 % ) 以上、好ましくは 7 N ( 9 9 . 9 9 9 9 % ) 以上、（即ち不純物濃度を 1 p p m 以下、好ましくは 0 . 1 p p m 以下）とすることが好ましい。

30

### 【 0 2 6 2 】

水分または水素などの不純物が酸化物半導体に添加されていると、ゲートバイアス・熱ストレス試験（B T 試験、試験条件は例えば、8 5 、 $2 \times 1 0^6$  V / c m、1 2 時間）において、不純物と酸化物半導体の主成分との結合手が、強電界（B : バイアス）と高温（T : 温度）により切断され、生成された未結合手がしきい値電圧（V t h）のドリフトを誘発することとなる。しかし、上述したように、ゲート絶縁膜と酸化物半導体膜との界面特性を良好にし、なおかつ、酸化物半導体膜中の不純物、特に水分または水素等を極力除去することにより、B T 試験に対しても安定なトランジスタが得られる。

40

### 【 0 2 6 3 】

以上の工程により酸化物半導体膜 6 0 5 中の水素の濃度を低減し、高純度化することができる。それにより酸化物半導体膜の安定化を図ることができる。また、ガラス転移温度以下の加熱処理で、キャリア密度が極端に少なく、バンドギャップの広い酸化物半導体膜を

50

形成することができる。このため、大面積基板を用いてトランジスタを作製することができるため、量産性を高めることができる。また、当該水素濃度が低減され高純度化された酸化物半導体膜を用いることで、耐圧性が高く、ショートチャネル効果が低く、オンオフ比の高いトランジスタを作製することができる。

#### 【0264】

なお、酸化物半導体膜を加熱する場合、酸化物半導体膜の材料や加熱条件にもよるが、その上表面に板状結晶が形成されることがある。板状結晶は、酸化物半導体膜の表面に対して略垂直にc軸配向した単結晶体であることが好ましい。また、単結晶体でなくとも、各結晶が、酸化物半導体膜の表面に対して略垂直にc軸配向した多結晶体であることが好ましい。そして、上記多結晶体は、c軸配向していることに加えて、各結晶のa b面が一致するか、a軸、或いは、b軸が一致していることが好ましい。なお、酸化物半導体膜の下地表面に凹凸がある場合、板状結晶は多結晶体となる。したがって、下地表面は可能な限り平坦であることが望まれる。

#### 【0265】

次に、絶縁膜530、絶縁膜531、絶縁膜532、ゲート絶縁膜603を部分的にエッチングすることで、nチャネル型トランジスタ520が有する高濃度不純物領域513と、pチャネル型トランジスタ521が有する高濃度不純物領域516と、電極602に達するコンタクトホールを形成する。そして、酸化物半導体膜605上に、ソース電極またはドレイン電極（これと同じ層で形成される配線を含む）として用いる導電膜を、スパッタ法や真空蒸着法で形成したあと、エッチング等により該導電膜をパターニングすることで、図11(A)に示すように、酸化物半導体膜605上のソース電極607及びドレイン電極608と、電極602及び高濃度不純物領域513に接する配線609と、高濃度不純物領域516に接する配線610と、高濃度不純物領域513及び高濃度不純物領域516に接する配線611とを、それぞれ形成する。

#### 【0266】

ソース電極及びドレイン電極（これと同じ層で形成される配線を含む）となる導電膜の材料としては、Al、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜等が挙げられる。また、Al、Cuなどの金属膜の下側もしくは上側にCr、Ta、Ti、Mo、Wなどの高融点金属膜を積層させた構成としても良い。また、Si、Ti、Ta、W、Mo、Cr、Nd、Sc、YなどAl膜に生ずるヒロックやウィスカーの発生を防止する元素が添加されているAl材料を用いることで耐熱性を向上させることができるとなる。

#### 【0267】

また、導電膜は、単層構造でも、2層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する2層構造、Ti膜と、そのTi膜上に重ねてアルミニウム膜を積層し、さらにその上にTi膜を成膜する3層構造などが挙げられる。

#### 【0268】

また、ソース電極及びドレイン電極（これと同じ層で形成される配線を含む）となる導電膜としては導電性の金属酸化物で形成しても良い。導電性の金属酸化物としては酸化インジウム(Indium Oxide)、酸化スズ(Sodium Oxide)、酸化亜鉛(Zinc Oxide)、インジウム錫酸化物(Indium Oxide-Sodium Oxide、ITOと略記する)、酸化インジウム酸化亜鉛合金(Indium Zinc Oxide)または前記金属酸化物材料にシリコン若しくは酸化シリコンを含ませたものを用いることができる。

#### 【0269】

導電膜形成後に加熱処理を行う場合には、この加熱処理に耐える耐熱性を導電膜に持たせることが好ましい。

#### 【0270】

なお、導電膜のエッチングの際に、酸化物半導体膜605がなるべく除去されないようにそれぞれの材料及びエッチング条件を適宜調節する。エッチング条件によっては、島状の

酸化物半導体膜 605 の露出した部分が一部エッティングされることで、溝部（凹部）が形成されることもある。

#### 【0271】

本実施の形態では、導電膜にチタン膜を用いたので、アンモニア過水（31重量%過酸化水素水：28重量%アンモニア水：水=5:2:2）を用いて、選択的に導電膜をウェットエッティングすることができるが、酸化物半導体膜605も一部エッティングされることがある。或いは、塩素（Cl<sub>2</sub>）、塩化硼素（BCl<sub>3</sub>）などを含むガスを用いて、導電膜をドライエッティングしても良い。

#### 【0272】

なお、フォトリソグラフィ工程で用いるフォトマスク数及び工程数を削減するため、透過した光に多段階の強度をもたせる多階調マスクによって形成されたレジストマスクを用いてエッティング工程を行ってもよい。多階調マスクを用いて形成したレジストマスクは複数の膜厚を有する形状となり、エッティングを行うことでさらに形状を変形することができるため、異なるパターンに加工する複数のエッティング工程に用いることができる。よって、一枚の多階調マスクによって、少なくとも二種類以上の異なるパターンに対応するレジストマスクを形成することができる。よって露光マスク数を削減することができ、対応するフォトリソグラフィ工程も削減できるため、工程の簡略化が可能となる。

#### 【0273】

次いで、N<sub>2</sub>O、N<sub>2</sub>、またはArなどのガスを用いたプラズマ処理を行う。このプラズマ処理によって露出している酸化物半導体膜の表面に付着した吸着水などを除去する。また、酸素とアルゴンの混合ガスを用いてプラズマ処理を行ってもよい。

#### 【0274】

なお、プラズマ処理を行った後、図11(B)に示すように、ソース電極607及びドレン電極608と、配線609～配線611と、酸化物半導体膜605とを覆うように、絶縁膜612を形成する。絶縁膜612は、水分や、水素などの不純物を極力含まないことが望ましく、単層の絶縁膜であっても良いし、積層された複数の絶縁膜で構成されても良い。絶縁膜612に水素が含まれると、その水素が酸化物半導体膜へ侵入し、又は水素が酸化物半導体膜中の酸素を引き抜き、酸化物半導体膜のバックチャネル部が低抵抗化（n型化）してしまい、寄生チャネルが形成されるおそれがある。よって、絶縁膜612はできるだけ水素を含まない膜になるように、成膜方法に水素を用いないことが重要である。上記絶縁膜612には、バリア性の高い材料を用いるのが望ましい。例えば、バリア性の高い絶縁膜として、窒化珪素膜、窒化酸化珪素膜、窒化アルミニウム膜、または窒化酸化アルミニウム膜などを用いることができる。複数の積層された絶縁膜を用いる場合、窒素の含有比率が低い酸化珪素膜、酸化窒化珪素膜などの絶縁膜を、上記バリア性の高い絶縁膜よりも、酸化物半導体膜605に近い側に形成する。そして、窒素の含有比率が低い絶縁膜を間に挟んで、ソース電極607及びドレン電極608及び酸化物半導体膜605と重なるように、バリア性の高い絶縁膜を形成する。バリア性の高い絶縁膜を用いることで、酸化物半導体膜605内、ゲート絶縁膜603内、或いは、酸化物半導体膜605と他の絶縁膜の界面とその近傍に、水分または水素などの不純物が入り込むのを防ぐことができる。また、酸化物半導体膜605に接するように窒素の比率が低い酸化珪素膜、酸化窒化珪素膜などの絶縁膜を形成することで、バリア性の高い材料を用いた絶縁膜が直接酸化物半導体膜605に接するのを防ぐことができる。

#### 【0275】

本実施の形態では、スパッタ法で形成された膜厚200nmの酸化珪素膜上に、スパッタ法で形成された膜厚100nmの窒化珪素膜を積層させた構造を有する、絶縁膜612を形成する。成膜時の基板温度は、室温以上300℃以下とすればよく、本実施の形態では100℃とする。

#### 【0276】