(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2015-0016508

(43) 공개일자 2015년02월12일

- (51) 국제특허분류(Int. Cl.)

*G03F 7/20* (2006.01) *H01L 21/027* (2006.01)

- (21) 출원번호 10-2014-7032173

- (22) 출원일자(국제) 2013년03월19일

심사청구일자 없음

- (85) 번역문제출일자 2014년11월17일

- (86) 국제출원번호 PCT/EP2013/055597

- (87) 국제공개번호 WO 2013/156236

국제공개일자 2013년10월24일

- (30) 우선권주장

61/635,754 2012년04월19일 미국(US)

- (71) 출원인

에이에스엠엘 네델란즈 비.브이.

네덜란드 5500 아하 벨트호벤 피.오.박스 324

- (72) 발명자

라파레, 레이몬드

네덜란드 엔엘-5607 요트에스 헬몬트 미텔레르세

르프 4

드지음키나, 니나

네덜란드 엔엘-5658 베엔 아인트호벤 잔드래프 48

(뒷면에 계속)

- (74) 대리인

특허법인(유)화우

전체 청구항 수 : 총 15 항

(54) 발명의 명칭 기판 홀더, 리소그래피 장치 및 디바이스 제조 방법

**(57) 요 약**

리소그래피 장치에서 사용하기 위한 기판 홀더가 제공되며, 상기 기판 홀더는, 표면(107)을 갖는 본체(100); 상기 표면으로부터 돌출되고, 기판을 지지하기 위한 단부면들을 갖는 복수의 벼얼(106); 및 전기 구성요소를 형성하는 상기 본체의 표면의 박막 스택(200)을 포함하고, 상기 박막 스택은 상기 스택의 평면 전반에 걸쳐 실질적으로 균일하게 전하를 분포시키도록 구성되는 전도성 층(108)을 포함하며, 상기 평면에 전도성 층이 위치된다.

**대 표 도** - 도13

(72) 발명자

**카라데, 요게시**

네델란드 엔엘-5611 계요트 아인트호벤 케르크스트

라트 6-아

**로덴버그, 엘리자베스**

네델란드 엔엘-5591 애베 해제 세인트 니카시우스

스트라트 39

---

**싱, 하미트**

미국 캘리포니아 94539 프리몬트 안자 스트리트

339

## 특허청구의 범위

### 청구항 1

리소그래피 장치에서 사용하기 위한 기판 홀더에 있어서,

표면을 갖는 본체(main body);

상기 표면으로부터 돌출되고, 기판을 지지하기 위한 단부면들을 갖는 복수의 벼얼(burls); 및

전기 구성요소를 형성하는 상기 본체의 표면의 박막 스택을 포함하고, 상기 박막 스택은 상기 스택의 평면 전반에 걸쳐 실질적으로 균일하게 전하를 분포시키도록 구성되는 전도성 층을 포함하며, 상기 평면에 상기 전도성 층이 위치되는 기판 홀더.

### 청구항 2

제 1 항에 있어서,

상기 전도성 층은, 평면에서(in plan), 패터닝되지 않는 기판 홀더.

### 청구항 3

제 1 항 또는 제 2 항에 있어서,

상기 전도성 층은, 평면에서, 상기 스택의 실질적으로 전체 영역에 걸쳐 연장되는 기판 홀더.

### 청구항 4

제 1 항 내지 제 3 항 중 어느 한 항에 있어서,

상기 전도성 층은 금속 층인 기판 홀더.

### 청구항 5

제 1 항 내지 제 3 항 중 어느 한 항에 있어서,

상기 전도성 층은 상기 본체 표면에 형성되는 평탄화 층인 기판 홀더.

### 청구항 6

제 1 항 내지 제 4 항 중 어느 한 항에 있어서,

상기 박막 스택은 상기 본체 표면에 형성되는 평탄화 층을 포함하는 기판 홀더.

### 청구항 7

제 1 항 내지 제 6 항 중 어느 한 항에 있어서,

상기 전도성 층에 인접한 적어도 하나의 층은 절연 층인 기판 홀더.

### 청구항 8

제 1 항 내지 제 7 항 중 어느 한 항에 있어서,

상기 전도성 층은 상기 본체에 전기적으로 연결되는 기판 홀더.

### 청구항 9

제 1 항 내지 제 8 항 중 어느 한 항에 있어서,

상기 전도성 층은 플로팅 전극(floating electrode)인 기판 홀더.

### 청구항 10

제 1 항 내지 제 8 항 중 어느 한 항에 있어서,

상기 박막 스택은 전극 충인 추가 전도성 층을 더 포함하는 기판 홀더.

### 청구항 11

제 10 항에 있어서,

상기 전극 층 및 전도성 층은 절연 층에 의해 분리되는 기판 홀더.

### 청구항 12

제 11 항에 있어서,

전극은, 사용 시, 정전기 클램프의 전극인 기판 홀더.

### 청구항 13

리소그래피 장치에 있어서,

패터닝 디바이스를 지지하도록 구성되는 지지 구조체;

기판 상으로 상기 패터닝 디바이스에 의해 패터닝된 빔을 투영하도록 배치된 투영 시스템; 및

상기 기판을 유지하도록 배치된 기판 홀더를 포함하고, 상기 기판 홀더는 제 1 항 내지 제 12 항 중 어느 한 항에 따르는 리소그래피 장치.

### 청구항 14

리소그래피 장치를 이용하는 디바이스 제조 방법에 있어서,

기판 홀더 내에 또는 기판 홀더 상에 기판을 유지하면서, 상기 기판 상으로 패터닝된 디바이스에 의해 패터닝된 빔을 투영하는 단계를 포함하고, 상기 기판 홀더는:

표면을 갖는 본체;

상기 표면으로부터 돌출되고, 기판을 지지하기 위한 단부면들을 갖는 복수의 벼얼; 및

전기 구성요소를 형성하는 상기 본체의 표면의 박막 스택을 포함하고, 상기 박막 스택은 상기 스택의 평면 전반에 걸쳐 실질적으로 균일하게 전하를 분포시키도록 구성되는 전도성 층을 포함하며, 상기 평면에 상기 전도성 층이 위치되는 디바이스 제조 방법.

### 청구항 15

리소그래피 장치에서 사용하기 위한 기판 홀더에 있어서,

표면을 갖는 본체;

상기 표면으로부터 돌출되고, 기판을 지지하기 위한 단부면들을 갖는 복수의 벼얼; 및

전기 구성요소를 형성하는 상기 본체의 표면의 박막 스택을 포함하고, 상기 박막 스택은, 평면에서, 상기 스택의 실질적으로 전체 영역에 걸쳐 연장되는 전도성 층을 포함하는 기판 홀더.

## 명세서

### 기술분야

[0001] 본 출원은 2012년 4월 19일에 출원된 미국 가출원 61/635.754의 이익을 주장하며, 이는 본 명세서에서 전문이 인용 참조된다.

[0002] 본 발명은 기판 홀더, 리소그래피 장치 및 디바이스 제조 방법에 관한 것이다.

### 배경기술

[0003] 리소그래피 장치는 기판 상에, 통상적으로는 기판의 타겟부 상에 원하는 패턴을 적용시키는 기계이다. 리소그

래피 장치는, 예를 들어 접적 회로(IC)의 제조시에 사용될 수 있다. 그 경우, 대안적으로 마스크 또는 레티를 이라 칭하는 패터닝 디바이스가 IC의 개별층에 형성될 회로 패턴을 생성하기 위해 사용될 수 있다. 이 패턴은 기판(예컨대, 실리콘 웨이퍼)의 (예를 들어, 다이의 일부분, 한 개 또는 수 개의 다이들을 포함하는) 타겟부 상으로 전사(transfer)될 수 있다. 패턴의 전사는, 통상적으로 기판에 제공된 방사선-감응재(레이저스트) 층 상으로의 이미징(imaging)을 통해 수행된다. 일반적으로, 단일 기판은 연속하여 패터닝되는 인접한 타겟부들의 네트워크를 포함할 것이다. 공지된 리소그래피 장치는, 한번에 타겟부 상으로 전체 패턴을 노광함으로써 각각의 타겟부가 조사되는(irradiated), 소위 스텝퍼, 및 방사선 빔을 통해 주어진 방향("스캐닝"- 방향)으로 패턴을 스캐닝하는 한편, 이 방향과 평행한 방향(같은 방향으로 평행한 방향) 또는 역-평행 방향(반대 방향으로 평행한 방향)으로 기판을 동기적으로 스캐닝함으로써 각각의 타겟부가 조사되는, 소위 스캐너를 포함한다. 또한, 기판 상에 패턴을 임프린트(imprint)함으로써, 패터닝 디바이스로부터 기판으로 패턴을 전사할 수도 있다.

**[0004]** 리소그래피 투영 장치에서 투영 시스템의 최종 요소와 기판 사이의 공간을 채우기 위해 비교적 높은 굴절률을 갖는 액체(예를 들어, 물)에 기판을 침지(immerse)시키는 것이 제안되었다. 일 실시예에서, 액체는 중류수이지만, 다른 액체가 사용될 수 있다. 본 발명의 일 실시예는 액체에 관련하여 설명될 것이다. 하지만, 또 다른 유체, 특히 습식 유체(wetting fluid), 비압축성 유체(incompressible fluid), 및/또는 공기보다 높은 굴절률을 갖고, 바람직하게는 물보다 높은 굴절률을 갖는 유체가 적합할 수 있다. 가스들을 배제시킨 유체들이 특히 바람직하다. 이것의 핵심은, 노광 방사선이 액체 내에서 더 짧은 과장을 가지기 때문에 더 작은 피쳐들을 이미징할 수 있다는 것에 있다[또한, 액체의 효과는 시스템의 유효 개구수(NA)를 증가시키고 초점심도(depth of focus)를 증가시키는 것으로도 간주될 수 있다]. 고체 입자들(예를 들어, 석영)이 부유되어 있는 물, 또는 나노-입자 부유물(예를 들어, 10 nm 이하의 치수를 갖는 입자들)을 갖는 액체를 포함하는 다른 침지 액체들이 제안되었다. 부유된 입자들은 입자들이 부유된 액체와 유사하거나 동일한 굴절률을 가질 수 있거나 또는 가질 수 없다. 적합할 수 있는 다른 액체로는, 탄화수소, 예컨대 방향족, 불화탄화수소(fluorohydrocarbon), 및/또는 수용액이 있다.

### 발명의 내용

#### 해결하려는 과제

**[0005]** 종래의 리소그래피 장치에서는, 노광될 기판이 기판 홀더에 의해 지지될 수 있으며, 기판 홀더는 기판 테이블에 의해 지지된다. 기판 홀더는, 흔히 크기 및 형상이 기판에 대응하는 평평한 강성의 디스크이다(하지만, 상이 크기 또는 형상을 가질 수도 있음). 이는 적어도 일 측으로부터 돌출되는 벼얼(burrs) 또는 펌플(pimples)이라고 칭해지는 돌출부들의 어레이를 갖는다. 일 실시예에서, 기판 홀더는 2 개의 대향 측들에 돌출부들의 어레이를 갖는다. 이 경우, 기판 홀더가 기판 테이블에 배치될 때, 기판 홀더의 본체는 기판 테이블 위로 약간의 간격을 두고 유지되는 한편, 기판 홀더 일 측 상의 벼얼의 단부들은 기판 테이블의 표면에 놓인다. 이와 유사하게, 기판이 기판 홀더의 반대쪽 상의 벼얼의 최상부에 놓일 때, 기판은 기판 홀더의 본체로부터 이격된다. 이의 한 가지 목적은, 기판 테이블 또는 기판 홀더에 존재할 수 있는 입자[즉, 먼지 입자와 같은 오염 입자]가 기판 홀더 또는 기판을 왜곡시키는 것을 방지하도록 돋기 위함이다. 벼얼의 전체 표면적은 기판 또는 기판 홀더의 전체 면적의 극히 일부이기 때문에, 여하한의 입자가 벼얼들 사이에 놓이게 될 가능성이 매우 높으며, 그 입자의 존재는 영향을 주지 않을 것이다.

**[0006]** 고-스루풋(high-throughput) 리소그래피 장치의 이용 시 기판이 겪게 되는 높은 가속도로 인해, 단순히 기판을 기판 홀더의 벼얼 상에 놓는 것만으로는 충분하지 않다. 기판은 제자리에 클램핑된다. 기판을 제자리에 클램핑하는 두 가지 방법 - 진공 클램핑 및 정전 클램핑이 알려져 있다. 진공 클램핑에서는, 기판 홀더와 기판 사이 그리고 선택적으로 기판 테이블과 기판 홀더 사이의 공간이 부분적으로 배기(evacuate)되어, 기판은 그 위의 가스 또는 액체의 더 높은 압력에 의해 제자리에 유지되게 된다. 하지만, 진공 클램핑은, 예를 들어 극자외(EUV) 방사선 리소그래피에 대하여, 기판 또는 기판 홀더 부근의 환경 및/또는 빔 경로가 낮은 또는 매우 낮은 압력으로 유지되는 경우에는 실현가능하지 않을 수 있다. 이 경우, 기판을 클램핑 하기 위해 기판(또는 기판 홀더)에 걸쳐 충분히 큰 압력 차를 조성하는 것이 가능하지 않을 수 있다. 그러므로, 이러한 상황에서(또는 다른 상황들에서) 정전기 클램핑이 사용될 수 있다. 정전기 클램핑에서는, 기판 테이블 및/또는 기판 홀더에 제공되는 전극이 높은 전위, 예를 들어 10 내지 5000 V로 상승되며, 정전기력이 기판을 끌어당긴다. 따라서, 벼얼의 또 다른 목적은, 정전기 클램핑을 가능하게 하기 위해 기판, 기판 홀더 및 기판 테이블을 이격시키는 것이다.

**[0007]** 기판 표면에 걸친 온도 제어는, 특히 액체(예컨대, 물) 증발 영향으로 인한 온도 변동에 민감한 침지 시스템들

에서 중요하다. 액체의 증발은 기판으로부터 열을 빼앗아 온도 변동을 야기한다. 온도 변동은 기판에 열 응력을 유발할 수 있고, 이는 결국 오버레이 오차에 기여할 수 있다. 온도 제어의 정확성을 개선하기 위해서는, 능동 가열(active heating)과 조합된 온도의 실시간 국부적 측정이 요구된다. 이러한 측정 및 가열 시스템은 시스템 내로, 예를 들어 기판 홀더(즉, 기판을 직접 지지하는 물체) 및/또는 기판 테이블(기판 스테이지의 거울 블록, 즉 기판 홀더를 지지하고 기판 홀더를 둘러싸는 상부 표면을 제공하는 물체)에 통합된다. 박막 스택이 구조체를 만드는데 이용될 수 있고, 이는 구조체를 측정 및 가열할 수 있으며, 기판 홀더 및/또는 테이블에 통합시키기 위한 기회를 제공한다.

[0008] 예를 들어, 1 이상의 박막 구성요소와 같은 1 이상의 전자 또는 전기 구성요소들이 형성되는 기판 테이블 또는 기판 홀더를 제공하는 것이 바람직하다.

### 과제의 해결 수단

[0009] 본 발명의 일 실시형태에 따르면, 리소그래피 장치에서 사용하기 위한 기판 홀더가 제공되며, 상기 기판 홀더는, 표면을 갖는 본체; 상기 표면으로부터 돌출되고, 기판을 지지하기 위한 단부면들을 갖는 복수의 베얼; 및 전기 구성요소를 형성하는 상기 본체의 표면의 박막 스택을 포함하고, 상기 박막 스택은 상기 스택의 평면 전반에 걸쳐 실질적으로 균일하게 전하를 분포시키도록 구성되는 전도성 층을 포함하며, 상기 평면에 상기 전도성 층이 위치된다.

[0010] 본 발명의 일 실시형태에 따르면, 리소그래피 장치를 이용하는 디바이스 제조 방법이 제공되며, 상기 방법은 기판 홀더 내에 또는 기판 홀더 상에 기판을 유지하면서, 상기 기판 상으로 패터닝된 디바이스에 의해 패터닝된 빔을 투영하는 단계를 포함하고, 상기 기판 홀더는, 표면을 갖는 본체; 상기 표면으로부터 돌출되고, 기판을 지지하기 위한 단부면들을 갖는 복수의 베얼; 및 전기 구성요소를 형성하는 상기 본체의 표면의 박막 스택을 포함하고, 상기 박막 스택은 상기 스택의 평면 전반에 걸쳐 실질적으로 균일하게 전하를 분포시키도록 구성되는 전도성 층을 포함하며, 상기 평면에 상기 전도성 층이 위치된다.

[0011] 본 발명의 일 실시형태에 따르면, 리소그래피 장치에서 사용하기 위한 기판 홀더가 제공되며, 상기 기판 홀더는, 표면을 갖는 본체; 상기 표면으로부터 돌출되고, 기판을 지지하기 위한 단부면들을 갖는 복수의 베얼; 및 전기 구성요소를 형성하는 상기 본체의 표면의 박막 스택을 포함하고, 상기 박막 스택은 평면에서(in plan) 상기 스택의 실질적으로 전체 영역에 걸쳐 연장되는 전도성 층을 포함한다.

### 도면의 간단한 설명

[0012] 이하, 대응하는 참조 부호들이 대응하는 부분들을 나타내는 첨부된 개략적인 도면들을 참조하여, 단지 예시의 방식으로만 본 발명의 실시예들을 설명할 것이다:

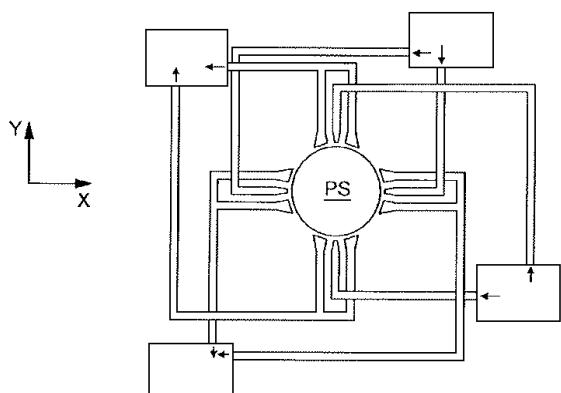

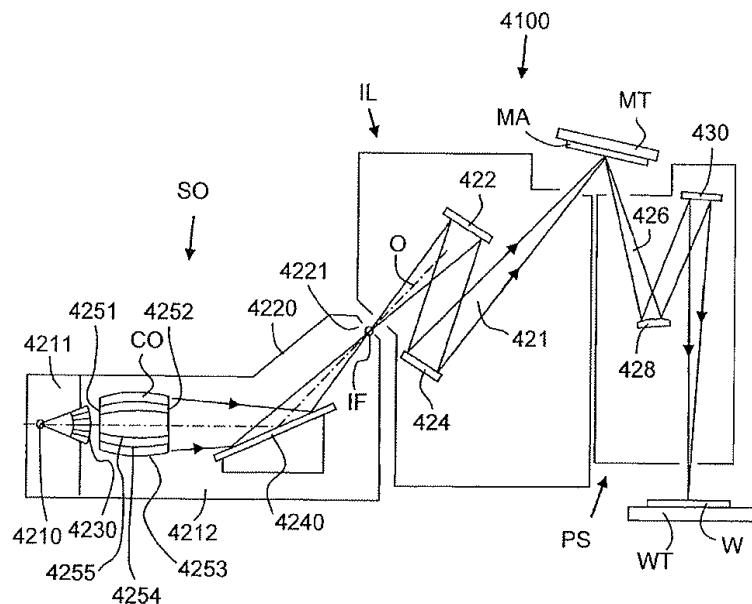

- 도 1은 본 발명의 일 실시예에 따른 리소그래피 장치를 도시하는 도면;

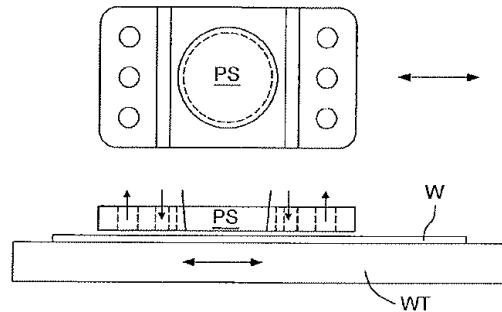

- 도 2 및 도 3은 리소그래피 투영 장치에서 사용하기 위한 액체 공급 시스템을 도시하는 도면;

- 도 4는 리소그래피 투영 장치에 사용하기 위한 또 다른 액체 공급 시스템을 도시하는 도면;

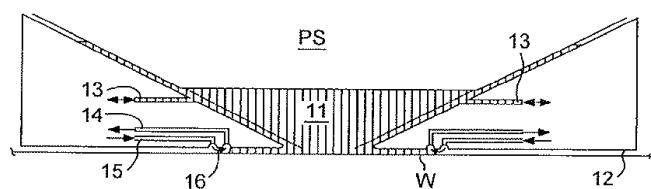

- 도 5는 침지 액체 공급 시스템으로서 본 발명의 일 실시예에서 사용될 수 있는 방벽 부재(barrier member)의 단면도;

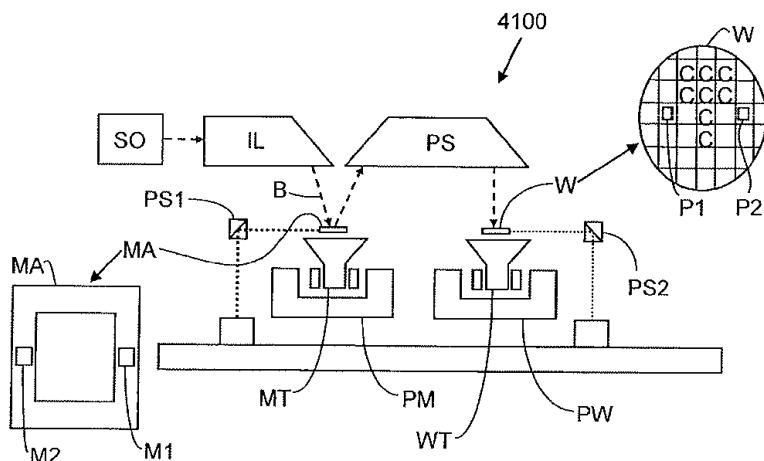

- 도 6은 본 발명의 일 실시예에 따른 리소그래피 장치를 도시하는 도면;

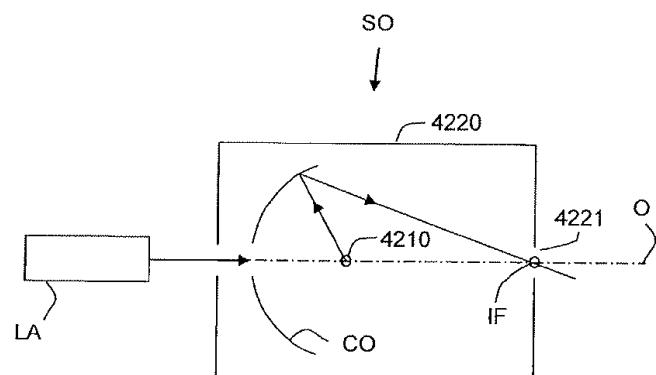

- 도 7은 장치(4100)의 상세도;

- 도 8은 도 6 및 도 7의 장치의 소스 컬렉터 장치(SO)의 상세도;

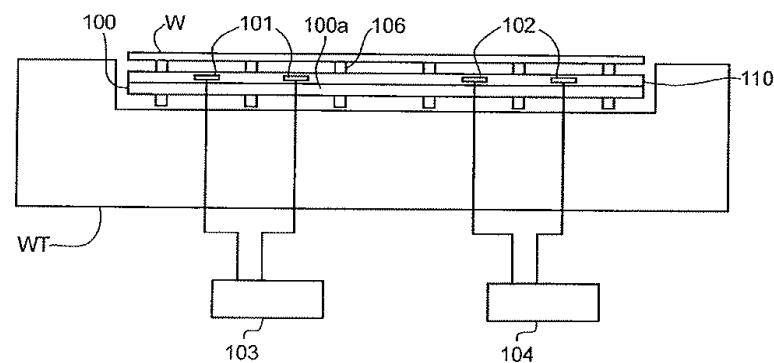

- 도 9는 본 발명의 일 실시예에 따른 기판 테이블 및 기판 홀더의 단면도; 및

- 도 10 내지 도 15는 본 발명의 실시예들에 따른 박막 스택(thin-film stacks)을 도시하는 도면이다.

### 발명을 실시하기 위한 구체적인 내용

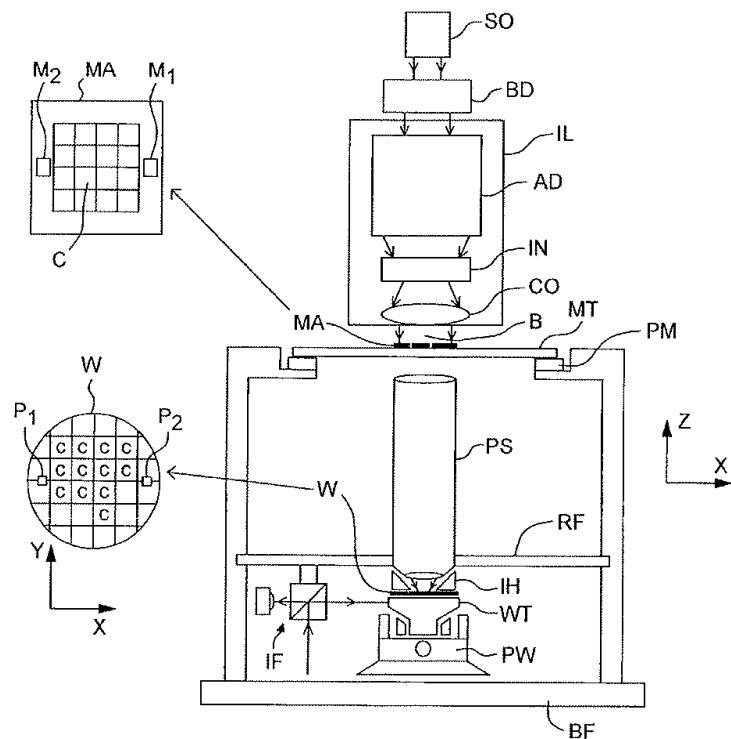

[0013] 도 1은 본 발명의 일 실시예에 따른 리소그래피 장치를 개략적으로 도시한다. 상기 장치는:

- 방사선 빔(B)(예를 들어, UV 방사선, DUV 방사선 또는 EUV 방사선)을 컨디셔닝(condition)하도록 구성된 조명

시스템(일루미네이터)(IL);

[0015] - 패터닝 디바이스(예를 들어, 마스크)(MA)를 지지하도록 구성되고, 소정 파라미터들에 따라 패터닝 디바이스를 정확히 위치시키도록 구성된 제 1 위치설정기(PM)에 연결된 지지 구조체(예를 들어, 마스크 테이블)(MT);

[0016] - 기판(예를 들어, 레지스트-코팅된 웨이퍼)(W)을 유지하도록 구성되고, 소정 파라미터들에 따라 기판을 정확히 위치시키도록 구성된 제 2 위치설정기(PW)에 연결된 기판 테이블(예를 들어, 웨이퍼 테이블)(WT); 및

[0017] - 기판(W)의 (예를 들어, 1 이상의 다이를 포함하는) 타겟부(C) 상으로 패터닝 디바이스(MA)에 의해 방사선 빔(B)에 부여된 패턴을 투영하도록 구성된 투영 시스템(예를 들어, 굴절 투영 렌즈 시스템)(PS)을 포함한다.

[0018] 조명 시스템은 방사선을 지향, 성형, 또는 제어하기 위하여, 굴절, 반사, 자기, 전자기, 정전기 또는 다른 타입의 광학 구성요소들, 또는 그 여하한의 조합과 같은 다양한 타입들의 광학 구성요소들을 포함할 수 있다.

[0019] 지지 구조체(MT)는 패터닝 디바이스를 유지한다. 지지 구조체(MT)는 패터닝 디바이스의 방위, 리소그래피 장치의 디자인, 및 예를 들어 패터닝 디바이스가 진공 환경에서 유지되는지의 여부와 같은 다른 조건들에 의존하는 방식으로 패터닝 디바이스를 유지한다. 지지 구조체(MT)는 패터닝 디바이스를 유지하기 위해 기계적, 진공, 정전기, 또는 다른 클램핑 기술들을 이용할 수 있다. 지지 구조체(MT)는, 예를 들어 필요에 따라 고정되거나 이동 가능할 수 있는 프레임 또는 테이블일 수 있다. 지지 구조체(MT)는, 패터닝 디바이스가 예를 들어 투영 시스템에 대해 원하는 위치에 있을 것을 보장할 수 있다. 본 명세서의 "레티클" 또는 "마스크"라는 용어의 어떠한 사용도 "패터닝 디바이스"라는 좀 더 일반적인 용어와 동의어로 간주될 수 있다.

[0020] 본 명세서에서 사용되는 "패터닝 디바이스"라는 용어는, 기판의 타겟부에 패턴을 생성하기 위해서, 방사선 빔의 단면에 패턴을 부여하는데 사용될 수 있는 여하한의 디바이스를 언급하는 것으로 폭넓게 해석되어야 한다. 방사선 빔에 부여된 패턴은, 예를 들어 상기 패턴이 위상-시프팅 피처들(phase-shifting features) 또는 소위 어시스턴트 피처들(assist features)을 포함하는 경우, 기판의 타겟부의 원하는 패턴과 정확히 일치하지 않을 수도 있다는 것을 유의하여야 한다. 일반적으로, 방사선 빔에 부여된 패턴은 집적 회로와 같이 타겟부에 생성될 디바이스의 특정 기능 층에 대응할 것이다.

[0021] 패터닝 디바이스는 투과형 또는 반사형일 수 있다. 패터닝 디바이스의 예로는 마스크, 프로그램 가능한 거울 어레이 및 프로그램 가능한 LCD 패널들을 포함한다. 마스크는 리소그래피 분야에서 잘 알려져 있으며, 바이너리(binary)형, 교변 위상-시프트형 및 감쇠 위상-시프트형과 같은 마스크 타입뿐만 아니라, 다양한 하이브리드(hybrid) 마스크 타입들을 포함한다. 프로그램 가능한 거울 어레이의 일 예시는 작은 거울들의 매트릭스 구성을 채택하며, 그 각각은 입사하는 방사선 빔을 상이한 방향으로 반사시키도록 개별적으로 기울어질 수 있다. 기울어진 거울들은 거울 매트릭스에 의해 반사되는 방사선 빔에 패턴을 부여한다.

[0022] 본 명세서에서 사용되는 "투영 시스템"이라는 용어는, 사용되는 노광 방사선에 대하여, 또는 침지 액체의 사용 또는 진공의 사용과 같은 다른 인자들에 대하여 적절하다면, 굴절, 반사, 카타디옵트릭(cataadioptric), 자기, 전자기 및 정전기 광학 시스템, 또는 이의 여하한의 조합을 포함하는 여하한 타입의 시스템을 포함하는 것으로서 폭넓게 해석되어야 한다. 본 명세서의 "투영 렌즈"라는 용어의 어떠한 사용도 "투영 시스템"이라는 좀 더 일반적인 용어와 동의어로 간주될 수 있다.

[0023] 본 명세서에 도시된 바와 같이, 상기 장치는 (예를 들어, 투과 마스크를 채택하는) 투과형으로 구성된다. 대안적으로, 상기 장치는 (예를 들어, 앞서 언급된 바와 같은 타입의 프로그램 가능한 거울 어레이를 채택하거나, 반사 마스크를 채택하는) 반사형으로 구성될 수 있다.

[0024] 리소그래피 장치는 기판 스테이지 또는 기판 테이블과 같은 2 이상의 기판 지지 구조체들, 및/또는 패터닝 디바이스들을 위한 2 이상의 지지 구조체들을 갖는 형태로 구성될 수 있다. 다수의 기판 스테이지들을 갖는 장치에서는, 모든 기판 테이블들이 동등하며 상호교환가능할 수 있다. 일 실시예에서, 다수의 기판 스테이지들 중 적어도 하나는 노광 단계들을 위해 특별히 구성되고, 다수의 기판 스테이지들 중 적어도 하나는 측정 또는 준비 단계들을 위해 특별히 구성된다. 본 발명의 일 실시예에서는 다수의 기판 스테이지들 중 1 이상이 측정 스테이지에 의해 대체된다. 측정 스테이지는, 센서 시스템의 타겟 및/또는 센서 검출기와 같은 1 이상의 센서 시스템들을 적어도 부분적으로 포함하지만, 기판을 지지하지는 않는다. 측정 스테이지는 패터닝 디바이스를 위한 지지 구조체 또는 기판 스테이지 대신 투영 빔에 위치가능하다. 이러한 장치에서는 추가 스테이지들이 병행하여 사용될 수 있거나, 1 이상의 스테이지들이 노광에 사용되고 있는 동안 1 이상의 다른 스테이지들에서는 준비작업 단계가 수행될 수 있다.

[0025] 도 1을 참조하면, 일루미네이터(IL)는 방사선 소스(SO)로부터 방사선 빔을 수용한다. 예를 들어, 상기 소스가 엑시머 레이저(excimer laser)인 경우, 상기 소스(SO) 및 리소그래피 장치는 별도의 개체일 수 있다. 이러한 경우, 상기 소스는 리소그래피 장치의 일부분을 형성하는 것으로 간주되지 않으며, 방사선 빔은 예를 들어 적절한 지향 거울 및/또는 빔 익스팬더(beam expander)를 포함하는 빔 전달 시스템(BD)의 도움으로, 소스(SO)로부터 일루미네이터(IL)로 통과된다. 다른 경우, 예를 들어 상기 소스가 수은 램프인 경우, 상기 소스는 리소그래피 장치의 통합부일 수 있다. 상기 소스(SO) 및 일루미네이터(IL)는, 필요에 따라 빔 전달 시스템(BD)과 함께 방사선 시스템이라고도 칭해질 수 있다.

[0026] 일루미네이터(IL)는 방사선 빔의 각도 세기 분포를 조정하도록 구성된 조정기(AM)를 포함할 수 있다. 일반적으로, 일루미네이터의 퓨필 평면의 세기 분포의 적어도 외반경 및/또는 내반경 크기(통상적으로, 각각 외측-o 및 내측-o 라 함)가 조정될 수 있다. 또한, 일루미네이터(IL)는 인터그레이터(IN) 및 콘텐서(CO)와 같이, 다양한 다른 구성요소들을 포함할 수도 있다. 일루미네이터는 방사선 빔의 단면에 원하는 균일성(uniformity) 및 세기 분포를 갖기 위해, 방사선 빔을 컨디셔닝하는데 사용될 수 있다. 소스(SO)와 유사하게, 일루미네이터(IL)는 리소그래피 장치의 일부분을 형성하는 것으로 간주될 수 있거나 간주되지 않을 수도 있다. 예를 들어, 일루미네이터(IL)는 리소그래피 장치의 통합부일 수 있거나, 리소그래피 장치로부터 별도의 개체일 수 있다. 후자의 경우, 리소그래피 장치는 일루미네이터(IL)가 그 위에 장착되도록 구성될 수 있다. 선택적으로, 일루미네이터(IL)는 분리가능하며(detachable), (예를 들어, 리소그래피 장치 제조업자 또는 다른 공급자에 의해) 별도로 제공될 수도 있다.

[0027] 방사선 빔(B)은 지지 구조체(예를 들어, 마스크 테이블)(MT)에 유지되어 있는 패터닝 디바이스(예를 들어, 마스크)(MA)에 입사되며, 패터닝 디바이스에 의해 패터닝된다. 패터닝 디바이스(MA)를 가로질렀으면, 방사선 빔(B)은 투영 시스템(PS)을 통하여 기판(W)의 타겟부(C) 상에 상기 빔을 포커스한다. 기판(W)은 본 발명의 일 실시예에 따른 기판 홀더에 의해 기판 테이블(WT)에 유지되며, 아래에 더 자세히 설명된다. 제 2 위치설정기(PW) 및 위치 센서(IF)[예를 들어, 간섭계 디바이스(interferometric device), 리니어 인코더(linear encoder) 또는 용량성 센서(capacitive sensor)]의 도움으로, 기판 테이블(WT)은 예를 들어 방사선 빔(B)의 경로에 상이 한 타겟부들(C)을 위치시키도록 정확하게 이동될 수 있다. 이와 유사하게, 제 1 위치설정기(PM) 및 (도 1에 명확히 도시되지 않은) 또 다른 위치 센서는, 예를 들어 마스크 라이브러리(mask library)로부터의 기계적인 회수 후에, 또는 스캔하는 동안, 방사선 빔(B)의 경로에 대해 패터닝 디바이스(MA)를 정확히 위치시키는데 사용될 수 있다. 일반적으로, 지지 구조체(MT)의 이동은 장-행정 모듈(long-stroke module: 개략 위치설정) 및 단-행정 모듈(short-stroke module: 미세 위치설정)의 도움으로 실현될 수 있으며, 이는 제 1 위치설정기(PM)의 일부분을 형성한다. 이와 유사하게, 기판 테이블(WT)의 이동은 장-행정 모듈 및 단-행정 모듈을 이용하여 실현될 수 있으며, 이는 제 2 위치설정기(PW)의 일부분을 형성한다. (스캐너와는 대조적으로) 스텝퍼의 경우, 지지 구조체(MT)는 단-행정 액추에이터에만 연결되거나 고정될 수 있다. 패터닝 디바이스(MA) 및 기판(W)은 패터닝 디바이스 정렬 마크들(M1 및 M2) 및 기판 정렬 마크들(P1 및 P2)을 이용하여 정렬될 수 있다. 비록, 예시된 기판 정렬 마크들이 지정된(dedicated) 타겟부들을 차지하고 있지만, 그들은 타겟부들 사이의 공간들에 위치될 수도 있다[이들은 스크라이브-레인 정렬 마크들(scribe-lane alignment marks)로 알려져 있다]. 이와 유사하게, 패터닝 디바이스(MA)에 1 이상의 다이가 제공되는 상황들에서, 패터닝 디바이스 정렬 마크들은 다이들 사이에 위치될 수 있다.

[0028] 도시된 장치는 다음 모드들 중 적어도 하나에 사용될 수 있다:

[0029] 1. 스텝 모드에서, 지지 구조체(MT) 및 기판 테이블(WT)은 본질적으로 정지 상태로 유지되는 한편, 방사선 빔에 부여되는 전체 패턴은 한번에 타겟부(C) 상에 투영된다[즉, 단일 정적 노광(single static exposure)]. 그 후, 기판 테이블(WT)은 상이한 타겟부(C)가 노광될 수 있도록 X 및/또는 Y 방향으로 시프트된다. 스텝 모드에서, 노광 필드의 최대 크기는 단일 정적 노광시에 이미징되는 타겟부(C)의 크기를 제한한다.

[0030] 2. 스캔 모드에서, 지지 구조체(MT) 및 기판 테이블(WT)은 방사선 빔에 부여된 패턴이 타겟부(C) 상에 투영되는 동안에 동기적으로 스캐닝된다[즉, 단일 동적 노광(single dynamic exposure)]. 지지 구조체(MT)에 대한 기판 테이블(WT)의 속도 및 방향은 투영 시스템(PS)의 확대(축소) 및 이미지 반전 특성에 의하여 결정될 수 있다. 스캔 모드에서, 노광 필드의 최대 크기는 단일 동적 노광시 타겟부의 (스캐닝 되지 않는 방향으로의) 폭을 제한하는 반면, 스캐닝 동작의 길이는 타겟부의 (스캐닝 방향으로의) 높이를 결정한다.

[0031] 3. 또 다른 모드에서, 지지 구조체(MT)는 프로그램 가능한 패터닝 디바이스를 유지하여 본질적으로 정지된 상태로 유지되며, 방사선 빔에 부여된 패턴이 타겟부(C) 상에 투영되는 동안 기판 테이블(WT)이 이동되거나 스캐닝

된다. 이 모드에서는, 일반적으로 펄스화된 방사선 소스(pulsed radiation source)가 채택되며, 프로그램가능한 패터닝 디바이스는 기판 테이블(WT)의 매 이동 후에, 또는 스캔 중에 계속되는 방사선 펄스 사이사이에 필요에 따라 업데이트된다. 이 작동 모드는 앞서 언급된 바와 같은 타입의 프로그램가능한 거울 어레이와 같은 프로그램가능한 패터닝 디바이스를 이용하는 마스크없는 리소그래피(maskless lithography)에 용이하게 적용될 수 있다.

[0032] 또한, 상술된 사용 모드들의 조합 및/또는 변형, 또는 완전히 다른 사용 모드들이 채택될 수도 있다.

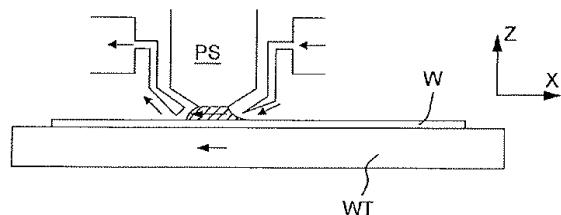

[0033] 다수의 리소그래피 장치들에서는, 더 작은 피처들의 이미징을 가능하게 하고 및/또는 장치의 유효 NA를 증가시키기 위해 액체 공급 시스템(IH)을 이용하여 투영 시스템의 최종 요소 사이에 유체, 특히 액체가 제공된다. 본 발명의 일 실시예는 이러한 침지 장치를 참조하여 아래에 더 자세히 설명되지만, 비-침지 장치에도 동일하게 구현될 수 있다. 투영 시스템의 최종 요소와 기판 사이에 액체를 제공하는 구성들은 적어도 2 개의 일반적인 카테고리들로 분류될 수 있다. 이들은 배스 타입 구성(bath type arrangement) 및 소위 국부화된 침지 시스템 (localized immersion system)이다. 배스 타입 구성에서는, 기판의 실질적으로 전체 및 기판 테이블의 선택적인 부분이 액체 배스에 담가진다(submersed). 국부화된 침지 시스템은 기판의 국부화된 영역에만 액체가 제공되는 액체 공급 시스템을 이용한다. 후자의 카테고리에서, 액체에 의해 채워진 공간은 평면에서 기판의 최상부 표면보다 작으며, 액체로 채워진 영역은 기판이 상기 영역 밑으로 이동하는 동안 투영 시스템에 대해 실질적으로 정지한 상태로 유지된다. 본 발명의 일 실시예가 추구하는 또 다른 구성은 액체가 비-한정된(unconfined) 완전 습식 솔루션(all wet solution)이다. 이 구성에서는, 기판의 실질적으로 전체 최상부 표면, 및 기판 테이블의 전체 또는 일부분이 침지 액체로 덮인다. 적어도 기판을 덮는 액체의 깊이는 얕다. 이러한 액체는 기판 상의 액체의 막, 예컨대 박막일 수 있다.

[0034] 4 개의 상이한 타입의 국부화된 액체 공급 시스템들이 도 2 내지 도 5에 도시된다. 도 2 내지 도 5의 액체 공급 디바이스들 중 어느 것이라도 비-한정된 시스템에서 사용될 수 있다; 하지만, 시일링 특징부(sealing feature)들이 존재하지 않거나, 활성화되지 않거나, 정상만큼 효율적이지 않거나, 아니면 국부화된 영역에 대해서만 액체를 시일링하기에는 비효과적이다.

[0035] 국부화된 침지 시스템에 제안된 구성들 중 하나는, 액체 공급 시스템이 액체 한정 시스템(liquid confinement system)을 이용하여 투영 시스템의 최종 요소와 기판 사이에 그리고 기판의 국부화된 영역에만 액체를 제공하는 것이다(일반적으로, 기판은 투영 시스템의 최종 요소보다 큰 표면적을 갖는다). 이처럼 배치하기 위해 제안된 한가지 방식이 PCT 특허 출원 공개공보 WO 99/49504에 개시된다. 도 2 및 도 3에 예시된 바와 같이, 적어도 하나의 유입구에 의해 기판 상으로, 바람직하게는 최종 요소에 대한 기판의 이동 방향을 따라 액체가 공급되고, 투영 시스템 아래를 통과한 후에는 적어도 하나의 유출구에 의해 제거된다. 즉, 기판이 요소 밑에서 -X 방향으로 스캐닝됨에 따라, 액체는 상기 요소의 +X 측에서 공급되고 -X 측에서 흡수(taken up)된다.

[0036] 도 2는 액체가 유입구를 통해 공급되고, 저압력원에 연결되어 있는 유출구에 의해 요소의 다른 측에서 흡수되는 구성을 개략적으로 도시한다. 기판(W) 위의 화살표들은 액체 유동 방향을 예시하고, 기판(W) 아래의 화살표는 기판 테이블의 이동 방향을 예시한다. 도 2의 예시에서, 액체는 최종 요소에 대해 기판의 이동 방향을 따라 공급되지만, 반드시 이와 같을 필요는 없다. 최종 요소 주변에 위치된 유입 및 유출구들의 다양한 방위들 및 개수들이 가능하며, 양측에 유출구를 갖는 유입구의 4 개의 세트가 최종 요소 주변에 규칙적인 패턴으로 제공된 일 예시가 도 3에 예시된다. 액체 공급 및 액체 회수 디바이스들에서의 화살표들은 액체 유동 방향을 나타낸다.

[0037] 국부화된 액체 공급 시스템을 갖는 또 다른 침지 리소그래피 솔루션이 도 4에 도시된다. 투영 시스템(PS)의 양 측 상의 2 개의 홈형 유입구에 의해 액체가 공급되고, 유입구들의 반경 방향 바깥쪽으로(radially outwardly) 배치된 복수의 개별 유출구들에 의해 제거된다. 유입구들 및 유출구들은 그 중심에 홀(hole)을 갖는 플레이트에 배치될 수 있고, 그 홀을 통해 투영 빔이 투영된다. 투영 시스템(PS)의 일 측 상의 하나의 홈형 유입구에 의해 액체가 공급되고, 투영 시스템(PS)의 다른 측 상의 복수의 개별 유출구들에 의해 제거되어, 투영 시스템(PS)과 기판(W) 사이에 박막의 액체 유동을 유도한다. 유입구 및 유출구들의 어떤 조합을 사용할지에 관한 선택은, 기판(W)의 이동 방향에 의존할 수 있다(유입구 및 유출구들의 다른 조합은 비활성이다). 도 4의 단면도에서, 화살표들은 유입구들 안으로의 액체 유동 방향과 유출구들로부터 나가는 액체 유동 방향을 예시한다.

[0038] 제안된 또 다른 구성은 액체 공급 시스템에 액체 한정 부재를 제공하는 것이며, 액체 한정 부재는 투영 시스템의 최종 요소와 기판 테이블 사이의 공간의 경계의 적어도 일부분을 따라 연장된다. 이러한 구성은 도 5에 예시된다. 액체 한정 부재는 Z 방향(광축 방향)으로 약간의 상대 이동이 있을 수 있지만, XY 평면에서는 투영 시

스템에 대해 실질적으로 정지 상태이다. 액체 한정 부재와 기판의 표면 사이에 시일이 형성된다. 일 실시예에서는, 유체 한정 부재와 기판의 표면 사이에 시일이 형성되며, 가스 시일과 같은 무접촉 시일일 수 있다. 이러한 시스템은 미국 특허 출원 공개공보 US 2004-0207824에 개시되어 있다.

[0039] 유체 핸들링 구조체(12)는 액체 한정 부재를 포함하고, 투영 시스템(PS)의 최종 요소와 기판(W) 사이의 공간(11)에 적어도 부분적으로 액체를 수용한다. 기판(W)에 대한 무접촉 시일(16)이 투영 시스템의 이미지 필드 주위에 형성될 수 있어, 기판(W) 표면과 투영 시스템(PS)의 최종 요소 사이의 공간 내에 액체가 한정되게 된다. 상기 공간은 투영 시스템(PS)의 최종 요소 아래에, 그리고 이를 둘러싸서 위치된 유체 핸들링 구조체(12)에 의해 적어도 부분적으로 형성된다. 액체 유입구(13)에 의해 투영 시스템 아래의 그리고 유체 핸들링 구조체(12) 내의 공간(11)으로 액체가 유입된다. 이 액체는 액체 유출구(13)에 의해 제거될 수 있다. 유체 핸들링 구조체(12)는 투영 시스템의 최종 요소 위로 약간 연장될 수 있다. 액체 수위가 상기 최종 요소 위로 상승하여 액체의 버퍼가 제공된다. 일 실시예에서, 유체 핸들링 구조체(12)는 상단부에서 투영 시스템 또는 그 최종 요소의 형상에 거의 들어맞고(closely conform), 예를 들어 원형일 수 있는 내측 주변부(inner periphery)를 갖는다. 최하부에서, 내측 주변부는 이미지 필드의 형상, 예를 들어 직사각형에 거의 들어맞지만, 반드시 이와 같을 필요는 없다.

[0040] 일 실시예에서, 사용 시 유체 핸들링 구조체(12)의 최하부와 기판(W)의 표면 사이에 형성된 가스 시일(16)에 의해 액체가 공간(11) 내에 수용된다. 가스 시일은 가스, 예를 들어 공기, 합성 공기(synthetic air), N<sub>2</sub> 또는 또 다른 불활성 기체에 의해 형성된다. 가스 시일의 가스는 유입구(15)를 통해 과소압력(under pressure)으로 유체 핸들링 구조체(12)와 기판(W) 사이의 캡에 제공된다. 상기 가스는 유출구(14)를 통해 추출된다. 가스 유입구(15) 상의 과대압력(overpressure), 유출구(14) 상의 진공 레벨, 및 캡의 지오메트리(geometry)는, 액체를 한정하는 안쪽으로의 고속 가스 유동(16)이 존재하도록 배치된다. 유체 핸들링 구조체(12)와 기판(W) 사이의 액체 상의 가스의 힘은 공간(11)에 액체를 수용한다. 유입구들/유출구들은 상기 공간(11)을 둘러싸는 환형의 홈일 수 있다. 상기 환형의 홈은 연속적이거나 불연속적일 수 있다. 가스의 유동(16)은 공간(11)에 액체를 수용하는데 효과적이다. 이러한 시스템은 미국 특허 출원 공개공보 US 2004-0207824에 개시되어 있다.

[0041] 도 5의 예시는, 어느 한 순간에 기판(W)의 최상부 표면의 국부화된 영역에만 액체가 제공되는 국부화된 영역 구성이다. 예를 들어, 미국 특허 출원 공개공보 US 2006-0038968에 개시된 바와 같이, 단-상 추출기(single phase extractor) 또는 2-상 추출기를 이용하는 유체 핸들링 시스템들을 포함하는 다른 구성들이 가능하다.

[0042] 가능한 또 다른 구성은 가스 드래그 원리(gas drag principle)에 따라 작동하는 구성이다. 소위 가스 드래그 원리는, 예를 들어 미국 특허 출원 공개공보 US 2008-0212046, US 2009-0279060 및 US 2009-0279062에 개시되었다. 이러한 시스템에서는, 추출 홀들이 바람직하게는 코너를 갖는 형상으로 배치된다. 이 코너는 스텝핑(stepping) 및 스캐닝 방향들과 정렬될 수 있다. 이는, 2 개의 유출구들이 스캔 방향에 대해 수직으로 정렬된 유체 핸들링 구조체에 비해, 스텝 또는 스캔 방향으로 주어진 속도에 대해 유체 핸들링 구조체 표면의 2 개의 개구부들 사이의 멘尼斯커스(meniscus) 상의 힘을 감소시킨다.

[0043] 또한, 주요 액체 회수 특징부(main liquid retrieval feature)의 반경방향 바깥쪽에 위치된 가스 나이프(gas knife)가 US 2008-0212046에 개시된다. 가스 나이프는 주요 액체 회수 특징부를 지나간 여하한의 액체를 포획한다. 이러한 가스 나이프는 (US 2008-0212046에 개시된 바와 같은) 소위 가스 드래그 원리 구성에, (미국 특허 출원 공개공보 US 2009-0262318에 개시된 바와 같은) 단일 또는 2-상 추출기 구성에, 또는 여타의 구성에 존재할 수 있다.

[0044] 액체 공급 시스템의 다수의 다른 타입들이 가능하다. 본 발명은 여하한의 특정한 타입의 액체 공급 시스템으로도 그리고 침지 리소그래피로도 제한되지 않는다. 본 발명은 여하한의 리소그래피에 동일하게 적용될 수 있다. EUV 리소그래피 장치에서, 빔 경로는 실질적으로 진공상태이며(evacuated), 앞서 설명된 침지 구성들이 사용되지 않는다.

[0045] 도 6은 소스 컬렉터 장치(SO)를 포함하는 EUV 리소그래피 장치(4100)를 개략적으로 도시한다. 상기 장치는:

[0046] - 방사선 빔(B)(예를 들어, EUV 방사선)을 컨디셔닝하도록 구성된 조명 시스템(일루미네이터)(EIL);

[0047] - 패터닝 디바이스(예를 들어, 마스크 또는 레티클)(MA)를 지지하도록 구성되고 패터닝 디바이스를 정확히 위치시키도록 구성된 제 1 위치설정기(PM)에 연결되는 지지 구조체(예를 들어, 마스크 테이블)(MT);

[0048] - 기판(예를 들어, 레지스트-코팅된 웨이퍼)(W)을 유지하도록 구성되고, 기판을 정확히 위치시키도록 구성된 제

2 위치설정기(PW)에 연결되는 기판 테이블(예를 들어, 웨이퍼 테이블)(WT); 및

[0049] - 패터닝 디바이스(MA)에 의해 방사선 빔(B)에 부여된 패턴을 기판(W)의 (예를 들어, 1 이상의 다이를 포함하는) 타겟부(C) 상으로 투영하도록 구성된 투영 시스템(예를 들어, 반사 투영 시스템)(PS)을 포함한다.

[0050] EUV 리소그래피 장치의 이러한 기본 구성요소들은 도 1의 리소그래피 장치의 대응하는 구성요소와 기능 면에서 유사하다. 이하의 설명은 주로 차이가 있는 영역들을 다루며, 동일한 구성요소들의 실시형태들에 관한 중복 설명은 생략하기로 한다.

[0051] EUV 리소그래피 장치에서는, 가스들이 너무 많은 방사선을 흡수할 수 있기 때문에, 진공 또는 저압 환경을 이용하는 것이 바람직하다. 그러므로, 진공 벽 및 1 이상의 진공 펌프들의 도움으로 전체 빔 경로에 진공 환경이 제공될 수 있다.

[0052] 도 6을 참조하면, EUV 일루미네이터(EIL)는 소스 컬렉터 장치(SO)로부터 극자외(EUV) 방사선 빔을 수용한다. EUV 광을 생성하기 위한 방법들은 EUV 범위에서 1 이상의 방출 라인들을 갖는 적어도 하나의 원소, 예를 들어 크세논, 리튬 또는 주석을 갖는 플라즈마 상태로 재료를 전환시키는 단계를 포함한다(단, 이로 제한되지 않음). 흔히 레이저 생성 플라즈마("LPP")로 칭해지는 이러한 방법에서, 플라즈마는 원하는 라인-방출 요소를 갖는 재료의 액적, 스트립 또는 클러스터와 같은 연료를 레이저 빔으로 조사함으로써 생성될 수 있다. 소스 컬렉터 장치(SO)는 연료를 여기시키는 레이저 빔을 제공하기 위해 도 6에는 도시되지 않은 레이저를 포함하는 EUV 방사선 시스템의 일부일 수 있다. 이로 인해 생성된 플라즈마는 출력 방사선, 예를 들어 EUV 방사선을 방출하며, 이는 소스 컬렉터 장치에 배치된 방사선 컬렉터를 이용하여 수집된다. 예를 들어, 연료 여리를 위해 레이저 빔을 제공하는 데 CO<sub>2</sub> 레이저가 사용되는 경우, 레이저 및 소스 컬렉터 장치는 별도의 개체들일 수 있다.

[0053] 이러한 경우, 레이저는 리소그래피 장치의 일부분을 형성하는 것으로 간주되지 않으며, 방사선 빔은 예를 들어 적절한 지향 거울 및/또는 빔 익스팬더를 포함하는 빔 전달 시스템의 도움으로 레이저로부터 소스 컬렉터 장치로 통과된다. 다른 경우, 예를 들어 상기 소스가 방전 생성 플라즈마 EUV 생성기(흔히, DPP 소스라고도 함)인 경우, 상기 소스는 소스 컬렉터 장치의 통합부일 수 있다.

[0054] EUV 일루미네이터(EIL)는 방사선 빔(EB)의 각도 세기 분포를 조정하는 조정기를 포함할 수 있다. 일반적으로, 일루미네이터의 퓨필 평면의 세기 분포의 적어도 외반경 및/또는 내반경 크기(통상적으로, 각각 외측- $\sigma$  및 내측- $\sigma$ 라 함)가 조정될 수 있다. 또한, EUV 일루미네이터(EIL)는 패싯 필드 및 퓨필 거울 디바이스(facetted field and pupil mirror device)들과 같은 다양한 다른 구성요소들을 포함할 수 있다. EUV 일루미네이터(EIL)는 방사선 빔(EB)의 단면에 원하는 균일성 및 세기 분포를 갖기 위해, 방사선 빔(EB)을 컨디셔닝하는데 사용될 수 있다.

[0055] 방사선 빔(EB)은 지지 구조체(예를 들어, 마스크 테이블)(MT)에 유지되어 있는 패터닝 디바이스(예를 들어, 마스크)(MA)에 입사되며, 패터닝 디바이스에 의해 패터닝된다. 패터닝 디바이스(예를 들어, 마스크)(MA)로부터 반사된 후, 방사선 빔(EB)은 투영 시스템(PS)을 통하여 기판(W)의 타겟부(C) 상으로 상기 빔을 포커스한다. 제 2 위치설정기(PW) 및 위치 센서(PS2)[예를 들어, 간접계 디바이스, 리니어 인코더 또는 용량성 센서]의 도움으로, 기판 테이블(WT)은 예를 들어 방사선 빔(EB)의 경로에 상이한 타겟부(C)들을 위치시키도록 정확하게 이동될 수 있다. 이와 유사하게, 제 1 위치설정기(PM) 및 또 다른 위치 센서(PS1)는 방사선 빔(EB)의 경로에 대해 패터닝 디바이스(예를 들어, 마스크)(MA)를 정확히 위치시키는 데 사용될 수 있다. 패터닝 디바이스(예를 들어, 마스크)(MA) 및 기판(W)은 마스크 정렬 마크들(M1 및 M2) 및 기판 정렬 마크들(P1 및 P2)을 이용하여 정렬될 수 있다.

[0056] 도시된 장치는 도 1의 장치와 동일한 모드들에 사용될 수 있다.

[0057] 도 7은 소스 컬렉터 장치(SO), EUV 조명 시스템(EIL) 및 투영 시스템(PS)을 포함하는 EUV 장치(4100)를 더 자세하게 도시한다. 소스 컬렉터 장치(SO)는 소스 컬렉터 장치(SO)의 인클로징 구조체(enclosing structure; 4220)에 진공 환경이 유지될 수 있도록 구성되고 배치된다. EUV 방사선 방출 플라즈마(4210)는 방전 생성 플라즈마 소스에 의해 형성될 수 있다. EUV 방사선은 전자기 스펙트럼의 EUV 범위의 방사선을 방출하기 위해 플라즈마(4210)가 생성되는 가스 또는 증기, 예를 들어 Xe 가스, Li 증기, 또는 Sn 증기에 의해 생성될 수 있다. 플라즈마(4210)는, 예를 들어 적어도 부분적으로 이온화된 플라즈마를 유도하는 전기 방전에 의해 생성된다. 방사선의 효율적인 생성을 위해서는 Xe, Li, Sn 증기 또는 여타 적합한 가스 또는 증기의, 예를 들어 10 Pa의 분압이 요구될 수 있다. EUV 방사선을 생성하기 위해 여기된 주석(Sn)의 플라즈마가 제공된다.

[0058] 플라즈마(4210)에 의해 방출되는 방사선은 소스 챔버(4211)의 개구부 안이나 뒤에 위치되는 선택적 가스 방벽 및/또는 오염물 트랩(contaminant trap: 4230)[몇몇 경우에는, 오염물 방벽 또는 포일 트랩(foil trap)이라 지칭되기도 함]을 통해 소스 챔버(4211)로부터 컬렉터 챔버(4212) 내로 전달된다. 오염물 트랩(4230)은 채널 구조체를 포함할 수 있다. 또한, 오염물 트랩(4230)은 가스 방벽, 또는 가스 방벽과 채널 구조체의 조합을 포함할 수 있다. 또한, 본 명세서에 개시된 오염물 트랩 또는 오염물 방벽(4230)은 적어도 당업계에 알려진 바와 같은 채널 구조체를 포함한다.

[0059] 컬렉터 챔버(4212)는 방사선 컬렉터(CO)를 포함할 수 있으며, 이는 소위 스침 입사 컬렉터(grazing incidence collector)일 수 있다. 방사선 컬렉터(CO)는 상류 방사선 컬렉터 측(4251) 및 하류 방사선 컬렉터 측(4252)을 갖는다. 컬렉터(CO)를 가로지르는(traverse) 방사선은 격자 스펙트럼 필터(4240)에 의해 반사되어 가상 소스 지점(IF)에 포커스될 수 있다. 가상 소스 지점(IF)은 통상적으로 중간 포커스라고도 칭해지며, 소스 컬렉터 장치는 중간 포커스(IF)가 인클로징 구조체(4220)의 개구부(4221)에 또는 그 부근에 배치되도록 구성된다. 가상 소스 지점(IF)은 방사선 방출 플라즈마(4210)의 이미지이다.

[0060] 후속하여, 방사선은 조명 시스템(IL)을 가로지르며, 상기 조명 시스템은 패터닝 디바이스(MA)에서 방사선 세기의 원하는 균일성뿐만 아니라, 패터닝 디바이스(MA)에서 방사선 빔(421)의 원하는 각도 분포를 제공하도록 배치된 패싯 퓨필 거울 디바이스(facetted pupil mirror device: 424) 및 패싯 필드 거울 디바이스(facetted field mirror device: 422)를 포함할 수 있다. 지지 구조체(MT)에 의해 유지된 패터닝 디바이스(MA)에서 방사선 빔(421)이 반사될 때, 패터닝된 빔(426)이 형성되며, 패터닝된 빔(426)은 투영 시스템(PS)에 의해 반사 요소들(428, 430)을 거쳐 기판 스테이지 또는 기판 테이블(WT)에 의해 유지된 기판(W) 상으로 이미징된다.

[0061] 일반적으로, 조명 광학 유닛(IL) 및 투영 시스템(PS)에는 도시된 것보다 많은 요소들이 존재할 수 있다. 리소그래피 장치의 타입에 따라, 선택적으로 격자 스펙트럼 필터(4240)가 존재할 수 있다. 도면들에 도시된 것보다 더 많은 거울들이 존재할 수 있으며, 예를 들어 투영 시스템(PS)에는 추가 반사 요소들이 도 7에 도시된 것보다 1 내지 6 개 더 많이 존재할 수 있다.

[0062] 도 7에 예시된 바와 같은 컬렉터 광학기(CO)는 컬렉터(또는 컬렉터 거울)의 단지 일 예시로서 스침 입사 반사기들(4253, 4254 및 4255)을 갖는 네스티드 컬렉터(nested collector)로서 도시된다. 스침 입사 반사기들(4253, 4254 및 4255)은 광축(O)을 중심으로 축방향 대칭으로 배치되며, 이러한 타입의 컬렉터 광학기(CO)는 흔히 DPP 소스라 칭해지는 방전 생성 플라즈마 소스와 조합하여 사용되는 것이 바람직하다.

[0063] 대안적으로, 소스 컬렉터 장치(SO)는 도 8에 도시된 바와 같은 LPP 방사선 시스템의 일부분일 수 있다. 레이저(LA)는 크세논(Xe), 주석(Sn) 또는 리튬(Li)과 같은 연료 내로 레이저 에너지를 축적(deposit)하도록 배치되어, 수십 eV의 전자 온도(electron temperatures)를 갖는 고도로 이온화된 플라즈마(4210)를 생성한다. 이러한 이온들의 텔-여기(de-excitation) 및 재조합(recombination) 동안 생성된 활성 방사선(energetic radiation)이 플라즈마로부터 방출되고, 근 수직 입사 컬렉터 광학기(near normal incidence collector optic: CO)에 의해 수집되며, 인클로징 구조체(4220)의 개구부(4221) 상으로 포커스된다.

[0064] 도 9는 본 발명의 일 실시예에 따른 기판 홀더를 도시한다. 기판 홀더는 기판 테이블(WT)의 후퇴부 내에 유지될 수 있고, 기판(W)을 지지한다. 기판 홀더(100)의 본체는 평탄한 플레이트, 예를 들어 형상 및 크기가 기판(W)에 실질적으로 대응하는 디스크의 형태를 갖는다. 적어도 최상부 측에, 일 실시예에서는 양측에, 기판 홀더는 통상적으로 벼얼이라 칭해지는 돌출부들(106)을 갖는다. 일 실시예에서, 기판 홀더는 기판 테이블의 일체형 부분이며, 하부면에 벼얼을 갖지 않는다. 도 9에는 벼얼이 축척대로 도시되어 있지 않다.

[0065] 기판 홀더의 표면은, 예를 들어 SiC, SiSiC, Zerodur 리튬 알루미노실리케이트 유리-세라믹(Zerodur lithium aluminosilicate glass-ceramic), 코디어라이트(cordierite), 석영 또는 여타의 적합한 세라믹 또는 유리-세라믹 재료로 형성될 수 있다. 기판 홀더(100)는, 돌출 벼얼을 남기기 위해 관련 재료의 솔리드 디스크(solid disc)로부터 재료를 선택적으로 제거함으로써 제조될 수 있다. 재료를 제거하는데 적합한 기술은 방전 가공(electrical discharge machining: EDM), 애칭 및/또는 레이저 어블레이션(laser ablation)을 포함한다. 이러한 기술은, 예를 들어 수 미크론 정도의 거칠기 값(Ra)을 갖는 거친 표면을 남길 수 있다. 이러한 제거 기술들로 달성가능한 최소 거칠기는 재료 특성들로부터 도출될 수 있다. 예를 들어, SiSiC와 같은 2-상 재료의 경우, 달성가능한 최소 거칠기는 2-상 재료의 입자 크기에 의해 결정된다. 이러한 잔여 거칠기(residual roughness)는 표면에 전기 구성요소, 특히 박막 구성요소의 형성을 어렵게 하며, 이러한 구성요소를 신뢰할 수 없게 한다(unreliability). 이러한 거칠기는 전자 구성요소를 형성하기 위해 기판 홀더에 코팅 또는 성장된 얇은 층에 1 이상의 캡 및/또는 균열을 유발하기 때문에 이러한 문제들이 생길 수 있다고 여겨진다. 박막 구성요소들은 약

2 nm 내지 약 50  $\mu\text{m}$  범위의 층 두께를 가질 수 있으며, 화학적 기상 증착, 물리적 기상 증착(예를 들어, 스퍼터링), 딥 코팅(dip coating), 스핀 코팅(spin coating), 및/또는 스프레이 코팅(spray coating)을 포함하는 공정에 의해 형성될 수 있다.

[0066] 실제 실시예에서는, 수천 개의, 예를 들어 10,000 개 이상 또는 40,000 개 이상의 베일이, 예를 들어 200 mm, 300 mm, 또는 450 mm의 폭(예를 들어, 직경)을 갖는 기판 홀더에 걸쳐 분포될 수 있다. 베일의 선단부들(tip s)은, 예를 들어 1  $\text{mm}$  미만의 작은 면적을 갖는다. 따라서, 기판 홀더(100)의 일 측 상의 모든 베일의 전체 면적은 기판 홀더의 전체 표면적의 전체 면적의 약 10 % 미만, 예를 들어 1 내지 3 %이다. 베일 구성으로 인해, 기판, 기판 홀더 또는 기판 테이블의 표면에 놓일 수 있는 여하한의 입자가 베일들 사이로 들어가 기판 또는 기판 홀더의 변형을 유도하지 않을 가능성이 높다.

[0067] 베일 배열(burl arrangement)은 패턴을 형성할 수 있고 및/또는 주기적인 배열을 가질 수 있다. 베일 배열은 규칙적일 수 있거나, 기판(W) 및/또는 기판 테이블(WT)에 적절한 힘의 분배를 제공하기 위해 필요에 따라 변동될 수 있다. 베일은 평면에서 여하한의 형상을 가질 수 있지만, 통상적으로는 평면에서 원형이다. 베일은 높이 전반에 걸쳐 동일한 형상 및 치수를 가질 수 있지만, 통상적으로 끝이 테이퍼링된다(tapered). 베일이 돌출되는 거리는 기판 홀더(100)의 본체(100a)의 표면의 받침대(rest)로부터이며, 기판 홀더(100)의 본체(100a)의 표면의 받침대로부터 약 1  $\mu\text{m}$  내지 약 5 mm, 바람직하게는 약 5  $\mu\text{m}$  내지 약 250  $\mu\text{m}$ 이다. 기판 홀더(100)의 본체(100a)의 두께는 약 1 mm 내지 약 50 mm 범위, 바람직하게는 약 5 mm 내지 20 mm 범위, 통상적으로 10 mm일 수 있다.

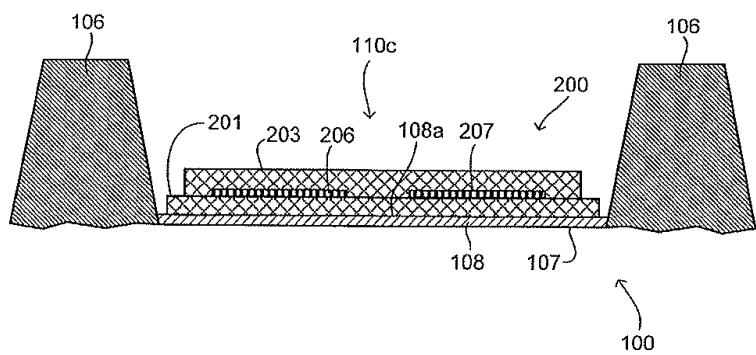

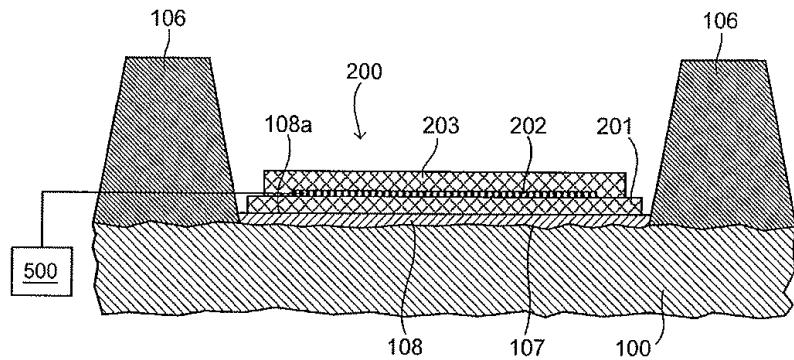

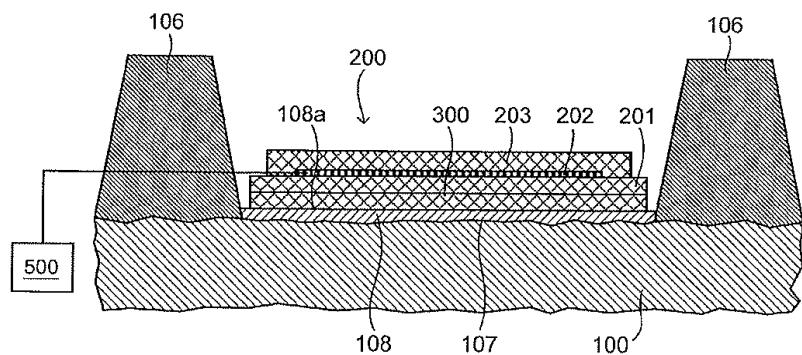

[0068] 도 10은 상부 표면(107) 및 몇몇 베일(106)을 단면도로 나타낸 도 9의 기판 홀더(100)의 부분 확대도이다. 베일들(106) 사이의 적어도 몇몇 영역의 상부 표면(107)에 평탄화 층(planarization layer; 108)이 제공된다. 일 실시예에서, 평탄화 층(108)은 전자 구성요소가 형성될 곳에만 제공될 수 있거나, 기판 홀더(100)의 실질적으로 전체 상부 표면에 걸쳐 제공될 수 있다. 평탄화 층(108)은 상부 표면(107)의 거친부분들을 채우며(fills in roughnesses), 상부 표면(107)보다 실질적으로 더 매끈한(smoothen) 상부 표면(108a)을 제공한다. 일 실시예에서, 평탄화 층(108)의 표면의 거칠기(Ra)는 약 1.5  $\mu\text{m}$  미만, 바람직하게는 약 1  $\mu\text{m}$  미만, 또는 바람직하게는 약 0.5  $\mu\text{m}$  미만이다. 일 실시예에서는, 경화(curing) 후 베일들 사이의 평탄화 층(108)을 폴리싱함으로써, 0.2  $\mu\text{m}$  미만의 평탄화 층(108)의 표면의 거칠기(Ra)가 달성된다.

[0069] 일 실시예에서, 평탄화 층(108)은 코팅 재료 또는 전구체 재료의 복수의 층, 예를 들어 2 개의 층을 도포함으로써 형성된다. 일 실시예에서, 평탄화 층(108)은 코팅 재료 또는 전구체 재료의 단일 층을 도포함으로써 형성될 수 있다. 평탄화 층의 재료에 따라, 형성된 코팅층의 검사로부터 코팅층이 다수의 서브-층들을 형성함으로써 도포되었는지를 결정할 수 있다. 일 실시예에서, 평탄화 층(108)의 다수의 서브-층들은 동일한 재료로 형성된다. 일 실시예에서, 평탄화 층(108)의 다수의 서브-층들은 상이한 재료들로 형성된다. 적합한 재료들은 아래에 설명된다.

[0070] 일 실시예에서, 평탄화 층(108)은 각각의 Si 원자에 부착되는 작용기(functional group)를 갖는 실리콘 산화물 또는 실리콘 질화물계 화합물로 형성된다. 작용기는 수소, 메틸, 플루오로, 비닐, 및/또는 그와 유사한 것의 그룹으로부터 적어도 하나 선택될 수 있다. 일 실시예에서, 평탄화 층(108)은  $\text{Si}(\text{CH}_3)_2\text{O}_x$ 로 형성된다. 일 실시예에서, 평탄화 층은  $\text{SiO}_x$ , 예를 들어  $\text{SiO}_2$ 로 형성된다. 일 실시예에서, 평탄화 층은 벤조사이클로부텐(BCB)으로 형성된다. 일 실시예에서, 평탄화 층은 폴리이미드 코팅 재료로 형성된다. 이러한 재료를 적용하는 방법은 미국 특허 7,524,735에 개시되어 있으며, 이는 본 명세서에서 전문이 인용 참조됨. 일 실시예에서, 평탄화 층(108)은  $\text{Si}(\text{CH}_3)_2\text{N}$  및  $\text{Si}(\text{CH}_3)_2\text{O}$  백본(backbone)들로 구성된 폴리머 체인들로 형성된다.

[0071] 평탄화 층(108)은 약 0.2  $\mu\text{m}$  내지 약 200  $\mu\text{m}$ , 바람직하게는 약 2  $\mu\text{m}$  내지 약 30  $\mu\text{m}$  범위의 두께를 가질 수 있다. 평탄화 층(108)은 기판 홀더 표면의 거친부분들의 대부분 또는 전부를 채우도록 충분히 두꺼운 것이 바람직하다. 평탄화 층(108)이 너무 두꺼운 경우, 경화 시 균열이 더 쉽게 일어날 것이다. 예를 들어, 2011년 4 월 19일에 출원된 미국 특허 출원 61/477,056(이는 본 명세서에서 전문이 인용 참조됨)에 개시된 바와 같이, 복수의 별개 코팅층에 평탄화 층(108)을 도포하면, 이러한 균열이 생길 가능성을 감소시킬 수 있고, 최종 층의 표면 거칠기를 감소시킬 수 있다.

[0072] 일 실시예에서, 평탄화 층(108)은 폴리실라잔(polysilazane) 용액으로 기판 홀더(100)를 코팅함으로써 도포되며, 이는 이후 실리콘계 평탄화 층을 형성하도록 경화된다. 관련된 반응은 US 61/477,056에 나타나 있다. 일 실시예에서, 폴리실라잔 용액은 스프레이 기술(spray technique)에 의해 도포된다. 추가적으로 또는

대안적으로, 중착 및/또는 스펀 코팅과 같은 1 이상의 다른 기술들이 사용될 수 있다. 일 실시예에서는, 단지 수성 매질(aqueous medium)을 통해 진행되는 반응이 사용될 수 있다. 일 실시예에서는, 열이 존재하는 수성 매질에서 진행되는 반응이 사용될 수 있다. 각각의 반응들에서는, US 61/477,056에 개시된 바와 같이, 수소, 메틸, 및/또는 플루오로로부터 선택된 1 이상의 작용기들이 존재할 수 있다.

[0073] 평탄화 층은 2011년 10월 14일에 출원된 미국 특허 출원 61/547,600에 개시된 바에 따라 형성될 수 있으며, 이는 본 명세서에서 전문이 인용 참조된다.

[0074] 평탄화 층(108)은 박막 구성요소를 형성하기 위한 금속 또는 다른 층의 신뢰가능한 형성을 위해 충분히 매끈한 표면을 제공한다. 특히, 기판 홀더를 형성하는데 사용되는 몇몇 재료들에 요구될 수 있는 유리 접착 단계가 불필요할 수 있다.

[0075] 도 10의 기판 홀더에서, 박막 스택(200)이 기판 홀더의 본체(100)의 표면(107)에 형성된다. 박막 스택(200)은 평탄화 층(108), 제 1 절연 층(first isolation layer: 201), 전극 층(202) 및 제 2 절연 층(203)을 포함한다. 전압원(500)은, 예를 들어 10 내지 5,000 V 범위의 전위를 전극 층(202)에 인가한다. 벼얼(106) 및 기판이 그려하듯이, 본체(100)가 접지된다(grounded). 전극 층(202)에 인가된 전위에 의해 생성되는 전기장은 기판 홀더에 대해 기판(W)을 클램핑하는 정전력을 유도한다.

[0076] 일 실시예에서, 전극 층(202)은 전기적으로 별개인 2 개(또는 이상)의 부분들로 나뉠 수 있다. 전압원은 전극 층(202)의 2 개의 부분들 사이에, 예를 들어 10 내지 5,000 V 범위의 전위차를 인가한다. 전극 층(202)의 상기 부분들 중 하나는 접지된다. 결과적인 전기장은 유사한 방식으로 정전기 클램핑력을 생성한다.

[0077] 2011년 12월 16일에 출원된 대응 미국 특허 출원 61/576,627에 개시된 바와 같이(이는 본 명세서에서 전문이 인용 참조됨), 1 이상의 센서들 및 여하한의 연계된 벼얼은 전자기 간섭의 핵업(pickup)을 최소화하도록 배치되는 것이 바람직하다.

[0078] 평탄화 층(108)을 포함하는 박막 스택을 이용하는데 따른 어려운 점(difficulty)은, 박막들이 결함을 겪게 될 수 있다는 점이다. 본체(100)의 거친 표면(107)의 튀어나온 돌출부들(Protruding projections)은 박막 스택 내로 튀어나올 수 있다. 튀어나온 돌출부들의 에지들을 평탄화 층(108)으로 완전히 적시는(wet) 것이 어려울 수 있다. 이로 인해, 거친 표면의 튀어나온 돌출부들 위의 절연 층(201)은 다른 영역들에 비해 비교적 얇을 수 있다. 그 결과, 전극(202)에 전하, 특히 정전기 클램프 인가에서와 같은 큰 전하가 인가될 때, 거친 표면의 튀어나온 돌출부를 둘러싸는 영역에서 높은 전하 집중 중심(hight charge concentration center)이 생성될 수 있다. 이는 본체(100)의 재료가 전도성인 때 어려움을 겪게 된다. 이러한 높은 전하 집중 중심은 절연 층(201)에 걸쳐 약 수  $\mu\text{A}$  이상의 누설 전류를 유발할 수 있다. 이는 절연 층(201)을 손상시킬 수 있다.

[0079] 폴리싱은 튀어나온 돌출부들의 전부를 제거하는데 효과적이지 않을 수 있다.

[0080] 일 실시예에서, 앞서 언급된 어려운 점은 박막 스택(200)에 전도성 층을 제공함으로써 해결된다. 전도성 층은, 전도성 층이 위치된 스택의 평면 전반에 걸쳐 실질적으로 균일하게 전하를 분포시키도록 구성된다.

[0081] 도 10 내지 도 13은 전도성 층을 포함시킨 박막 스택의 실시예들의 단면도이다. 전도성 층은 넓은 면적에 걸쳐, 바람직하게는 전도성 층의 평면 전반에 걸쳐 전하를 분포시키는 역할을 한다. 이와 달리, 전하는 거친 표면의 튀어나온 돌출부의 위치에 집중될 수도 있다.

[0082] 일 실시예에서, 전도성 층은 평면에서 패터닝되지 않는다. 본체(100)의 튀어나온 돌출부가 존재할 곳을 예측하는 것이 불가능할 수 있다. 그러므로, 잠재적으로 문제가 될 튀어나온 돌출부들 모두가 전도성 층에 의해 덮일 가능성을 증가시키기 위해 전도성 층을 패터닝하지 않는 것이 바람직할 수 있다. 일 실시예에서, 전도성 층은 평면에서 스택(200)의 실질적으로 전체 영역에 걸쳐 연장된다.

[0083] 도 10의 실시예는 평탄화 층(108), 상기 평탄화 층(108) 상의 제 1 절연 층(201), 제 1 전극(202), 및 상기 제 1 전극(202)을 덮는 제 2 절연 층(203)을 포함하는 박막 스택(200)을 예시한다. 제 2 절연 층은 제 1 전극(202)의 측면 에지들을 포함한다. 전도성 층(108) 및 전극 층(202)은 절연 층, 즉 제 1 절연 층(201)에 의해 분리된다.

[0084] 일 실시예에서, 전극(202)은 평면에서 패터닝된다. 전극(202)은, 다른 곳에 설명되는 바와 같이, 정전기 클램프의 전극을 형성할 수 있고, 및/또는 히터 또는 센서의 일부분을 형성할 수 있다. 도 10 내지 도 13의 실시예들은 하나의 전극(202) 층만을 도시하지만, 도 14에 예시된 바와 같이 1 이상의 전극 층이 제공될 수 있다.

[0085] 평탄화 층(108)은 전도성 평탄화 층이다. 그러므로, 그렇지 않다면 본체(100)로부터 튀어나와 제 1 절연 층(201)으로 연장된 돌출부로 인해 존재할 수 있는 전하 집중이 평면에서 전체 평탄화 층(108) 전반에 걸쳐 분포될 수 있다.

[0086] 평탄화 층(108)은 상기 층이 전도성이라는 것을 제외하고는 앞서 설명된 바와 같은 평탄화 층(108)일 수 있다. 예를 들어 은 입자와 같은 전도성 첨가제를 첨가함으로써 달성될 수 있다. 평탄화 층의 에멀전(emulsion)이 형성될 수 있으며, 이후 예를 들어 본체(100)의 표면 상으로 분무될(sprayed) 수 있다. 평탄화 층(108)은, 상기 층이 본체(100)와 접촉해 있기 때문에, 접지에 연결된 본체(100)에 전기적으로 연결된다.

[0087] 도 10에 도시된 바와 같이, 벼얼들(106) 사이에 기판 홀더(100)의 SiSiC 표면에 박막 스택(200)을 형성하는 상이한 층들의 중착이 가능하다. 상기 층들은 일반적인 순서, 즉 1) 평탄화 층(108), 2) (필요하다면) 제 1 절연 층(201), 3) (예를 들어, 금속 라인 형태의) 전극 층(202), 및 4) 제 2 (최상부) 절연 층(203)의 순서를 따른다. 이러한 얇은 층 스택은 (앞서 설명된 바와 같은) 1 이상의 다른 재료들로 형성된 기판 홀더 또는 1 이상의 유사한 재료들로 형성된 기판 테이블에 형성될 수 있다.

[0088] 평탄화 층(108)은 앞서 설명된 바와 같은 것이 일반적이지만, 다른 형태의 층 및 상기 층을 형성하는 방법들이 사용될 수 있다. 일 실시예에서 평탄화 층은 10  $\mu\text{m}$  이상의 두꺼운 두께를 갖는다. SiSiC 기판 홀더는 벼얼들 사이에 거친 표면[약 4  $\mu\text{m}$ 의 높은 Ra 및 약 43  $\mu\text{m}$ 의 피크 대 밸리(peak to valleys)를 가짐]을 갖는다. 이러한 거칠기는 얇은 금속 전극 라인들(예를 들어, 20 nm 내지 200 nm의 두께)의 패터닝을 허용하지 않을 수 있다. 거칠기를 감소시키기 위해, 적합한 용매에 용해된 폴리머가 거친 SiSiC 표면에 분무된다. 이러한 액체 층은 벼얼들 사이의 EDM-마무리된(EDM finished) 거친 SiSiC에 존재하는 밸리들을 채운다. 액체는, 용매를 증발시키고 매끈한 폴리머 층 또는 평탄화 층(108)을 형성하기 위해 경화된다. 금속 전극 라인들은 이러한 평탄화된 표면 상에서 패터닝될 수 있다. 또한, 평탄화 층이 충분히 두껍고 뾰족한 SiSiC 피크들을 모두 덮는 경우, 이는 SiSiC와 패터닝된 금속 전극 라인들 간에 전기 절연(electrical isolation)을 제공할 수 있다. 평탄화 층은 한번에 모두 분무될 수 있거나, 원하는 층 두께가 달성될 때까지 얇은 층을 분무하고 경화시키며 다음 층을 분무하는 등의 사이클을 반복함으로써 스택으로 측적될 수 있다. 평탄화 층은 BCB(1,3,5-트리메틸 벤젠에 용해된 40 % 비스-벤조사이클로부텐)의 분무된 층으로만 또는 NN 120[디-부틸 에테르 내 20 % 페하이드로폴리실라잔(perhydropolysilazane)]의 분무된 층들과 조합하여 구성될 수 있다.

[0089] 평탄화 층(108)은 금속 전극 패터닝을 촉진하는데(facilitating) 적합하지만, SiSiC 피크들을 모두 덮을 수는 없다. 필요하다면, SiSiC 피크들과 금속 전극 라인들 간에 전기 절연을 제공하기 위해, PE CVD(Plasma Enhanced Chemical Vapor Deposition)  $\text{SiO}_x$ 의 얇은 층(절연 층)이 평탄화 층 위에 중착될 수 있다. 절연 층에 의해 제공되는 전기 절연이 충분하지 않은 경우, 평탄화 층이 2 개의 절연 층 사이에 개재될(sandwiched) 수 있으며, 이러한 스택은 제 1 절연 층(PE CVD  $\text{SiO}_x$ ), 그 다음 평탄화 층 그리고 제 2 절연 층(PE CVD  $\text{SiO}_x$ )의 순서를 따른다. 절연 층(201)은 0.1  $\mu\text{m}$  이상의 두꺼운 두께를 갖는 것이 바람직하다. 절연 층은 10  $\mu\text{m}$  미만의 두께를 갖는 것이 바람직하다. 일 실시예에서, 절연 층은 5  $\mu\text{m}$ 의 두께를 갖는다.

[0090] 절연 층 위에, 1 이상의 금속 라인들(202)이 포토리소그래피 또는 금속 중착 및 하드 마스크를 통한 에칭에 의해 중착된다. 금속 라인(202)은 20  $\mu\text{m}$  이상의 폭을 갖는 것이 바람직하다. 금속 라인의 최대 폭은 그의 기능 및 이용가능한 공간에 의해 결정된다. 금속 라인을 형성하는 다른 방법들이 이용가능하다. 히터 및/또는 센서의 경우, 1 이상의 넓은 금속 라인들(예를 들어, 약 1500  $\mu\text{m}$ )이 가열 요소로서 사용될 수 있고, 좁은 금속 라인(예컨대, 약 100  $\mu\text{m}$ )이 센서 요소로서 사용될 수 있다. 정전기 클램프에 대하여, 서로 약 500  $\mu\text{m}$ 로 분리된 연속적인 금속 막(하지만, 벼얼 최상부들로부터 격리됨)의 2 개의 절반부들(halves)이 정전기 클램프의 포지티브 및 네거티브 요소들(positive and negative elements)을 형성하도록 중착될 수 있다. 금속 라인(202)은 약 20 nm 이상, 바람직하게는 약 40 nm 이상의 층 두께를 갖는 것이 바람직하다. 금속 라인(202)은 약 1  $\mu\text{m}$  이하, 바람직하게는 약 500 nm 미만, 더 바람직하게는 약 200 nm 미만의 층 두께를 갖는 것이 바람직하다.

[0091] 히터 및/또는 센서에 대하여, 패터닝된 금속 라인(202)은 다수의 금속 층들, 예를 들어 티타늄(Ti) 및 백금(Pt)을 가질 수 있다. 일 실시예에서, 10 nm 두께의 티타늄 층은 약 250 두께의 백금 라인에 대해 개선된 접착성을 제공한다. 다수의 층들의 패터닝은 포토레지스트 중착, 금속 막 중착을 위한 PVD 및 리프트-오프 공정(lift-off process)의 조합을 이용하여 달성될 수 있다. 히터에 대해, 넓은 크롬 라인(~ 1500  $\mu\text{m}$ )이 Cr 막 중착(PVD) 및 마스크를 이용하는 선택적 Cr 에칭에 의해 중착될 수 있다. 정전 클램프에 대해, 전극은 알루미늄, 크롬, 또는 여타의 다른 전도성 재료로 구성될 수 있다. 전극은 PVD 또는 스팍터링에 의해 형성될 수 있다.

여하한의 적합한 조합의 이러한 금속들의 합금이 사용될 수 있다.

[0092] 상부로부터 증착된 금속 라인을 전기적으로 절연시키고 상기 금속 라인을 입자 증착, 스크래치 및 산화로부터 보호하는 것이 바람직하다. 그러므로, 최상부 또는 최외측 절연 층이 금속 라인(202)에 증착된다. 히터 또는 센서에 대해, 절연 층은 BCB(1,3,5-트리메틸 벤젠에 용해된 40 % 비스-벤조사이클로부тен) 또는 NN 120(디부틸 에테르 내 20 % 폐하이드로폴리실라잔); 이전에 설명된 바와 같은 SiO<sub>x</sub>; 또는 분무된 층들과 SiO<sub>x</sub>의 조합의 스프레이 코팅에 의해 증착된다. 또한, 정전기 클램프의 경우, 최상부 절연 층은 절연 내력(dielectric strength)을 제공하여, 층 스택과 기판 사이의 캡 및 클램핑 압력이 원하는 값으로 조절될 수 있다. 일 실시예에서, 정전기 클램프를 위한 최상부 절연 층은 BCB, NN 120(또는 이러한 2 개의 분무된 재료들의 조합), SiO<sub>x</sub> 단독(alone), 1 이상의 스프레이 코팅된 폴리머 층들과 SiO<sub>x</sub>의 조합, 또는 파릴렌(CVD) 단독의 스프레이 코팅된 폴리머 층들을 갖거나 이로 구성된다. 최상부 절연 층(203)은 약 0.1 μm 이상, 바람직하게는 약 1 μm 이상의 층 두께를 갖는 것이 바람직하다. 히터 또는 센서에 대해, 최상부 절연 층(203)은 약 10 μm 미만, 바람직하게는 약 3 μm 미만의 층 두께를 갖는 것이 바람직하다. 정전기 클램프에 대해, 최상부 절연 층은 약 100 μm 미만, 바람직하게는 약 20 μm 미만의 층 두께를 갖는 것이 바람직하다. 일 실시예에서, 이러한 두께는 약 10 내지 약 60 μm 범위에 있다.

[0093] 표 1은 박막 스택을 축적하기 위해 층마다의 적합한 재료들의 예시를 나타낸다. 각각의 층은 나열된 재료들 중 하나 또는 2 이상의 재료들의 조합으로 형성될 수 있다. 도포 방법은 팔호 안에 표시되어 있다.

표 1

| 도포 층      | 1. 히터 단독                                                                                             | 2. 센서 & 히터                                                                                             | 3. 클램프                                                                                                            |

|-----------|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| 최하부<br>절연 | BCB (분무)<br>CAG 37 (분무)<br>NN 120 (분무)<br>SiO <sub>x</sub> ,(PVD/CVD/PECV<br>D/ 스퍼터링)<br>폴리이미드 (분무)  | BCB (분무)<br>CAG 37 (분무)<br>NN 120 (분무)<br>SiO <sub>x</sub> ,<br>(PVD/CVD/PECVD/<br>스퍼터링)<br>폴리이미드 (분무) | BCB (분무)<br>CAG 37 (분무)<br>NN 120 (분무)<br>SiO <sub>x</sub><br>(PVD/CVD/PECVD/<br>스퍼터링)<br>파릴렌 (CVD)<br>폴리이미드 (분무) |

| 금속 층      | 크롬<br>(PVD/CVD/ 스퍼터링)                                                                                | 백금<br>(PVD/CVD/ 스퍼터링<br>리프트-오프)                                                                        | 크롬,<br>알루미늄<br>(PVD/CVD/ 스퍼터링)                                                                                    |

| 최상부<br>절연 | BCB (분무)<br>CAG 37 (분무)<br>NN 120 (분무)<br>SiO <sub>x</sub><br>(PVD/CVD/PECVD/<br>스퍼터링)<br>폴리이미드 (분무) | BCB (분무)<br>CAG 37 (분무)<br>NN 120 (분무)<br>SiO <sub>x</sub><br>(PVD/CVD/PECVD/<br>스퍼터링)<br>폴리이미드 (분무)   | BCB (분무)<br>CAG 37 (분무)<br>NN 120 (분무)<br>SiO <sub>x</sub><br>(PVD/CVD/PECVD/<br>스퍼터링)<br>파릴렌 (CVD)<br>폴리이미드 (분무) |

[0095] 표 2는 도포를 위한 층마다의 특정 기능 및 요건들의 예시를 나타낸다.

[0097] 표 2

| 도포 층   | 1. 히터 단독                                                                                                    | 2. 센서 & 히터                                                                                                              | 3. 클램프                                                                                                      |

|--------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| 최하부 절연 | <ul style="list-style-type: none"> <li>- 적절한 전기 절연</li> <li>- 층에 걸쳐 낮은 온도 차이</li> <li>- 짧은 반응 시간</li> </ul> | <ul style="list-style-type: none"> <li>- 높은 전기 절연 (센서 분해능의 경우)</li> <li>- 층에 걸쳐 낮은 온도 차이</li> <li>- 짧은 반응 시간</li> </ul> | <ul style="list-style-type: none"> <li>- 높은 절연 내력</li> <li>- 높은 체적 저항률</li> <li>- 층에 걸쳐 낮은 온도 차이</li> </ul> |

| 금속 층   | <ul style="list-style-type: none"> <li>- 히터 전력</li> </ul>                                                   | <ul style="list-style-type: none"> <li>- 센서 민감도</li> <li>- 센서 안정성</li> <li>- 히터 전력</li> </ul>                           | <ul style="list-style-type: none"> <li>- 높은 전압 요건</li> <li>(전극 레이아웃)</li> </ul>                             |

|        |       |       |                                                                                                             |

|--------|-------|-------|-------------------------------------------------------------------------------------------------------------|

| 최상부 절연 | - 캡슐화 | - 캡슐화 | <ul style="list-style-type: none"> <li>- 높은 절연 내력</li> <li>- 높은 체적 저항률</li> <li>- 층에 걸쳐 낮은 온도 차이</li> </ul> |

|--------|-------|-------|-------------------------------------------------------------------------------------------------------------|

[0098]

[0099]

박막 기술은 오버레이 개선 및 히터 및/또는 센서 개발을 위한 비용 효율적인 솔루션을 제공한다. 금속 패턴 디자인은 (마스크 디자인을 수정함으로써) 쉽게 수정될 수 있다. 백금(Pt) 금속 층이 사용되는 경우, Pt 층의 접착성을 개선시키기 위해 티타늄 접착 층이 먼저 도포될 수 있다. 정전기 클램프에 대해, 낮은 저항을 갖는 여하한의 적합한 금속이 사용될 수 있다.

[0100]

1 이상의 유전 층들(dielectric layers)은 스프레이 코팅, 스판 코팅 및/또는 PE CVD 기술들에 의해 증착될 수 있다. 스프레이 코팅은 BCB 및/또는 NN 120 층과 같은 폴리머계 층(유기 용매에 용해됨)을 증착하는데 특히 적합하다. 하지만, 너무 두꺼운 층이 증착되는 경우, 먼저 분무된 층은 (국부적 불순물로 인한) 핀-홀(pin-hole) 및/또는 (가장 유력하게는 층에 유도된 응력으로 인한) 균열과 같은 표면 결함을 겪게 될 수 있다. 상이한 증착 공정들을 조합함으로써 표면 결함(surface imperfection)의 영향을 감소시킬 수 있다. 일 실시예에서는, 잉크젯 또는 버블젯 프린팅 기술(inkjet or bubblejet printing technique)을 이용하여 층이 도포될 수 있다. 이는 층 두께의 국부적 제어를 허용하며, 이는 기판 홀더의 표면 거칠기 또는 표면 윤곽(surface contour)의 국부적 변동을 보정하는데 유용할 수 있다. 또한, 이러한 기술들은 전도성 잉크를 이용하여 전도성 층의 패터닝을 가능하게 한다. 하나의 층의 결함이 또 다른 층에 의해 바로잡힐(cured) 수 있음에 따라, 상이한 재료들 및/또는 층 형성 기술들의 조합이 바람직 할 수 있다.

[0101]

절연 층들(201, 203)은 앞서 설명된 바와 같을 수 있으며, 예를 들어 1 이상의 층들로 형성될 수 있다. 일 실시예에서, 제 1 절연 층(201)은 5  $\mu\text{m}$ 의 SiO<sub>2</sub>, 20  $\mu\text{m}$ 의 BCB, 및 5  $\mu\text{m}$ 의 SiO<sub>2</sub> 층으로 이루어진다. 일 실시예에서, SiO<sub>2</sub>는 PECVD에 의해 도포된다. 일 실시예에서, 제 2 (최상부) 절연 층(203)은, 예를 들어 SiO<sub>2</sub> 또는 BCB를 포함할 수 있다. 일 실시예에서, 평탄화 층(108)은 10  $\mu\text{m}$ 의 두께를 가지며, 예를 들어 BCB를 포함한다.

[0102]

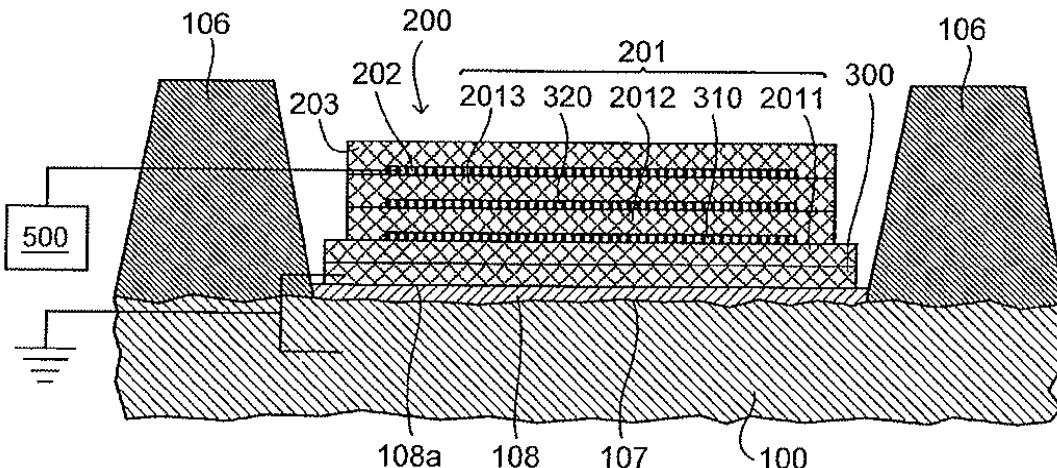

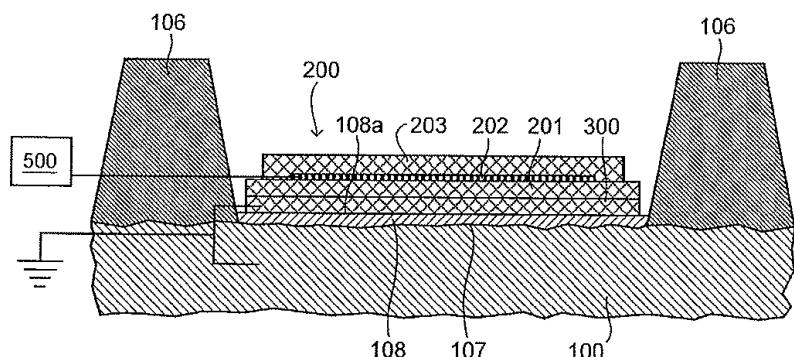

도 11의 실시예는 아래에 설명되는 것을 제외하고는 도 10과 동일하다. 평탄화 층(108)은 전기 전도성일 수 있거나 전기 전도성이 아닐 수 있다. 전도성 층(300)은 평탄화 층(108) 위에 그리고 제 1 절연 층(201) 아래에 제공된다. 전기 전도성 층(300)은 금속, 예를 들어 크롬, 알루미늄, 백금, 및/또는 상기의 금속들 중 2 이상의 합금일 수 있다. 일 실시예에서, 평탄화 층(108)은 이를테면 10  $\mu\text{m}$  두께의 비-전도성 폴리머 층(예를 들어, BCB)이고, 전도성 층은 얇은 금속 층(이를테면, 200 nm의 크롬)이다. 얇은 금속 층은, 도 12에서와 같이 본체 (100)와 함께 접지에 연결될 수 있거나 없다. 일 실시예에서, 전도성 층은 두께가 20 nm 내지 1  $\mu\text{m}$ 이다. 전도성 층의 이러한 두께는 박막 기술을 이용하여 증착하기가 비교적 쉬우며[이는 전극(202)과 거의 동일한 두께 범

위임], 전하를 균일하게 분포시키기에 충분히 두껍다. 일 실시예에서, 평탄화 층(108)이 전도성이 아닌 경우, 전도성 층(300)은 어디에도 전기적으로 연결되지 않으며, 플로팅 전극(floating electrode)이다. 플로팅 전극은 층 전반에 걸쳐 전하를 실질적으로 균일하게 분포시킬 것이며, 절연 층(201)을 통한 전하의 집중이 존재하지 않을 것이기 때문에 전하 전파를 회피할 것이다. 물론, 뛰어나온 돌출부가 존재할 수 있으며, 플로팅 전극은 양으로 하전된 전극(202)과 접지된 본체(100) 사이의 중간 전압으로서 양 전하를 분포시킬 것이다. 전도성 층(300)의 플로팅 전극은 스택 내 어디에도 위치될 수 있다. 일 실시예에서는, 도 13을 참조하여 설명되는 바와 같이, 전도성 층(300) 형태의 1 이상의 플로팅 전극이 존재한다. 예를 들어, 1 이상의 플로팅 전극들은 제 1 절연 층(201)을 포함하는 층들 사이에 위치될 수 있다.

[0103] 도 12는 아래에 설명되는 것을 제외하고는 도 11의 실시예와 동일한 일 실시예를 예시한다. 전도성 층(300)은 본체(100)에 전기적으로 연결된다. 그러므로, 전기 전도성 층(300)은 접지에 연결되며, 도 10의 전도성 평탄화 층(108)과 동일한 방식으로 작동한다.

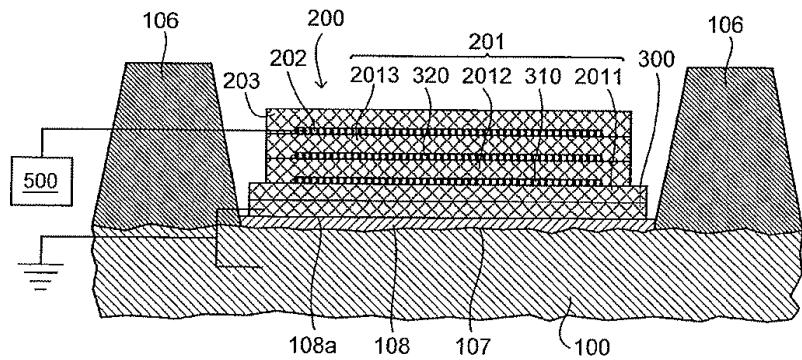

[0104] 도 13은 도 10 내지 도 12의 실시예들의 조합인 일 실시예를 예시한다. 특징부들의 여하한의 조합이 존재할 수 있다. 도 13에 예시된 바와 같이, 전도성 평탄화 층(108) 및 접지된 전도성 층(300)을 포함해, 모든 특징부들이 존재한다. 일 실시예에서, 평탄화 층(108)은 10  $\mu\text{m}$ 의 BCB이다. 제 1 절연 층(201)은 3 개의 절연 층들(2011, 2012, 2013), 예를 들어 5  $\mu\text{m}$  SiO<sub>2</sub>의 제 1 층(2011), 20  $\mu\text{m}$  BCB의 제 2 층(2012), 및 5  $\mu\text{m}$  BCB의 제 3 층(2013)으로 이루어진다. 제 1 및 제 2 층들(2011 및 2012) 사이에, 제 1 플로팅 전극(310)이 제공된다. 플로팅 전극(310)은 도 11의 플로팅 전극(300)과 동일하다. 제 2 플로팅 전극(320)은 제 1 절연 층(201)의 제 2 및 제 3 층들(2012 및 2013) 사이에 제공된다. 일 실시예에서, 플로팅 전극(310, 320)은 그들의 인접한 층들(2011, 2012, 2013) 사이에 캡슐화된다(encapsulated). 본 발명의 일 실시예는, 다음의 어느 특징부들 중 1 이상: 전도성 평탄화 층(108), 전도성 층(300), 제 1 플로팅 전극(310), 및/또는 제 2 플로팅 전극(320)이 존재하는 한 수행될 것이다. 일 실시예에서는, 접지된 전도성 층(300)이 존재하지 않는다. 일 실시예에서는, 베얼(106)이 본체(100)에 증착되며, 본체(100)는 베얼(106)과 상이한 재료로 구성될 수 있다. 이 실시예에서는, 2012년 4월 9일에 출원된 미국 특허 출원 61/621,648에 개시된 바와 같이(이는 본 명세서에서 전문이 인용 참조됨), 본체가 충분히 매끈할 수 있어, 평탄화 층(108)이 요구되지 않는다. 하지만, 적어도 하나의 플로팅 전극(310, 320), 및/또는 접지된 또는 비-접지된 전도성 층(300)이 여전히 요구될 수 있다.

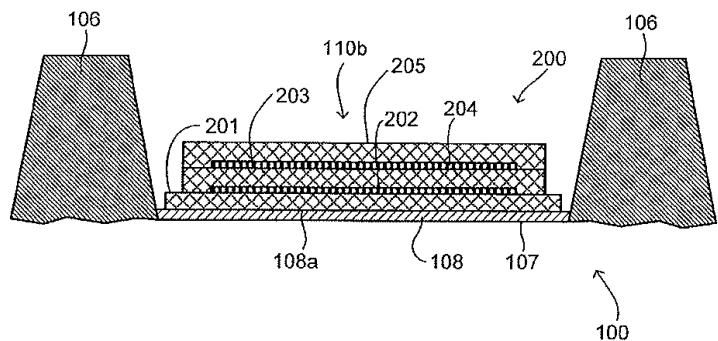

[0105] 도 14에 도시된 박막 스택(110b)은 아래에 설명되는 것을 제외하고는 도 10과 동일하다. 상기 스택(110b)은 순서대로 베이스 층(100), 제 1 절연 층(201), 제 1 금속 층(예를 들어, 금속 라인들: 202), 제 2 절연 층(203), 제 2 금속 층(예를 들어, 금속 라인들: 204) 및 제 3 절연 층(205)을 포함한다. 이러한 층들의 각각은 본 명세서에 설명된 바와 같은 적합한 방법에 의해 형성될 수 있다. 또한, 1 이상의 추가 금속 층들 및 1 이상의 추가 절연 층들이 제공될 수 있다. 이 실시예에서, 2 이상의 스택된 금속 층들의 사용은 2 이상의 스택된 구성요소들, 예를 들어 센서들의 형성을 허용한다. 스택된 센서들은 잡음으로부터 증가된 격리를 제공할 수 있다. 일 실시예에서, 1 이상의 금속 층들은 또 다른 층의 1 이상의 신호 라인들에 대한 차폐부(shielding)로서 작용할 수 있다.

[0106] 도 15에 도시된 박막 스택(110c)은 아래에 설명되는 것을 제외하고는 도 10과 동일하다. 상기 스택(110c)은 전자 또는 전기 구성요소들(206, 207)의 양측에 제 1 절연 층(201) 및 제 2 절연 층(203)을 포함한다. 다시 말해, 상기 구성요소들은 제 1 및 제 2 절연 층들 사이에 개재된다. 다수의 구성요소들이 기판 상의 단일 층에 형성될 수 있다. 일 실시예에서, 각각의 구성요소들(206, 207)은 복수의 층들에 의해 형성된다. 예를 들어, 구성요소의 연속 층들은 금속-비정질 실리콘-금속(metal-amorphous silicon-metal)으로 구성될 수 있다. 이러한 실시예에서, 1 이상의 구성요소들(206, 207)은 트랜지스터 또는 다른 논리 디바이스를 형성한다. 이러한 논리 디바이스는, 각각의 히터에 개별적인 연결을 필요로 하지 않고 기판 홀더의 표면에 걸쳐 배치된 히터들의 어레이를 제어하는데 사용될 수 있다. 트랜지스터는 워드 및 비트 라인들의 교차점에 배치될 수 있으며, 각각은 액티브 매트릭스(active matrix)를 형성하기 위해 연계된 히터에 연결될 수 있다.

[0107] 정전기 클램프를 갖는 일 실시예에서는, 박막 정전기 클램프와 기판 사이의 간격이 양호하게 제어되고 일관성을 가져(consistent), 정전기 클램프에 의해 인가되는 클램핑력이 (정전기 클램프와 기판 사이의 간격이 다소 덜 제어된 경우에 인가될 힘에 비해) 더 일관성을 갖게 된다. 이는, 기판에 인가되는 클램핑력의 불균일성이 회피되어야 하기 때문에 유리하다. 이는 클램핑 힘의 불균일성이 기판에 왜곡을 초래할 수 있기 때문이다.

[0108] 소위, 핀홀 또는 균열, 예컨대 전위(dislocation)로도 알려져 있는 박막의 결정질 구조의 어긋남(break)이 박막 층, 예컨대 정전기 클램프의 절연 층에 생길 수 있다. 이러한 단층(fault)은 박막 스택의 일 구성요소의 감소

된 성능 또는 고장, 예를 들어 빈약한 격리(poor isolation)를 유발할 수 있다. 일 실시예에서, 이는 절연 층을 함께 스택되는 여러 개의 얇은 층들로 제공함으로써 유리하게 회피될 수 있어, 특정 절연 층의 편향 또는 균열은 다음 절연 층이 증착될 때 적어도 부분적으로 채워지게 된다. 하나의 층의 단층이 또 다른 층의 단층과 중첩될 확률은 적다.

[0109] 기판 테이블에 형성될 전자 또는 전기 구성요소는, 예를 들어 전극, 저항성 히터 및/또는 센서, 예컨대 (비-제한적인 목록으로) 변형 센서(strain sensor), 자기 센서, 압력 센서, 용량성 센서 또는 온도 센서를 포함할 수 있다. 기판 홀더 및/또는 기판의 온도를 국부적으로 제어 및/또는 모니터링하여 기판 홀더 또는 기판의 원하는 온도 변동 및 응력을 유도하거나 원하지 않는 온도 변동 및 응력을 감소시키기 위해 히터 및 센서가 사용될 수 있다. 바람직하게는, 히터 및 센서는 서로 동일한 영역에, 동일한 영역 주위에 그리고 동일한 영역 위에 형성된다. 기판의 국부적 팽창 또는 수축으로 인한 오버레이 오차와 같은 이미징 오차를 감소 또는 제거하기 위해 기판의 온도 및/또는 응력을 제어하는 것이 바람직하다. 예를 들어, 침지 리소그래피 장치에서는 기판에 잔존하는 침지 액체(예를 들어, 물)의 증발로 인해, 국부적인 냉각이 야기될 수 있고, 액체가 위치된 표면에 열 부하를 인가할 수 있으며, 이에 따라 기판의 수축을 초래할 수 있다. 반대로, 노광 시 투영 빔에 의해 기판으로 전달된 에너지는 상당한 열을 초래할 수 있으며, 따라서 기판의 팽창을 유발할 수 있다.

[0110] 일 실시예에서, 형성될 구성요소는 정전기 클램프용 전극이다. 정전기 클램핑에서, 기판 테이블 및/또는 기판 홀더에 제공된 전극은 높은 전위, 예를 들어 10 내지 5,000 V로 상승된다. 기판은 접지되거나 플로팅(floating)될 수 있다. 전극에 의해 생성되는 전기장의 정전기력은 기판을 기판 테이블 및/또는 홀더로 끌어당겨 클램핑력을 제공한다. 이는 아래에 자세히 설명하기로 한다.

[0111] 기판 홀더 상의 전기 또는 전자 구성요소를 전압원(편의상 도시되지 않음)에 연결하기 위해 1 이상의 전기 연결들이 제공될 수 있다. 이러한 구성요소가 정전기 클램프인 경우, 기판 상의 전극은 전압원에 대해 전기적 연결을 갖는다. 상기 구성요소는 기판 지지체의 최상부 표면에 존재할 수 있다. 2011년 11월 3일에 출원된 미국 특허 출원 61/555,359(이는 본 명세서에서 전문이 인용 참조됨)에 개시된 바와 같이, 전기적 연결의 적어도 일부분이 기판 지지체의 본체를 통과할 수 있다.

[0112] 일 실시예에서는, 기판 홀더(100) 및 기판(W)에 원하는 양의 열을 제공하여 기판(W)의 온도를 제어하기 위해 1 이상의 국부화된 히터들(101)이 제어기에 의해 제어된다. 1 이상의 온도 센서들(102)이 제어기에 연결되며, 제어기는 기판 홀더(100) 및/또는 기판(W)의 온도를 모니터링한다. 1 이상의 히터들 및 온도 센서들을 이용하여 기판의 온도를 국부적으로 제어하는 구성은, 동시계류중인 미국 특허 출원 공개공보 US 2012-0013865에 개시되어 있으며, 이는 본 명세서에서 전문이 인용 참조된다. 본 명세서에 설명된 구성들은 본 명세서에 설명된 바와 같은 저항성 히터 및 온도 센서를 이용하도록 수정될 수 있다.

[0113] 이상, 다층 구조로서 통합된 방식(unitary manner)으로 1 이상의 벼얼, 센서, 히터 및/또는 정전기 클램프를 형성하는데 사용될 수 있는 특정한 방법들이 설명되었지만, 여타의 적합한 방법이 사용될 수도 있다. 본 발명의 일 실시예에서, 박막 스택은 기판 홀더의 일 측에만 제공된다. 일 실시예에서, 박막 스택들은 기판 홀더의 양 측에 제공된다. 일 실시예에서, 벼얼은 기판 홀더의 양측에 제공된다. 벼얼이 박막 스택을 갖지 않는 기판 홀더의 측에 제공되는 경우, 그 측에 벼얼을 형성하기 위해 여하한의 편리한 방법이 사용될 수 있다. 이러한 방법은 앞서 설명된 것들뿐만 아니라, 본체로부터 재료의 제거를 수반하는 기계가공과 같은 1 이상의 다른 방법들 중 1 이상을 포함한다. 1 이상의 층들의 증착은, 플라즈마 향상 화학적 기상 증착(PECVD), 화학적 기상 증착(CVD), 물리적 기상 증착(PVD), 및/또는 스퍼터링에 의해 달성될 수 있다. 증착에 사용되는 방법은 증착되는 재료(들)에 따라 달라진다. 증착에 의해 얻어지는 두께 변동은 5 %보다 작을 수 있다.

[0114] 종래의 (DUV) 리소그래피 장치(예컨대, 침지 리소그래피 장치)에서 사용하기 위한 기판 홀더에는 1 이상의 박막 온도 센서들 및/또는 박막 히터들이 제공되는 것이 바람직하다.

[0115] EUV 리소그래피 장치에서 사용하기 위한 기판 홀더에는 박막 정전기 클램프 그리고 선택적으로는 1 이상의 박막 온도 센서들 및/또는 박막 히터들이 제공되는 것이 바람직하다.

[0116] 이해되는 바와 같이, 앞서 설명된 특징부들 중 어떠한 것도 여타의 특징부와 함께 사용될 수 있으며, 본 출원에서 다루어지는 것들은 명시적으로 설명된 이러한 조합들뿐만은 아니다. 예를 들어 도 14 및 도 15에 예시되고 앞서 설명된 것과 같은 구조체는 도 11 내지 도 13 중 어느 하나의 제 1 절연 층(201) 및/또는 전도성 층(300) 및/또는 평탄화 층(108) 위에 배치될 수 있다.

[0117] 본 명세서에서는, IC 제조에 있어서 리소그래피 장치의 특정 사용예에 대하여 언급되지만, 본 명세서에 서술된

리소그래피 장치는 집적 광학 시스템, 자기 도메인 메모리용 안내 및 검출 패턴, 평판 디스플레이(flat-panel display), 액정 디스플레이(LCD), 박막 자기 헤드 등의 제조와 같이, 마이크로스케일, 또는 심지어 나노스케일 피처들을 갖는 구성요소들을 제조하는데 있어서 다른 적용예들을 가질 수도 있음을 이해하여야 한다. 당업자라면, 이러한 대안적인 적용예와 관련하여, 본 명세서의 "웨이퍼" 또는 "다이"라는 용어의 어떠한 사용도 각각 "기판" 또는 "타겟부"라는 좀 더 일반적인 용어와 동의어로 간주될 수도 있음을 이해할 것이다. 본 명세서에서 언급되는 기판은 노광 전후에, 예를 들어 트랙(전형적으로, 기판에 레지스트 층을 도포하고 노광된 레지스트를 현상하는 틀), 메트롤로지 틀 및/또는 검사 틀에서 처리될 수 있다. 적용가능하다면, 이러한 기판 처리 틀과 다른 기판 처리 틀에 본 명세서의 기재 내용이 적용될 수 있다. 또한, 예를 들어 다층 IC를 생성하기 위하여 기판이 한번 이상 처리될 수 있으므로, 본 명세서에 사용되는 기판이라는 용어는 이미 여러번 처리된 층들을 포함한 기판을 청할 수도 있다.

[0118] 본 명세서에서 사용된 "방사선" 및 "빔"이라는 용어는 (예를 들어, 약 365, 248, 193, 157 또는 126 nm, 또는 그 정도의 파장을 갖는) 자외(UV) 방사선을 포함하는 모든 형태의 전자기 방사선을 포괄한다.

[0119] 본 명세서가 허용하는 "렌즈"라는 용어는, 굴절 및 반사 광학 구성요소들을 포함하는 다양한 형태의 광학 구성요소들 중 어느 하나 또는 이의 조합으로 언급될 수 있다.

[0120] 이상, 본 발명의 특정 실시예가 설명되었지만, 본 발명은 적어도 본 명세서에 설명된 바와 같은 장치의 작동 방법의 형태로, 설명된 것과 다르게 실시될 수 있다는 것을 이해할 것이다. 예를 들어, 본 발명의 실시예들은, 적어도 장치의 작동 방법의 형태로, 앞서 개시된 바와 같은 장치의 작동 방법을 구현하는 기계-판독가능한 명령어의 1 이상의 시퀀스를 포함하는 1 이상의 컴퓨터 프로그램, 또는 이러한 컴퓨터 프로그램이 저장되어 있는 데 이터 저장 매체(예를 들어, 반도체 메모리, 자기 또는 광학 디스크)의 형태를 취할 수 있다. 또한, 기계 판독 가능한 명령어는 2 이상의 컴퓨터 프로그램들에서 구현될 수 있다. 2 이상의 컴퓨터 프로그램들은 1 이상의 상이한 메모리 및/또는 데이터 저장 매체에 저장될 수 있다.

[0121] 1 이상의 컴퓨터 프로그램이 리소그래피 장치의 적어도 하나의 구성요소 내에 위치된 1 이상의 컴퓨터 프로세서에 의해 판독될 때, 본 명세서에 설명된 여하한의 제어기들은 각각 또는 조합하여 작동할 수 있다. 제어기들은 각각 또는 조합하여 신호들을 수신하고, 처리하며, 보내는 여하한의 적합한 구성을 가질 수 있다. 1 이상의 다중 프로세서들이 제어기들 중 적어도 하나와 통신하도록 구성된다. 예를 들어, 각각의 제어기는 앞서 설명된 바와 같은 장치의 작동 방법을 위해 기계-판독가능한 명령어들을 포함하는 컴퓨터 프로그램들을 실행하는 1 이상의 프로세서들을 포함할 수 있다. 또한, 제어기들은 이러한 컴퓨터 프로그램들을 저장하는 데이터 저장 매체, 및/또는 이러한 매체를 수용하는 하드웨어를 포함할 수 있다. 따라서, 제어기(들)는 1 이상의 컴퓨터 프로그램의 기계-판독가능한 명령어들에 따라 작동할 수 있다.

[0122] 본 발명의 일 실시예는 300 mm 또는 450 mm 또는 여하한의 다른 크기의 폭(예를 들면, 직경)을 갖는 기판에 적용될 수 있다.

[0123] 본 발명의 1 이상의 실시예들은 여하한의 침지 리소그래피 장치, 특히 배타적인 것은 아니지만, 앞서 언급된 타입들에 적용될 수 있으며, 침지 액체가 배스의 형태로 기판의 국부화된 표면 영역 상에만 제공되는지 또는 기판 및/또는 기판 테이블 상에 한정되지 않는지에 따라 적용될 수 있다. 한정되지 않는 구성에서는, 기판 및/또는 기판 테이블의 덮이지 않은 전체 표면이 실질적으로 습식 상태가 되도록, 기판 및/또는 기판 테이블의 표면에 걸쳐 침지 액체가 유동할 수 있다. 이러한 한정되지 않은 침지 시스템에서, 액체 공급 시스템은 침지 액체를 한정하지 않을 수 있거나, 침지 액체의 일부분을 한정하지만, 실질적으로 침지 액체를 완전하게 한정하지 않을 수도 있다.

[0124] 본 명세서에서 고려되는 액체 공급 시스템은 폭넓게 해석되어야 한다. 소정 실시예들에서, 이는 투영 시스템과 기판 및/또는 기판 테이블 사이의 공간에 액체를 제공하는 메커니즘 또는 구조체들의 조합일 수 있다. 이는 1 이상의 구조체, 1 이상의 액체 유입구, 1 이상의 가스 유입구, 1 이상의 가스 유출구, 및/또는 상기 공간에 액체를 제공하는 1 이상의 액체 유출구의 조합을 포함할 수 있다. 일 실시예에서, 상기 공간의 표면은 기판 및/또는 기판 테이블의 일부분일 수 있거나, 상기 공간의 표면은 기판 및/또는 기판 테이블의 표면을 완전히 덮을 수 있거나, 상기 공간은 기판 및/또는 기판 테이블을 에워쌀 수 있다. 액체 공급 시스템은, 선택적으로 위치, 양, 질, 형상, 유속 또는 액체의 여타의 특징들을 제어하는 1 이상의 요소들을 더 포함할 수 있다.

[0125] 본 발명의 제 1 실시형태에서는, 리소그래피에 사용하기 위한 기판 홀더가 제공된다. 상기 기판 홀더는 본체, 복수의 벼얼 및 박막 스택을 포함한다. 본체는 표면을 갖는다. 복수의 벼얼은 표면으로부터 돌출되며, 기판을

지지하기 위한 단부면들을 갖는다. 박막 스택은 본체 표면 상에 놓이며, 전기 구성요소를 형성하고, 상기 박막 스택은 상기 스택의 평면 전반에 걸쳐 전하를 실질적으로 균일하게 분포시키도록 구성된 전도성 층을 포함하며, 이 평면에 전도성 층이 위치된다.

[0126] 전도성 층은 평면에서 패터닝되지 않을 수 있다. 전도성 층은 평면에서 스택의 실질적으로 전체 영역에 걸쳐 연장될 수 있다. 전도성 층은 금속 층일 수 있다. 이러한 금속은 Cr, Al, Pt 및/또는 이 금속들 중 2 이상의 합금으로부터 선택된 적어도 하나의 금속일 수 있다. 전도성 층은 두께가 20 nm 내지 1  $\mu\text{m}$ 일 수 있다.

[0127] 전도성 층은 본체 표면에 형성되는 평탄화 층일 수 있다. 평탄화 층은 전도성 첨가제를 포함할 수 있다. 박막 스택은 본체 표면에 형성되는 평탄화 층을 포함할 수 있다. 평탄화 층은 약 1.5  $\mu\text{m}$  미만, 약 1.0  $\mu\text{m}$  미만, 또는 약 0.5  $\mu\text{m}$  미만의 표면 거칠기(Ra)를 가질 수 있다. 평탄화 층은 실리콘 재료로 형성될 수 있다. 평탄화 층은 실리콘 산화물 또는 실리콘질화물-계 재료로 형성될 수 있다. 평탄화 층은 수소, 메틸, 플루오로, 비닐 등으로 구성된 그룹으로부터 선택된 적어도 하나의 작용기를 포함할 수 있다. 평탄화 층은 벤조사이클로부텐, 페하이드로폴리실라잔,  $\text{SiO}_2$ , 파릴렌, 폴리아미드, 및/또는 이의 2 이상의 조합으로 구성된 그룹으로부터 선택된 적어도 하나의 재료를 포함할 수 있다.

[0128] 적어도 전도성 층에 인접한 층은 절연 층일 수 있다. 전도성 층은 본체에 전기적으로 연결될 수 있다. 전도성 층은 플로팅 전극일 수 있다. 박막 스택은 전극 층인 추가 전도성 층을 더 포함할 수 있다. 전극 층은 평면에서 패터닝될 수 있다. 전극 층 및 전도성 층은 절연 층에 의해 분리될 수 있다. 상기 스택은 전극 층 위에 제 공되는 최상부 절연 층을 더 포함할 수 있다. 절연 층은 약 0.1  $\mu\text{m}$  내지 약 100  $\mu\text{m}$  범위의 두께를 가질 수 있다. 절연 층은 약 0.1  $\mu\text{m}$  내지 약 10  $\mu\text{m}$ , 바람직하게는 약 1  $\mu\text{m}$  내지 약 3  $\mu\text{m}$  범위의 두께를 가질 수 있다. 절연 층은 벤조사이클로부텐, 페하이드로폴리실라잔,  $\text{SiO}_x$ , 파릴렌, 폴리아미드, 및/또는 이의 2 이상의 조합으로 구성된 그룹으로부터 선택된 적어도 하나의 재료로 형성될 수 있다. 절연 층은 약 20  $\mu\text{m}$  내지 약 100  $\mu\text{m}$ , 바람직하게는 약 40  $\mu\text{m}$  내지 약 60  $\mu\text{m}$  범위의 두께를 가질 수 있다. 상기 전극은 사용 시 정전기 클램프의 전극일 수 있다.

[0129] 상기 본체는  $\text{SiC}$ (실리콘 카바이드),  $\text{SiSiC}$ (실리코나이즈드 실리콘 카바이드),  $\text{Si}_3\text{N}_4$ (실리콘 나이트라이드), 석영, 및/또는 Zerodur<sup>TM</sup>으로 구성된 그룹으로부터 선택된 적어도 하나의 재료로 형성될 수 있다.

[0130] 본 발명의 제 2 실시형태에서는, 지지 구조체, 투영 시스템 및 기판 홀더를 포함하는 리소그래피 장치가 제공된다. 기판 홀더는 패터닝 디바이스를 지지하도록 구성된다. 투영 시스템은 기판 상으로 패터닝 디바이스에 의해 패터닝된 빔을 투영하도록 배치된다. 기판 홀더는 기판을 유지하도록 배치되며, 기판 홀더는 본 발명의 제 1 실시형태에 따른다.

[0131] 리소그래피 장치는 기판 테이블을 더 포함할 수 있으며, 기판 홀더는 기판 테이블 내로 통합된다. 상기 장치는 EUV 투영 장치일 수 있다.

[0132] 본 발명의 제 3 실시형태에서는, 리소그래피 장치를 이용하는 디바이스 제조 방법이 제공되며, 상기 방법은, 기판 홀더 내에 또는 기판 홀더 상에 기판을 유지하면서, 기판 상으로 패터닝 디바이스에 의해 패터닝된 빔을 투영하는 단계를 포함하고, 상기 기판 홀더는 표면을 갖는 본체, 상기 표면으로부터 돌출되고 기판을 지지하기 위한 단부면들을 갖는 복수의 벼얼, 및 전기 구성요소를 형성하는 본체 표면의 박막 스택을 포함하고, 상기 박막 스택은 상기 스택의 평면 전반에 걸쳐 전하를 실질적으로 균일하게 분포시키도록 구성된 전도성 층을 포함하며, 이 평면에 전도성 층이 위치된다.

[0133] 본 발명의 제 4 실시형태에서는, 리소그래피 장치에 사용하기 위한 기판 홀더가 제공되며, 상기 기판 홀더는 표면을 갖는 본체, 상기 표면으로부터 돌출되고 기판을 지지하기 위한 단부면들을 갖는 복수의 벼얼, 및 전기 구성요소를 형성하는 본체 표면의 박막 스택을 포함하고, 상기 박막 스택은 평면에서 상기 스택의 실질적으로 전체 영역에 걸쳐 연장되는 전도성 층을 포함한다.

[0134] 상기 서술내용은 예시를 위한 것이지, 제한하려는 것이 아니다. 따라서, 당업자라면 아래에 설명되는 청구항들의 범위를 벗어나지 않고 서술된 본 발명에 대한 변형예가 행해질 수도 있음을 이해할 것이다.

## 도면

## 도면1

## 도면2

## 도면3

도면4

도면5

도면6

도면7

도면8

도면9

도면10

도면11

도면12

도면13

도면14

도면15