(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2018년06월12일

(11) 등록번호 10-1851614

(24) 등록일자 2018년04월18일

(51) 국제특허분류(Int. Cl.)

*G06F 1/04* (2006.01) *H03K 5/19* (2006.01)

(21) 출원번호 10-2011-0133195

(22) 출원일자 2011년12월12일

심사청구일자 2016년09월09일

(65) 공개번호 10-2013-00666398

(43) 공개일자 2013년06월20일

(56) 선행기술조사문헌

JP2005285093 A\*

JP2005339310 A\*

\*는 심사관에 의하여 인용된 문헌

(73) 특허권자

삼성전자주식회사

경기도 수원시 영통구 삼성로 129 (매탄동)

(72) 발명자

김동근

서울특별시 서초구 효령로74길 57 101동 902호 (서초동, 동원베네스트)

권순철

경기도 용인시 기흥구 강남동로 54 701동 1702호 (구갈동, 강남마을7단지계룡리슈빌아파트)

(뒷면에 계속)

(74) 대리인

한지희, 윤재석, 권영규

심사관 : 구본재

전체 청구항 수 : 총 19 항

(54) 발명의 명칭 기능블럭을 포함하는 SoC의 클락 제어 방법, 이를 구현한 SoC 및 이를 포함하는 반도체 시스템

**(57) 요 약**

적어도 하나 이상의 기능블럭을 포함하는 SoC의 클락 제어 방법 및 그 SoC가 개시된다. 본 발명의 SoC(System On Chip)의 클락 제어 방법은 기능블럭의 상태를 모니터링하는 단계, 상기 모니터링된 상태에 따라 상기 기능블럭의 상태를 비활성화모드, 적어도 하나의 웨이크업모드 또는 활성화모드로 판단하는 단계, 상기 기능블럭의 상태가

(뒷면에 계속)

**대 표 도** - 도1

10

상기 비활성화 모드이면 기 설정된 제1주파수를 동작주파수로 설정하고, 상기 기능블력의 상태가 상기 활성화 모드이면 기 설정된 제2주파수를 동작주파수로 설정하며, 상기 기능블력의 상태가 상기 웨이크업모드이면 기 설정된 제3주파수를 동작주파수로 설정하는 단계 및 상기 설정한 동작주파수를 가진 동작클락을 상기 기능블력에 공급하는 단계를 포함한다. 그 결과 기능블력들 각각의 상태에 따라 각 기능블력들에 공급되는 동작클락을 별도로 제어함으로써 불필요한 전력 소모를 감소시킬 수 있다. 또한 기능블력이 비활성화 상태에서 활성화 상태로 변할 때 일어날 수 있는 전압 강하에 따른 오동작을 방지할 수 있다.

(72) 발명자

김시영

서울특별시 강남구 광평로10길 15 211동 202호 (일원동, 상록수아파트)

이재곤

경기도 용인시 수지구 수지로 166, 109동 18층

1801호 (풍덕천동, 정자뜰마을태영 데시앙1차아파트 )

허정훈

경기도 수원시 영통구 효원로 363, 131동 1703호

(매탄동, 매탄 위브 하늘채)

## 명세서

### 청구범위

#### 청구항 1

적어도 하나 이상의 기능블럭을 포함하는 SoC(System On Chip)의 클럭 제어 방법에 있어서,

상기 적어도 하나 이상의 기능블럭의 동작 상태가 비활성화 상태, 활성화 상태 또는 비활성화 상태에서 활성화 상태로의 전환 상태인지를 검출하는 단계;

상기 검출된 동작 상태가 상기 활성화 상태에서 상기 비활성화 상태로 변경된 경우 기설정된 제1주파수를 동작 주파수로 설정하고, 상기 검출된 동작 상태가 상기 전환 상태인 경우 기설정된 제2주파수를 동작주파수로 설정 하며, 상기 검출된 동작 상태가 상기 비활성화 상태에서 상기 활성화 상태로 변경된 경우 기설정된 제3주파수를 동작주파수로 설정하는 단계; 및

상기 설정한 동작주파수를 가진 동작클럭을 상기 기능블럭에 공급하는 단계를 포함하고,

상기 제1주파수 내지 상기 제3주파수는 0보다 크고, 상기 제1주파수는 제2주파수보다 작으며, 상기 제2주파수는 상기 제1주파수보다 크고 상기 제3주파수보다 작거나 같은 클럭 제어 방법.

#### 청구항 2

제1항에 있어서, 상기 검출하는 단계는

상기 기능블럭이 상기 비활성화 상태로 변경된 경우 비활성화 모드로 판단하는 단계를 포함하고,

상기 설정하는 단계는

상기 비활성화 모드에 상응하여 기준클럭의 주파수를 다수의 분주비 중 제1분주비로 분주(divide)한 상기 제1주파수를 상기 동작주파수로 설정하는 클럭 제어 방법.

#### 청구항 3

제1항에 있어서, 상기 검출하는 단계는

상기 기능블럭이 상기 활성화 상태로 변경된 경우 활성화 모드로 판단하는 단계를 포함하고,

상기 설정하는 단계는

기준클럭의 주파수를 다수의 분주비 중 제2분주비로 분주(divde)한 상기 제3주파수를 상기 동작주파수로 설정하는 클럭 제어 방법.

#### 청구항 4

제3항에 있어서, 상기 검출하는 단계는

상기 기능블럭이 상기 비활성화 상태에서 활성화 상태로 변한 시점부터 기설정된 카운트타임 각각이 경과할 때 까지 적어도 하나의 웨이크업 모드로 판단하는 단계를 포함하고,

상기 설정하는 단계는

상기 기준클럭의 주파수를 적어도 하나의 웨이크업분주비로 분주한 각 제2주파수를 상기 동작주파수로 설정하는 클럭 제어 방법.

#### 청구항 5

제4항에 있어서, 상기 설정하는 단계는

상기 적어도 하나의 제2주파수에 상응하는 적어도 하나의 카운트타임을 갖도록 설정하는 클럭 제어 방법.

#### 청구항 6

적어도 하나 이상의 기능블럭을 포함하는 SoC(System On Chip)의 클락 제어 방법에 있어서,

상기 적어도 하나 이상의 기능블럭의 동작 상태가 비활성화 상태, 활성화 상태 또는 비활성화 상태에서 활성화 상태로의 전환 상태인지를 검출하는 단계;

상기 검출된 동작 상태가 상기 활성화 상태에서 상기 비활성화 상태로 변경된 경우 기준클락의 주파수를 기설정된 제1주파수로 설정하고, 상기 검출된 동작 상태가 상기 비활성화 상태에서 상기 활성화 상태로 변경된 경우 상기 기준클락의 주파수를 기설정된 제2주파수로 설정하여 동작주파수를 설정하는 단계; 및

상기 동작주파수를 가진 동작클락을 상기 기능블럭에 공급하는 단계를 포함하고,

상기 제1주파수는 0보다 크고 상기 제2주파수보다 작으며,

상기 동작주파수를 설정하는 단계는

상기 검출된 동작 상태가 상기 전환 상태인 경우, 기설정된 카운트타임동안 상기 기준클락의 주파수를 웨이크업 분주비로 분주(divide)한 제3주파수로 설정하는 단계; 및

상기 카운트타임이 경과하면 상기 기준클락의 주파수를 상기 제2주파수로 설정하는 단계를 포함하는 클락 제어 방법.

#### 청구항 7

제6항에 있어서, 상기 기능블럭의 동작 상태를 검출하는 단계는

상기 기능블럭에서 출력되는 상태 신호를 모니터링하고, 상기 상태신호에 기초하여 비활성화모드 또는 활성화모드로 판단하는 클락 제어 방법.

#### 청구항 8

제7항에 있어서, 상기 동작주파수를 설정하는 단계는

상기 기능블럭의 비활성화 모드에 상응하여 상기 기준클락의 주파수를 다수의 분주비 중 제1분주비로 분주(divide)한 상기 제1주파수를 동작주파수로 설정하는 클락 제어 방법.

#### 청구항 9

제7항에 있어서, 상기 동작주파수를 설정하는 단계는

상기 기능블럭의 활성화 모드에 상응하여 상기 기준클락의 주파수를 다수의 분주비 중 제2분주비로 분주(divide)한 상기 제2주파수를 동작주파수로 설정하는 클락 제어 방법.

#### 청구항 10

삭제

#### 청구항 11

제9항에 있어서, 상기 제3주파수는

상기 제1주파수 이상 상기 제2주파수 이하의 범위 내인 것을 특징으로 하는 클락 제어 방법.

#### 청구항 12

적어도 하나 이상의 기능블럭을 포함하는 SoC(System On Chip)에 있어서,

기준주파수를 가진 기준클락을 생성하는 클락생성기; 및

상기 적어도 하나 이상의 기능블럭의 동작 상태가 비활성화 상태, 활성화 상태 또는 비활성화 상태에서 활성화 상태로의 전환 상태인지를 검출하고, 상기 검출된 동작 상태가 상기 활성화 상태에서 상기 비활성화 상태로 변경된 경우 상기 기준주파수로부터 기설정된 제1주파수로 동작주파수를 변경하고, 상기 검출된 동작 상태가 상기 전환 상태인 경우 상기 기준주파수로부터 기설정된 적어도 하나의 각 제2주파수로 동작주파수를 변경하며, 상기 검출된 동작 상태가 상기 비활성화 상태에서 상기 활성화 상태로 변경된 경우 상기 기준주파수로부터 기설정된

제3주파수로 동작주파수를 변경하여, 상기 동작 상태에 상응하는 동작주파수를 가진 동작클락을 상기 기능블럭으로 출력하는 클락컨트롤러를 포함하고,

상기 제1주파수 내지 상기 제3주파수는 0보다 크고, 상기 제1주파수는 제2주파수보다 작으며, 상기 제2주파수는 상기 제1주파수보다 크고 상기 제3주파수보다 작거나 같은 SoC.

### 청구항 13

제12항에 있어서, 상기 클락컨트롤러는

상기 기능블럭의 동작 상태를 검출하여 비활성화모드, 적어도 하나의 웨이크업모드 또는 활성화모드 중 어느 하나로 판단한 결과에 상응하는 분주비를 출력하는 분주기컨트롤러; 및

상기 분주비로 상기 기준주파수를 분주(divide)하여 상기 동작주파수를 가진 상기 동작클락을 출력하는 분주기 를 포함하는 SoC.

### 청구항 14

제13항에 있어서, 상기 분주기컨트롤러는

상기 기능블럭의 동작 상태를 검출하여 비활성화모드, 적어도 하나의 웨이크업모드 또는 활성화모드 중 어느 하나로 판단한 결과를 선택신호로 출력하는 모드검출부;

다수의 분주비들을 각각 저장하는 다수의 레지스터들; 및

상기 선택신호에 따라 상기 다수의 분주비들 중 어느 하나의 분주비를 출력하는 선택기를 포함하는 SoC.

### 청구항 15

제14항에 있어서, 상기 모드검출부는

상기 기능블럭의 상태신호를 모니터링하는 SoC.

### 청구항 16

제14항에 있어서, 상기 모드검출부는

상기 기능블럭의 상태가 상기 비활성화 모드로 판단되면 제1선택신호를 출력하고,

상기 분주기는

상기 제1선택신호에 상응하는 제1분주비로 상기 기준주파수를 분주한 상기 제1주파수를 동작 주파수로 설정하는 SoC.

### 청구항 17

제14항에 있어서, 상기 모드검출부는

상기 기능블럭의 상태가 상기 활성화 모드로 판단되면 제2선택신호를 출력하고,

상기 분주기는

상기 제2선택신호에 상응하는 제2분주비로 상기 기준주파수를 분주한 상기 제3주파수를 동작 주파수로 설정하는 SoC.

### 청구항 18

제14항에 있어서, 상기 모드검출부는

상기 기능블럭이 비활성화 상태에서 활성화 상태로 변한 시점부터 기설정된 카운트 타임이 경과할 때까지 상기 적어도 하나의 웨이크업 모드로 판단하여 적어도 하나의 제3선택신호를 출력하고,

상기 분주기는

상기 각 제3선택신호에 상응하는 각 웨이크업분주비로 상기 기준주파수를 분주(divide)한 상기 각 제2주파수를

동작 주파수로 설정하는 SoC.

### 청구항 19

적어도 하나 이상의 기능블럭을 포함하는 SoC(System On Chip)에 있어서,

기준주파수를 가진 기준클락을 생성하는 클락생성기;

상기 적어도 하나 이상의 기능블럭의 동작 상태가 비활성화 상태, 활성화 상태 또는 비활성화 상태에서 활성화 상태로의 전환 상태인지를 검출하고, 상기 검출된 동작 상태에 기초하여 선택신호를 출력하는 모드검출부;

다수의 분주비들을 저장하고, 상기 선택신호가 상기 활성화 상태에서 상기 비활성화 상태로의 변화를 나타내는 경우 제1분주비를 출력하고, 상기 선택신호가 상기 전환 상태를 나타내는 경우 적어도 하나의 제2분주비를 출력하며, 상기 선택신호가 상기 비활성화 상태에서 상기 활성화 상태로의 변화를 나타내는 경우 제3분주비를 출력하는 루업테이블; 및

상기 분주비로 상기 기준주파수를 분주하여 상기 동작 상태에 상응하는 동작주파수를 가진 동작클락을 상기 기능블럭으로 출력하는 분주기를 포함하고,

상기 제1분주비 내지 상기 제3분주비는 0이 아니고, 상기 제1분주비는 상기 제2분주비보다 크고, 상기 제2분주비는 상기 제3분주비보다 크거나 같은 SoC.

### 청구항 20

동작클락에 따라 메모리 장치의 데이터 처리 동작을 제어하는 CPU;

기준주파수를 가진 기준클락을 생성하는 클락생성기; 및

상기 기준클락으로부터 상기 CPU에 입력되는 상기 동작클락을 생성하는 클락컨트롤러를 포함하고,

상기 클락컨트롤러는

상기 CPU의 동작 상태가 비활성화 상태, 활성화 상태 또는 비활성화 상태에서 활성화 상태로의 전환 상태인지를 검출하고, 상기 검출된 동작 상태가 상기 활성화 상태에서 상기 비활성화 상태로 변경된 경우 상기 기준주파수를 기설정된 제1주파수로 변경하고, 상기 검출된 동작 상태가 상기 전환 상태인 경우 상기 기준주파수를 기설정된 제3주파수로 변경하며, 상기 검출된 동작 상태가 상기 비활성화 상태에서 상기 활성화 상태로 변경된 경우 상기 기준주파수를 기설정된 제2주파수로 변경하여 상기 동작클락의 동작주파수를 설정하는 SoC(System On Chip).

### 청구항 21

삭제

### 청구항 22

삭제

### 청구항 23

삭제

### 청구항 24

삭제

### 청구항 25

삭제

### 청구항 26

삭제

청구항 27

삭제

청구항 28

삭제

청구항 29

삭제

## 발명의 설명

### 기술 분야

[0001]

본 발명은 SoC(System on Chip)에 관한 것으로, 보다 구체적으로는 SoC 내 기능블럭에 공급되는 동작클락을 제어하는 클락 제어 방법, 이를 구현한 SoC 및 이를 포함하는 반도체 시스템에 관한 것이다.

### 배경 기술

[0002]

SoC(System on Chip)는 기존의 여러 가지 기능을 가진 복잡한 시스템을 하나의 시스템으로 구현한 기술집약적 반도체 기술이다. SoC는 시스템 전체를 제어하는 프로세서와 그 프로세서에 의해서 제어되는 다양한 IP(Intellectual Properties: 이하 IP)로 구성된다. 여기서, IP라 함은 SoC에 접적될 수 있는 회로(circuit), 로직(logic), 또는 이들의 조합을 의미한다. 또한, 상기 회로 또는 상기 로직에는 코드(code)가 저장될 수 있다.

[0003]

일반적으로 다양한 다수의 IP를 포함하는 SoC를 구비한 시스템은 배터리에 의해 동작하게 되므로 저전력 설계가 중요시된다. PLL(Phase Locked Loop) 등에 의해 기준클락이 SoC에 공급되면, 다수의 IP 각각은 그 기능에 따라 다양한 주파수를 갖는 동작클락에 따라 동작한다.

[0004]

다수의 IP들은 그 기능에 따라 각각 활성화모드(active)일 수도 있고 비활성화모드(idle)일 수 있다. 어느 하나의 IP가 비활성화모드일 때 다른 하나의 IP가 활성화모드일 수도 있고, 적어도 둘 이상의 IP들이 동시에 활성화 모드거나 비활성화모드일 수 있다.

[0005]

상기 다수의 IP들 중 적어도 어느 하나가 비활성화모드로 동작을 하지 않을 때에도 상기 IP에 동작할 때와 같은 활성화모드의 동작클락을 계속 공급하게 되면, SoC는 불필요한 전력을 소모한다. 이와 같은 불필요한 전력 소모는 수백 MHz 내지 수 GHz의 주파수를 사용하는 IP의 경우 배터리의 수명에 큰 영향을 끼친다.

### 발명의 내용

#### 해결하려는 과제

[0006]

따라서, 본 발명이 이루고자 하는 기술적인 과제는 SoC 내 기능블럭의 상태에 따라 기능블럭에 공급되는 동작클락을 제어하여 소비전력을 감소시킬 수 있는 SoC의 클락 제어 방법, 이를 구현한 SoC 및 이를 포함하는 반도체 시스템을 제공하는 것이다.

#### 과제의 해결 수단

[0007]

상술한 기술적 과제를 해결하기 위하여, 적어도 하나 이상의 기능블럭을 포함하는 SoC(System On Chip)의 클락 제어 방법은 상기 기능블럭의 상태를 모니터링하는 단계, 상기 모니터링 된 상태에 따라 상기 기능블럭의 상태를 비활성화(idle)모드, 적어도 하나의 웨이크업모드 또는 활성화(active)모드로 판단하는 단계, 상기 기능블럭의 상태가 상기 비활성화(idle) 모드이면 기 설정된 제1주파수를 동작주파수로 설정하고, 상기 기능블럭의 상태가 상기 웨이크업모드이면 기 설정된 제3주파수를 동작주파수로 설정하며, 상기 기능블럭의 상태가 상기 활성화(active) 모드이면 기 설정된 제2주파수를 동작주파수로 설정하는 단계 및 상기 설정한 동작주파수를 가진 동작클락을 상기 기능블럭에 공급하는 단계를 포함한다.

[0008]

상기 판단하는 단계는 상기 기능블럭이 상기 비활성화 상태이면 비활성화모드로 판단하고, 상기 설정하는 단계는 상기 비활성화모드에 상응하여 상기 기준클락의 주파수를 다수의 분주비 중 제1분주비로 분주(divide)한 상

기 제1주파수를 상기 동작주파수로 설정한다.

[0009] 상기 판단하는 단계는 상기 기능블럭이 상기 활성화 상태인 동안 활성화모드로 판단하고, 상기 설정하는 단계는 상기 기준클락의 주파수를 다수의 분주비 중 제2분주비로 분주(divide)한 상기 제2주파수를 상기 동작주파수로 설정한다.

[0010] 상기 판단하는 단계는 상기 기능블럭이 상기 비활성화 상태에서 활성화 상태로 변한 시점부터 기 설정된 카운트타임 동안이 경과할 때까지 하나의 웨이크업모드로 판단하고, 상기 설정하는 단계는 상기 기준클락의 주파수를 적어도 하나의 웨이크업분주비로 분주(divide)한 각 제3주파수를 상기 동작주파수로 설정한다.

[0011] 상기 설정하는 단계는 상기 적어도 하나의 제3주파수에 상응하는 적어도 하나의 카운트타임을 갖도록 설정한다.

[0012] 상술한 기술적 과제를 해결하기 위하여, 적어도 하나 이상의 기능블럭을 포함하는 SoC(System On Chip)의 클락제어 방법은 상기 기능블럭의 상태를 모니터링 하여 해당 모드를 판단하는 단계, 상기 기능블럭의 상태가 비활성화 모드 시 기 설정된 제1주파수로 설정하고, 상기 기능블럭의 상태가 활성화모드로 변하면 상기 기준클락의 주파수를 기 설정된 제2주파수로 설정하여 동작주파수를 설정하는 단계 및 상기 동작주파수를 가진 동작클락을 상기 기능블럭에 공급하는 단계를 포함한다.

[0013] 상기 해당 모드는 상기 기능블럭에서 출력되는 상태 신호를 모니터링하고, 상기 상태신호에 기초하여 상기 비활성화모드 또는 상기 활성화모드로 판단한다.

[0014] 상기 제1주파수는 0보다 크고 상기 제2주파수보다 작은 것을 특징으로 한다.

[0015] 상기 동작주파수를 설정하는 단계는 상기 기능블럭의 비활성화모드에 상응하여 상기 기준클락의 주파수를 다수의 분주비 중 제1분주비로 분주한 상기 제1주파수를 동작주파수로 설정할 수 있다.

[0016] 상기 동작주파수를 설정하는 단계는 상기 기능블럭의 활성화모드에 상응하여 상기 기준클락의 주파수를 다수의 분주비 중 제2분주비로 분주한 상기 제2주파수를 동작주파수로 설정할 수 있다.

[0017] 상기 동작주파수를 설정하는 단계는 상기 기능블럭이 비활성화모드에서 활성화모드로 변하면, 기 설정된 카운트타임 동안 상기 기준클락의 주파수를 웨이크업분주비로 분주한 제3주파수로 설정하는 단계 및 상기 카운트타임이 경과하면 상기 기준클락의 주파수를 상기 제2주파수로 설정하는 단계를 포함할 수 있다.

[0018] 상기 제3주파수는 상기 제1주파수 이상 상기 제2주파수 이하의 범위 내인 것을 특징으로 한다.

[0019] 상술한 기술적 과제를 해결하기 위하여, 본 발명의 또다른 실시 예에 따른 적어도 하나 이상의 기능블럭을 포함하는 SoC(System On Chip)는 기준주파수를 가진 기준클락을 생성하는 클락생성기 및 상기 기능블럭의 상태를 모니터링 하여 상기 기능블럭의 상태를 비활성화모드, 적어도 하나의 웨이크업모드 또는 활성화모드 중 어느 하나로 판단하고, 상기 비활성화 모드 시 상기 기준주파수로부터 기 설정된 제1주파수로 동작주파수를 변경하고, 상기 웨이크업 모드 시 상기 기준주파수로부터 기 설정된 적어도 하나의 각 제3주파수로 동작주파수를 변경하며, 상기 활성화 모드 시 상기 기준주파수로부터 기 설정된 제2주파수로 동작주파수를 변경하여, 상기 모드에 상응하는 동작주파수를 가진 동작클락을 상기 기능블럭으로 출력하는 클락컨트롤러를 포함한다.

[0020] 상기 클락컨트롤러는 기준주파수를 가진 기준클락을 생성하는 클락생성기 및 상기 기능블럭의 상태를 모니터링 하여 비활성화모드, 적어도 하나의 웨이크업모드 또는 활성화모드 중 어느 하나로 판단한 결과에 상응하는 분주비를 출력하는 분주기컨트롤러 및 상기 분주비로 상기 기준주파수를 분주하여 상기 동작주파수를 가진 상기 동작클락을 출력하는 분주기를 포함한다.

[0021] 일례로 상기 분주기컨트롤러는 상기 기능블럭의 상태를 모니터링 하여 비활성화모드, 적어도 하나의 웨이크업모드 또는 활성화모드 중 어느 하나로 판단한 결과를 선택신호로 출력하는 모드검출부, 다수의 분주비들을 각각 저장하는 다수의 레지스터들 및 상기 선택신호에 따라 상기 다수의 분주비들 중 어느 하나의 분주비를 출력하는 선택기를 포함할 수 있다.

[0022] 상기 모드검출부는 상기 기능블럭의 상태신호를 모니터링 할 수 있다.

[0023] 상기 모드검출부는 상기 기능블럭의 상태가 상기 비활성화모드로 판단되면 제1선택신호를 출력하고, 상기 분주기는 상기 제1선택신호에 상응하는 제1분주비로 상기 기준주파수를 분주한 상기 제1주파수를 동작주파수로 설정한다.

[0024] 상기 모드검출부는 상기 기능블럭의 상태가 상기 활성화모드로 판단되면 제2선택신호를 출력하고, 상기 분주기

는 상기 제2선택신호에 상응하는 제2분주비로 상기 기준주파수를 분주한 상기 제2주파수를 동작주파수로 설정한다.

- [0025] 상기 모드검출부는 상기 기능블력의 상태가 비활성화 상태에서 활성화 상태로 변한 시점부터 기 설정된 카운트타임 동안이 경과할 때까지 적어도 하나의 웨이크업모드로 판단하여 적어도 하나의 제3선택신호를 출력하고, 상기 분주기는 상기 각 제3선택신호에 상응하는 각 웨이크업분주비로 상기 기준주파수를 분주한 상기 각 제3주파수를 동작주파수로 설정한다.

- [0026] 상기 모드검출부는 상기 각 웨이크업모드마다 각각 기설정되는 적어도 하나의 카운트타임을 카운트하는 적어도 하나의 카운터를 포함하는 카운터를 포함할 수 있다.

- [0027] 일례로 상기 분주기컨트롤러는 상기 기능블력의 상태를 모니터링 하여 비활성화모드, 적어도 하나의 웨이크업모드 또는 활성화모드 중 어느 하나로 판단한 결과를 선택신호로 출력하는 모드검출부 및 상기 다수의 분주비들을 저장하고, 상기 선택신호에 따라 상기 분주비들 중 어느 하나를 출력하는 루프테이블을 포함한다.

- [0028] 상기 모드검출부는 상기 기능블력의 상태신호(State Signal)를 모니터링 할 수 있다.

- [0029] 상기 모드검출부는 상기 기능블력의 상태가 상기 비활성화모드로 판단되면 제1선택신호를 출력하고, 상기 분주기는 상기 제1선택신호에 상응하는 제1분주비로 상기 기준주파수를 분주한 상기 제1주파수를 동작주파수로 설정한다.

- [0030] 상기 모드검출부는 상기 기능블력의 상태가 상기 활성화모드로 판단되면 제2선택신호를 출력하고, 상기 분주기는 상기 제2선택신호에 상응하는 제2분주비로 상기 기준주파수를 분주한 상기 제2주파수를 동작주파수로 설정한다.

- [0031] 상기 모드검출부는 상기 기능블력의 상태가 비활성화 상태에서 활성화 상태로 변한 시점부터 기 설정된 카운트타임 동안이 경과할 때까지 적어도 하나의 웨이크업모드로 판단하여 적어도 하나의 제3선택신호를 출력하고, 상기 분주기는 상기 각 제3선택신호에 상응하는 각 웨이크업분주비로 상기 기준주파수를 분주한 상기 각 제3주파수를 동작주파수로 설정한다.

- [0032] 상기 모드검출부는 상기 각 웨이크업모드마다 각각 기설정되는 적어도 하나의 카운트타임을 카운트하는 적어도 하나의 카운터를 포함하는 카운터를 포함할 수 있다.

- [0033] 상술한 기술적 과제를 해결하기 위하여, 본 발명의 또다른 일실시 예에 따른 SoC는 메모리 장치, 상기 메모리 장치의 데이터 처리 동작을 제어하는 메모리 컨트롤러, 동작클락에 따라 상기 메모리 장치의 데이터 처리 동작을 제어하는 적어도 하나 이상의 기능블력, 기준주파수를 가진 기준클락을 생성하는 클락생성기 및 상기 기준클락으로부터 상기 각 기능블력에 입력되는 상기 동작클락을 생성하는 클락컨트롤러를 포함한다.

- [0034] 상기 클락컨트롤러는 상기 기능블력의 상태를 모니터링 하여 상기 기능블력의 상태를 비활성화모드, 적어도 하나의 웨이크업모드 또는 활성화모드 중 어느 하나로 판단하고, 상기 비활성화모드로 판단시 상기 기준주파수를 기 설정된 제1주파수로 변경하고, 상기 웨이크업모드로 판단시 상기 기준주파수를 기 설정된 제3주파수로 변경하며, 상기 활성화모드로 판단시 상기 기준주파수를 기 설정된 제2주파수로 변경하여 상기 동작클락의 동작주파수를 설정한다.

### 발명의 효과

- [0035] 본 발명의 SoC의 클락 제어 방법, 이를 구현한 SoC 및 이를 포함하는 반도체 시스템에 따르면 다수의 기능블력이 있는 경우, 기능블력들 각각의 상태에 따라 각 기능블력들에 공급되는 동작클락을 별도로 제어함으로써 불필요한 전력 소모를 감소시킬 수 있다. 또한 기능블력이 비활성화 상태에서 활성화 상태로 변할 때 일어날 수 있는 전압 강하에 따른 오동작을 방지할 수 있다.

### 도면의 간단한 설명

- [0036] 본 발명의 상세한 설명에서 인용되는 도면을 보다 충분히 이해하기 위하여 각 도면의 간단한 설명이 제공된다.

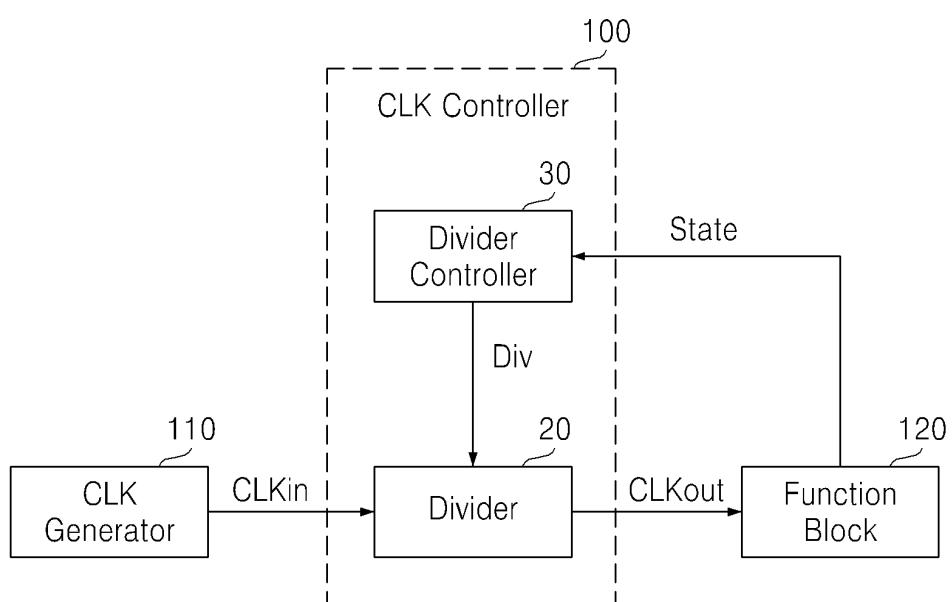

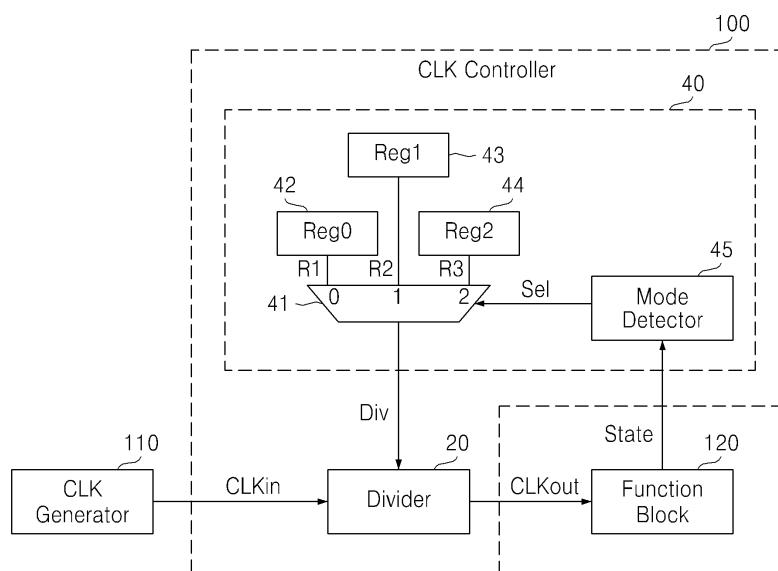

- 도 1은 본 발명의 일 실시 예에 따른 SoC(System on Chip)의 블록도이다.

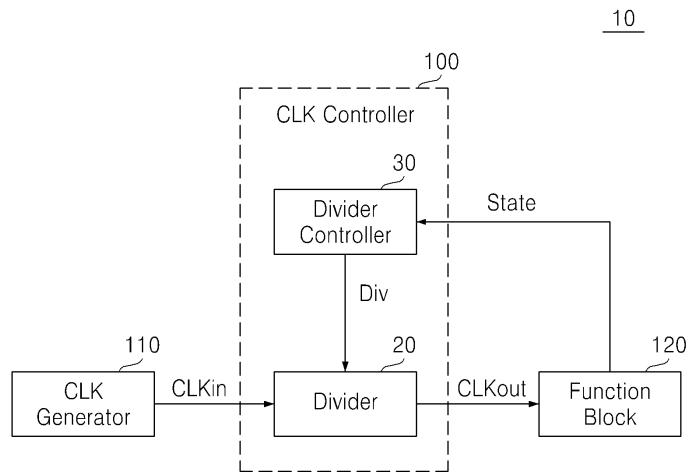

- 도 2는 도 1에 도시된 SoC의 일 실시 예를 구체적으로 나타내는 블록도이다.

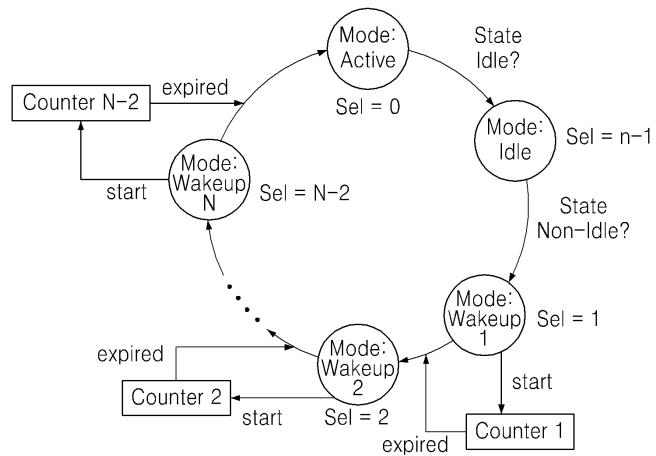

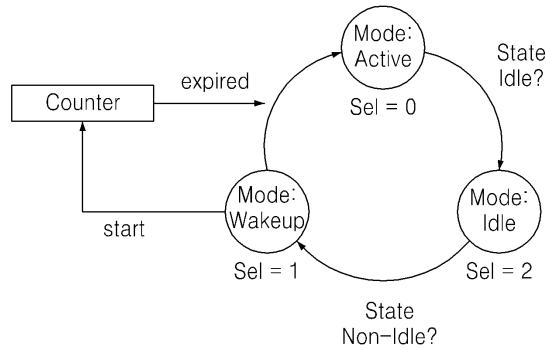

- 도 3은 도 2에 도시된 모드검출부의 동작모드를 나타낸 상태도이다.

도 4는 도 2에 도시된 SoC의 일 실시 예를 구체적으로 나타내는 블록도이다.

도 5는 도 4에 도시된 모드검출부의 동작모드를 나타낸 상태도이다.

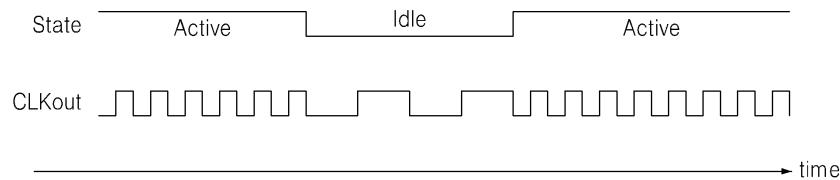

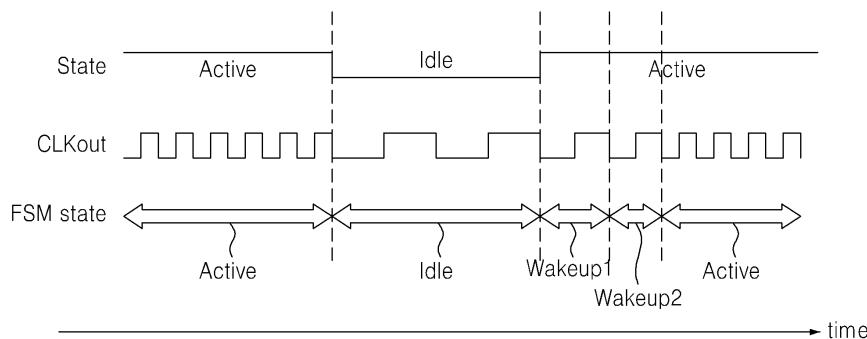

도 6은 본 발명의 일 실시 예에 따른 SoC의 신호 타이밍도이다.

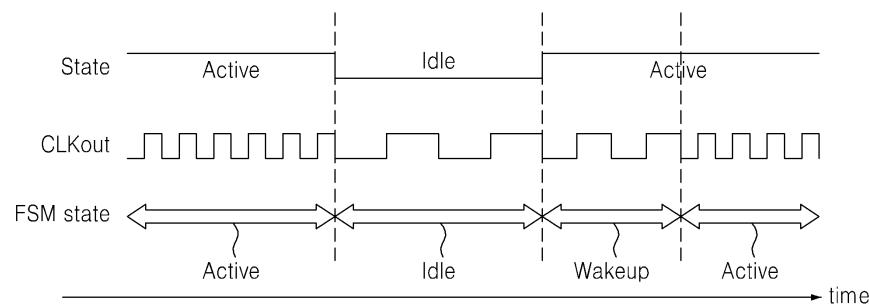

도 7은 본 발명의 다른 실시 예에 따른 SoC의 신호 타이밍도이다.

도 8은 본 발명의 또 다른 일 실시 예에 따른 SoC의 신호 타이밍도이다.

도 9는 도 1에 도시된 SoC의 다른 일 실시 예를 구체적으로 나타내는 블록도이다.

도 10은 본 발명의 일 실시 예에 따른 클락 제어 방법을 나타낸 흐름도이다.

도 11은 본 발명의 실시 예들에 따른 SoC를 포함한 반도체 시스템의 블럭도이다.

도 12는 도 1에 도시된 SoC를 포함하는 반도체 시스템의 일 실시 예를 나타낸다.

도 13은 도 1에 도시된 SoC를 포함하는 컴퓨터 시스템의 일 실시 예를 나타낸다.

도 14는 도 1에 도시된 SoC를 포함하는 컴퓨터 시스템의 다른 실시 예를 나타낸다.

도 15는 도 1에 도시된 SoC를 포함하는 컴퓨터 시스템의 또 다른 실시 예를 나타낸다.

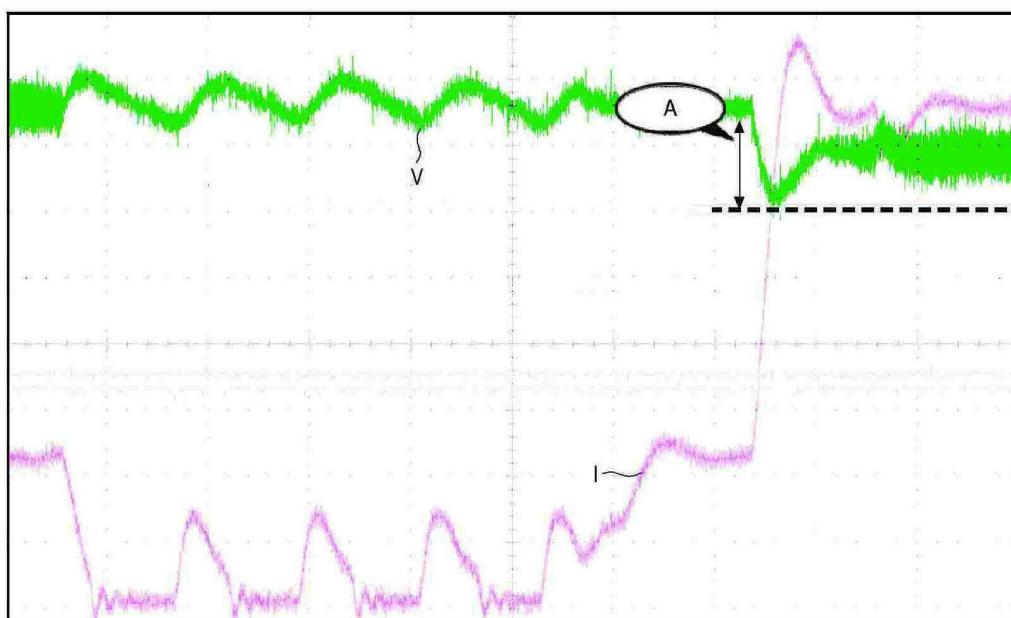

도 16은 기능블럭의 상태를 고려하지 않고 동작클락을 인가한 경우의 전류 및 전압 그래프이다.

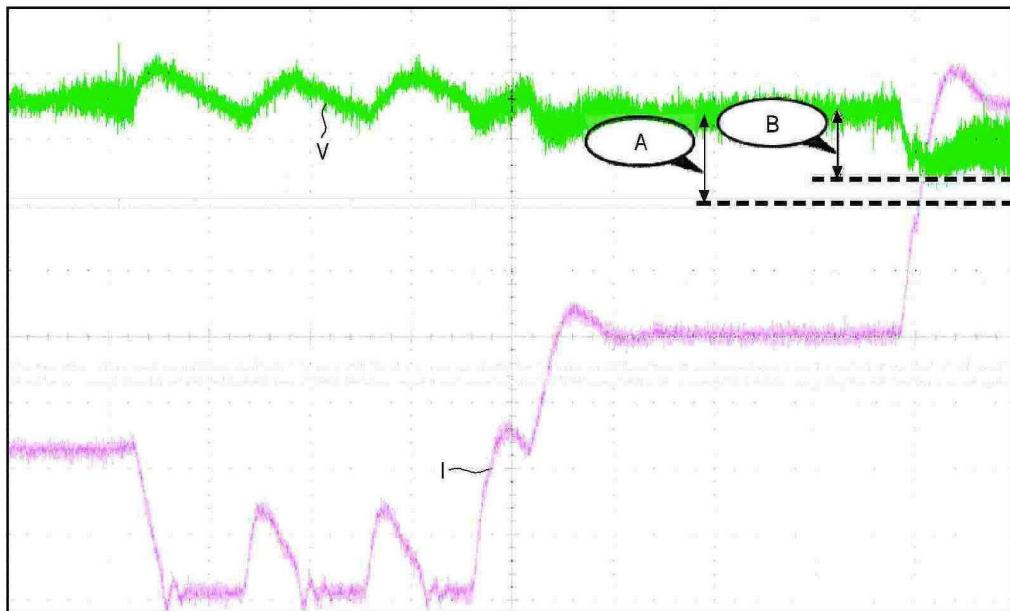

도 17은 기능블럭의 상태를 고려하여 동작클락을 인가한 경우의 전류 및 전압 그래프이다.

### 발명을 실시하기 위한 구체적인 내용

[0037]

본 명세서 또는 출원에 개시되어 있는 본 발명의 실시 예들에 대해서 특정한 구조적 내지 기능적 설명들은 단지 본 발명에 따른 실시 예를 설명하기 위한 목적으로 예시된 것으로, 본 발명에 따른 실시 예들은 다양한 형태로 실시될 수 있으며 본 명세서 또는 출원에 설명된 실시 예들에 한정되는 것으로 해석되어서는 아니 된다.

[0038]

본 발명에 따른 실시 예는 다양한 변경을 가할 수 있고 여러 가지 형태를 가질 수 있으므로 특정실시 예들을 도면에 예시하고 본 명세서 또는 출원에 상세하게 설명하고자 한다. 그러나, 이는 본 발명의 개념에 따른 실시 예를 특정한 개시 형태에 대해 한정하려는 것이 아니며, 본 발명의 사상 및 기술 범위에 포함되는 모든 변경, 균등물 내지 대체물을 포함하는 것으로 이해되어야 한다.

[0039]

제1 및/또는 제2 등의 용어는 다양한 구성 요소들을 설명하는데 사용될 수 있지만, 상기 구성요소들은 상기 용어들에 의해 한정되어서는 안 된다. 상기 용어들은 하나의 구성 요소를 다른 구성 요소로부터 구별하는 목적으로만, 예컨대 본 발명의 개념에 따른 권리 범위로부터 이탈되지 않은 채, 제1 구성요소는 제2 구성요소로 명명될 수 있고, 유사하게 제2 구성요소는 제1 구성요소로도 명명될 수 있다.

[0040]

어떤 구성요소가 다른 구성요소에 "연결되어" 있다거나 "접속되어" 있다고 언급된 때에는, 그 다른 구성요소에 직접적으로 연결되어 있거나 또는 접속되어 있을 수도 있지만, 중간에 다른 구성요소가 존재할 수도 있다고 이해되어야 할 것이다. 반면에, 어떤 구성요소가 다른 구성요소에 "직접 연결되어" 있다거나 "직접 접속되어" 있다고 언급된 때에는, 중간에 다른 구성요소가 존재하지 않는 것으로 이해되어야 할 것이다. 구성요소들 간의 관계를 설명하는 다른 표현들, 즉 "~사이에"와 "바로 ~사이에" 또는 "~에 이웃하는"과 "~에 직접 이웃하는" 등도 마찬가지로 해석되어야 한다.

[0041]

본 명세서에서 사용한 용어는 단지 특정한 실시 예를 설명하기 위해 사용된 것으로, 본 발명을 한정하려는 의도가 아니다. 단수의 표현은 문맥상 명백하게 다르게 뜻하지 않는 한, 복수의 표현을 포함한다. 본 명세서에서, "포함하다" 또는 "가지다" 등의 용어는 실시된 특징, 숫자, 단계, 동작, 구성요소, 부분품 또는 이들을 조합한 것이 존재함을 지정하려는 것이지, 하나 또는 그 이상의 다른 특징들이나 숫자, 단계, 동작, 구성요소, 부분품 또는 이들을 조합한 것들의 존재 또는 부가가능성을 미리 배제하지 않는 것으로 이해되어야 한다.

[0042]

다르게 정의되지 않는 한, 기술적이거나 과학적인 용어를 포함해서 여기서 사용되는 모든 용어들은 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자에 의해 일반적으로 이해되는 것과 동일한 의미이다. 일반적으로 사용되는 사전에 정의되어 있는 것과 같은 용어들은 관련 기술의 문맥상 가지는 의미와 일치하는 의미인 것으로 해석되어야 하며, 본 명세서에서 명백하게 정의하지 않는 한, 이상적이거나 과도하게 형식적인 의미로 해석되지 않는다.

- [0043] 이하, 첨부한 도면을 참조하여 본 발명의 바람직한 실시 예를 설명함으로써, 본 발명을 상세히 설명한다. 각 도면에 제시된 동일한 참조부호는 동일한 부재를 나타낸다.

- [0044] 도 1은 본 발명의 일 실시 예에 따른 SoC(System on Chip)의 블록도이다.

- [0045] 도 1을 참조하면, SoC(10)는 클락생성기(Clock Generator, 110), 클락컨트롤러(Clock Controller, 100) 및 기능블럭(120)을 포함한다. SoC(10)는 단일의 칩으로 제조되어 하나의 패키지(package)로 구현될 수 있다. 도 1에서는 설명의 편의를 위하여 클락생성기(110), 클락컨트롤러(100) 및 하나의 기능블럭(120)을 포함하는 SoC(10)가 도시되었으나, 이에 한정되는 것은 아니다.

- [0046] 클락생성기(Clock Generator, 110)는 SoC(10)의 동작에 필요한 기준주파수를 가진 기준클락(CLK<sub>in</sub>)을 생성하여 클락컨트롤러(100)로 출력한다.

- [0047] 클락컨트롤러(Clock Controller, 100)는 기능블럭(120)의 상태를 모니터링 하여 상기 기능블럭의 상태를 비활성화(idle)모드, 적어도 하나의 웨이크업모드 또는 활성화(active)모드 중 어느 하나로 판단한다. 클락컨트롤러(100)는 기능블럭(120)의 상태가 비활성화(idle) 모드 시 상기 기준주파수로부터 기 설정된 제1주파수로 동작주파수를 변경한다. 클락컨트롤러(100)는 기능블럭(120)의 상태가 활성화(active) 모드 시 상기 기준주파수로부터 기 설정된 제2주파수로 동작주파수를 변경한다. 클락컨트롤러(100)는 기능블럭(120)의 상태가 웨이크업 모드 시 상기 기준주파수로부터 기 설정된 적어도 하나의 각 제3주파수로 동작주파수를 변경한다. 클락컨트롤러(100)는 기능블럭(120)의 상태가 해당 모드에 상응하는 동작주파수를 가진 동작클락(CLK<sub>out</sub>)을 상기 기능블럭으로 출력한다. 상기 제1주파수 내지 상기 제3주파수는 0보다 크고, 서로 다른 주파수로서, 비활성화모드의 제1주파수, 웨이크업모드의 제3주파수, 활성화모드의 제2주파수로 갈수록 주파수가 점점 더 커진다. 즉, 상기 제1주파수 내지 상기 제3주파수는 0보다 크고 서로 다른 값을 가진다. 상기 제2주파수는 상기 제1주파수보다 크고 상기 제3주파수보다 작다.

- [0048] 클락 컨트롤러(100)는 분주기(Divider, 20) 및 분주기컨트롤러(Divider controller, 30)를 포함한다.

- [0049] 분주기컨트롤러(30)는 기능블럭(120)의 상태(State)를 모니터링 하여 비활성화(idle)모드, 적어도 하나의 웨이크업모드 또는 활성화(active)모드 중 어느 하나로 판단한 결과에 상응하는 분주비를 출력한다. 분주기(20)는 출력된 분주비(Div)에 따라 기준주파수를 분주(divide)한 동작주파수를 설정하여 동작클락(CLK<sub>out</sub>)을 출력한다.

- [0050] 분주기컨트롤러(30)는 기능블럭(120)에서 출력되는 상태(State)를 모니터링(monitoring)할 수 있다. 기능블럭의 상태를 모니터링하는 것은, 일례로 기능블럭(120)에서 출력되는 상태 신호가 하이(high)면 기능블럭(120)의 상태를 활성화(active)모드로 판단하고, 로우(Low)면 기능블럭(120)의 상태를 비활성화(idle)모드로 판단할 수 있다. 기능블럭(120)은 SoC(10) 내 데이터 처리 동작을 수행한다. 도 1에는 하나의 기능블럭만이 도시되었으나, 이에 한정되지 아니하고 SoC(10)는 다수의 기능블럭을 포함할 수 있다.

- [0051] 기능블럭(120)은 예를 들어 시스템 전체를 제어하는 프로세서 또는 그 프로세서에 의해서 제어되는 다양한 지능소자들 중 어느 하나일 수 있다. 지능소자는 예를 들면, CPU(Central Processing Unit), 상기 CPU에 포함된 복수의 코어들(cores) 각각, GPU(Graphic Processing Unit), MFC(Multi-Format Codec), 비디오 모듈(예컨대, 카메라 인터페이스(Camera Interface), JPEG(Joint Photographic Experts Group) 프로세서, 비디오 프로세서(Video Processor), 또는 믹서(Mixer), 등), 오디오 시스템(Audio System), 드라이버(Driver), 디스플레이 드라이버(Display Driver), 휘발성 메모리(Volatile Memory Device), 비휘발성 메모리(Non-volatile Memory), 메모리 컨트롤러(Memory Controller), 캐시 메모리(Cache Memory), 시리얼 포트(Serial Port), 시스템 타이머(System Timer), 워치독타이머(Watch Dog Timer) 또는 아날로그-디지털 컨버터(Analog-to-Digital Converter) 등을 포함할 수 있다. 각 기능블럭들(120)은 서로 다른 클락 주파수(clock frequency)를 갖기 때문에 하나의 SoC(10) 내에는 다양한 동작클락(CLK<sub>out</sub>)이 사용된다.

- [0052] SoC(10)는 집적 회로(integrated circuit)로 구현될 수 있다. 또한, SoC(10)는 이동 전화기(mobile phone), 스마트폰(smart phone), 태블릿 PC(tablet personal computer), 또는 PDA(personal digital assistant)와 같은 이동 통신 장치 내에 내장(embedded)될 수 있다. 실시 예에 따라 SoC(10)는 IT 장치(information technology device) 또는 휴대용 전자 장치(portable electronic device)에 내장될 수 있다.

- [0053] 도 2는 도 1에 도시된 SoC의 일 실시 예를 구체적으로 나타내는 블록도이다.

- [0054] 도 2를 참조하면, 분주기컨트롤러(Divider Controller, 30)는 다수의 레지스터들(32), 모드검출부(Mode Detector, 35) 및 선택기(31)를 포함한다(N은 3이상의 자연수).

- [0055] 설명의 편의를 위하여, 제1주파수, 제3주파수, 제2주파수로 갈수록 주파수 크기는 점점 커지고, 이에 따라 기 설정된 제1분주비, 제3분주비 및 제2분주비는 점점 작아진다고 가정하나 이에 한정되지는 아니하고, 실시 예에 따라 다양하게 구현될 수 있다.

- [0056] 다수의 레지스터들(32)은 다수의 분주비(Div)들을 각각 저장한다. 일례로 N개의 분주비(Div)가 있는 경우 레지스터마다 하나의 분주비를 저장할 수 있다. 모드검출부(35)는 기능블럭(120)의 상태(State)를 모니터링 하여 비 활성화모드, 적어도 하나의 웨이크업모드 또는 활성화모드 중 어느 하나로 판단한 결과를 선택신호(Sel)로 출력 한다. 선택기(31)는 선택신호(Sel)에 따라 상기 다수의 분주비들 중 어느 하나의 분주비(Div)을 출력한다.

- [0057] 일례로 모드검출부(35)는 기능블럭(120)이 비활성화모드로 판단되면, 제1선택신호(Sel0)를 출력한다. 선택기(31)는 제1선택신호(Sel0)에 상응하는 제1분주비(D1)를 레지스터 0(Reg 0)으로부터 출력한다. 분주기(20)는 제1 분주비(D1)로 기준주파수를 분주(divide)한 제1주파수를 동작주파수로 설정하여 동작클락(CLKout)을 출력한다. 기능블럭이 활성화모드에서 비활성화모드가 되면, 동작클락이 상기 기능블럭의 상태에 응답하여 제2주파수에서 제1주파수가 되므로 SoC 내의 불필요한 전력소모를 줄일 수 있게 된다.

- [0058] 일례로 모드검출부(35)는 기능블럭(120)이 활성화모드로 판단되면, 제2선택신호(Seln-1)를 출력한다. 선택기(31)는 제2선택신호(Seln)에 상응하는 제2분주비(Dn)를 레지스터 n-1(Reg n-1)로부터 출력한다. 분주기(20)는 제2분주비(Dn)로 기준주파수를 분주(divide)한 제2주파수를 동작주파수로 설정하여 동작클락(CLKout)을 출력한다. 기능블럭(120)이 비활성화모드에서 다시 활성화모드가 되면, 동작클락이 상기 기능블럭의 상태에 응답하여 제1주파수에서 제2주파수가 되므로 기능블럭이 제 기능대로 다시 동작할 수 있게 된다.

- [0059] 일례로 모드검출부(35)는 기능블럭(120)이 비활성화 상태에서 활성화 상태로 변한 시점부터 기 설정된 카운트 타임 동안이 경과할 때까지 적어도 하나의 웨이크업모드로 판단하여 적어도 하나의 제3선택신호(Sel k)를 출력 한다. 선택기(31)는 제3선택신호(Sel k)에 상응하는 웨이크업분주비(Dk)를 레지스터 k(Reg k)로부터 출력한다. 분주기(20)는 상기 웨이크업분주비(Dk)로 기준주파수를 분주한 상기 각 제3주파수를 동작주파수로 설정하여 동작클락(CLKout)을 출력한다.

- [0060] 모드검출부(35)는 상기 각 웨이크업모드마다 각각 기 설정되는 적어도 하나의 카운트타임을 카운트하는 적어도 하나의 카운터를 포함할 수 있다. 상기 카운트타임이 카운트되는 동안 적어도 하나의 각 제3주파수를 상기 동작 주파수로 설정하고, 모든 카운트타임들이 경과되면 제2주파수를 상기 동작주파수로 설정할 수 있다. 그 결과 기 능블럭이 비활성화모드에서 다시 활성화모드가 될 때 동작클락이 제1주파수에서 갑자기 제2주파수가 되면, 갑작 스런 전압 강하(Voltage Drop)에 의해 SoC(10)가 오동작할 수 있다. 따라서 기능블럭(120)은 웨이크업모드 시 일정 카운트타임 동안 제3주파수로 동작하면, 전류가 점차적으로 커지도록 인가되어 갑작스런 전압 강하(voltage drop) 없이 동작하게 된다.

- [0061] 도 3은 도 2에 도시된 모드검출부의 동작모드를 나타낸 상태도이다.

- [0062] 도 3을 참조하면, 모드검출부(35)는 기능블럭(120)의 모드 각각에 상응하여, 해당 분주비(Div)을 선택하기 위한 선택신호(Sel)를 출력한다. 이를 유한상태기계(Finite State Machine)로 나타낼 수 있다.

- [0063] 유한상태기계는 기능블럭(120)의 다수 개(예를 들어 N개)의 제한된 모드가 존재하고, 그 상태들이 특정 조건에 물려 서로 연결되는 것으로 하드웨어, 소프트웨어 또는 하드웨어 및 소프트웨어의 결합으로 구현될 수 있다.

- [0064] 기능블럭(120)의 초기 상태가 활성화모드(active)라고 하자. 이때 모드검출부(35)는 제2분주비(Dn)를 선택하기 위한 제1선택신호(Sel n)을 출력한다. 선택기(41)는 상기 제1선택신호(Sel n)에 따라 레지스터 (n-1)(Reg (n-1))을 선택하여 제2분주비(Dn)를 분주기(20)로 출력한다.

- [0065] 모드검출부(35)는 기능블럭(120)의 상태(state)가 활성화 상태에서 비활성화 상태로 바뀌면, 비활성화모드(idle)로 판단하고, 제1분주비(D0)을 선택하기 위한 제2선택신호(Sel 1)를 출력한다. 선택기(31)는 상기 제2선택신호(Sel 1)에 따라 레지스터 0(Reg 0)를 선택하여 제1분주비(D1)를 분주기(20)로 출력한다.

- [0066] 모드검출부(35)는 기능블럭(120)이 비활성화 상태에서 활성화 상태로 전환되는 시점부터 기 설정된 카운트타임이 경과할 때까지 웨이크업모드로 판단한다. 모드검출부(35)는 웨이크업모드에서 상기 카운트타임이 경과하기 전까지 적어도 하나의 제3선택신호(Sel k)를 출력한다. 선택기(31)는 상기 선택신호(Sel k)에 따라 레지스터 k(Reg k)를 선택하여 각 제3분주비(Dk)를 분주기(20)로 출력한다.

- [0067] 모드 검출부(35)는 적어도 하나 이상의 웨이크업모드(wakeup 1 내지 wakeup N-2)를 둘 수 있다. 상기 웨이크업 모드들은 기 설정된 순서에 의할 수 있으며, 기 설정된 순서란 사용자의 설정 또는 설계공정상 필요에 따라 달

라질 수 있고, 예를 들면 제1주파수부터 제2주파수까지 주파수가 옮겨가는(transient) 순서일 수 있다. 각각의 웨이크업모드마다 기 설정된 각각의 카운트타임(counter 1 내지 counter N-2)이 존재한다.

[0068] 모드검출부(35)는 적어도 하나 이상의 각 제3주파수를 기 설정된 각 카운트타임 동안에만 동작주파수로 인가한다. 상기 카운트타임들이 모두 경과(counter expired)하면 모드검출부(35)는 기능블럭의 상태를 활성화모드로 판단하여 선택신호(Sel n)을 출력한다.

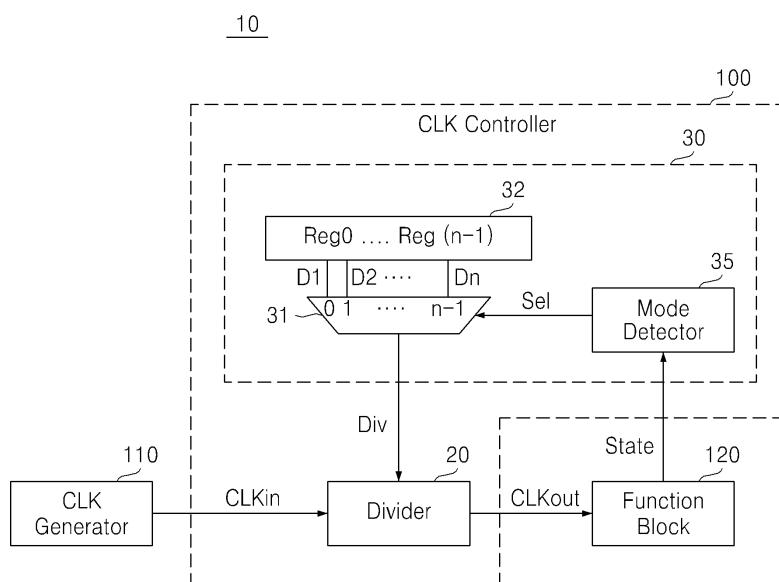

[0069] 도 4는 도 2에 도시된 SoC의 일실시 예를 구체적으로 나타내는 블록도이고, 도 5는 도 4에 도시된 모드검출부의 동작모드를 나타낸 상태도이다.

[0070] 도 4 및 도 5를 참조하면, 먼저 서로 다른 분주비가 총 3개(즉, N=3)라고 가정하자. 즉, 기준클락(CLKin)의 기준주파수를 분주하는 제1분주비(R0), 웨이크업분주비(R1), 제2분주비(R2)가 있다.

[0071] 기능블럭(120)의 초기 상태가 활성화모드(active)라고 하자. 이때 모드검출부(45)는 제1분주비(R0)를 선택하기 위한 제1선택신호(Sel 0)을 출력한다. 선택기(41)는 상기 제1선택신호(Sel 0)에 따라 레지스터 0(Reg 0)을 선택하여 제1분주비(R0)를 분주기(20)로 출력한다.

[0072] 기능블럭(120)의 상태가 비활성화모드(idle)로 판단되면, 모드검출부(45)는 제2분주비(R2)를 선택하기 위한 제2선택신호(Sel 2)을 출력한다. 선택기(41)는 상기 제2선택신호(Sel 2)에 따라 레지스터 2(Reg 2)을 선택하여 제2분주비(R2)를 분주기(20)로 출력한다.

[0073] 기능블럭(120)의 상태가 웨이크업모드(Wakeup)로 판단되면, 모드검출부(45)는 웨이크업분주비(R1)를 선택하기 위한 제3선택신호(Sel 1)을 출력한다. 선택기(41)는 상기 제3선택신호(Sel 1)에 따라 레지스터 1(Reg 1)을 선택하여 웨이크업분주비(R1)를 분주기(20)로 출력한다. 일례로, 제3주파수는 제2주파수의 1/2배일 수 있다.

[0074] 도 6은 본 발명의 일 실시 예에 따른 SoC의 신호 타이밍도이다.

[0075] 도 6을 참조하면, 클락 컨트롤러(100)는 기능블럭(120)에서 출력되는 상태(State) 신호를 모니터링 할 수 있다. 일례로 상태 신호가 하이(high)면 기능블럭(120)의 상태를 활성화(active)모드로 판단하고, 로우(low)면 기능블럭(120)의 상태를 비활성화(idle)모드로 판단할 수 있다. 기능블럭(120)이 활성화모드(active)일 때, 클락 컨트롤러(100)는 제2주파수를 동작주파수로 설정하고, 기능블럭(120)에 동작클락(CLKout)을 인가한다. 기능블럭(120)이 비활성화모드(Idle)로 전환되면, 클락 컨트롤러(100)는 제1주파수를 동작주파수로 설정하고, 기능블럭(120)에 동작클락(CLKout)을 인가한다. 기능블럭(120)이 다시 활성화모드(active)로 전환되면, 클락 컨트롤러(100)는 제1주파수를 제2주파수로 다시 설정하여, 기능블럭(120)에 동작클락(CLKout)을 인가한다.

[0076] 그 결과, 기능블럭(120)은 제2주파수가 아닌 제1주파수의 동작클락으로 동작하게 되어 불필요한 전력소모를 감소할 수 있다. 또한 경우에 따라 불가피하게 기능블럭(120)의 동작클락(CLKout)을 게이팅할 수 있는 경우에 지속적으로 제1주파수의 동작클락을 공급함으로써 지속적으로 제 기능을 하도록 유지할 수 있다.

[0077] 도 7은 본 발명의 다른 실시 예에 따른 SoC의 신호 타이밍도이다.

[0078] 도 7을 참조하면, 기능블럭(120)의 활성화모드(active) 및 비활성화모드(idle)일 때 클락 컨트롤러(100)의 동작은 도 6과 동일하다. 설명의 편의를 위하여, 도 6와의 차이점을 위주로 설명한다.

[0079] 기능블럭(120)이 비활성화모드(idle)에서 활성화모드(active)로 전환될 때, 클락 컨트롤러(100)는 도 6과 달리, 웨이크업모드가 추가된다.

[0080] 웨이크업모드란 비활성화 상태에서 활성화 상태로 전환되는 시점부터 기 설정된 카운트타임 동안을 말한다. 웨이크업모드에서는 제3주파수를 제1주파수 내지 제2주파수 범위 내의 주파수를 동작주파수로 설정한다. 이때 제3주파수는 제2주파수의 1/2배일 수 있으나 이에 한정되지 아니하고, 다양한 실시 예에 따라 레지스터 단(35)으로부터 중간 주파수에 상응하는 분주비(Div)을 선택하여 다양하게 설정 가능하다.

[0081] 비활성화모드의 기능블럭(120)에 갑자기 제2주파수의 동작클락(CLKout)이 인가되면, 기능블럭(120)에 인가되는 전류가 갑자기 증가하여 전압 강하(Voltage drop)가 일어날 수 있다. 따라서, 제1주파수와 제2주파수의 중간단계인 제3주파수를 일정 카운트타임 동안 인가한다. 그 결과, 기능블럭(120)은 제1주파수에서 제2주파수로 갑작스런 천이로 인해 일어나는 전압 강하 없이 동작하게 되어 오동작이 방지된다.

[0082] 도 8은 본 발명의 또 다른 일 실시 예에 따른 SoC의 신호 타이밍도이다.

[0083] 도 8을 참조하면, 기능블럭(120)의 활성화모드(active) 및 비활성화모드(idle)일 때 클락 컨트롤러(100)의 동작

은 도 6 및 도 7과 동일하다. 설명의 편의를 위하여, 도 7과의 차이점을 위주로 설명한다.

[0084] 기능블럭(120)이 비활성화 상태(idle)에서 활성화 상태(active)로 전환될 때, 클락 컨트롤러(100)는 도 5와 달리, 웨이크업모드가 다수의 단계로 존재한다. 다만, 기능블럭(120)은 도 6와 달리 적어도 둘 이상의 웨이크업모드를 가질 수 있다. 설명의 편의를 위하여 제3주파수는 적어도 둘 이상의 웨이크업주파수를 포함한다고 하자.

[0085] 보다 구체적으로 설명하면, 기능블럭(120)이 비활성화 상태(Idle)에서 활성화 상태(active)로 전환되는 시점부터 기 설정된 제1 카운트타임(Wakeup 1) 동안, 클락컨트롤러(100)는 제1웨이크업주파수로 동작클락을 인가한다.

[0086] 제1 카운트타임이 완료되는 시점부터 기 설정된 제2 카운트타임(Wakeup 2) 동안, 클락컨트롤러(100)는 제2웨이크업주파수로 동작클락을 인가한다. 이때 제1웨이크업 주파수와 제2웨이크업 주파수는 제1주파수 내지 제2주파수 이내의 범위로써 제1웨이크업주파수는 제2웨이크업주파수보다 작을 수 있다. 즉, 모드검출부(35)에 의해 적어도 둘 이상의 서로 다른 웨이크업 주파수들이 각각의 카운트타임 동안 설정된다.

[0087] 상기 실시 예에서는 2개의 웨이크업주파수만을 예시하고 있으나, 이에 한정되는 것은 아니고 다양한 실시 예에 따라 둘 이상의 웨이크업주파수로 구현할 수 있다.

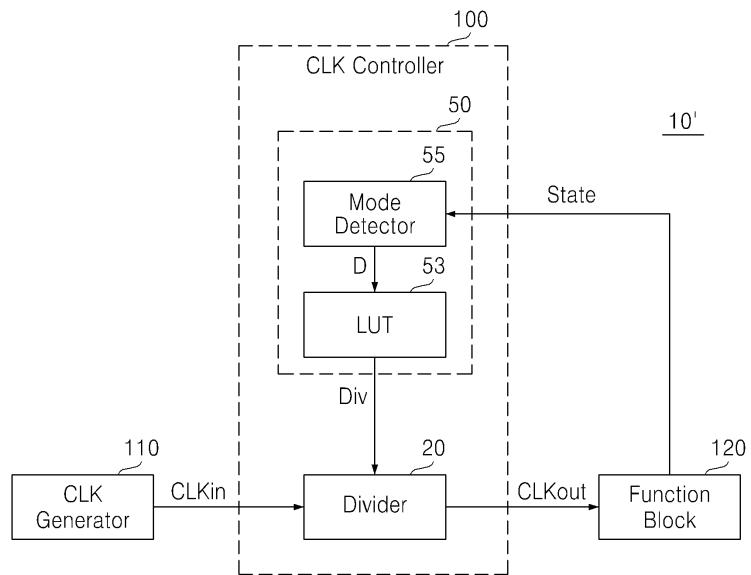

[0088] 도 9는 도 1에 도시된 SoC의 또다른 일실시 예를 구체적으로 나타내는 블록도이다. 설명의 편의를 위해 도 2와의 차이점을 위주로 설명한다.

[0089] 도 9를 참조하면, 클락컨트롤러(100)는 분주기컨트롤러(50) 및 분주기(20)를 포함한다. 분주기컨트롤러(50)는 모드검출부(55) 및 루업테이블(LookUp Table; 이하 LUT, 53)을 포함한다.

[0090] 모드검출부(55)는 상기 기능블럭의 상태(State)를 모니터링 하여 비활성화(idle)모드, 적어도 하나의 웨이크업모드 또는 활성화(active)모드 중 어느 하나로 판단한 결과를 선택신호(D)로 출력한다. 즉, 모드검출부(55)는 도 2의 모드검출부(35)와 동일하게 동작한다.

[0091] 루업테이블(LUT, 53)은 상기 다수의 분주비들을 저장하고, 상기 선택신호(Se1)에 따라 상기 분주비들 중 어느 하나를 출력한다. 일례로 루업테이블(53)은 상기 다수의 분주비들을 저장하고, 상기 선택신호(Se1)에 따라 상기 비활성화(idle) 모드 시 제1분주비를 출력하고, 상기 활성화(active) 모드 시 제2분주비를 출력하며 상기 웨이크업 모드 시 적어도 하나의 제3분주비를 출력한다. 상기 제1분주비 내지 상기 제3분주비는 0이 아닌 서로 다른 수로써, 상기 제1분주비는 상기 제3분주비보다 크고, 상기 제3분주비는 상기 제2분주비보다 크다.

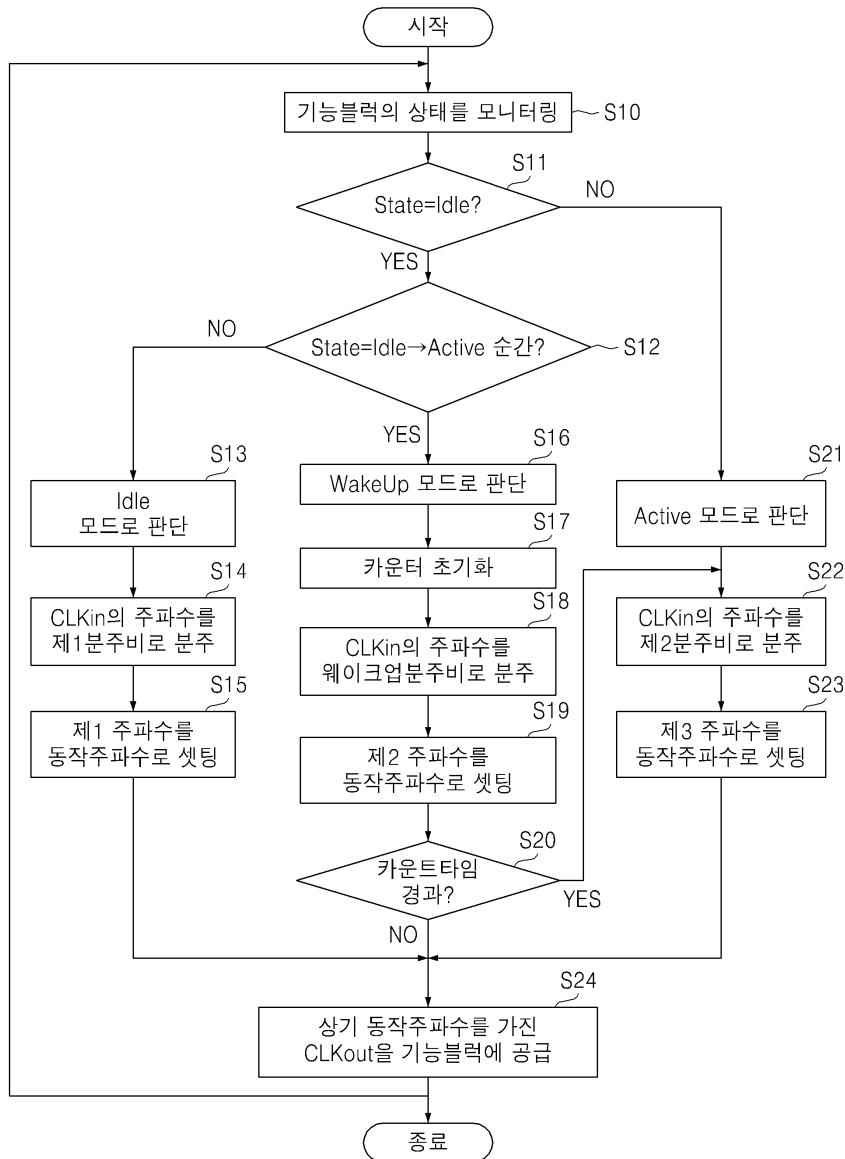

[0092] 도 10은 본 발명의 일 실시 예에 따른 클락 제어 방법을 나타낸 흐름도이다.

[0093] 도 10을 참조하면, 먼저 클락컨트롤러는 기능블럭의 상태를 모니터링한다(S10).

[0094] 기능블럭(120)이 비활성화 상태(idle)이고 비활성화 상태에서 활성화 상태로 전환된 시점이 아니면(S12), 모드검출부(35)는 비활성화모드(idle, S13)로 판단한다. 그리고 비활성화모드에 상응하여 기준클락의 주파수를 제1분주비으로 분주한다(S14). 클락컨트롤러는 S14단계에서 분주된 결과인 제1주파수를 동작주파수로 설정하고(S15), 상기 동작주파수를 가진 동작클락을 기능블럭에 공급한다(S24).

[0095] 기능블럭(120)이 비활성화 상태(idle)이고 비활성화 상태에서 활성화 상태로 전환된 시점이면(S12), 모드검출부(35)는 웨이크업모드로 판단한다(S16). 카운터는 카운트타임을 초기화하고(S17), 모드검출부(35)는 웨이크업모드에 상응하여 기준클락의 주파수를 웨이크업분주비로 분주한다(S18). 클락컨트롤러는 S18단계에서 분주된 결과인 제3주파수를 동작주파수로 설정하고(S19), 기 설정된 카운트타임이 경과할 때까지(S20) 상기 동작주파수를 가진 동작클락을 기능블럭에 공급한다(S24). 상기 카운트타임이 경과하면, 클락컨트롤러는 기준클락의 주파수를 제2분주비로 분주한(S22) 제2주파수를 동작주파수로 설정하고(S23), 그 동작클락을 기능블럭에 공급한다(S24).

[0096] 기능블럭(120)이 활성화 상태(active)이면, 모드검출부(35)는 활성화모드로 판단한다(S21). 그리고 활성화모드에 상응하여 기준클락의 주파수를 상기 제2분주비으로 분주한다(S22). 클락컨트롤러는 S21단계에서 분주된 결과인 제2주파수를 동작주파수로 설정하고(S23), 상기 동작주파수를 가진 동작클락을 기능블럭에 공급한다(S24).

[0097] 모드 검출부(35)는 기능블럭이 상기 각 동작클락(CLKout)에 따라 동작하더라도 계속하여 상기 기능블럭의 상태를 모니터링 하여 그 상태에 따른 동작클락을 공급할 수 있도록 제어한다.

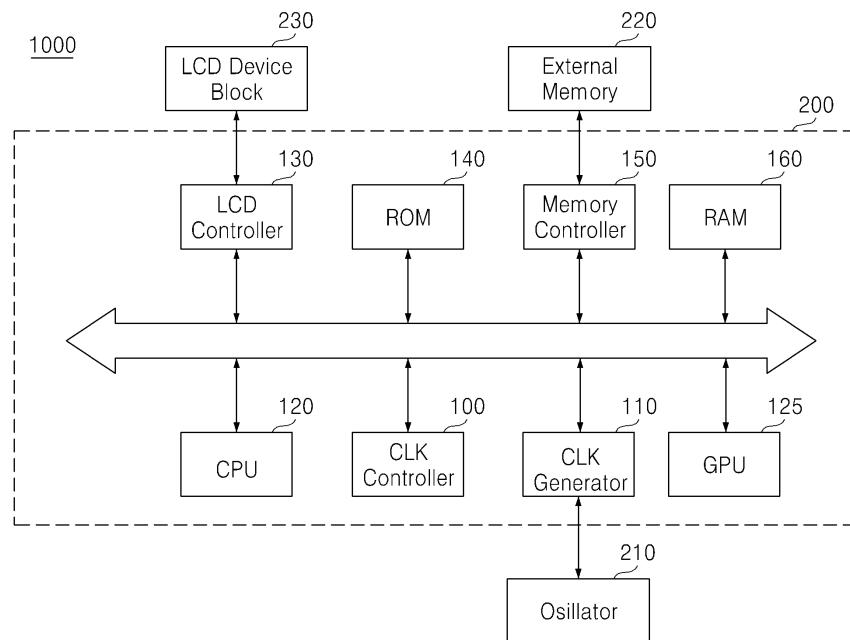

[0098] 도 11은 본 발명의 실시 예들에 따른 SoC를 포함한 반도체시스템의 블럭도이다.

[0099] 도 11을 참조하면, 반도체 시스템(1000)은 이동 전화기, 스마트폰, 태블릿 컴퓨터(tablet computer), PDA(personal digital assistant), EDA(enterprise digital assistant), 디지털 스틸 카메라(digital still

camera), 디지털 비디오 카메라(digital video camera), PMP(portable multimedia player), PDN(personal navigation device 또는 portable navigation device), 손으로 들고 다닐 수 있는 게임 콘솔(handheld game console), 또는 e-북(e-book)과 같이 손으로 들고 다닐 수 있는 장치(handheld device)로 구현될 수 있다.

- [0100] 반도체 시스템(1000)은 SoC(200), 오실레이터(210), 외부 메모리 장치(220) 및 디스플레이 디바이스(230)를 포함한다. SoC(200)은 애플리케이션 프로세서(Application Processor)일 수 있다. 애플리케이션 프로세서는 반도체 시스템(1000)의 동작을 전반적으로 제어할 수 있다.

- [0101] SoC(200)는 클락컨트롤러(100), 클락생성기(110), CPU(120), GPU(125), LCD 컨트롤러(130), ROM(read only memory; 140), RAM(random access memory; 160), 메모리 컨트롤러(150) 및 버스를 포함할 수 있다. SoC(200)는 도시된 구성요소 외에도 다른 구성요소, 예컨대, 전원 관리 유닛(power management unit), TV 프로세서 등을 더 포함할 수 있다. 기능블럭은 CPU(120), GPU(125), 메모리컨트롤러(150) 및 주변회로 제어유닛(미도시) 등을 의미할 수 있다.

- [0102] CPU(120)는 메모리(150 또는 220)에 저장된 프로그램들 및/또는 데이터를 처리 또는 실행할 수 있다. 예컨대, CPU(120)는 클락컨트롤러(100)로부터 출력된 동작클락에 응답하여 상기 프로그램들 및/또는 상기 데이터를 처리 또는 실행할 수 있다.

- [0103] CPU(120)는 멀티-코어 프로세서(multi-core processor)로 구현될 수 있다. 상기 멀티-코어 프로세서는 두 개 또는 그 이상의 독립적인 실질적인 프로세서들('코어들(cores)'이라고 불림)을 갖는 하나의 컴퓨팅 컴포넌트(computing component)이고, 상기 프로세서들 각각은 프로그램 명령들(program instructions)을 읽고 실행할 수 있다. 상기 멀티-코어 프로세서는 다수의 가속기를 동시에 구동할 수 있으므로, 상기 멀티-코어 프로세서를 포함하는 데이터 처리 시스템은 멀티-가속(multi-acceleration)을 수행할 수 있다.

- [0104] GPU(125)는 CPU(120)의 부하를 감소시킬 수 있고, 그래픽 처리와 관련된 프로그램 명령들을 읽고 수행할 수 있다. GPU(125)는 메모리 인터페이스(미도시)를 통해 메모리(220)로부터 출력된 데이터를 수신하거나 GPU(125)에 의해 처리된 데이터를 메모리(220)로 전송한다. 예를 들어 GPU(125)는 클락컨트롤러(100)로부터 출력된 동작클락에 응답하여 상기 프로그램들 및/또는 상기 데이터를 처리 또는 실행할 수 있다.

- [0105] 메모리(220)에 저장된 프로그램들 및/또는 데이터는 필요에 따라 CPU(120) 또는 GPU(125) 내 메모리에 로드(load)될 수 있다.

- [0106] ROM(140)은 영구적인 프로그램들 및/또는 데이터를 저장할 수 있다. ROM(140)은 EPROM(erasable programmable read-only memory) 또는 EEPROM(electrically erasable programmable read-only memory)으로 구현될 수 있다.

- [0107] RAM(160)은 프로그램들, 데이터, 또는 명령들(instructions)을 일시적으로 저장할 수 있다. 예컨대, 메모리(220)에 저장된 프로그램들 및/또는 데이터는 CPU(120)의 제어 또는 ROM(140)에 저장된 부팅 코드(booting code)에 따라 RAM(160)에 일시적으로 저장될 수 있다. RAM(160)은 DRAM(dynamic RAM) 또는 SRAM(static RAM)으로 구현될 수 있다.

- [0108] 메모리 컨트롤러(150)는 외부 메모리 장치(220)와 인터페이스하기 위한 블록이다. 메모리 컨트롤러(150)는 메모리 장치(220)의 동작을 전반적으로 제어하며, 또한 호스트와 메모리 장치(220)간의 제반 데이터 교환을 제어한다. 예컨대, 메모리 컨트롤러(150)는 호스트의 요청에 따라 메모리 컨트롤러(150)를 제어하여 데이터를 쓰거나 데이터를 독출한다.

- [0109] 여기서, 호스트는 CPU(120), LCD 컨트롤러(130)와 같은 마스터 장치일 수 있다.

- [0110] 메모리 장치(220)는 데이터를 저장하기 위한 저장 장소로서, OS(Operating System), 각종 프로그램들, 및 각종 데이터를 저장할 수 있다. 메모리 장치(220)는 DRAM 일수 있으나, 이에 한정되는 것은 아니다. 예컨대, 메모리 장치(220)는 비휘발성 메모리 장치(플래시 메모리, PRAM, MRAM, ReRAM, 또는 FeRAM 장치)일 수도 있다. 본 발명의 다른 실시 예에서는 메모리 장치(220)는 SoC(200) 내부에 구비되는 내장 메모리일 수 있다.

- [0111] 각 구성 요소는 시스템 버스를 통하여 서로 통신할 수 있다.

- [0112] 디스플레이 디바이스(230)는 기능블럭(120)에 로드된 멀티미디어를 디스플레이할 수 있다. 본 실시 예에서 디스플레이 디바이스(230)는 LCD 디바이스이지만, 본 발명의 실시 예가 이에 한정되는 것은 아니다. 예컨대, 디스플레이 디바이스는 LED, OLED 디바이스, 혹은 다른 종류의 디바이스일 수 있다.

- [0113] 디스플레이 디바이스 컨트롤러(130)는 디스플레이 디바이스(230)의 동작을 제어한다.

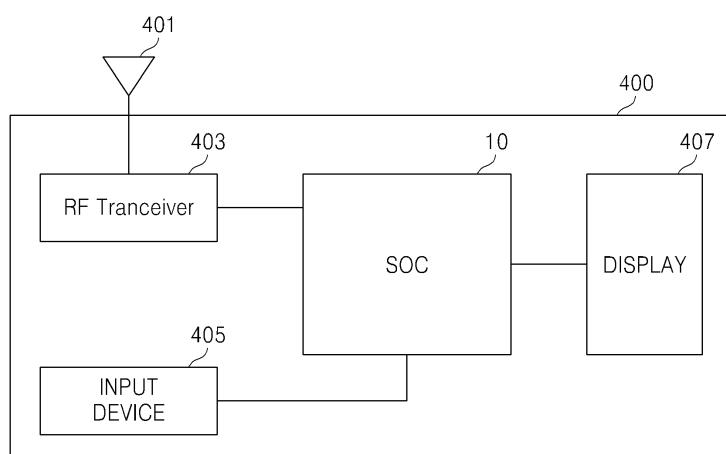

- [0114] 도 12는 도 1에 도시된 SoC를 포함하는 반도체 시스템의 일 실시 예를 나타낸다.

- [0115] 도 12를 참조하면, 반도체 시스템(400)은 도 1에 도시된 SoC(10), 안테나(401), 무선 송수신기(403), 입력 장치(405), 및 디스플레이(407)를 포함한다.

- [0116] 무선 송수신기(403)는 안테나(401)를 통하여 무선 신호를 주거나 받을 수 있다. 예컨대, 무선 송수신기(403)는 안테나(401)를 통하여 수신된 무선 신호를 SoC(10)에서 처리될 수 있는 신호로 변경할 수 있다.

- [0117] 따라서, SoC(10)는 무선 송수신기(403)로부터 출력된 신호를 처리하고 처리된 신호를 디스플레이(407)로 전송할 수 있다. 또한, 무선 송수신기(403)는 SoC(10)로부터 출력된 신호를 무선 신호로 변경하고 변경된 무선 신호를 안테나(401)를 통하여 외부 장치로 출력할 수 있다.

- [0118] 입력 장치(405)는 SoC(10)의 동작을 제어하기 위한 제어 신호 또는 SoC(10)에 의하여 처리될 데이터를 입력할 수 있는 장치로서, 터치 패드(touch pad)와 컴퓨터 마우스(computer mouse)와 같은 포인팅 장치(pointing device), 키패드(keypad), 또는 키보드로 구현될 수 있다.

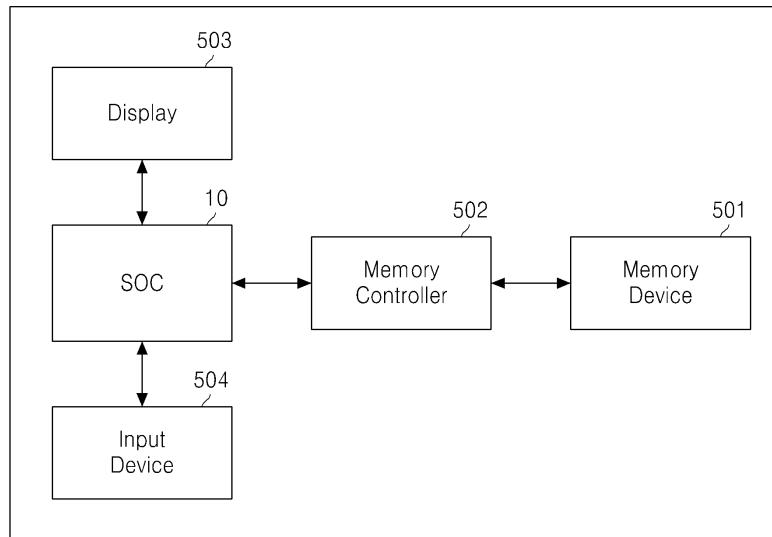

- [0119] 도 13은 도 1에 도시된 SoC를 포함하는 컴퓨터 시스템의 일 실시 예를 나타낸다. 도 13을 참조하면, 도 1에 도시된 SoC(10)를 포함하는 컴퓨터 시스템(500)은 PC(personal computer), 네트워크 서버(Network Server), 태블릿(tablet) PC, 넷-북(net-book), e-리더(e-reader), PDA(personal digital assistant), PMP(portable multimedia player), MP3 플레이어, 또는 MP4 플레이어로 구현될 수 있다.

- [0120] 컴퓨터 시스템(500)은 SoC(10), 메모리 장치(501)와 메모리 장치(501)의 데이터 처리 동작을 제어할 수 있는 메모리 컨트롤러(502), 디스플레이(503) 및 입력 장치(504)를 포함한다.

- [0121] SoC(10)는 입력 장치(504)를 통하여 입력된 데이터에 따라 메모리 장치(501)에 저장된 데이터를 디스플레이(503)를 통하여 디스플레이할 수 있다. 예컨대, 입력 장치(504)는 터치 패드 또는 컴퓨터 마우스와 같은 포인팅 장치, 키패드, 또는 키보드로 구현될 수 있다. SoC(10)는 컴퓨터 시스템(500)의 전반적인 동작을 제어할 수 있고 메모리 컨트롤러(502)의 동작을 제어할 수 있다.

- [0122] 실시 예에 따라 메모리 장치(501)의 동작을 제어할 수 있는 메모리 컨트롤러(502)는 SoC(10)의 일부로서 구현될 수 있고 또한 SoC(10)와 별도의 칩으로 구현될 수 있다.

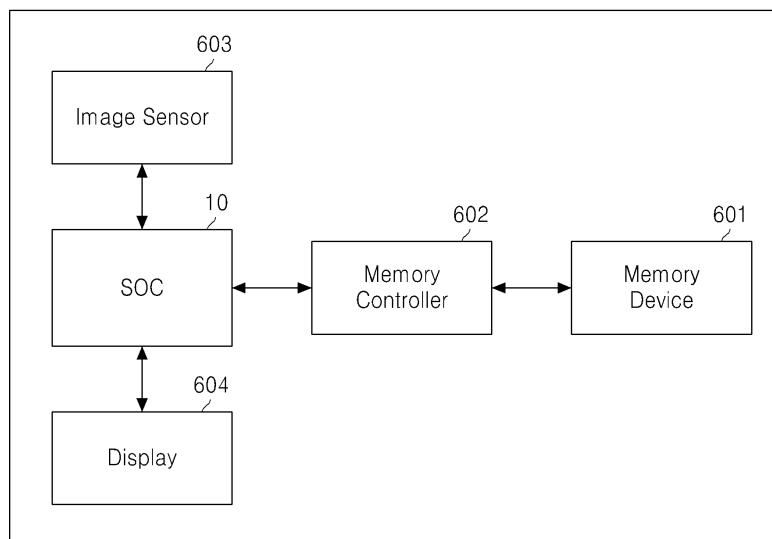

- [0123] 도 14는 도 1에 도시된 SoC를 포함하는 컴퓨터 시스템의 다른 실시 예를 나타낸다. 도 14를 참조하면, 도 1에 도시된 SoC(10)를 포함하는 컴퓨터 시스템(600)은 이미지 처리 장치(image process device), 예컨대 디지털 카메라 또는 디지털 카메라가 부착된 이동 전화기 또는 스마트폰으로 구현될 수 있다.

- [0124] 컴퓨터 시스템(600)은 SoC(10), 메모리 장치(601)와 메모리 장치(601)의 데이터 처리 동작, 예컨대 라이트 동작 또는 리드 동작을 제어할 수 있는 메모리 컨트롤러(602)를 포함한다. 또한, 컴퓨터 시스템(600)은 이미지 센서(603) 및 디스플레이(604)를 더 포함한다.

- [0125] 컴퓨터 시스템(600)의 이미지 센서(603)는 광학 이미지를 디지털 신호들로 변환하고, 변환된 디지털 신호들은 SoC(10) 또는 메모리 컨트롤러(602)로 전송된다. SoC(10)의 제어에 따라, 상기 변환된 디지털 신호들은 디스플레이(604)를 통하여 디스플레이 되거나 또는 메모리 컨트롤러(602)를 통하여 메모리 장치(601)에 저장될 수 있다.

- [0126] 또한, 메모리 장치(601)에 저장된 데이터는 SoC(10) 또는 메모리 컨트롤러(602)의 제어에 따라 디스플레이(604)를 통하여 디스플레이 된다. 실시 예에 따라 메모리 장치(601)의 동작을 제어할 수 있는 메모리 컨트롤러(602)는 SoC(10)의 일부로서 구현될 수 있고 또한 SoC(10)와 별개의 칩으로 구현될 수 있다.

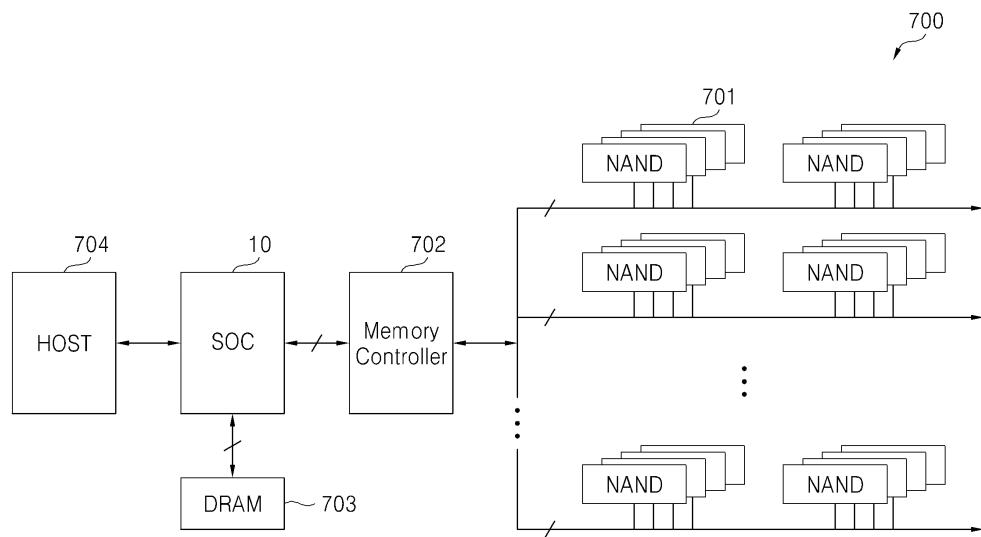

- [0127] 도 15는 도 1에 도시된 SoC를 포함하는 메모리 시스템의 또 다른 실시 예를 나타낸다. 도 15를 참조하면, 메모리 시스템(700)은 SSD(solid state drive)와 같은 데이터 처리 장치로 구현될 수 있다.

- [0128] 메모리 시스템(700)은 다수의 메모리 장치들(701), 다수의 메모리 장치들(701) 각각의 데이터 처리 동작을 제어할 수 있는 메모리 컨트롤러(702), DRAM과 같은 휘발성 메모리 장치(703), 메모리 컨트롤러(702)와 호스트(704) 사이에서 주고받는 데이터를 휘발성 메모리 장치(703)에 저장하는 것을 제어하는 SoC(10)를 포함할 수 있다.

- [0129] 본 발명은 또한 컴퓨터로 읽을 수 있는 기록매체에 컴퓨터가 읽을 수 있는 코드로서 구현하는 것이 가능하다. 컴퓨터가 읽을 수 있는 기록매체는 컴퓨터 시스템에 의하여 읽혀질 수 있는 데이터가 저장되는 모든 종류의 기록장치를 포함한다. 컴퓨터가 읽을 수 있는 기록매체의 예로는 ROM, RAM, CD-ROM, 자기 테이프, 플로피 디스크,

광 데이터 저장장치 등이 있다.

- [0130] 또한 컴퓨터가 읽을 수 있는 기록매체는 네트워크로 연결된 컴퓨터 시스템에 분산되어, 분산방식으로 컴퓨터가 읽을 수 있는 코드가 저장되고 실행될 수 있다. 그리고 본 발명을 구현하기 위한 기능적인(functional) 프로그램, 코드 및 코드 세그먼트들은 본 발명이 속하는 기술분야의 프로그래머들에 의해 용이하게 추론될 수 있다.

- [0131] 도 16은 기능블럭의 상태를 고려하지 않고 동작클락을 인가한 경우의 전류 및 전압 그래프이고, 도 17은 기능블럭의 상태를 고려하여 동작클락을 인가한 경우의 전류 및 전압 그래프이다.

- [0132] 도 16을 참조하면, 기능블럭(120)의 상태를 고려하지 않고 동작클락을 인가한 경우 전압강하(A)가 나타난 것을 볼 수 있다. 그러나 도 17에 도시된 바와 같이, 기능블럭(120)이 비활성화모드에서 활성화모드로 전환시 제3주파수의 동작클락을 인가하는 경우, 기능블럭(120)으로 전류(V)가 서서히 인가되어 전압강하(B)의 폭이 감소하는 것을 볼 수 있다.

- [0133] 또한 기능블럭의 상태를 고려하지 않고 동작클락을 인가한 경우, 제1주파수에서 갑자기 큰 제2주파수의 동작클락이 인가되면서 도 16의 전류(I)슬로프(slope)가 급상승한다. 그러나 도 17에 도시된 바와 같이, 기능블럭(120)이 비활성화모드에서 활성화모드로 전환시 제3주파수의 동작클락을 카운트타임 동안 인가하는 경우, 기능블럭(120)으로 전류(I)가 서서히 인가되어 전류슬로프가 비교적 완만하게 상승하는 것을 볼 수 있다. 그 결과 기능블럭(120)은 큰 전압강하(A) 또는 전류슬로프 급상승에 의한 오동작 없이 동작할 수 있다.

- [0134] 발명은 도면에 도시된 일 실시 예를 참고로 설명되었으나 이는 예시적인 것에 불과하며, 본 기술 분야의 통상의 지식을 가진 자라면 이로부터 다양한 변형 및 균등한 타 실시 예가 가능하다는 점을 이해할 것이다. 따라서, 본 발명의 진정한 기술적 보호 범위는 첨부된 등록청구범위의 기술적 사상에 의해 정해져야 할 것이다.

### 부호의 설명

- |                       |                       |

|-----------------------|-----------------------|

| 10 : SoC              | 100 : 클락컨트롤러          |

| 110 : 클락생성기           | 120 : 기능블럭            |

| 20 : 분주기              | 30, 40 : 분주기컨트롤러      |

| 31, 41 : 선택기          | 32, 42, 43, 44 : 레지스터 |

| 35, 45, 50 : 모드검출부    |                       |

| 1 : 활성화모드             | 2 : 비활성화모드            |

| 4 : 웨이크업모드            | 4 : 카운터               |

| 55 : 검출부              | 53 : 루프테이블            |

| 130 : 디스플레이 디바이스 컨트롤러 |                       |

| 140 : ROM             | 150 : 메모리컨트롤러         |

| 160 : RAM             | 210 : 오실레이터           |

| 220 : 외부메모리장치         | 230 : 디스플레이 디바이스      |

| 200 : SoC             | 1000 : 전자시스템          |

## 도면

## 도면1

## 도면2

## 도면3

35

## 도면4

10

## 도면5

45

## 도면6

## 도면7

## 도면8

## 도면9

## 도면10

도면11

도면12

## 도면13

500

## 도면14

600

도면15

도면16

도면17

【심사관 직권보정사항】

【직권보정 1】

【보정항목】 청구범위

【보정세부항목】 제11항

【변경전】

제6항에 있어서

【변경후】

제9항에 있어서