(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4825529号

(P4825529)

(45) 発行日 平成23年11月30日(2011.11.30)

(24) 登録日 平成23年9月16日(2011.9.16)

(51) Int.Cl.

H01L 23/12 (2006.01)

F 1

H01L 23/12

Q

H01L 23/12 501W

請求項の数 7 (全 18 頁)

(21) 出願番号 特願2006-27830 (P2006-27830)

(22) 出願日 平成18年2月6日 (2006.2.6)

(65) 公開番号 特開2007-208153 (P2007-208153A)

(43) 公開日 平成19年8月16日 (2007.8.16)

審査請求日 平成21年2月2日 (2009.2.2)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人 100080001

弁理士 筒井 大和

(72) 発明者 嶋貫 好彦

北海道亀田郡七飯町字中島145番地 株式会社ルネサス北日本セミコンダクタ内

審査官 越本 秀幸

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

平面形状が方形状からなる主面、平面形状が方形状からなり、かつ前記主面とは反対側の裏面、前記主面に形成された複数のワイヤ接合部、前記裏面に形成された複数のランド部、前記主面と前記裏面の間に形成された複数の第1貫通孔、前記主面と前記裏面の間に形成された複数の第2貫通孔、および前記複数の第1貫通孔のそれぞれの内壁に形成され、前記複数のワイヤ接合部と前記複数のランド部とをそれぞれ電気的に接続するメッキ膜を有する配線基板と、

前記配線基板の主面上に搭載された半導体チップと、

前記半導体チップの複数の電極と前記配線基板の主面に形成された前記複数のワイヤ接合部とをそれぞれ電気的に接続する複数のワイヤと、

前記半導体チップ及び前記複数のワイヤを封止する樹脂体と、

前記複数のランド部上に形成された複数の外部端子と、

を有し、

前記複数の第1貫通孔のうち、前記複数のランド部において最外周に配置された第1ランド部と電気的に接続されるメッキ膜が形成された貫通孔は、前記第1ランド部より前記配線基板の中心側に形成されており、

前記複数の第2貫通孔は、前記複数の第1貫通孔および前記複数のランド部より前記配線基板の外側にそれぞれ形成されており、かつ、前記複数のワイヤ接合部のうちの前記配線基板の第1辺と並ぶ第1方向に沿って形成された複数の第1ワイヤ接合部の配列延長線

10

20

と、前記複数のワイヤ接合部のうちの前記配線基板の前記第1辺と交差する第2辺と並ぶ第2方向に沿って形成された複数の第2ワイヤ接合部の配列延長線との交点部にそれぞれ形成されており、

前記複数の第2貫通孔のそれぞれは、前記複数のワイヤ接合部、前記複数のランド部、および前記複数の第1貫通孔のそれぞれの内壁に形成された前記メッキ膜と接続されていないことを特徴とする半導体装置。

【請求項2】

請求項1記載の半導体装置において、前記複数の第1貫通孔の内部に金属膜が埋め込まれていることを特徴とする半導体装置。

【請求項3】

10

請求項1記載の半導体装置において、前記複数の第1貫通孔及び前記複数の第2貫通孔の内部に金属膜が埋め込まれていることを特徴とする半導体装置。

【請求項4】

請求項1記載の半導体装置において、前記複数の第1貫通孔はレーザによって形成されていることを特徴とする半導体装置。

【請求項5】

請求項1記載の半導体装置において、前記複数の第1貫通孔及び前記複数の第2貫通孔はレーザによって形成されていることを特徴とする半導体装置。

【請求項6】

20

請求項1記載の半導体装置において、前記配線基板は、複数のコア材を貼り合わせて形成されていることを特徴とする半導体装置。

【請求項7】

請求項1記載の半導体装置において、前記複数の第1貫通孔のそれぞれは、前記複数のワイヤ接合部よりも前記配線基板の中心側に形成されていることを特徴とする半導体装置。

。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置及びその組み立てに関し、特に、配線基板を有する半導体装置に適用して有効な技術に関する。

30

【背景技術】

【0002】

大型基板の正面に半田バンプを介して複数個の半導体チップを搭載した後、各半導体チップをエポキシ樹脂でモールドし、次いでバーンイン試験および電気特性評価試験を行った後、ダイシング装置を使って大型基板を切断することにより、複数個のBGAを製造する技術がある（例えば、特許文献1参照）。

【特許文献1】特開平9-321088号公報（図7）

【発明の開示】

【発明が解決しようとする課題】

【0003】

40

BGA (Ball Grid Array)やCSP (Chip Size Package)等に使用される配線基板は、1層から成るコア材の正面及び裏面に配線パターンが形成されている。

【0004】

しかしながら、半導体装置の薄型化に伴い、配線基板の厚さも薄くする傾向にある。これにより、コア材も薄くなるためコア材の機械的強度が低くなり縦方向（基板厚さ方向）に亀裂が生じ易くなる。

【0005】

そこで、配線基板の機械的強度を向上するために、薄いコア材の片面に配線パターンを形成したものを準備し、それぞれのコア材を貼り合わせた、コア材が複数層から成る配線基板が使用されてきている。例えば、コア材が2層から成る配線基板を用いた半導体装置

50

がある。

【0006】

しかしながら、半導体装置の更なる小型化に伴い、特にチップサイズと配線基板がほぼ同じ大きさからなるCSPにおいて、温度サイクル試験等で貼り合わせたコア材が剥離（コアクラック）するという問題が生じた。その結果、配線基板の正面と裏面を電気的に接続する貫通孔（スルーホール）内に形成された配線が断線する。

【0007】

この剥離の問題について本発明者らが検討した結果、以下のことが明らかになった。

【0008】

まず、半導体チップは、例えばシリコンからなるため、その熱膨張係数は約1.4である。これに対し、半導体チップを実装するための配線基板の熱膨張係数は約1.0と半導体チップよりも遙かに大きい。すなわち、温度サイクル試験において貼り合わせたコア材のうち、熱膨張係数の差により半導体チップを実装している側のコア材の膨張がはんだボールを形成している側のコア材に比べ抑えられるため、貼り合わせた界面で剥離が生じる。

10

【0009】

なお、半導体装置の薄型化に伴い、コア材の厚さも薄くなっているため、配線基板自体の機械的強度が低下していることも原因である。

【0010】

さらに、剥離は温度サイクル試験によってパッケージ外周から生じ易いため、特に基板において貫通孔が複数のランドよりも外周に配置されていると、パッケージ外周からのコア材の剥離により、貼りあわせた部分で貫通孔が分離して断線に至ることが問題である。

20

【0011】

本発明の目的は、半導体装置の信頼性の向上を図ることができる技術を提供することにある。

【0012】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0013】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、以下のとおりである。

30

【0014】

すなわち、本発明は、配線基板の複数のランド部において最外周に配置された第1ランド部と電気的に接続されるメッキ膜が形成された第1貫通孔は、前記第1ランド部より前記配線基板の中心側に形成されているものである。

【発明の効果】

【0016】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば、以下のとおりである。

【0017】

40

半導体装置の配線基板において最外周に配置されたランド部に電気的に接続される第1貫通孔が、ランド部より配線基板の中心側に形成されていることにより、温度サイクル試験等で配線基板の外周からクラックが生じても第1貫通孔より外側に配置されたランド部でクラックの進展を抑制することができる。これにより、半導体装置の信頼性の向上を図ることができる。

【発明を実施するための最良の形態】

【0018】

以下の実施の形態では特に必要なとき以外は同一または同様な部分の説明を原則として繰り返さない。

【0019】

50

さらに、以下の実施の形態では便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明などの関係にある。

【0020】

また、以下の実施の形態において、要素の数など（個数、数値、量、範囲などを含む）に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合などを除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良いものとする。

【0021】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。

【0022】

（実施の形態1）

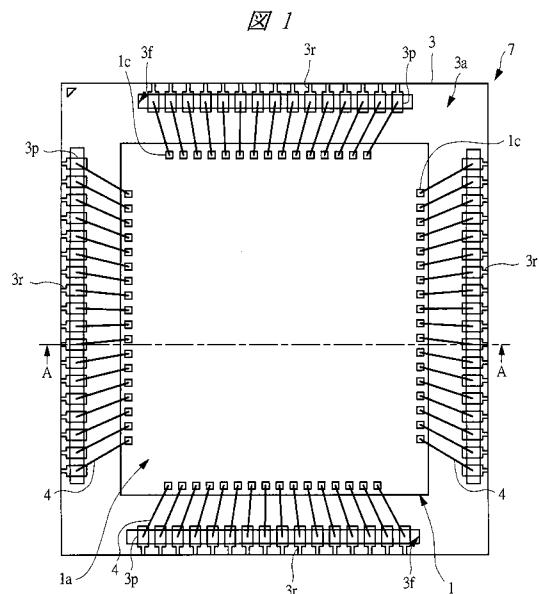

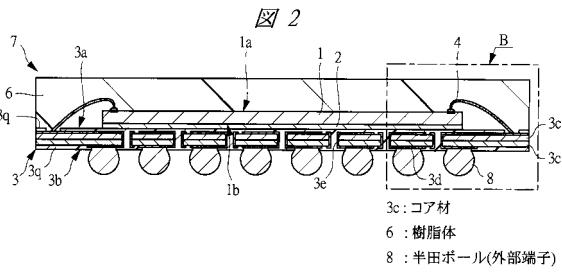

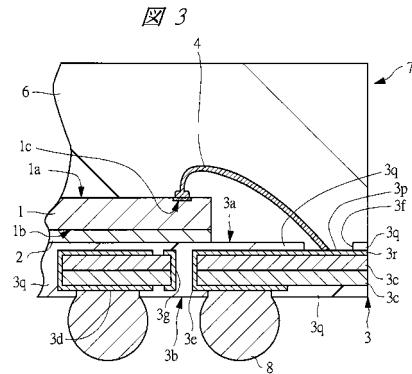

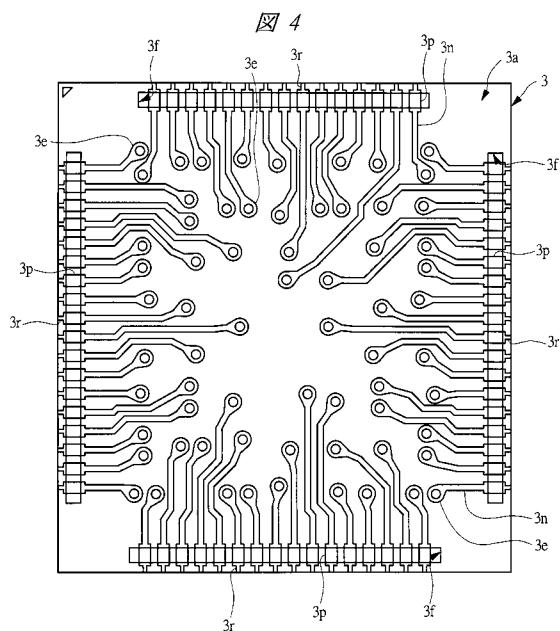

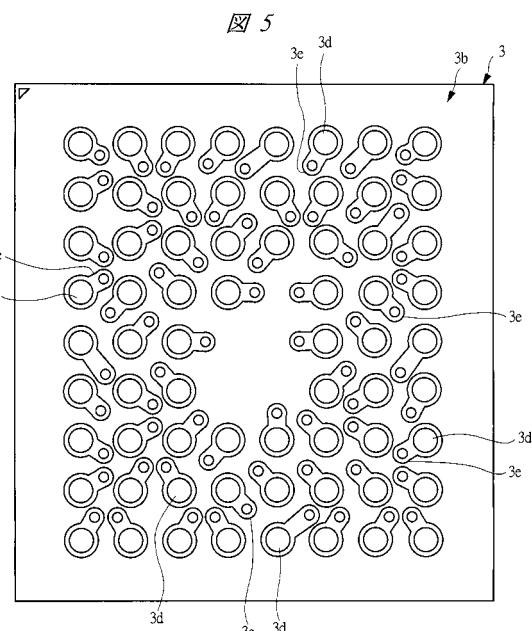

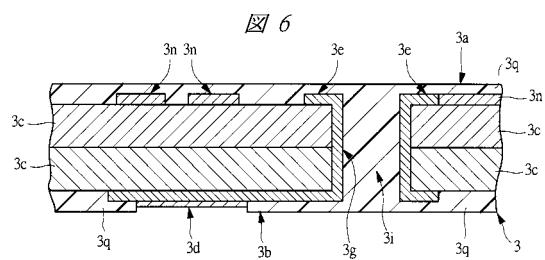

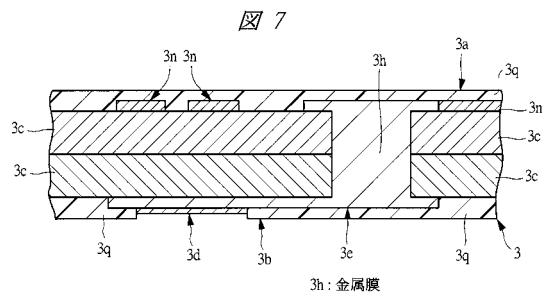

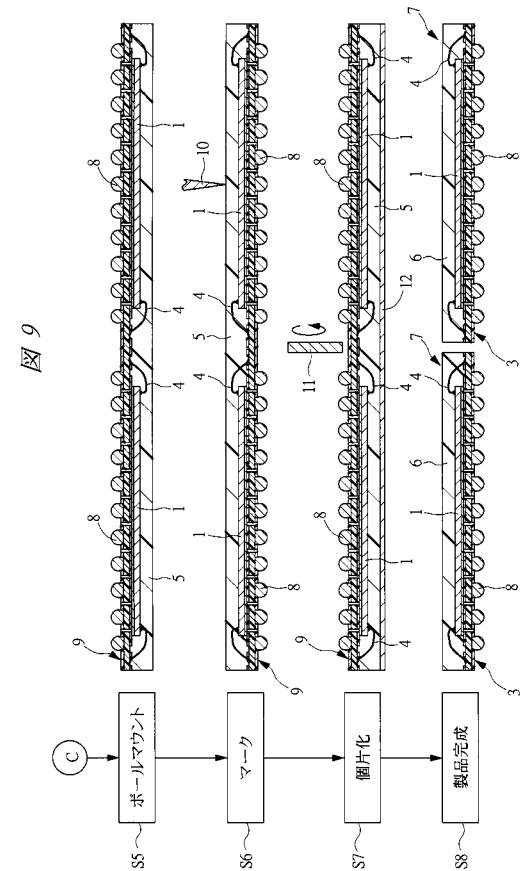

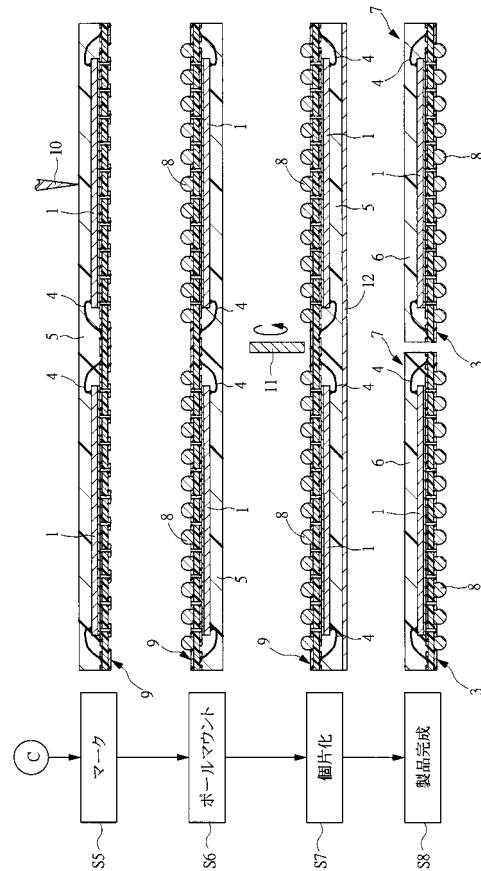

図1は本発明の実施の形態1の半導体装置の構造の一例を封止体を透過して示す平面図、図2は図1に示すA-A線に沿って切断した断面の構造を示す断面図、図3は図2に示すB部の構造を示す拡大部分断面図、図4は図1に示す半導体装置に組み込まれる配線基板の正面側の導体パターンの一例を示す平面図、図5は図4に示す配線基板の裏面側の導体パターンの一例を示す裏面図である。また、図6は図4に示す配線基板のスルーホールの構造の一例を示す拡大部分断面図、図7は図4に示す配線基板の変形例のスルーホールの構造を示す拡大部分断面図である。さらに、図8は図1に示す半導体装置の組み立てにおける樹脂モールドまでの組み立ての一例を示す製造プロセスフロー図、図9は図1に示す半導体装置の組み立てにおける樹脂モールド後の組み立ての一例を示す製造プロセスフロー図、図10は図1に示す半導体装置の組み立てにおける樹脂モールド後の組み立ての変形例を示す製造プロセスフロー図である。

【0023】

本実施の形態1の半導体装置は、配線基板上に半導体チップ1が搭載された樹脂封止型の小型の半導体パッケージであり、本実施の形態1ではその一例として、図1～図3に示すようなCSP7を取り上げて説明する。なお、CSP7は、配線基板の裏面3bに複数の外部端子である半田ボール8が格子状に配置されて取り付けられており、したがって、CSP7は、BGA型の半導体パッケージである。

【0024】

図1～図3に示すCSP7の構造について説明すると、配線基板であるパッケージ基板3と、パッケージ基板3の正面3aに搭載され、かつ集積回路を有する半導体チップ1と、半導体チップ1の電極であるパッド1cとパッケージ基板3のボンディング用端子3pとを電気的に接続する導電性のワイヤ4と、パッケージ基板3の裏面3bの複数のランド部3d上に設けられた複数の外部端子である半田ボール8と、樹脂体6とからなる。

【0025】

なお、半導体チップ1は、例えば、シリコンなどによって形成され、その正面1aには集積回路が形成されている。また、半導体チップ1におけるその厚さと交差する平面形状は方形状であり、本実施の形態1では正方形である。さらに、図1に示すように正面1aの周縁部には集積回路と電気的に接続される複数のパッド1cが形成されている。また、このパッド1cと、パッケージ基板3の正面3aの周縁部に配置されたボンディング用端子3pとが導電性のワイヤ4によってそれぞれ電気的に接続されている。このワイヤ4は、例えば、金線等である。

【0026】

また、半導体チップ1は、図3に示すように、その裏面1bが、ペースト剤やダイアタッチフィルム等の接着剤2を介してパッケージ基板3に固着され、正面1aを上方に向けた状態でパッケージ基板3に搭載されている。

10

20

30

40

50

## 【0027】

また、樹脂体6は、例えば、エポキシ樹脂等からなるとともに、パッケージ基板3の正面3a側に形成されており、半導体チップ1及び複数の導電性のワイヤ4を樹脂封止するものである。

## 【0028】

また、パッケージ基板3の裏面3bに設けられた複数の外部端子である半田ボール8は、例えば、Pb-Sn等の半田からなり、パッケージ基板3の裏面3bに格子状に配置されている。

## 【0029】

ここで、パッケージ基板3は、正面3aと、正面3aに対向する裏面3bと、正面3aの周縁部に形成された複数のボンディング用端子（ワイヤ接合部）3pと、裏面3bに形成された複数のランド部3dと、正面3a及び裏面3bに形成され、かつ複数のボンディング用端子3pと複数のランド部3dの間にそれぞれ形成された複数のスルーホール（第1貫通孔）3eとを有している。すなわち、正面3aの周縁部に形成された複数のボンディング用端子3pは、それぞれ対応するスルーホール3eを介して裏面3bのランド部3dに電気的に接続されている。

## 【0030】

なお、パッケージ基板3におけるその厚さと交差する平面形状は方形状であり、本実施の形態1では正方形である。

## 【0031】

また、パッケージ基板3は、図3に示すように比較的薄い2枚のコア材3cを貼り合わせて形成されている。2枚のコア材3cの貼り合わせ後の厚さは、例えば、0.1mm程度であり、表裏面のソルダレジスト膜3qを含めた基板の総厚は、例えば、0.2mm程度である。これにより、パッケージ基板3の機械的強度の向上が図られているとともに、パッケージ基板3の薄型化に対応している。すなわち、CSP7の薄型化に対応している。

## 【0032】

また、本実施の形態1のCSP7は、小型の半導体パッケージであるが、図1及び図2に示すように、特にチップサイズとパッケージ基板3がほぼ同じ大きさのものである。すなわち、パッケージ基板3は、半導体チップ1より僅かに大きい程度の面積であり、半導体チップ1の外側のパッケージ基板3の周縁部の領域に、複数のボンディング用端子3pが並んで設けられており、これらのボンディング用端子3pと半導体チップ1のパッド1cがそれぞれワイヤ4で電気的に接続されている。

## 【0033】

なお、複数のボンディング用端子3pは、図3及び図4に示すようにパッケージ基板3の正面3aの周縁部において、ソルダレジスト膜3qの開口窓3fに露出している。さらに、ボンディング用端子3pは、その一端はそれぞれ配線3nを介してスルーホール3eに接続され、他端には電解メッキ処理用の給電線3rが接続されている。したがって、ボンディング用端子3p、配線3n及びスルーホール3eには電解メッキ処理が施されている。パッケージ基板3のボンディング用端子3p、配線3n、給電線3r、スルーホール3e及びランド部3d等の導体パターンは、例えば、銅合金からなり、さらにこれらの導体パターンに施されるメッキは、例えば、Ni/Auメッキである。本実施の形態1では、例えばサブトラクティブ法によりパッケージ基板3を製造した場合について説明したが、これに限定されるものではない。例えば、セミアディティブ法によりパッケージ基板3を製造する場合は、下地となるCuシード層を無電解メッキ処理により形成した後、電解メッキ処理によりCu配線を形成してもよい。

## 【0034】

一方、パッケージ基板3の裏面3bには、図5に示すように、それぞれスルーホール3eとランド部3dが相互に接続されてなる複数の導体パターンが形成されており、複数のランド部3dのうち、パッケージ基板3の裏面3bにおいて最外周に配置されたランド部（第1ランド部）3dと電気的に接続されているスルーホール3eは、最外周に配置され

10

20

30

40

50

たランド部（第1ランド部）3dよりパッケージ基板3の中心側に形成されている。すなわち、スルーホール3eとランド部3dが相互に接続されてなる複数の導体パターンのうち、ランド部3dが最外周に配置された前記導体パターンにおいて、スルーホール3eはランド部3dより内側に形成されている。

#### 【0035】

なお、正面3a側のスルーホール3eと裏面3b側のスルーホール3eは、図3に示すように、ホール内壁に形成されたメッキ膜3gによって電気的に接続されている。

#### 【0036】

本実施の形態1のCSP7では、パッケージ基板3において、最外周に配置されたランド部（第1ランド部）3dに電気的に接続されるスルーホール3eが、最外周に配置されたランド部（第1ランド部）3dよりパッケージ基板3の中心側（内側）に形成されることにより、温度サイクル試験等でパッケージ基板3の外周から剥離が生じてもスルーホール3eより外側に配置されたランド部（第1ランド部）3dで剥離の進展を抑制することができる。

10

#### 【0037】

これにより、剥離がスルーホール3eに対して直接的なダメージを与えることを抑制でき、不良に至るまでの時間を稼ぐことができる。

#### 【0038】

その結果、スルーホール3eでの断線の発生を低減することができ、CSP7の信頼性の向上を図ることができる。

20

#### 【0039】

なお、最外周ではなく、外側から2列目及びそれより内側に形成されたランド部（第2ランド部）3dを有する導体パターンにおいては、必ずしもスルーホール3eが対応するランド部（第2ランド部）3dより基板の中心側に配置されていなくてもよく、少なくとも複数のスルーホール（第1貫通孔）3eが最外周のランド部（第1ランド部）3dよりパッケージ基板3の中心側（内側）に配置されれば、外周から2列目及びそれより内側に形成されたランド部（第2ランド部）3dより外側に配置されていてもよい。

#### 【0040】

また、図6及び図7は、パッケージ基板3のスルーホール3e内に孔埋め材を充填する構造の例を示すものであり、例えば、図6に示すパッケージ基板3では、スルーホール3eの孔埋め材として、ソルダレジスト等の絶縁膜3iを充填している。前記孔埋め材としてソルダレジスト等の絶縁膜3iを充填することにより、基板のコスト上昇を抑えることができる。

30

#### 【0041】

一方、図7に示す変形例のパッケージ基板3では、スルーホール3eの孔埋め材として、銅合金等の金属膜3hが充填されている。前記孔埋め材として、スルーホール3e内に金属膜3hが埋め込まれていることにより、スルーホール3e内にボイドが形成されることを阻止できる。更には、パッケージ基板3の正面3a及び裏面3bに形成された配線3nと一体形成することが可能であるため、機械的強度を向上することができる。その結果、放熱性も向上させることができるだけでなく、仮に剥離（クラック）がパッケージ基板3の最外周に形成されたランド部（第1ランド部）3dを通過してスルーホール3eにまで到達したとしても断線不良を抑制することができ、CSP7の信頼性を向上させることができる。

40

#### 【0042】

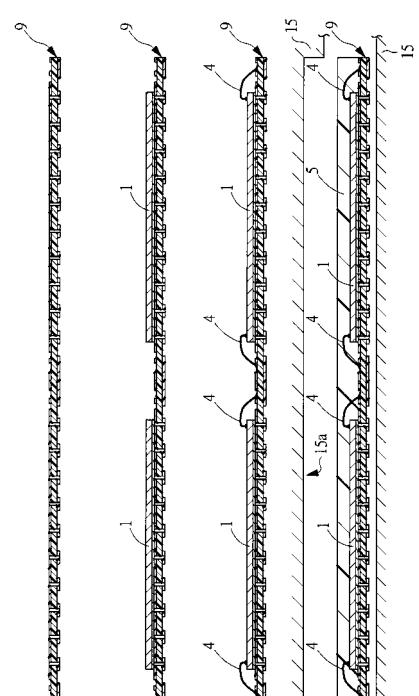

次に、本実施の形態1のCSP7の製造方法を、図8～図10に示す製造プロセスフロー図を用いて説明する。

#### 【0043】

まず、図8のステップS1に示す基板準備を行う。ここでは、複数のパッケージ基板3を形成する領域が区画配置された多数個取り基板9を準備する。なお、パッケージ基板3を形成する領域では、最外周に配置されたランド部（第1ランド部）3dと電気的に接続

50

されるスルーホール 3 e が、ランド部（第1ランド部）3 d よりパッケージ基板 3 を形成する領域の中心側（内側）に形成されている基板を準備する。

【0044】

その後、ステップ S 2 に示すダイボンディングを行って多数個取り基板 9 上に図 3 に示す接着剤 2 を介して半導体チップ 1 を固着する。その際、パッケージ基板 3 を形成する領域の周縁部のボンディング用端子 3 p 列の内側に半導体チップ 1 を搭載する。

【0045】

その後、ステップ S 3 に示すワイヤボンディングを行う。ここでは、図 3 に示すように、半導体チップ 1 の正面 1 a のパッド 1 c と、これに対応する多数個取り基板 9 のパッケージ基板 3 のワイヤ接合部であるボンディング用端子 3 p とを金線等の導電性のワイヤ 4 によって電気的に接続する。

【0046】

その後、ステップ S 4 に示す樹脂モールドを行う。ここでは、多数個取り基板 9 上において、複数の半導体チップ 1 や複数のワイヤ 4 を樹脂成形金型 15 の 1 つのキャビティ 15 a で一括して覆って樹脂封止し、これによって一括封止体 5 を形成する。なお、一括封止体 5 を形成する封止用樹脂は、例えば、熱硬化性のエポキシ樹脂等である。

【0047】

その後、図 9 のステップ S 5 に示すボールマウントを行って図 3 に示すようにパッケージ基板 3 の裏面 3 b の各ランド部 3 d に半田ボール 8 を接続する。

【0048】

その後、ステップ S 6 に示すマークを行う。ここではレーザマーキング法等でマーキング 10 を行って一括封止体 5 にマークを付す。なお、マーキング 10 は、例えば、インクマーキング法などで行ってもよい。

【0049】

その後、ステップ S 7 に示す個片化を行う。ここでは、一括封止体 5 の表面にダイシングテープ 12 を貼り、ダイシングテープ 12 で固定した状態でダイシングブレード 11 によって切断して各 CSP 7 に個片化する。

【0050】

これにより、ステップ S 8 に示すように CSP 7 の組み立てを完了して製品完成となる。

【0051】

なお、図 10 は樹脂モールド後の組み立ての変形例を示す製造プロセスフロー図である。

【0052】

図 10 に示す変形例は、マークを行った後にボールマウントを行うものである。

【0053】

ボールマウントの工程は、パッケージ基板 3 のランド部 3 d に半田を塗布した後、リフロー処理により半田ボール 8 を形成する。このため、ボールマウントの工程においても、このリフロー処理によりパッケージ基板 3 が更に反る問題が生じる。マークの工程では、レーザマーキング法などでマーキングを行うが、パッケージ基板 3 が反った状態では、一括封止体 5 の表面に垂直にレーザを照射することが困難となるため、一括封止体 5 の表面にマークが付されないというマーキング不良が発生する。

【0054】

そこで、図 10 に示す変形例は、パッケージ基板 3 が反る要因の一つである半田ボール 8 形成時のリフロー処理を行う前に、先にマークの工程を行うものである。これにより、マーキング不良を抑制することができる。

【0055】

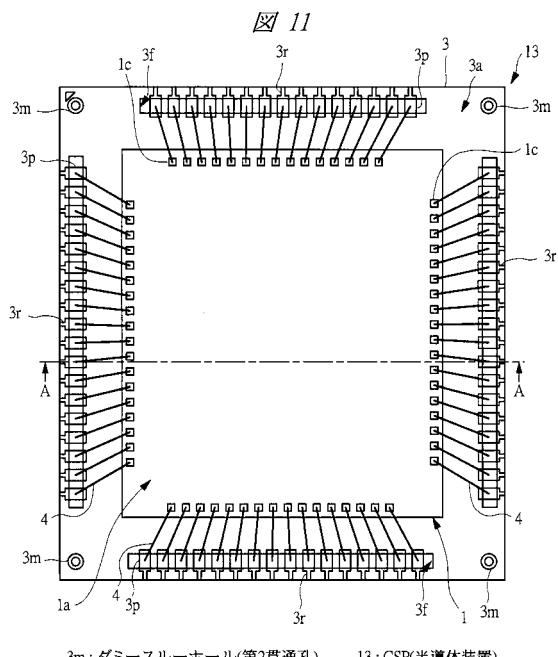

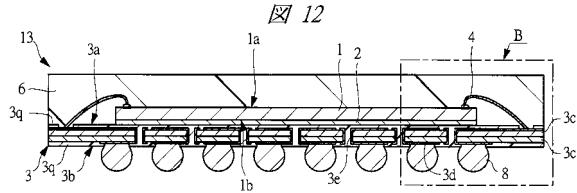

（実施の形態 2）

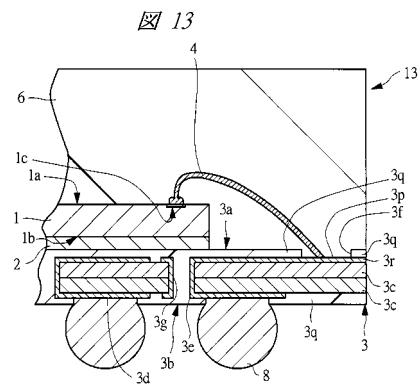

図 11 は本発明の実施の形態 2 の半導体装置の構造の一例を封止体を透過して示す平面図、図 12 は図 11 に示す A - A 線に沿って切断した断面の構造を示す断面図、図 13 は

10

20

30

40

50

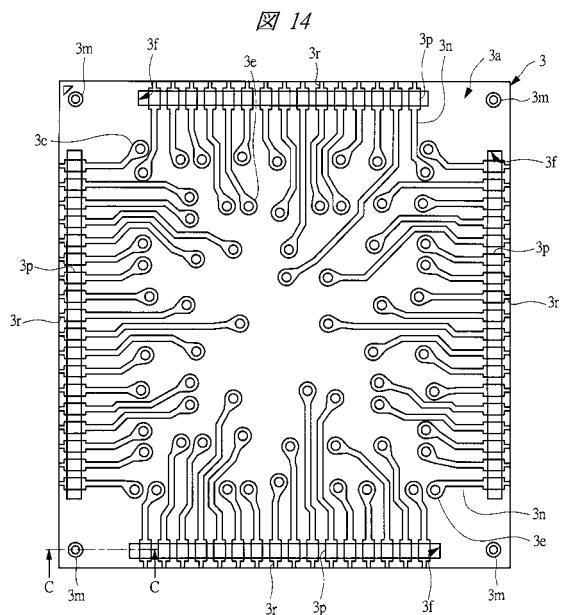

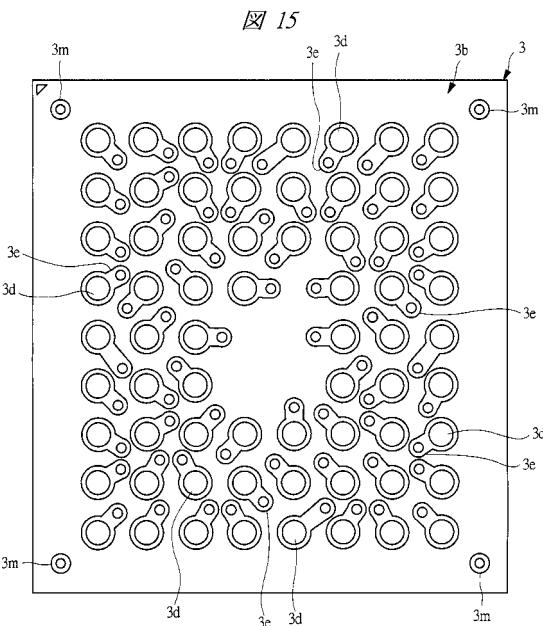

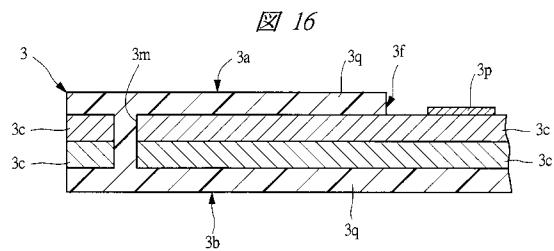

図12に示すB部の構造を示す拡大部分断面図である。また、図14は図11に示す半導体装置に組み込まれる配線基板の正面側の導体パターンの一例を示す平面図、図15は図14に示す配線基板の裏面側の導体パターンの一例を示す裏面図、図16は図14に示すC-C線に沿って切断した断面の構造を示す拡大部分断面図である。

【0056】

図11～図13に示す本実施の形態2の半導体装置は、実施の形態1のCSP7と同様に、配線基板上に半導体チップ1が搭載された樹脂封止型の小型のCSP13である。

【0057】

本実施の形態2のCSP13では、パッケージ基板3の裏面3bの複数のランド部3dにおいて、図15に示すように最外周に配置されたランド部(第1ランド部)3dと電気的に接続されるスルーホール3eは、ランド部(第1ランド部)3dよりパッケージ基板3の中心側に形成されている。さらに、これに加えて複数のスルーホール(第1貫通孔)3eより外側に複数のダミースルーホール(第2貫通孔)3mが形成されており、本実施の形態2では、パッケージ基板3の4つの角部付近にダミースルーホール3mが形成されている。詳細には、パッケージ基板3において、複数のダミースルーホール(第2貫通孔)3mは、複数のスルーホール(第1貫通孔)3e及び複数のランド部3dより外側に形成されており、さらに、第1方向に形成された複数のボンディング用端子3pの配列延長線と第1方向と交差する第2方向に形成された複数のボンディング用端子3pの配列延長線との交点付近にダミースルーホール3mが形成されている。

【0058】

すなわち、最外周に配置されたランド部(第1ランド部)3dと電気的に接続されるスルーホール(第1貫通孔)3eが、ランド部(第1ランド部)3dより内側に形成されており、さらにパッケージ基板3の4つの角部付近にダミースルーホール(第2貫通孔)3mが形成されている。

【0059】

なお、ダミースルーホール3mは、図14～図16に示すように、ランド部3dやスルーホール3e、さらにボンディング用端子3p等の他の導体パターンと接続していないノンコネクトホールである。ダミースルーホール3mは、パッケージ基板3の周縁部に形成されるものであるが、特に応力が集中し易い角部に形成することが好ましい。上記した剥離(コアクラック)はパッケージ基板3の外周から進展するが、外周の中でも特にパッケージ基板3の中心から最も遠い箇所、すなわち角部付近に応力が集中し易いためである。

【0060】

また、CSP13は、CSP7と同様に、小型の半導体パッケージであり、パッケージ基板3は、半導体チップ1より僅かに大きい程度ある。そこで、本実施の形態2のCSP13のように、最外周に配置されたランド部3dと電気的に接続されるスルーホール3eを、ランド部3dより内側に形成することにより、周縁部に形成するダミースルーホール3mとスルーホール3eとが同列配置になることを避けられる。つまり、最外周に配置されたランド部3dと電気的に接続されるスルーホール3eを、ランド部3dより内側に形成することにより、パッケージ基板3が半導体チップ1より僅かに大きなCSP13であってもパッケージ基板3の周縁部にダミースルーホール3mを配置することが可能になる。

【0061】

ただし、半導体チップ1とパッケージ基板3の大きさは、極めて近いため、パッケージ基板3の角部を含む周縁部にダミースルーホール3mを形成した場合、これらダミースルーホール3mの更に外側に放熱用ビア等の他の貫通孔を形成するスペースは無い。

【0062】

本実施の形態2のCSP13によれば、最外周に配置されたランド部(第1ランド部)3dと電気的に接続されるスルーホール(第1貫通孔)3eが、ランド部3dより内側に形成され、さらにパッケージ基板3の周縁部にダミースルーホール(第2貫通孔)3mが形成されていることにより、温度サイクル試験等でパッケージ基板3の外周から剥離が生

10

20

30

40

50

じてもダミースルーホール 3 m によって剥離の進展を抑制することができる。さらに、剥離が内側に進展したとしても最外周のランド部 3 d でクラックの進展を抑制することができる。

【 0 0 6 3 】

これにより、実施の形態 1 に比べスルーホール 3 e における断線の発生をさらに低減することができ、C S P 1 3 の信頼性の向上をさらに図ることができる。

【 0 0 6 4 】

なお、ダミースルーホール 3 m 内に充填する孔埋め材としては、実施の形態 1 と同様に、ソルダレジスト等の絶縁膜 3 i を充填してもよいし、または、銅合金等の金属膜 3 h を充填してもよい。ただし、ダミースルーホール 3 m 内に金属膜 3 h を充填する場合、ダミースルーホール 3 m に導体膜を形成するとともに前記導体膜に繋がる給電線 3 r が接続されている必要がある。

【 0 0 6 5 】

また、本実施の形態 2 の C S P 1 3 は、少なくともスルーホール 3 e の外側に複数のダミースルーホール 3 m が設けられていればよく、最外周に配置されたランド部 3 d と電気的に接続されるスルーホール 3 e が、必ずしもランド部 3 d より内側に形成されていなくてもよい。

【 0 0 6 6 】

本実施の形態 2 の C S P 1 3 のその他の構造と、C S P 1 3 によって得られるその他の効果については、C S P 7 と同様であるため、その重複説明は省略する。

【 0 0 6 7 】

( 実施の形態 3 )

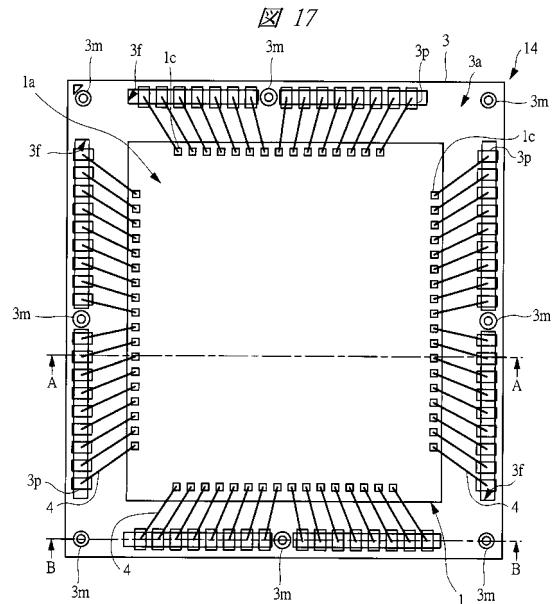

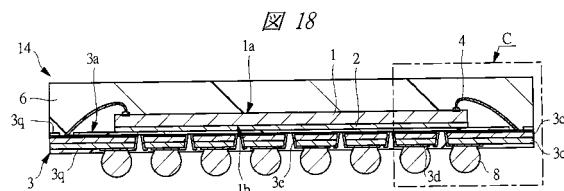

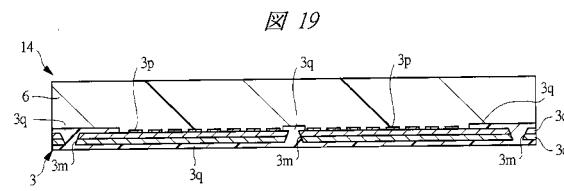

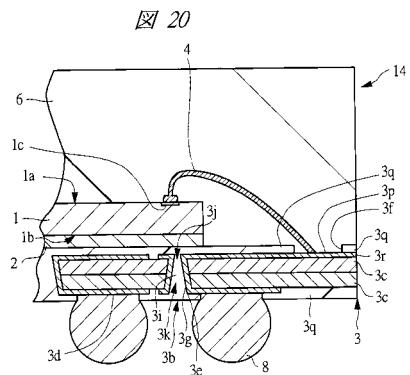

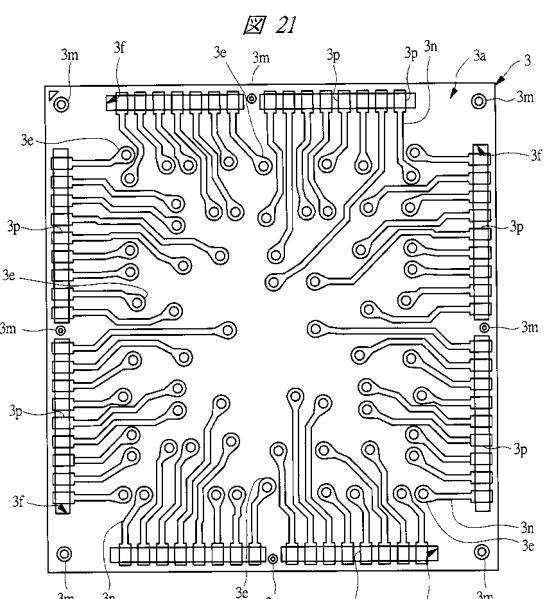

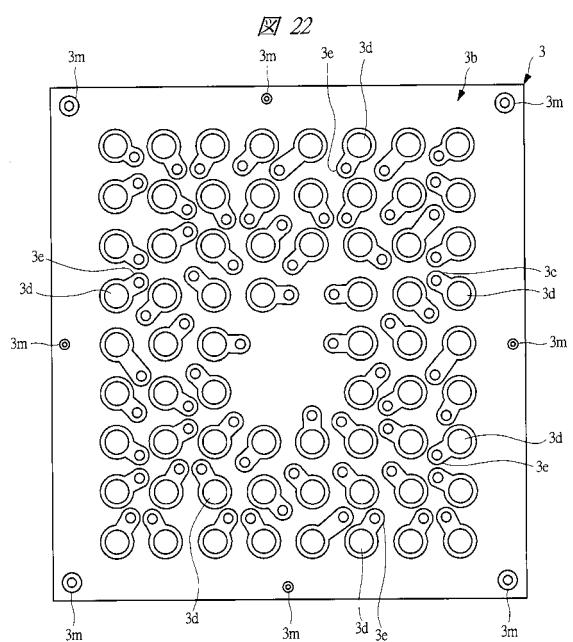

図 1 7 は本発明の実施の形態 3 の半導体装置の構造の一例を封止体を透過して示す平面図、図 1 8 は図 1 7 に示す A - A 線に沿って切断した断面の構造を示す断面図、図 1 9 は図 1 7 に示す B - B 線に沿って切断した断面の構造を示す断面図、図 2 0 は図 1 8 に示す C 部の構造を示す拡大部分断面図である。さらに、図 2 1 は図 1 7 に示す半導体装置に組み込まれる配線基板の正面側の導体パターンの一例を示す平面図、図 2 2 は図 2 1 に示す配線基板の裏面側の導体パターンの一例を示す裏面図である。

【 0 0 6 8 】

図 1 7 ~ 図 2 0 に示す本実施の形態 3 の半導体装置は、実施の形態 1 の C S P 7 と同様に、配線基板上に半導体チップ 1 が搭載された樹脂封止型の小型の C S P 1 4 である。

【 0 0 6 9 】

本実施の形態 3 の C S P 1 4 では、パッケージ基板 3 の裏面 3 b の複数のランド部 3 d において、図 2 2 に示すように最外周に配置されたランド部 3 d と電気的に接続されるスルーホール 3 e は、ランド部 3 d よりパッケージ基板 3 の中心側に形成されている。さらに、これに加えて複数のスルーホール ( 第 1 貫通孔 ) 3 e より外側に複数のダミースルーホール ( 第 2 貫通孔 ) 3 m が形成されており、本実施の形態 2 では、図 2 1 に示すようにパッケージ基板 3 の 4 つの角部付近 ( 第 1 方向に形成された複数のボンディング用端子 3 p の配列延長線と第 1 方向と交差する第 2 方向に形成された複数のボンディング用端子 3 p の配列延長線との交点付近 ) と、ボンディング用端子 3 p の列間にダミースルーホール 3 m が形成されている。

【 0 0 7 0 】

また、C S P 1 4 では、パッケージ基板 3 のスルーホール 3 e とダミースルーホール 3 m それぞれが、レーザ加工によって形成されている。レーザ加工では、基板に貫通孔を形成する場合、ドリルで貫通孔を形成する場合に比較して貫通孔の孔径を非常に小さくすることができる。さらに、図 2 0 に示すように、貫通孔におけるレーザの進行方向の前側の開口部 3 j と後ろ側の開口部 3 k とではその大きさが異なる。

【 0 0 7 1 】

レーザ加工においては、レーザの中心の強度が最も高く、中心から離れて外周に向かうにつれてレーザの強度が低くなる。したがって、レーザの中心は強度が高いことにより、

10

20

40

50

基板を貫通するが、これに比べて外周は強度が低いため貫通までは至らず、結果として図20に示すように、スルーホール3eにおける基板の厚さ方向に沿った断面の形状は、台形(正台形)になる。

【0072】

図20に示すパッケージ基板3の場合には、レーザの進行方向の前側の開口部(レーザ照射面とは反対側に形成されるスルーホール3eの開口部)3jは、その形状が、例えば、直径0.02~0.03mm程度の円形であり、一方、レーザの進行方向の後ろ側の開口部(レーザ照射面に形成されるスルーホール3eの開口部)3kは、その形状が、例えば、直径0.05~0.07mm程度の円形である。

【0073】

なお、ダミースルーホール3mを形成する際に、レーザ加工の方向は正面側からでも裏面側からでもどちらでもよい。

【0074】

また、CSP14のパッケージ基板3では、図21に示すように、各ボンディング用端子3pの外側に図4に示すような給電線3rが形成されていない。すなわち、CSP14のパッケージ基板3は、無電解メッキ処理等によって各導体パターンのメッキを形成したものである。

【0075】

また、CSP14は、CSP7と同様に、小型の半導体パッケージであり、パッケージ基板3は、半導体チップ1より僅かに大きい程度ある。したがって、パッケージ基板3の周縁部にダミースルーホール3mを形成するスペースを確保するのが困難である。そこで、本実施の形態3のCSP14では、ボンディング用端子3pの列間にダミースルーホール3mを配置するにあたり、全てのスルーホール3eをレーザ加工によって形成して貫通孔の孔径を非常に小さくすることで、スペースを確保している。すなわち、最外周に配置されたランド部3dと電気的に接続するスルーホール3eを、ランド部3dよりパッケージ基板3の中心側に形成できるとともに、周縁部にダミースルーホール3mを形成することができる。

【0076】

特に、ピン数の増加によってダミースルーホール3mの形成がスペース的に困難な場合、スルーホール3eやダミースルーホール3mをレーザ加工によって形成することに相対的に小径の穴(ドリル加工で開けた穴よりも小さい穴)を開けることが可能となり、ダミースルーホール3mを形成するためのスペースの確保が容易になる。例えば、多ピン化に対応させてボンディング用端子3pの列間に形成する際のダミースルーホール3mは、図21に示すように、可能な限り孔径が小さな方が好ましい。

【0077】

このようにCSP14においても、実施の形態2のCSP13と同様に、最外周に配置されたランド部3dと電気的に接続されるスルーホール3eが、ランド部3dより内側に形成され、さらに4つの角部を含むパッケージ基板3の周縁部にダミースルーホール3mが形成されていることにより、温度サイクル試験等でパッケージ基板3の外周からクラックが生じてもダミースルーホール3mによってクラックの進展を抑制することができる。さらに、クラックが内側に進展したとしても最外周のランド部3dでクラックの進展を抑制することができる。

【0078】

これにより、スルーホール3eにおける断線の発生をさらに低減することができ、CSP14の信頼性の向上をさらに図ることができる。

【0079】

なお、ダミースルーホール3m内に充填する孔埋め材としては、実施の形態1と同様に、ソルダレジスト等の絶縁膜3iを充填してもよいし、または、銅合金等の金属膜3hを充填してもよい。ただし、ダミースルーホール3m内に金属膜3hを充填する場合、ダミースルーホール3mに導体膜を形成するとともに前記導体膜に繋がる給電線3rが接続さ

10

20

30

40

50

れている必要がある。

【0080】

本実施の形態3のCSP14のその他の構造と、CSP14によって得られるその他の効果については、実施の形態2のCSP13と同様であるため、その重複説明は省略する。

【0081】

以上、本発明者によってなされた発明を発明の実施の形態に基づき具体的に説明したが、本発明は前記発明の実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

【0082】

例えば、前記実施の形態1、2及び3では、パッケージ基板3においてコア材3cが2層の場合を説明したが、コア材3cは2層以上の複数の層が貼り合わされて形成されれば何層であってもよい。

【産業上の利用可能性】

【0083】

本発明は、配線基板を有した電子装置に好適である。

【図面の簡単な説明】

【0084】

【図1】本発明の実施の形態1の半導体装置の構造の一例を封止体を透過して示す平面図である。

20

【図2】図1に示すA-A線に沿って切断した断面の構造を示す断面図である。

【図3】図2に示すB部の構造を示す拡大部分断面図である。

【図4】図1に示す半導体装置に組み込まれる配線基板の正面側の導体パターンの一例を示す平面図である。

【図5】図4に示す配線基板の裏面側の導体パターンの一例を示す裏面図である。

【図6】図4に示す配線基板のスルーホールの構造の一例を示す拡大部分断面図である。

【図7】図4に示す配線基板の変形例のスルーホールの構造を示す拡大部分断面図である。

【図8】図1に示す半導体装置の組み立てにおける樹脂モールドまでの組み立ての一例を示す製造プロセスフロー図である。

30

【図9】図1に示す半導体装置の組み立てにおける樹脂モールド後の組み立ての一例を示す製造プロセスフロー図である。

【図10】図1に示す半導体装置の組み立てにおける樹脂モールド後の組み立ての変形例を示す製造プロセスフロー図である。

【図11】本発明の実施の形態2の半導体装置の構造の一例を封止体を透過して示す平面図である。

【図12】図11に示すA-A線に沿って切断した断面の構造を示す断面図である。

【図13】図12に示すB部の構造を示す拡大部分断面図である。

【図14】図11に示す半導体装置に組み込まれる配線基板の正面側の導体パターンの一例を示す平面図である。

40

【図15】図14に示す配線基板の裏面側の導体パターンの一例を示す裏面図である。

【図16】図14に示すC-C線に沿って切断した断面の構造を示す拡大部分断面図である。

【図17】本発明の実施の形態3の半導体装置の構造の一例を封止体を透過して示す平面図である。

【図18】図17に示すA-A線に沿って切断した断面の構造を示す断面図である。

【図19】図17に示すB-B線に沿って切断した断面の構造を示す断面図である。

【図20】図18に示すC部の構造を示す拡大部分断面図である。

【図21】図17に示す半導体装置に組み込まれる配線基板の正面側の導体パターンの一例を示す平面図である。

50

【図22】図21に示す配線基板の裏面側の導体パターンの一例を示す裏面図である。

【符号の説明】

【0085】

- |           |                   |    |

|-----------|-------------------|----|

| 1         | 半導体チップ            |    |

| 1 a       | 正面                |    |

| 1 b       | 裏面                |    |

| 1 c       | パッド（電極）           |    |

| 2         | 接着剤               |    |

| 3         | パッケージ基板（配線基板）     | 10 |

| 3 a       | 正面                |    |

| 3 b       | 裏面                |    |

| 3 c       | コア材               |    |

| 3 d       | ランド部              |    |

| 3 e       | スルーホール（第1貫通孔）     |    |

| 3 f       | 開口窓               |    |

| 3 g       | メッキ膜              |    |

| 3 h       | 金属膜               |    |

| 3 i       | 絶縁膜               |    |

| 3 j , 3 k | 開口部               |    |

| 3 m       | ダミースルーホール（第2貫通孔）  | 20 |

| 3 n       | 配線                |    |

| 3 p       | ボンディング用端子（ワイヤ接合部） |    |

| 3 q       | ソルダレジスト膜          |    |

| 3 r       | 給電線               |    |

| 4         | ワイヤ               |    |

| 5         | 一括封止体             |    |

| 6         | 樹脂体               |    |

| 7         | CSP（半導体装置）        |    |

| 8         | 半田ボール（外部端子）       |    |

| 9         | 多数個取り基板           | 30 |

| 1 0       | マーキング             |    |

| 1 1       | ダイシングブレード         |    |

| 1 2       | ダイシングテープ          |    |

| 1 3 , 1 4 | CSP（半導体装置）        |    |

| 1 5       | 樹脂成形金型            |    |

| 1 5 a     | キャビティ             |    |

【図1】

1: 半導体チップ

1c: パッド(電極)

3a: 主面

3p: ボンディング用端子(ワイヤ接合部)

3r: ワイヤ

4: CSR(半導体装置)

7: CSP(半導体装置)

【図2】

3c: コア材

6: 树脂体

8: 半田ボール(外部端子)

【図3】

【図4】

【図5】

3: パッケージ基板(配線基板)

3b: 裏面

3d: ランド部

3e: スルーホール(第1貫通孔)

【図 6】

【図 7】

【図 8】

【図 9】

【図 10】

【図11】

3m: ダミースルーホール(第2貫通孔)

### 13 : CSP(半導体装置)

【 図 1 2 】

【図13】

【図14】

【図15】

## 【図16】

【図17】

#### 14 : CSP(半導体装置)

【 図 1 8 】

【図19】

【図20】

### 【図21】

【図22】

---

フロントページの続き

(56)参考文献 特開2005-072515(JP,A)

特開平11-003954(JP,A)

特開2004-056137(JP,A)

特開2002-118204(JP,A)

特開2005-101137(JP,A)

特開平09-186422(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 23/12