(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4118971号

(P4118971)

(45) 発行日 平成20年7月16日(2008.7.16)

(24) 登録日 平成20年5月2日(2008.5.2)

(51) Int.Cl.

G09G 3/36 (2006.01)

G02F 1/133 (2006.01)

F 1

G09G 3/36

G02F 1/133 520

請求項の数 3 (全 9 頁)

(21) 出願番号 特願平9-42467

(22) 出願日 平成9年2月26日(1997.2.26)

(65) 公開番号 特開平10-240192

(43) 公開日 平成10年9月11日(1998.9.11)

審査請求日 平成16年2月26日(2004.2.26)

(73) 特許権者 307003227

ティーピーオー ホンコン ホールディング

リミテッド

香港、シャティン、サイエンス パーク

イースト アベニュー、フィリップス エ

レクトロニクス ビルディング 5, フロ

ア 2

(74) 代理人 100070150

弁理士 伊東 忠彦

(72) 発明者 神谷 長生

兵庫県神戸市西区高塚台4-3-1 ホシ

デン株式会社 開発技術研究所内

審査官 後藤 亮治

最終頁に続く

(54) 【発明の名称】多階調液晶ドライバ

## (57) 【特許請求の範囲】

## 【請求項 1】

直流電圧を直列接続されたN個( N は 3 以上の整数 )のストリング抵抗器により分割して、N個の階調電圧を得、入力ディジタルデータに基づいて前記階調電圧の1つを選択して液晶素子に出力すると共に、前記一連のストリング抵抗器の中間のN-1個の接続点よりn-1個( 1 < n-1 < N-1 )の接続点を抽出して、それらの抽出された接続点よりタップを導出し、それらのタップ及び一連のストリング抵抗器の両端の端子に前記階調電圧を液晶素子の透過率対印加電圧特性に合わせるための補正電圧を印加するようにした多階調液晶ドライバにおいて、前記補正電圧を、前記隣接の端子、タップ間の電位差が全て相等しくなるように印加すると共に、それら隣接の端子、タップ間のストリング抵抗器の抵抗値の合計を全てほぼ等しく設定したことを特徴とする多階調液晶ドライバ。

## 【請求項 2】

前記各ストリング抵抗器の抵抗値が、前記液晶素子の透過率対印加電圧特性における1階調当たりの透過率の一定変化幅に対応する印加電圧の変化幅に応じた値に設定されていることを特徴とする請求項1記載の多階調液晶ドライバ。

## 【請求項 3】

前記の一連のストリング抵抗器の隣接する端子、タップ間に存在する個々のストリング抵抗器の個数は、前記液晶素子の透過率対印加電圧特性曲線の傾斜に応じて一連のストリング抵抗器の両端側で少なく、中間で多く設定されていることを特徴とする請求項1記載の多階調液晶ドライバ。

## 【発明の詳細な説明】

## 【0001】

## 【発明の属する技術分野】

この発明は、例えばTFTマトリクス液晶表示素子の各信号バス等を駆動する多階調液晶ドライバに関し、特に該ドライバ及び該ドライバに動作電源を供給する電源回路の消費電力の軽減に関する。

## 【0002】

## 【従来の技術】

近年、マルチメディアの発達に伴い、コンピュータの表示色数は飛躍的に増大した。それに伴って、ノートパソコンに搭載されるTFTマトリクス液晶表示素子(LCD)もその表示色数を増やしてきた。表示色数を増やすために、LCDで使われる信号バス(ソースバス)用のドライバの階調数を増やすことになる。これはドライバ内にDAC(デジタル・アナログ・変換器)を設置して解決される。反面、色数の増大に比例して回路規模を増大し、ドライバの消費電力が増えることは避けられない。LCDはその用途に鑑みて、でき得る限り低消費電力であることが望ましいので、ドライバメーカーは様々な方式を採用し、低消費電力への努力をしている。

10

## 【0003】

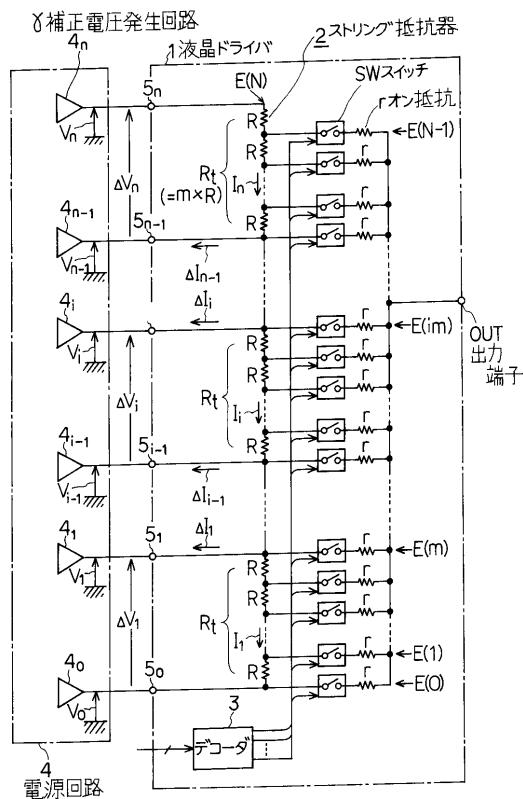

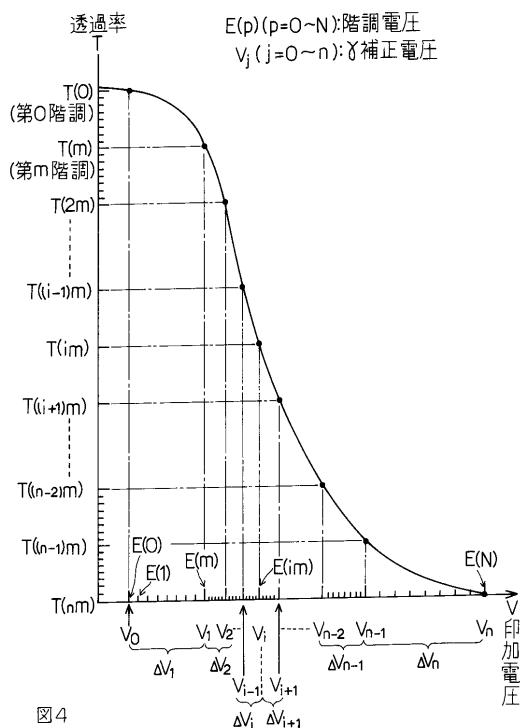

信号バス用ドライバのDAC方式の一つに、直列接続された一連の抵抗器(STRING抵抗器と言う)をもつR-STRING方式がある。この方式の回路ブロック図を電源回路と共に図3に示す。これは、例えば符号1が $N = 64$ 階調のドライバであれば64個のストリング抵抗器2を直列に接続し、その抵抗分割により生じた電圧を64個のスイッチSWで一つだけ選択することにより階調電圧を発生させるものである。

20

## 【0004】

図3において、各ストリング抵抗器の抵抗値を全てRとし、隣接する端子、タップ $5_i \sim 5_{i+1}$ ( $i = 1 \sim n$ )間の抵抗値を $R_t (= m \times R)$ 、スイッチのオン抵抗を $r$ とする。このR-STRING方式の液晶ドライバ1及び電源回路4の消費電力は以下の4つに分けられる。

## 【0005】

1  $m \times n = N$ 個分のSTRING抵抗 $R \times m \times n$ に電源回路4より電圧を印加することによる消費電力

30

2 とりこんだ6bitデータに従って、 $N = 64$ 個の電圧を選択するスイッチSWを制御するデコーダ部分の消費電力

3 出力端子OUTを経由してソースバス(信号バス)を充放電するのに使われる電力

4 液晶ドライバ1の内部のロジック回路(図示せず)が消費する電力

次に、図3の液晶ドライバ1の構成上の特徴を挙げると次の点である。

## 【0006】

イ)  $N = m \times n = 64$ 個の抵抗Rが全て等しい値になっている。

ロ)  $N = 64$ 個の各ストリング抵抗器2の $m = 8$ 個ごとに 補正用のタップ $5_i$ ( $i = 1 \sim n - 1$ )を有する。

40

LCDは一般的に図4に示すような透過率-電圧特性(T-V特性)を有するため、階調の変化がなめらかな変化として目視できるよう、階調ごとに印加電圧Vを変えなければならない。いわゆる 補正と呼ばれるものである。

## 【0007】

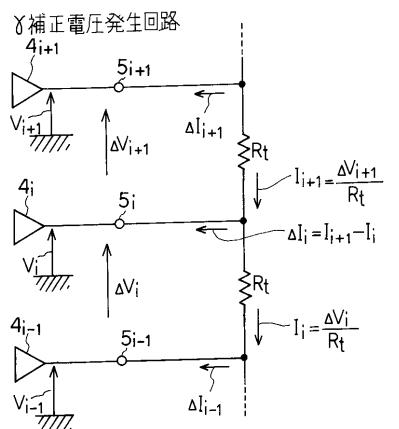

従来のR-STRING方式のドライバは、ロ)のタップ $5_i$ ( $i = 1 \sim n - 1$ )及び両端の端子 $5_0, 5_n$ に補正電圧 $V_i$ を印加することによってLCDのT-V特性に合わせてきた。そのため、隣合った端子、タップ $5_i \sim 5_{i+1}$ 間の電位差 $V_i$ ( $i = 1 \sim n$ )は各々異なる。各隣接端子、タップ間の抵抗値 $m \times R = R_t$ は等しいので、各端子 $5_i$ に異なる電圧 $V_i$ が印加されることにより、合成抵抗 $R_t$ を流れる電流 $I_i$ は図5より明らかなように、

50

$$I_i = V_i / R_t \quad \dots \dots \dots \quad (1)$$

中間のタップ  $5_i$  ( $i = 1 \sim n - 1$ ) には (2) 式で表される電流  $I_i$  が流れることとなる。

【0008】

$$\begin{aligned} \Delta I_i &= I_{i+1} - I_i \\ &= (\Delta V_{i+1} - \Delta V_i) / R_t; i = 1, 2 \dots, n-1 \end{aligned} \quad \dots \dots \dots \quad (2)$$

(2) 式で表される電流  $I_i$  は中間タップに接続される 補正電圧発生回路  $4_i$  ( $i = 1 \sim n - 1$ ) での電力消費  $P_i$  をもたらす。

【0009】

$$P_i = V_i \times I_i = V_i (V_{i+1} - V_i) / R_t \quad (i = 1 \dots, n-1) \quad \dots \dots \dots \quad (3)$$

また、回路  $4_n$  及び  $4_0$  内でそれぞれ消費される電力は、電源電圧を  $V_{cc}$  とすれば

$$\begin{aligned} P_n &= (V_{cc} - V_n) I_n \\ P_0 &= V_0 I_1 \end{aligned} \quad \dots \dots \dots \quad (4)$$

ドライバ1 内部での R - STRING 2 そのものが消費する電力もある。この R - STRING 2 そのものの電力消費は R - STRING 2 の値が大きい程少なくなるのは明らかであるが、ドライド1 の出力インピーダンスと LCD パネルの容量との合成時定数が LCD を充放電する時間に対して十分小さい値でないと、LCD に適正な電圧を与えることができなくなる。これはコントラストの低下やクロストークの増大となって表示品位を低下させる。そのため、端子、タップ  $5_i$  ( $i = 0 \sim n$ ) に電圧源を接続することは単に 補正のための入力としてだけでなく、R - STRING の抵抗値を大きくし、かつドライバの出力インピーダンスを下げるという側面がある。

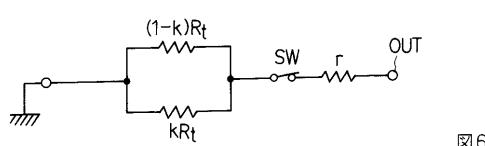

【0010】

ドライバ1 の出力インピーダンスは選択されるスイッチ SW の位置によって変化する。スイッチ SW により分割される  $R_t$  の分割比を  $k$  とすると、出力インピーダンス  $R_{out}$  は抵抗  $(1 - k) R_t$  と  $k R_t$  の並列抵抗値と、オン抵抗  $r$  の和となり、以下の (5) 式で表される。

$$\begin{aligned} R_{out} &= \{k (1 - k) R_t^2\} / \{k R_t + (1 - k) R_t\} + r \\ &= k (1 - k) R_t + r \\ &= -R_t k^2 + R_t k + r \end{aligned} \quad \dots \dots \dots \quad (5)$$

$$d R_{out} / d k = -2 R_t k + R_t = (1 - 2k) R_t = 0 \quad \dots \dots \dots \quad (6)$$

と置くと、 $k = 1 / 2$  が得られる。このとき  $R_{out}$  が最大になり、その値は (7) 式となる。

【0011】

$$[R_{out}]_{max} = (R_t / 4) + r \quad \dots \dots \dots \quad (7)$$

一般に、R - STRING 方式のドライバでは出力インピーダンスの最大値と LCD の容量との時定数が 1 水平時間  $H$  に対して十分小さくなるように設定される。

【0012】

【発明が解決しようとする課題】

従来の R - STRING 方式のドライバは  $N = m \times n = 64$  個の抵抗が全て等しい値 ( $R$ ) になっているため、外部から 補正用の端子、タップ  $5_i$  に電圧を印加して、特性を補正していた。この 補正のために各中間のタップ  $5_i$  には (2) 式で表される電流  $I_i$  が 補正電圧発生回路  $4_i$  ( $i = 1 \sim n - 1$ ) に流れるため、その電流  $I_i \times$  出力電

20

30

30

40

40

50

圧  $V_i = P_i$  は回路  $4_i$  での電力消費となる。また、この不平衡電流  $I_i$  はストリング抵抗器を流れるので、それだけストリング抵抗器の消費電力が増加する。

【0013】

この発明は、補正電圧発生回路  $4_i$  ( $i = 1 \sim n - 1$ ) に吸込まれる電流  $I_i$  をほぼゼロにして、ドライバ1のストリング抵抗器及び電源回路4の消費電力を低減することを目的としている。

【0014】

【課題を解決するための手段】

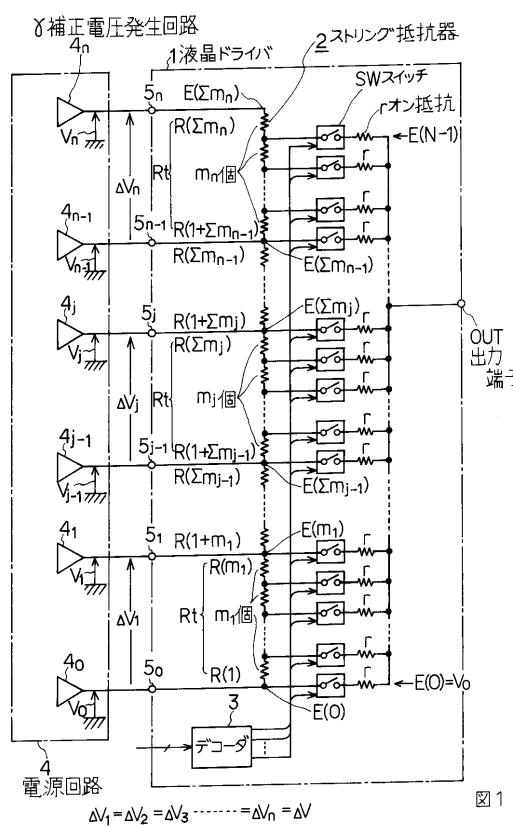

(1) 請求項1の発明は、直流電圧を直列接続されたN個 (Nは3以上の整数) のストリング抵抗器により分割して、N個の階調電圧を得、入力ディジタルデータに基づいて階調電圧の1つを選択して液晶素子に出力すると共に、ストリング抵抗器のN-1個の接続点よりn-1個 ( $1 \sim n - 1 < N - 1$ ) の接続点を抽出して、それらの抽出された接続点よりタップを導出し、それらのタップ ( $5_1 \sim 5_{n-1}$ ) 及び一連のストリング抵抗器の両端の端子 ( $5_0, 5_n$ ) に補正電圧 ( $V_0, V_1 \dots, V_n$ ) を印加するようにした多階調液晶ドライバに関する。

【0015】

請求項1では特に、補正電圧を、前記隣接の端子、タップ間の電位差 ( $V_j$ ) が全て相等しくなるように印加すると共に、それら隣接の端子、タップ間のストリング抵抗器の抵抗値 ( $Rt_j$ ) を全てほぼ等しく設定する。

(2) 請求項2の発明では、前記(1)において、N個の各ストリング抵抗器の抵抗値  $R(p)$  が、液晶素子の透過率対印加電圧特性における1階調当たりの透過率の一定変化幅に対応する印加電圧の変化幅 ( $(p)$ ;  $p = 1, 2 \dots, N$ ) に応じた値に設定される。

【0016】

(3) 請求項3の発明では、前記(1)において、一連のストリング抵抗器の隣接する端子、タップ間に存在する個々のストリング抵抗器の個数 ( $m_1, m_2, \dots, m_n$ ) は、前記液晶素子の透過率対印加電圧特性曲線の傾斜に応じて一連のストリング抵抗器の両端側で少なく、中間で多く設定される。

【0017】

【発明の実施の形態】

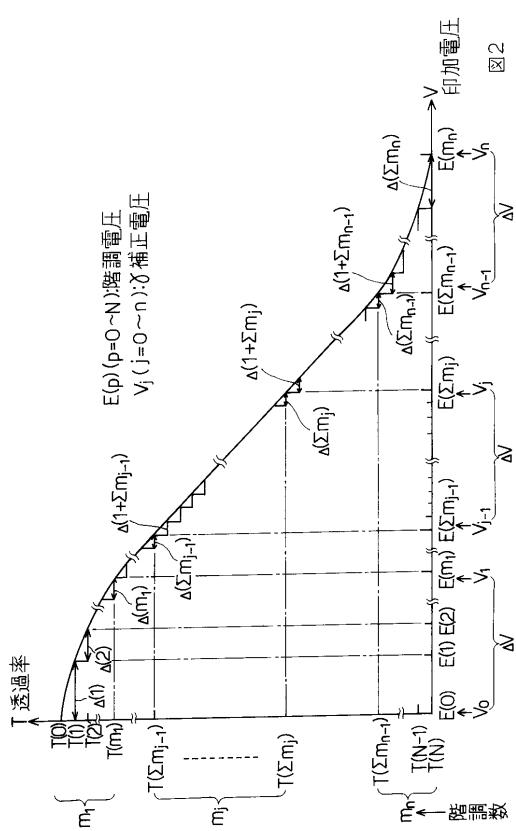

N (例えば  $N = 64$ ) 階調表示を行うものとして、図2に示す液晶のT-V特性より、階調に対応する一定ピッチ幅の透過率  $T(0), T(1) \dots, T(N)$  に対応する印加電圧  $E(0), E(1), \dots, E(N)$  を求める。従来と同様に  $n + 1$  個 (例えば  $n = 8$ ) の端子 (タップ)  $5_0 \sim 5_n$  を設けるものとする。隣接端子、タップ間の電位差  $V_j$  を  $j$  に関係なく  $V$  に等しくする。即ち、

$$V_j (j = 1 \sim n) = V \quad \dots \dots \dots (8)$$

また、隣接タップ間の抵抗値  $Rt_j$  を全てほぼ等しくする。即ち、

$$Rt_j (j = 1 \sim n) = Rt \text{ (一定)} \quad \dots \dots \dots (9)$$

このとき、隣接端子、タップ間のストリング抵抗器を流れる電流  $I_j$  は

$$I_j = V_j / Rt_j = V / Rt \quad \dots \dots \dots (10)$$

即ち、 $I_j$  は  $j$  に依らず一定値となる。従って、電圧補正回路  $4_j$  に流れ込む  $I_j$  は

、

$$I_j = I_{j+1} - I_j = 0 \quad (j = 1 \sim n - 1) \quad \dots \dots \dots (11)$$

となり、低消費電力化が図られる。

【0018】

透過率  $T(j)$  ( $j = 0 \sim N$ ) に対応する印加電圧  $E(p)$  ( $p = 0 \sim N$ ) より 1 階調増すごとのステップ電圧 ( $p$ ) (図2) を求める。

$$(1) = E(1) - E(0)$$

$$(2) = E(2) - E(1),$$

...

$$(p) = E(p) - E(p - 1),$$

10

20

30

40

50

$$\begin{aligned}

&= K \{ E(1 + m_{j-1}) - E(m_{j-1}) \\

&+ E(2 + m_{j-1}) - E(1 + m_{j-1}) \\

&\dots \\

&+ E(m_j + m_{j-1}) - E(m_{j-1} + m_{j-1}) \} \\

&= K \{ E(m_j) - E(m_{j-1}) \}

\end{aligned}$$

(16) 式を代入して

$$K \{ V_j - V_{j-1} \} \dots \dots \dots \quad (19)$$

(15) 式を代入して

$$= K \{ E(0) + j V - E(0) - (j-1) V \}$$

$$= K V \dots \dots \dots \quad (20)$$

10

以上により、各隣接端子、タップ間の抵抗値  $R_t_j$  ( $j = 1 \sim n$ ) は  $j$  の値に依らずほぼ  $K V$  の一定値となっていることが検証できた。

### 【0023】

実際に補正電圧発生回路  $4_j$  ( $j = 0 \sim n$ ) よりタップに供給する電圧は (15) 式より求めた電圧  $V_0, V_1 \dots V_n$  であるので、隣接タップ間の電位差は全て  $V$  であり、両端の  $4_0$  と  $4_n$  を除く中間の補正電圧発生回路  $4_1 \sim 4_{n-1}$  の出力端子を出入りする不平衡電流 (従来技術で述べた  $I_j$ ) はほぼゼロとなり、省電力化が図られる。この場合、中間の補正電圧発生回路  $4_1 \sim 4_{n-1}$  は液晶ドライバの出力抵抗を下げる機能を発揮していることは勿論である。不平衡電流  $I_j$  はストリング抵抗器を流れる。この発明では  $I_j = 0$  であるので、ストリング抵抗器での消費電力もそれだけ少なくなる。

20

### 【0024】

各補正電圧発生回路  $4_j$  の印加電圧  $V_1, V_2 \dots, V_{n-1}$  は、図2の  $T - V$  特性より求めた  $E(m_1), E(m_1 + m_2) \dots, E(m_{n-1})$  とそれぞれ僅かの差をもつので、出力端子 OUT より LCD に供給する階調電圧は両端の  $E(0), E(N)$  を除いて僅かな誤差が存在する。しかし、この誤差は僅かであり、また階調数が例えば  $N = 64$  と多いので何ら問題になることはない。

### 【0025】

図2からも分かるように、この発明では隣接端子、タップ間のストリング抵抗器の数、即ち階調数は、 $T - V$  特性の傾斜に応じて設定され、 $T(0)$  (ゼロ階調) 側及び  $T(N-1)$  ( $N-1$  階調) 側では、従来の例えば  $m = 8$  に比べて、例えば  $m_1 = 5, m_n = 5$  と少なく、中間のタップ間の階調数は例えば  $m_j = 20$  と多くなる。

30

### 【0026】

隣接端子、タップ間のストリング抵抗  $R_t$  の消費電力は

$$P = (V)^2 / R_t \dots \dots \dots \quad (21)$$

であるので、ストリング抵抗は液晶の画像表示に影響の出ない範囲で、できるだけ大きくする望ましい。

### 【0027】

#### 【発明の効果】

この発明では、補正電圧  $V_j$  ( $j = 0 \sim n$ ) を隣接端子、タップ間の電位差  $V_j$  が全て相等しくなるように印加すると共に、それら隣接端子、タップ間のストリング抵抗  $R_t$  を全てほぼ等しく設定したので、中間のタップ  $5_1 \sim 5_{n-1}$  から補正電圧発生回路  $4_1 \sim 4_{n-1}$  側に流れる不平衡電流  $I_j$  はほぼゼロとなり、それだけ電源回路  $4_1$  及びストリング抵抗器 2 の消費電力を低減できる。

40

#### 【図面の簡単な説明】

【図1】この発明の実施例を示す回路図。

【図2】この発明における階調電圧  $E(p)$  ( $p = 0, 1 \dots, N$ )、透過率  $T(p)$  及び補正電圧  $V_j$  ( $j = 0 \sim n$ ) の対応を説明するための LCD の透過率対印加電圧特性を示すグラフ。

【図3】従来の液晶ドライバを電源回路と共に示す回路図。

【図4】従来の階調電圧  $E(p)$  ( $p = 0 \sim N$ )、透過率  $T(p)$  及び補正電圧  $V_i$  (

50

$i = 0 \sim n$  ) の対応を説明するための L C D の透過率対印加電圧特性を示すグラフ。

【図5】図3の要部の電圧、電流を示すための回路図。

【図6】図3の液晶ドライバ1の出力抵抗を説明するための回路図。

【 図 1 】

【 図 2 】

【図3】

3

【 図 4 】

4

【 図 5 】

5

〔 四 6 〕

6

---

フロントページの続き

(56)参考文献 特開平08-022266 (JP, A)

特開平05-264963 (JP, A)

特開平08-211367 (JP, A)

特開平09-068695 (JP, A)

特開平05-181436 (JP, A)

特開平08-227283 (JP, A)

特開平03-089392 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G09G 3/00 - 3/38

G02F 1/133