(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2015년12월23일

(11) 등록번호 10-1579917

(24) 등록일자 2015년12월17일

(51) 국제특허분류(Int. Cl.)

*H04L 12/939* (2013.01) *H04L 29/10* (2006.01)

(21) 출원번호 10-2014-7000908

(22) 출원일자(국제) 2012년10월27일

심사청구일자 2014년01월13일

(85) 번역문제출일자 2014년01월13일

(65) 공개번호 10-2014-0082630

(43) 공개일자 2014년07월02일

(86) 국제출원번호 PCT/CN2012/083631

(87) 국제공개번호 WO 2014/063370

국제공개일자 2014년05월01일

(56) 선행기술조사문헌

JP4670676 B2

KR1020050006783 A

JP2007219873 A

JP2009163633 A

(73) 특허권자

후아웨이 테크놀러지 컴퍼니 리미티드

중화인민공화국 선전 롱강 디스트릭트 반티안 어드미니스트레이션 빌딩 후아웨이 테크놀러지스 컴퍼니 리미티드

(72) 발명자

수 데시안

중국 518129 광동성 선전 반티안 후아웨이 어드미니스트레이션 빌딩

야오 위민

중국 518129 광동성 선전 반티안 후아웨이 어드미니스트레이션 빌딩

왕 정

중국 518129 광동성 선전 롱강 디스트릭트 반티안 후아웨이 어드미니스트레이션 빌딩

(74) 대리인

유미특허법인

전체 청구항 수 : 총 46 항

심사관 : 이형일

(54) 발명의 명칭 PCIE 스위칭 네트워크에서 패킷 전송을 실행하기 위한 방법, 장치, 시스템, 및 저장 매체

**(57) 요 약**

본 발명의 실시예는 주변 구성요소 상호접속 고속 인터페이스 제어 유닛에 대해 개시한다. 주변 구성요소 상호접속 고속 인터페이스 제어 유닛은, 루트 복합(RC) 또는 종점 장치(EP)로부터 제1 트랜잭션 계층 패킷(TLP)을 수신하고, 상기 제1 TLP를 프로세싱을 위한 신뢰할 수 있는 TLP 전송(RTT) 모듈에 포워딩하도록 구성되어 있는 PCI

(뒷면에 계속)

**대 표 도** - 도3

대 PCI 브리지 P2P 모듈을 포함하며; 상기 신뢰할 수 있는 TLP 전송(RTT) 모듈은, 상기 수신된 제1 TLP에 따라, 활성 및 대기 PCIE 스위칭 유닛에 연결된 송신 링크를 결정하고, 상기 제1 TLP를 상기 송신 링크를 통해 상기 활성 및 대기 PCIE 스위칭 유닛에 동시에 송신하도록 구성되어 있으며, 이에 따라 상기 제1 TLP의 목적지 PCIE 인터페이스 제어기가 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 상기 제1 TLP를 선택적으로 수신하고 상기 제1 TLP의 목적지 EP 또는 목적지 RC에 상기 제1 TLP를 송신하며, 이에 의해 PCIE 스위칭 이중 평면 네트워킹 접속의 경우에 TLP의 신뢰할 수 있는 전송을 실행하며, PCIE 스위칭을 사용하여 시스템의 신뢰성을 높인다. 본 발명의 실시예는 또한 PCIE 스위칭 네트워크에서 패킷 전송을 위한 방법, 시스템, 및 저장 매체에 대해 개시한다.

---

## 명세서

### 청구범위

#### 청구항 1

주변 구성요소 상호접속 고속 인터페이스 제어기(peripheral component interconnect express interface controller: PEIC)에 있어서,

루트 복합(root complex: RC) 또는 종점 장치(endpoint device: EP)로부터 제1 트랜잭션 계층 패킷(transaction layer packet: TLP)을 수신하고, 상기 제1 TLP를, 프로세싱을 위한 신뢰할 수 있는 TLP 전송(reliable TLP transmission: RTT) 모듈에 포워딩하도록 구성되어 있는 PCI 대 PCI 브리지 P2P 모듈; 및

상기 수신된 제1 TLP에 따라, 활성 및 대기 PCIE 스위칭 유닛에 연결된 송신 링크를 결정하고, 상기 제1 TLP를 상기 송신 링크를 통해 상기 활성 및 대기 PCIE 스위칭 유닛에 동시에 송신하도록 구성되어 있고, 이에 따라 상기 제1 TLP의 목적지 PCIE 인터페이스 제어기가 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 상기 제1 TLP를 선택적으로 수신하고 상기 제1 TLP의 목적지 EP 또는 목적지 RC에 상기 제1 TLP를 송신하는, 상기 신뢰할 수 있는 TLP 전송(RTT) 모듈

을 포함하는 주변 구성요소 상호접속 고속 인터페이스 제어기.

#### 청구항 2

제1항에 있어서,

상기 신뢰할 수 있는 TLP 전송 모듈은, 상기 제1 TLP를 캡슐화하고, 상기 제1 TLP의 자체 정의 단대단(self-defined end-to-end) TLP 접두사에 송신지 PEIC 번호 및 TLP 송신 순차 번호를 부가하도록 추가로 구성되어 있으며, 이에 따라 상기 제1 TLP의 목적지 PEIC가 상기 송신지 PEIC 번호 및 상기 TLP 송신 순차 번호에 따라 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 상기 제1 TLP를 선택적으로 수신하며,

상기 TLP 송신 순차 번호는 송신지 PEIC에 의해 상기 제1 TLP의 목적지 PEIC에 송신된 TLP의 순차 번호이고, 상기 송신지 PEIC 번호 및 상기 TLP 송신 순차 번호에 따라 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 상기 제1 TLP를 선택적으로 수신하는 과정은, 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩되고 동일한 송신지 PEIC 번호 및 동일한 TLP 송신 순차 번호를 가지는 제1 TLP에 있어서, 먼저 도착하는 제1 TLP만을 수신하는 과정인, 주변 구성요소 상호접속 고속 인터페이스 제어기.

#### 청구항 3

제1항에 있어서,

상기 신뢰할 수 있는 TLP 전송 모듈은,

상기 수신된 제1 TLP에 따라 어드레스 포워딩 테이블 또는 ID 포워딩 테이블을 검색하고, TLP 전송 큐(TLP transmission queue: TTQ)를 결정하며, 상기 제1 TLP를 상기 TLP 전송 큐에 놓도록 구성되어 있고, 상기 TLP 전송 큐는 상기 제1 TLP의 목적지 PEIC에 대응하는, TLP 디스패치 모듈; 및

상기 TLP 전송 큐 내의 제1 TLP를 상기 TLP 전송 큐의 상기 송신 링크를 통해 상기 활성 및 대기 PCIE 스위칭 유닛에 동시에 송신하도록 구성되어 있고, 이에 따라 상기 제1 TLP의 목적지 PCIE 인터페이스 제어기가 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 상기 제1 TLP를 선택적으로 수신하고 상기 제1 TLP의 목적지 EP 또는 목적지 RC에 상기 제1 TLP를 송신하는, 송신 모듈

을 포함하는, 주변 구성요소 상호접속 고속 인터페이스 제어기.

#### 청구항 4

제3항에 있어서,

상기 송신 모듈은, 상기 제1 TLP를 캡슐화하고, 상기 제1 TLP의 단대단 TLP 접두사에 송신지 PEIC 번호(SPEIC)

및 TLP 송신 순차 번호(SEQUENCE)를 부가하도록 추가로 구성되어 있으며, 이에 따라 상기 목적지 PEIC가 상기 SPEIC 및 상기 SEQUENCE에 따라 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 상기 제1 TLP를 선택적으로 수신하며,

상기 TLP 송신 순차 번호는 송신지 PEIC에 의해 상기 제1 TLP의 목적지 PEIC에 송신된 TLP의 순차 번호이고, 상기 SPEIC 및 상기 SEQUENCE에 따라 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 상기 제1 TLP를 선택적으로 수신하는 과정은, 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩되고 동일한 상기 SPEIC 및 동일한 SEQUENCE를 가지는 제1 TLP에 있어서, 먼저 도착하는 제1 TLP만을 수신하는 과정인, 주변 구성요소 상호접속 고속 인터페이스 제어기.

#### 청구항 5

제3항 또는 제4항에 있어서,

상기 신뢰할 수 있는 TLP 전송 모듈은,

상기 활성 및 대기 PCIE 스위칭 유닛에 의해 송신된 제2 TLP를 선택적으로 수신하고, 상기 수신된 제2 TLP를 상기 P2P 모듈에 송신하도록 구성되어 있고, 이에 따라 상기 P2P 모듈이 상기 제2 TLP의 목적지 RC 또는 목적지 EP에 상기 제2 TLP를 포워딩하는, 수신 모듈

을 더 포함하는, 주변 구성요소 상호접속 고속 인터페이스 제어기.

#### 청구항 6

제5항에 있어서,

상기 수신 모듈은 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 송신된 제2 TLP를 선택적으로 수신하도록 추가로 구성되어 있고, 이것은 구체적으로,

상기 수신 모듈은 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 송신된 제2 TLP를 수신하고, 자체 정의 TLP 접두사가 동일한 송신지 PEIC 번호(SPEIC) 및 동일한 TLP 송신 순차 번호(SEQUENCE)를 수반하는 제2 TLP에 있어서, 먼저 수신된 제2 TLP만 수신하고 나중에 수신된 제2 TLP는 폐기하도록 구성되어 있는, 주변 구성요소 상호접속 고속 인터페이스 제어기.

#### 청구항 7

제6항에 있어서,

상기 수신 모듈은, 자체 정의 TLP 접두사가 동일한 송신지 PEIC 번호(SPEIC) 및 동일한 TLP 송신 순차 번호(SEQUENCE)를 수반하는 제2 TLP에 있어서, 먼저 수신된 제2 TLP만 수신하고 나중에 수신된 제2 TLP는 폐기하도록 구성되어 있고, 이것은 구체적으로,

상기 수신 모듈은, 상기 제2 TLP의 자체 정의된 단대단 TLP 접두사에 수반되어 있는 SPEIC 및 SEQUENCE와 상기 제2 TLP의 송신지 PEIC로부터 수신될 것으로 예상되는 TLP의 순차 번호를 비교하고, 상기 제2 TLP의 자체 정의된 단대단 TLP 접두사에 수반되어 있는 SPEIC 및 SEQUENCE가 상기 제2 TLP의 송신지 PEIC로부터 수신될 것으로 예상되는 TLP의 순차 번호와 같으면 제2 TLP를 수신하고, 같지 않으면 제2 TLP를 폐기하도록 구성되어 있는, 주변 구성요소 상호접속 고속 인터페이스 제어기.

#### 청구항 8

제3항 또는 제4항에 있어서,

상기 신뢰할 수 있는 TLP 전송 모듈은,

각각의 TLP 전송 큐의 TLP 송신 순차 번호 및 TLP 송신 링크를 유지 및 관리하도록 구성되어 있는 TLP 전송 큐 관리 모듈

을 더 포함하며,

상기 TLP 전송 큐의 TLP 송신 순차 번호는 전송 큐에 대응하는 목적지 PEIC에 송신된 TLP의 송신 순차 번호이고, 상기 TLP 전송 큐의 TLP 송신 링크는 전송 큐에 대응하는 목적지 PEIC에 대한 TLP 송신 링크인, 주변

구성요소 상호접속 고속 인터페이스 제어기.

### 청구항 9

주변 구성요소 상호접속 고속 인터페이스 제어기(PEIC)에 있어서,

루트 복합(RC) 또는 종점 장치(EP)로부터 제3 트랜잭션 계층 페킷(TLP)을 수신하고, 상기 제3 TLP를 신뢰할 수 있는 TLP 전송(RTT) 모듈에 포워딩하도록 구성되어 있는 PCI 대 PCI 브리지 P2P 모듈; 및

상기 수신된 제3 TLP에 따라, 활성 및 대기 PCIE 스위칭 유닛에 연결된 송신 링크를 결정하고, 상기 제3 TLP를 상기 송신 링크를 통해 상기 활성 및 대기 PCIE 스위칭 유닛에 송신하도록 구성되어 있으며, 이에 따라 상기 제3 TLP의 목적지 PCIE 인터페이스 제어기가 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 상기 제3 TLP를 선택적으로 수신하고 상기 제3 TLP의 목적지 EP 또는 목적지 RC에 상기 제3 TLP를 송신하며; 상기 제3 TLP의 목적지 PEIC에 의해 회신되고 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 제1 수신확인 메시지 TLP가 시간이 종료될 때까지도 수신되지 않으면, 상기 제3 TLP를 다시 송신하는, 상기 신뢰할 수 있는 TLP 전송(RTT) 모듈

을 포함하는 주변 구성요소 상호접속 고속 인터페이스 제어기.

### 청구항 10

제9항에 있어서,

상기 RTT 모듈은, 상기 제3 TLP를 캡슐화하고, 상기 제3 TLP의 자체 정의 단대단 TLP 접두사에 송신지 PEIC 번호 및 TLP 송신 순차 번호를 부가하고, 상기 캡슐화된 제3 TLP를 상기 송신 링크를 통해 상기 활성 및 대기 PCIE 스위칭 유닛에 송신하도록 추가로 구성되어 있으며, 이에 따라 상기 제3 TLP의 목적지 PEIC가 상기 수신된 제3 TLP에 있는 상기 송신지 PEIC 번호 및 상기 TLP 송신 순차 번호에 따라 제1 수신확인 메시지 TLP를 회신하며,

상기 회신된 제1 수신확인 메시지 TLP의 자체 정의된 단대단 TLP 접두사는 상기 제3 TLP의 목적지 PEIC의 PEIC 번호 및 수신확인된 TLP 송신 순차 번호를 수반하고 있으며, 상기 제3 TLP 내의 TLP 송신 순차 번호는 상기 제3 TLP의 송신지 PEIC에 의해 상기 제3 TLP의 목적지 PEIC에 송신된 TLP의 순차 번호이고, 상기 제1 수신확인 메시지 TLP 내의 상기 수신확인된 TLP 송신 순차 번호는 상기 송신지 PEIC의 TLP 송신 순차 번호이고 상기 제3 TLP의 목적지 PEIC에 의해 이미 수신된 제3 TLP의 TLP 송신 순차 번호인, 주변 구성요소 상호접속 고속 인터페이스 제어기.

### 청구항 11

제9항에 있어서,

상기 신뢰할 수 있는 TLP 전송 모듈은,

상기 수신된 제3 TLP에 따라 어드레스 포워딩 테이블 또는 ID 포워딩 테이블을 검색하고, TLP 전송 큐(TTQ)를 결정하며, 상기 제3 TLP를 상기 TLP 전송 큐에 놓도록 구성되어 있고, 상기 TLP 전송 큐는 상기 제3 TLP의 목적지 PEIC에 대응하는, TLP 디스패치 모듈;

상기 TLP 전송 큐 내의 제3 TLP를 상기 TLP 전송 큐의 상기 송신 링크를 통해 상기 활성 및 대기 PCIE 스위칭 유닛에 송신하도록 구성되어 있고, 이에 따라 상기 제3 TLP의 목적지 PCIE 인터페이스 제어기가 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 상기 제3 TLP를 선택적으로 수신하고 상기 제3 TLP의 목적지 EP 또는 목적지 RC에 상기 제3 TLP를 송신하며; 상기 제3 TLP의 목적지 PEIC에 의해 회신되고 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 제1 수신확인 메시지 TLP가 시간이 종료될 때까지도 수신되지 않으면, 상기 제3 TLP를 다시 송신하도록 추가적으로 구성되어 있는 송신 모듈;

상기 제3 TLP의 목적지 PEIC에 의해 회신되고 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 제1 수신확인 메시지 TLP를 수신하고, 상기 제1 수신확인 메시지 TLP를 수신확인 모듈에 전달하도록 구성되어 있는 수신 모듈;

상기 제1 수신확인 메시지 TLP에 수반되어 있는 TLP 송신 순차 번호 및 송신지 PEIC 번호에 따라, 상기 TLP 전송 큐 내의 수신확인된 제3 TLP를 삭제한다는 것을 TLP 전송 큐 관리 모듈에 통지하도록 구성되어 있는 상기 수신 모듈;

신확인 모듈; 및

상기 수신확인 모듈의 통지에 따라 상기 TLP 전송 큐 내의 수신확인된 제3 TLP를 삭제하도록 구성되어 있는 상기 TLP 전송 큐 관리 모듈

을 포함하는, 주변 구성요소 상호접속 고속 인터페이스 제어기.

### 청구항 12

제11항에 있어서,

상기 송신 모듈은, 상기 제3 TLP를 캡슐화하고, 상기 제3 TLP의 단대단 TLP 접두사에 송신지 PEIC 번호 및 TLP 송신 순차 번호를 부가하며, 상기 캡슐화된 제3 TLP를 상기 TTQ의 송신 링크를 통해 상기 활성 및 대기 PCIE 스위칭 유닛에 송신하도록 구성되어 있으며, 이에 따라 상기 제3 TLP의 목적지 PEIC가, 상기 송신지 PEIC 번호 및 상기 TLP 송신 순차 번호에 따라, 상기 수신된 TLP에 응답해서 제1 수신확인 메시지 TLP를 회신하며, 상기 회신된 제1 수신확인 메시지 TLP의 단대단 TLP 접두사는 상기 송신지 PEIC 번호 및 수신확인된 TLP 송신 순차 번호를 수반하고 있으며,

상기 제3 TLP의 TLP 송신 순차 번호는 상기 제3 TLP의 송신지 PEIC에 의해 상기 제3 TLP의 목적지 PEIC에 송신된 TLP의 순차 번호이고, 상기 제1 수신확인 메시지의 상기 수신확인된 TLP 송신 순차 번호는 상기 송신지 PEIC의 TLP 송신 순차 번호이고 상기 제3 TLP의 목적지 PEIC에 의해 이미 수신된 제3 TLP의 TLP 송신 순차 번호인, 주변 구성요소 상호접속 고속 인터페이스 제어기.

### 청구항 13

제11항 또는 제12항에 있어서,

상기 TLP 전송 큐 관리 모듈은, 각각의 TLP 전송 큐의 TLP 송신 순차 번호 및 TLP 송신 링크를 유지하도록 추가로 구성되어 있는, 주변 구성요소 상호접속 고속 인터페이스 제어기.

### 청구항 14

제13항에 있어서,

상기 수신 모듈은 상기 활성 및 대기 PCIE 스위칭 유닛으로부터 송신된 제4 TLP를 수신하고, 상기 제4 TLP가 수신확인 메시지 TLP인지를 판단하며, 상기 제4 TLP가 수신확인 메시지 TLP가 아니면, 상기 수신된 제4 TLP를 상기 제4 TLP의 송신지 PEIC에 대응하는 TLP 수신확인 순차 TAS에 버퍼링하도록 추가로 구성되어 있으며,

상기 P2P 모듈은 상기 TLP 수신확인 순차 TAS 내의 상기 제4 TLP를 획득하고, 상기 제4 TLP를 상기 제4 TLP의 목적지 RC/EP에 포워딩하도록 추가로 구성되어 있는, 주변 구성요소 상호접속 고속 인터페이스 제어기.

### 청구항 15

제14항에 있어서,

상기 신뢰할 수 있는 TLP 전송 모듈은,

상기 TLP 수신확인 순차가 상기 제4 TLP를 수신한 후, 상기 제4 TLP의 송신지 PEIC에 수신확인 메시지 TLP를 회신한다는 것을 상기 수신확인 모듈에 통지하도록 구성되어 있는 TLP 수신확인 순차 관리 모듈

을 더 포함하고,

상기 수신확인 모듈은 제2 수신확인 메시지 TLP를 생성하고, 상기 제2 수신확인 메시지 TLP를 상기 제4 TLP의 송신지 PEIC에 대응하는 TLP 전송 큐에 버퍼링하도록 추가로 구성되어 있으며, 이에 따라 상기 제2 수신확인 메시지 TLP는 스케줄링되고 상기 송신 모듈에 의해 송신되는, 주변 구성요소 상호접속 고속 인터페이스 제어기.

### 청구항 16

제15항에 있어서,

상기 수신확인 모듈은, 상기 수신된 제1 수신확인 메시지 TLP에 수반되어 있는 상기 송신지 PEIC 번호 및 수신확인된 송신 순차 번호 정보에 따라, 대응하는 TTQ의 슬라이딩 윈도(sliding window)를 갱신하도록 추가로 구성

되어 있는, 주변 구성요소 상호접속 고속 인터페이스 제어기.

### 청구항 17

제11항 또는 제12항에 있어서,

상기 신뢰할 수 있는 TLP 전송 모듈은,

고정-시간 검출 TLP를 시간 간격으로 모든 다른 PEIC에 송신하고, 목적지 PEIC에 의해 회신된 검출 응신 TLP가 지정된 시간 내에 수신되지 않으면, 상기 검출 응신 TLP를 회신하는 목적지 PEIC에 대응하는 TTQ의 송신 링크를 개선한다는 것을 TLP 송신 큐 관리 모듈에 통지하도록 구성되어 있는 중추부 모듈(heartbeat module)

을 더 포함하며,

상기 TLP 전송 큐 관리 모듈은 상기 중추부 모듈의 통지에 따라 상기 TLP 전송 큐의 송신 링크를 개선하도록 추가로 구성되어 있는, 주변 구성요소 상호접속 고속 인터페이스 제어기.

### 청구항 18

주변 구성요소 상호접속 고속 스위칭 네트워크에서 패킷 전송을 위한 방법에 있어서,

RC 또는 EP로부터 제1 TLP를 수신하는 단계; 및

상기 수신된 제1 TLP에 따라, 활성 및 대기 PCIE 스위칭 유닛에 연결된 송신 링크를 결정하고, 상기 제1 TLP를 상기 송신 링크를 통해 상기 활성 및 대기 PCIE 스위칭 유닛에 동시에 송신하며, 이에 따라 상기 제1 TLP의 목적지 PCIE 인터페이스 제어기가 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 상기 제1 TLP를 선택적으로 수신하고 상기 제1 TLP의 목적지 EP 또는 목적지 RC에 상기 제1 TLP를 송신하는 단계

를 포함하는 패킷 전송 방법.

### 청구항 19

제18항에 있어서,

상기 제1 TLP를 상기 송신 링크를 통해 상기 활성 및 대기 PCIE 스위칭 유닛에 동시에 송신하는 단계 이전에,

상기 제1 TLP를 캡슐화하고, 상기 제1 TLP의 자체 정의 단대단(self-defined end-to-end) TLP 접두사에 송신지 PEIC 번호 및 TLP 송신 순차 번호를 부가하며, 이에 따라 상기 목적지 PEIC가 상기 송신지 PEIC 번호 및 상기 TLP 송신 순차 번호에 따라 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 상기 제1 TLP를 선택적으로 수신하는 단계

를 더 포함하며,

상기 TLP 송신 순차 번호는 상기 제1 TLP의 송신지 PEIC에 의해 상기 제1 TLP의 목적지 PEIC에 송신된 TLP의 순차 번호이고, 상기 송신지 PEIC 번호 및 상기 TLP 송신 순차 번호에 따라 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 상기 제1 TLP를 선택적으로 수신하는 단계는, 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩되고 동일한 송신지 PEIC 번호 및 동일한 TLP 송신 순차 번호를 가지는 제1 TLP에 있어서, 먼저 도착하는 제1 TLP만을 수신하는 단계인, 패킷 전송 방법.

### 청구항 20

제18항 또는 제19항에 있어서,

상기 수신된 제1 TLP에 따라, 활성 및 대기 PCIE 스위칭 유닛에 연결된 송신 링크를 결정하고, 상기 제1 TLP를 상기 송신 링크를 통해 상기 활성 및 대기 PCIE 스위칭 유닛에 동시에 송신하며, 이에 따라 상기 제1 TLP의 목적지 PCIE 인터페이스 제어기가 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 상기 제1 TLP를 선택적으로 수신하고 상기 제1 TLP의 목적지 EP 또는 목적지 RC에 상기 제1 TLP를 송신하는 단계는 구체적으로,

상기 수신된 제1 TLP에 따라 대응하는 어드레스 포워딩 테이블 또는 ID 포워딩 테이블을 검색하고, TLP 전송 큐(TTQ)를 결정하며, 상기 제1 TLP의 목적지 PEIC에 대응하는 TLP 전송 큐에 상기 제1 TLP를 놓는 단계; 및

상기 TLP 전송 큐 내의 제1 TLP를 상기 TLP 전송 큐의 송신 링크를 통해 상기 활성 및 대기 PCIE 스위칭 유닛에

동시에 송신하며, 이에 따라 상기 제1 TLP의 목적지 PCIE 인터페이스 제어기가 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 상기 제1 TLP를 선택적으로 수신하고 상기 제1 TLP의 목적지 EP 또는 목적지 RC에 상기 제1 TLP를 송신하는 단계인, 패킷 전송 방법.

### 청구항 21

제20항에 있어서,

자체 정의 단대단 TLP 접두사가 동일한 송신지 PEIC 번호 및 동일한 TLP 송신 순차 번호를 수반하고 있는 제1 TLP에 있어서, 상기 제1 TLP의 목적지 PEIC가, 먼저 수신된 제2 TLP만 수신하고 나중에 수신된 제2 TLP는 폐기하는 단계

를 더 포함하는 패킷 전송 방법.

### 청구항 22

제21항에 있어서,

상기 자체 정의 단대단 TLP 접두사가 동일한 송신지 PEIC 번호 및 동일한 TLP 송신 순차 번호를 수반하고 있는 제1 TLP에 있어서, 상기 제1 TLP의 목적지 PEIC가, 먼저 수신된 제2 TLP만 수신하고 나중에 수신된 제2 TLP는 폐기하는 단계는 구체적으로,

상기 제1 TLP의 자체 정의된 TLP 접두사에 수반되어 있는 송신지 PEIC 번호 및 TLP 송신 순차와 송신지 PEIC로부터 수신될 것으로 예상되는 TLP의 순차 번호를 비교하고, 상기 제1 TLP의 자체 정의된 TLP 접두사에 수반되어 있는 송신지 PEIC 번호 및 TLP 송신 순차가 상기 송신지 PEIC로부터 수신될 것으로 예상되는 TLP의 순차 번호와 같으면 상기 제1 TLP를 수신하고, 같지 않으면 상기 제1 TLP를 폐기하는 단계인, 패킷 전송 방법.

### 청구항 23

제22항에 있어서,

각각의 TLP 전송 큐의 TLP 송신 순차 번호 및 TLP 송신 링크를 유지하고, 대응하는 TLP 전송 큐의 TLP 송신 순차 번호를 TLP가 송신될 때마다 1씩 증가시키는 단계; 및

TLP가 수신될 것으로 예상되는 다른 PEIC의 TLP 송신 순차 번호를 유지하고, TLP가 수신될 때마다, TLP가 수신될 것으로 예상되는 대응하는 송신지 PEIC의 TLP 송신 순차 번호를 1씩 증가시키는 단계

를 더 포함하는 패킷 전송 방법.

### 청구항 24

주변 구성요소 상호접속 고속 스위칭 네트워크에서 패킷 전송을 위한 방법에 있어서,

RC 또는 EP로부터 제3 TLP를 수신하는 단계; 및

상기 수신된 제3 TLP에 따라, 활성 및 대기 PCIE 스위칭 유닛에 연결된 송신 링크를 결정하고, 상기 제3 TLP를 상기 송신 링크를 통해 상기 활성 및 대기 PCIE 스위칭 유닛에 송신하는 단계

를 포함하며,

이에 따라 상기 제3 TLP의 목적지 PCIE 인터페이스 제어기는 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 상기 제3 TLP를 선택적으로 수신하고 상기 제3 TLP의 목적지 EP 또는 목적지 RC에 상기 제3 TLP를 송신하고; 상기 제3 TLP의 목적지 PEIC에 의해 회신되고 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 제1 수신확인 메시지 TLP가 시간이 종료될 때까지도 수신되지 않으면, 상기 제3 TLP를 다시 송신하며,

상기 제1 수신확인 메시지 TLP는 상기 제3 TLP가 수신되는 것을 확인하기 위한 패킷인, 패킷 전송 방법.

### 청구항 25

제24항에 있어서,

상기 제3 TLP를 상기 송신 링크를 통해 상기 활성 및 대기 PCIE 스위칭 유닛에 송신하는 단계 이전에,

상기 제3 TLP를 캡슐화하고, 상기 제3 TLP의 자체 정의 단대단 TLP 접두사에 송신지 PEIC 번호 및 TLP 송신 순차 번호를 부가하며, 이에 따라 상기 제3 TLP의 목적지 PEIC가 상기 제3 TLP에 있는 상기 송신지 PEIC 번호 및 상기 TLP 송신 순차 번호에 따라 제1 수신확인 메시지 TLP를 회신하는 단계

를 더 포함하며,

상기 회신된 제1 수신확인 메시지 TLP의 단대단 TLP 접두사는 상기 제3 TLP의 목적지 PEIC의 PEIC 번호 및 수신 확인된 TLP 송신 순차 번호를 수반하고 있으며,

상기 제3 TLP 내의 TLP 송신 순차 번호는 상기 제3 TLP의 송신지 PEIC에 의해 상기 제3 TLP의 목적지 PEIC에 송신된 TLP의 순차 번호이고, 상기 제1 수신확인 메시지 TLP 내의 수신확인된 TLP 송신 순차 번호는 상기 송신지 PEIC의 TLP 송신 순차 번호이고 상기 제3 TLP의 목적지 PEIC에 의해 이미 수신된 제3 TLP의 TLP 송신 순차 번호인, 패킷 전송 방법.

### **청구항 26**

제24항에 있어서,

상기 수신된 제3 TLP에 따라, 활성 및 대기 PCIE 스위칭 유닛에 연결된 송신 링크를 결정하고, 상기 제3 TLP를 상기 송신 링크를 통해 상기 활성 및 대기 PCIE 스위칭 유닛에 송신하는 단계는 구체적으로,

상기 수신된 제3 TLP에 따라 대응하는 어드레스 포워딩 테이블 또는 ID 포워딩 테이블을 검색하고, TLP 전송 큐 (TTQ)를 결정하며, 상기 제3 TLP의 목적지 PEIC에 대응하는 TLP 전송 큐에 상기 제3 TLP를 놓는 단계; 및

상기 제3 TLP를 상기 TLP 전송 큐의 상기 송신 링크를 통해 상기 활성 및 대기 PCIE 스위칭 유닛에 송신하는 단계인, 패킷 전송 방법.

### **청구항 27**

제26항에 있어서,

상기 제3 TLP의 목적지 PEIC에 의해 회신되고 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 제1 수신확인 메시지 TLP를 수신하는 단계; 및

상기 제1 수신확인 메시지 TLP에 수반되어 있는 TLP 송신 순차 번호 및 송신지 PEIC 번호에 따라 상기 TLP 전송 큐 내의 수신확인 제3 TLP를 삭제하는 단계

를 더 포함하는, 패킷 전송 방법.

### **청구항 28**

제26항에 있어서,

상기 제3 TLP의 목적지 PEIC에 의해 회신되고 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 제1 수신확인 메시지 TLP를 수신하는 단계 이전에,

상기 활성 및 대기 PCIE 스위칭 유닛에 의해 송신된 제4 TLP를 수신하고, 상기 제4 TLP의 유형에 따라, 상기 제4 TLP가 상기 제1 수신확인 메시지 TLP인지를 판단하고, 상기 제4 TLP가 상기 제1 수신확인 메시지 TLP가 아니면, 상기 수신된 제4 TLP를 상기 제4 TLP의 목적지 RC 또는 목적지 EP에 포워딩하는 단계

를 더 포함하는 패킷 전송 방법.

### **청구항 29**

제28항에 있어서,

상기 제4 TLP의 송신지 PEIC에 제2 수신확인 메시지 TLP를 회신하는 단계

를 더 포함하는 패킷 전송 방법.

### **청구항 30**

제29항에 있어서,

각각의 TLP 전송 큐의 TLP 송신 순차 번호 및 TLP 송신 링크를 유지하는 단계

를 더 포함하는 패킷 전송 방법.

### 청구항 31

제30항에 있어서,

상기 제1 수신확인 메시지 TLP에 수반되어 있는 상기 송신지 PEIC 번호 및 수신확인된 TLP 송신 순차 번호 정보

에 따라, 대응하는 TLP 전송 큐의 슬라이딩 윈도를 갱신하는 단계

를 더 포함하는 패킷 전송 방법.

### 청구항 32

제27항 내지 제31항 중 어느 한 항에 있어서,

고정-시간 검출 TLP를 시간 간격으로 모든 다른 PEIC에 송신하고, 목적지 PEIC에 의해 회신된 검출 응신 TLP가

지정된 시간 내에 수신되지 않으면, 대응하는 TLP 전송 큐의 송신 링크를 갱신하는 단계

를 더 포함하는 패킷 전송 방법.

### 청구항 33

주변 구성요소 상호접속 고속 스위칭 네트워크에서 패킷 전송을 위한 시스템에 있어서,

적어도 2개의 PCIE 노드 장치, 적어도 2개의 PCIE 인터페이스 제어기(PEIC), 및 2개의 활성 및 대기 PCIE 스위

칭 유닛을 포함하며, 상기 적어도 2개의 PCIE 노드 장치 각각은 상기 적어도 2개의 PCIE 인터페이스 제어기 중

하나에 연결되어 있고, 상기 적어도 2개의 PCIE 인터페이스 제어기 각각은 상기 2개의 활성 및 대기 PCIE 스위

칭 유닛에 각각 연결되어 있으며,

상기 적어도 2개의 PCIE 노드 장치 중 제1 PCIE 노드 장치는 상기 적어도 2개의 PCIE 인터페이스 제어기 중 제1

PCIE 인터페이스 제어기에 연결된 제1 TLP를 송신하도록 구성되어 있으며,

상기 제1 PCIE 인터페이스 제어기는 상기 제1 TLP를 수신하고, 상기 수신된 제1 TLP에 따라, 상기 2개의 활성

및 대기 PCIE 스위칭 유닛에 연결된 송신 링크를 결정하며, 상기 제1 TLP를 상기 송신 링크를 통해 상기 2개의

활성 및 대기 PCIE 스위칭 유닛에 동시에 송신하도록 구성되어 있으며,

상기 2개의 활성 및 대기 PCIE 스위칭 유닛 각각은 상기 제1 TLP를 상기 적어도 2개의 PCIE 인터페이스 제어기

중 제2 PCIE 인터페이스 제어기에 포워딩하도록 구성되어 있으며, 상기 제2 PCIE 인터페이스 제어기는 상기 제1

TLP의 목적지 PCIE 인터페이스 제어기이며,

상기 제2 PCIE 인터페이스 제어기는 상기 2개의 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 제1 TLP를 선

택적으로 수신하고 상기 제1 TLP를 상기 적어도 2개의 PCIE 노드 장치 중 제2 PCIE 노드 장치에 송신하도록 구

성되어 있으며, 상기 제2 PCIE 노드 장치는 상기 제1 TLP의 목적지 PCIE 노드 장치이며,

상기 제2 PCIE 노드 장치는 상기 제2 PCIE 인터페이스 제어기에 의해 포워딩된 상기 제1 TLP를 수신하도록 구

성되어 있는, 시스템.

### 청구항 34

제33항에 있어서,

상기 제1 PCIE 인터페이스 제어기는, 상기 제1 TLP를 캡슐화하고, 상기 제1 TLP의 단대단 TLP 접두사에 송신지

PEIC 번호 및 TLP 송신 순차 번호를 부가하도록 추가로 구성되어 있으며,

상기 제2 PCIE 인터페이스 제어기는, 상기 제1 TLP에 있는 상기 송신지 PEIC 번호 및 상기 TLP 송신 순차 번호

에 따라, 상기 2개의 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 상기 제1 TLP를 선택적으로 수신하도록 구

성되어 있으며,

상기 TLP 송신 순차 번호는 상기 제1 PEIC에 의해 상기 제2 PEIC에 송신된 TLP의 순차 번호이고, 상기 제1 TLP

에 있는 상기 송신지 PEIC 번호 및 상기 TLP 송신 순차 번호에 따라, 상기 제1 TLP를 선택적으로 수신하는 과정

은, 동일한 송신지 PEIC 번호 및 동일한 TLP 송신 순차 번호를 가지는 제1 TLP에 있어서, 먼저 도착하는 제1 TLP만을 수신하는 과정인, 시스템.

### 청구항 35

제33항 또는 제34항에 있어서,

상기 제1 PCIE 인터페이스 제어기는 상기 수신된 제1 TLP에 따라, 상기 2개의 활성 및 대기 PCIE 스위칭 유닛에 연결된 송신 링크를 결정하도록 구성되어 있으며, 이것은 구체적으로,

상기 제1 PCIE 인터페이스 제어기는 상기 제1 TLP에 따라 어드레스 포워딩 테이블 또는 ID 포워딩 테이블을 검색하고, 상기 제1 TLP에 대응하는 목적지 PEIC 번호를 결정하여, 상기 2개의 활성 및 대기 PCIE 스위칭 유닛에 연결되어 있고 상기 제1 TLP에 대응하는 송신 링크를 결정하도록 구성되어 있는, 시스템.

### 청구항 36

제35항에 있어서,

상기 PCIE 노드 장치는 루트 복합(RC) 또는 종점 장치(EP)이고, 각각의 PCIE 인터페이스 제어기는 하나의 RC 또는 적어도 하나의 EP에 연결되어 있는, 시스템.

### 청구항 37

주변 구성요소 상호접속 고속 스위칭 네트워크에서 패킷 전송을 위한 시스템에 있어서,

적어도 2개의 PCIE 노드 장치, 적어도 2개의 PCIE 인터페이스 제어기(PEIC), 및 2개의 활성 및 대기 PCIE 스위칭 유닛을 포함하며, 상기 적어도 2개의 PCIE 노드 장치 각각은 상기 적어도 2개의 PCIE 인터페이스 제어기 중 하나에 연결되어 있고, 상기 적어도 2개의 PCIE 인터페이스 제어기 각각은 상기 2개의 활성 및 대기 PCIE 스위칭 유닛에 각각 연결되어 있으며,

상기 적어도 2개의 PCIE 노드 장치 중 제3 PCIE 노드 장치는 상기 적어도 2개의 PCIE 인터페이스 제어기 중 제3 PCIE 인터페이스 제어기에 연결된 제3 TLP를 송신하도록 구성되어 있으며,

상기 제3 PCIE 인터페이스 제어기는 상기 제3 TLP를 수신하고, 상기 수신된 제3 TLP에 따라, 2개의 활성 및 대기 PCIE 스위칭 유닛에 연결된 송신 링크를 결정하고, 상기 제3 TLP를 상기 송신 링크를 통해 상기 2개의 활성 및 대기 PCIE 스위칭 유닛에 송신하며, 상기 적어도 2개의 PCIE 인터페이스 제어기 중 제4 PCIE 인터페이스 제어기에 의해 회신되고 상기 2개의 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 제1 수신확인 메시지 TLP가 시간이 종료될 때까지도 수신되지 않으면, 상기 2개의 활성 및 대기 PCIE 스위칭 유닛에 연결된 송신 링크를 통해 상기 제4 PCIE 인터페이스 제어기에 상기 제3 TLP를 다시 송신하도록 구성되어 있으며, 상기 제4 PCIE 인터페이스 제어기는 상기 제3 TLP의 목적지 PCIE 인터페이스 제어기이며,

상기 2개의 활성 및 대기 PCIE 스위칭 유닛은 상기 제3 TLP를 상기 제4 PCIE 인터페이스 제어기에 포워딩하며, 상기 제4 PCIE 인터페이스 제어기에 의해 회신된 상기 제1 수신확인 메시지 TLP를 상기 제3 PCIE 인터페이스 제어기에 포워딩하도록 구성되어 있으며,

상기 제4 PCIE 인터페이스 제어기는 상기 2개의 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 제3 TLP를 수신하고 상기 제3 TLP를 상기 적어도 2개의 PCIE 노드 장치 중 제4 PCIE 노드 장치에 송신하며, 상기 제4 PCIE 노드 장치는 상기 제3 TLP의 목적지 PCIE 노드 장치이며; 상기 제1 수신확인 메시지 TLP를 상기 제3 PCIE 인터페이스 제어기에 회신하여, 상기 제3 TLP가 수신된 것을 확인하도록 구성되어 있으며,

상기 제4 PCIE 노드 장치는 상기 제4 PCIE 인터페이스 제어기에 의해 포워딩된 상기 제3 TLP를 수신하도록 구성되어 있는, 시스템.

### 청구항 38

제37항에 있어서,

상기 제3 PEIC는 상기 제4 PEIC에 의해 회신되고 상기 2개의 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 상기 제1 수신확인 메시지 TLP를 수신하며, 상기 제1 수신확인 메시지 TLP에 수반되어 있는 TLP 송신 순차 번호 정보 및 송신지 PEIC 번호에 따라 상기 수신확인된 제3 TLP를 삭제하도록 추가로 구성되어 있는, 시스템.

**청구항 39**

제37항 또는 제38항에 있어서,

상기 제3 PEIC는 상기 TLP를 캡슐화하고, 상기 제3 TLP의 단대단 TLP 접두사에 송신지 PEIC 번호(SPEIC) 및 TLP 송신 순차 번호를 부가하며, 상기 캡슐화된 제3 TLP를 상기 송신 링크를 통해 상기 2개의 활성 및 대기 PCIE 스위칭 유닛에 송신하도록 추가로 구성되어 있으며,

상기 제4 PCIE는 상기 제3 TLP에 수반되어 있는 상기 송신지 PEIC 번호 및 상기 TLP 송신 순차 번호에 따라 상기 제1 수신확인 메시지 TLP를 회신하도록 구성되어 있으며,

상기 회신된 제1 수신확인 메시지 TLP의 단대단 TLP 접두사는 상기 송신지 PEIC 번호 및 수신확인된 TLP 송신 순차 번호를 수반하고 있으며, 상기 TLP 송신 순차 번호는 상기 제3 PEIC에 의해 상기 제4 PEIC에 송신된 TLP의 순차 번호이고, 상기 수신확인된 TLP 송신 순차 번호는 상기 제3 PEIC로부터 상기 제4 PEIC에 의해 이미 수신된 TLP의 송신 순차 번호인, 시스템.

**청구항 40**

제39항에 있어서,

상기 제3 PEIC는 다른 PEIC에 대한 TLP 송신 순차 번호 및 TLP 송신 링크를 유지하도록 추가로 구성되어 있는, 시스템.

**청구항 41**

제40항에 있어서,

각각의 PCIE 인터페이스 제어기는 고정-시간 겹출 TLP를 시간 간격으로 모든 다른 PEIC에 송신하고, 회신된 겹출 응신 TLP가 지정된 시간 내에 수신되지 않은 PEIC에 대응하는 송신 링크를 개선하도록 추가로 구성되어 있는, 시스템.

**청구항 42**

제41항에 있어서,

상기 PCIE 노드 장치는 루트 복합(RC) 또는 종점 장치(EP)이고, 각각의 PCIE인터페이스 제어기는 하나의 RC 또는 적어도 하나의 EP에 연결되어 있는, 시스템.

**청구항 43**

주변 구성요소 상호접속 고속 인터페이스 제어기(PEIC)에 있어서,

프로세서 및 메모리를 포함하고, 상기 메모리는 실행 명령을 저장하며; 상기 주변 구성요소 상호접속 고속 인터페이스 제어기(PEIC)가 실행되면, 상기 프로세서는 상기 메모리와 통신하고, 상기 프로세서는 상기 실행 명령을 실행하며, 이에 따라 주변 구성요소 상호접속 고속 인터페이스 제어기(PEIC)는 제18항에 따른 방법을 실행하는, 주변 구성요소 상호접속 고속 인터페이스 제어기(PEIC).

**청구항 44**

주변 구성요소 상호접속 고속 인터페이스 제어기(PEIC)에 있어서,

프로세서 및 메모리를 포함하고, 상기 메모리는 실행 명령을 저장하며; 상기 주변 구성요소 상호접속 고속 인터페이스 제어기(PEIC)가 실행되면, 상기 프로세서는 상기 메모리와 통신하고, 상기 프로세서는 상기 실행 명령을 실행하며, 이에 따라 주변 구성요소 상호접속 고속 인터페이스 제어기(PEIC)는 제24항에 따른 방법을 실행하는, 주변 구성요소 상호접속 고속 인터페이스 제어기(PEIC).

**청구항 45**

컴퓨터 관독 가능형 매체에 있어서,

컴퓨터 실행 명령을 포함하며, 상기 컴퓨터 실행 명령은 주변 구성요소 상호접속 고속 인터페이스 제어기(PEI

C)가 제18항에 따른 방법을 실행할 수 있게 하는 데 사용되는, 컴퓨터 관독 가능형 매체.

#### 청구항 46

컴퓨터 관독 가능형 매체에 있어서,

컴퓨터 실행 명령을 포함하며, 상기 컴퓨터 실행 명령은 주변 구성요소 상호접속 고속 인터페이스 제어기(PEI C)가 제24항에 따른 방법을 실행할 수 있게 하는 데 사용되는, 컴퓨터 관독 가능형 매체.

#### 발명의 설명

##### 기술 분야

[0001] 본 발명의 실시 예는 컴퓨터 분야에 관한 것이며, 특히, 주변 구성요소 상호접속 고속(Interconnet Express: PCIE로 약칭) 스위칭 네트워크에서 패킷 전송을 실행하기 위한 방법, 장치, 시스템, 및 저장 매체에 관한 것이다.

##### 배경 기술

[0002] 컴퓨터와 통신기술이 나날이 발전함에 따라, 대용량의 차세대 입출력(Input/Output: I/O로 약칭) 인터페이스, 예를 들어, 기가비트 이더넷(Gigabit Ethernet: GE로 약칭) 및 10 기가비트 이더넷(10 Gigabit Ethernet: 10GE로 약칭) 기술, 및 4G/8G 파이버 채널(Fibre Channel: FC) 기술을 사용하는 I/O 인터페이스가 출현하고 있다. I/O 인터페이스의 속도는 비약적으로 향상되고 있다. 종래의 주변 구성요소 상호접속(Peripheral Component Interconnet: PCI로 약칭) 버스의 대역폭은 컴퓨터 시스템에서 대량의 고대역폭 동시 읽기 및 쓰기의 요건에 더 이상 부합하지 못하며, PCI 버스는 시스템 성능의 향상에 걸림돌이 되어 버렸다. 그러므로 PCIE 버스가 개발되었다. PCIE 버스는 복수의 채널(X1/X2/X4/X8/X16/X/32)을 통해 지극히 높은 대역폭을 제공하여 시스템 요건을 충족시킬 수 있다.

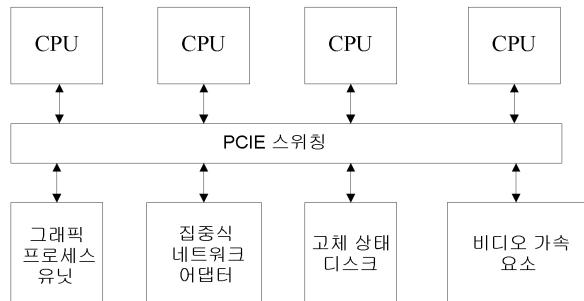

[0003] PCIE는 점대점(point-to-point) 통신 모드를 사용한다. 루트 복합(Root Complex: RC로 약칭)에서 종점(Endpoint: EP로 약칭) 장치에 이르기까지 트리 네트워크 구조가 형성되어 있다. 트랜잭션 계층 패킷(Transaction Layer Packet: TLP로 약칭)을 기초로 해서 전송 계층에서 데이터 교환을 수행한다. 보드에서 PCIE를 버스로 사용하면, 간단한 트리 구조로 시스템의 신뢰도를 높일 수 있다. PCIE 버스가 실패이면, 보드 내에서 효과가 제한된다. 컴퓨터, 네트워크 및 저장 아키텍처를 교체할 때, 이러한 구성요소 중 PCIE를 스위칭 네트워크로서 사용하는 장점은 탁월해진다. 도 1에 도시된 바와 같이, 그래픽 프로세스 유닛(Graphics Process Unit: GPU로 약칭), 집중식 네트워크 어댑터(Converge Network Adapter: CNA로 약칭), 고체 상태 디스크(Solid-State Disk: SSD), 비디오 가속 요소 등을 가상화 기술을 제공하며, GPU, CNA, SSD 등의 자원 공유는 PCIE 스위칭을 통해 중앙처리장치(CPU) 간 또는 가상 머신(Virtual Machine: VM으로 약칭) 간에 실행될 수 있으며, 이에 의해 시스템의 활용 비율도 향상된다. GPU/CNA/SSD/비디오 가속 요소/PCIE 스위칭 요소 또는 PCIE 링크가 실패이면, PCIE 사양에서 규정된 트리 스위치 구조로 인해 모든 CPU에서 비정상적인 동작이 수행되어, 시스템의 신뢰도가 급격하게 저하된다.

##### 발명의 내용

##### 해결하려는 과제

[0004] 전술한 설명에 따라, PCIE의 현재의 트리-구조 네트워킹 방식으로 인해, 시스템의 신뢰도가 어플리케이션 요건을 충족하지 못한다.

##### 과제의 해결 수단

[0005] 따라서, 본 발명의 실시예는 PCIE 스위칭 네트워크에서 패킷 전송을 실행하기 위한 방법, 장치, 시스템, 및 저장 매체를 제공하며, 이에 의해 PCIE 이중-평면 스위칭 네트워크에서 패킷 전송을 실행한다.

[0006] 한 관점에서, 본 발명의 실시예는 주변 구성요소 상호접속 고속 인터페이스 제어기(PEIC)를 제공하며, 상기 주변 구성요소 상호접속 고속 인터페이스 제어기는,

[0007] 루트 복합(Root Complex: RC) 또는 종점 장치(Endpoint: EP)로부터 제1 트랜잭션 계층 패킷(transaction layer packet: TLP)을 수신하고, 상기 제1 TLP를, 프로세싱을 위한 신뢰할 수 있는 TLP 전송(reliable TLP

transmission: RTT) 모듈에 포워딩하도록 구성되어 있는 PCI 대 PCI 브리지 P2P 모듈; 및

[0008] 상기 수신된 제1 TLP에 따라, 활성 및 대기 PCIE 스위칭 유닛에 연결된 송신 링크를 결정하고, 상기 제1 TLP를 상기 송신 링크를 통해 상기 활성 및 대기 PCIE 스위칭 유닛에 동시에 송신하도록 구성되어 있고, 이에 따라 상기 제1 TLP의 목적지 PCIE 인터페이스 제어기가 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 상기 제1 TLP를 선택적으로 수신하고 상기 제1 TLP의 목적지 EP 또는 목적지 RC에 상기 제1 TLP를 송신하는, 신뢰할 수 있는 TLP 전송(RTT) 모듈

을 포함한다.

[0010] 제1 관점의 제1 가능한 실행 방식에서,

[0011] 상기 신뢰할 수 있는 TLP 전송 모듈은, 상기 제1 TLP를 캡슐화하고, 상기 제1 TLP의 자체 정의 단대단(self-defined end-to-end) TLP 접두사에 송신지 PEIC 번호 및 TLP 송신 순차 번호를 부가하도록 추가로 구성되어 있으며, 이에 따라 상기 제1 TLP의 목적지 PEIC가 상기 송신지 PEIC 번호 및 상기 TLP 송신 순차 번호에 따라 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 상기 제1 TLP를 선택적으로 수신하며, 상기 TLP 송신 순차 번호는 송신지 PEIC에 의해 상기 제1 TLP의 목적지 PEIC에 송신된 TLP의 순차 번호이고, 상기 송신지 PEIC 번호 및 상기 TLP 송신 순차 번호에 따라 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 상기 제1 TLP를 선택적으로 수신하는 과정은, 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩되고 동일한 송신지 PEIC 번호 및 동일한 TLP 송신 순차 번호를 가지는 제1 TLP에 있어서, 먼저 도착하는 제1 TLP만을 수신하는 과정이다.

[0012] 제1 관점의 실행 방식과 결합해서, 제2 가능한 실행 방식에서, 상기 신뢰할 수 있는 TLP 전송 모듈은,

[0013] 상기 수신된 제1 TLP에 따라 어드레스 포워딩 테이블 또는 ID 포워딩 테이블을 검색하고, TLP 전송 큐(TLP transmission queue: TTQ)를 결정하며, 상기 제1 TLP를 상기 TLP 전송 큐에 놓도록 구성되어 있고, 상기 TLP 전송 큐는 상기 제1 TLP의 목적지 PEIC에 대응하는, TLP 디스패치 모듈; 및

[0014] 상기 TLP 전송 큐 내의 제1 TLP를 상기 TLP 전송 큐의 상기 송신 링크를 통해 상기 활성 및 대기 PCIE 스위칭 유닛에 동시에 송신하도록 구성되어 있고, 이에 따라 상기 제1 TLP의 목적지 PCIE 인터페이스 제어기가 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 상기 제1 TLP를 선택적으로 수신하고 상기 제1 TLP의 목적지 EP 또는 목적지 RC에 상기 제1 TLP를 송신하는, 제2 모듈

을 포함한다.

[0016] 제1 관점의 제2 가능한 실행 방식과 결합해서, 제3 가능한 실행 방식에서,

[0017] 상기 송신 모듈은, 상기 제1 TLP를 캡슐화하고, 상기 제1 TLP의 단대단 TLP 접두사에 송신지 PEIC 번호(SPEIC) 및 TLP 송신 순차 번호(SEQUENCE)를 부가하도록 추가로 구성되어 있으며, 이에 따라 상기 목적지 PEIC가 상기 SPEIC 및 상기 SEQUENCE에 따라 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 상기 제1 TLP를 선택적으로 수신하며, 상기 TLP 송신 순차 번호는 송신지 PEIC에 의해 상기 제1 TLP의 목적지 PEIC에 송신된 TLP의 순차 번호이고, 상기 SPEIC 및 상기 SEQUENCE에 따라 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 상기 제1 TLP를 선택적으로 수신하는 과정은, 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩되고 동일한 상기 SPEIC 및 동일한 SEQUENCE를 가지는 제1 TLP에 있어서, 먼저 도착하는 제1 TLP만을 수신하는 과정이다.

[0018] 제1 관점의 제2 가능한 실행 방식 또는 제1 관점의 제3 가능한 실행 방식과 결합해서, 제4 가능한 실행 방식에서, 상기 신뢰할 수 있는 TLP 전송 모듈은,

[0019] 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 송신된 제2 TLP를 선택적으로 수신하고, 상기 수신된 제2 TLP를 상기 P2P 모듈에 송신하도록 구성되어 있고, 이에 따라 상기 P2P 모듈이 상기 제2 TLP의 목적지 RC 또는 목적지 EP에 상기 제2 TLP를 포워딩하는, 수신 모듈을 더 포함한다.

[0020] 제1 관점의 제4 가능한 실행 방식과 결합해서, 제5 가능한 실행 방식에서, 상기 수신 모듈은 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 송신된 제2 TLP를 선택적으로 수신하도록 추가로 구성되어 있고, 이것은 구체적으로,

[0021] 상기 수신 모듈은 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 송신된 제2 TLP를 수신하고, 자체 정의 TLP 접두사가 동일한 송신지 PEIC 번호(SPEIC) 및 동일한 TLP 송신 순차 번호(SEQUENCE)를 수반하는 제2 TLP에 있어서, 먼저 수신된 제2 TLP만 수신하고 나중에 수신된 제2 TLP는 폐기하도록 구성되어 있다.

[0022] 제1 관점의 제2 내지 제5 가능한 실행 방식 중 하나와 결합해서, 제6 가능한 실행 방식에서, 상기 신뢰할 수 있

는 TLP 전송 모듈은,

[0023] 각각의 TLP 전송 큐의 TLP 송신 순차 번호 및 TLP 송신 링크를 유지 및 관리하도록 구성되어 있는 TLP 전송 큐 관리 모듈을 더 포함하며, 상기 TLP 전송 큐의 TLP 송신 순차 번호는 전송 큐에 대응하는 목적지 PEIC에 송신된 TLP의 송신 순차 번호이고, 상기 TLP 전송 큐의 TLP 송신 링크는 전송 큐에 대응하는 목적지 PEIC에 대한 TLP 송신 링크이다.

[0024] 제2 관점에서, 본 발명의 실시예에는 주변 구성요소 상호접속 고속 인터페이스 제어기(PEIC)를 제공하며, 상기 주변 구성요소 상호접속 고속 인터페이스 제어기는,

[0025] 루트 복합(RC) 또는 종점 장치(EP)로부터 제3 트랜잭션 계층 패킷(TLP)을 수신하고, 상기 제1 TLP를 신뢰할 수 있는 TLP 전송(RTT) 모듈에 포워딩하도록 구성되어 있는 PCI 대 PCI 브리지 P2P 모듈; 및

[0026] 상기 수신된 제3 TLP에 따라, PCIE 스위칭 유닛에 연결된 송신 링크를 결정하고, 상기 제3 TLP를 상기 송신 링크를 통해 상기 PCIE 스위칭 유닛에 송신하도록 구성되어 있으며, 이에 따라 상기 제3 TLP의 목적지 PCIE 인터페이스 제어기가 상기 PCIE 스위칭 유닛에 의해 포워딩된 상기 제3 TLP를 수신하고 상기 제3 TLP의 목적지 EP 또는 목적지 RC에 상기 제3 TLP를 송신하며; 상기 제3 TLP의 목적지 PEIC에 의해 회신되고 상기 PCIE 스위칭 유닛에 의해 포워딩된 제1 수신확인 메시지 TLP가 시간이 종료될 때까지도 수신되지 않으면, 상기 제3 TLP를 다시 송신하는, 상기 신뢰할 수 있는 TLP 전송(RTT) 모듈

을 포함한다.

[0027] 제2 관점의 제1 가능한 실행 방식에서,

[0029] 상기 RTT 모듈은, 상기 제3 TLP를 캡슐화하고, 상기 제3 TLP의 자체 정의 단대단 TLP 접두사에 송신지 PEIC 번호 및 TLP 송신 순차 번호를 부가하고, 상기 캡슐화된 제3 TLP를 상기 송신 링크를 통해 상기 PCIE 스위칭 유닛에 송신하도록 추가로 구성되어 있으며, 이에 따라 상기 제3 TLP의 목적지 PEIC가 상기 수신된 제3 TLP에 있는 상기 송신지 PEIC 번호 및 상기 TLP 송신 순차 번호에 따라 제1 수신확인 메시지 TLP를 회신하며, 상기 회신된 제1 수신확인 메시지 TLP의 자체 정의된 단대단 TLP 접두사는 상기 제3 TLP의 목적지 PEIC의 PEIC 번호 및 수신 확인된 TLP 송신 순차 번호를 수반하고 있으며, 상기 제3 TLP 내의 TLP 송신 순차 번호는 상기 제3 TLP의 송신지 PEIC에 의해 상기 제3 TLP의 목적지 PEIC에 송신된 TLP의 순차 번호이고, 상기 제1 수신확인 메시지 TLP 내의 상기 수신확인된 TLP 송신 순차 번호는 상기 송신지 PEIC의 TLP 송신 순차 번호이고 상기 제3 TLP의 목적지 PEIC에 의해 이미 수신된 제3 TLP의 TLP 송신 순차 번호이다.

[0030] 제2 관점의 실행 방식과 결합해서, 제2 가능한 실행 방식에서, 상기 신뢰할 수 있는 TLP 전송 모듈은,

[0031] 상기 수신된 제3 TLP에 따라 어드레스 포워딩 테이블 또는 ID 포워딩 테이블을 검색하고, TLP 전송 큐(TTQ)를 결정하며, 상기 제3 TLP를 상기 TLP 전송 큐에 놓도록 구성되어 있고, 상기 TLP 전송 큐는 상기 제3 TLP의 목적지 PEIC에 대응하는, TLP 디스패치 모듈;

[0032] 상기 TLP 전송 큐 내의 제3 TLP를 상기 TLP 전송 큐의 상기 송신 링크를 통해 상기 PCIE 스위칭 유닛에 송신하도록 구성되어 있고, 이에 따라 상기 제3 TLP의 목적지 PCIE 인터페이스 제어기가 상기 PCIE 스위칭 유닛에 의해 포워딩된 상기 제3 TLP를 수신하고 상기 제3 TLP의 목적지 EP 또는 목적지 RC에 상기 제3 TLP를 송신하며; 상기 제3 TLP의 목적지 PEIC에 의해 회신되고 상기 PCIE 스위칭 유닛에 의해 포워딩된 제1 수신확인 메시지 TLP가 시간이 종료될 때까지도 수신되지 않으면, 상기 제3 TLP를 다시 송신하도록 구성되어 있는 송신 모듈;

[0033] 상기 제3 TLP의 목적지 PEIC에 의해 회신되고 상기 PCIE 스위칭 유닛에 의해 포워딩된 제1 수신확인 메시지 TLP를 수신하고, 상기 제1 수신확인 메시지 TLP를 수신확인 모듈에 전달하도록 구성되어 있는 수신 모듈;

[0034] 상기 제1 수신확인 메시지 TLP에 수반되어 있는 TLP 송신 순차 번호 및 송신지 PEIC 번호에 따라, 상기 TLP 전송 큐 내의 수신확인된 제3 TLP를 삭제한다는 것을 TLP 전송 큐 관리 모듈에 통지하도록 구성되어 있는 상기 수신확인 모듈; 및

[0035] 상기 수신확인 모듈의 통지에 따라 상기 TLP 전송 큐 내의 수신확인된 제3 TLP를 삭제하도록 구성되어 있는 상기 TLP 전송 큐 관리 모듈

을 포함한다.

[0036] 제2 관점의 제2 가능한 실행 방식과 결합해서, 제3 가능한 실행 방식에서,

- [0038] 상기 송신 모듈은, 상기 제3 TLP를 캡슐화하고, 상기 제3 TLP의 단대단 TLP 접두사에 송신지 PEIC 번호 및 TLP 송신 순차 번호를 부가하며, 상기 캡슐화된 제3 TLP를 상기 TTQ의 송신 링크를 통해 상기 PCIE 스위칭 유닛에 송신하도록 구성되어 있으며, 이에 따라 상기 제3 TLP의 목적지 PEIC가, 상기 송신지 PEIC 번호 및 상기 TLP 송신 순차 번호에 따라, 상기 수신된 TLP에 응답해서 제1 수신확인 메시지 TLP를 회신하며, 상기 회신된 제1 수신확인 메시지 TLP의 단대단 TLP 접두사는 상기 송신지 PEIC 번호 및 수신확인된 TLP 송신 순차 번호를 수반하고 있으며, 상기 TLP 송신 순차 번호는 상기 제3 TLP의 송신지 PEIC에 의해 상기 제3 TLP의 목적지 PEIC에 송신된 TLP의 순차 번호이고, 상기 수신확인된 TLP 송신 순차 번호는 상기 송신지 PEIC로부터 상기 제3 TLP의 목적지 PEIC에 의해 이미 수신된 TLP의 송신 순차 번호이다.

- [0039] 제2 관점의 제2 가능한 실행 방식 또는 제2 관점의 제3 가능한 실행 방식과 결합해서, 제4 가능한 실행 방식에서,

- [0040] 상기 TLP 전송 큐 관리 모듈은, 각각의 TLP 전송 큐의 TLP 송신 순차 번호 및 TLP 송신 링크를 유지하도록 추가로 구성되어 있다.

- [0041] 제2 관점의 제1 내지 제3 가능한 실행 방식 중 어느 하나와 결합해서, 제4 가능한 실행 방식에서,

- [0042] 상기 수신 모듈은 상기 PCIE 스위칭 유닛으로부터 송신된 제4 TLP를 수신하고, 상기 제4 TLP가 수신확인 메시지 TLP인지를 판단하며, 상기 제4 TLP가 수신확인 메시지 TLP가 아니면, 상기 수신된 제4 TLP를 상기 제4 TLP의 송신지 PEIC에 대응하는 TLP 수신확인 순차 TAS에 베퍼링하도록 추가로 구성되어 있으며,

- [0043] 상기 P2P 모듈은 상기 TLP 수신확인 순차 TAS 내의 상기 제4 TLP를 획득하고, 상기 제4 TLP를 상기 제4 TLP의 목적지 RC/EP에 포워딩하도록 추가로 구성되어 있다.

- [0044] 제2 관점의 제4 가능한 실행 방식과 결합해서, 제5 가능한 실행 방식에서, 상기 신뢰할 수 있는 TLP 전송 모듈은,

- [0045] 상기 TLP 수신확인 순차가 상기 제4 TLP를 수신한 후, 상기 제4 TLP의 송신지 PEIC에 수신확인 메시지 TLP를 회신한다는 것을 상기 수신확인 모듈에 통지하도록 추가로 구성되어 있는 TLP 수신확인 순차 관리 모듈

- [0046] 을 더 포함하고,

- [0047] 상기 수신확인 모듈은 제2 수신확인 메시지 TLP를 생성하고, 상기 제2 수신확인 메시지 TLP를 상기 제4 TLP의 송신지 PEIC에 대응하는 TLP 전송 큐에 베퍼링하도록 추가로 구성되어 있으며, 이에 따라 상기 제2 수신확인 메시지 TLP는 스캐줄링되고 상기 송신 모듈에 의해 송신된다.

- [0048] 제2 관점의 제2 내지 제5 가능한 실행 방식 중 어느 하나와 결합해서, 제6 가능한 실행 방식에서, 상기 신뢰할 수 있는 TLP 전송 모듈은,

- [0049] 고정-시간 검출 TLP를 시간 간격으로 모든 다른 PEIC에 송신하고, 목적지 PEIC에 의해 회신된 검출 응신 TLP가 지정된 시간 내에 수신되지 않으면, 상기 검출 응신 TLP를 회신하는 목적지 PEIC에 대응하는 TTQ의 송신 링크를 개선한다는 것을 TLP 송신 큐 관리 모듈에 통지하도록 구성되어 있는 중추부 모듈(heartbeat module)

- [0050] 을 더 포함하며,

- [0051] 상기 TLP 전송 큐 관리 모듈은 상기 중추부 모듈의 통지에 따라 상기 TLP 전송 큐의 송신 링크를 개선하도록 추가로 구성되어 있다.

- [0052] 제3 관점에서, 본 발명의 실시예는 주변 구성요소 상호접속 고속 스위칭 네트워크에서 패킷 전송을 위한 방법을 제공하며, 상기 패킷 전송 방법은,

- [0053] RC 또는 EP로부터 제1 TLP를 수신하는 단계; 및

- [0054] 상기 수신된 제1 TLP에 따라, 활성 및 대기 PCIE 스위칭 유닛에 연결된 송신 링크를 결정하고, 상기 제1 TLP를 상기 송신 링크를 통해 상기 활성 및 대기 PCIE 스위칭 유닛에 동시에 송신하며, 이에 따라 상기 제1 TLP의 목적지 PCIE 인터페이스 제어기가 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 상기 제1 TLP를 선택적으로 수신하고 상기 제1 TLP의 목적지 EP 또는 목적지 RC에 상기 제1 TLP를 송신하는 단계

- [0055] 를 포함한다.

- [0056] 제3 관점의 제1 가능한 실행 방식에서,

- [0057] 상기 제1 TLP를 상기 송신 링크를 통해 상기 활성 및 대기 PCIE 스위칭 유닛에 동시에 송신하는 과정 이전에,

- [0058] 상기 제1 TLP를 캡슐화하고, 상기 제1 TLP의 자체 정의 단대단(self-defined end-to-end) TLP 접두사에 송신지 PEIC 번호 및 TLP 송신 순차 번호를 부가하며, 이에 따라 상기 송신지 PEIC 번호 및 상기 TLP 송신 순차 번호에 따라 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 상기 제1 TLP를 선택적으로 수신하는 단계

- [0059] 를 더 포함하며,

- [0060] 상기 TLP 송신 순차 번호는 상기 제1 TLP의 송신지 PEIC에 의해 상기 제1 TLP의 목적지 PEIC에 송신된 TLP의 순차 번호이고, 상기 송신지 PEIC 번호 및 상기 TLP 송신 순차 번호에 따라 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 상기 제1 TLP를 선택적으로 수신하는 단계는, 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩되고 동일한 송신지 PEIC 번호 및 동일한 TLP 송신 순차 번호를 가지는 제1 TLP에 있어서, 먼저 도착하는 제1 TLP만을 수신한다.

- [0061] 제3 관점 또는 제3 관점의 제1 가능한 실행 방식과 결합해서, 제2 가능한 실행 방식에서, 상기 수신된 제1 TLP에 따라, 활성 및 대기 PCIE 스위칭 유닛에 연결된 송신 링크를 결정하고, 상기 제1 TLP를 상기 송신 링크를 통해 상기 활성 및 대기 PCIE 스위칭 유닛에 동시에 송신하며, 이에 따라 상기 제1 TLP의 목적지 PCIE 인터페이스 제어기가 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 상기 제1 TLP를 선택적으로 수신하고 상기 제1 TLP의 목적지 EP 또는 목적지 RC에 상기 제1 TLP를 송신하는 단계는 구체적으로,

- [0062] 상기 수신된 제1 TLP에 따라 어드레스 포워딩 테이블 또는 ID 포워딩 테이블을 검색하고, TLP 전송 큐(TTQ)를 결정하며, 상기 제1 TLP의 목적지 PEIC에 대응하는 TLP 전송 큐에 상기 제1 TLP를 놓는 단계; 및

- [0063] 상기 TLP 전송 큐 내의 제1 TLP를 상기 TLP 전송 큐의 송신 링크를 통해 상기 활성 및 대기 PCIE 스위칭 유닛에 동시에 송신하며, 이에 따라 상기 제1 TLP의 목적지 PCIE 인터페이스 제어기가 상기 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 상기 제1 TLP를 선택적으로 수신하고 상기 제1 TLP의 목적지 EP 또는 목적지 RC에 상기 제1 TLP를 송신하는 단계이다.

- [0064] 제3 관점의 제1 가능한 실행 방식 또는 제3 관점의 제2 가능한 실행 방식에서,

- [0065] 자체 정의 단대단 TLP 접두사가 동일한 송신지 PEIC 번호 및 동일한 TLP 송신 순차 번호를 수반하고 있는 제1 TLP에 있어서, 상기 제1 TLP의 목적지 PEIC가, 먼저 수신된 제2 TLP만 수신하고 나중에 수신된 제2 TLP는 폐기하는 단계

- [0066] 를 더 포함한다.

- [0067] 제3 관점의 제1 내지 제3 가능한 실행 방식 중 어느 하나와 조합해서, 제4 가능한 실행 방식에서,

- [0068] 각각의 TLP 전송 큐의 TLP 송신 순차 번호 및 TLP 송신 링크를 유지하고, 대응하는 TLP 전송 큐의 TLP 송신 순차 번호를 TLP가 송신될 때마다 1씩 증가시키는 단계; 및

- [0069] TLP가 수신될 것으로 예상되는 다른 PEIC의 TLP 송신 순차 번호를 유지하고, TLP가 수신될 때마다, TLP가 수신될 것으로 예상되는 대응하는 송신지 PEIC의 TLP 송신 순차 번호를 1씩 증가시키는 단계

- [0070] 를 더 포함한다.

- [0071] 제4 관점에서, 본 발명의 실시예는 주변 구성요소 상호접속 고속 스위칭 네트워크에서 패킷 전송을 위한 방법을 제공하며, 상기 패킷 전송 방법은,

- [0072] RC 또는 EP로부터 제3 TLP를 수신하는 단계; 및

- [0073] 상기 수신된 제3 TLP에 따라, PCIE 스위칭 유닛에 연결된 송신 링크를 결정하고, 상기 제3 TLP를 상기 송신 링크를 통해 상기 PCIE 스위칭 유닛에 송신하는 단계

- [0074] 를 포함하며,

- [0075] 이에 따라 상기 제3 TLP의 목적지 PCIE 인터페이스 제어기는 상기 PCIE 스위칭 유닛에 의해 포워딩된 상기 제3 TLP를 수신하고 상기 제1 TLP의 목적지 EP 또는 목적지 RC에 상기 제3 TLP를 송신하며; 상기 제3 TLP의 목적지 PEIC에 의해 회신되고 상기 PCIE 스위칭 유닛에 의해 포워딩된 제1 수신확인 메시지 TLP가 시간이 종료될 때까지도 수신되지 않으면, 상기 제3 TLP를 다시 송신한다.

- [0076] 제4 관점의 제1 실행 방식에서,

- [0077] 상기 수신된 제3 TLP에 따라, PCIE 스위칭 유닛에 연결된 송신 링크를 결정하고, 상기 제3 TLP를 상기 송신 링크를 통해 상기 PCIE 스위칭 유닛에 송신하는 단계는 구체적으로,

- [0078] 상기 수신된 제3 TLP에 따라 어드레스 포워딩 테이블 또는 ID 포워딩 테이블을 검색하고, TLP 전송 큐(TTQ)를 결정하며, 상기 제3 TLP의 목적지 PEIC에 대응하는 TLP 전송 큐에 상기 제1 TLP를 놓는 단계; 및

- [0079] 상기 제3 TLP를 상기 TLP 전송 큐의 송신 링크를 통해 상기 PCIE 스위칭 유닛에 송신하는 단계이다.

- [0080] 제4 관점의 제1 가능한 실행 방식과 결합해서, 제2 가능한 실행 방식에서,

- [0081] 상기 제3 TLP의 목적지 PEIC에 의해 회신되고 상기 PCIE 스위칭 유닛에 의해 포워딩된 제1 수신확인 메시지 TLP를 수신하는 단계; 및

- [0082] 상기 제1 수신확인 메시지 TLP에 수반되어 있는 TLP 송신 순차 번호 및 송신지 PEIC 번호에 따라 상기 TLP 전송 큐 내의 수신확인 제3 TLP를 삭제하는 단계

- [0083] 를 더 포함한다.

- [0084] 제4 관점의 제1 가능한 실행 방식 또는 제4 관점의 제2 가능한 실행 방식과 결합해서, 제3 가능한 실행 방식에서,

- [0085] 상기 제3 TLP를 캡슐화하고, 상기 제3 TLP의 자체 정의 단대단 TLP 접두사에 송신지 PEIC 번호 및 TLP 송신 순차 번호를 부가하며, 이에 따라 상기 제3 TLP의 목적지 PEIC가 상기 제3 TLP에 있는 상기 송신지 PEIC 번호 및 상기 TLP 송신 순차 번호에 따라 제1 수신확인 메시지 TLP를 회신하는 단계

- [0086] 를 더 포함하며,

- [0087] 상기 회신된 제1 수신확인 메시지 TLP의 단대단 TLP 접두사는 상기 제3 TLP의 목적지 PEIC의 PEIC 번호 및 수신 확인된 TLP 송신 순차 번호를 수반하고 있으며,

- [0088] 상기 제3 TLP 내의 TLP 송신 순차 번호는 상기 제3 TLP의 송신지 PEIC에 의해 상기 제3 TLP의 목적지 PEIC에 송신된 TLP의 순차 번호이고, 상기 수신확인된 TLP 송신 순차 번호는 상기 송신지 PEIC로부터 제3 TLP의 목적지 PEIC에 의해 이미 수신된 TLP의 송신 순차 번호이다.

- [0089] 제4 관점의 제2 가능한 실행 방식과 결합해서, 제4 가능한 실행 방식에서,

- [0090] 상기 제3 TLP의 목적지 PEIC에 의해 회신되고 상기 PCIE 스위칭 유닛에 의해 포워딩된 제1 수신확인 메시지 TLP를 수신하는 단계 이전에,

- [0091] 상기 PCIE 스위칭 유닛에 의해 송신된 제4 TLP를 수신하고, 상기 제4 TLP의 유형에 따라, 상기 제4 TLP가 상기 제1 수신확인 메시지 TLP인지를 판단하고, 상기 제4 TLP가 상기 제1 수신확인 메시지 TLP가 아니면, 상기 수신된 제4 TLP를 상기 제4 TLP의 목적지 RC 또는 목적지 EP에 포워딩하는 단계

- [0092] 를 더 포함한다.

- [0093] 제4 관점의 제4 가능한 실행 방식과 결합해서, 제5 가능한 실행 방식에서,

- [0094] 상기 제4 TLP의 송신지 PEIC에 제2 수신확인 메시지 TLP를 회신하는 단계

- [0095] 를 더 포함한다.

- [0096] 제4 관점의 제3 내지 제5 가능한 실행 방식 중 어느 하나와 결합해서, 제6 가능한 실행 방식에서,

- [0097] 각각의 TLP 전송 큐의 TLP 송신 순차 번호 및 TLP 송신 링크를 유지하는 단계

- [0098] 를 더 포함한다.

- [0099] 제4 관점의 제3 내지 제6 가능한 실행 방식 중 어느 하나와 결합해서, 제7 가능한 실행 방식에서,

- [0100] 상기 제1 수신확인 메시지 TLP에 수반되어 있는 상기 송신지 PEIC 번호 및 수신확인된 송신 순차 번호 정보에 따라, 대응하는 TLP 전송 큐의 슬라이딩 윈도를 갱신하는 단계

- [0101] 를 더 포함한다.

- [0102] 제5 관점에서, 본 발명의 실시예는 주변 구성요소 상호접속 고속 스위칭 네트워크에서 패킷 전송을 위한 시스템을 제공하며, 상기 시스템은,

- [0103] 적어도 2개의 PCIE 노드 장치, 적어도 2개의 PCIE 인터페이스 제어기(PEIC), 및 2개의 PCIE 스위칭 유닛을 포함하며, 상기 적어도 2개의 PCIE 노드 장치 각각은 상기 적어도 2개의 PCIE 인터페이스 제어기 중 하나에 연결되어 있고, 상기 적어도 2개의 PCIE 인터페이스 제어기 각각은 상기 2개의 PCIE 스위칭 유닛에 각각 연결되어 있으며,

- [0104] 상기 적어도 2개의 PCIE 노드 장치 중 제1 PCIE 노드 장치는 상기 적어도 2개의 PCIE 인터페이스 제어기 중 제1 PCIE 인터페이스 제어기에 연결된 제1 TLP를 송신하도록 구성되어 있으며,

- [0105] 상기 제1 PCIE 인터페이스 제어기는 상기 제1 TLP를 수신하고, 상기 수신된 제1 TLP에 따라, 상기 2개의 PCIE 스위칭 유닛에 연결된 송신 링크를 결정하며, 상기 제1 TLP를 상기 송신 링크를 통해 상기 2개의 PCIE 스위칭 유닛에 동시에 송신하도록 구성되어 있으며,

- [0106] 상기 2개의 PCIE 스위칭 유닛 각각은 상기 제1 TLP를 상기 적어도 2개의 PCIE 인터페이스 제어기 중 제2 PCIE 인터페이스 제어기에 포워딩하도록 구성되어 있으며, 상기 제2 PCIE 인터페이스 제어기는 상기 제1 TLP의 목적지 PCIE 인터페이스 제어기이며,

- [0107] 상기 제2 PCIE 인터페이스 제어기는 상기 PCIE 스위칭 유닛에 의해 포워딩된 제1 TLP를 선택적으로 수신하고 상기 제1 TLP를 상기 적어도 2개의 PCIE 노드 장치 중 제2 PCIE 노드 장치에 송신하도록 구성되어 있으며, 상기 제2 PCIE 노드 장치는 상기 제1 TLP의 목적지 PCIE 노드 장치이며,

- [0108] 상기 제2 PCIE 노드 장치는 상기 제2 PCIE 인터페이스 제어기에 의해 포워딩된 상기 제1 TLP를 수신하도록 구성되어 있다.

- [0109] 제5 관점의 제1 가능한 실행 방식에서,

- [0110] 상기 제1 PCIE 인터페이스 제어기는, 상기 제1 TLP를 캡슐화하고, 상기 제1 TLP의 단대단 TLP 접두사에 송신지 PEIC 번호 및 TLP 송신 순차 번호를 부가하도록 추가로 구성되어 있으며,

- [0111] 상기 제2 PCIE 인터페이스 제어기는, 상기 제1 TLP에 있는 상기 송신지 PEIC 번호 및 상기 TLP 송신 순차 번호에 따라, 상기 PCIE 스위칭 유닛에 의해 포워딩된 상기 제1 TLP를 선택적으로 수신하도록 구성되어 있으며,

- [0112] 상기 TLP 송신 순차 번호는 상기 제1 PEIC에 의해 상기 제2 PEIC에 송신된 TLP의 순차 번호이고, 상기 제1 TLP에 있는 상기 송신지 PEIC 번호 및 상기 TLP 송신 순차 번호에 따라, 상기 제1 TLP를 선택적으로 수신하는 과정은, 동일한 송신지 PEIC 번호 및 동일한 TLP 송신 순차 번호를 가지는 제1 TLP에 있어서, 먼저 도착하는 제1 TLP만을 수신하는 과정이다.

- [0113] 제5 관점 또는 제5 관점의 제1 가능한 실행 방식에서, 제2 가능한 실행 방식에서,

- [0114] 상기 제1 PCIE 인터페이스 제어기는 상기 수신된 제1 TLP에 따라, 상기 2개의 PCIE 스위칭 유닛에 연결된 송신 링크를 결정하도록 구성되어 있으며, 이것은 구체적으로,

- [0115] 상기 제1 PCIE 인터페이스 제어기는 상기 제1 TLP에 따라 어드레스 포워딩 테이블 또는 ID 포워딩 테이블을 검색하고, 상기 제1 TLP에 대응하는 목적지 PEIC 번호를 결정하여, 상기 2개의 PCIE 스위칭 유닛에 연결되어 있고 상기 제1 TLP에 대응하는 송신 링크를 결정하도록 구성되어 있다.

- [0116] 제5 관점 또는 제5 관점의 제1 또는 제2 가능한 실행 방식과 결합해서, 제3 가능한 실행 방식에서,

- [0117] 상기 PCIE 노드 장치는 루트 복합(RC) 또는 종점 장치(EP)이고, 각각의 PCIE 인터페이스 제어기는 하나의 RC 또는 적어도 하나의 EP에 연결되어 있다.

- [0118] 제6 관점에서, 본 발명의 실시예는 주변 구성요소 상호접속 고속 스위칭 네트워크에서 패킷 전송을 위한 시스템을 제공하며, 상기 시스템은,

- [0119] 적어도 2개의 PCIE 노드 장치, 적어도 2개의 PCIE 인터페이스 제어기(PEIC), 및 2개의 PCIE 스위칭 유닛을 포함하며, 상기 적어도 2개의 PCIE 노드 장치 각각은 상기 적어도 2개의 PCIE 인터페이스 제어기 중 하나에 연결되어 있고, 상기 적어도 2개의 PCIE 인터페이스 제어기 각각은 상기 2개의 PCIE 스위칭 유닛에 각각 연결되어 있으며,

- [0120] 상기 적어도 2개의 PCIE 노드 장치 중 제3 PCIE 노드 장치는 상기 적어도 2개의 PCIE 인터페이스 제어기 중 제3 PCIE 인터페이스 제어기에 연결된 제3 TLP를 송신하도록 구성되어 있으며,

- [0121] 상기 제3 PCIE 인터페이스 제어기는 상기 제3 TLP를 수신하고, 상기 수신된 제3 TLP에 따라, 상기 2개의 PCIE 스위칭 유닛 중 하나에 연결된 송신 링크를 결정하고, 상기 제3 TLP를 상기 송신 링크를 통해 상기 PCIE 스위칭 유닛에 송신하며, 상기 적어도 2개의 PCIE 인터페이스 제어기 중 제4 PCIE 인터페이스 제어기에 의해 회신되고 상기 PCIE 스위칭 유닛에 의해 포워딩된 제1 수신확인 메시지 TLP가 시간이 종료될 때까지도 수신되지 않으면, 상기 PCIE 스위칭 유닛에 연결된 송신 링크를 통해 상기 제4 PCIE 인터페이스 제어기에 상기 제3 TLP를 다시 송신하도록 구성되어 있으며, 상기 제4 PCIE 인터페이스 제어기는 상기 제3 TLP의 목적지 PCIE 인터페이스 제어기이며,

- [0122] 상기 PCIE 스위칭 유닛은 상기 제3 TLP를 상기 제4 PCIE 인터페이스 제어기에 포워딩하며, 상기 제4 PCIE 인터페이스 제어기에 의해 회신된 상기 제1 수신확인 메시지 TLP를 상기 제3 PCIE 인터페이스 제어기에 포워딩하도록 구성되어 있으며,

- [0123] 상기 제4 PCIE 인터페이스 제어기는 상기 PCIE 스위칭 유닛에 의해 포워딩된 제3 TLP를 선택적으로 수신하고 상기 제3 TLP를 상기 적어도 2개의 PCIE 노드 장치 중 제4 PCIE 노드 장치에 송신하며, 상기 제2 PCIE 노드 장치는 상기 제3 TLP의 목적지 PCIE 노드 장치이며; 상기 제1 수신확인 메시지 TLP를 상기 제3 PCIE 인터페이스 제어기에 회신하여, 상기 제3 TLP가 수신된 것을 확인하도록 구성되어 있으며,

- [0124] 상기 제4 PCIE 노드 장치는 상기 제4 PCIE 인터페이스 제어기에 의해 포워딩된 상기 제3 TLP를 수신하도록 구성되어 있다.

- [0125] 제6 관점의 제1 가능한 실행 방식에서, 상기 제3 PEIC는 상기 제4 PEIC에 의해 회신되고 상기 PCIE 스위칭 유닛에 의해 포워딩된 상기 제1 수신확인 메시지 TLP를 수신하며, 상기 제1 수신확인 메시지 TLP에 수반되어 있는 TLP 송신 순차 번호 정보 및 송신지 PEIC 번호에 따라 상기 수신확인된 제3 TLP를 삭제하도록 추가로 구성되어 있다.

- [0126] 제6 관점 또는 제6 관점의 제1 가능한 실행 방식과 결합해서, 제2 가능한 실행 방식에서,

- [0127] 상기 제3 PCIE는 상기 TLP를 캡슐화하고, 상기 제3 TLP의 단대단 TLP 접두사에 송신지 PEIC 번호(SPEIC) 및 TLP 송신 순차 번호를 부가하며, 상기 캡슐화된 제3 TLP를 상기 송신 링크를 통해 상기 PCIE 스위칭 유닛에 송신하도록 추가로 구성되어 있으며,

- [0128] 상기 제4 PCIE는 상기 제3 TLP에 수반되어 있는 상기 송신지 PEIC 번호 및 상기 TLP 송신 순차 번호에 따라 상기 제1 수신확인 메시지 TLP를 회신하도록 구성되어 있으며,

- [0129] 상기 회신된 제1 수신확인 메시지 TLP의 단대단 TLP 접두사는 상기 송신지 PEIC 번호 및 수신확인된 TLP 송신 순차 번호를 수반하고 있으며, 상기 TLP 송신 순차 번호는 상기 제3 PEIC에 의해 상기 제4 PEIC에 송신된 TLP의 순차 번호이고, 상기 수신확인된 TLP 송신 순차 번호는 상기 제3 PEIC로부터 상기 제4 PEIC에 의해 이미 수신된 TLP의 송신 순차 번호이다.

- [0130] 제6 관점의 제2 가능한 실행 방식과 결합해서, 제3 가능한 실행 방식에서,

- [0131] 상기 제3 PEIC는 다른 PEIC에 대한 TLP 송신 순차 번호 및 TLP 송신 링크를 유지하도록 추가로 구성되어 있다.

- [0132] 제6 관점 또는 제6 관점의 제1 내지 제3 가능한 실행 방식과 결합해서, 제4 가능한 실행 방식에서,

- [0133] 각각의 PCIE 인터페이스 제어기는 고정-시간 겹출 TLP를 시간 간격으로 모든 다른 PEIC에 송신하고, 회신된 겹출 송신 TLP가 지정된 시간 내에 수신되지 않은 PEIC에 대응하는 송신 링크를 개선하도록 추가로 구성되어 있다.

- [0134] 제6 관점 또는 제6 관점의 제1 내지 제4 가능한 실행 방식 중 어느 하나와 결합해서, 제5 가능한 실행 방식에서,

- [0135] 상기 PCIE 노드 장치는 루트 복합(RC) 또는 종점 장치(EP)이고, 각각의 PCIE 인터페이스 제어기는 하나의 RC 또는 적어도 하나의 EP에 연결되어 있다.

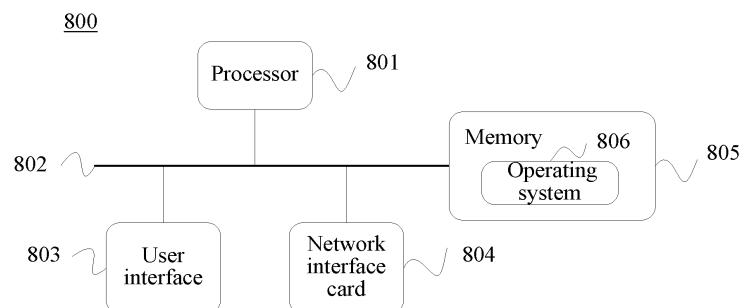

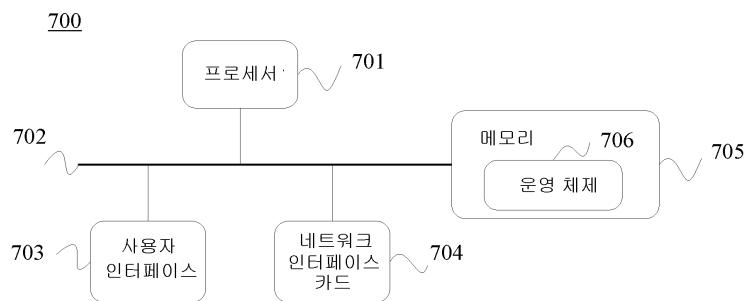

- [0136] 제7 관점에서, 본 발명의 실시예는 주변 구성요소 상호접속 고속 인터페이스 제어기(PEIC)를 더 제공하며, 상기 주변 구성요소 상호접속 고속 인터페이스 제어기는, 프로세서 및 메모리를 포함하고, 상기 메모리는 실행 명령

을 저장하며; 상기 주변 구성요소 상호접속 고속 인터페이스 제어기(PEIC)가 실행되면, 상기 프로세서는 상기 메모리와 통신하고, 상기 프로세서는 상기 실행 명령을 실행하며, 이에 따라 주변 구성요소 상호접속 고속 인터페이스 제어기(PEIC)는 전술한 제3 관점에서의 방법을 실행한다.

[0137] 제8 관점에서, 본 발명의 실시예는 주변 구성요소 상호접속 고속 인터페이스 제어기(PEIC)를 더 제공하며, 상기 주변 구성요소 상호접속 고속 인터페이스 제어기는 프로세서 및 메모리를 포함하고, 상기 메모리는 실행 명령을 저장하며; 상기 주변 구성요소 상호접속 고속 인터페이스 제어기(PEIC)가 실행되면, 상기 프로세서는 상기 메모리와 통신하고, 상기 프로세서는 상기 실행 명령을 실행하며, 이에 따라 주변 구성요소 상호접속 고속 인터페이스 제어기(PEIC)는 전술한 제4 관점에서의 방법을 실행한다.

[0138] 제9 관점에서, 본 발명의 실시예는 컴퓨터 관독 가능형 매체를 더 제공하며, 상기 매체는 컴퓨터 실행 명령을 포함하며, 상기 컴퓨터 실행 명령은 주변 구성요소 상호접속 고속 인터페이스 제어기(PEIC)가 전술한 제3 관점에서의 방법을 실행할 수 있게 하는 데 사용된다.

[0139] 제10 관점에서, 본 발명의 실시예는 컴퓨터 관독 가능형 매체를 더 제공하며, 상기 매체는 컴퓨터 실행 명령을 포함하며, 상기 컴퓨터 실행 명령은 주변 구성요소 상호접속 고속 인터페이스 제어기(PEIC)가 전술한 제3 관점에서의 방법을 실행할 수 있게 하는 데 사용된다.

### 발명의 효과

[0140] 전술한 솔루션을 통해, 본 발명의 실시예에서 제공하는 PCIE 스위칭 네트워크에서 패킷 전송을 실행하기 위한 방법, 장치, 시스템, 및 저장 매체에서는, 제1 TLP가 활성 및 대기 PCIE 스위칭 유닛에 연결된 송신 링크를 통해 활성 및 대기 PCIE 스위칭 유닛에 동시에 송신되고, 제1 TLP의 목적지 PEIC는 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 제1 TLP를 선택적으로 수신하고 제1 TLP의 목적지 EP 또는 목적지 RC에 제1 TLP를 송신하며; 대안으로, 제3 TLP가 PCIE 스위칭 유닛에 연결된 송신 링크를 통해 PCIE 스위칭 유닛에 송신되고, PCIE 스위칭 유닛은 그 수신된 제3 TLP를 목적지 PEIC에 송신하며, 목적지 PEIC는 제3 TLP를 제3 TLP의 목적지 EP 또는 목적지 RC에 포워딩하고 제1 수신확인 메시지 TLP를 송신지 PEIC에 회신한다. 시간이 종료될 때 목적지 PEIC에 의해 회신된 제1 수신확인 메시지 TLP를 수신하면, 송신지 PEIC는 PCIE 스위칭 유닛에 연결된 송신 링크를 통해 제3 TLP를 다시 송신하고, 이에 의해 PCIE 스위칭 이중-평면 네트워킹 접속의 경우 TLP의 신뢰할 수 있는 단대단(end-to-end) 전송이 실행되고, PCIE 스위칭을 사용하는 시스템의 신뢰도가 향상된다.

### 도면의 간단한 설명

[0141] 본 발명의 실시예의 기술적 솔루션을 더 명확하게 설명하기 위해, 이하에서는 본 발명의 실시예를 설명하는 데 필요한 첨부된 도면에 대해 간략하게 설명한다. 당연히, 이하의 실시예의 첨부된 도면은 본 발명의 일부의 실시예에 지나지 않으며, 당업자라면 창조적 노력 없이 첨부된 도면에 따라 다른 도면을 도출해낼 수 있을 것이다.

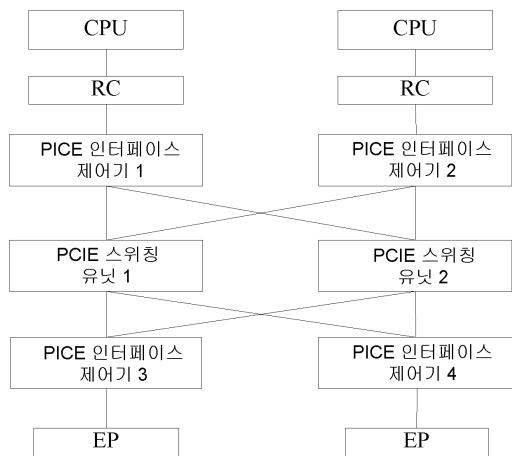

도 1은 종래기술의 PCIE 스위칭 어플리케이션의 시스템 개략도이다.

도 2는 현재의 PCIE 사양에서의 트리 네트워크의 네트워크 구조도이다.

도 3은 본 발명의 실시예에 따른 PCIE 네트워크의 네트워크 구조도이다.

도 4는 본 발명의 실시예 1에 따른 PCIE 인터페이스 제어기의 구조도이다.

도 5는 본 발명의 실시예 2에 따른 PCIE 인터페이스 제어기의 구조도이다.

도 6은 본 발명의 실시예에 따른 TLP의 어드레스 포워딩 테이블이다.

도 7은 본 발명의 실시예에 따른 TLP의 ID 포워딩 테이블이다.

도 8은 본 발명의 실시예에 따른 TLP 전송 큐(queue)와 PCIE 인터페이스 제어기 간의 접속 관계도이다.

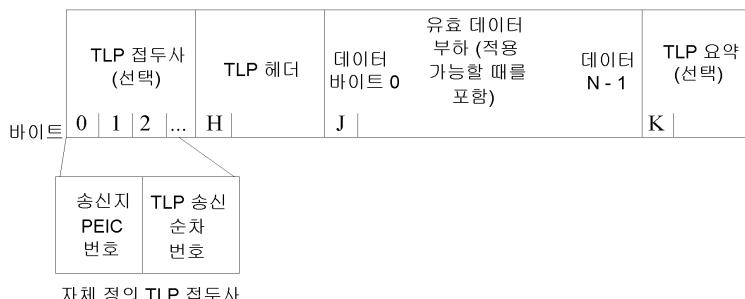

도 9는 본 발명의 실시예에 따른 TLP 포맷의 도면이다.

도 10은 본 발명의 실시예 3에 따른 PCIE 인터페이스 제어기의 구조도이다.

도 11은 본 발명의 실시예 4에 따른 PCIE 인터페이스 제어기의 구조도이다.

도 12는 본 발명의 실시예 5에 따른 PCIE 인터페이스 제어기의 구조도이다.

도 13은 본 발명의 실시예에 따른 TLP 전송 큐의 슬라이딩 윈도의 개략도이다.

도 14는 본 발명의 실시예 6에 따른 PCIE 인터페이스 제어기의 구조도이다.

도 15는 본 발명의 실시예 7에 따른 PCIE 스위칭 네트워크에서 패킷 전송을 위한 방법에 대한 흐름도이다.

도 16은 본 발명의 실시예 8에 따른 PCIE 스위칭 네트워크에서 패킷 전송을 위한 방법에 대한 흐름도이다.

도 17은 본 발명의 실시예 9에 따른 PCIE 스위칭 네트워크에서 패킷 전송을 위한 방법에 대한 흐름도이다.

도 18은 본 발명의 실시예 10에 따른 PCIE 스위칭 네트워크에서 패킷 전송을 위한 방법에 대한 흐름도이다.

도 19는 본 발명의 실시예 11에 따른 PCIE 스위칭 네트워크에서 패킷 전송을 위한 시스템에 대한 흐름도이다.

도 20은 본 발명의 실시예 12에 따른 PCIE 스위칭 네트워크에서 패킷 전송을 위한 시스템에 대한 흐름도이다.

도 21은 본 발명의 실시예 13에 따른 PCIE 인터페이스 제어기의 개략도이다.

도 22는 본 발명의 실시예 14에 따른 PCIE 인터페이스 제어기의 개략도이다.

### 발명을 실시하기 위한 구체적인 내용

[0142] 이하에서는 본 발명의 실시예에 첨부된 도면을 참조하여 본 발명의 실시예의 기술적 솔루션에 대해 명확하게 완전하게 설명한다. 당연히, 설명될 실시예는 본 발명의 모든 실시예가 아닌 일부에 지나지 않는다. 당업자가 창조적 노력 없이 본 발명의 실시예에 기초하여 획득하는 모든 다른 실시예는 본 발명의 보호 범위 내에 있게 된다.

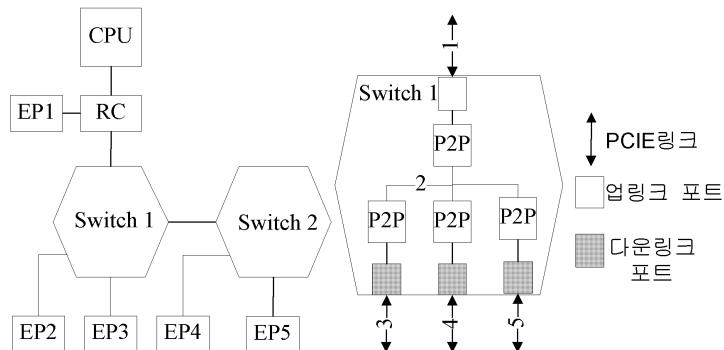

[0143] 도 2는 현재의 PCIE 사양에서의 트리 네트워크의 구조도이다. 도면에 도시된 바와 같이, 왼쪽 부분은 PCIE 애플리케이션 접속에 대한 개략도이고 루트 복합(root complex: RC)으로부터 종단 장치(endpoint device: EP)까지 트리 네트워크가 형성된다. RC는 EP에 직접 연결되거나 하나 이상의 스위치에 연결될 수 있다. PCIE는 점대점(point-to-point) 통신 모드를 사용하며, 각각의 RC와 각각의 EP/스위치 간에는 단지 하나의 경로만이 존재 한다. 오른쪽 부분은 PCIE 스위치의 내부 개략도이다. 각각의 PCIE 스위치에는 고유한 업링크 포트 및 수 개의 다운링크 포트가 있다. 스위치의 각각의 포트에는 내부 가상 PCI 대 PCI(PCI TO PCI: P2P로 약칭함) 브리지가 있다. PCIE 사양에 정의되어 있는 점대점 통신 모드 및 트리 스위치 구조로 인해, 이중 평면 네트워킹은 지원되지 않는다.

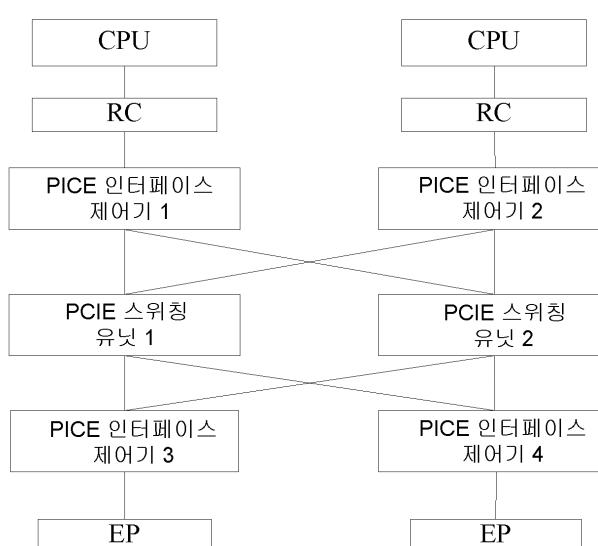

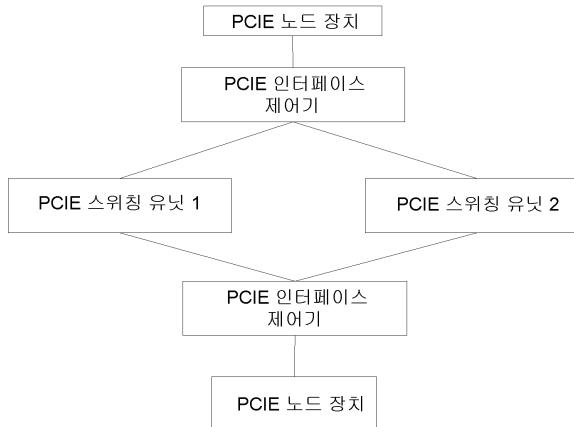

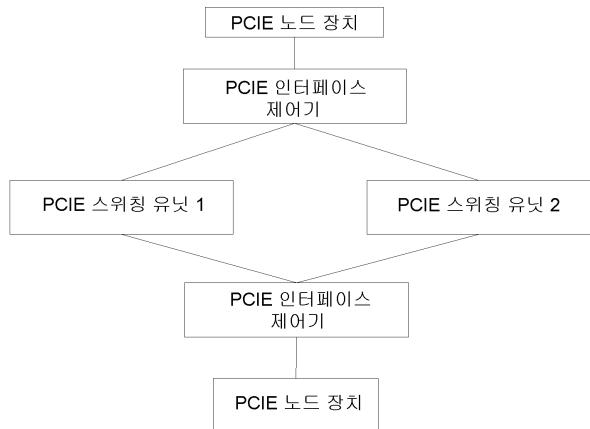

[0144] 도 3은 본 발명의 실시예에 적용되는 PCIE 네트워크의 구조도이다. 도 3에 도시된 바와 같이, RC/EP와 PCIE 스위칭 유닛 간에 PCIE 인터페이스 제어기(PCIE Interface Controller: PEIC로 약칭)가 부가된다. PEIC는 내부적으로는 RC/EP에 연결되어 있고, 외부적으로는 활성 및 대기 PCIE 스위칭 유닛에 연결되어 있으며, 이에 의해 이중 평면 네트워킹, 및 실패 겸출과 스위칭과 같은 기능을 실행한다. PCIE 스위칭 유닛은 PCIE 사양에 기초한 스위칭 유닛이고, PEIC들 간에 데이터 교환을 완료한다. 활성 평면 및 대기 평면이 구성되어 있다. 도 3에서의 PCIE 스위칭 유닛 1 및 PCIE 스위칭 유닛 2는 PCIE 스위칭의 활성 평면 및 대기 평면을 각각 나타낸다. EP는 PCIE 사양에 정의된 표준 기능 장치로서, 이더넷 카드, FC 네트워크 카드, 인피니밴드(InfiniBand: IB로 약칭) 네트워크 카드, 및 저렴한 디스크의 리던던트 어레이(Redundant Array of Inexpensive Disk: RAID로 약칭) 카드를 들 수 있다. PEIC, EP, RC 및 PCIE 스위칭 유닛은 PCIE 사양에 기초하여 데이터 교환을 수행한다.

[0145] 도 3의 네트워크 구조로부터, PCIE 인터페이스 제어기(PEIC)는 RC/EP와 PCIE 스위칭 유닛 간에 부가된 구성요소임을 알 수 있다. 본 발명과 PCIE 사양에 정의된 트리 구조의 가장 큰 차이점이 PEIC이며, PCIE 스위칭에 기초한 이중 평면 네트워킹은 PEIC를 통해 수행된다.

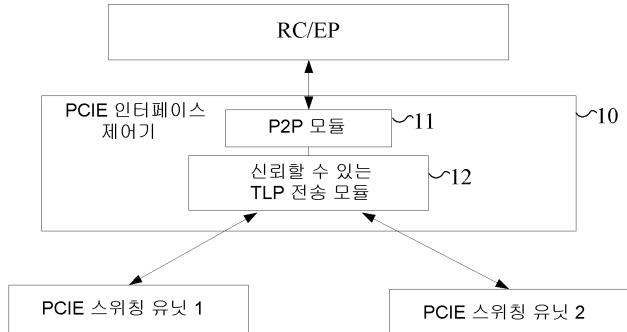

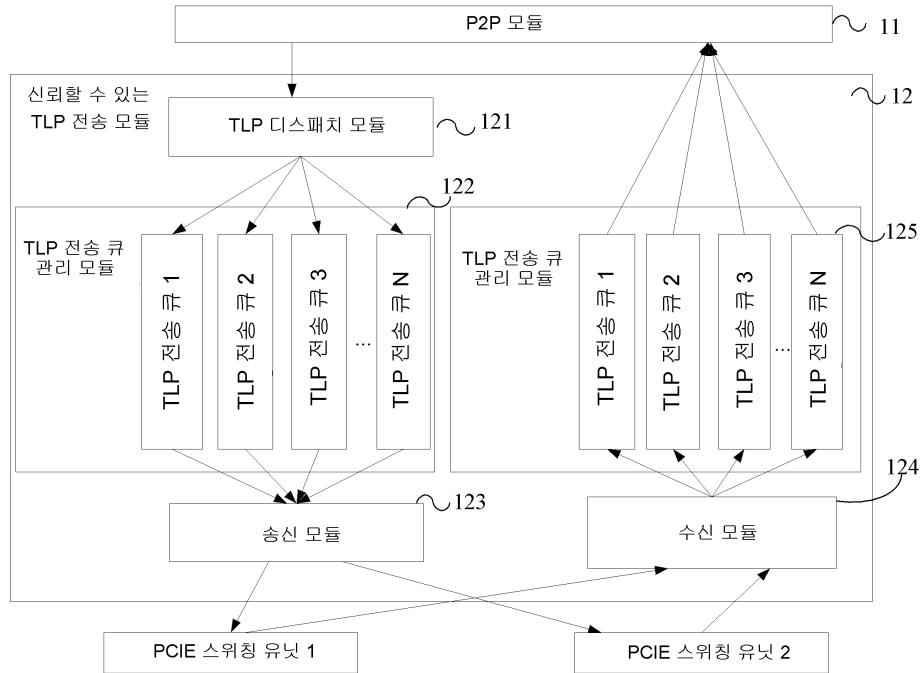

[0146] 본 발명의 실시예 1에 제공된 PEIC의 구조가 도 4에 도시되어 있으며, 하나의 P2P 브리지 모듈 및 하나의 TLP 전송(Reliable TLP Transmission: RTT로 약칭) 모듈을 포함한다. P2P 브리지는 PCIE 사양에 정의되어 있는 표준 점대점 브리지이고, PCIE의 링크 계층 프로토콜과 전송 계층 프로토콜을 실행한다. RC/EP와 PEIC 간의 링크는 표준 PCIE 링크이다. RTT 모듈은 주로 활성 및 대기 PCIE 스위칭 유닛에 대한 링크의 선택 및 PEIC로부터 임의의 다른 PEIC까지의 TLP의 신뢰할 수 있는 단대단 전송을 완료한다. PCIE 사양의 관점에서 보면, RTT 모듈은 투명한 모듈이다. RC/EP에서 보면, PEIC는 실제로 PCIE 트리 구조에서 P2P 브리지이고, RTT, PEIC 및 PCIE 스위칭 유닛을 통해 가상의 P2P가 연결되어 있는데, 즉, RC/EP는 활성 및 대기 PCIE 스위칭 유닛이 아닌 도 2에 도시된 표준 PCIE 스위치를 본다.

[0147] 도 4에 도시된 바와 같이, PCIE 인터페이스 제어기(10)는 PCI 대 PCI 브리지 모듈(P2P 모듈)(11) 및 신뢰할 수

있는 TLP 전송 모듈(RTT 모듈)(12)을 포함한다.

[0148] P2P 모듈(11)은 RC 또는 EP로부터 제1 TLP를 수신하고, 이 제1 TLP를 프로세싱을 위한 신뢰할 수 있는 TLP 전송 모듈(RTT 모듈)에 포워딩하도록 구성되어 있다.

[0149] RTT 모듈(12)은 그 수신된 제1 TLP에 따라, 활성 및 대기 PCIE 스위칭 유닛에 연결된 송신 링크를 결정하고, 제1 TLP를 송신 링크를 통해 활성 및 대기 PCIE 스위칭 유닛에 동시에 송신하도록 구성되어 있고, 이에 따라 제1 TLP의 목적지 PCIE 인터페이스 제어기는 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 제1 TLP를 선택적으로 수신하고 제1 TLP의 목적지 EP 또는 목적지 RC에 제1 TLP를 송신한다.

[0150] 바람직하게, RTT 모듈(12)은, P2P 모듈(11)에 의해 포워딩된 제1 TLP를 수신한 후, TLP의 유형에 따라, 즉 패킷이 어드레스를 통해 루팅되는지 또는 식별(Identity: ID로 약칭)을 통해 루팅되는지에 따라, 대응하는 어드레스 포워딩 테이블 또는 ID 포워딩 테이블을 검색하고, 제1 TLP에 대응하는 목적지 PEIC 번호를 획득하여, 패킷에 대응하는 활성 및 대기 PCIE 스위칭 유닛의 송신 링크를 결정하며, 제1 TLP를 송신 링크를 통해 활성 및 대기 PCIE 스위칭 유닛에 동시에 송신하도록 구성되어 있다. 이 경우, 활성 및 대기 PCIE 스위칭 유닛은 수신된 제1 TLP를 목적지 PEIC에 송신하고, 목적지 PEIC는 대응하는 패킷을 선택적으로 수신하고, 예를 들어, 이전에 도착한 제1 TLP를 수신하고 나중에 도착하는 제1 TLP를 폐기하며; 그 수신된 제1 TLP를 제1 TLP의 목적지 EP 또는 목적지 RC에 포워딩한다.

[0151] 또한, RTT 모듈(12)은 제1 TLP를 캡슐화하고, 자체 정의(self-defined) TLP 접두사(Prefix)를 부가하며, 캡슐화된 제1 TLP를 송신 링크를 통해 활성 및 대기 PCIE 스위칭 유닛에 송신하도록 구성되어 있다. TLP의 포맷에 대한 정의가 도 9에 도시되어 있다: PCIE 사양에서의 정의에 따르면, TLP는 0 또는 복수의 표준 또는 자체 지정 TLP 접두사를 포함할 수 있다. TLP 접두사는 단대단 확장 및 점대점 확장의 파라미터 전달을 실행하고, 기능 확장을 실행할 수 있다. TLP Prefix는 또한 로컬 및 단대단 TLP Prefix로 분류된다. TLP 헤더는 TLP의 표준 헤더 부분이고, Data Payload는 TLP의 데이터 부분이고, TLP Digest는 TLP의 요약 부분이며; 이 3 부분이 PCIE 사양의 표준 내용이다. 바람직하게, 실시예에서, 송신지 PEIC로부터 목적지 PEIC까지의 송신지 PEIC 번호(SPEIC) 및 TLP 송신 순차 번호(SEQUENCE)의 전달은 송신지 PEIC 번호(SPEIC) 및 TLP 송신 순차 번호(SEQUENCE)가 부가되어 있는 자체 정의 단대단 TLP Prefix를 사용하여 실행된다. SEQUENCE는 송신지 PEIC에 의해 목적지 PEIC에 송신된 TLP의 순차 번호이고, 이에 따라 목적지 PEIC는 SPEIC 및 SEQUENCE에 따라 그 수신된 TLP를 순서를 정하여 수신확인하며, 이에 의해 활성 및 대기 PCIE 스위칭 유닛에 의해 전달되는 제1 TLP의 수신을 선택적으로 실행한다. RTT 모듈(12)은 제1 TLP를 2개의 링크를 통해 활성 및 대기 PCIE 스위칭 유닛에 송신하고; 패킷이 송신된 후, 목적지 PEIC에 대응하는 TLP 송신 순차 번호(SEQUENCE)가 1 증가한다. 목적지 PEIC는 활성 및 대기 링크를 통해 먼저 수신된 제1 TLP를 선택하고, 그 먼저 수신된 제1 TLP를 목적지 EP 또는 목적지 RC에 송신하며, 나중에 수신된 제1 TLP를 폐기하는데, 즉 동일한 SPEIC 및 동일한 SEQUENCE를 가지는 TLP에 있어서, 먼저 도착하는 TLP만을 수신한다. 제1 TLP를 수신한 후, 목적지 PEIC는 제1 TLP를 제1 TLP의 목적지 EP 또는 목적지 RC에 송신하고, 이에 의해 TLP의 전송을 신뢰할 수 있게 순차적으로 완료한다.

[0152] 본 발명의 실시예에서 제공하는 PCIE 인터페이스 제어기에서, 제1 TLP는 활성 및 대기 PCIE 스위칭 유닛에 연결된 송신 링크를 통해 활성 및 대기 PCIE 스위칭 유닛에 동시에 송신되고, 제1 TLP의 목적지 PEIC는 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 제1 TLP를 선택적으로 수신하고 제1 TLP의 목적지 EP 또는 목적지 RC에 제1 TLP를 송신하며, 이에 의해 PCIE 이중 평면 네트워킹 접속의 경우에 TLP의 신뢰할 수 있는 전송을 수행하고, PCIE 스위칭을 사용하는 시스템의 신뢰성을 높인다.

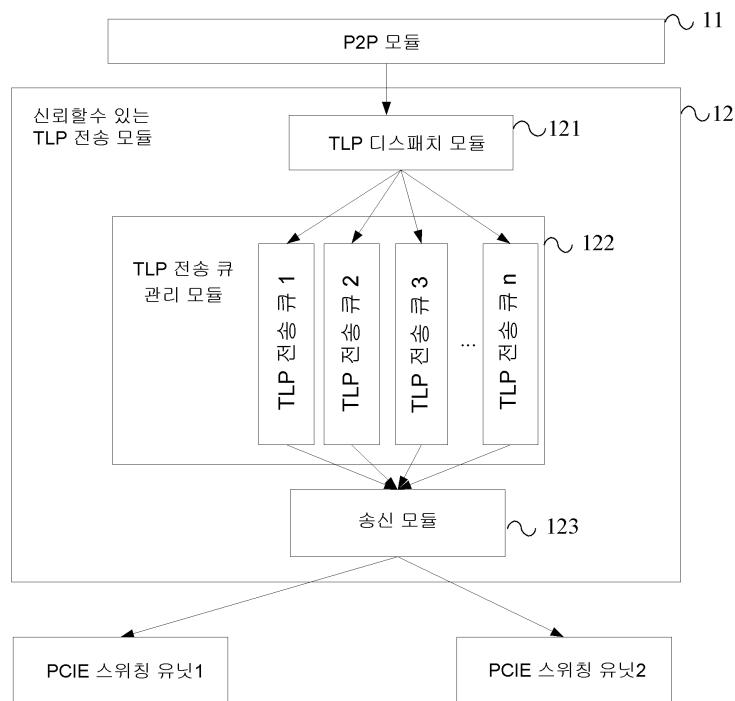

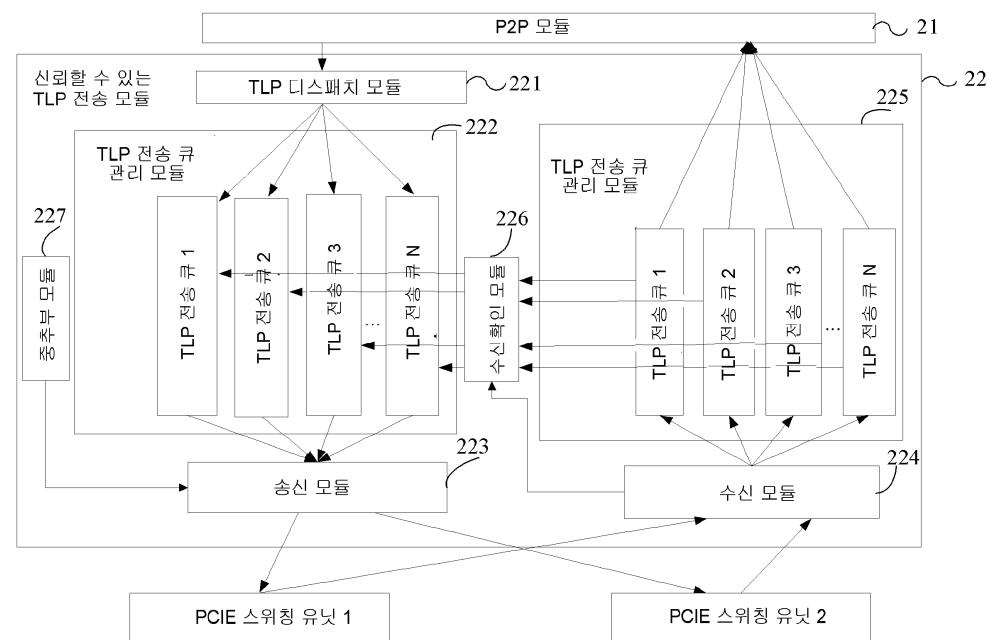

[0153] 도 5는 본 발명의 실시예 2에 따른 PCIE 인터페이스 제어기의 구조도이다. 도 4에 도시된 PCIE 인터페이스 제어기와 마찬가지로, 본 실시예에서의 PCIE 인터페이스 제어기(PEIC)(10)도 PCI 대 PCI 브리지 모듈(P2P 모듈)(11) 및 신뢰할 수 있는 TLP 전송 모듈(RTT 모듈)(12)을 포함한다.

[0154] P2P 모듈(11)은 RC 또는 EP로부터 제1 TLP를 수신하고, 이 제1 TLP를 프로세싱을 위한 신뢰할 수 있는 TLP 전송 모듈(RTT 모듈)에 포워딩하도록 구성되어 있다.

[0155] 도면에 도시된 바와 같이, RTT 모듈(12)은, 수신된 제1 TLP에 따라 어드레스 포워딩 테이블 또는 ID 포워딩 테이블을 검색하고, TLP 전송 큐(TLP transmission queue: TTQ)를 결정하며, 제1 TLP를 TLP 전송 큐에 놓도록 구성되어 있고, 상기 TLP 전송 큐는 제1 TLP의 목적지 PEIC에 대응하는, TLP 디스패치 모듈(Dispatch Module: DPT로 약칭)(121); 및 TLP 전송 큐 내의 제1 TLP를 TLP 전송 큐의 송신 링크를 통해 활성 및 대기 PCIE 스위칭 유닛에 동시에 송신하도록 구성되어 있고, 이에 따라 제1 TLP의 목적지 PCIE 인터페이스 제어기가 활성 및 대기

PCIE 스위칭 유닛에 의해 포워딩된 제1 TLP를 선택적으로 수신하고 제1 TLP의 목적지 EP 또는 목적지 RC에 제1 TLP를 송신하도록 구성되어 있는, 송신 모듈(Send Module: SND로 약칭)(123)을 포함한다.

[0156] 바람직하게, TLP 디스패치 모듈(121)은 P2P 모듈(11)에 의해 포워딩된 제1 TLP를 수신하고, TLP의 루팅 방식(어드레스 루팅 또는 ID 루팅)에 따라, 대응하는 어드레스 포워딩 테이블 또는 ID 포워딩 테이블을 검색하며, 테이블 검색 결과에 따라 목적지 PEIC 번호를 획득하도록 구성되어 있다.

[0157] 어드레스 포워딩 테이블은 도 6에 도시될 수 있으며, I/O 공간 또는 메모리 공간의 어드레스 범위에 대응하는 목적지 PCIE 인터페이스 제어기 번호가 테이블에 구성되어 있다. ID 포워딩 테이블은 도 7에 도시된 포맷을 사용할 수 있으며, 장치 ID에 대응하는 목적지 PCIE 인터페이스 제어기 번호가 테이블에 구성되어 있으며, 장치 ID는 TLP에 포함되어 있는 버스(Bus), 장치(Device), 또는 기능(Function)의 ID일 수 있다. 일반적으로, 어드레스를 통해 루팅된 TLP(예를 들어, I/O 공간 또는 메모리 공간의 읽기 및 쓰기 패킷)에 있어서는, 연산 어드레스를 사용하여 어드레스 포워딩 엔트리를 검색하고, 연산 어드레스가 어드레스 포워딩 테이블 내의 특정한 테이블 엔트리에 맞으면, 그 패킷을 테이블 엔트리의 목적지 PEIC 번호에 따라 대응하는 TTQ에 버퍼링한다. ID를 통해 루팅된 TLP, 예를 들어, 읽기/쓰기 요구 구성 패킷은 요청자 ID 및 액세스 목적지 ID를 포함하며, 그 대응하는 응신 패킷에 있어서는, 원래의 요청 패킷 내의 요청자 ID를 사용하여 어드레스 포워딩 테이블을 검색한다. 특정한 테이블 엔트리가 맞으면, 테이블 내의 목적지 PEIC 번호에 따라 대응하는 TTQ에 TLP를 버퍼링한다. 어드레스 포워딩 테이블 및 ID 포워딩 테이블은 RTT 모듈에 직접 구성될 수 있고, PCIE 인터페이스 제어기의 다른 모듈에 구성되어 대응하는 모듈로부터 RTT에 의해 획득될 수도 있다.

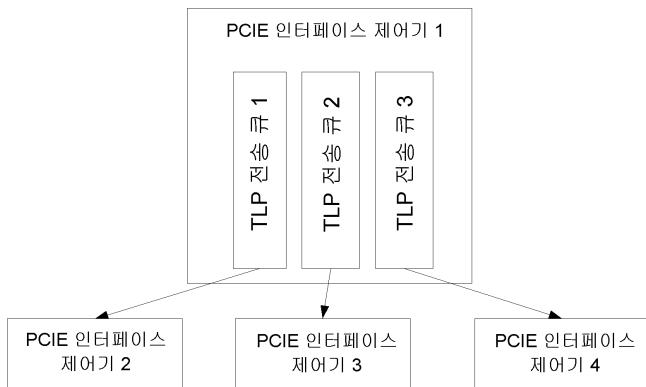

[0158] 도 5에 도시된 바와 같이, RTT 모듈(12)은 복수의 TLP 전송 큐, 예를 들어, 도면에서 TLP 전송 큐 1 내지 TLP 전송 큐 n을 더 포함하며, 각각의 TLP 전송 큐(TTQ)는 목적지 PEIC에 대응한다. 예를 들어, 도 8에 도시된 바와 같이, PCIE 인터페이스 전송 1의 3개의 전송 큐: TLP 전송 큐 1/a, TLP 전송 큐 2/a, TLP 전송 큐 3은 3개의 목적지 PEIC: PCIE 인터페이스 제어기 2/a, PCIE 인터페이스 제어기 3/a, PCIE 인터페이스 제어기 4에 각각 대응한다. 예를 들어, PCIE 인터페이스 제어기 1이 PCIE 인터페이스 제어기 2에 송신된 TLP를 수신하면, PCIE 인터페이스 제어기 1은 대응 관계에 따라 TLP를 TLP 전송 큐 1에 버퍼링한다. 장치의 변경에 따라 TTQ와 PEIC 간의 대응 관계에 대해 동적 부가 또는 동적 삭제가 수행될 수 있다. 예를 들어, 새로운 PEIC 장치가 네트워크에 부가되면, 대응하는 TTQ가 부가되어야 한다. 또한, 각각의 TTQ는 송신지 PEIC로부터 목적지 PEIC까지의 TLP 송신 순차 번호(SEQUENCE) 및 TLP 송신 링크를 저장하는데, 여기서 PEIC의 TLP 송신 순차 번호란 목적지 PEIC에 송신된 TLP의 순차 번호를 말한다. TTQ의 PEIC의 TLP 송신 순차 번호는 TLP 전송 큐(TTQ)가 TLP를 송신할 때마다 1씩 증가한다. TLP 송신 링크란 큐가 TLP를 목적지 PEIC에 송신하는 통신 링크를 말한다. 구체적으로, TTQ는 TLP 송신 링크를 유지하고 관련 정보를 저장할 수 있다.

[0159] 또한, RTT 모듈(12)은, 각각의 TLP 전송 큐의 TLP 송신 순차 번호 및 TLP 송신 링크를 유지 및 관리하도록 구성되어 있는 TLP 전송 큐 관리 모듈(122)을 포함한다.

[0160] 바람직하게, 송신 모듈(123)은 TLP 전송 큐(TTQ) 내의 제1 TLP를 스케줄링하고, TLP를 캡슐화하고, 자체 정의 TLP 접두사(Prefix)를 부가하며, 캡슐화된 제1 TLP를 TTQ의 송신 링크를 통해 활성 및 대기 PCIE 스위칭 유닛에 동시에 송신한다. TLP의 포맷에 대한 정의는 도 9에 도시된 바와 같다: PCIE 사양에서의 정의에 따르면, TLP는 0 또는 복수의 표준 또는 자체 정의 TLP 접두사를 포함할 수 있다. TLP Prefix는 단대단 확장 및 점대점 확장의 파라미터 전달을 실행하고, 기능 확장을 실행할 수 있다. TLP Prefix는 또한 로컬 및 단대단 TLP Prefix로 분류된다. TLP 헤더는 TLP의 표준 헤더 부분이고, Data Payload는 TLP의 데이터 부분이고, TLP Digest는 TLP의 요약 부분이며; 이 3 부분이 PCIE 사양의 표준 내용이다. 바람직하게, 실시예에서, 송신지 PEIC로부터 목적지 PEIC까지의 송신지 PEIC 번호(SPEIC) 및 TLP 송신 순차 번호(SEQUENCE)의 전달은 송신지 PEIC 번호(SPEIC) 및 TLP 송신 순차 번호(SEQUENCE)가 부가되어 있는 자체 정의 단대단 TLP Prefix를 사용하여 실행된다. SEQUENCE는 송신지 PEIC에 의해 목적지 PEIC에 송신된 TLP의 순차 번호이고, 즉 TLP 전송 큐에 대응하는 목적지 PEIC에 송신된 TLP의 순차 번호이며, 각각의 TTQ에서 독립적으로 순서가 정해져 있으며, 이에 따라 목적지 PEIC는 SPEIC 및 SEQUENCE에 따라 그 수신된 TLP를 순서를 정하여 수신확인하며, 이에 의해 활성 및 대기 PCIE 스위칭 유닛에 의해 전달되는 제1 TLP의 수신을 선택적으로 실행한다. 송신 모듈은 제1 TLP를 2개의 링크를 통해 활성 및 대기 PCIE 스위칭 유닛에 송신하고; 패킷이 송신된 후, TTQ의 TLP 송신 순차 번호(SEQUENCE)가 1 증가 한다. 목적지 PEIC는 활성 및 대기 링크를 통해 먼저 수신된 제1 TLP를 선택하고, 그 먼저 수신된 제1 TLP를 목적지 EP 또는 목적지 RC에 송신하며, 나중에 수신된 제1 TLP를 폐기하는데, 즉 동일한 SPEIC 및 동일한 SEQUENCE를 가지는 TLP에 있어서, 먼저 도착하는 TLP만을 수신한다. 제1 TLP를 수신한 후, 목적지 PEIC는 제1 TLP를 제1 TLP의 목적지 EP 또는 목적지 RC에 송신하고, 이에 의해 TLP의 전송을 신뢰할 수 있게 순차적으로 완

료한다.

[0161] 또한, P2P 모듈(11)은, 제1 TLP를 프로세싱을 위한 신뢰할 수 있는 TLP 전송(RTT) 모듈에 포워딩하기 전에, 그 수신된 TLP의 유형, 및 패킷 내의 목적지 장치 ID 또는 액세스 목적지 어드레스에 따라, 제1 TLP를 프로세싱을 위한 신뢰할 수 있는 TLP 전송(RTT) 모듈에 포워딩해야 하는지를 판단하도록 구성되어 있다. P2P 모듈은 그 수신된 패킷의 유형(어드레스 루팅 또는 ID 루팅)에 따라, 대응하는 어드레스 포워딩 테이블 또는 ID 포워딩 테이블을 검색한다. 어드레스 포워딩 테이블 또는 ID 포워딩 테이블에 목적지 PEIC가 구성되어 있으면, 제1 TLP를 프로세싱을 위한 신뢰할 수 있는 TLP 전송(RTT) 모듈에 포워딩해야 하는 것을 나타내며, 제1 TLP를 프로세싱을 위한 RTT에 포워딩한다. 바람직하게, 로컬 어드레스 또는 로컬 ID를 가지는 TLP를, 프로세싱을 위한 RTT에 포워딩할 필요 없이 RC 또는 EP에 직접 회신할 수 있다.

[0162] 본 발명의 실시예에서 제공하는 PCIE 인터페이스 제어기에서는, TLP 전송 큐가 TLP의 목적지 PEIC에 따라 결정되고, TLP는 대응하는 TLP 전송 큐의 송신 링크를 통해 활성 및 대기 PCIE 스위칭 유닛에 동시에 송신되고, 활성 및 대기 PCIE 스위칭 유닛은 제1 TLP의 목적지 PEIC에 제1 TLP를 포워딩하며, 목적지 PEIC는 제1 TLP의 자체 정의 단대단 TLP 접두사에 수반되어 있는 송신지 PEIC 번호 및 TLP 송신 순차 번호에 따라 제1 TLP를 선택적으로 수신하고, 먼저 수신된 제1 TLP를 목적지 EP 또는 목적지 RC에 송신하며, 나중에 수신된 제1 TLP는 폐기하며, 이에 의해 TLP의 신뢰할 수 있는 전송을 완료하고, PCIE 이중 평면 네트워킹의 경우 신뢰성 있는 전송을 실행하며, PCIE 스위칭을 사용하는 시스템의 신뢰성을 높인다.

[0163] 도 10은 본 발명의 실시예 3에 따른 PCIE 인터페이스 제어기의 구조도이다. 도 5에 도시된 실시예 2에서의 PCIE 인터페이스 제어기에 기초해서, 본 발명의 실시예에서의 신뢰할 수 있는 전송 모듈(RTT 모듈)(12)은:

[0164] 활성 및 대기 PCIE 스위칭 유닛에 의해 송신된 제2 TLP를 선택적으로 수신하고, 수신된 제2 TLP를 P2P 모듈에 송신하도록 구성되어 있고, 이에 따라 P2P 모듈이 제2 TLP의 목적지 RC/EP에 상기 제2 TLP를 포워딩하는, 수신 모듈(124)

[0165] 을 더 포함한다.

[0166] 바람직하게, PEIC를 TLP의 수신단(목적지 PEIC)으로서 사용하면, 수신 모듈(124)은 활성 및 대기 PCIE 스위칭 유닛에 의해 송신된 제2 TLP의 자체 정의 단대단 TLP 접두사에 수반되어 있는 SPEIC 및 SEQUENCE에 따라 TLP를 선택적으로 수신할 수 있고, 즉 2개의 링크를 통해 연속으로 수신되고 동일한 SPEIC 및 동일한 SEQUENCE를 가지는 제2 TLP에 있어서, 먼저 수신된 제2 TLP만이 선택되어 P2P 모듈을 통해 제2 TLP의 목적지 RC/EP에 송신되고, 나중에 수신된 제2 TLP는 폐기된다.

[0167] 바람직하게, 도 10에 도시된 바와 같이, RTT 모듈(12)은 복수의 TLP 수신확인 순차(TLP Acknowledge Sequence: TAS)를 더 포함할 수 있다. 각각의 TLP 수신확인 순차(TAS)는 피어 PEIC(패킷의 송신지 PEIC)에 대응하는데, 즉 TLP 전송 큐에 대응하고, 이 TLP 전송 큐를 통해 피어 PEIC는 패킷을 로컬 단에 송신한다. 즉, PEIC에 연결된 각각의 PEIC는 TAS에 대응하는 TLP 전송 큐를 가진다. TTQ는 송신을 위해 사용되고, TAS는 수신을 위해 사용된다. 각각의 TAS는 예상 순차 번호를 가지는데, 이 예상 순차 번호는 대응하는 피어 PEIC(패킷의 송신지 PEIC)로부터 수신될 다음 TLP에 의해 실려야 하는 SEQUENCE를 나타낸다. 예를 들어, TLP 인터페이스 제어기 1의 TLP 수신확인 순차 1이 TLP 인터페이스 제어기 2의 TLP 전송 큐 1에 대응하면, PEIC 1의 TAS 1은, 송신지 단 PEIC 2로부터 수신될 것으로 예상되는 TLP에 실려 있으면서 PEIC 2의 TTQ 1을 통해 송신된 SEQUENCE를 기록한다. 예를 들어, PEIC 1의 TAS 1의 예상 순차 번호가 3이면, 이것은 PEIC 1이 송신지 단 PEIC 2로부터 수신할 예정인 다음 TLP의 SEQUENCE가 3이어야 한다는 것을 의미한다. TTQ의 변경에 따라 TAS와 TTQ 간의 대응 관계에 대해 동적 부가 또는 삭제가 수행될 수 있다. 예를 들어, 새로운 PEIC 장치가 네트워크에 부가되면, 대응하는 TTQ가 부가되어야 하고, TAS 역시 부가되어야 한다. 바람직하게, 수신 모듈(124)은 제2 TLP를 수신하고, 제1 TLP 내의 자체 정의 Prefix의 SPEIC에 따라 대응하는 TAS를 결정하고, 제2 TLP의 SEQUENCE와 TAS의 예상 순차 번호를 비교하며, 제2 TLP의 SEQUENCE가 TAS의 예상 순차 번호와 같으면 제2 TLP를 P2P 모듈에 송신하며, 이에 따라 P2P 모듈은 제2 TLP를 목적지 RC/EP에 포워딩하고 TAS의 예상 순차 번호를 1 증가시키고; 제2 TLP의 SEQUENCE가 TAS의 예상 순차 번호와 같지 않으면 TLP를 폐기하며, 이에 의해 동일한 SPEIC 및 동일한 SEQUENCE를 가지는 TLP에 있어서, 하나의 TLP만이 수신되고, 패킷이 순차적으로 하나씩 수신되게 함으로써, 이 중 평면에서의 신뢰할 수 있는 수신을 실행한다.

[0168] 또한, RTT 모듈(12)은 각각의 수신확인 순차의 예상 순차 번호를 유지 및 관리하도록 구성되어 있는 TLP 수신확인 순차 관리 모듈(125)을 포함한다.

[0169] 본 발명의 실시예에서 제공하는 PCIE 인터페이스 제어기에서는, 활성 및 대기 PCIE 스위칭 유닛에 의해 송신된 제2 TLP가 선택적으로 수신된다. 먼저 수신된 제2 TLP만이 선택되어 P2P 모듈을 통해 제2 TLP의 목적지 RC/EP에 송신되고, 나중에 수신된 제2 TLP는 폐기되며, 이에 의해 TLP의 이중 공급 및 선택적 수신 전송을 신뢰할 수 있게 순차적으로 완료하고, PCIE 이중 평면 네트워킹을 실행하며, PCIE 스위칭을 사용하는 시스템의 신뢰성을 높인다.

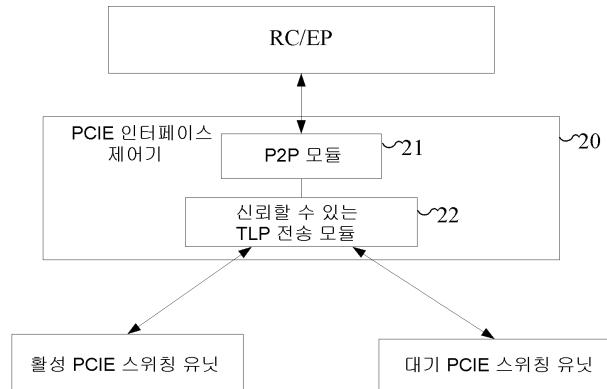

[0170] 도 11은 본 발명의 실시예 4에 따른 PCIE 인터페이스 제어기의 구조도이다. 실시예 1 내지 실시예 3과 마찬가지로, 본 실시예에서의 PCIE 인터페이스 제어기는 P2P 브리지 모듈 및 TLP 전송(Reliable TLP Transmission: RTT로 약칭) 모듈을 포함한다. P2P 브리지는 PCIE 사양에 정의되어 있는 표준 점대점 브리지이고, PCIE의 링크 계층 프로토콜과 전송 계층 프로토콜을 실행한다. RC/EP와 PEIC 간의 링크는 표준 PCIE 링크이다. RTT 모듈은 주로 활성 및 대기 PCIE 스위칭 유닛에 대한 링크의 선택 및 PEIC로부터 임의의 다른 PEIC까지의 TLP의 신뢰할 수 있는 단대단 전송을 완료한다. PCIE 사양의 관점에서 보면, RTT 모듈은 투명한 모듈이다. RC/EP에서 보면, PEIC는 실제로 PCIE 트리 구조에서 P2P 브리지이고, RTT, PEIC 및 PCIE 스위칭 유닛을 통해 가상의 P2P가 연결되어 있는데, 즉, RC/EP는 활성 및 대기 PCIE 스위칭 유닛이 아닌 도 2에 도시된 표준 PCIE 스위치를 본다.

[0171] 도 11에 도시된 바와 같이, PCIE 인터페이스 제어기(20)는 PCI 대 PCI 브리지 모듈(P2P 모듈)(21) 및 신뢰할 수 있는 TLP 전송 모듈(RTT 모듈)(22)을 포함한다.

[0172] PCI 대 PCI 브리지 모듈(P2P 모듈)(21)은 RC 또는 EP로부터 제3 TLP를 수신하고, 이 제3 TLP를 프로세싱을 위한 신뢰할 수 있는 TLP 전송 모듈(RTT 모듈)에 포워딩하도록 구성되어 있다.

[0173] 신뢰할 수 있는 TLP 전송 모듈(RTT 모듈)(22)은 그 수신된 제3 TLP에 따라, PCIE 스위칭 유닛에 연결된 송신 링크를 결정하고, 제3 TLP를 송신 링크를 통해 PCIE 스위칭 유닛에 동시에 송신하도록 구성되어 있고, 이에 따라 제3 TLP의 목적지 PCIE 인터페이스 제어기는 PCIE 스위칭 유닛에 의해 포워딩된 제3 TLP를 수신하고 제3 TLP의 목적지 EP 또는 목적지 RC에 제3 TLP를 송신하며; 제3 TLP의 목적지 PEIC에 의해 회신되고 상기 PCIE 스위칭 유닛에 의해 포워딩된 제1 수신확인 메시지 TLP가 시간이 종료될 때까지도 수신되지 않으면, PCIE 스위칭 유닛에 연결된 송신 링크를 통해 제3 TLP를 다시 송신한다.

[0174] 바람직하게, RTT 모듈(22)은, P2P 모듈(21)에 의해 포워딩된 제3 TLP를 수신한 후, TLP의 유형에 따라, 즉 패킷이 어드레스를 통해 루팅되는지 또는 식별(Identity: ID로 약칭)을 통해 루팅되는지에 따라, 대응하는 어드레스 포워딩 테이블 또는 ID 포워딩 테이블을 검색하고, 제3 TLP에 대응하는 목적지 PEIC 번호를 획득하여, 패킷에 대응하는 PCIE 스위칭 유닛의 송신 링크를 결정하며, 제3 TLP를 송신 링크를 통해 PCIE 스위칭 유닛에 송신하도록 구성되어 있다. 이 경우, PCIE 스위칭 유닛은 수신된 제3 TLP를 목적지 PEIC에 송신하고, 이에 따라 목적지 PEIC는 제3 TLP를 수신하고 이 제3 TLP의 목적지 EP 또는 목적지 RC에 제3 TLP를 포워딩한다. 한편, 목적지 PEIC는 제3 TLP에 대한 제1 수신확인 메시지 TLP를 회신하고, 제1 수신확인 메시지 TLP가 PCIE 스위칭 유닛을 통해 RTT 모듈(22)에 포워딩되어, 제3 TLP가 수신되었다는 것을 나타낸다. RTT 모듈(22)은 목적지 PEIC에 의해 회신된 제1 수신확인 메시지 TLP가 시간이 종료될 때까지도 수신되지 않으면, PCIE 스위칭 유닛에 연결된 송신 링크를 통해 제3 TLP를 다시 송신한다(이중 평면의 경우에, 이 경우의 PCIE 스위칭 유닛에 연결된 송신 링크는 제3 TLP가 이전에 송신된 송신 링크와 다를 수 있다).

[0175] 또한, RTT 모듈(22)은 제3 TLP를 캡슐화하고, 제3 TLP의 자체 정의 단대단 TLP 접두사에 송신지 PEIC 번호 및 TLP 송신 순차 번호를 부가하며, 캡슐화된 제3 TLP를 송신 링크를 통해 PCIE 스위칭 유닛에 송신하며, 이에 따라 수신된 제3 TLP에 있는 송신지 PEIC 번호 및 TLP 송신 순차 번호에 따라, 제3 TLP의 목적지 PEIC는 제1 수신확인 메시지 TLP를 회신한다. 회신된 제1 수신확인 메시지 TLP의 자체 정의 단대단 TLP 접두사는 제3 TLP의 목적지 PEIC의 PEIC 번호 및 수신확인된 TLP 송신 순차 번호를 수반하고 있으며, 여기서 제3 TLP의 목적지 PEIC의 PEIC 번호는 제3 TLP의 송신지 PEIC에 의해 제3 TLP의 목적지 PEIC에 송신된 TLP의 순차 번호이고, 제1 수신확인 메시지 TLP의 수신확인된 TLP 송신 순차 번호는 송신지 PEIC의 TLP 송신 순차 번호이고 제3 TLP의 목적지 PEIC에 의해 이미 수신된 제3 TLP를 지니는 TLP 송신 순차 번호이다.

[0176] 현재의 PCIE 사양에서는, 점대점 수신확인 메커니즘을 통해 TLP의 신뢰할 수 있는 전송이 실행되고 있다. 예를 들어, 도 2에서, 스위치 1은 스위치 2에 TLP를 송신하는데, 스위치 1은 TLP를 저장하고, 스위치 2가 정확한 TLP를 수신하고 스위치 1에 수신확인 정보를 회신할 때까지 그 대응하는 TLP를 삭제하지 않는다. 그렇지만, RC에 의해 스위치 2에 송신되는 TLP에 있어서, 스위치 1과 스위치 2 간의 링크가 실패하면, RC에 의해 스위치 1에 이미 성공적으로 송신된 패킷은 스위치 1과 스위치 2 간의 링크의 실패로 인해 폐기될 수도 있다. 그렇지만, RC는 스위치 1로부터 수신확인 정보를 수신하기 때문에 RC는 패킷이 성공적으로 송신된 것으로 간주한다. 이러한

실패는 RC가 TLP의 전송 결과를 정확하게 감지할 수 없게 만들어 버리며, 이에 의해 시스템은 비정상으로 작동하거나 데이터 연산이 폐기되어 버린다. 본 발명의 실시예에서 제공하는 PCIE 인터페이스 제어기(PEIC)에서는, PCIE 스위칭 유닛에 연결된 송신 링크를 통해 제3 TLP가 PCIE 스위칭 유닛에 송신되고, PCIE 스위칭 유닛은 수신된 제3 TLP를 목적지 PEIC에 송신하며, 목적지 PEIC는 제3 TLP의 목적지 EP 또는 목적지 RC에 제3 TLP를 송신하고, 제1 수신확인 메시지 TLP를 송신지 PEIC에 회신한다. 목적지 PEIC에 의해 회신된 제1 수신확인 메시지 TLP가 시간이 종료될 때까지도 수신되지 않으면, 송신지 PEIC는 PCIE 스위칭 유닛에 연결된 송신 링크를 통해 제3 TLP를 다시 송신하며, 이에 의해 PCIE 스위칭 이중 평면 네트워킹 접속의 경우 TLP의 신뢰할 수 있는 단대단 전송을 실행하고, PCIE 스위칭을 사용하는 시스템의 신뢰성이 높아진다.

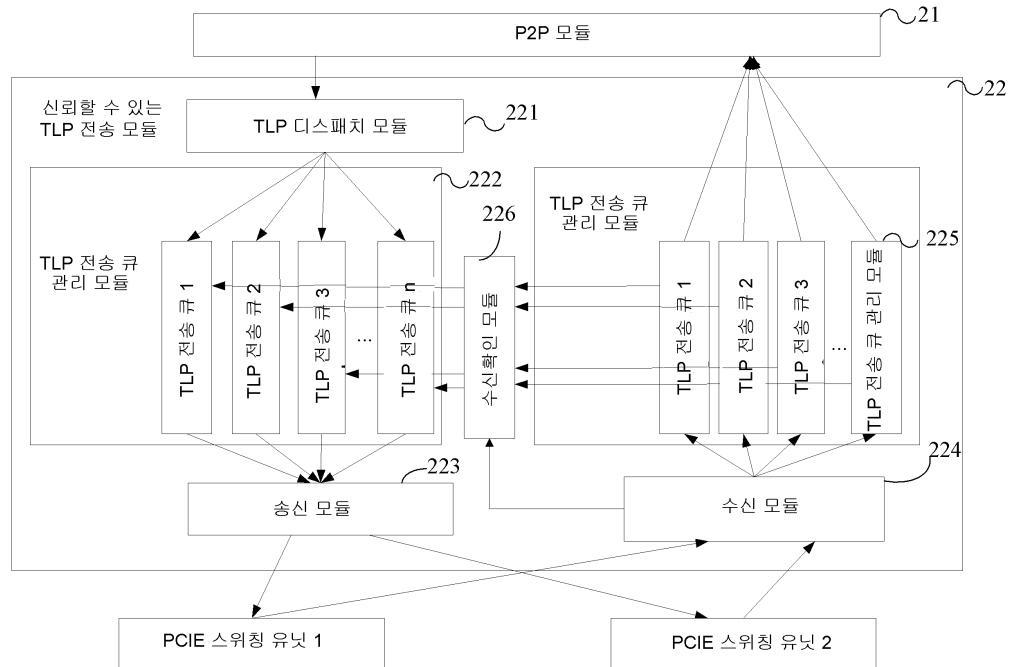

[0177] 도 12는 본 발명의 실시예 5에 따른 PCIE 인터페이스 제어기의 구조도이다. 도면에 도시된 바와 같이, 신뢰할 수 있는 TLP 전송(RTT) 모듈(22)은:

[0178] 수신된 제3 TLP에 따라 어드레스 포워딩 테이블 또는 ID 포워딩 테이블을 검색하고, TLP 전송 큐(TTQ)를 결정하며, 제3 TLP를 TLP 전송 큐에 놓도록 구성되어 있고, TLP 전송 큐는 제3 TLP의 목적지 PEIC에 대응하는, TLP 디스패치 모듈(221);

[0179] TLP 전송 큐(TTQ)를 스케줄링하고, 제3 TLP를 TLP 전송 큐의 송신 링크를 통해 PCIE 스위칭 유닛에 송신하도록 구성되어 있고, 이에 따라 제3 TLP의 목적지 PCIE 인터페이스 제어기가 PCIE 스위칭 유닛에 의해 포워딩된 제3 TLP를 수신하고 제3 TLP의 목적지 EP 또는 목적지 RC에 제3 TLP를 송신하며; 제3 TLP의 목적지 PEIC에 의해 회신되고 PCIE 스위칭 유닛에 의해 포워딩된 제1 수신확인 메시지 TLP가 시간이 종료될 때까지도 수신되지 않으면, PCIE 스위칭 유닛에 연결된 송신 링크를 통해 제3 TLP를 다시 송신하도록 구성되어 있는 송신 모듈(223);

[0180] 제3 TLP의 목적지 PEIC에 의해 회신되고 상기 PCIE 스위칭 유닛에 의해 포워딩된 제1 수신확인(ACK) 메시지 TLP를 수신하고, 제1 수신확인 메시지 TLP를 수신확인 모듈(226)에 전달하도록 구성되어 있는 수신 모듈(224);

[0181] 제1 수신확인 메시지 TLP에 수반되어 있는 TLP 송신 순차 번호(SEQUENCE) 및 송신지 PEIC 번호(SPEIC)에 따라, TLP 전송 큐 내의 수신확인된 제3 TLP를 삭제한다는 것을 TLP 전송 큐 관리 모듈(222)에 통지하도록 구성되어 있는 상기 수신확인 모듈(226); 및

[0182] 상기 수신확인 모듈(226)의 통지에 따라 TLP 전송 큐 내의 수신확인된 제3 TLP를 삭제하도록 구성되어 있는 상기 TLP 전송 큐 관리 모듈(222)

[0183] 을 더 포함한다.

[0184] 바람직하게, TLP 디스패치 모듈(221)은 P2P 모듈(21)에 의해 포워딩된 TLP를 수신하고, TLP의 루팅 방식(어드레스 루팅 또는 ID 루팅)에 따라, 대응하는 어드레스 포워딩 테이블 또는 ID 포워딩 테이블을 검색하고, 테이블 검색 결과에 따라 목적지 PEIC를 획득하며, 수신된 제3 TLP를 대응하는 TTQ에 버퍼링하도록 구성되어 있다. 어드레스 포워딩 테이블은 도 6에 도시될 수 있으며; ID 포워딩 테이블은 도 7에 도시된 포맷을 사용할 수 있다. 특정한 내용 및 구성 방법은 전술한 실시예 2 및 실시예 3에서의 설명에서의 내용 및 구성 방법과 동일하므로, 여기서 반복 설명하지 않는다.

[0185] 도 12에 도시된 바와 같이, RTT 모듈(22)은 복수의 TLP 전송 큐를 더 포함한다. 본 실시예에서의 TLP 전송 큐의 기능 및 구조는 도 5에 도시된 실시예 2에서의 TLP 전송 큐의 기능 및 구조와 동일하다. 특정한 설명에 대해서는 관련 부분을 참조하면 되므로, 상세한 설명에 대해서는 여기서 반복 설명하지 않는다.

[0186] 바람직하게, 송신 모듈(223)은 TLP 전송 큐(TTQ) 내의 TLP를 스케줄링하고, 자체 정의 TLP 접두사(Prefix)를 부가하며, 캡슐화된 제3 TLP를 TTQ의 송신 링크를 통해 PCIE 스위칭 유닛에 송신한다. TLP의 포맷에 대한 정의가 도 9에 도시되어 있다: 특정한 구조에 대한 관련 정의에 대해서는, 전술한 실시예 2 및 실시예 3의 도 9에서의 TLP의 포맷에 관한 설명을 참조하면 되므로, 상세한 설명에 대해서는 여기서 반복 설명하지 않는다. 바람직하게, 본 실시예에서는, 송신지 PEIC로부터 목적지 PEIC까지의 송신지 PEIC 번호(SPEIC) 및 TLP 송신 순차 번호(SEQUENCE)의 전달은 TLP 내의 자체 정의 단대단 TLP Prefix를 사용하여 실행된다. SEQUENCE는 송신지 PEIC에 의해 목적지 PEIC에 송신된 TLP의 순차 번호이고, 즉 TLP 전송 큐에 대응하는 목적지 PEIC에 송신된 TLP의 순차 번호이고, 각각의 TTQ에서 독립적으로 순서가 정해져 있으며, 이에 따라 목적지 PEIC는 SPEIC + SEQUENCE에 따라 그 수신된 TLP를 순서를 정하여 수신확인한다. 회신된 제1 수신확인 메시지 TLP의 단대단 TLP 접두사는 송신지 PEIC 번호 및 수신확인된 TLP 송신 순차 번호를 수반하고 있으며, 여기서 수신확인 메시지 패킷 내의 SEQUENCE 필드는 수신확인된 TLP 송신 순차 번호를 수반하고 있고, 수신확인된 TLP 송신 순차

번호는 목적지 PEIC에 의해 송신지 PEIC로부터 이미 수신된 TLP의 송신 순차 번호를 나타낸다. 송신 모듈은 TTQ의 송신 링크를 통해 PCIE 스위칭 유닛에 제3 TLP를 송신한다. 패킷이 송신된 후, TTQ의 TLP 송신 순차 번호(SEQUENCE)가 1 증가한다.

[0187] 또한, TLP 전송 큐 관리 모듈(222)은 각각의 전송 큐의 TLP 송신 순차 번호 및 TLP 송신 링크를 유지하도록 구성되어 있다. TLP 전송 큐 관리 모듈은 각각의 전송 큐의 TLP 송신 순차 번호 및 TLP 송신 링크를 유지하도록 구성되어 있고, 각각의 전송 큐의 TLP 송신 순차 번호는 TTQ에 의해 이미 송신된 TLP의 송신 순차 번호를 나타내고, TLP 송신 링크는 TTQ의 활성 및 대기 송신 링크를 나타내며, 이에 따라 활성 송신 링크는 TLP를 송신하는 데 사용된다.

[0188] 바람직하게, TTQ는 TLP을 송신하는데 슬라이딩 윈도를 사용할 수 있으며, 이에 의해 각각의 TTQ에 의해 동시에 송신된 패킷의 수를 제한한다. TTQ의 슬라이딩 윈도 메커니즘은 도 13에 도시되어 있다. 도면에서 숫자가 붙은 각각의 박스는 TLP를 나타낸다. 예를 들어, 슬라이딩 윈도의 크기 4인데, 즉 목적지 PEIC에 의해 수신확인되지 않은 TLP 가 최대 4개까지 공존할 수 있다. 목적지 PEIC에 의해 회신된 TLP 수신확인 패킷을 수신한 후, 수신확인 모듈(226)은 수신확인된 SEQUENCE에 따라 윈도를 전진 이동시킨다. 예를 들어, 현재의 윈도에서 수신확인될 TLP가 2, 3, 4 및 5이고; 수신 모듈에 의해 포워딩된 그 수신된 상기 수신확인된 SEQUENCE가 2이면, 슬라이딩 윈도가 하나의 패킷만큼 전진 이동하고, 수신확인될 TLP가 3, 4, 및 5이며; TTQ는 순차 번호가 6인 TLP를 송신하도록 허용된다. PEIC의 버퍼 성능에 따르면, 슬라이딩 윈도의 크기는 2 내지 n에 설정될 수 있다(n은 임의의 양의 정수). 슬라이딩 윈도를 설정함으로써, 각각의 TTQ에 의해 동시에 송신된 패킷의 수를 효과적으로 제어할 수 있고, 프로세싱 효율성이 향상되며, 동시에 송신 및 수신이 순차적으로 신뢰할 수 있게 수행된다.

[0189] 바람직하게, 제3 TLP의 목적지 PEIC는 제3 TLP를 수신하고, 제3 패킷 내의 송신지 PEIC 번호(SPEIC)에 따라 송신지 PEIC에 수신확인 TLP를 회신한다. 당연히, 목적지 PEIC 역시 송신지 PEIC로부터 복수의 TLP를 수신한다음 수신확인 TLP를 송신지 PEIC에 송신할 수 있다. 예를 들어, 순차 번호가 3, 4, 및 5이고 SPEIC가 101인 패킷이 수신되면, 순차 번호가 5인 수신확인 TLP만이 송신될 수 있고, 이것은 순차 번호가 5인 패킷 이전의 모든 TLP가 수신된다는 것을 의미하고, 이에 의해 수신확인 TLP의 횟수가 감소된다. 바람직하게, 수신확인 TLP는 ID 루팅을 사용할 수 있고, 목적지 장치 ID는 송신지 PEIC의 P2P 모듈의 장치 ID이다. 수신확인 TLP의 자체 정의 TLP Prefix는 송신지 PEIC 번호(SPEIC) 및 수신확인된 TLP 송신 순차 번호(SEQUENCE)를 포함하며, 여기서 수신확인된 TLP 송신 순차 번호(SEQUENCE)는 송신지 PEIC에 의해 수신된 최신의 TLP 송신 순차 번호이다(이것은 일반적으로 가장 큰데, 순차 번호가 주기적인 방식으로 사용될 때는 가장 큰 순차 번호가 아닐 수도 있다). 수신확인 TLP를 수신한 후, 수신 모듈은 수신확인 TLP를 수신확인 모듈(226)에 포워딩하고, 수신확인 모듈(226)은, 패킷 내의 수신확인된 TLP 송신 순차 번호 및 SPEIC에 따라, 큐 내의 제3 TLP를 삭제하였다는 것을 TTQ에 통지 한다. 송신지 PEIC의 TLP 전송 큐 관리 모듈은, 제1 수신확인 메시지 패킷의 수신확인된 순차 번호에 따라, 대응하는 TTQ에 버퍼링되어 있는 TLP를 삭제한다. PEIC로부터 PCIE 스위칭 유닛까지의 링크가 실패하거나 PCIE 스위칭 유닛이 실패하면, TLP는 폐기되며, 이에 대응해서 송신지 PEIC는, 이 경우 제3 TLP를 위해 목적지 PEIC에 의해 회신되는 제1 수신확인 메시지 TLP를 수신할 수 없다. 송신지 단 PEIC 시간이 종료되면, TTQ에 버퍼링되어 있는 제3 TLP가 PCIE 스위칭 유닛에 연결된 송신 링크를 통해 다시 송신되며; 이 경우, 실패된 링크 또는 실패된 PCIE 스위칭 유닛이 복구될 수 있거나, PEIC의 이중 평면이 스위칭되며, 이에 따라 송신지 PEIC의 송신 모듈(223)은 PCIE 스위칭 유닛에 연결된 송신 링크를 통해 제3 TLP를 다시 송신하며, 이에 의해 송신지 PEIC에 의해 송신되는 모든 TLP를 신뢰할 수 있게 목적지 PEIC에 송신할 수 있다.

[0190] 바람직하게, 수신확인 모듈(226)은, 제1 수신확인 메시지 TLP에 수반되어 있는 수신확인된 TLP 송신 순차 번호(SEQUENCE) 정보 및 송신지 PEIC 번호(SPEIC)에 따라, 대응하는 TTQ의 슬라이딩 윈도를 개선하도록 추가로 구성되어 있다.

[0191] 바람직하게, 도 12에 도시된 바와 같이, RTT 모듈(22)은 복수의 TLP 수신확인 순차(TAS)를 더 포함할 수 있다. 본 실시예에서의 TLP 수신확인 순차의 구조 및 설정은 도 10에 도시된 실시예 3에서의 TLP 수신확인 순차의 구조 및 설정과 동일하다. 동일한 방식으로, 각각의 TLP 수신확인 순차(TAS)는 하나의 전송 큐에 대응한다. 특정한 구조 및 설정에 대해서는, 도 10에 도시된 실시예 3에서의 관련 설명을 참조하면 되므로, 상세한 설명에 대해서는 여기서 반복 설명하지 않는다.

[0192] 수신 모듈(224)은 PCIE 스위칭 유닛에 의해 송신된 제4 TLP를 수신하고, TLP의 유형에 따라, 제4 TLP가 수신확인 메시지 TLP인지를 판정하며; 제4 TLP가 수신확인 메시지 TLP이면, 제4 TLP를 수신확인 모듈(226)에 포워딩하고; 제4 TLP가 수신확인 메시지 TLP가 아니면, 그 수신된 제4 TLP를 제4 TLP의 송신지 PEIC에 대응하는 TLP 수

신확인 순차(TAS)에 버퍼링한다.

[0193] 이 경우, P2P 모듈(21)은 TLP 수신확인 순차(TAS) 내의 제4 TLP를 획득하고, 제4 TLP의 목적지 RC/EP에 제4 TLP를 포워딩하도록 구성되어 있다.

[0194] RTT 모듈(22)은, TLP 수신확인 순차가 제4 TLP를 수신한 후, 수신확인 메시지 TLP를 송신지 PEIC에 회신하였다는 것을 수신확인 모듈(226)에 통지하도록 구성되어 있는 TLP 수신확인 순차 관리 모듈(223)을 더 포함한다.

[0195] 수신확인 모듈(226)은 제2 수신확인 메시지 TLP를 생성하고, 제2 수신확인 메시지 TLP를 송신지 PEIC에 대응하는 TLP 전송 큐(TTQ)에 버퍼링하며, 이에 따라 제2 수신확인 메시지 TLP를 스케줄링하여 송신 모듈에 송신하도록 추가로 구성되어 있다. 바람직하게, 수신확인 모듈(226)은 특정한 시간 간격에서 수신확인 메시지 TLP를 송신하거나, 수신확인되어야 하는 특정한 수의 TLP를 수신한 후에 수신확인 메시지 TLP를 송신한다(수신확인되어야 하는 TLP의 수는 원도의 수보다 커서는 안 된다).

[0196] 또한, P2P 모듈(21)은, 프로세싱을 위한 신뢰할 수 있는 TLP 전송 모듈(RTT 모듈)(22)에 제3 TLP를 포워딩하기 전에, 수신된 TLP의 유형, 패킷 내의 목적지 장치 ID 및 액세스 목적지 어드레스에 따라, 제3 TLP를 프로세싱을 위한 신뢰할 수 있는 TLP 전송 모듈(RTT 모듈)에 포워딩해야 하는지를 판단하도록 구성되어 있다. P2P 모듈은, 수신된 패킷의 유형(어드레스 루팅 또는 ID 루팅)에 따라, 대응하는 어드레스 포워딩 테이블 또는 ID 포워딩 테이블을 검색한다. 어드레스 포워딩 테이블 또는 ID 포워딩 테이블에 목적지 PEIC가 구성되어 있으면, 제3 TLP를 프로세싱을 위한 신뢰할 수 있는 TLP 전송 모듈(RTT 모듈)에 포워딩해야 함을 의미하고, 제3 TLP를 신뢰할 수 있는 RTT에 포워딩한다. 바람직하게, 로컬 어드레스 또는 로컬 ID를 가지는 TLP는 프로세싱을 위한 RTT에 포워딩될 필요 없이 RC 또는 EP에 직접적으로 회신될 수 있다.

[0197] 현재의 PCIE 사양에서는, 절대점 수신확인 메커니즘을 통해 TLP의 신뢰할 수 있는 전송이 실행되고 있다. 예를 들어, 도 2에서, 스위치 1은 스위치 2에 TLP를 송신하는데, 스위치 1은 TLP를 저장하고, 스위치 2가 정확한 TLP를 수신하고 스위치 1에 수신확인 정보를 회신할 때까지 그 대응하는 TLP를 삭제하지 않는다. 그렇지만, RC에 의해 스위치 2에 송신되는 TLP에 있어서, 스위치 1과 스위치 2 간의 링크가 실패하면, RC에 의해 스위치 1에 이미 성공적으로 송신된 패킷은 스위치 1과 스위치 2 간의 링크의 실패로 인해 폐기될 수도 있다. 그렇지만, RC는 스위치 1로부터 수신확인 정보를 수신하기 때문에 RC는 패킷이 성공적으로 송신된 것으로 간주한다. 이러한 실패는 RC가 TLP의 전송 결과를 정확하게 감지할 수 없게 만들어 버리며, 이에 의해 시스템은 비정상으로 작동하거나 데이터 연산이 폐기되어 버린다.

[0198] 본 발명의 실시예에서 제공하는 PCIE 인터페이스 제어기에서는, 송신된 TLP의 송신지 PEIC 번호 및 순차 번호를 실은 제3 TLP가 PCIE 스위칭 유닛에 연결된 송신 링크를 통해 PCIE 스위칭 유닛에 송신되고, PCIE 스위칭 유닛은 수신된 제3 TLP를 목적지 PEIC에 송신하며, 목적지 PEIC는 제3 TLP의 목적지 EP 또는 목적지 RC에 제3 TLP를 송신하고, 제1 수신확인 메시지 TLP를 그 송신된 TLP의 송신지 PEIC 번호 및 순차 번호에 따라 송신지 PEIC에 회신하며, 이에 의해 TLP의 전달을 완료한다. 목적지 PEIC에 의해 회신된 제1 수신확인 메시지 TLP가 시간이 종료될 때까지도 수신되지 않으면, 송신지 PEIC는 PCIE 스위칭 유닛에 연결된 송신 큐의 송신 링크를 통해 제3 TLP를 다시 송신하며, 이에 의해 PCIE 스위칭 이중 평면 네트워킹 접속의 경우 TLP의 신뢰할 수 있는 단대단 전송을 실행하고, PCIE 스위칭을 사용하는 시스템의 신뢰성이 높아진다.

[0199] 도 14는 본 발명의 실시예 6에 따른 PCIE 인터페이스 제어기의 구조도이다. 도면에 도시된 바와 같이, 신뢰할 수 있는 TLP 전송(RTT) 모듈(22)은:

[0200] 고정-시간(fixed-time) 검출 TLP를 시간 간격으로 모든 다른 PEIC에 송신하고, 목적지 PEIC에 의해 회신된 검출 응신 TLP가 지정된 시간 내에 수신되지 않으면, 대응하는 TTQ의 송신 링크를 재생한다는 것을 TLP 송신 큐 관리 모듈(222)에 통지하도록 구성되어 있는 중추부 모듈(heartbeat module)(227); 및

[0201] 상기 중추부 모듈(227)의 통지에 따라, 대응하는 TLP 전송 큐의 송신 링크를 재생하도록 추가로 구성되어 있는 TLP 전송 큐 관리 모듈(222)

을 더 포함한다.

[0203] 바람직하게, 중추부 모듈(227)은 고정-시간 검출 TLP를 통신 접속되어 있는 모든 다른 PEIC에 시간 간격으로 송신하고(시간 간격은 네트워크 상황에 따라 구성될 수 있는데, 예를 들어 10us 내지 1ms 사이의 값에 설정될 수 있다), 회신된 검출 응신 TLP가 지정된 시간 내에 수신되지 않는 목적지 PEIC에 있어서, 활성 및 대기 링크를 스위칭한다. 지정된 시간도 네트워크 상황에 따라 구성될 수 있는데, 고정-시간 검출 TLP가 송신될 때부터 검

출 응신 TLP가 수신되어야 할 때까지의 주기보다는 더 크다. 지정된 시간이 만료될 때까지도 검출 응신 TLP가 수신되지 않으면, 이것은 링크 실패 또는 PCIE 스위칭 유닛의 실패와 같이, 목적지 PEIC에 대한 통신 루트에 문제가 있다는 것을 의미한다. 이 경우, 중추부 모듈은 대응하는 TTQ의 송신 링크를 갱신한다는 것을 TLP 송신 큐 관리 모듈(222)에 통지하는데, 즉 TLP를 활성 링크를 통해 송신할지 또는 대기 링크를 통해 송신할지를 통지 한다.

[0204] 본 발명의 실시예에서, 중추부는 검출 패킷을 송신하고, 이에 의해 PEIC들 간의 링크에 대해 실패 검출을 실행하여, 활성 및 대기 평면의 자동 스위칭을 보장하며, PCIE 이중 평면 스위칭 네트워크에서 신뢰할 수 있는 패킷 전송을 더 보장한다.

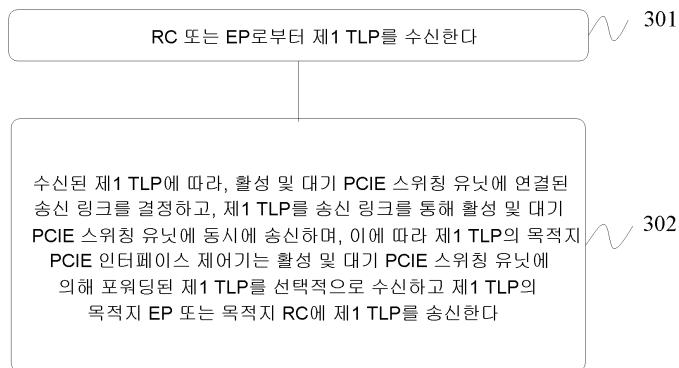

[0205] 도 15는 본 발명의 실시예 7에 따른 PCIE 스위칭 네트워크에서 패킷 전송을 위한 방법에 대한 흐름도이다. 도면에 도시된 바와 같이, 방법은 이하를 포함한다:

[0206] 단계 301: RC 또는 EP로부터 제1 TLP를 수신한다.

[0207] 단계 302: 수신된 제1 TLP에 따라, 활성 및 대기 PCIE 스위칭 유닛에 연결된 송신 링크를 결정하고, 제1 TLP를 송신 링크를 통해 활성 및 대기 PCIE 스위칭 유닛에 동시에 송신하며, 이에 따라 제1 TLP의 목적지 PCIE 인터페이스 제어기는 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 제1 TLP를 선택적으로 수신하고 제1 TLP의 목적지 EP 또는 목적지 RC에 제1 TLP를 송신한다.

[0208] 바람직하게, PCIE 인터페이스 제어기는, 수신된 제1 TLP에 따라, 활성 및 대기 PCIE 스위칭 유닛에 연결된 송신 링크를 결정하는데, 이것은 구체적으로: 제1 TLP를 수신한 후, 제1 PCIE 인터페이스 제어기는 제1 TLP의 유형에 따라, 즉 패킷이 어드레스 또는 식별(Identity: ID로 약칭)을 통해 루팅되는지에 따라, 대응하는 어드레스 포워딩 테이블 또는 ID 포워딩 테이블을 검색하고, 제1 TLP에 대응하는 목적지 PEIC 번호를 결정하여, 패킷에 대응하는 활성 및 대기 PCIE 스위칭 유닛의 송신 링크를 결정하고 송신 링크를 통해 활성 및 대기 PCIE 스위칭 유닛에 제1 TLP를 동시에 송신하는 것이다. 이 경우, 활성 및 대기 PCIE 스위칭 유닛은 수신된 제1 TLP를 목적지 PEIC에 송신하고, 목적지 PEIC는 제1 TLP를 선택적으로 수신하며, 예를 들어, 먼저 도착하는 제1 TLP를 수신하고 나중에 도착하는 제1 TLP를 폐기하며, 수신된 제1 TLP를 제1 TLP의 목적지 EP 또는 목적지 RC에 포워딩한다.

[0209] 또한, 제1 TLP가 송신 링크를 통해 활성 및 대기 PCIE 스위칭 유닛에 동시에 송신되기 전에, 방법은, 제1 TLP를 캡슐화하고, 제1 TLP의 자체 정의 단대단 TLP 접두사에 송신지 PEIC 번호 및 TLP 송신 순차 번호를 부가하며, 이에 따라 제1 TLP의 목적지 PEIC가 송신지 PEIC 번호 및 TLP 송신 순차 번호에 따라 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 제1 TLP를 선택적으로 수신하는 단계를 포함하며, TLP 송신 순차 번호는 송신지 PEIC에 의해 제1 TLP의 목적지 PEIC에 송신된 TLP의 순차 번호이다. 송신지 PEIC 번호 및 TLP 송신 순차 번호에 따라 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 제1 TLP를 선택적으로 수신하는 단계는, 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩되고 동일한 송신지 PEIC 번호 및 동일한 TLP 송신 순차 번호를 가지는 제1 TLP에 있어서, 먼저 도착하는 제1 TLP만을 수신하는 단계이다.

[0210] 본 발명의 실시예에서 제공하는 PCIE 이중 평면 스위칭 네트워크에서 패킷 전송을 위한 방법에서, PCIE 인터페이스 제어기(PEIC)는 제1 TLP를 활성 및 대기 PCIE 스위칭 유닛에 연결된 송신 링크를 통해 활성 및 대기 PCIE 스위칭 유닛에 동시에 송신하고, 제1 TLP의 목적지 PEIC는 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 제1 TLP를 선택적으로 수신하고 제1 TLP의 목적지 EP 또는 목적지 RC에 제1 TLP를 송신하며, 이에 의해 PCIE 이중 평면 네트워킹 접속의 경우에 TLP의 신뢰할 수 있는 전송을 수행하고, PCIE 스위칭을 사용하는 시스템의 신뢰성을 높인다.

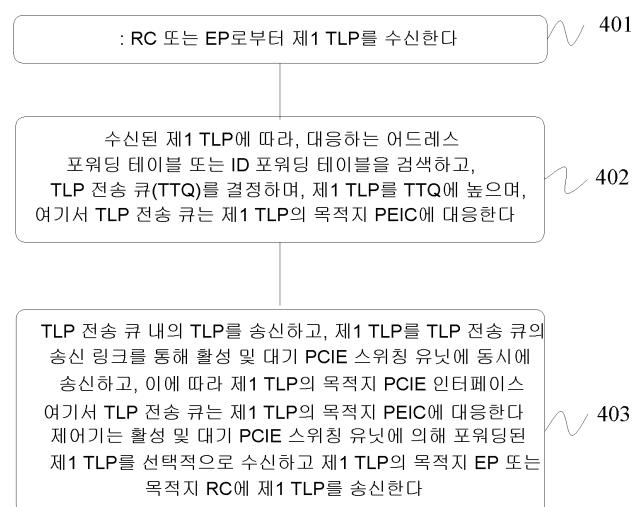

[0211] 도 16은 본 발명의 실시예 8에 따른 PCIE 스위칭 네트워크에서 패킷 전송을 위한 방법에 대한 흐름도이다. 도면에 도시된 바와 같이:

[0212] 단계 401: RC 또는 EP로부터 제1 TLP를 수신한다.

[0213] 단계 402: 수신된 제1 TLP에 따라, 대응하는 어드레스 포워딩 테이블 또는 ID 포워딩 테이블을 검색하고, TLP 전송 큐(TTQ)를 결정하며, 제1 TLP를 TTQ에 놓으며, 여기서 TLP 전송 큐는 제1 TLP의 목적지 PEIC에 대응한다.

[0214] 구체적으로, PEIC 인터페이스 제어기는 TLP의 루팅 방식(어드레스 루팅 또는 ID 루팅)에 따라, 대응하는 어드레스 포워딩 테이블 또는 ID 포워딩 테이블을 검색하며, 테이블 검색 결과에 따라 목적지 PEIC 번호를 획득한다.

[0215] 어드레스 포워딩 테이블은 도 6에 도시될 수 있으며; ID 포워딩 테이블은 도 7에 도시된 포맷을 사용할 수

있다. 특정한 내용 및 구성 방법은 전술한 실시예 2 및 실시예 3에서의 설명에서의 내용 및 구성 방법과 동일 하므로, 여기서 반복 설명하지 않는다. 바람직하게, 어드레스 포워딩 테이블 또는 ID 포워딩 테이블은 PCIE 인터페이스 제어기 상에 구성된다.

[0216] PCIE 인터페이스 제어기는 복수의 TLP 전송 큐를 더 포함한다. 본 실시예에서의 TLP 전송 큐의 기능 및 구조는 도 5에 도시된 실시예 2에서의 TLP 전송 큐의 기능 및 구조와 동일하다. 특정한 설명에 대해서는 관련 부분을 참조하면 되므로, 상세할 설명에 대해서는 여기서 반복 설명하지 않는다.

[0217] 단계 403: TLP 전송 큐 내의 TLP를 송신하고, 제1 TLP를 TLP 전송 큐의 송신 링크를 통해 활성 및 대기 PCIE 스위칭 유닛에 동시에 송신하고, 이에 따라 제1 TLP의 목적지 PCIE 인터페이스 제어기는 활성 및 대기 PCIE 스위칭 유닛에 의해 포워딩된 제1 TLP를 선택적으로 수신하고 제1 TLP의 목적지 EP 또는 목적지 RC에 제1 TLP를 송신한다.

[0218] PCIE 인터페이스 제어기는 TLP 전송 큐(TTQ) 내의 제1 TLP를 스케줄링하고, 제1 TLP를 캡슐화하고, 자체 정의 TLP 접두사(Prefix)를 부가하며, 캡슐화된 제1 TLP를 TTQ의 송신 링크를 통해 활성 및 대기 PCIE 스위칭 유닛에 동시에 송신한다. TLP의 포맷에 대한 정의가 도 9에 도시되어 있다: PCIE 사양에서의 정의에 따르면, TLP는 0 또는 복수의 표준 또는 자체 지정 TLP 접두사를 포함할 수 있다. TLP 접두사는 단대단 확장 및 점대점 확장의 파라미터 전달을 실행하고, 기능 확장을 실행할 수 있다. TLP Prefix는 또한 로컬 및 단대단 TLP Prefix로 분류된다. TLP 헤더는 TLP의 표준 헤더 부분이고, Data Payload는 TLP의 데이터 부분이고, TLP Digest는 TLP의 요약 부분이며; 이 3 부분이 PCIE 사양의 표준 내용이다. 바람직하게, 실시예에서, 송신지 PEIC로부터 목적지 PEIC까지의 송신지 PEIC 번호(SPEIC) 및 TLP 송신 순차 번호(SEQUENCE)의 전달은 자체 정의 단대단 TLP Prefix를 사용하여 실행된다. SEQUENCE는 송신지 PEIC에 의해 목적지 PEIC에 송신된 TLP의 순차 번호이고, TLP 전송 큐에 대응하는 목적지 PEIC에 송신된 TLP의 순차 번호이며, 각각의 TTQ에서 독립적으로 순서가 정해져 있으며, 이에 따라 목적지 PEIC는 SPEIC + SEQUENCE에 따라 그 수신된 TLP를 순서를 정하여 수신확인하며, 이에 의해 활성 및 대기 PCIE 스위칭 유닛에 의해 전달되는 제1 TLP의 수신을 선택적으로 실행한다. PCIE 인터페이스 제어기는 제1 TLP를 2개의 링크를 통해 활성 및 대기 PCIE 스위칭 유닛에 송신한다. 패킷이 송신된 후, TTQ의 목적지 PEIC에 대응하는 TLP 송신 순차 번호(SEQUENCE)가 1 증가한다. 목적지 PEIC는 활성 및 대기 링크를 통해 먼저 수신된 제1 TLP를 선택하고, 그 먼저 수신된 제1 TLP를 목적지 EP 또는 목적지 RC에 송신하며, 나중에 수신된 제1 TLP를 폐기하며; 즉 동일한 SPEIC + SEQUENCE를 가지는 TLP에 있어서, 먼저 도착하는 TLP만을 수신한다. 제1 TLP를 수신한 후, 목적지 PEIC는 제1 TLP를 제1 TLP의 목적지 EP 또는 목적지 RC에 송신하고, 이에 의해 TLP의 전송을 신뢰할 수 있게 순차적으로 완료한다.

[0219] 또한, PCIE 인터페이스 제어기는 추가로 각각의 전송 큐의 TLP 송신 순차 번호 및 TLP 송신 링크를 유지 및 관리한다.

[0220] 또한, 제1 TLP의 목적지 PEIC는 활성 및 대기 PCIE 스위칭 유닛에 의해 송신된 패킷을 선택적으로 수신하고, 수신된 제1 TLP를 제1 TLP의 목적지 RC/EP에 포워딩한다. 바람직하게, 제1 TLP의 목적지 PEIC는 활성 및 대기 PCIE 스위칭 유닛에 의해 송신된 제1 TLP의 자체 정의 단대단 TLP 접두사에 수반되어 있는 SPEIC 및 SEQUENCE에 따라 선택적 수신을 수행할 수 있고, 즉 2개의 링크를 통해 연속으로 수신되고 동일한 SPEIC 및 동일한 SEQUENCE를 가지는 제1 TLP에 있어서, 먼저 수신된 제1 TLP만이 선택되어 제1 TLP의 목적지 RC/EP에 송신되고, 나중에 수신된 제1 TLP는 폐기된다.

[0221] 바람직하게, PEIC는 복수의 TLP 수신확인 순차(TAS)를 더 포함할 수 있으며, 각각의 TLP 수신확인 순차(TAS)는 송신지 PEIC의 전송 큐에 대응한다(여기서 송신지 PEIC의 전송 큐란 PEIC에 대응하면서 TLP를 PEIC에 송신하는 다른 PEIC에 있는 전송 큐를 말한다). 본 실시예에서의 TLP 수신확인 순차의 기능 및 구조는 도 10에 도시된 실시예 3에서의 TLP 수신확인 순차의 기능 및 구조와 동일하다. 특정한 설명에 대해서는 관련 부분을 참조하면 되므로, 상세한 설명에 대해서는 여기서 반복 설명하지 않는다. 본 실시예에서, PCIE는 또한 각각의 TLP 수신 확인 순차에 의해 수신될 것으로 예상되는 TLP의 예상 순차 번호를 유지 및 관리한다.

[0222] 또한, PCIE 인터페이스 제어기는 또한, 수신된 TLP의 유형, 및 패킷 내의 목적지 장치 ID 또는 액세스 목적지 어드레스에 따라, 제1 TLP를 프로세싱을 위한 TLP 전송 큐에 베퍼링해야 하는지를 판단한다. PCIE 인터페이스 제어기는 그 수신된 패킷의 유형(어드레스 루팅 또는 ID 루팅)에 따라, 대응하는 어드레스 포워딩 테이블 또는 ID 포워딩 테이블을 검색한다. 어드레스 포워딩 테이블 또는 ID 포워딩 테이블에 목적지 PEIC가 구성되어 있으면, 포워딩 프로세싱이 필요하다는 것을 나타내며, 제1 TLP를 후속의 프로세싱을 위한 TLP 전송 큐에 베퍼링한다. 바람직하게, 로컬 어드레스 또는 로컬 ID를 가지는 TLP를, 프로세싱을 위한 RTT에 포워딩 할 필요 없이 RC

또는 EP에 직접 회신할 수 있다.

[0223] 본 발명의 실시예에서 제공하는 PCIE 이중 평면 스위칭 네트워크에서의 패킷 전송을 위한 방법에서, PCIE 인터페이스 제어기(PEIC)는 TLP의 목적지 PEIC에 따라 TLP 전송 큐를 결정하고, TLP를 대응하는 TLP 전송 큐의 송신 링크를 통해 활성 및 대기 PCIE 스위칭 유닛에 동시에 송신하고, 활성 및 대기 PCIE 스위칭 유닛은 제1 TLP를 제1 TLP의 목적지 PEIC에 포워딩하며, 목적지 PEIC는 제1 TLP에 수반되어 있는 송신지 PEIC 번호 및 TLP 송신 순차 번호에 따라 제1 TLP를 선택적으로 수신하며, 먼저 수신된 제1 TLP를 목적지 EP 또는 목적지 RC에 송신하고, 나중에 수신된 제1 TLP는 폐기하며, 이에 의해 TLP의 신뢰할 수 있는 전송을 완료하고, PCIE 이중 평면 네트워킹을 실행하며, PCIE 스위칭을 사용하는 시스템의 신뢰성을 높인다.

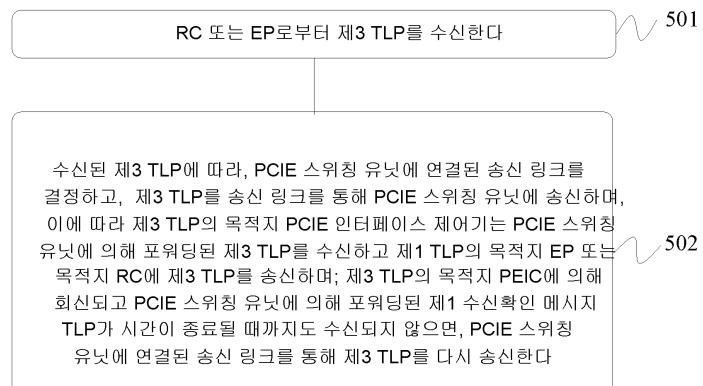

[0224] 도 17은 본 발명의 실시예 9에 따른 PCIE 스위칭 네트워크에서 패킷 전송을 위한 방법에 대한 흐름도이다. 도면에 도시된 바와 같이, 방법은 이하를 포함한다:

[0225] 단계 501: RC 또는 EP로부터 제3 TLP를 수신한다.

[0226] 단계 502: 수신된 제3 TLP에 따라, PCIE 스위칭 유닛에 연결된 송신 링크를 결정하고, 제3 TLP를 송신 링크를 통해 PCIE 스위칭 유닛에 송신하며, 이에 따라 제3 TLP의 목적지 PCIE 인터페이스 제어기는 PCIE 스위칭 유닛에 의해 포워딩된 제3 TLP를 수신하고 제1 TLP의 목적지 EP 또는 목적지 RC에 제3 TLP를 송신하며; 제3 TLP의 목적지 PEIC에 의해 회신되고 PCIE 스위칭 유닛에 의해 포워딩된 제1 수신확인 메시지 TLP가 시간이 종료될 때까지도 수신되지 않으면, PCIE 스위칭 유닛에 연결된 송신 링크를 통해 제3 TLP를 다시 송신한다.

[0227] 바람직하게, 제3 TLP를 수신한 후, PCIE 인터페이스 제어기(PEIC)는 TLP의 유형에 따라, 즉 패킷이 어드레스를 통해 루팅되는지 또는 식별(Identity: ID로 약칭)을 통해 루팅되는지에 따라, 대응하는 어드레스 포워딩 테이블 또는 ID 포워딩 테이블을 검색하고, 제3 TLP에 대응하는 목적지 PEIC 번호를 획득하여, 패킷에 대응하는 활성 및 대기 PCIE 스위칭 유닛의 송신 링크를 결정하고, 제3 TLP를 송신 링크를 통해 활성 및 대기 PCIE 스위칭 유닛에 동시에 송신한다. 이 경우, PCIE 스위칭 유닛은 수신된 제3 TLP를 목적지 PEIC에 송신하고, 이에 따라 목적지 PEIC는 대응하는 제3 TLP를 수신하고, 제3 TLP의 목적지 EP 또는 목적지 RC에 제3 TLP를 포워딩한다. 한편, 목적지 PEIC는 제3 TLP에 대한 제1 수신확인 메시지 TLP를 회신하고, PCIE 스위칭 유닛은 제1 수신확인 메시지 TLP를 송신지 PCIE 인터페이스 제어기에 포워딩하여, 제3 TLP가 수신되었다는 것을 나타낸다. 목적지 PEIC에 의해 회신된 제1 수신확인 메시지 TLP가 시간이 종료될 때까지 수신되지 않으면 송신지 PCIE 인터페이스 제어기는 PCIE 스위칭 유닛에 연결된 송신 링크를 통해 제3 TLP를 다시 송신한다(이중 평면의 경우, 이 경우의 PCIE 스위칭 유닛에 연결된 송신 링크가 제3 TLP가 이전에 송신된 송신 링크와 다를 수 있다).

[0228] 또한, 제3 TLP가 송신 링크를 통해 PCIE 스위칭 유닛에 송신되기 전에, 방법은, 제3 TLP를 캡슐화하고, 제3 TLP의 자체 정의 단대단 TLP 접두사에 송신지 PEIC 번호 및 TLP 송신 순차 번호를 부가하고, 이에 따라 제3 TLP의 목적지 PEIC가 제3 TLP에 있는 송신지 PEIC 번호 및 TLP 송신 순차 번호에 따라 제1 수신확인 메시지 TLP를 회신하는 단계를 더 포함하며, 여기서 상기 회신된 제1 수신확인 메시지 TLP의 자체 정의된 단대단 TLP 접두사는 제3 TLP의 목적지 PEIC의 PEIC 번호 및 수신확인된 TLP 송신 순차 번호를 수반하고 있다. 제3 TLP 내의 TLP 송신 순차 번호는 제3 TLP의 송신지 PEIC에 의해 제3 TLP의 목적지 PEIC에 송신된 TLP의 순차 번호이고, 제1 수신확인 메시지 TLP 내의 수신확인된 TLP 송신 순차 번호는, 송신지 PEIC의 TLP 송신 순차 번호이고 제3 TLP의 목적지 PEIC에 의해 이미 수신된 제3 TLP를 지니는 TLP 송신 순차 번호이다.

[0229] 현재의 PCIE 사양에서는, 절대점 수신확인 메커니즘을 통해 TLP의 신뢰할 수 있는 전송이 실행되고 있다. 예를 들어, 도 2에서, 스위치 1은 스위치 2에 TLP를 송신하는데, 스위치 1은 TLP를 저장하고, 스위치 2가 정확한 TLP를 수신하고 스위치 1에 수신확인 정보를 회신할 때까지 그 대응하는 TLP를 삭제하지 않는다. 그렇지만, RC에 의해 스위치 2에 송신되는 TLP에 있어서, 스위치 1과 스위치 2 간의 링크가 실패이면, RC에 의해 스위치 1에 이미 성공적으로 송신된 패킷은 스위치 1과 스위치 2 간의 링크의 실패로 인해 폐기될 수도 있다. 그렇지만, RC는 스위치 1로부터 수신확인 정보를 수신하기 때문에 RC는 패킷이 성공적으로 송신된 것으로 간주한다. 이러한 실패는 RC가 TLP의 전송 결과를 정확하게 감지할 수 없게 만들어 버리며, 이에 의해 시스템은 비정상으로 작동하거나 데이터 연산이 폐기되어 버린다.

[0230] 본 발명의 실시예에서 제공하는 PCIE 스위칭 네트워크에서의 패킷 전송을 위한 방법에서는, PCIE 스위칭 유닛에 연결된 송신 링크를 통해 제3 TLP가 PCIE 스위칭 유닛에 송신되고, PCIE 스위칭 유닛은 수신된 제3 TLP를 목적지 PEIC에 송신하며, 목적지 PEIC는 제3 TLP의 목적지 EP 또는 목적지 RC에 제3 TLP를 송신하고, 제1 수신확인 메시지 TLP를 송신지 PEIC에 회신한다. 목적지 PEIC에 의해 회신된 제1 수신확인 메시지 TLP가 시간이 종료될

때까지도 수신되지 않으면, 송신지 PEIC는 PCIE 스위칭 유닛에 연결된 송신 링크를 통해 제3 TLP를 다시 송신하며, 이에 의해 PCIE 스위칭 이중 평면 네트워킹 접속의 경우 TLP의 신뢰할 수 있는 단대단 전송을 실행하고, PCIE 스위칭을 사용하는 시스템의 신뢰성이 높아진다.

[0231] 도 18은 본 발명의 실시예 10에 따른 PCIE 스위칭 네트워크에서 패킷 전송을 위한 방법에 대한 흐름도이다. 도면에 도시된 바와 같이, 방법은 구체적으로 이하를 포함한다:

단계 601: RC 또는 EP로부터 제3 TLP를 수신한다.

단계 602: 수신된 제3 TLP에 따라, 어드레스 포워딩 테이블 또는 ID 포워딩 테이블을 검색하고, TLP 전송 큐(TTQ)를 결정하며, 제1 TLP를 TLP 전송 큐에 놓으으며, TLP 전송 큐는 제3 TLP의 목적지 PEIC에 대응한다.

바람직하게, PEIC 인터페이스 제어기는 수신된 제3 TLP의 루팅 방식(어드레스 루팅 또는 ID 루팅)에 따라, 대응하는 어드레스 포워딩 테이블 또는 ID 포워딩 테이블을 검색하고, 테이블 검색 결과에 따라 목적지 PEIC 번호를 획득하며, 수신된 제3 TLP를 대응하는 TTQ에 버퍼링한다. 어드레스 포워딩 테이블은 도 6에 도시될 수 있으며; ID 포워딩 테이블은 도 7에 도시된 포맷을 사용할 수 있다. 특정한 내용 및 구성 방법은 전술한 실시예 2 및 실시예 3에서의 설명에서의 내용 및 구성 방법과 동일하므로, 여기서 반복 설명하지 않는다.

도 12에 도시된 바와 같이, RTT 모듈(22)은 복수의 TLP 전송 큐를 더 포함한다. 본 실시예에서의 TLP 전송 큐의 기능 및 구조는 도 5에 도시된 실시예 2에서의 TLP 전송 큐의 기능 및 구조와 동일하다. 특정한 설명에 대해서는 관련 부분을 참조하면 되므로, 상세한 설명에 대해서는 여기서 반복 설명하지 않는다.

단계 603: 제3 TLP를 TLP 전송 큐의 송신 링크를 통해 PCIE 스위칭 유닛에 송신하고, 이에 따라 제3 TLP의 목적지 PCIE 인터페이스 제어기는 PCIE 스위칭 유닛에 의해 포워딩된 제3 TLP를 수신하고 제3 TLP의 목적지 EP 또는 목적지 RC에 제3 TLP를 송신하며; 제3 TLP의 목적지 PEIC에 의해 회신되고 PCIE 스위칭 유닛에 의해 포워딩된 제1 수신확인 메시지 TLP가 시간이 종료될 때까지도 수신되지 않으면, 제3 TLP를 다시 송신한다.

바람직하게, PCIE 인터페이스 제어기는 TLP 전송 큐(TTQ) 내의 TLP를 스캐줄링하고, TLP를 캡슐화하고, 자체 정의 TLP 접두사(Prefix)를 부가하여, 캡슐화된 제3 TLP를 TTQ의 송신 링크를 통해 PCIE 스위칭 유닛에 송신한다. TLP의 포맷에 대한 정의는 도 9에 도시된 바와 같다: 특정한 구조에 대한 관련 정의에 대해서는, 전술한 실시예 2 및 실시예 3의 도 9에서의 TLP의 포맷에 관한 설명을 참조하면 되므로, 상세한 설명에 대해서는 여기서 반복 설명하지 않는다. 바람직하게, 본 실시예에서는, 송신지 PEIC로부터 목적지 PEIC까지의 송신지 PEIC 번호(SPEIC) 및 TLP 송신 순차 번호(SEQUENCE)의 전달은 TLP 내의 자체 정의 단대단 TLP Prefix를 사용하여 실행된다. SEQUENCE는 송신지 PEIC에 의해 목적지 PEIC에 송신된 TLP의 순차 번호이고, 즉 TLP 전송 큐에 대응하는 목적지 PEIC에 송신된 TLP의 순차 번호이고, 각각의 TTQ에서 독립적으로 순서가 정해져 있으며, 이에 따라 목적지 PEIC는 SPEIC 및 SEQUENCE에 따라 그 수신된 TLP를 순서를 정하여 수신확인한다. 회신된 제1 수신확인 메시지 TLP의 단대단 TLP 접두사는 송신지 PEIC 번호 및 수신확인된 TLP 송신 순차 번호를 수반하고 있으며, 여기서 수신확인된 TLP 송신 순차 번호는 목적지 PEIC에 의해 송신지 PEIC로부터 이미 수신된 TLP의 송신 순차 번호이다. PEIC는 TTQ의 송신 링크를 통해 PCIE 스위칭 유닛에 제3 TLP를 송신한다. 패킷이 송신된 후, TTQ의 TLP 송신 순차 번호(SEQUENCE)가 1 증가한다.

[0238] 각각의 TLP 전송의 TLP 송신 시퀀스 번호 및 TLP 송신 링크가 유지되어야 한다. PEIC는 각각의 전송 큐의 TLP 송신 순차 번호 및 TLP 송신 링크를 유지하고, 각각의 전송 큐의 TLP 송신 순차 번호는 TTQ에 의해 이미 송신된 TLP의 송신 순차 번호를 나타내고, TLP 송신 링크는 TTQ의 활성 및 대기 송신 링크를 나타내며, 이에 따라 활성 송신 링크는 TLP를 송신하는 데 사용된다.

[0239] 604: 제3 TLP의 목적지 PEIC에 의해 회신되고 상기 PCIE 스위칭 유닛에 의해 포워딩된 제1 수신확인(ACK) 메시지 TLP를 수신한다.

[0240] 605: 제1 수신확인 메시지 TLP에 수반되어 있는 TLP 송신 순차 번호(SEQUENCE) 및 송신지 PEIC 번호(SPEIC)에 따라, TLP 전송 큐 내의 수신확인된 제3 TLP를 삭제한다.

바람직하게, TTQ는 TLP를 송신하는데 슬라이딩 윈도를 사용할 수 있으며, 이에 의해 각각의 TTQ에 의해 동시에 송신된 패킷의 수를 제한한다. TTQ의 슬라이딩 윈도 메커니즘은 도 13에 도시되어 있다. 도면에서 숫자가 붙은 각각의 박스는 TLP를 나타낸다. 예를 들어, 슬라이딩 윈도의 크기 4인데, 즉 목적지 PEIC에 의해 수신확인되지 않은 TLP 가 최대 4개까지 공존할 수 있다. 목적지 PEIC에 의해 회신된 TLP 수신확인 패킷을 수신한 후, 슬라이딩 윈도는 수신확인된 SEQUENCE에 따라 전진 이동한다. 예를 들어, 현재의 윈도에서 수신확인될 TLP가 2,

3, 4 및 5이고; 수신된 수신확인 메시지 TLP의 수신확인된 SEQUENCE가 2이면, 슬라이딩 윈도는 하나의 패킷만큼 전진 이동하고, 수신확인될 TLP는 현재의 윈도에서 3, 4, 5, 6이다. PEIC의 버퍼 성능에 따르면, 슬라이딩 윈도의 크기는 2 내지 n에 설정될 수 있다(n은 임의의 양의 정수). 슬라이딩 윈도를 설정함으로써, 각각의 TTQ에 의해 동시에 송신된 패킷의 수를 효과적으로 제어할 수 있고, 프로세싱 효율성이 향상되며, 동시에 송신 및 수신이 순차적으로 신뢰할 수 있게 수행된다.