(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6668332号

(P6668332)

(45) 発行日 令和2年3月18日(2020.3.18)

(24) 登録日 令和2年2月28日(2020.2.28)

|                     |             |

|---------------------|-------------|

| (51) Int.Cl.        | F 1         |

| HO3H 9/64 (2006.01) | HO3H 9/64 Z |

| HO3H 9/54 (2006.01) | HO3H 9/54 Z |

| HO3H 9/17 (2006.01) | HO3H 9/17 F |

請求項の数 14 (全 19 頁)

|                    |                               |

|--------------------|-------------------------------|

| (21) 出願番号          | 特願2017-512698 (P2017-512698)  |

| (86) (22) 出願日      | 平成27年8月5日(2015.8.5)           |

| (65) 公表番号          | 特表2017-526307 (P2017-526307A) |

| (43) 公表日           | 平成29年9月7日(2017.9.7)           |

| (86) 国際出願番号        | PCT/EP2015/068064             |

| (87) 国際公開番号        | W02016/034357                 |

| (87) 国際公開日         | 平成28年3月10日(2016.3.10)         |

| 審査請求日              | 平成30年7月13日(2018.7.13)         |

| (31) 優先権主張番号       | 102014112676.9                |

| (32) 優先日           | 平成26年9月3日(2014.9.3)           |

| (33) 優先権主張国・地域又は機関 | ドイツ(DE)                       |

早期審査対象出願

|           |                                                                                            |

|-----------|--------------------------------------------------------------------------------------------|

| (73) 特許権者 | 500480274<br>スナップトラック・インコーポレーテッド<br>アメリカ合衆国、カリフォルニア 921<br>21, サン デイエゴ, モアハウス<br>ドライブ 5775 |

| (74) 代理人  | 100108855<br>弁理士 蔵田 昌俊                                                                     |

| (74) 代理人  | 100109830<br>弁理士 福原 淑弘                                                                     |

| (74) 代理人  | 100158805<br>弁理士 井関 守三                                                                     |

| (74) 代理人  | 100112807<br>弁理士 岡田 貴志                                                                     |

最終頁に続く

(54) 【発明の名称】直線性を改善したフィルター

(57) 【特許請求の範囲】

## 【請求項 1】

フィルターを備えるフィルター回路であって、

前記フィルターは、

第1のフィルターポートを第2のフィルターポートに接続する直列信号経路と、

前記直列信号経路内に配置されたノード、前記ノードの各々は、それぞれ並列分岐を介して固定電位に接続される、と、

前記直列信号経路及び前記並列分岐に配置された共振部の回路構成、前記共振部の回路構成は、

各並列分岐内に配置され、複数の共振部をカスケード接続した並列共振部と、

前記直列信号経路内に配置され、複数の共振部をカスケード接続した直列共振部のセットと

を備える、と、

第1のコンデンサーまたは第2のコンデンサーのうちの少なくとも1つ、前記第1のコンデンサーは、前記並列分岐のうちの1つと直列または並列に配置され、前記第2のコンデンサーは、前記直列信号経路と直列または並列に配置される、と

を備え、前記並列分岐それぞれは、前記並列分岐における前記並列共振部の容量、または前記並列分岐における前記並列共振部の容量と、前記並列分岐における前記並列共振部と並列または直列に接続された前記第1のコンデンサーとから生じる総容量を有し、

前記総容量は、前記第2のフィルターポートに最も近い並列分岐を除いて同じである、

10

20

フィルター回路。

【請求項 2】

前記共振部は、電気音響共振部である、請求項 1 に記載のフィルター回路。

【請求項 3】

前記並列共振部は、直列に接続された 1 個 ~ 8 個の共振部を備える、請求項 1 に記載のフィルター回路。

【請求項 4】

前記第 2 のコンデンサーは、前記直列共振部と前記第 1 のフィルターポートとの間の前記直列信号経路内に配置され、前記第 1 のコンデンサーは、前記並列共振部と並列に配置される、請求項 1 に記載のフィルター回路。

10

【請求項 5】

前記第 1 または第 2 のフィルターポートのうちの少なくとも 1 つに接続された 1 つまたは複数の受信分岐または 1 つまたは複数の送信分岐のうちの少なくとも 1 つをさらに備え、1 つまたは複数の送信分岐は、異なる送信帯域における送信のために構成され、前記 1 つまたは複数の受信分岐は、異なる受信帯域における受信のために構成される、請求項 1 に記載のフィルター回路。

【請求項 6】

前記フィルターは、デュプレクサの受信フィルターまたは送信フィルターである、請求項 1 に記載のフィルター回路。

【請求項 7】

前記フィルター回路は、前記直列信号経路内の前記第 2 のフィルターポートに最も近い前記並列共振部のうちの 1 つから下流に配置された第 4 のコンデンサーを備え、前記第 2 のコンデンサーは、前記直列共振部のセットから上流に配置され、前記第 1 のコンデンサーの各々は、前記並列共振部の残りのセットの間に配置される、請求項 1 に記載のフィルター回路。

20

【請求項 8】

前記直列信号経路内に配置されたダブルモード弾性表面波 (DMS) フィルターをさらに備える、請求項 1 に記載のフィルター回路。

【請求項 9】

フィルター回路は、チップであり、

30

前記共振部の各々は、弾性表面波 (SAW) 1 ポート共振部であり、前記共振部の各々は、前記チップ上に配置され、前記第 1 のコンデンサーまたは前記第 2 のコンデンサーのうちの少なくとも 1 つは、2 つのコンデンサー電極を有する平板コンデンサーとして前記チップ上に実現され、導体トラックに対して平面形状において共有され、誘電体層がそれらの間に配置され、

前記チップの追加の機能層と共に前記誘電体層は、同じ材料および同じ層厚を備え、

前記第 1 のコンデンサーまたは前記第 2 のコンデンサーのうちの前記少なくとも 1 つの下部電極は、前記 1 ポート共振部のうちの 1 つのメタライゼーションから形成され、

前記第 1 のコンデンサーまたは前記第 2 のコンデンサーのうちの前記少なくとも 1 つの上部電極は、前記フィルターの接続パッド上に作成されるパッド肥厚化から形成される、

40

請求項 1 に記載のフィルター回路。

【請求項 10】

前記誘電体層は、別の 1 つと交差する前記フィルター回路の導体トラック部の間の絶縁のために使用される絶縁層と共に前記コンデンサー電極の間に作成される、請求項 9 に記載のフィルター回路。

【請求項 11】

前記誘電体層は、正の温度係数を有する材料を備える、請求項 9 に記載のフィルター回路。

【請求項 12】

前記第 1 および第 2 のコンデンサーは、外部のディスクリートコンデンサーとして埋め

50

込まれた、または低温度同時焼成セラミック (L T C C) または積層体に一体化されたもののうちの少なくとも 1 つである、請求項 1 に記載のフィルター回路。

【請求項 1 3】

フィルターを備えるフィルター回路であって、

前記フィルターは、

第 1 のフィルターポートを第 2 のフィルターポートに接続する直列信号経路と、

前記直列信号経路内に配置されたノード、前記ノードの各々は、それぞれ並列分岐を介して固定電位に接続される、と、

前記直列信号経路及び前記並列分岐に配置された共振部の回路構成、前記共振部の回路構成は、

各並列分岐内に配置され、複数の共振部をカスケード接続した並列共振部と、

前記直列信号経路内に配置され、複数の共振部をカスケード接続した直列共振部のセットと

を備える、と、

第 1 のコンデンサーまたは第 2 のコンデンサーのうちの少なくとも 1 つ、前記第 1 のコンデンサーは、前記並列分岐のうちの 1 つと直列または並列に配置され、前記第 2 のコンデンサーは、前記直列信号経路と直列または並列に配置される、と

を備え、前記直列信号経路における前記直列共振部のセットの各々は、前記直列共振部の容量、または前記直列共振部の容量と、前記直列共振部と並列または直列に接続された前記第 1 のコンデンサーのものとから生じる総容量を有し、

前記総容量は、前記直列信号経路内に配置された前記直列共振部のセットのうちの、前記第 2 のフィルターポートに最も近い直列共振部を除いて同じである、

フィルター回路。

【請求項 1 4】

フィルターを備えるフィルター回路であって、

前記フィルターは、

第 1 のフィルターポートを第 2 のフィルターポートに接続する直列信号経路と、

前記直列信号経路内に配置されたノード、前記ノードの各々は、それぞれ並列分岐を介して固定電位に接続される、と、

前記直列信号経路及び前記並列分岐に配置された共振部の回路構成、前記共振部の回路構成は、

各並列分岐に配置され、複数の共振部をカスケード接続した並列共振部と、

前記直列信号経路内に配置され、複数の共振部をカスケード接続した直列共振部のセットと

を備える、と、

第 1 のコンデンサーまたは第 2 のコンデンサーのうちの少なくとも 1 つ、前記第 1 のコンデンサーは、前記並列分岐のうちの 1 つと直列または並列に配置され、前記第 2 のコンデンサーは、前記直列信号経路と直列または並列に配置され、カスケード接続された共振部のカスケードしている度合は、前記第 1 のフィルターポートからの距離が増加すると共に減少し、前記並列分岐それぞれは、前記並列分岐における前記並列共振部の容量、または前記並列分岐における前記並列共振部の容量と、前記並列分岐における前記並列共振部と並列または直列に接続された前記第 1 のコンデンサーとから生じる総容量を有し、

前記総容量は、前記第 2 のフィルターポートに最も近い並列分岐を除いて同じである、と

を備える、フィルター回路。

【発明の詳細な説明】

【背景技術】

【0 0 0 1】

通信工学及び電気音響学における相互変調 (IM 又は IMD) は、少なくとも 2 つの異なる周波数を処理しなくてはならない場合に、回路部品からの非線形伝達関数を介する不

10

20

30

40

50

要な電波の発生を意味する。使用周波数範囲におけるこのような相互変調積は、不要な信号及び妨害を引き起こすことがあるため、混乱を生じる相互変調積の発生は常に回避するよう努められる。

【0002】

H F 信号発生時に、高調波も形成することがあり、またその周波数を合わせるのは、基本モードの偶数倍である必要がない。このような高調波は、基本モードから十分離れ得るが、それでも他の帯域を妨害する場合がある。通常、高調波も、 $f_1$  及び  $f_2$  が、 $f_1 = f_2$  である特殊ケースの 2 つの周波数の相互変調積として現れることがある。

【0003】

係数又は合計が異なり、混合積の基本周波数を含む、第二次、第三次及び高次の相互変調積又は高調波がある。 10

【0004】

相互変調積及び混乱を生じる高調波を回避するために、成分及び回路部品の直線性の向上が最初に求められる場合がある。これが達成しないと、回路素子が直線的に対応する範囲を広げるために、非直線性成分にかかる電圧を下げる事となる。

【0005】

フィルター技術の領域、特に直列及び並列共振回路のネットワークから構成される、リアクタンスフィルターにおいて、複数の共振部をカスケード接続することにより相互変調積を抑制することができるが、完全に除去することはできない。カスケード接続の欠点は、共振部の回路構成における、フィルターに必要な静電容量であり、つまり、共振部のカスケード接続は、各コンデンサー又は共振部の空き容量条件を増加することによってのみ持続及び適応することができる。結果として、カスケード接続を増加させた共振部フィルターの空き容量条件は過大であり、従ってカスケード接続は不経済となる。さらに、これは小型化への要求に逆らう。 20

【0006】

さらなる欠点は、カスケード接続の増加により飽和効果が生じ、そのため、カスケード接続への共振部の追加にかかわらずその効果が出ない、又は、達成し得る相互変調積及び高調波の抑制が、追加の共振部の使用で、より小さくなってしまうことである。

【0007】

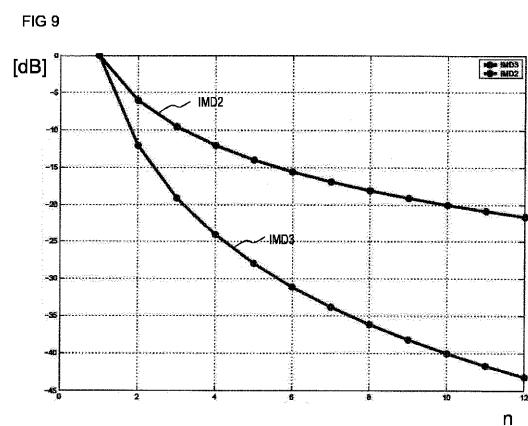

図 9 は、カスケード接続の  $n$  度に応じて、第二次高調波 ( IMD2 ) 及び第三次高調波 ( IMD3 ) の相互変調積抑制がどのように現れるかを示し、この  $n$  は直列接続する共振部の数を示す。直線箇所の増加、曲線箇所の減少が、飽和状態を明確に表す。これは、カスケード接続が、特定の角度においてのみ技術的及び経済的に実現可能であることを示す。 30

【発明の概要】

【発明が解決しようとする課題】

【0008】

本発明の目的は、直線性を改善し、相互変調積及び高調波の抑制を行うフィルター回路を明示することである。さらに、フィルター回路は、共振部表面積の適度な増加を実現すべきである。 40

【0009】

本目的は、請求項 1 に記載の特徴を有するフィルター回路による本発明に従い達成する。本発明の有利な実施形態は、追加の請求項により明示される。

【課題を解決するための手段】

【0010】

フィルター回路は、リアクタンスフィルターとして形成される第一フィルターを含む。このようなフィルターは、第一フィルターポートと第二フィルターポートとの間に接続する、直列信号経路 ( 直列枝 ) を含む。並列枝は、固定電位の回路ノードに接続する直列信号経路に配置される各回路ノードから分岐する。少なくとも 1 つの共振部又は 1 つの共振部の回路構成は、直列枝及び各並列枝に配置される。 50

## 【0011】

リアクタンスフィルターは、直列枝の回路ノード又は共振部との接続ポートから開始することができる。

## 【0012】

フィルターポートの1つに最も近く配置、又は、直列枝のフィルターポートに直接接続、あるいは、[missing]された、少なくとも第一並列枝において、複数の共振部は、直列又は並列で複数の共振部の直列回路構成と接続する第一コンデンサーと直列接続し、その結果、第一ケースでは電圧分割、第二ケースでは電流分割を生じる。

## 【0013】

従って、本発明の根本概念は、少なくとも1つの線形要素を含む、電圧デバイダ又は電流デバイダ回路を提供することである。上記のコンデンサーは、好ましくは線形要素であるが、電圧分割に適する他の線形要素であってもよい。この方法によって最初に述べた飽和を低減することが可能であり、そうでなければ、カスケード率の増加に伴い、すなわち、直列接続の共振部の数が増加することで、相互変調積の回避効果が低減され続けることとなる。コンデンサーはさらに、比較的広帯域で作動し、故に広域周波数帯域に適応する電圧分割又は電力分割効果という利点を有する。電圧分割の場合、以下のケースとなる。線形要素になる電圧が大きくなるほど、相互変調積の低減への影響が大きくなる。直列又は並列枝の総静電容量に比べて、コンデンサーの容量がより小さくなれば、効果がより大きくなり、かつ、相互変調積及び高調波の発生をより強力に回避する。

## 【0014】

共振部の回路構成に並列接続、つまり、共振部との直列カスケード接続するコンデンサーは電流デバイダの代わりになる。より大きな電流が線形要素を流れるに、非線形要素には電流がわずかしか流れず、本発明に従う相互変調積又は高調波の発生がほとんどなくなるという場合もある。

## 【0015】

線形要素は通常フィルター回路内に配置され単独で機能する。しかし線形要素は、少なくとも1つの信号が信号経路へ発信又は接続するフィルターポートに最も近いこれらの共振部に並列接続又は直列接続することで最大の効果を有し、かつ、それ自身、又は、非線形要素での異なるシステム周波数にて相互変調積及び高調波を形成することができる。全体として、回路環境にカップリングが依存しないため、このフィルターポートはフィルター入力又はフィルター出力となる場合があり、従って、クライアント特有で、かつ、フィルター回路などに依存しない。本発明に従い、線形要素は、この「第一」共振部にどの場合も接続する。第一ノード及び「第一」並列アームが並列共振部のフィルターポートにより近い場合、「第一」共振部は、直列共振部などであってよい。

## 【0016】

線形コンデンサーは、平板コンデンサーとして共通回路基板上の共振部と共に容易に実現することができる。しかし、別々の外部要素として共振部にコンデンサーを接続することも可能である。しかしながら、これに関して、共通回路基板上の統合は、さらなる利点を有する。フィードバック要素として共振部に接続することもできるインダクタンスに比べて、コンデンサーはその使用時に、追加の共振部、及び、フィルターの伝播挙動における追加の混乱が起こらず、コンデンサーを利用して電圧分割又は電力分割の影響が広帯域にて達成することができるという利点を有する。

## 【0017】

提示されたフィルター回路の1つの欠点は、電圧分割又は電力分割にて共振部のゼロピッチが減少し、これがフィルターの帯域幅に直接影響することである。フィルターの最適化により、所望の帯域幅を定めることができ、同時に欠点も考慮しなければならないが、通過帯域、特にVSWRや阻止帯域付近では、フィルター挙動は容易に減衰することができる。

## 【0018】

本発明に従い最適化された第一フィルターにより提示されたフィルター挙動は、優れた

10

20

30

40

50

透過拳動又はV S W R、及び、相互変調積又は高調波との間の相反関係を示す。混乱を生じる相互変調積又は高調波の混乱を回避するか、若しくは、最適化された透過拳動又はV S W Rをさらに重視するかどうかについても評価すべきである。

【0019】

本発明に従う好ましい影響は既に達成されたが、これは、單一共振部が、第一直列枝又は並列枝のコンデンサーに直列又は並列に接続する場合である。共振部の静電容量及びコンデンサーの容量を合わせると、直列枝又は並列枝の総容量となる。両方とも、フィルター設計において考慮されなければならない。

【0020】

好ましい実施形態においては、共振部は音波と共に用いるよう設計される。従って、S A W、F B A R、又はB A W（弹性表面波（Surface Acoustic Wave）、薄膜バルク音響波（Thin Film Bulk Acoustic Wave）、又はバルク音響波（Bulk Acoustic Wave））は、フィルター回路又はフィルター回路の第一フィルターに適している。ガイドバルク波と共に発振するG B A W（ガイドバルク音響波（Guided Bulk Acoustic Wave））共振部も適応する。いかなる場合でも、共振部の容量は共振部表面積によって設定される。第一板状電極と第二板状電極との間の重複範囲に、特に圧電性物質がそれらとの間に配設される限りにおいては、B A W共振部の共振部表面が配置される。S A W共振部では、静電容量は、共振部の開口積及び共振部の電極指数の関数である。

【0021】

原則として、共振部はL C共振部として設計することができるが、並列枝内で、又はその並列枝に並列して、相互接続することにより、相互変調積又は高調波の低減もまた達成することが可能である。

【0022】

実施可能な実施形態の1つにおいて、第一並列枝の共振部の回路構成は、直列する4つから8つの回路構成を含む。相互変調積又は高調波の十分な減衰性を有する優れた透過拳動は、この数を適当な空き容量条件に使用することで達成される。他の実施形態は、回路構成により多くの又はより少ない共振部を含むことができる。

【0023】

さらなる実施形態では、第二コンデンサーは、追加の直列又は並列共振部に、直列又は並列に接続される。この第二コンデンサーは任意であり、コンデンサー自身はほとんどが線形要素であるのに対して、さらなる個々の電圧降下を引き起こして非線形要素となる。相互変調積又は高調波もこのようにして低減される。

【0024】

第二コンデンサーもまた、混乱又は相互変調積を生じる1つの信号を接続することにより、可能な限りフィルターポートに付近に配設される。

【0025】

対応共振部が、直列共振部である場合、「並列接続」とは、第二コンデンサーを共振部の前後にある側枝の回路ノードに通じる並列経路内に配設することを意味する。

【0026】

対応共振部が並列共振部である場合、第二コンデンサーは、有利に共振部を含む並列枝に隣接し、かつ、共振部を有する並列枝としての直列信号経路にある同様の回路ノードに特に接続する並列枝に配設される。

【0027】

有利な実施形態では、第一フィルターは、フィルター入力又はフィルター出力に接続する複数の送信ブランチを含むフィルター回路の受信フィルターである。送信ブランチは、異なる伝送帯域にて送信するよう設計されているので、受信フィルターの通過帯域内に好ましくない通信がある場合に生じることがあり、また、このようなフィルター回路にて、相互変調積が理論上生じる場合がある。フィルター内で使用される信号外の異なる周波数の相互接続又は周波数のカップリングが容量性経路、誘導性経路、抵抗性経路又は電磁経路にて起こることがあり、これは完全には回避ができない。しかし、カップリングのさらな

10

20

30

40

50

る結果である、非線形要素の結果としての相互変調積又は高調波は、本発明にむしろ低減することが可能である。

【0028】

さらなる実施形態では、第一フィルターは受信フィルターとして設計される。これは、他の発信又は受信フィルターを含むフィルター回路の一部となることがある。

【0029】

第一フィルターは複数の送信ブランチを含むフィルター回路の一部であるデュプレクサ又はマルチプレクサの一部になる場合があり、それらの信号は、フィルターの信号経路に接続することができる。

【0030】

本発明のさらなる実施形態では、第一共振部の前、最後の共振部の後に設置され、かつ、信号経路内に配設される各共振部との間に追加的に、又は、2つの共振部毎の間に常に設置され、若しくは、信号経路内に配設される共振部の全回路構成との間に配置される。追加的なコンデンサーは、共振部又はカスケード接続された共振部の回路構成に接続されることがある。

10

【0031】

第一フィルターは、フィルター素子としての共振部だけを含み得る。しかし、信号経路内で、DMSフィルターと接続することが可能である。これは、直列信号経路内の回路ノードがDMSフィルターの入力に接続され、かつ、さらなる回路ノードはDMSフィルターの出力に接続されるという容易な方法により達成する。DMSフィルターは有利にフィルター入力に隣接しないが、2つの共振部の間、又は直列信号経路内の共振部の2つの回路構成の間に配置される。

20

【0032】

既に述べたように、フィルター基板内に組み込まれるコンデンサーを搭載する実施形態は、特に有利であることを示している。共振部は、音波と共に用いるよう設計され、かつ、共通チップ上に配設される。第一コンデンサー及び/又は第二コンデンサー及び/又は追加の第一第二コンデンサーは、同じチップ上に平板コンデンサーとして導入される。このような平板コンデンサーは、2つの平状キャパシタ電極とそれらとの間に配設される誘電体層を有する。本明細書の平板デザインは、印刷導体より断面積が非常に大きいことを意味する。

30

【0033】

チップ素子の追加機能層と合わさる誘電体層が、单一工程にて製造される場合は、優れた組み込み性に利点となる。このようにして、コンデンサー又はコンデンサーの誘導体に積層、又はこれらを作成する公知のフィルターの製造に既に使用されている手段が使用できる。

【0034】

一般的に、機能層及び誘電体層の組み合わせ製造は、両方が同じ材料、及び、同じコーティング厚を有することを意味する。しかし、次の工程にて機能層又は誘電体層を厚くすること、又は、コーティングの厚みを薄くすることが可能である。いかなる場合でも、特に高い厚み制御性を特徴とする、できる限り高い直線性を有するコンデンサーを製造することが重要である。

40

【0035】

1つの実施形態は、2つの伝導路の交差領域にて、伝導路を絶縁するために、第一フィルター又はフィルター回路内の他の場所で使用される誘電体として有機ポリマーを有する。ベンゾシクロブテンをベースにしたポリマー類及びその誘導体類は、実績があり、かつ有益な材料である。半導体回路に実績のある本材料は、低誘電率を有し、均一な多層厚を容易に製造することができる。

【0036】

さらなる実施形態では、中周波数の過昇温反応の補正、つまり、中周波数の過昇温の温度係数のために、材料は公知のフィルターに使用される誘電体層として使用される。通常

50

、機械的特性の正特性を有する材料層、特に  $\text{SiO}_2$  がこのために使用される。本発明に従い、この  $\text{SiO}_2$  層は、誘電体層として使用することができ、そのコーティング厚は、コンデンサーの最適な静電容量値、又は温度係数の最適な補正值、若しくはこの 2 つのトレードオフのどれかを提供するよう最適化することができる。

【0037】

一般的に、機械的特性の正特性を有する他の材料も、本目的のために使用することができる。誘導体層の作成後、コンデンサーの上部電極は、誘導体層上で印加されなければならない。

【0038】

さらなる実施形態では、フィルターの別の場所や、別な方法に既に使用されている材料も、平板コンデンサーの電極に有利に使用される。 10

【0039】

例えば、コンデンサーの下部電極は、共振部として使用される SAW1 ポート共振部の金属化から形成することができるコンデンサーの上部電極は、例えばフィルターの端子パッド上に形成されるパッドの厚みと共に形成することができる。

【0040】

線形化コンデンサーが電子音響共振部の通常の電極構造体を有することが可能である。コンデンサーはその共振周波数に離調する場合がある。疑似 SAW 共振部又は疑似 GBAW 共振部は、基板の結晶軸に対応して回転することができるため、電気音響結合係数  $k^2$  は十分に低いという可能性もある。 20

【0041】

本発明に従う 1 つのフィルター回路にて、相互変調積又は高調波が結合する結果となる少なくとも 1 つの信号によって明白な効果を示すコンデンサーは、フィルターポート近辺に配設される。共振部のカスケード接続についても同様であり、好ましくは、フィルター入力に直接又は近隣にあるそれらの共振部を特に実行する。

【0042】

従って、有利なフィルター回路は、共振部及び複数の共振部の回路構成を有し、1 つの実施形態では、回路構成は、カスケード接続した共振部の複数の共振部及び共振部のカスケード率を含み、フィルター入力から離れるに伴いこのフィルター回路が縮小する。このようにして、増加するカスケード率に並列する、増加するフィルター回路の空き容量条件に制限をすることは可能である。 30

【0043】

本発明に従うフィルターは、並列枝の最適化数値を含み得る。有利には、2 ~ 7、具体的には 2 ~ 4 の並列枝が提供される。本発明に従うフィルターは、並列枝の最適化数値を含み得る。直列要素は、直列共振部の回路構成として、あるいは、DMS フィルター又は DMS 基板などの別の要素としての直接共振部である。第二コンデンサーは、直列要素の一部でもあり得る。直列要素は、回路ノードによって両側に接する。1 つの直列要素は、都度、フィルター入力とフィルター回路ノードとの間に、又は、フィルター出力とフィルター出力との間に配設することができる。有利には、2 ~ 6 の直列要素が提供される。

【0044】

各共振部若しくは直列枝又は並列枝へ線形化要素を追加することは必要ではない。通常、要素を、効果が高い線形稼動のコンデンサーなどの定位置に接続することで十分である。基本信号及び / 又は干渉信号が通過帯域に位置するかどうかに応じて、回路トポロジーにおける要素の理想的な位置は変更することができる。 40

【0045】

本発明はさらなる詳細を例示的実施形態及び添付図で参照し、以下で説明する。図がフィルター及びフィルター回路を表す限りにおいては、これらは単に概略的な説明を意味する。これは、提示される各フィルター回路は、フィルターのさらなる最適化のために、不可欠ではないがフィルター回路に使用することができる、それ自体公知の他の要素を含み得ることも意味する。本発明に無関係である要素は削除することができる。 50

## 【図面の簡単な説明】

## 【0046】

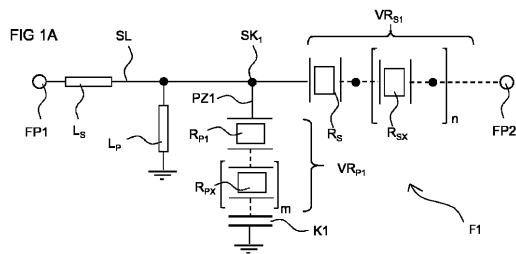

【図1A】簡易的実施形態を示し、それぞれ並列枝に配設されたコンデンサーを有する。

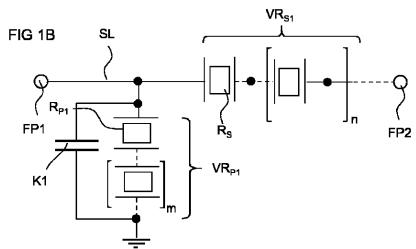

【図1B】簡易的実施形態を示し、それぞれ並列枝に配設されたコンデンサーを有する。

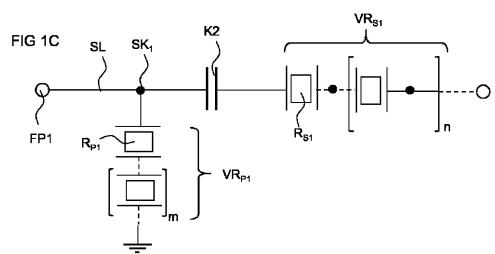

【図1C】簡易的実施形態を示し、それぞれ直列枝に配設されたコンデンサーを有する。

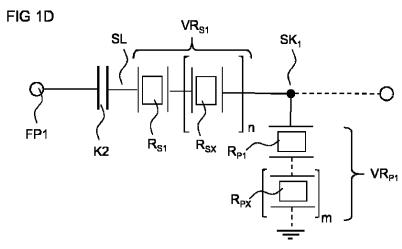

【図1D】簡易的実施形態を示し、それぞれ直列枝に配設されたコンデンサーを有する。

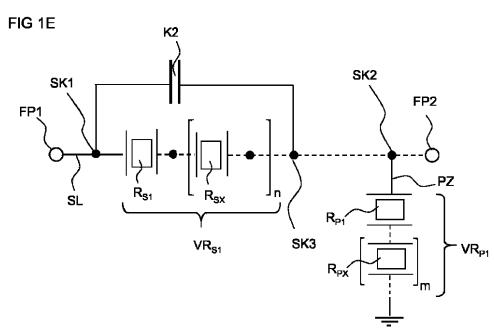

【図1E】直並列枝に配設するコンデンサーを有する実施形態を示す。

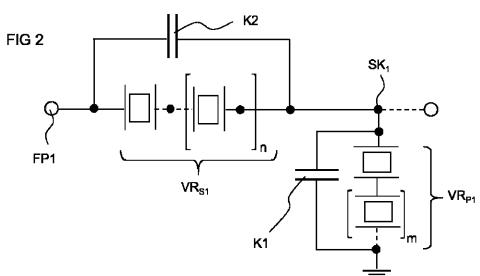

【図2】並列枝、さらに信号経路に配設する各2つのコンデンサーを有する実施形態を示し、このコンデンサーは、共振部に直列又は並列の両方で接続、若しくは、直列枝及び並列枝の両コンデンサーは、別に接続する。

10

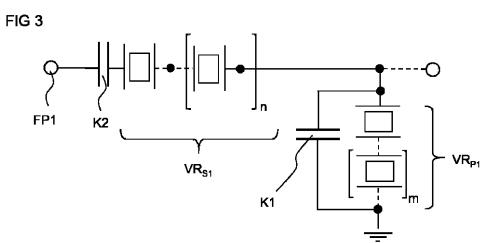

【図3】並列枝、さらに信号経路に配設する各2つのコンデンサーを有する実施形態を示し、このコンデンサーは、共振部に直列又は並列の両方で接続、若しくは、直列枝及び並列枝の両コンデンサーは、別に接続する。

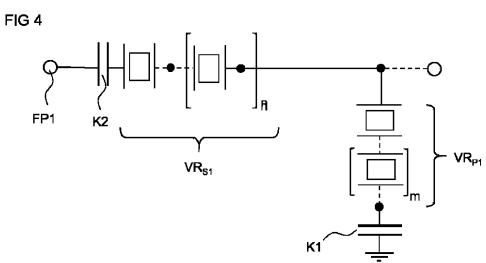

【図4】並列枝、さらに信号経路に配設する各2つのコンデンサーを有する実施形態を示し、このコンデンサーは、共振部に直列又は並列の両方で接続、若しくは、直列枝及び並列枝の両コンデンサーは、別に接続する。

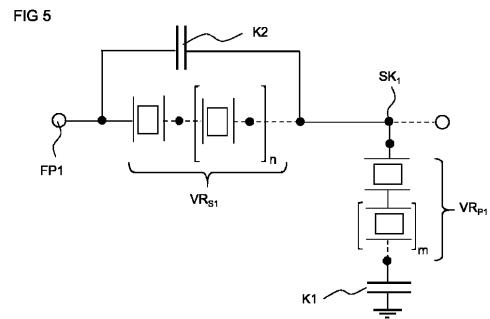

【図5】並列枝、さらに信号経路に配設する各2つのコンデンサーを有する実施形態を示し、このコンデンサーは、共振部に直列又は並列の両方で接続、若しくは、直列枝及び並列枝の両コンデンサーは、別に接続する。

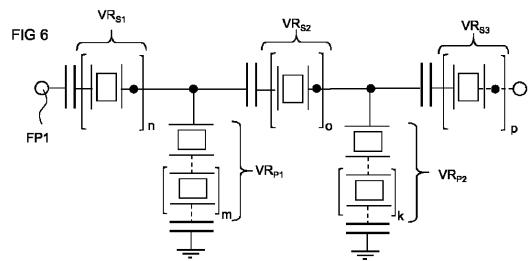

【図6】並列経路及び信号経路に、第一、第二コンデンサー及び追加コンデンサーを含むフィルター回路を示す。

20

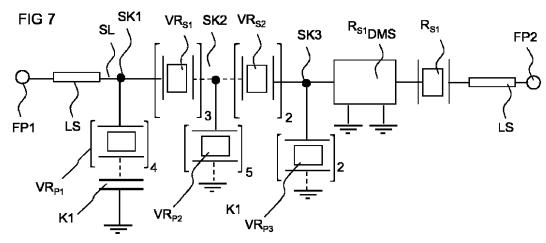

【図7】追加的回路要素としてフィルター入力及びノーマル又はフィルター出力に隣接する信号経路にインダクタンスを含むフィルター回路を示す。

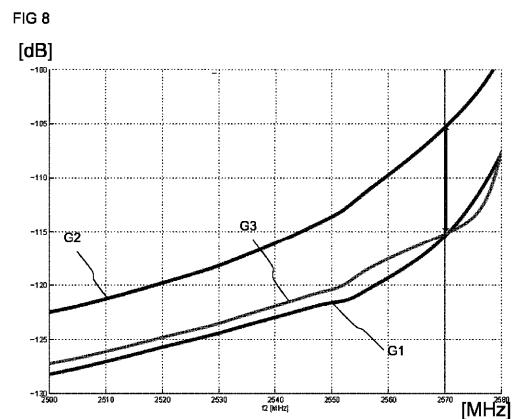

【図8】本発明に従うフィルター回路の使用によって、相互変調積の発生がどのように減少するかの異なるシミュレーション結果を示す。

【図9】回路内で使用される共振部のカスケード率によって決まる相互変調積の低減効果を示す。

## 【発明を実施するための形態】

## 【0047】

図1Aは、本発明の簡略的かつ典型的な実施形態を示している。図1Aに示すのは、直列信号線S\_Lにより第一フィルターポートF\_P\_1と第二フィルターポートF\_P\_2とが接続されているフィルター回路のフィルターである。第一フィルターポートF\_P\_1及び第二フィルターポートF\_P\_2は、任意選択により、フィルター入力又はフィルター出力に割り当てることができる。信号線S\_Lには、直列共振部R\_S\_1が配置されている。任意選択により、信号経路S\_L内の第一直列共振部R\_S\_1に、追加の共振部R\_S\_Xを接続することができる。Nは、0～約10の整数値を表し得る。直接直列接続された直列共振部により、共振部V\_R\_S\_1の第一回路構成が形成される。全ての共振部R\_S\_Xは、それぞれ異なる特性（共振周波数又は静電容量等）を有する。

30

## 【0048】

直列共振部の前後に、回路ノードS\_Kを備えることができる。回路ノードS\_Kには、他の要素、フィルター分岐、又は信号経路を接続することができる。図1Aにおいて、第一並列分岐P\_Z\_1は、第一回路ノードS\_K\_1から分岐し、第一回路ノードS\_K\_1と固定電位とを接続する。ここでは、固定電位はフレーム電位である。第一並列分岐P\_Z\_1に、第一並列共振部R\_P\_1が配置されている。第一並列分岐P\_Z\_1は、任意選択により、直列接続されたm個の他の並列共振部R\_P\_Xに直列接続されている。値mは、nとは独立して選択され、同様の値をとることができる。これらの並列共振部により、回路構成V\_R\_P\_1が形成される。第一コンデンサーK\_1は、並列共振部と固定電位との相互接続部に直列接続されている。共振部R\_P\_Xの特性（共振周波数又は静電容量等）は互いに異なり、R\_S\_Xの特性とも異なる。

40

## 【0049】

50

任意選択により、信号線 S L に追加の受動素子を一体化又は接続することができる。例えば、フィルターポート F P 1 と第一回路ノード S K 1との間に、直列インダクタンス L S を一体化させることができる。あるいは、第一フィルターポート F P 1 と第一共振部 R S 1との間の回路ノードから、並列コイル L P をグランドに接続することができる。

【 0 0 5 0 】

追加の直列コイル L S 及び / 又は追加の並列コイル L P は、第二フィルターポート F P 2 側に備えることができる。

【 0 0 5 1 】

指標 n 及び m は回路のカスケード率を決定するものである。そのため、1 ~ 約 10 の整数値をとる。原理上、指標 n 及び m は大きな値をとることができる。ただし、そのような高いカスケード率が、フィルター回路に必要な面という理由により経済的に又は技術的に意味を為さない場合は、n 及び m は互いに異なるように選択することができる。図 1 A には、信号線 S L 内の他の回路ノードによってグランドに接続され得る追加の並列分岐は、示されていない。また、直列共振部の追加の回路を、2 つのそのような回路ノード S K の間に備えることができる。

10

【 0 0 5 2 】

第一コンデンサー K 1 のないフィルター回路と比較すると、図 1 A のフィルター回路を使用することにより、特定の相互変調積を約 10 dB 低減、又は、約 10 dB 改善することができる。図 1 A 及び後出の図では、フィルター回路内に存在し得る追加の要素（特に、追加の並列分岐、追加の共振部、又は直列共振部の追加の回路構成）が省略されている。直列及び / 又は並列インダクタンスを、信号線に備える又は連結することができる。

20

【 0 0 5 3 】

図 1 B は、他の典型的な実施形態を示している。図 1 A と比較すると、図 1 B の実施形態では、第一コンデンサー K 1 は、並列共振部 V R P 1 の回路に直列接続されておらず、第一並列分岐 P Z 1 内でこの回路に並列接続されている。そのため、並列接続されたこの第一コンデンサー K 1 により、信号線内の回路ノードと固定電位とが接続されている。この実施形態においても、相互変調積を最大 10 dB 低減することができる。

【 0 0 5 4 】

図 1 C は、本発明の追加の実施形態を示している。図 1 C は、図 1 A に類似するように設計されている。ただし、この場合、第二コンデンサー K 2 は、第一並列分岐 P Z 1 が分岐する第一回路ノード S K 1 と、直列共振部 V R S 1 の第一回路構成との間で、直列分岐 S L 内で相互接続されている。このように第二コンデンサー K 2 が信号線において分圧部として機能している場合でも、同じ数の共振部 R S 、 R P を有するがコンデンサーを有しない公知のフィルター回路と比べて、フィルター回路の線形性は向上する。また、図 1 A 及び図 1 B を参照して説明した拡張の可能性は、この構造にも当てはまる。

30

【 0 0 5 5 】

図 1 D は、図 1 C に類似の実施形態を示している。図 1 D では、信号線 S L 内の第一回路ノード S K 1 が第一共振部 R S 1 又は直列共振部 V R S 1 の第一回路構成の後方に配置され、第二コンデンサー K 2 が第一共振部 R S 1 又は第一回路構成 V R S と第一フィルターポート F P 1との間に備えられている。第一回路ノード S K 1 と第二フィルターポート F P 2との間には、直列共振部の追加の回路構成 V R S を備えることができる。また、追加の並列分岐が接続された追加の回路ノード S K を備えることができる。更に、別の直列の第二コンデンサー K 2 を、各 2 つの回路ノードの間に備えることができる。固定電位と並列共振部の回路構成との間に配置されるように、追加の第一コンデンサー K 1 を各並列分岐に追加的に備えることができる。

40

【 0 0 5 6 】

図 1 E は、図 1 D に類似のフィルター回路を示している。ここで、第二コンデンサー K 2 は、第一回路構成 V R S 又は直列共振部 V R S に並列に配置されている。第一回路ノード S K 1 に接続された第一並列分岐 P Z は、並列共振部の回路構成 V R P 1 を有する。直列共振部 V R S 1 の第一回路と第二フィルターポート F P 2との間には、直列共振部 V R

50

S の追加の回路構成を少なくとも 1 つ備えることができる。直列共振部 V R の回路構成の両側で、並列分岐が各回路ノード S K に接続し得る。

【 0 0 5 7 】

第二コンデンサー K 2 が直列信号線において分圧を行う本実施形態においても、フィルター回路の線形性が向上し、相互変調積 / 高調波の出現が低減される。

【 0 0 5 8 】

図 2 は、第一コンデンサー K 1 が並列共振部 V R P の回路構成に並列接続され、かつ、第二コンデンサー K 2 が直列共振部 V R S の回路構成に並列接続された、フィルター回路を示している。信号線 V R S 1 内の直列共振部の回路構成及び第一並列分岐 P Z 1 内の並列共振部 S R P の回路構成は、それぞれコンデンサー K 1、K 2 でブリッジされている。

10

【 0 0 5 9 】

図 3 は、信号線 S L に備えられた第二コンデンサー K 2 及び第一並列分岐 P Z 1 に並列接続された第一コンデンサー K 1 が相互接続されている実施形態を示している。フィルター回路は、追加の直列共振部又は直列共振部の追加の回路構成、及び追加の共振部又は並列共振部の追加の回路構成が配置されている追加の並列分岐を含み得る。

【 0 0 6 0 】

図 4 は、図 3 に類似のフィルター回路を示している。ただし、第一コンデンサー K 1 は、並列共振部 R P 又は並列共振部 V R P の回路構成に並列に配置されている。

【 0 0 6 1 】

図 5 は、図 4 に類似のフィルター回路を示している。ただし、第一コンデンサー K 1 は、並列共振部 R P 又は並列共振部 V R P の回路構成に直列に配置されている。

20

【 0 0 6 2 】

図示されていない実施形態では、フィルター回路は並列分岐から始まる。一方、図 1 D ~ 図 6 では全て直列共振部又は直列共振部の回路構成から始まる。「から始まる」とは、入力として機能するフィルターポートの最も近くに配置されている共振部のことを意味する。

【 0 0 6 3 】

図 6 は、信号線 S L 内に直列共振部 V R S の回路構成が 3 つ配置されたフィルター回路を示している。このような回路構成 2 つ毎に、回路ノード S K が備えられ、その間に配置されている。この各回路ノード S K から、いずれの場合にも、並列分岐 P Z には対応する並列共振部 V R P の回路構成が備えられている。

30

【 0 0 6 4 】

第二コンデンサー K 2 が、各フィルター入力と直列共振部の第一回路構成との間と、直列共振部の第一回路構成と第二回路構成との間と、直列共振部の第二回路構成と第三回路構成との間に備えられている。

【 0 0 6 5 】

対応する並列共振部の回路構成を有する並列分岐 P Z は、共振部 V R S の各 2 つの直列回路構成の間ににおいて、グランドに向かって延びている。

【 0 0 6 6 】

直列共振部 V R S の回路構成のカスケード率を示す指標 n、o、p は個別に選択され、1 ~ 10 の値をとることができる。並列共振部 V R P の回路構成のカスケード率を特定する指標 m、k も、1 ~ 10 の値をとることができる。インターバルの下側領域における直列の回路構成及び並列の回路構成のカスケード率は、好ましくは適切な各指標が 1 ~ 7 の値を有するように、より好ましくは 1 ~ 5 の値を有するように選択される。

40

【 0 0 6 7 】

図 7 は、特定の回路環境又はある実際のシステム要件に応じて設計され、かつ、相互変調積を最大限低減させるために設計された、実際のフィルター回路を図示している。ここで、直列信号線 S L は、例えば、3 つの回路ノード S K 1、S K 2、S K 3 を有している。この 3 つの回路ノード S K 1、S K 2、S K 3 からは、それぞれ、並列分岐 P Z がグランドに向かって分岐している。また、D M S フィルター D M S が、第三並列分岐の後方で

50

信号線に直列接続されている。

【0068】

第二回路ノードSK2と第三回路ノードSK3との間には、直列共振部の第二直列回路構成VRS2が配置されている。DMSフィルターDMSと第二フィルターポートFP2との間には、非カスケード直列共振部RS1が備えられている。

【0069】

このようなフィルター回路は、例えば、公称通過帯域2620MHz～2630MHzに対応するように設計されている。フィルター回路の一部である本発明のこのフィルターと、既知の技術によって構成されているが本発明のフィルターに可能な限り類似させたフィルターとを比較するために、7個の相互接続された並列共振部を有する第一並列分岐と、直列共振部の二重カスケード回路構成と、2個の並列共振部を有する第二並列分岐と、直列共振部と、DMSフィルターと、追加の直列共振部と、2個の並列共振部の二重カスケード回路構成とを含む参照用フィルターが設計された。

10

【0070】

図7に示す本発明のフィルターと上述の参照用フィルターとを比較すると、通過帯域の位置と帯域幅が、両フィルターで同じであることが分かった。本発明のフィルターにおいては、通過帯域における挿入損失に関する劣化が最小限であり、阻止帯域付近における劣化減衰もわずかである。定在波比VSWRを示すマトリクスパラメータS11及びS22でさえも、劣化がわずかな値を示す。

【0071】

20

参照用フィルターにおいて周波数2690MHzで発生する破壊的な三次相互変調積は、本発明のフィルターにおいては低減されており、その低減の程度は10dBを超える。フィルター特性の実質的な変更やわずかな劣化もなく、相互変調積の抑制による改善が顕著であったことから、本発明により得られるメリットが明らかとなった。本発明の成果は、次の点でも見られる。本発明のようにコンデンサーが接続されていない既知の技術のフィルターにおいて、相互変調積を同様に低減するためには、第一並列共振部のカスケード率は13とされる。このような高いカスケード率では、追加で必要となる面が大きすぎるため、問題外である。そのため、現実的な用途から除外される。本発明を利用することにより、非常に小さい面において同じ結果を得ることができる。

【0072】

30

図8は、図7に示すフィルターを使用して、破壊的な相互変調積の発生又は消滅をどのように実証することができるかを示す。このために、例えば、図7のフィルターの入力に、特定の周波数範囲f1及び10dBmの強さの第一干渉音が加えられる。第二干渉周波数は、2500MHz～2570MHzの周波数範囲f2で変化して、フィルター入力に同様に加えられる。この第二干渉信号の強さは、5dBmである。

【0073】

典型的なシステム要件によると、三次相互変調積の評価は、一定の周波数 $f_{IMD} = 2690\text{MHz} = 2 * f_2 - f_1$ で行わなければならない。図8に、この方法を使用して図7のフィルターで測定された第一グラフG1を示す。第二グラフG2は、同じ方法でテストされた比較用フィルターを示す。ただし、比較用フィルターは、第一並列分岐に第一コンデンサーがない状態で実施されている。図8では、周波数に対して、対応する三次相互変調積の減衰がプロットされている。

40

【0074】

図8を参照すると、第二グラフG2と比べて、本発明のフィルターのグラフG1では、特に相互変調積が最大となる臨界周波数2570MHzにおいて、発生する相互変調積に対する抑制が約10dB向上していることが分かる。第三グラフG3は、第一並列分岐に第一コンデンサーがない状態で実施されているフィルター構成の性能を示している。ただし、このフィルター構成においては、カスケード接続された並列共振部の数が、上述の周波数2570において相互変調積を同じように抑制できる数まで増加されている。これは、カスケード率が13のときにのみ可能であり、つまり、13個の並列共振部の回路構成

50

であることを意味する。

【0075】

これは、第一並列分岐に4個のカスケード接続された並列共振部を有する本発明のフィルターと比較して、必要なフィルター面が大幅に減少することを意味する。上述した参照用フィルターの相対音響空間要件は、1.0である。本発明のフィルターの相対音響空間要件は、1.6である。一方、カスケード率13を有するフィルター（図8中のグラフG3に対応）の相対音響空間要件は、2.8である。これは、上述の本発明のフィルターと比較すると、1.8倍増加した相対音響空間要件に対応する。あるいは、言い換えると、本発明によれば、対象の $f_{IMD}$ において同じ抑制を行うと、音響空間要件を1.8倍削減することができる。

10

【0076】

フィルター回路に、2つより多い強い干渉信号が発生することが考えられる。スマートフォンの4つの異なる周波数（2×セル方式、2×WLAN）で最大4つの同時発生的な強い伝送信号が予想される方向において、標準化が行われている。その結果、周波数が受信帯域内に位置する、複数の可能な追加の非線形混合物が発生し得る。これにより、受信感度が著しく減少する。この複数の可能な追加の非線形混合物についても、本発明によれば大幅に低減することができる。これにより、これらのあらゆる場合において、受信感度が向上したフィルターが提供される。

【0077】

最初に説明した通り、カスケード率を変更した場合、カスケード接続された共振部の静電容量を調整してバランスをとる必要がある。図7に示すような、第一並列分岐において直列接続された4個の共振部及び第一コンデンサーK1を有する本発明のフィルターの場合、直列又は並列共振部の直列回路構成（カスケード）における全ての共振部が、同じ静電容量 $C_{S,R}$ を有することで可能となり、好ましい。

20

【0078】

通例、m個の共振部がカスケード接続されている場合、このカスケードの総静電容量 $C_{S,R,ges}$ は、 $C_{S,R,ges} = C_{S,R} / m$ となる。このカスケードに直列接続されたコンデンサーKは、以下の容量 $C_K$ を有する。

$$C_K = a * C_{S,R,ges}$$

このとき、1以上の量が選択されるものとする。

30

カスケード及びコンデンサーからの容量 $C_{S,gesamt}$ は、以下で表される。

$$C_{S,gesamt} = C_K / (a + 1)$$

それぞれが静電容量 $C_{S,R}$ を有するm個の共振部のカスケードにコンデンサーが並列接続されている実施形態では、このカスケードの総静電容量は、 $C_{S,R} / m$ で $C_{S,R,ges}$ となる。

【0079】

このカスケードに並列接続されたコンデンサーKは、容量 $C_K = b * C_{S,R,ges} = b / m * C_{S,R}$ を有する。このとき、bも、1以上の値が選択されるものとする。

【0080】

カスケード及びこのカスケードに並列なコンデンサーによる容量 $C_{S,gesamt}$ は、以下で表される。

$$C_{S,gesamt} = C_K * (1 + b) / b$$

【0081】

本発明のフィルターにおける容量を測定するために、異なった好ましい測定方法が適用される2つの一般的な場合AとBとに区別することができる。

【0082】

場合Aでは、フィルターは、カスケードVRS接続された直列共振部及びこの直列共振部に直列又は並列接続された第二コンデンサーK2から始まる。後続の第一並列分岐PZ1にも、第一コンデンサーK1に直列又は並列接続された共振部のカスケードVRP1が含まれる。直列分岐には、カスケードVRS2接続された追加の直列共振部が存在する。

50

少なくとも 1 つの追加の並列分岐 P Z が、共振部の追加のカスケード V R P 2 を含む。

【 0 0 8 3 】

ラダー型フィルター又はサブフィルターの全ての並列分岐の総容量は、接続されているコンデンサーの有無に関わらず、ほぼ同じサイズとなるように選択されなければならない。ただし、第二フィルターポート F P 2 における最後の並列分岐又はフィルター出力に限っては例外である。最後の並列分岐は、最終の並列分岐であり得る。直列分岐では、これ以上音響要素が（信号方向に）後続することはない。

【 0 0 8 4 】

前記コンデンサーを含む第二コンデンサーに接続された直列共振部の第一カスケードの総容量は、直列分岐における追加のカスケード V R S 2 の総容量の約 2 倍となるように計算することが好ましい。ただし、第二フィルターポート F P 2 の最後の直列共振部又はフィルター出力に限っては例外である。最後の直列共振部は、最終の直列共振部であり得る。並列分岐では、これ以上音響要素が（信号方向に）後続することはない。

10

【 0 0 8 5 】

場合 B では、フィルターは、第一コンデンサー K 1 に直列又は並列接続された共振部のカスケード V R P 1 を含む並列分岐から始まる。この後方に、直列分岐において、カスケード V R S 接続された直列共振部及びこの直列共振部に直列又は並列接続されたコンデンサー K 2 が続く。直列分岐には、カスケード V R S 2 接続された追加の直列共振部も存在する。少なくとも 1 つの追加の並列分岐 P Z が、共振部のカスケード V R P 2 を含む。

20

【 0 0 8 6 】

この場合、ラダー型フィルター又はサブフィルターの全てのカスケードの総容量（第二コンデンサーの有無に関わらず）がほぼ同じサイズとなるように選択されなければならない。ただし、第二フィルターポート F P 2 の最後又は最終の直列共振部又はフィルター出力に限っては例外である。第一コンデンサー（コンデンサー K 1 を含む）に接続された並列共振部の第一カスケード V R P 1 の総容量は、並列分岐における追加のカスケード V R P 2 の総容量の約半分となるように計算することが好ましい。ただし、第二フィルターポート F P 2 の最後の又は最終の並列分岐又はフィルター出力に限っては例外である。

以下に本願の出願当初の特許請求の範囲に記載された発明を付記する。

【 C 1 】

第一フィルター（ F 1 ）を含むフィルター回路であって、

30

- 直列信号経路（ S L ）により第一フィルターポート（ I N ）と第二フィルターポート（ O U T ）とが接続されており、

- 回路ノード（ S K ）が直列信号経路内に配置され、前記回路ノード（ S K ）はそれぞれ並列分岐（ P Z ）を介して固定電位に接続されており、

- 共振部（ R S 、 R P ）又は共振部の回路構成（ V R S 、 V R P ）が、直列分岐及び前記並列分岐に配置されており、

- 前記フィルター入力（ I N ）の最も近くに配置された第一並列分岐（ P Z 1 ）は、並列共振部又は直列接続された複数の並列共振部の回路構成を含み、

- 第一直列共振部、又は直列接続された複数の共振部の第一回路構成が、信号経路（ S P ）内に含まれ、かつ、前記フィルター入力（ I N ）の最も近くに配置されており、

40

- 第一コンデンサー（ K 1 ）が、前記第一並列分岐（ P Z 1 ）に直列又は並列接続されている、及び / 又は、第二コンデンサー（ K 2 ）が、前記第一直列共振部、又は直列接続されている複数の共振部の前記第一回路構成に直列又は並列接続されている、フィルター回路。

【 C 2 】

前記共振部は、音波によって動作する共振部として設計されている、【 C 1 】に記載のフィルター回路。

【 C 3 】

前記第一並列分岐における共振部の回路構成は、1 個 ~ 8 個の直列の共振部の回路構成を含む、【 C 1 】又は【 C 2 】に記載のフィルター回路。

50

## [ C 4 ]

第二コンデンサー (K 2) は、前記第一直列共振部又は直列共振部の第一回路構成 (V R S 1) と前記第一フィルターポート (F P 1)との間ににおいて、直列信号経路に接続されている、又は、直列信号経路に並列にされており、

第一コンデンサー (K 1) は、前記第一並列共振部 (R P 1)、又は前記第一並列分岐 (P Z 1) における並列共振部の第一回路構成 (V R P 1) に直列又は並列接続されている、[ C 1 ] ~ [ C 3 ] のいずれか一項に記載のフィルターレート。

## [ C 5 ]

前記第一フィルター (F 1) は送信フィルター又は受信フィルターであり、

前記フィルターレートは、第一又は第二フィルターポート (F P 1、F P 2) に連結された 1 つ以上の受信分岐又は送信分岐を追加的に含み、前記送信分岐は異なる送信周波数帯域で送信を行うように設計され、前記受信分岐は異なる受信周波数帯域で受信を行うように設計されている、[ C 1 ] ~ [ C 4 ] のいずれか一項に記載のフィルターレート。

10

## [ C 6 ]

前記第一フィルター (F 1) は、送受切換器の受信フィルター又は送信フィルターである、[ C 1 ] ~ [ C 5 ] のいずれか一項に記載のフィルターレート。

## [ C 7 ]

- 前記フィルターは、第二コンデンサー (K 2) が直列又は並列接続された直列共振部又は直列共振部 (R S) の回路構成 (V R S 1) から始まり、

- 並列共振部の回路構成及びこの回路構成に並列又は直列接続されたコンデンサーの回路構成の容量の結果として、並列分岐はそれぞれ同じ総容量を有しております、

20

- 前記信号線における最後又は最終の並列分岐は、前記総容量に関するこの規定から除外される、[ C 1 ] ~ [ C 6 ] のいずれか一項に記載のフィルターレート。

## [ C 8 ]

- 前記フィルターは第一並列分岐 (P Z 1) から始まり、前記第一並列分岐 (P Z 1)においては、並列共振部又は並列共振部の回路構成 (V R P 1) が第一コンデンサー (K 1) に直列又は並列接続されており、

- 直列共振部の回路構成及びこの回路構成に並列又は直列接続された第二コンデンサー (K 2) の容量の結果として、直列共振部又は直列共振部 (R S) の回路構成 (V R S) はそれぞれ同一の総容量を有しております、

30

- 前記信号経路における最後又は最終の直列共振部、又は直列共振部の最後又は最終の回路構成は、前記総容量に関するこの規定から除外される、[ C 1 ] ~ [ C 6 ] のいずれか一項に記載のフィルターレート。

## [ C 9 ]

第二コンデンサー (K 2) は、いずれの場合にも、前記第一共振部の前、前記最後の共振部の後、及び信号経路 (S L) に配置された全ての共振部の間に配置されている、[ C 1 ] ~ [ C 8 ] のいずれか一項に記載のフィルターレート。

## [ C 10 ]

前記信号経路 (S L) には、D M S フィルター (D M S) が直列接続されている、[ C 1 ] ~ [ C 9 ] のいずれか一項に記載のフィルターレート。

40

## [ C 11 ]

前記フィルターレートはチップ部品として設計されており、

- 前記共振部が、S A W シングルポート共振部として設計されており、

- 前記共振部が、1 つの共通のチップ上に配置されており、

- 前記チップ上の第一及び / 又は第二コンデンサー (K 1、K 2) は平板コンデンサーとして実現されており、前記平板コンデンサーは 2 つの平板コンデンサー電極を有し、前記 2 つの平板コンデンサー電極は、前記 2 つの平板コンデンサー電極の間に配置されたスリップ導体及び誘電体層に対向しており、

- 前記誘電体層と、前記チップ部品の追加の機能層とは、1 つの製造工程で作成され、同じ材料及び同じ層厚を有しております、

50

- 前記コンデンサーの下部電極は、前記シングルポート共振部のメタライゼーションにより形成され、

- 前記コンデンサーの上部電極は、前記フィルターの端子パッド上に作成されるパッドの肥厚化により形成される、[ C 1 ] ~ [ C 10 ] のいずれか一項に記載のフィルター回路。

[ C 12 ]

- 前記コンデンサー電極の間の前記誘電体層は、前記フィルター回路の交差するストリップ導体部分間の絶縁に使用される絶縁層と共に作成される、[ C 11 ] に記載のフィルター回路。

[ C 13 ]

- 前記コンデンサー電極間の面全体に形成された層は、機械特性、特に剛化性について温度係数が正である材料を有する前記フィルター回路の温度係数を最小化する誘電体層として機能し、コンデンサーの領域では、前記上部コンデンサー電極が、前記コンデンサーの領域内の前記誘電体層に追加的に形成されている、[ C 11 ] に記載のフィルター回路。

[ C 14 ]

コンデンサーは、前記第一フィルターを有する前記チップのラダー型回路として設計されておらず、L T C C に一体化されている、又は、外部のディスクリートコンデンサーとして積層体に一体化されている、[ C 1 ] ~ [ C 10 ] のいずれか一項に記載のフィルター回路。

[ C 15 ]

共振部構成には、複数のカスケード接続された共振部が含まれており、

前記フィルター回路内の前記共振部のカスケード率は、前記フィルター入力からの距離が増加するにつれ減少する、[ C 1 ] ~ [ C 14 ] のいずれか一項に記載のフィルター回路。

【 0087 】

用語と符号のリスト

F 1 第一フィルター

F P 1 第一フィルターポート、フィルター入力 ( 一例 )

F P 2 第二フィルターポート、フィルター出力 ( 一例 )

30

G 1 第一グラフ

G 2 第二グラフ

G 3 第三グラフ

K 1 第一コンデンサー ( 並列分岐内 )

K 2 第二コンデンサー ( 直列信号経路内 )

L P インダクタンス ( 並列分岐内 )

L S インダクタンス ( 信号経路内 )

P Z 並列分岐

R P 共振部 ( 並列分岐内 )

R S 共振部 ( 直列信号経路内 )

40

S K 回路ノード ( 直列分岐内、被接続側 )

S L 直列信号経路 ( 接続側 )

V R P 共振部の回路構成 ( 並列分岐内 )

V R S 共振部の回路構成 ( 信号経路内 )

【図1A】

【 図 1 B 】

【図1C】

### 【図1D】

【図1E】

【図2】

【 図 3 】

【 図 4 】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

(72)発明者 フレイスレベン、シュテファン

ドイツ連邦共和国、85579 ノイビーベルク、ユニヴェルジーツシュトラーセ 35

審査官 石田 昌敏

(56)参考文献 特開2014-143675 (JP, A)

特開2009-239963 (JP, A)

国際公開第2005/088836 (WO, A1)

特表2012-506185 (JP, A)

特開平08-065089 (JP, A)

特開2010-109694 (JP, A)

国際公開第2004/112246 (WO, A1)

(58)調査した分野(Int.Cl., DB名)

H03H 9/00 - 9/76

H03H 5/00 - 7/13