(12)

DEMANDE DE BREVET D'INVENTION

A1

(22) Date de dépôt : 04.01.91.

(30) Priorité : 04.09.90 KR 9013935.

(71) Demandeur(s) : Société dite: SAMSUNG

ELECTRONICS CO., LTD — KR.

(43) Date de la mise à disposition du public de la

demande : 06.03.92 Bulletin 92/10.

(56) Liste des documents cités dans le rapport de

recherche : Le rapport de recherche n'a pas été

établi à la date de publication de la demande.

(60) Références à d'autres documents nationaux

apparentés :

(72) Inventeur(s) : Kim Kyouchul et Youn Jongmil.

(73) Titulaire(s) :

(74) Mandataire : Cabinet Lavoix.

(54) Procédé pour fabriquer un transistor bipolaire à émetteurs multiples.

(57) Selon ce procédé, après avoir formé une couche en-sévelie (5) et une couche épitaxiale (6) sur un substrat en Si (1), une région de puits (10), une couche d'oxyde de champ (14) et une couche de diffusion de collecteur (17), une couche de base et une couche d'oxyde (21), on aménage une fenêtre dans cette couche d'oxyde et on forme une structure multiple formée d'une couche de polysilicium en formant une région de base (27) et une région d'émetteur en faisant diffuser des impuretés implantées par implantation ionique, et on forme une couche d'oxyde (30), dans laquelle on aménage des fenêtres par corrosion pour insérer une structure d'électrodes métalliques (32).

Application notamment à la fabrication de transistors bipolaires dans des circuits CMOS.

La présente invention concerne un procédé pour fabriquer un transistor bipolaire à émetteurs multiples possédant une faible résistance et plus particulièrement un procédé pour réduire la valeur résistive élevée que l'on obtient lors de la formation des émetteurs multiples.

L'émetteur en polysilicium est largement utilisé dans les transistors bipolaires à hautes performances et fonctionnant à grande vitesse, ainsi que dans des dispositifs BI-CMOS.

10 Pour fabriquer un transistor bipolaire possédant une structure à émetteurs multiples, on élimine la couche d'oxyde formée sur un substrat en silicium monocristallin de manière à mettre en contact une couche de polysilicium servant à former une électrode en contact avec le substrat, 15 puis à déposer la couche de polysilicium. Mais, dans ce cas, il se pose deux problèmes que l'on rencontre lors de la suppression de la couche d'oxyde et du dépôt de la couche de polysilicium.

Tout d'abord, le problème qui se présente lors de 20 l'élimination de la couche d'oxyde formée sur le substrat en Si monocristallin, est qu'on élimine la couche d'oxyde par corrosion ionique réactive et que, de ce fait, la surface du substrat est endommagée, ce qui accroît la résistance d'émetteur.

25 Ci-après, on va considérer le problème que l'on rencontre lors du dépôt du polysilicium sur le substrat, après suppression de la couche d'oxyde.

Le dépôt de la couche de polysilicium est obtenu 30 au moyen d'un procédé de dépôt classique ou procédé de dépôt en rampe.

#### 1. Procédé classique

Le procédé classique consiste à placer la pastille dans un tube à une température de 600-650°C pour le dépôt du polysilicium. Dans ce cas, on obtient une croissance de la couche d'oxyde sur le substrat en Si mono-

cristallin, en raison de la température élevée du tube lors de l'insertion dans ce dernier. Par conséquent, bien que la couche d'oxyde ait été éliminée du substrat lors de l'étape précédente, l'étape ultérieure de traitement pour le dépôt de polysilicium entraîne la croissance d'une couche d'oxyde sur le substrat en empêchant l'établissement du contact de la couche de polysilicium avec ce substrat.

En outre, la couche d'oxyde formée entre la couche de polysilicium et le substrat entraîne un accroissement de la résistance d'émetteur, de sorte qu'une caractéristique du transistor, comme par exemple une faible vitesse de fonctionnement ou une faible transconductance, s'en trouve altérée.

D'autre part, pour éliminer la couche d'oxyde formée pendant le dépôt du polysilicium, il est nécessaire d'appliquer un traitement thermique séparé à une température élevée dépassant 900°C, mettant en oeuvre une étape de traitement thermique en utilisant un tube de diffusion, une étape de recuit thermique rapide, etc.

Cependant, le traitement thermique utilisant le tube de diffusion entraîne une altération de la performance du dispositif en raison de l'énergie thermique produite lors du traitement de longue durée à haute température, tandis que le recuit thermique rapide réduit l'uniformité et la productivité du processus bien que l'énergie thermique appliquée au dispositif soit faible en raison de la brève durée de traitement.

## 2. Dépôt en rampe

Il s'agit d'un procédé récemment utilisé pour empêcher la croissance de la couche d'oxyde pendant l'insertion de la pastille dans un tube de diffusion à haute température. La température du tube est maintenue à la température ambiante lorsque la pastille est introduite dans le tube de diffusion du polysilicium.

On augmente la température jusqu'à un niveau de

600-650°C de manière à déposer du polysilicium une fois que la pastille a été complètement insérée dans le tube. Cependant, dans ce procédé il se pose un problème lié à la productivité en raison de l'accroissement de la température 5 d'un niveau bas à un niveau élevé.

La présente invention a pour but de fournir un procédé pour fabriquer un transistor bipolaire à émetteurs multiples, qui permette de réduire la résistance d'émetteur moyennant une corrosion de la couche d'oxyde présente sur 10 le substrat en silicium monocristallin, avant le dépôt de la couche de silicium, puis en réalisant la corrosion à sec du substrat en silicium monocristallin endommagé lors de la corrosion de la couche d'oxyde, au moyen du procédé de dépôt chimique en phase vapeur CVD amélioré par un plasma.

15 Un autre but de la présente invention est de fournir un procédé permettant de fabriquer un transistor bipolaire à émetteurs multiples, qui permette de réduire la résistance d'émetteur moyennant le maintien de la température dans un tube de dépôt à un faible niveau au moyen du 20 dépôt en rampe, lors de la mise en place de la pastille dans le tube, et au moyen du dépôt d'une couche de polysilicium à une température accrue de dépôt convenant pour la couche de polysilicium une fois que la pastille a été complètement introduite pour supprimer la croissance de la 25 couche d'oxyde.

Conformément à la présente invention, il est prévu un procédé pour fabriquer un transistor bipolaire possédant une faible résistance d'émetteur, incluant les étapes consistant à :

30 former une couche ensevelie de type  $N^+$  et une couche épitaxiale de type N dans un substrat en Si;

former un puits de type N pour la région dudit transistor bipolaire en exécutant une implantation ionique d'une impureté du type N dans la couche épitaxiale;

35 former une couche d'oxyde de champ au moyen d'une

- oxydation classique;

- former une couche de diffusion de type N+ dans une région de collecteur;

- former par implantation ionique une couche pour une région de base en exécutant l'implantation ionique d'une impureté de type P ;

- déposer une couche d'oxyde;

- former une fenêtre de contact en corrodant l'oxyde;

- 10 former une structure multiple par structuration après dépôt d'une couche de polysilicium au moyen du procédé de dépôt en rampe;

- exécuter une implantation ionique dans le substrat de manière à former une région d'émetteur;

- 15 former la région de base et la région d'émetteur au moyen d'une diffusion simultanée des impuretés implantées par implantation ionique;

- former une couche d'oxyde et une couche de verre au silicate de bore et de phosphore BPSG;

- 20 ménager une fenêtre pour contact métallique en corrodant séquentiellement la couche de BPSG et la couche d'oxyde par photolithographie; et

- former une structure d'électrodes métalliques en déposant une couche métallique et en la structurant.

- 25 Conformément à un aspect de la présente invention, l'étape de formation de la fenêtre de contact pour la mise en contact de la couche de polysilicium avec le substrat en Si monocristallin inclut les étapes partielles consistant à :

- 30 déposer une résine photosensible sur la couche d'oxyde;

- mettre à nu une partie du substrat pour former une fenêtre de contact en corrodant ladite résine photosensible par photolithographie;

- 35 corroder la couche d'oxyde au moyen d'une corro-

sion ionique réactive; et

corroder, au moyen du procédé CVD amélioré avec un plasma, le substrat en silicium monocristallin endommagé pendant la corrosion de la couche d'oxyde.

5 Selon un autre aspect de la présente invention, lors du dépôt du polysilicium, on maintient la température d'un tube de dépôt à une valeur aussi faible qu'environ 400°C pendant l'insertion de la pastille dans le tube, puis, une fois que la pastille a été complètement insérée 10 dans le tube, on augmente graduellement la température pour l'amener au niveau de la température normale de dépôt du polysilicium.

D'autres caractéristiques et avantages de la présente invention ressortiront de la description détaillée 15 donnée ci-après, prise en référence aux dessins annexés, sur lesquels :

- les figures 1A-1N illustrent le procédé conforme à l'invention pour fabriquer un transistor bipolaire à émetteurs multiples possédant une faible résistance 20 d'émetteur.

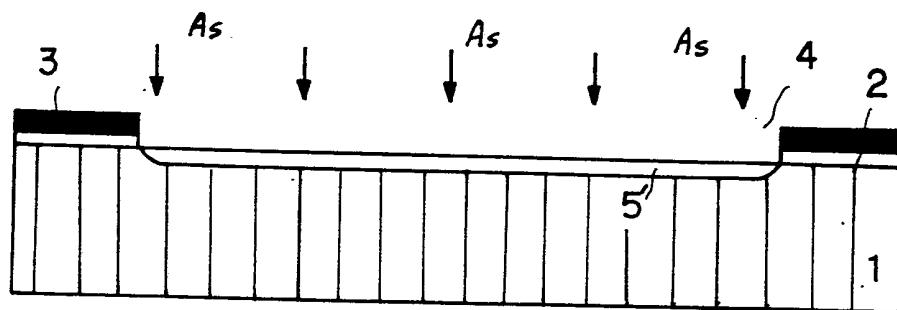

En se référant à la figure 1A illustrant la formation d'une couche ensevelie, le matériau de départ est un substrat 1 en Si de type P, possédant une résistance spécifique égale à  $5 \Omega \cdot \text{cm}$  et un plan cristallin (100). Sur le 25 substrat 1, on dépose successivement une première couche d'oxyde 2 et une couche de nitrure 3. Puis on applique une résine photosensible sur la couche de nitrure 3, et on soumet le substrat au procédé de photolithographie de manière à former une fenêtre 4 pour implantation ionique. On 30 plante alors une impureté de type N formée par du As, au moyen de cette fenêtre 4, à une dose égale à  $5 \times 10^{15}$  ions/cm<sup>2</sup> pour former une couche 5' formée par implantation ionique, pour une couche ensevelie de type N+. Puis on élimine la résine photosensible.

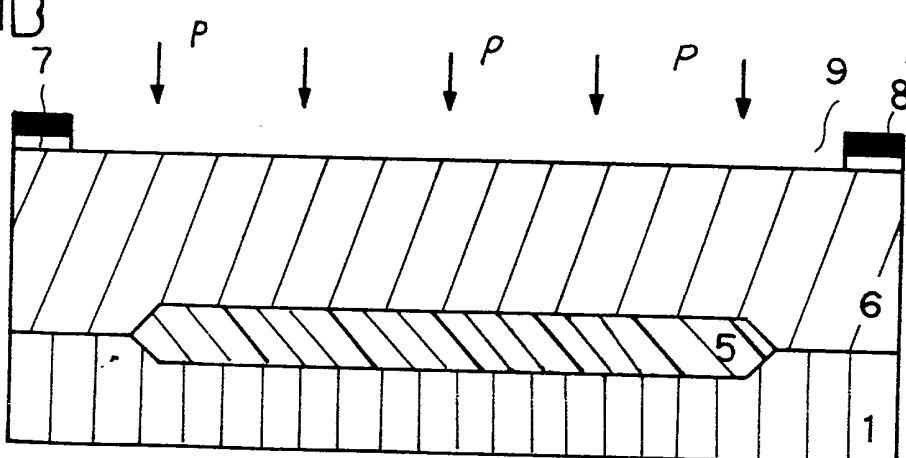

35 En se référant à la figure 1B, les ions implantés

sont activés selon un procédé d'oxydation classique pour former la couche ensevelie 5 de type N+. Puis on retire par décollement la première couche d'oxyde de la couche de nitrure 3, et on fait croître sur le substrat une couche épitaxiale 6 possédant une épaisseur d'environ 1,5  $\mu\text{m}$ .

Ensuite, sur la couche épitaxiale 6, on dépose successivement une seconde couche d'oxyde 7 et une couche de nitrure 8, et on dépose une résine photosensible sur la couche de nitrure. On soumet le substrat au procédé de photolithographie pour former une fenêtre 9 pour l'implantation ionique de manière à former une région de collecteur.

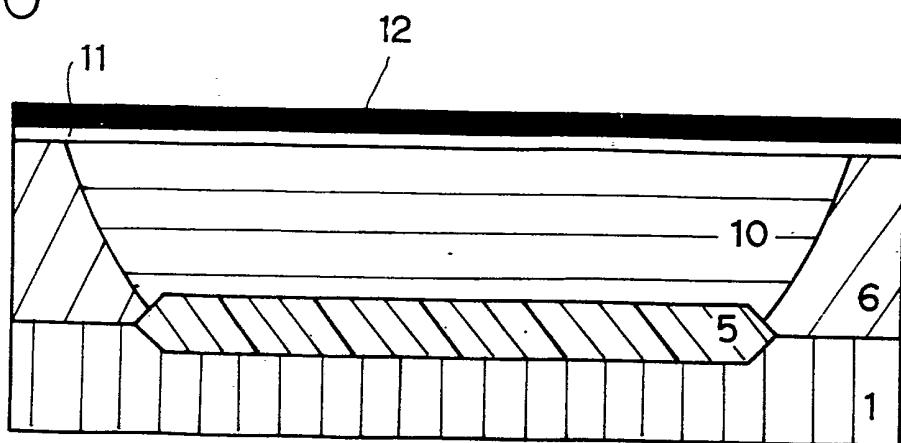

Puis on implante une impureté de type N formée par des ions de phosphore (P), à travers la fenêtre 9, à une dose comprise entre  $1 \times 10^6$  et  $3 \times 10^{12}$  ions/cm<sup>2</sup>, à former un puits 10 de type N, dans lequel un transistor bipolaire est formé, comme cela est représenté sur la figure 1C. Ensuite, on élimine la résine photosensible appliquée pour former la fenêtre 9, et on forme successivement une troisième couche d'oxyde 11 et une couche de nitrure 12 pour former une couche d'oxyde de champ.

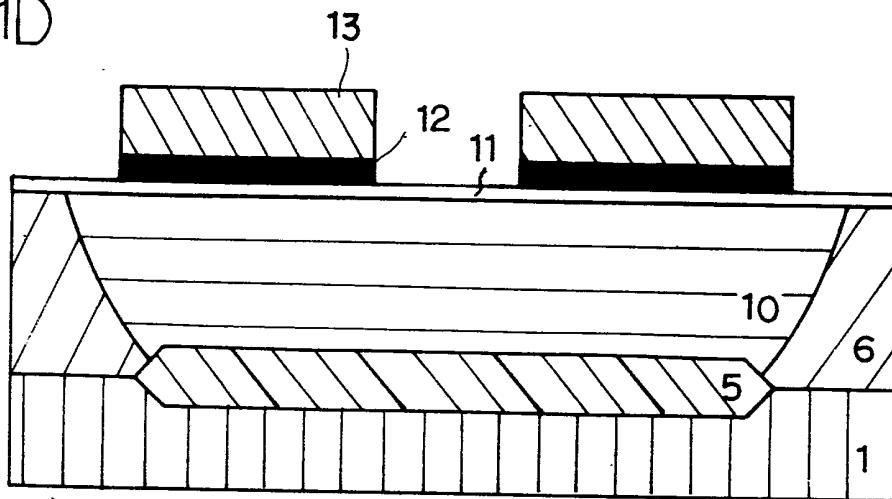

En se référant à la figure 1D, qui représente l'isolation de la région de l'élément actif au moyen de la formation d'une couche d'oxyde de champ, on dépose une résine photosensible 13 sur la troisième couche de nitrure 12, que l'on soumet au traitement de photolithographie pour corroder la partie de la couche de nitrure 12, dans laquelle le nitrure de champ doit être formé.

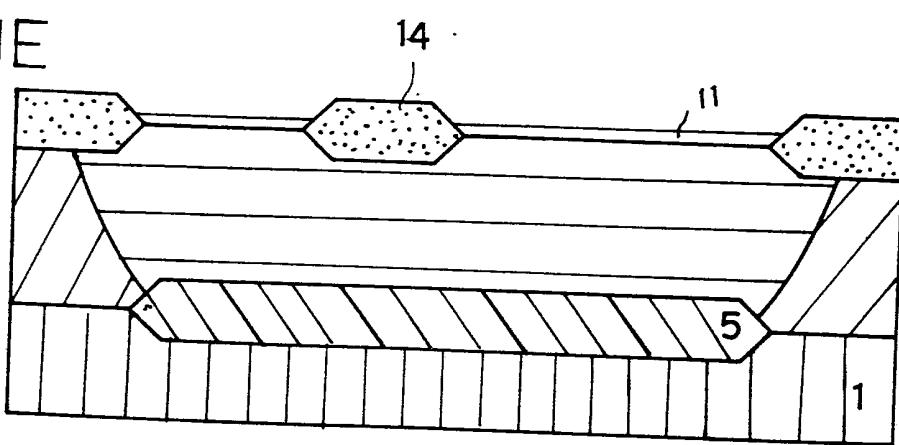

En se référant à la figure 1E, après élimination de la résine photosensible 13, on applique un traitement d'oxydation classique au substrat pour former la couche d'oxyde de champ 14, puis on élimine la troisième couche de nitrure 12.

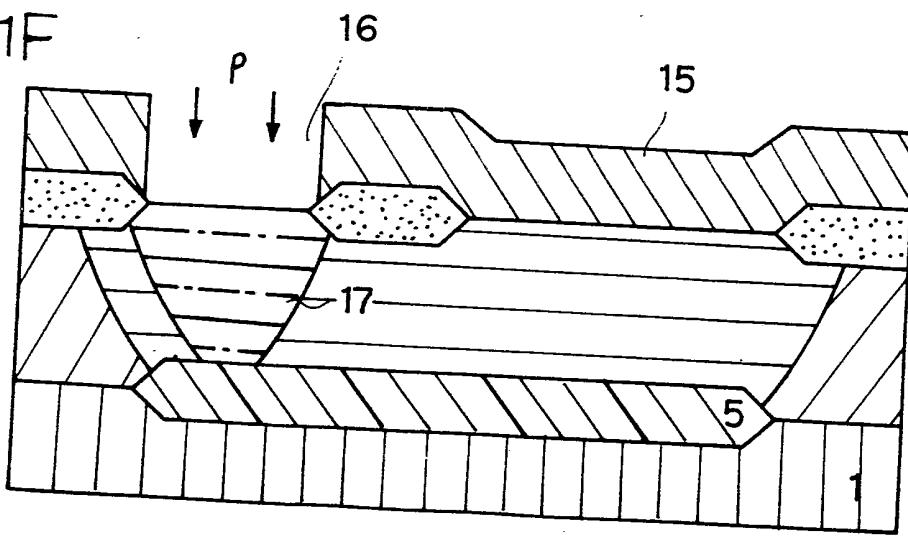

En se référant à la figure 1F servant à illustrer le procédé pour former une couche de diffusion de type N+

dans la région de collecteur 10, on dépose à nouveau sur le substrat une résine photosensible 15, qu'on soumet à nouveau au traitement de photolithographie pour former une fenêtre 16 pour l'implantation ionique.

5 On implante les ions de phosphore à travers la fenêtre 16 dans la région de collecteur 10 avec une dose comprise entre  $3 \times 10^{15}$  et  $5 \times 10^{15}$  ions/cm<sup>2</sup> pour former une couche de diffusion 17 de type N<sup>+</sup> servant à réduire la résistance de collecteur, et on élimine la résine photosensible 15.

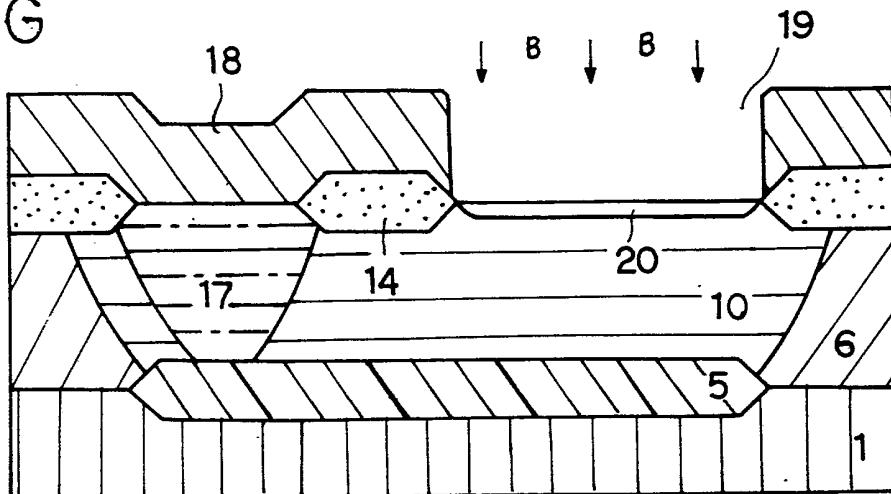

10 En se référant à la figure 1G servant à illustrer le procédé pour former la région de base, on applique sur le substrat une résine photosensible 18, qu'on soumet à son tour au traitement photolithographique pour former une fenêtre 19. Puis on implante du bore (B) avec une dose de  $1 \times 10^{13}$  -  $3 \times 10^{13}$  ions/cm<sup>2</sup> pour former une couche 20 formée par implantation ionique, et on élimine la résine photosensible 18.

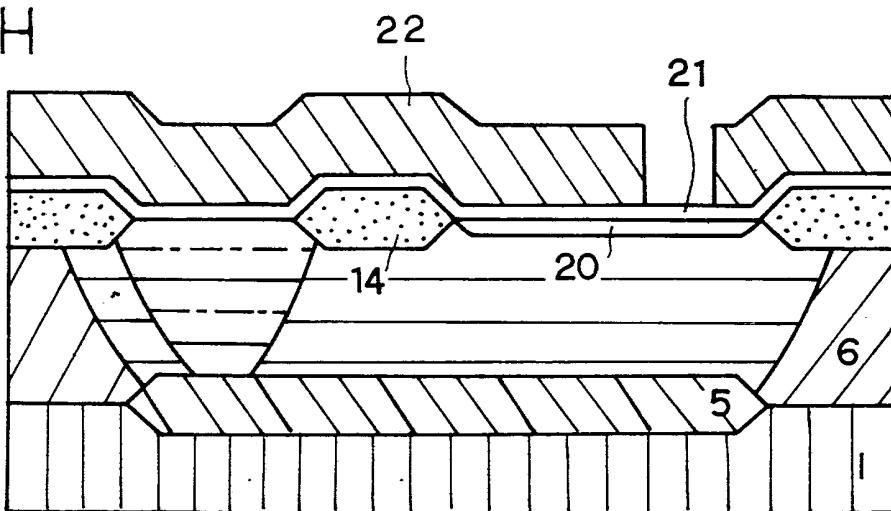

15 Les figures 1H et 1I illustrent le procédé de formation d'une fenêtre pour placer la couche de polysilicium, qui sera formée lors du traitement suivant, en contact avec le substrat en silicium monocristallin.

20 En se référant à la figure 1H, on dépose successivement une couche d'oxyde 21 et une résine photosensible 22 sur le substrat, que l'on soumet à son tour au processus photolithographique pour corroder la résine photosensible 22 de manière à mettre à nu la partie de la couche d'oxyde 21, dans laquelle une fenêtre de contact doit être formée.

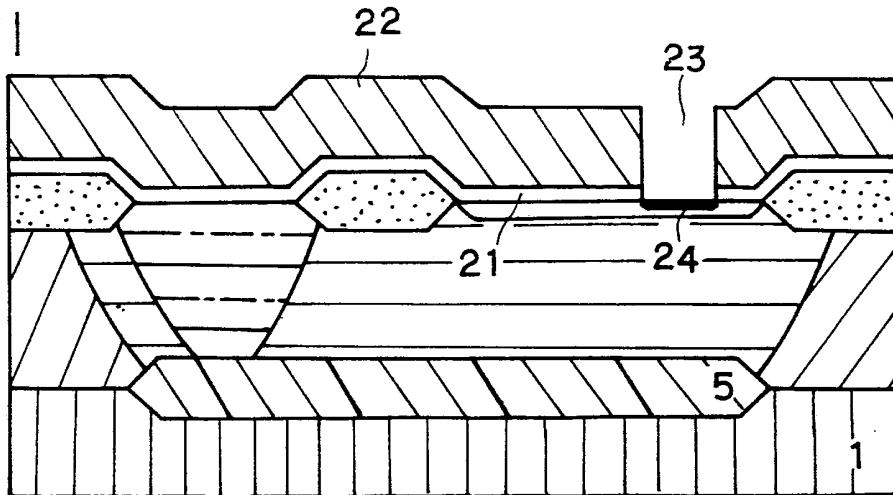

25 En se référant à la figure 1I, on élimine la partie de la couche d'oxyde 21 par corrosion ionique réactive pour former la fenêtre de contact 23. A cet instant, la partie à nu du substrat en Si monocristallin est endommagée, ce qui est indiqué par le chiffre de référence 24.

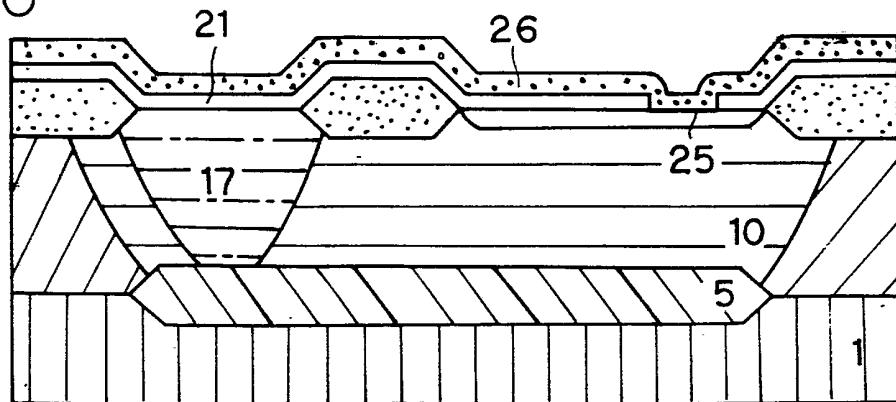

30 En référence à la figure 1J, qui sert à illustrer le traitement de formation d'une couche de polysilicium

pour le contact d'émetteur, on corrode la couche 24 en Si monocristallin située dans la fenêtre de contact 23 en utilisant le procédé de dépôt chimique en phase vapeur CVD amélioré par un plasma pour mettre à nu une partie propre 5 et non endommagée 25, et on élimine la résine photosensible 22.

Ensuite, on utilise le procédé de traitement en rampe pour déposer une couche de polysilicium 26 sur le substrat. Dans ce cas, lorsqu'on introduit la pastille dans 10 le tube de dépôt, on maintient la température de ce dernier à un niveau suffisamment faible égal à environ 400°C. Une fois que la pastille a été complètement insérée dans le tube de dépôt, on augmente graduellement la température du tube de dépôt pour l'amener à la température normale de dépôt du polysilicium afin de déposer correctement la couche 15 de polysilicium 26.

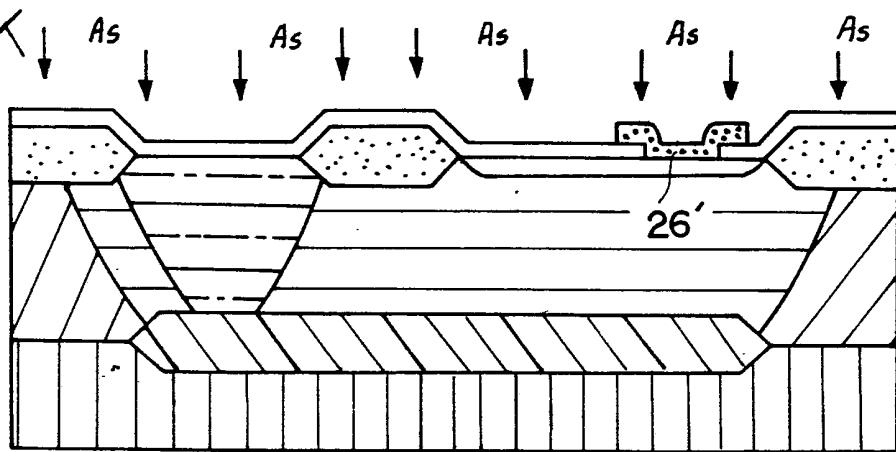

En référence à la figure 1K, on structure la couche de polysilicium 26 par photolithographie de manière à former la structure multiple 26'.

Ensuite, on implante des ions arsenic (As) à une dose comprise entre  $1 \times 10^{16}$  et  $2 \times 10^{16}$  ions/cm<sup>2</sup> pour former l'émetteur et la source.

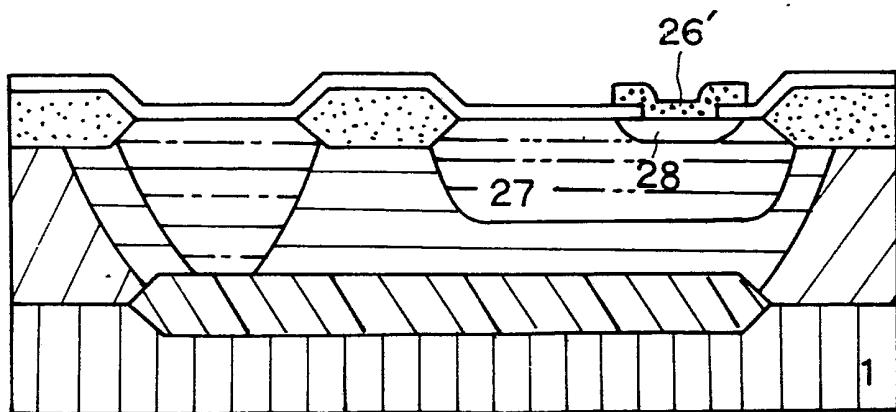

En référence à la figure 1L, les impuretés implantées lors des étapes des figures 1G et 1K diffusent simultanément de manière à former la région de base 27 et la région d'émetteur 28.

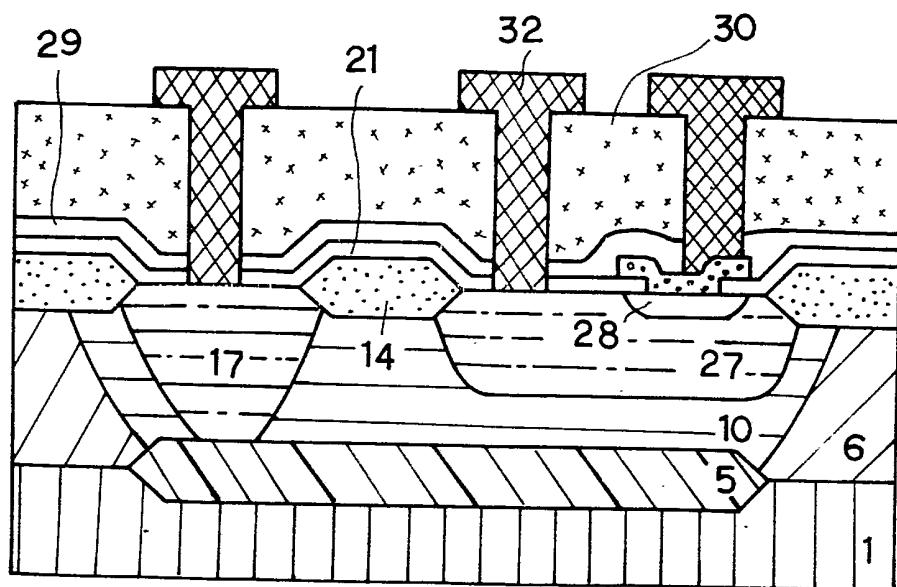

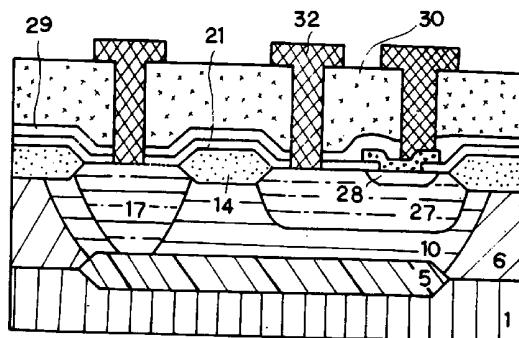

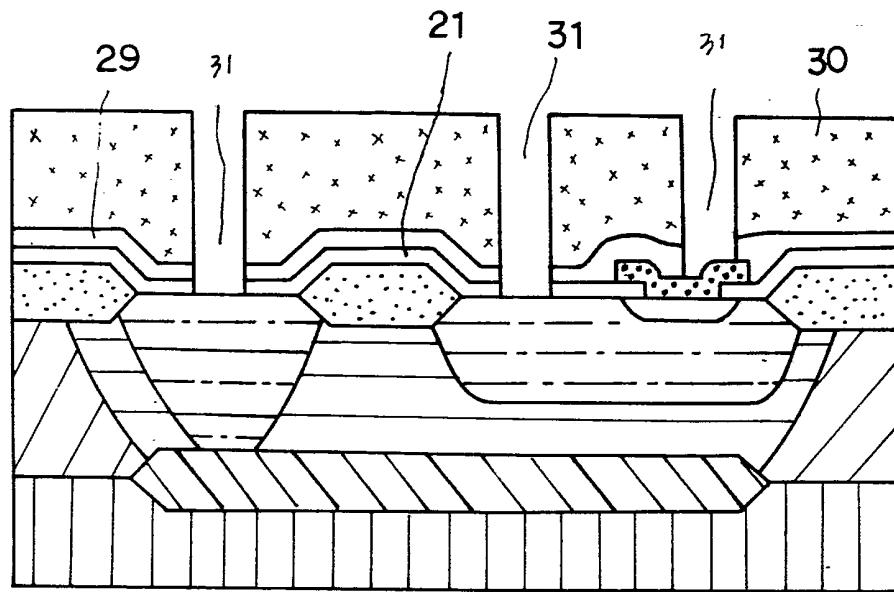

En référence à la figure 1M, on dépose successivement une couche d'oxyde 29 et une couche de BPSG 30 sur la pastille, on dépose une résine photosensible sur la 30 couche de BPSG, puis on corrode successivement la couche 30 de BPSG et les couches d'oxyde 29,21, par photolithographie de manière à former une fenêtre 31 d'établissement d'un contact métallique.

Enfin, on élimine la résine photosensible, et on 35 forme sur la pastille, une couche métallique que l'on

structure ensuite pour former une structure d'électrodes métalliques 32. On obtient ainsi un transistor bipolaire à émetteurs multiples possédant une faible résistance, conforme à la présente invention.

5 Comme cela a été décrit précédemment, conformément à la présente invention, on soumet à une corrosion à sec au moyen du procédé CVD amélioré par des plasmas, la surface du substrat en silicium monocristallin endommagée lors de l'élimination de la couche d'oxyde pour mettre en 10 contact la couche de polysilicium avec le substrat en silicium monocristallin, afin d'empêcher un accroissement de la résistance d'émetteur lors de la formation de l'émetteur multiple.

En outre, lors de l'utilisation du procédé de dépôt en rampe pour déposer une couche de polysilicium sur la 15 pastille, on maintient la température du tube de dépôt à une faible valeur pendant l'insertion de la pastille dans le tube, puis, une fois que la pastille a été complètement 20 insérée dans le tube, on augmente la température jusqu'au niveau de la température normale de dépôt du polysilicium de manière à empêcher la formation de la couche d'oxyde en cours pour produire un transistor bipolaire à émetteurs multiples, présentant une faible résistance.

REVENDICATIONS

1. Procédé pour fabriquer un transistor bipolaire à émetteurs multiples, caractérisé en ce qu'il consiste à mettre en oeuvre les étapes opératoires consistant à :

- 5 former une couche ensevelie (5) de type N<sup>+</sup> et une couche épitaxiale (6) de type N dans un substrat (1) en Si;

- 10 former un puits (10) de type N pour la région dudit transistor bipolaire en exécutant une implantation ionique d'une impureté du type N dans la couche épitaxiale (6);

- 15 former une couche d'oxyde de champ (14) au moyen d'une oxydation classique;

- 20 former une couche de diffusion (17) de type N<sup>+</sup> dans une région de collecteur (10);

- 25 former par implantation ionique une couche (20) pour une région de base en exécutant l'implantation ionique d'une impureté de type P ;

- 30 déposer une couche d'oxyde (21);

- 35 former une fenêtre de contact (23) en corrodant ladite couche d'oxyde (21);

- 40 former une structure multiple (26') par structuration après dépôt d'une couche de polysilicium (26) au moyen du procédé de dépôt en rampe;

- 45 exécuter une implantation ionique dans le substrat de manière à former une région d'émetteur;

- 50 former la région de base (27) et la région d'émetteur (28) au moyen d'une diffusion simultanée des impuretés implantées par implantation ionique;

- 55 former une couche d'oxyde (29) et une couche de verre au silicate de bore et de phosphore BPSG (30);

- 60 ménager une fenêtre pour contact métallique en corrodant séquentiellement la couche de BPSG et la couche d'oxyde par photolithographie; et

- 65 former une structure d'électrodes métalliques (32) en déposant une couche métallique et en la structurant.

2. Procédé selon la revendication 1, caractérisé en ce que ladite fenêtre de contact (23), met ladite structure multiple (26') en contact avec ledit substrat en Si monocristallin.

5 3. Procédé selon la revendication 1 ou 2, caractérisé en ce que l'étape de formation de la fenêtre de contact inclut les étapes partielles consistant à:

déposer une résine photosensible (22) sur ladite couche d'oxyde (21);

10 mettre à nu une partie du substrat pour former ladite fenêtre de contact en corrodant ladite résine photosensible (22) par photolithographie;

corroder ladite couche d'oxyde (21) au moyen d'une corrosion ionique réactive; et

15 corroder la partie (24) dudit substrat en silicium monocristallin endommagé pendant la corrosion de ladite couche d'oxyde (21).

4. Procédé selon la revendication 3, caractérisé en ce qu'on corrode la partie endommagée (24) au moyen du 20 procédé CVD de dépôt chimique en phase vapeur amélioré au moyen d'un plasma.

5. Procédé selon la revendication 1, caractérisé en ce que lors du dépôt dudit polysilicium (26), on maintient la température d'un tube de dépôt à une valeur aussi 25 faible qu'environ 400°C pendant l'insertion de la pastille dans le tube, puis, une fois que la pastille a été complètement insérée dans le tube, on augmente graduellement la température pour l'amener au niveau de la température normale de dépôt du polysilicium.

30 6. Procédé selon la revendication 1, caractérisé en ce que ladite structure multiple (26') est la source de diffusion de la région d'émetteur.

FIG 1A

FIG 1B

FIG 1C

FIG1D

FIG1E

FIG1F

FIG1G

FIG1H

FIG1I

FIG1J

FIG1K

FIG1L

FIG1M

FIG1N