(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2007년10월11일

(11) 등록번호 10-0766318

(24) 등록일자 2007년10월05일

(51) Int. Cl.

*G02F 1/136* (2006.01) *G02F 1/361* (2006.01)

(21) 출원번호 10-2005-0114957

(22) 출원일자 2005년11월29일

심사청구일자 2005년11월29일

(65) 공개번호 10-2007-0056393

공개일자 2007년06월04일

(56) 선행기술조사문헌

KR1020050048463A

(뒷면에 계속)

전체 청구항 수 : 총 29 항

심사관 : 임동재

(54) 유기 반도체 물질을 이용한 박막트랜지스터와 이를 구비한 액정표시장치용 어레이 기판 및 그 제조방법

**(57) 요 약**

본 발명은 기판 상에 형성된 버퍼층과; 상기 버퍼층 위로 형성되며 서로 이격하는 소스 및 드레인 전극; 상기 소스 전극과 드레인 전극의 이격한 영역을 포함하여 상기 소스 및 드레인 전극과 동시에 접촉하며 형성된 유기 반도체층과; 상기 유기 반도체층 상부로 상기 유기 반도체층과 동일한 형태로 형성된 게이트 절연막과; 상기 게이트 절연막 위로 상기 소스 및 드레인 전극 간 이격영역에 대응하여 형성된 게이트 전극을 포함하는 탑 게이트 (top gate)의 보텀 콘택트(bottom contact) 구조로서 상기 유기 반도체층의 밑면이 소스 및 드레인 전극의 표면과 접촉하도록 하는 구조의 박막트랜지스터 및 이를 구비한 액정표시장치용 어레이 기판을 제안함으로써 소자 특성을 향상시키는 효과가 있으며, 또한, 그 표면 상태가 매끈한 것을 특징으로 하는 버퍼층을 형성하고, 상기 버퍼층 위로 유기 반도체층을 형성하는 것을 제안함으로써 상기 유기 반도체층의 결정성을 향상시켜 소자 특성을 향상시키는 더욱 향상시키는 효과가 있다.

**대표도** - 도4g

(56) 선 행 기술조사 문현

JP17236149 A

JP17203728 A

KR1020050070479A

---

## 특허청구의 범위

### 청구항 1

기판 상에 형성된 버퍼층과;

상기 버퍼층 위로 형성되며 서로 이격하는 소스 및 드레인 전극;

상기 소스 전극과 드레인 전극의 이격한 영역을 포함하여 상기 소스 및 드레인 전극과 동시에 접촉하며 형성된 유기 반도체층과;

상기 유기 반도체층 상부로 상기 유기 반도체층과 동일한 형태로 형성된 게이트 절연막과;

상기 게이트 절연막 위로 상기 소스 및 드레인 전극 간 이격영역에 대응하여 형성된 게이트 전극

을 포함하는 유기 반도체 물질을 이용한 박막트랜지스터.

### 청구항 2

제 1 항에 있어서,

상기 게이트 전극은 상기 게이트 절연막과 동일한 형태인 유기 반도체 물질을 이용한 박막트랜지스터.

### 청구항 3

제 1 항에 있어서,

상기 버퍼층은, 질화실리콘(SiNx), 산화실리콘(SiO<sub>2</sub>), SiNxOy 중에서 선택되는 무기절연물질로 형성되거나 또는 PVP(poly vinyl pyrrolidone), PVA(polyvinyl alcohol), BCB(benzocyclobutene), PMMA(poly methyl meta acrylate) 중에서 선택되는 유기절연물질로 형성된 것이 특징인 유기 반도체 물질을 이용한 박막트랜지스터.

### 청구항 4

제 1 항에 있어서,

상기 유기 반도체층은 펜타신(pentacene)으로 이루어진 유기 반도체 물질을 이용한 박막트랜지스터.

### 청구항 5

제 1 항에 있어서,

상기 게이트 절연막은 산화실리콘(SiO<sub>2</sub>), 또는 질화실리콘(SiNx) 등의 무기절연물질 또는 PVA(poly vinyl alcohol) 또는 기상 증착된 고분자물질인 폴리이미드(polyimide) 등의 유기절연물질로 이루어진 유기 반도체 물질을 이용한 박막트랜지스터.

### 청구항 6

제 1 항에 있어서,

상기 소스 및 드레인 전극은 금(Au), ITO, 니켈(Ni), 납(Pb), 알루미늄(Al), 탄탈륨(Ta), 티타늄(Ti) 중에서 선택되는 금속물질 또는 PEDOT:PSS(poly ethylene dioxy thiophene : poly styrene sulfonate) 등의 유기 도전성 물질로 이루어진 유기 반도체 물질을 이용한 박막트랜지스터.

### 청구항 7

기판 상에 형성된 버퍼층과;

상기 버퍼층 위로 형성되며 서로 이격하는 소스 및 드레인 전극과, 상기 소스 전극과 연결된 데이터 배선과;

상기 소스 및 드레인 전극과 이들 두 전극 사이의 이격영역을 포함하여 상기 데이터 배선 위로 형성된 유기 반도체층과;

상기 유기 반도체층 상부로 상기 유기 반도체층과 동일한 형태로 형성된 게이트 절연막과;

상기 게이트 절연막 위로 상기 소스 및 드레인 전극 간 이격영역에 형성된 게이트 전극 및 상기 게이트 전극과 연결되며 상기 데이터 배선과 교차하는 게이트 배선과;

상기 게이트 전극과 게이트 배선 위로 전면에 드레인 콘택홀을 갖는 보호층과;

상기 보호층 상부로 상기 드레인 콘택홀을 통해 상기 드레인 전극과 연결되는 화소전극

을 포함하는 유기 반도체 물질을 이용한 박막트랜지스터를 구비한 액정표시장치용 어레이 기판.

#### 청구항 8

제 7 항에 있어서,

상기 유기 반도체층과 그 상부의 게이트 절연막에는 상기 드레인 전극을 노출시키는 제 1 콘택홀이 형성된 유기 반도체 물질을 이용한 박막트랜지스터를 구비한 액정표시장치용 어레이 기판.

#### 청구항 9

제 8 항에 있어서,

상기 게이트 절연막 위로 상기 제 1 콘택홀을 통해 상기 드레인 전극과 접촉하는 드레인 접촉 패드가 형성된 유기 반도체 물질을 이용한 박막트랜지스터를 구비한 액정표시장치용 어레이 기판.

#### 청구항 10

제 9 항에 있어서,

상기 드레인 콘택홀은 상기 드레인 접촉 패드를 노출시키는 것이 특징인 유기 반도체 물질을 이용한 박막트랜지스터를 구비한 액정표시장치용 어레이 기판.

#### 청구항 11

제 10 항에 있어서,

상기 화소전극은 상기 드레인 콘택홀을 통해 상기 드레인 접촉 패드와 접촉하는 것이 특징인 유기 반도체 물질을 이용한 박막트랜지스터를 구비한 액정표시장치용 어레이 기판.

#### 청구항 12

제 7 항에 있어서,

상기 게이트 전극은 상기 게이트 절연막과 동일한 형태인 유기 반도체 물질을 이용한 박막트랜지스터를 구비한 액정표시장치용 어레이 기판.

#### 청구항 13

제 7 항 또는 제 11 항 또는 제 12 항 중 어느 하나의 항에 있어서,

상기 벼퍼층은 질화실리콘(SiNx), 산화실리콘(SiO<sub>2</sub>), SiNxOy 중에서 선택되는 무기절연물질로 형성되거나 또는 PVP(poly vinyl pyrrolidone), PVA(polyvinyl alcohol), BCB(benzocyclobutene), PMMA(poly methyl meta acrylate) 중에서 선택되는 유기절연물질로 형성된 것이 특징인 유기 반도체 물질을 이용한 박막트랜지스터를 구비한 액정표시장치용 어레이 기판.

#### 청구항 14

제 7 항 또는 제 11 항 또는 제 12 항 중 어느 하나의 항에 있어서,

상기 유기 반도체층은 펜타신(pentacene)으로 이루어진 유기 반도체 물질을 이용한 박막트랜지스터를 구비한 액정표시장치용 어레이 기판.

#### 청구항 15

제 7 항 또는 제 11 항 또는 제 12 항 중 어느 하나의 항에 있어서,

상기 게이트 절연막은 산화실리콘(SiO<sub>2</sub>), 또는 질화실리콘(SiNx) 등의 무기절연물질 또는 PVA(poly vinyl alcohol) 또는 기상 증착된 고분자물질인 폴리이미드(polyimide) 등의 유기절연물질로 이루어진 유기 반도체 물질을 이용한 박막트랜지스터를 구비한 액정표시장치용 어레이 기판.

### 청구항 16

제 7 항 또는 제 11 항 또는 제 12 항 중 어느 하나의 항에 있어서,

상기 소스 및 드레인 전극은 금(Au), ITO, 니켈(Ni), 납(Pb), 알루미늄(Al), 탄탈륨(Ta), 티타늄(Ti) 중에서 선택되는 금속물질 또는 PEDOT:PSS(poly ethylene dioxy thiophene : poly styrene sulfonate) 등의 유기 도전성 물질로 이루어진 유기 반도체 물질을 이용한 박막트랜지스터를 구비한 액정표시장치용 어레이 기판.

### 청구항 17

제 7 항 또는 제 11 항 또는 제 12 항 중 어느 하나의 항에 있어서,

상기 기판은 플라스틱, 유기 또는 금속물질로 이루어진 유기 반도체 물질을 이용한 박막트랜지스터를 구비한 액정표시장치용 어레이 기판.

### 청구항 18

기판 위로 전면에 벼퍼층을 형성하는 단계와;

상기 벼퍼층 위로 서로 이격하는 소스 및 드레인 전극과, 상기 소스 전극과 연결된 데이터 배선을 형성하는 단계와;

상기 소스 및 드레인 전극과 데이터 배선 위로 전면에 유기 반도체 물질을 진공 열 증착하여 유기 반도체 물질층을 형성하는 단계와;

상기 유기 반도체 물질층 위로 절연층을 형성하는 단계와;

상기 절연층 위로 포토레지스트 패턴을 형성하는 단계와;

상기 포토레지스트 패턴을 외부로 노출된 절연층 및 그 하부의 유기 반도체 물질층을 드라이 에칭하여 제거함으로써 상기 소스 및 드레인 전극의 이격영역을 포함하여 상기 소스 및 드레인 전극과 데이터 배선 위로 유기 반도체층과 그 위로 게이트 절연막을 형성하는 단계와;

상기 게이트 절연막 위로 상기 소스 및 드레인 전극의 이격영역에 대응하여 게이트 전극과, 상기 게이트 전극과 연결되며 상기 데이터 배선과 교차하는 게이트 배선을 형성하는 단계와;

상기 게이트 전극과 게이트 배선 위로 제 1 콘택홀을 갖는 보호층을 형성하는 단계와;

상기 보호층 위로 상기 제 1 콘택홀을 통해 드레인 전극과 연결되는 화소전극을 형성하는 단계

를 포함하는 유기 반도체 물질을 이용한 박막트랜지스터를 구비한 액정표시장치용 어레이 기판의 제조 방법.

### 청구항 19

제 18 항에 있어서,

상기 벼퍼층은 질화실리콘(SiNx), 산화실리콘(SiO<sub>2</sub>), SiNxOy 중에서 선택되는 무기절연물질을 증착함으로써 형성하거나 또는 PVP(polyvinylpyrrolidone), PVA(polyvinyl alcohol), BCB(benzocyclobutene), PMMA(poly methyl meta acrylate) 중에서 선택되는 유기절연물질을 코팅하여 형성함으로써 매끈한 표면상태를 갖는 것이 특징인 유기 반도체 물질을 이용한 박막트랜지스터를 구비한 액정표시장치용 어레이 기판의 제조 방법.

### 청구항 20

제 18 항에 있어서,

상기 소스 및 드레인 전극과 데이터 배선을 형성하는 단계는

금(Au), ITO, 니켈(Ni), 납(Pb), 알루미늄(Al), 탄탈륨(Ta), 티타늄(Ti) 중에서 선택되는 금속물질을 증착하여 제 1 금속층을 형성하거나 또는 PEDOT:PSS(poly ethylene dioxy thiophene : poly styrene sulfonate)의 유기 도전성 물질을 상온에서 코팅하여 유기 도전성 물질층을 형성하는 단계와;

상기 제 1 금속층 또는 유기 도전성 물질층을 패터닝하는 단계

를 포함하는 유기 반도체 물질을 이용한 박막트랜지스터를 구비한 액정표시장치용 어레이 기판의 제조 방법.

### 청구항 21

삭제

### 청구항 22

제 18 항에 있어서,

상기 유기 반도체층 및 게이트 절연막을 형성하는 단계는,

상기 드레인 전극을 노출시키는 제 2 콘택홀을 형성하는 단계

를 포함하는 유기 반도체 물질을 이용한 박막트랜지스터를 구비한 액정표시장치용 어레이 기판의 제조 방법.

### 청구항 23

제 22 항에 있어서,

상기 게이트 전극 및 게이트 배선을 형성하는 단계는,

상기 제 2 콘택홀을 통해 상기 드레인 전극과 접촉하며 상기 게이트 전극과 이격하는 드레인 접촉 패드를 형성하는 단계

를 포함하는 유기 반도체 물질을 이용한 박막트랜지스터를 구비한 액정표시장치용 어레이 기판의 제조 방법.

### 청구항 24

제 23 항에 있어서,

상기 제 1 콘택홀은 상기 드레인 접촉 패드를 노출시키도록 형성하는 유기 반도체 물질을 이용한 박막트랜지스터를 구비한 액정표시장치용 어레이 기판의 제조 방법.

### 청구항 25

제 24 항에 있어서,

상기 화소전극은 상기 제 1 콘택홀을 통해 상기 드레인 접촉 패드와 접촉하도록 형성됨으로써 상기 드레인 전극과 연결되는 유기 반도체 물질을 이용한 박막트랜지스터를 구비한 액정표시장치용 어레이 기판의 제조 방법.

### 청구항 26

기판 위로 전면에 베퍼층을 형성하는 단계와;

상기 베퍼층 위로 서로 이격하는 소스 및 드레인 전극과, 상기 소스 전극과 연결된 데이터 배선을 형성하는 단계와;

상기 소스 및 드레인 전극과 데이터 배선 위로 전면에 유기 반도체 물질을 진공 열 증착하여 유기 반도체 물질층을 형성하는 단계와;

상기 유기 반도체 물질층 위로 절연층을 형성하는 단계와;

상기 절연층 위로 제 2 금속물질을 증착하여 제 2 금속물질층을 형성하는 단계와;

상기 제 2 금속물질층을 패터닝하여 상기 소스 및 드레인 전극 간 이격영역에 대응하여 게이트 전극과, 상기 게이트 전극과 연결된 게이트 배선을 형성하는 단계와;

상기 게이트 전극 및 게이트 배선을 마스크로 하여 상기 게이트 전극 및 게이트 배선 외부로 노출된 상기 절연층 및 그 하부의 유기 반도체 물질층을 드라이 에칭을 실시하여 제거함으로써 상기 게이트 전극 하부에 상기 게이트전극과 동일한 형태의 유기 반도체층과, 게이트 절연막을 형성하는 단계

를 포함하는 유기 반도체 물질을 이용한 박막트랜지스터를 구비한 액정표시장치용 어레이 기판의 제조 방법.

### 청구항 27

제 26 항에 있어서,

상기 유기 반도체층과 그 상부에 위치한 상기 게이트 절연막은 상기 유기 반도체층 하부에 위치한 드레인 전극을 일부 노출시키며 형성되는 것이 특징인 유기 반도체 물질을 이용한 박막트랜지스터를 구비한 액정표시장치용 어레이 기판의 제조 방법.

### 청구항 28

제 27 항에 있어서,

상기 제 1 콘택홀은 상기 유기 반도체층과 그 상부에 위치한 상기 게이트 절연막 외부로 노출된 부분의 상기 드레인 전극에 대응하여 형성하는 것이 특징인 유기 반도체 물질을 이용한 박막트랜지스터를 구비한 액정표시장치용 어레이 기판의 제조 방법.

### 청구항 29

삭제

### 청구항 30

제 18 항에 있어서,

상기 유기 반도체층은 펜타신(pentacene)을 진공 열 증착하여 형성하는 것이 특징인 유기 반도체 물질을 이용한 박막트랜지스터를 구비한 액정표시장치용 어레이 기판의 제조 방법.

### 청구항 31

제 18 항에 있어서,

상기 게이트 절연막은 산화실리콘(SiO<sub>2</sub>), 또는 질화실리콘(SiNx) 등의 무기절연물질을 증착하거나 또는 PVA(poly vinyl alcohol) 또는 기상 증착된 고분자물질인 폴리이미드(polyimide) 등의 유기절연물질을 코팅하여 형성하는 유기 반도체 물질을 이용한 박막트랜지스터를 구비한 액정표시장치용 어레이 기판의 제조 방법.

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

<16> 본 발명은 액정표시장치에 관한 것으로, 좀 더 자세하게는 유기 반도체 물질을 이용한 액정표시장치용 어레이 기판 및 이의 제조방법에 관한 것이다.

<17> 근래에 들어 사회가 본격적인 정보화 시대로 접어들에 따라 대량의 정보를 처리 및 표시하는 디스플레이(display) 분야가 급속도로 발전해 왔고, 최근에는 특히 박형화, 경량화, 저 소비전력화의 우수한 성능을 지닌 박막트랜지스터(Thin Film Transistor : TFT)형 액정표시장치(TFT-LCD)가 개발되어 기존의 브라운관(Cathode Ray Tube : CRT)을 대체하고 있다.

<18> 액정표시장치의 화상구현원리는 액정의 광학적 이방성과 분극성질을 이용하는 것으로, 주지된 바와 같이 액정은 분자구조가 가늘고 길며 배열에 방향성을 갖는 광학적 이방성과 전기장 내에 놓일 경우에 그 크기에 따라 분자 배열 방향이 변화되는 분극성질을 띤다. 이에 액정표시장치는 액정층을 사이에 두고 서로 마주보는 면으로 각각

화소전극과 공통전극이 형성된 어레이 기판(array substrate)과 컬러필터 기판(color filter substrate)을 합착시켜 구성된 액정패널을 필수적인 구성요소로 하며, 이를 전극 사이의 전기장 변화를 통해서 액정분자의 배열 방향을 인위적으로 조절하고 이때 변화되는 빛의 투과율을 이용하여 여러 가지 화상을 표시하는 비발광 소자이다.

- <19> 최근에는 특히 화상표현의 기본단위인 화소(pixel)를 행렬 방식으로 배열하고 스위칭 소자를 각 화소에 배치시켜 독립적으로 제어하는 능동행렬방식(active matrix type)이 해상도 및 동영상 구현능력에서 뛰어나 주목받고 있는데, 이 같은 스위칭 소자로 박막 트랜지스터(Thin Film Transistor : TFT)를 사용한 것이 잘 알려진 TFT-LCD(Thin Film Transistor Liquid Crystal Display device) 이다.

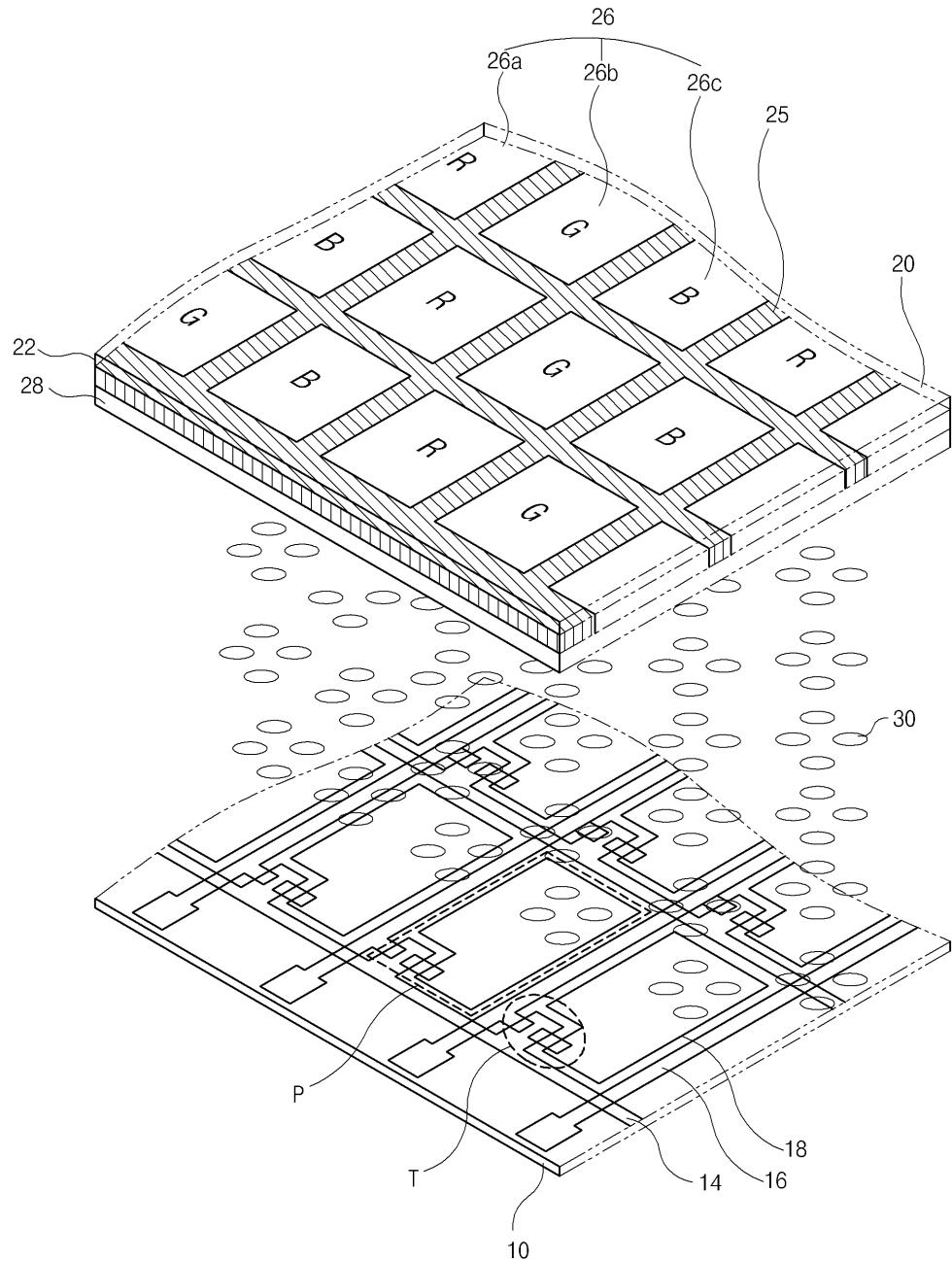

- <20> 좀 더 자세히, 일반적인 액정표시장치의 분해사시도인 도 1에 나타낸 바와 같이 액정층(30)을 사이에 두고 아래의 기판(10)과 컬러필터 기판(20)이 대면 합착된 구성을 갖는데, 이중 하부의 어레이 기판(10)은 상면으로 종횡 교차 배열되어 다수의 화소영역(P)을 정의하는 복수개의 게이트 배선(14)과 데이터 배선(16)을 포함하며, 이들 두 배선(14, 16)의 교차지점에는 박막 트랜지스터(T)가 구비되어 각 화소영역(P)에 마련된 화소전극(18)과 일대일 대응 접속되어 있다.

- <21> 또한 이와 마주보는 상부의 컬러필터 기판(20)은 그 배면으로 상기 게이트 배선(14)과 데이터 배선(16) 그리고 박막 트랜지스터(T) 등의 비표시영역을 가리도록 각 화소영역(P)을 테두리하는 격자 형상의 블랙매트릭스(25)가 형성되어 있으며, 이들 격자 내부에서 각 화소영역(P)에 대응되게 순차적으로 반복 배열된 적, 녹, 청색 컬러필터층(26)이 형성되어 있으며, 상기 블랙매트릭스(25)와 적, 녹, 청색 컬러필터층(26)의 전면에 걸쳐 투명한 공통전극(28)이 마련되어 있다.

- <22> 그리고 도면상에 명확하게 도시되지는 않았지만, 이들 두 기판(10, 20)은 그 사이로 개재된 액정층(30)의 누설을 방지하기 위하여 가장자리 따라 실링제 등으로 봉함(封函)된 상태에서 각 기판(10, 20)과 액정층(30)의 경계 부분에는 액정의 문자배열 방향에 신뢰성을 부여하는 상, 하부 배향막이 개재되며, 각 기판(10, 20)의 적어도 하나의 외측면에는 편광판이 부착된다.

- <23> 더불어 액정패널 배면으로는 백라이트(back-light)가 구비되어 빛을 공급하는 바, 게이트배선(14)으로 박막트랜지스터(T)의 온(on)/오프(off) 신호가 순차적으로 스캔 인가되어 선택된 화소영역(P)의 화소전극(18)에 데이터 배선(16)의 화상신호가 전달되면 이들 사이의 수직전계에 의해 그 사이의 액정분자가 구동되고, 이에 따른 빛의 투과율 변화로 여러 가지 화상을 표시할 수 있다.

- <24> 한편, 이 같은 액정표시장치에 있어 어레이 기판(10)과 컬러필터 기판(20)의 모체가 되는 절연기판은 전통적으로 유리기판이 사용되었지만, 최근 들어 노트북이나 PDA와 같은 소형의 휴대용 단말기가 널리 보급됨에 따라 이들에 적용 가능하도록 유리보다 가볍고 경량임과 동시에 유연한 특성을 지니고 있어 과손위험이 적은 플라스틱 기판을 이용한 액정패널이 소개된 바 있다.

- <25> 하지만, 플라스틱 기판을 이용한 액정패널은 액정표시장치의 제조 특성상 특히 스위칭 소자인 박막트랜지스터가 형성되는 어레이 기판의 제조에는 200°C 이상의 고온을 필요로 하는 고온 공정이 많아 내열성 및 내화학성이 유리기판 보다 떨어지는 플라스틱 기판으로 상기 어레이 기판을 제조하는 데에는 어려움이 있어, 상부기판을 이루는 컬러필터 기판만을 플라스틱 기판으로 제조하고 하부기판인 어레이 기판은 통상적인 유리 기판을 이용하여 액정표시장치를 제조하고 있는 실정이다.

- <26> 이러한 문제를 해결하고자 최근에는 유기 반도체 물질 등을 이용하여 200°C 이하의 저온 공정을 진행하여 박막트랜지스터를 형성하는 것을 특징으로 하는 어레이 기판을 제조하는 기술이 제안되었다.

- <27> 이후에는 200°C 이하의 저온 공정을 진행되는 유기 반도체 물질을 이용한 어레이 기판의 제조 방법에 대해 설명한다.

- <28> 200°C 이하의 저온 공정으로 박막트랜지스터를 포함하는 화소를 형성함에 있어서, 전극과 배선을 이루는 금속물질과 절연막과 보호층등의 형성을 저온 중착 또는 코팅의 방법등을 통해 형성하여도 박막 트랜지스터의 특성에 별 영향을 주지 않지만, 채널을 형성하는 반도체층을 일반적인 반도체 물질인 비정질 실리콘을 사용하여 저온 공정에 의해 형성하게 되면, 내구 구조가 치밀하지 못하여 전기 전도도 등의 중요 특성이 저하되는 문제가 발생한다.

- <29> 따라서, 이를 극복하고자 비정질 실리콘 등의 종래의 반도체 물질 대신 반도체 특성을 가진 유기 물질을 이용하여 유기 반도체층을 형성하는 것이 제안되고 있다.

- <30> 이때, 반도체 특성을 갖는 유기 물질은 크게 고분자 유기 반도체 물질과 저분자 유기 반도체 물질로 나뉘고 있으며, 상기 저분자 유기 반도체 물질은 고분자 유기 반도체 물질 대비 전기 전도도 등의 우수한 물성을 갖고 있기에 주로 실리콘을 대신하는 반도체 물질로 이용되고 있지만, 유기 용제나 알코올 등과 같은 용매에 매우 취약하여 용액 형태로 만들기 힘든 단점이 있다.

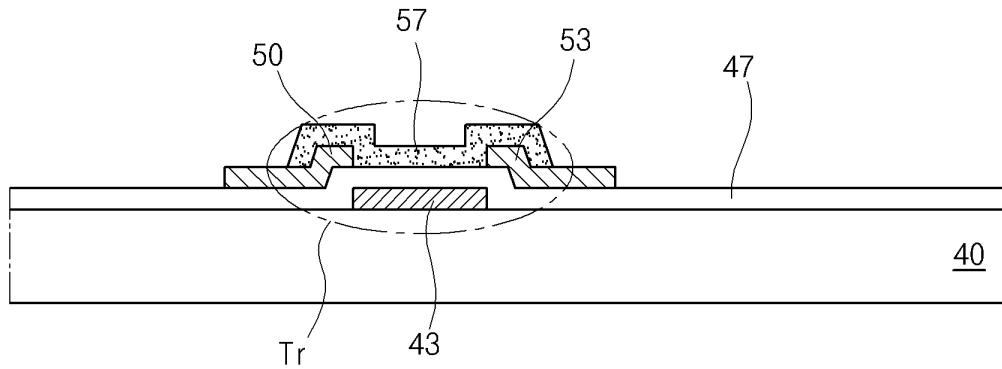

- <31> 유기 반도체 물질을 이용하여 박막트랜지스터를 형성할 경우, 상기 유기 반도체 물질은 통상적으로 이베퍼레이션 의해 기판 상에 형성되며, 상기 일부 유기 반도체 물질은 유기 용제나 알코올 등에 취약한 구조를 갖는 바, 유기 반도체 물질이 유기 용매나 알코올 등의 용매(현상액이나 식각액의 성분임)에 노출되는 것을 최소화하기 위해, 종래의 유기 반도체 물질을 이용한 박막트랜지스터의 단면도인 도 2에 도시한 바와 같이, 통상적으로 게이트 전극(43)이 최하부에 형성되고, 소스 및 드레인 전극(50, 53)의 표면과 유기 반도체층(57)의 밑면이 접촉하는 것을 특징으로 하는 보텀 게이트(bottom gate)의 보텀 콘택트(bottom contact) 구조로 형성되고 있다.

- <32> 하지만, 보텀 게이트(bottom gate) 구조에 있어서, 보텀 콘택트(bottom contact)의 경우 접촉 저항이 커서 전하 주입의 어려워 문제가 되고 있으며, 이러한 결과 이동도 등이 일반적으로 낮게 되어 박막트랜지스터의 특성이 저하되게 된다.

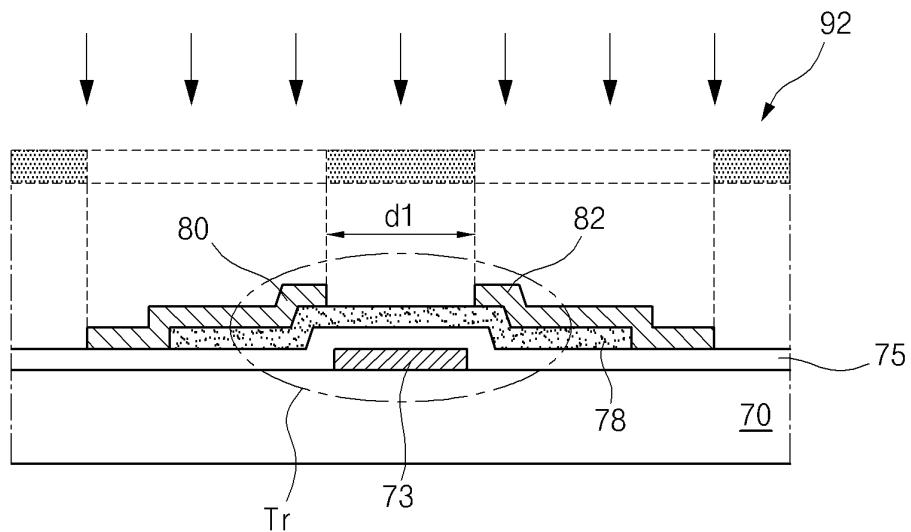

- <33> 한편, 유기 반도체 물질을 이용하여 보텀 게이트(bottom gate)의 탑 콘택트(top contact) 구조로 형성할 경우, 박막트랜지스터의 특성은 우수하나 패터닝 시, 현상액 또는 식각액에 노출되면 그 특성상 그 반도체 물질로서의 성능이 급격히 저하되는 바, 도 3에 도시한 바와 같이, 기판(70)상에 상기 유기 반도체 물질을 쉐도우 마스크(shadow mask) 등을 이용하여 특정 형태로 패터닝 된 유기 반도체층(78)을 형성 후, 그 상부로 소스 및 드레인 전극(80, 82)까지도 쉐도우 마스크(shadow mask)(92)를 이용하여 형성함으로써, 상기 쉐도우 마스크(shadow mask)(92)를 이용한 물리적 한계로 인해 상기 소스 및 드레인 전극(80, 82) 간 이격간격(d1) 즉, 채널의 길이(d1)가 수십  $\mu\text{m}$  이상이 되어 박막트랜지스터(Tr) 자체의 사이즈가 커지게 되어 개구율 및 해상도 등에 영향을 주는 바, 실제 액정표시장치 등의 표시장치에 적용하기에는 무리가 있다.

- <34> 이를 극복하고자, 게이트 전극이 반도체층의 상부에 위치하는 탑 게이트(top gate) 구조도 제안되고 있으나, 이러한 탑 게이트(top gate) 구조는 고분자 유기 반도체 물질을 이용하여 이를 반도체층으로 형성할 경우 그 상부에 형성되는 유기절연물질로 이루어진 게이트 절연막과의 상호 간의 공정 영향이 적으로 이러한 구조로써 형성하는 것이며, 저분자 유기 반도체물질은 탑 게이트(top gate) 구조로써 형성되지 않고 있는 실정이다.

- <35> 또한, 이러한 고분자 유기 반도체 물질로 이루어진 박막트랜지스터의 경우, 저분자 유기 반도체 물질로 이루어진 박막트랜지스터 보다 반도체 물질 자체의 물성으로 인해 그 성능이 떨어지므로 제한적으로 사용되고 있다.

- <36>

### 발명이 이루고자 하는 기술적 과제

- <37> 전술한 문제를 해결하기 위해서 본 발명은 안출된 것으로 유기 용제나 알코올 등의 용매에 매우 취약한 특성을 갖는 유기 반도체 물질을 이용한 박막트랜지스터 또는 어레이 기판의 제조에 있어, 유기 반도체 물질로 이루어진 반도체층의 손상없이 탑 게이트(top gate) 보텀 콘택트(bottom contact) 구조의 박막트랜지스터 및 이를 구비한 어레이 기판을 제조하는 것을 그 목적으로 하고 있으며, 나아가 유기 반도체 물질의 금속물질과의 접촉저항을 최소화하여 소자 특성을 향상시킬 수 있는 구조의 유기 반도체 물질을 이용한 박막트랜지스터 및 이를 이용한 액정표시장치용 어레이 기판의 제조 방법을 제공하는데 그 또 다른 목적이 있다.

### 발명의 구성 및 작용

- <38> 상기와 같은 목적을 달성하기 위한 본 발명의 일실시예에 따른 유기 반도체 물질을 이용한 박막트랜지스터는 기판 상에 형성된 베퍼층과; 상기 베퍼층 위로 형성되며 서로 이격하는 소스 및 드레인 전극; 상기 소스 전극과 드레인 전극의 이격한 영역을 포함하여 상기 소스 및 드레인 전극과 동시에 접촉하며 형성된 유기 반도체층과; 상기 유기 반도체층 상부로 상기 유기 반도체층과 동일한 형태로 형성된 게이트 절연막과; 상기 게이트 절연막 위로 상기 소스 및 드레인 전극 간 이격영역에 대응하여 형성된 게이트 전극을 포함한다.

- <39> 이때, 상기 게이트 전극은 상기 게이트 절연막과 동일한 형태이며, 상기 베퍼층은 질화실리콘(SiNx), 산화실리콘(SiO<sub>2</sub>), SiNxOy 중에서 선택되는 무기절연물질로 형성되거나 또는 PVP(poly vinyl pyrrolidone), PVA(polyvinyl alcohol), BCB(benzocyclobutene), PMMA(poly methyl meta acrylate) 중에서 선택되는 유기절연물질로 형성된 것이 특징이다.

- <40> 또한, 상기 유기 반도체층은 펜타신(pentacene)으로 이루어지며, 상기 게이트 절연막은 산화실리콘(SiO<sub>2</sub>), 또는 질화실리콘(SiNx) 등의 무기절연물질 또는 PVA(poly vinyl alcohol) 또는 기상 증착된 고분자물질인 폴리이미드(polyimide) 등의 유기절연물질로 이루어진 것이 특징이다.

- <41> 또한, 상기 소스 및 드레인 전극은 금(Au), ITO, 니켈(Ni), 납(Pb), 알루미늄(Al), 탄탈륨(Ta), 티타늄(Ti) 중에서 선택되는 금속물질 또는 PEDOT:PSS(poly ethylene dioxy thiophene : poly styrene sulfonate) 등의 유기 도전성 물질로 이루어진 것이 특징이다.

- <42> 본 발명의 일실시예에 따른 유기 반도체 물질을 이용한 박막트랜지스터를 구비한 액정표시장치용 어레이 기판은 기판 상에 형성된 베퍼층과; 상기 베퍼층 위로 형성되며 서로 이격하는 소스 및 드레인 전극과, 상기 소스 전극과 연결된 데이터 배선과; 상기 소스 및 드레인 전극과 이들 두 전극 사이의 이격영역을 포함하여 상기 데이터 배선 위로 형성된 유기 반도체층과; 상기 유기 반도체층 상부로 상기 유기 반도체층과 동일한 형태로 형성된 게이트 절연막과; 상기 게이트 절연막 위로 상기 소스 및 드레인 전극 간 이격영역에 형성된 게이트 전극 및 상기 게이트 전극과 연결되며 상기 데이터 배선과 교차하는 게이트 배선과; 상기 게이트 전극과 게이트 배선 위로 전면에 드레인 콘택홀을 갖는 보호층과; 상기 보호층 상부로 상기 드레인 콘택홀을 통해 상기 드레인 전극과 연결되는 화소전극을 포함한다.

- <43> 이때, 상기 유기 반도체층과 그 상부의 게이트 절연막에는 상기 드레인 전극을 노출시키는 제 1 콘택홀이 더욱 형성되며, 이때, 상기 게이트 절연막 위로 상기 제 1 콘택홀을 통해 상기 드레인 전극과 접촉하는 드레인 접촉 패드가 더욱 형성되며, 상기 드레인 콘택홀은 상기 드레인 접촉 패드를 노출시키는 것이 특징이며, 이때, 상기 화소전극은 상기 드레인 콘택홀을 통해 상기 드레인 접촉 패드와 접촉하는 것이 특징이다.

- <44> 또한, 상기 게이트 전극은 상기 게이트 절연막과 동일한 형태이며, 상기 베퍼층은 질화실리콘(SiNx), 산화실리콘(SiO<sub>2</sub>), SiNxOy 중에서 선택되는 무기절연물질로 형성되거나 또는 PVP(poly vinyl pyrrolidone), PVA(polyvinyl alcohol), BCB(benzocyclobutene), PMMA(poly methyl meta acrylate) 중에서 선택되는 유기절연물질로 형성된 것이 특징이다.

- <45> 또한, 상기 유기 반도체층은 펜타신(pentacene)으로 이루어지며, 상기 게이트 절연막은 산화실리콘(SiO<sub>2</sub>), 또는 질화실리콘(SiNx) 등의 무기절연물질 또는 PVA(poly vinyl alcohol) 또는 기상 증착된 고분자물질인 폴리이미드(polyimide) 등의 유기절연물질로 이루어진 것이 특징이다.

- <46> 또한, 상기 소스 및 드레인 전극은 금(Au), ITO, 니켈(Ni), 납(Pb), 알루미늄(Al), 탄탈륨(Ta), 티타늄(Ti) 중에서 선택되는 금속물질 또는 PEDOT:PSS(poly ethylene dioxy thiophene : poly styrene sulfonate) 등의 유기 도전성 물질로 이루어진 것이 특징이다.

- <47> 또한, 상기 기판은 플라스틱, 유기 또는 금속물질로 이루어진 것이 특징이다.

- <48> 본 발명의 일실시예에 따른 유기 반도체 물질을 이용한 박막트랜지스터를 구비한 액정표시장치용 어레이 기판의 제조 방법은 기판 위로 전면에 베퍼층을 형성하는 단계와; 상기 베퍼층 위로 서로 이격하는 소스 및 드레인 전극과, 상기 소스 전극과 연결된 데이터 배선을 형성하는 단계와; 상기 소스 및 드레인 전극의 이격영역을 포함하여 상기 데이터 배선과 소스 및 드레인 전극 위로 유기 반도체층과, 상기 유기 반도체층과 동일한 형태의 게이트 절연막과, 상기 게이트 절연막 위로 상기 소스 및 드레인 전극의 이격영역에 대응하여 게이트 전극과, 상기 게이트 전극과 연결되며 상기 데이터 배선과 교차하는 게이트 배선을 형성하는 단계와; 상기 게이트 전극과 게이트 배선 위로 제 1 콘택홀을 갖는 보호층을 형성하는 단계와; 상기 보호층 위로 상기 제 1 콘택홀을 통해 드레인 전극과 연결되는 화소전극을 형성하는 단계를 포함한다.

- <49> 이때, 상기 베퍼층은 질화실리콘(SiNx), 산화실리콘(SiO<sub>2</sub>), SiNxOy 중에서 선택되는 무기절연물질을 증착함으로써 형성하거나 또는 PVP(polyvinylpyrrolidone), PVA(polyvinyl alcohol), BCB(benzocyclobutene), PMMA(poly methyl meta acrylate) 중에서 선택되는 유기절연물질을 코팅하여 형성한 것이 특징이다.

- <50> 또한, 상기 소스 및 드레인 전극과 데이터 배선을 형성하는 단계는 금(Au), ITO, 니켈(Ni), 납(Pb), 알루미늄(Al), 탄탈륨(Ta), 티타늄(Ti) 중에서 선택되는 금속물질을 200°C 이하의 온도에서 증착하여 제 1 금속층을 형성하거나 또는 PEDOT:PSS(poly ethylene dioxy thiophene : poly styrene sulfonate)의 유기 도전성 물질을 상온에서 코팅하여 유기 도전성 물질층을 형성하는 단계와; 상기 제 1 금속층 또는 유기 도전성 물질층을 패터닝하는 단계를 포함한다.

- <51> 또한, 상기 유기 반도체층과, 게이트 절연막과 게이트 전극 및 게이트 배선을 형성하는 단계는 상기 소스 및 드레인 전극과 데이터 배선 위로 전면에 유기 반도체 물질을 진공 열 증착하여 유기 반도체 물질층을 형성하는 단계와; 상기 유기 반도체 물질층 위로 절연층을 형성하는 단계와; 상기 절연층 위로 포토레지스트 패턴을 형성하는 단계와; 상기 포토레지스트 패턴을 외부로 노출된 절연층 및 그 하부의 유기 반도체 물질층을 드라이 에칭하여 제거함으로써 상기 소스 및 드레인 전극의 이격영역을 포함하여 상기 소스 및 드레인 전극과 데이터 배선 위로 유기 반도체층과 그 위로 게이트 절연막을 형성하는 단계와; 상기 게이트 절연막 위로 제 2 금속물질을 증착함으로써 제 2 금속물질층을 형성하는 단계와; 상기 제 2 금속물질층을 패터닝함으로써 상기 게이트 전극과, 상기 게이트 전극과 게이트 배선을 형성하는 단계를 포함하며, 이때, 상기 유기 반도체층 및 게이트 절연막을 형성하는 단계는 상기 드레인 전극을 노출시키는 제 2 콘택홀을 형성하는 단계를 더욱 포함하며, 더욱이 상기 게이트 전극 및 게이트 배선을 형성하는 단계는 상기 제 2 콘택홀을 통해 상기 드레인 전극과 접촉하며 상기 게이트 전극과 이격하는 드레인 접촉 패드를 형성하는 단계를 더욱 포함한다. 이때, 상기 제 1 콘택홀은 상기 드레인 접촉 패드를 노출시키도록 형성하는 것이 바람직하며, 이때, 상기 화소전극은 상기 제 1 콘택홀을 통해 상기 드레인 접촉 패드와 접촉하도록 형성됨으로써 상기 드레인 전극과 연결되는 것이 특징이다.

- <52> 또한, 상기 유기 반도체층과, 게이트 절연막과 게이트 전극 및 게이트 배선을 형성하는 단계는 상기 소스 및 드레인 전극과 데이터 배선 위로 전면에 유기 반도체 물질을 진공 열 증착하여 유기 반도체 물질층을 형성하는 단계와; 상기 유기 반도체 물질층 위로 절연층을 형성하는 단계와; 상기 절연층 위로 제 2 금속물질을 증착하여 제 2 금속물질층을 형성하는 단계와; 상기 제 2 금속물질층을 패터닝하여 상기 소스 및 드레인 전극 간 이격영역에 대응하여 게이트 전극과, 상기 게이트 전극과 연결된 게이트 배선을 형성하는 단계와; 상기 게이트 전극 및 게이트 배선을 마스크로 하여 상기 게이트 전극 및 게이트 배선 외부로 노출된 절연층 및 하부의 유기 반도체 물질층을 드라이 에칭을 실시함으로써 유기 반도체층과, 게이트 절연막을 형성하는 단계를 포함하며, 이때, 상기 유기 반도체층과 그 상부의 게이트 절연막은 하부의 드레인 전극을 일부 노출시키며 형성되는 것이 특징이다. 또한 이때, 상기 제 1 콘택홀을 상기 유기 반도체층과 그 상부의 게이트 절연막은 외부로 노출된 부분의 드레인 전극을 노출시키며 형성되는 것이 특징이다.

- <53> 또한, 상기 유기 반도체층은 펜타신(pentacene)을 진공 열 증착하여 형성하는 것이 특징이며, 상기 게이트 절연막은 산화실리콘(SiO<sub>2</sub>), 또는 질화실리콘(SiNx) 등의 무기절연물질을 증착하거나 또는 PVA(poly vinyl alcohol) 또는 기상 증착된 고분자물질인 폴리이미드(polyimide) 등의 유기절연물질을 코팅하여 형성하는 것이 특징이다.

- <54> 삭제

- <55> 이하 도면을 참조하여 본 발명을 보다 상세하게 설명한다.

- <제 1 실시예>

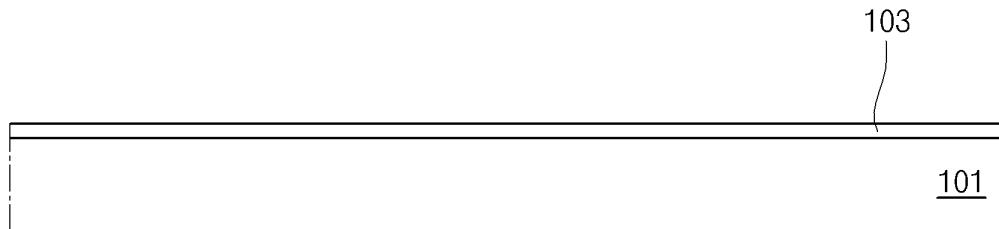

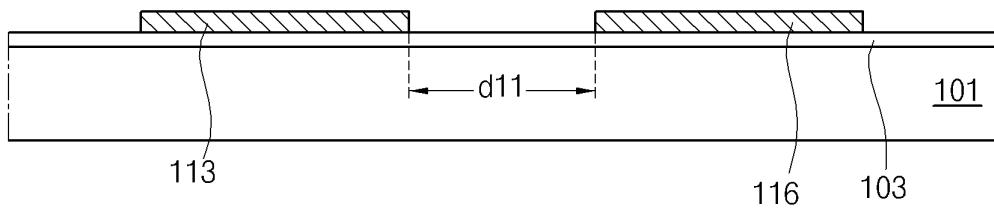

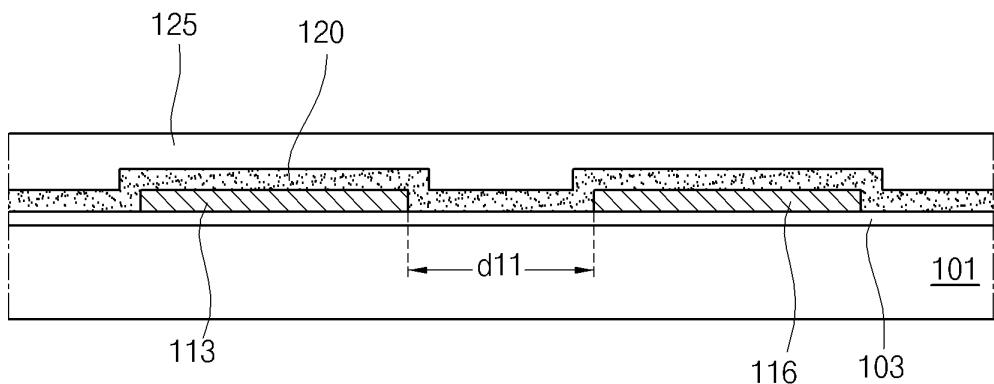

- <57> 도 4a 내지 4g는 본 발명의 제 1 실시예에 따른 유기 반도체 물질을 이용하여 박막트랜지스터 및 이를 구비한 액정표시장치용 어레이 기판을 제조하는 방법을 도시한 도면으로서, 어레이 기판상의 박막트랜지스터를 포함하는 하나의 화소영역에 대한 제조 공정별 단면도이다.

- <58> 도 4a에 도시한 바와 같이, 플라스틱, 유리 또는 절연층으로 코팅된 금속물질(버퍼층을 형성할 경우 상기 절연층은 없어도 무방)로 이루어진 절연기판(101) 상에 버퍼층(103)을 형성한다. 상기 버퍼층(103)을 형성하는 이유는 이후에 형성될 유기 반도체층의 결정성을 향상시키기 위함이며, 따라서, 상기 버퍼층(103)은 표면 거칠기(surface roughness)가 양호한 즉, 매우 매끄러운 표면 상태를 갖는 물질을 이용하는 것이 바람직하다.

- <59> 일례로서 매끄러운 표면을 갖는 무기절연물질로서는 질화실리콘(SiO<sub>2</sub>), 산화실리콘(SiNx), SiNxOy 등이 있으며, 이러한 무기절연물질로 상기 버퍼층(103)을 형성시에는 200°C 이하의 온도 분위기에서 증착하여 형성하는 것이 바람직하다.

- <60> 또한, 매끄러운 표면을 갖는 유기절연물질로서는 PVP(poly vinyl pyrrolidone), PVA(poly vinyl alcohol), BCB(benzocyclobutene), PMMA(poly methyl meta acrylate) 등이 있으며, 이러한 유기 절연물질은 상온의 분위기에서 도포 또는 코팅함으로써 형성할 수 있다.

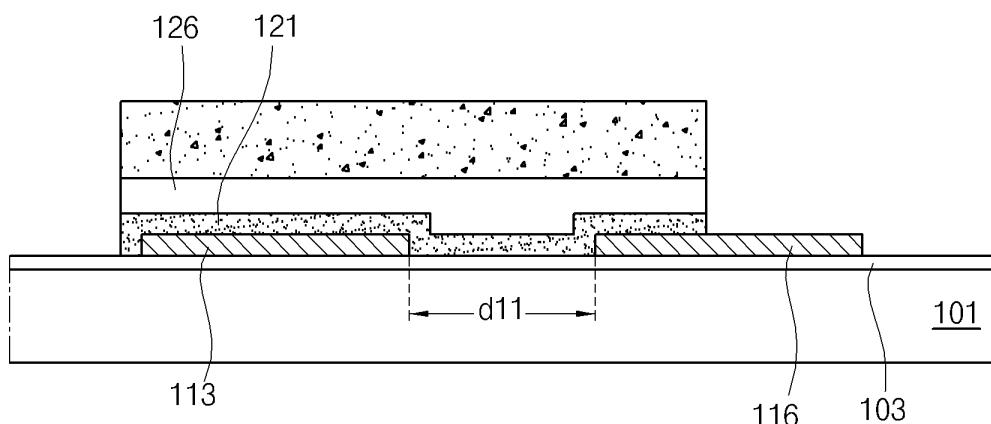

- <61> 다음, 도 4b에 도시한 바와 같이, 상기 버퍼층(103) 위로, 유기 반도체물질과 전기적 접촉이 우수한 금속 또는

도전성 유기물질을 증착 또는 도포하고, 이를 패터닝함으로써 소스 및 드레인 전극(113, 116)을 형성한다.

<62> 조금 더 상세히 설명하면, 추후 공정에 있어서 p타입 유기 반도체층을 형성할 경우, 홀(hole) 주입이 용이하도록 일함수(work function)가 비교적 높은 금속물질 예를들면 금(Au), ITO, 니켈(Ni), 납(Pb) 중에서 선택되는 금속물질 중 하나의 물질을 200°C 이하의 온도 분위기에서 스퍼터링(sputtering)을 통해 증착하여 금속층을 형성하거나, 또는 PEDOT:PSS(poly ethylene dioxy thiophene : poly styrene sulfonate) 등의 유기 도전성 물질을 도포하여 유기 도전성 물질층을 형성하고, n타입의 유기 반도체층을 형성할 경우, 비교적 일함수(work function)가 낮은 금속물질인 알루미늄(Al), 탄탈륨(Ta), 티타늄(Ti) 중에서 선택되는 물질 중 하나를 200°C 이하의 온도 분위기에서 스퍼터링(sputtering)을 통해 증착함으로써 금속층을 형성하고, 이후, 상기 금속층 또는 유기 도전성 물질층을 위로 포토레지스트를 도포하고, 이를 마스크를 이용한 노광하고, 노광된 포토레지스트층을 현상한 후, 식각함으로써 패터닝하여 도시한 바와 같은 서로 이격하는 소스 및 드레인 전극(113, 116)을 형성한다. 이때, 상기 서로 이격한 소스 및 드레인 전극(113, 116)은 마스크 공정에 의해 패터닝되어 형성하고 있는 바, 그 이격간격(d11)을 수  $\mu\text{m}$  내지 수십  $\mu\text{m}$ 에서 선택적으로 결정될 수 있다.

<63> 또한, 이때, 도면에는 나타나지 않았지만, 상기 소스 전극(113)과 연결되며 일방향으로 연장하는 데이터 배선을 동시에 형성한다.

<64> 다음, 도 4c에 도시한 바와 같이, 상기 소스 및 드레인 전극(113, 116)과 데이터 배선(미도시)위로 진공 열 증착기를 이용하여 유기 반도체 물질 예를들면 펜타신(pentacene)을 200°C이하의 온도 분위기에서 열 증착함으로써 전면에 유기 반도체 물질층(120)을 형성한다.

<65> 이 경우, 종래와는 달리 쉐도우 마스크(shadow mask) 등을 이용한 이베퍼레이션(evaporation)을 진행하여 증착하는 것보다 진공 열 증착기를 이용하여 쉐도우 마스크(shadow mask) 없이 열 증착함으로써 전면에 형성된 유기 반도체 물질층(120)의 표면 균일도가 우수한 것이 특징적인 면이 된다.

<66> 다음, 상기 전면에 형성된 유기 반도체 물질층(120) 위로 상기 유기 반도체 물질층(120)의 특성을 열화시키지 않는 절연물질을 증착 또는 코팅함으로써 절연층(125)을 형성한다. 이러한 유기 반도체 물질층과 접촉하여 이를 열화시키지 않는 절연물질로서는 산화실리콘(SiO<sub>2</sub>), 또는 질화실리콘(SiNx) 등의 무기절연물질과, PVA(poly vinyl alcohol) 또는 기상 증착된 고분자물질인 폴리이미드(polyimide) 등의 유기절연물질이 있다.

<67> 이때, 산화실리콘(SiO<sub>2</sub>), 또는 질화실리콘(SiNx) 등의 무기절연물질을 이용하여 상기 절연층(125)을 형성할 경우, 비교적 플라즈마에 의한 손상이 적은 e-beam을 이용한 증착장치 또는 CVD(chemical vapor deposition) 장치를 이용하여 형성하는 것이 바람직하며, 상기 유기 반도체 물질의 특성을 열화시키는 유기 용매, 또는 알코올 등이 포함되지 않은 용매를 사용한 유기 절연물질인 PVA(poly vinyl alcohol) 또는 폴리이미드(polyimide)를 이용하여 상기 절연층을 형성할 경우, 상온의 분위기에서 코팅 또는 도포함으로써 형성할 수 있다.

<68> 이때, 또한 상기 유기절연물질을 코팅한 후, 상기 무기절연물질을 연속하여 증착함으로써 이중구조의 절연층(미도시)을 형성할 수도 있다.

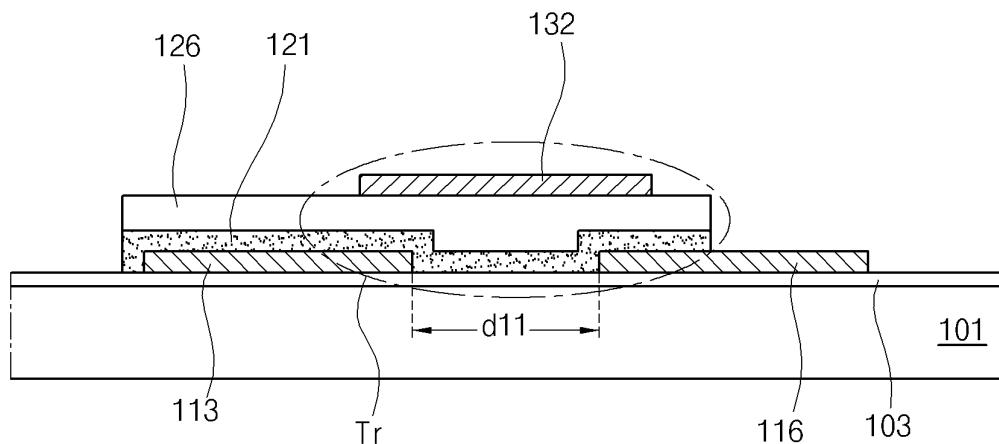

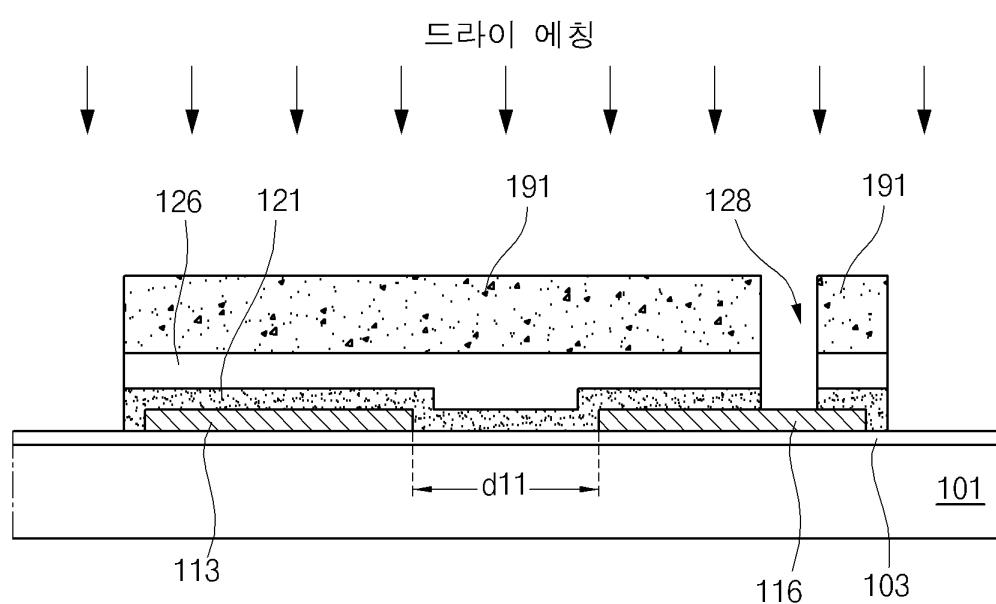

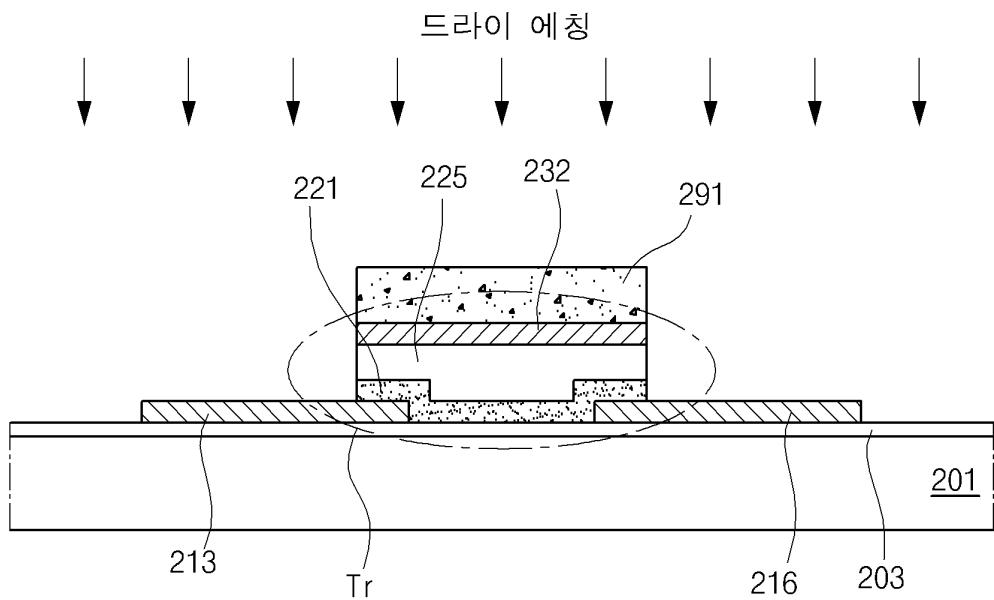

<69> 다음, 4d에 도시한 바와 같이, 상기 절연층(도 4c의 125) 위로 포토레지스트를 코팅하고, 이를 빛의 투과영역과 차단영역을 갖는 마스크를 이용하여 노광하고, 현상함으로써 포토레지스트 패턴(191)을 형성하고, 이후, 이방성 특성을 갖는 RIE(reactive ion etching)와 같은 드라이 에칭을 실시함으로써 상기 포토레지스트 패턴(191) 외부로 노출된 상기 절연층(도 4c의 125)과, 그 하부의 유기 반도체 물질층(도 4c의 120)을 제거함으로써 상기 소스 전극(113)과 드레인 전극(116) 사이의 이격된 영역을 포함하여 상기 소스 및 드레인 전극(113, 116)을 덮는 형태의 유기 반도체층(121)과, 그 상부로 상기 유기 반도체층(121)과 동일한 패턴 형태를 갖는 게이트 절연막(126)을 형성한다. 이때, 상기 드레인 전극(116)에 대해서는 그 일부가 노출되도록 하는 제 1 콘택홀(128)을 형성한다.

<70> 이때, 본 발명의 특성상, 상기 소스 전극(113)과 연결된 데이터 배선(미도시)의 상부에도 상기 유기 반도체층(121)과 게이트 절연막(126)을 형성한다. 이는 추후 공정에서 그 상부에 형성된 게이트 배선(미도시)이 형성됨으로써 교차되는 부분에서 쇼트(short)가 발생됨을 방지하기 위함이다.

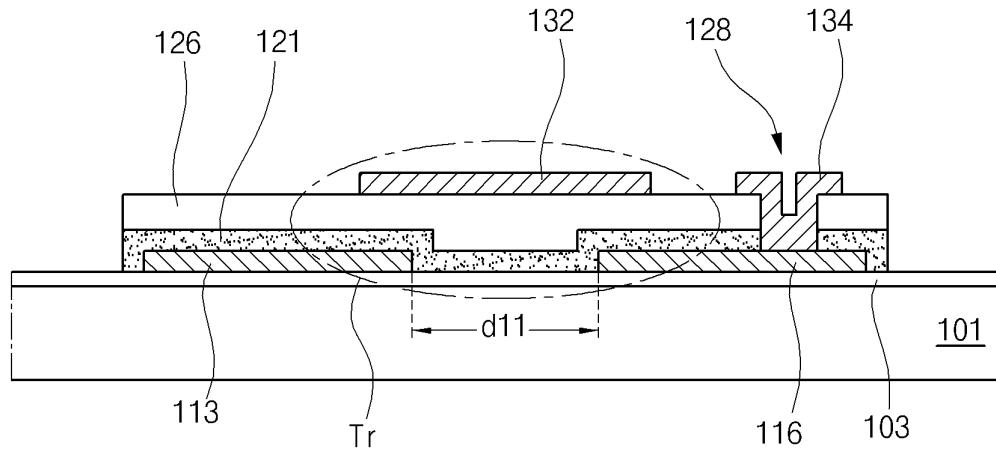

<71> 다음, 도 4e에 도시한 바와 같이, 상기 게이트 절연막(126) 상에 남아있는 포토레지스트 패턴(도 4d의 191)을 애싱(ashing)함으로써 제거하고, 상기 게이트 절연막(126) 위로 금속물질 예를들어 알루미늄(Al), 알루미늄 합금(AlNd), 크롬(Cr) 중 선택되는 하나를 200°C 이하의 온도 분위기에서 스퍼터(sputter) 또는 이베퍼레이터(evaporator) 등의 장치를 이용하여 증착함으로써 제 2 금속층을 형성하고, 이를 마스크 공정을 진행함으로써

패터닝하여 상기 소스 및 드레인 전극(113, 116)의 이격영역에 대응하여 상기 이격영역의 폭(d11)과 동일하거나, 또는 상기 이격영역의 폭(d11)보다 넓고 하부의 유기 반도체층(121)의 폭보다는 작거나 같은 크기의 폭을 갖는 게이트 전극(132)을 형성함으로써 하부로부터 소스 및 드레인 전극(113, 116)과, 유기 반도체층(121)과, 게이트 절연막(126)과 상기 게이트 전극(132)은 하나의 박막트랜지스터(Tr)를 형성하게 된다.

<72> 또한, 본 발명의 제조 공정상의 특징적인 것으로써, 상기 게이트 전극(132)을 형성함과 동시에 상기 게이트 전극(132)과 이격하며, 상기 제 1 콘택홀(128)을 통해 상기 드레인 전극(116)과 접촉하는 드레인 접촉 패드(134)를 형성한다.

<73> 이때, 상기 게이트 전극(132) 및 드레인 접촉 패드(134) 형성을 위한 상기 제 2 금속층의 패터닝 시, 습식(wet) 식각을 진행해도 무방하지만, 등방성 특성을 갖는 PE(plasma etching) 등의 드라이 에칭을 실시함으로써 상기 게이트 전극(132) 및 드레인 접촉 패드(134)를 형성하는 것이 바람직하다. 이는, 게이트 전극(132)을 패터닝 시, 유기 용매를 포함하는 식각액을 이용한 습식 식각을 진행하게 되면, 상기 게이트 절연막(126) 측면으로 유기 반도체층(121)이 노출되는 구조를 갖는 바, 비록 측면이라 할지라도 상기 식각액과 접촉함으로써 미소하더라도 손상되게 되므로 이를 방지하기 위함이다.

<74> 또한, 상기 게이트 전극(132)과 드레인 접촉 패드(134)의 형성 시 동일한 패터닝 공정에 의해 상기 게이트 전극(132)과 연결되며 하부의 데이터 배선(미도시)과 교차하여 화소영역을 정의하는 게이트 배선(미도시)을 형성한다.

<75> 변형예로써, 도 6a 및 6b를 참조하여 설명한다. 상기 도 6a 및 6b는 본 발명의 제 1 실시예의 변형예에 따른 유기 반도체 물질을 이용한 어레이 기판의 제조 과정 중, 유기 반도체층과 게이트 절연막 및 게이트 전극을 형성하는 공정을 도시한 단면도로서 이때, 상기 제 1 실시예와 동일한 구성요소에 대해서는 동일한 도면 부호를 부여하였다.

<76> 도 6a에 도시한 바와 같이, 제 1 실시예에서와 같이, 상기 드레인 접촉 패드(도 4e의 134)를 형성하지 않고, 상기 게이트 절연막(126)과 유기 반도체층(121) 형성 시, 상기 드레인 전극(116) 일부에 대해서는 노출되도록 형성 할 수도 있다. 이렇게 형성하는 이유는 추후 공정에서 상기 드레인 전극(116)은 화소전극과 전기적으로 연결하여야 하는데, 상기 게이트 전극과 화소전극이 접촉을 방지하고자 보호층을 더욱 형성하게 되며, 상기 드레인 전극을 게이트 절연막과 유기 반도체층 외부로 노출시키지 않을 경우, 상기 보호층을 패터닝 시 상기 드레인 전극을 노출시켜야 하는데, 이 경우 상기 게이트 절연막과 유기 반도체층을 함께 식각해야 하며, 각 패드부에 게이트 및 데이터 패드 콘택홀 형성 시 문제가 될 수 있기 때문에 이를 방지하기 위함이다.

<77> 이 경우, 도 6b를 참조하면, 상기 게이트 절연막(126) 상부로 상기 게이트 전극(132)을 형성하기 위한 제 2 금속층 형성 시, 상기 게이트 절연막(126) 외부로 노출된 드레인 전극(116)과 접촉하게 되지만, 상기 소스 및 드레인 전극(113, 116)을 이루는 금속물질과 상기 게이트 전극(132)을 이루는 금속물질은 서로 다른 재질을 사용함으로써 드라이 에칭 또는 습식식각 시 선택비를 달리하는 가스 또는 식각액을 이용하게 되면 선택적으로 제거가 가능함으로 문제되지 않는다.

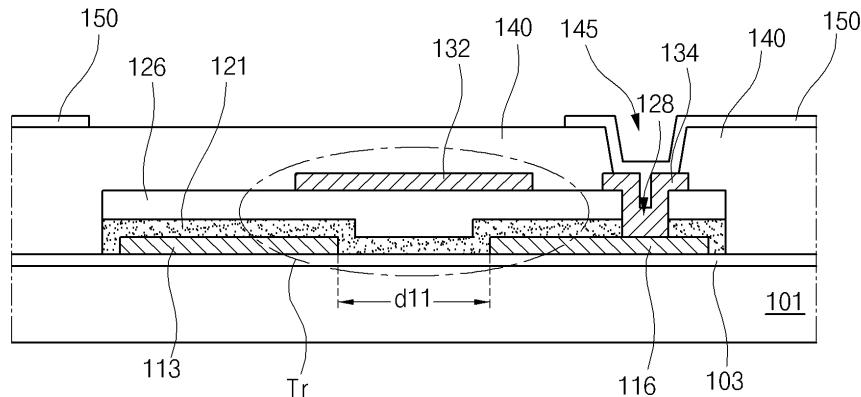

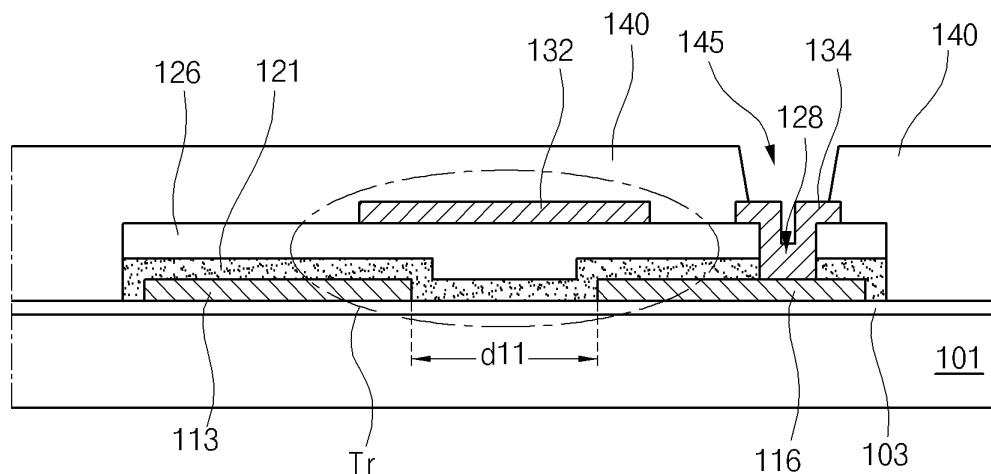

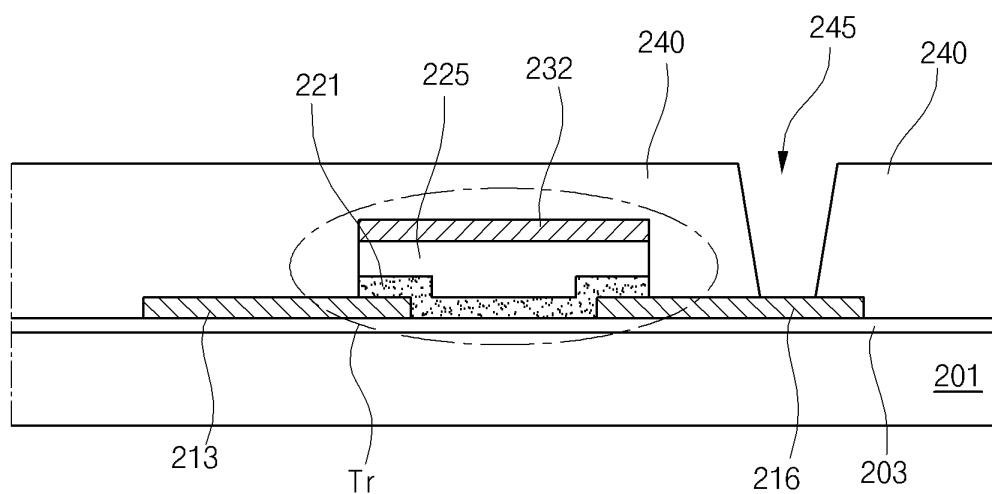

<78> 다음, 도 4f에 도시한 바와 같이, 상기 게이트 전극(132) 및 게이트 배선(미도시) 위로 전면에 유기 절연물질 예를들면, PVP(poly vinyl pyrrolidone), PVA(polyvinyl alcohol), BCB(benzocyclobutene), PMMA(poly methyl meta acrylate) 또는 포토 아크릴(photo acryl) 중에서 선택되는 하나의 물질을 도포 또는 코팅함으로써 전면에 그 표면이 평탄한 보호층(140)을 형성하고, 마스크 공정을 진행하여 상기 보호층(140)을 패터닝함으로써 상기 유기 반도체층(121) 외측으로 노출된 드레인 접촉 패드(134)를 노출시키는 드레인 콘택홀(145)을 형성한다.

<79> 이때, 도면에는 나타나지 않았으나, 상기 게이트 배선 및 데이터 배선 끝단에는 상기 게이트 배선과 데이터 배선을 자체로 게이트 패드 전극과 데이터 패드전극을 각각 형성하며, 게이트 및 데이터 패드부를 형성하는데, 각 패드부에 있어서 상기 드레인 콘택홀 형성 시 동시에 상기 게이트 및 데이터 패드전극을 각각 노출시키는 게이트 및 데이터 패드 콘택홀을 더욱 형성한다.

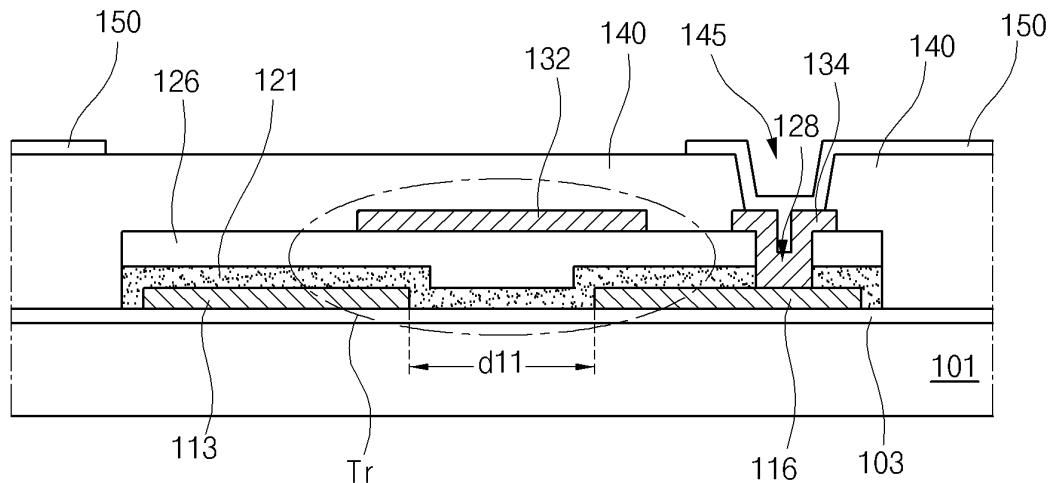

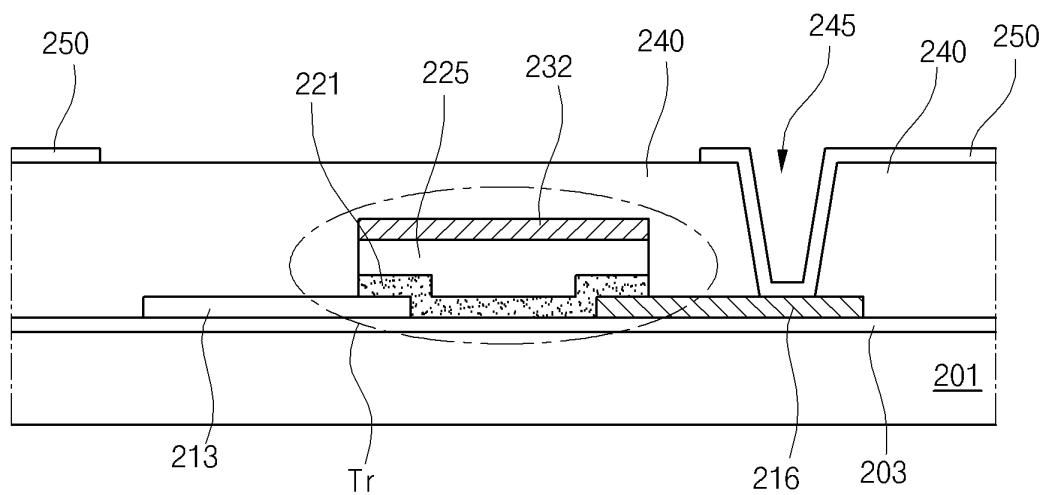

<80> 다음, 도 4g에 도시한 바와 같이, 상기 드레인 콘택홀(145)을 갖는 보호층(140) 위로 전면에 투명 도전성 물질 예를들면 ITO 또는 IZO를 200°C 이하에서 전면에 증착함으로써 투명 도전성 물질층을 형성하고, 이를 마스크 공정을 진행하여 패터닝함으로써 상기 드레인 콘택홀(145)을 통해 상기 드레인 전극(116)과 접촉하는 드레인 접촉 패드(134)에 연결된 화소전극(150)을 형성함으로써 어레이 기판(101)을 완성한다.

<81> 이때, 도면에 나타나지 않았지만, 상기 화소전극(150) 형성 시, 상기 게이트 및 데이터 패드부에 있어서는, 상기 게이트 및 데이터 패드전극과 각각 게이트 및 데이터 패드 콘택홀을 통해 접촉하는 게이트 및 데이터 보조패

드 전극을 형성한다.

<82> <제 2 실시예>

도 5a 내지 5f는 본 발명의 제 2 실시예에 따른 유기 반도체 물질을 이용하여 박막트랜지스터 및 이를 구비한 액정표시장치용 어레이 기판을 제조하는 방법을 도시한 도면으로서, 어레이 기판상의 박막트랜지스터를 포함하는 하나의 화소영역에 대한 제조 공정별 단면도이다. 본 발명의 제 2 실시예에 있어, 제 1 실시예와 동일하게 진행되는 부분에 대해서는 간단히 설명한다.

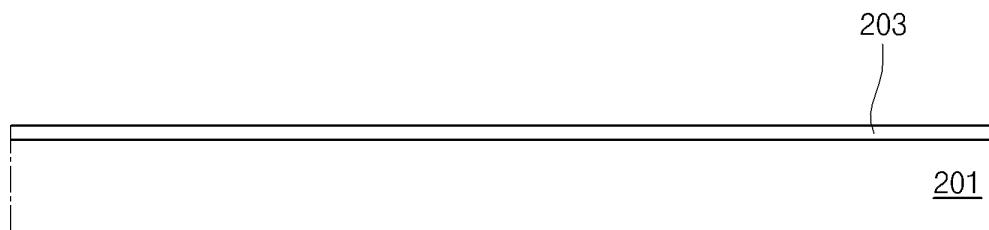

<84> 도 5a에 도시한 바와 같이, 플라스틱, 유리 또는 절연층으로 코팅된 금속물질(버퍼층을 형성할 경우 상기 절연층은 없어도 무방)로 이루어진 절연기판(201) 상에 버퍼층(203)을 형성한다. 상기 버퍼층(203)을 형성하는 이유 및 상기 버퍼층(203)을 형성하는 물질에 대해서는 제 1 실시예에 언급하고 있는 바, 설명은 생략한다.

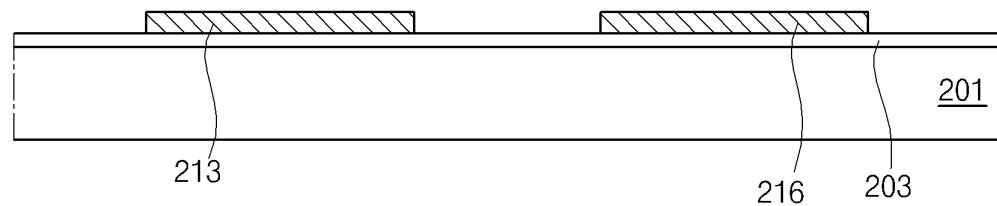

<85> 다음, 도 5b에 도시한 바와 같이, 상기 버퍼층(203) 위로, 유기 반도체물질과 전기적 접촉이 우수한 금속물질 예를들면 금(Au), ITO, 니켈(Ni), 납(Pb), 알루미늄(Al), 탄탈륨(Ta), 티타늄(Ti) 중에서 선택되는 하나의 물질을 200°C 이하의 분위기에서 증착함으로써, 또는 도전성 유기 물질 예를들면 PEDOT:PSS(poly ethylene dioxy thiophene : poly styrene sulfonate)을 코팅함으로써 금속층 또는 도전성 유기 물질층을 형성하고, 이를 200°C 이하의 분위기에서 패터닝함으로써 소스 및 드레인 전극(213, 216)과, 상기 소스 전극(213)과 연결되며 일방향으로 연장하는 데이터 배선(미도시)을 형성한다.(이때, 추후 형성될 유기 반도체층의 타입에 따라 상기 소스 및 드레인 전극(213, 216)을 형성하는 금속물질을 일함수(work function)의 높고 낮음으로 선택해야 하며, 이는 제 1 실시예에 언급한 바, 그 설명은 생략한다.)

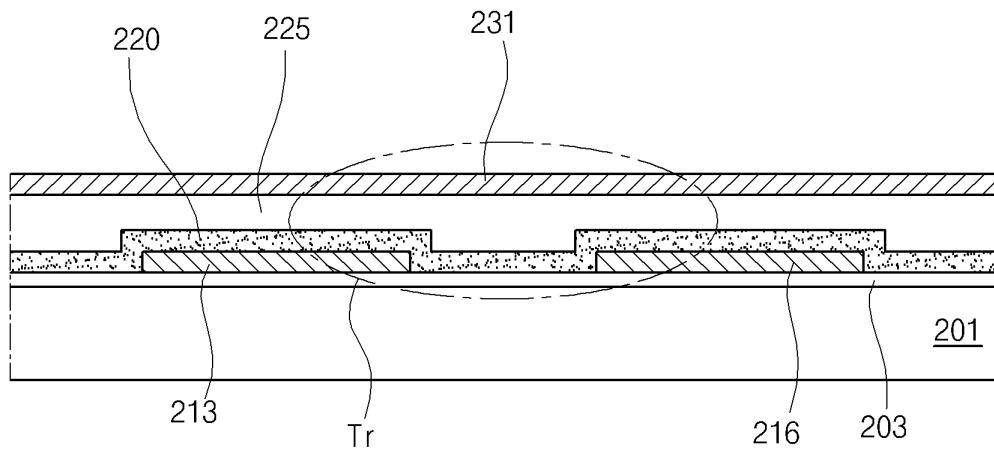

<86> 다음, 도 5c에 도시한 바와 같이, 상기 소스 및 드레인 전극(213, 216)과 데이터 배선(미도시)이 형성된 기판(201) 상에 진공 열 증착기를 이용하여 유기 반도체 물질 예를들면 펜타실(pentacene)을 200°C 이하의 온도 분위기에서 열 증착함으로써 전면에 유기 반도체 물질층(220)을 형성한다.

<87> 이 경우, 종래와는 달리 쉐도우 마스크(shadow mask) 등을 이용한 이베퍼레이션(evaporation)을 진행하여 증착하는 것보다 진공 열 증착기를 이용하여 열 증착함으로써 형성된 상기 유기 반도체 물질층(220)의 표면 균일도가 우수한 것이 특징적인 면이 된다.

<88> 다음, 상기 전면에 형성된 유기 반도체 물질층(220) 위로 상기 유기 반도체 물질층(220)의 특성을 열화시키지 않는 절연물질을 증착 또는 코팅함으로써 절연층(225)을 형성한다.

<89> 상기 유기 반도체 물질층(225)의 특성을 열화시키지 않는 절연물질로는 무기절연물질 중에서는 산화실리콘(SiO<sub>2</sub>), 또는 질화실리콘(SiNx) 등이며, 유기 절연물질 중에는 유기 용매, 또는 알코올 등이 포함되지 않은 것을 특징으로 하는 PVA(poly vinyl alcohol) 또는 기상 증착된 고분자물질인 폴리이미드(polyimide) 등이 있다.

<90> 이때, 산화실리콘(SiO<sub>2</sub>), 또는 질화실리콘(SiNx) 등의 무기절연물질을 이용하여 상기 절연층(225)을 형성할 경우, 비교적 플라즈마 손상이 적은 e-beam을 이용한 증착장치 또는 CVD(chemical vapor deposition) 장치를 이용하여 증착 형성하는 것이 바람직하며, 상기 PVA(poly vinyl alcohol) 또는 폴리이미드(polyimide)의 유기절연물질을 이용하여 상기 절연층(225)을 형성할 경우에는 상기 유기절연물질을 도포하거나 또는 코팅함으로써 형성 할 수 있다.

<91> 또한, 상기 유기절연물질을 코팅한 후, 그 위로 무기절연물질을 증착함으로써 이중구조의 절연층을 형성할 수도 있다.

<92> 다음, 상기 절연층(225) 위로 금속물질 예를들어 알루미늄(Al), 알루미늄 합금(AlNd), 크롬(Cr) 중 선택되는 하나를 200°C 이하의 온도 분위기에서 스퍼터(sputter) 또는 이베퍼레이터(evaporator) 등의 장치를 이용하여 증착하여 제 2 금속층(231)을 형성한다.

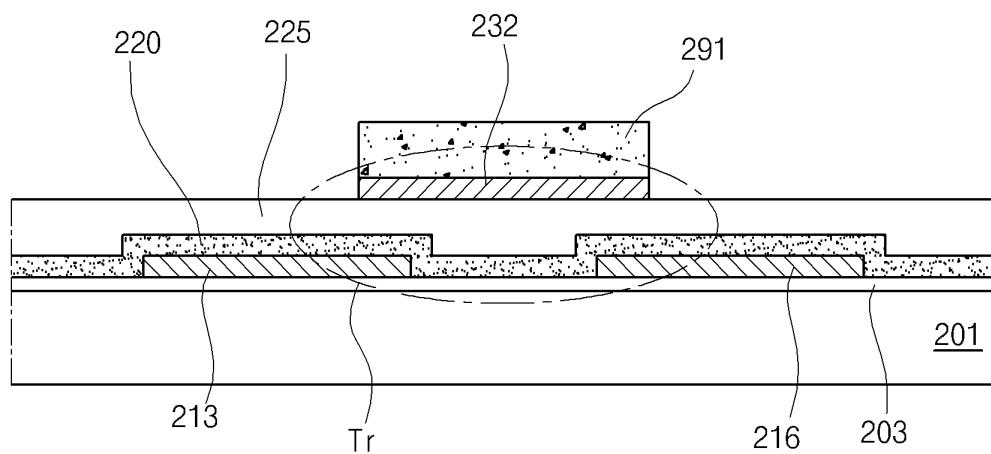

<93> 다음, 도 5d에 도시한 바와 같이, 상기 제 2 금속층(도 5c의 231) 위로 포토레지스트를 전면에 도포하여 포토레지스트층(미도시)을 형성하고, 빛의 투과영역과 반사영역을 갖는 마스크(미도시)를 상기 포토레지스트층(미도시) 상부로 위치시킨 후, 상기 마스크(미도시)를 통해 상기 포토레지스트층(미도시)의 노광을 실시한다.

<94> 이후, 상기 마스크를 통해 노광된 포토레지스트층(미도시)을 현상함으로서 포토레지스트 패턴(291)을 형성한다. 이 경우, 상기 유기 반도체 물질층(220)의 측면이 현상액 등에 노출되나 기판(201)의 테두리부에 형성된 상기 유기 반도체 물질층(220)은 추후 공정에서 제거되는 바, 문제되지 않는다.

- <95> 다음, 상기 포토레지스트 패턴(291) 외부로 노출된 제 2 금속층(도 5c의 231)을 식각함으로써 게이트 전극(232)과 하부의 데이터 배선(미도시)과 교차하여 화소영역을 정의하는 게이트 배선(미도시)을 형성한다. 이 경우 상기 제 2 금속층(도 5c의 231)의 식각은 습식(wet)이든 아니면 건식(dry)이든 어느 식각방법을 이용해도 무방하다.

- <96> 이때, 상기 게이트 전극(232)은 하부의 서로 마주하는 소스 및 드레인 전극(213, 216)의 서로 마주대하는 끝단과 소정 폭 중첩되어 형성되는 것이 바람직하다. 이는 추후 상기 게이트 전극(232)을 식각 마스크로 하여 하부의 절연층(225) 및 유기 반도체 물질층(220)을 식각하게 되는데, 상기 게이트 전극(232)과 동일한 형태로 유기 반도체층이 형성되고, 상기 유기 반도체층은 반드시 상기 소스 및 드레인 전극(213, 216)과 동시에 접촉하는 구조가 되어야 하기 때문이다.

- <97> 다음, 도 5e에 도시한 바와 같이, 상기 게이트 전극(232)과 게이트 배선(미도시)이 형성된 기판(201)에 있어, 상기 게이트 전극(232)과 게이트 배선(미도시)(또는 상기 게이트 전극(232)과 게이트 배선(미도시) 상부에 남아 있는 포토레지스트 패턴(도 5d의 291))을 식각 마스크로 하여 이방성(anisotropic) 특성을 갖는 RIE(reactive ion etching)와 같은 드라이 에칭을 실시함으로써 상기 게이트 전극(232) 및 게이트 배선(미도시) 외부로 노출된 절연층(도 5d의 225)과 그 하부의 유기 반도체 물질층(도 5d의 220)을 제거한다. 따라서, 기판(201)의 최하부로부터 상기 소스 및 드레인 전극(213, 216)과, 그 상부로 유기 반도체층(221) 및 게이트 절연막(226)과, 상기 게이트 절연막(226) 상부로 게이트 전극(232)으로 구성된 박막트랜지스터(Tr)가 형성된다.

- <98> 이때, 상기 게이트 전극(232) 및 게이트 배선(미도시)에 의해 가려지지 않은 부분에 대해서는 상기 절연층(도 5d의 220) 및 그 하부의 유기 반도체 물질층(도 5d의 220)은 드라이 에칭에 의해 모두 제거되는 바, 상기 소스 및 드레인 전극(213, 216)과 데이터 배선(미도시)에 있어서도, 상기 게이트 배선(미도시)과 교차함으로써 중첩되는 영역을 제외한 부분이 노출되지만, 상기 게이트 배선(미도시)과 교차하는 영역에 있어서는 여전히 유기 반도체층(221)과 그 상부로 게이트 절연막(226)이 형성되는 바, 쇼트(short) 등의 문제는 발생하지 않음을 알 수 있다.

- <99> 다음, 도 5f에 도시한 바와 같이, 상기 게이트 전극(232)과 게이트 배선(미도시) 상부에 남아 있는 포토레지스트 패턴(도 5e의 291)을 애싱(ashing)을 실시함으로써 제거한다. 이때, 상기 포토레지스트 패턴(도 5e의 291)은 상기 게이트 절연막(226)과 유기 반도체층(221)을 형성하기 위한 드라이 에칭을 실시하기 전에 먼저 애싱(ashing)을 실시함으로써 제거될 수도 있다.

- <100> 이후, 상기 게이트 전극(232)과 게이트 배선(미도시) 및 노출된 소스 및 드레인 전극(213, 216)과 데이터 배선(미도시) 위로 전면에 유기 절연물질 예를들면, PVP(poly vinyl pyrrolidone), PVA(polyvinyl alcohol), BCB(benzocyclobutene), PMMA(poly methyl meta acrylate), 폴리아미드(polyimide) 또는 포토 아크릴(photo acryl) 중에서 선택되는 하나의 물질을 도포 또는 코팅함으로써 유기절연물질 특성 상 하부의 단차에 영향없이 전면에 그 표면이 평탄한 보호층(240)을 형성하거나, 또는 무기 절연물질인 산화실리콘(SiO<sub>2</sub>) 또는 질화실리콘(SiNx)을 플라즈마에 의한 손상이 적은 e-beam 또는 CVD 장치를 이용하여 200°C 이하에서 증착함으로써 보호층(240)을 형성한다.

- <101> 따라서, 상기 게이트 전극(232)과 게이트 배선(미도시) 형성 시, 드라이 에칭에 의해 절연층(도 5d의 225) 및 유기 반도체 물질층(도 5d의 220)이 제거됨으로써 외부로 노출된 상기 데이터 배선(미도시)과 소스 및 드레인 전극(213, 216)과, 최상부에 형성된 게이트 전극(232) 및 게이트 배선(미도시)이 모두 상기 보호층(240)에 의해 덮혀지게 됨을 알 수 있다.

- <102> 다음, 상기 보호층(240) 위로 포토레지스트층(미도시)을 형성하고 그 상부로 마스크(미도시)를 위치시킨 후, 노광하고 상기 포토레지스트층(미도시)을 현상하여 포토레지스트 패턴(미도시)을 형성 후, 상기 포토레지스트 패턴(미도시) 외부로 노출된 보호층(240)을 식각함으로써 상기 유기 반도체층(221) 외측으로 노출된 상기 드레인 전극(216)을 노출시키는 드레인 콘택홀(245)을 형성하거나 또는 상기 보호층(240)이 그 자체로 감광성 특성을 갖는 유기절연 물질(예를들어 감광성의 BCB 또는 포토아크릴(photo acryl))로 이루어진 경우 상기 보호층(240) 위로 마스크(미도시)를 위치시킨 후, 노광하고 현상함으로써 상기 드레인 전극(216)을 노출시키는 드레인 콘택홀(245)을 형성한다.

- <103> 이때, 도면에 나타나지는 않았지만, 동일한 공정에 의해 게이트 배선 및 데이터 배선 끝단이 위치한 영역 즉 게이트 및 데이터 패드부에 있어서도 상기 게이트 패드 전극 및 데이터 패드 전극을 노출시키는 게이트 및 데이터 패드 콘택홀을 형성한다.

<104> 다음, 도 5g에 도시한 바와 같이, 상기 드레인 콘택홀(245)을 갖는 보호층(240) 위로 전면에 투명 도전성 물질 예를들면 ITO 또는 IZO를 200°C 이하에서 전면에 증착함으로서 투명 도전성 물질층(미도시)을 형성하고, 이를 마스크 공정을 진행하여 패터닝함으로써 상기 드레인 콘택홀(245)을 통해 상기 드레인 전극(216)과 접촉하는 화소전극(250)을 형성함으로써 어레이 기판(201)을 완성한다.

<105> 이때, 도면에 나타나지 않았지만, 상기 화소전극(250) 형성 시, 게이트 및 데이터 패드부에 있어서는, 상기 게이트 및 데이터 패드전극과 각각 게이트 및 데이터 패드 콘택홀을 통해 접촉하는 게이트 및 데이터 보조패드 전극을 형성한다.

### 발명의 효과

<106> 본 발명에 의한 유기 반도체물질을 이용한 액정표시장치용 어레이 기판은 수분 및 약액(유기 용제 또는 알코올 등을 포함하는 현상액 또는 식각액)에 취약한 유기 반도체 물질을 이용하여 손상없이 유기 반도체층을 형성할 수 있는 제조방법을 제공하는 효과가 있으며, 나아가, 탑 게이트(top gate)의 보텀 콘택트(bottom contact) 구조로서 상기 유기 반도체층의 밑면이 소스 및 드레인 전극의 표면과 접촉하도록 하는 구조의 박막트랜지스터 및 이를 구비한 액정표시장치용 어레이 기판을 제안함으로써 소자 특성을 향상시키는 효과가 있다.

<107> 또한, 그 표면 상태가 매끈한 것을 특징으로 하는 버퍼층을 형성하고, 상기 버퍼층 위로 유기 반도체층을 형성하는 것을 제안함으로써 상기 유기 반도체층의 결정성을 향상시켜 소자 특성을 향상시키는 더욱 향상시키는 효과가 있다.

### 도면의 간단한 설명

<1> 도 1은 일반적인 액정표시장치의 분해사시도.

<2> 도 2는 종래의 유기 반도체 물질을 이용한 일반적인 박막트랜지스터의 단면도.

<3> 도 3은 종래의 유기 반도체 물질을 이용하여 보텀 게이트(bottom gate)의 탑 콘택트(top contact) 구조로 형성된 박막트랜지스터의 단면도.

<4> 도 4a 내지 4g는 본 발명의 제 1 실시예에 따른 유기 반도체 물질을 이용하여 액정표시장치용 어레이 기판을 제조하는 방법을 도시한 것으로 박막트랜지스터를 포함하는 하나의 화소영역에 대한 제조 공정별 단면도.

<5> 도 5a 내지 5g는 본 발명의 제 2 실시예에 따른 유기 반도체 물질을 이용하여 액정표시장치용 어레이 기판을 제조하는 방법을 도시한 것으로 박막트랜지스터를 포함하는 하나의 화소영역에 대한 제조 공정별 단면도.

<6> 도 6a 및 6b는 본 발명의 제 1 실시예의 변형예에 따른 유기 반도체 물질을 이용하여 액정표시장치용 어레이 기판을 제조하는 방법을 도시한 것으로 박막트랜지스터를 포함하는 하나의 화소영역에 대한 제조 공정별 단면도.

<7> <도면의 주요부분에 대한 부호의 설명>

<8> 101 : 기판                          103 : 버퍼층

<9> 113 : 소스 전극                          116 : 드레인 전극

<10> 121 : 유기 반도체층                          126 : 게이트 절연막

<11> 128 : 제 1 콘택홀                          132 : 게이트 전극

<12> 134 : 드레인 접촉 패드                          140 : 보호층

<13> 145 : 제 2 콘택홀                          150 : 화소전극

<14> Tr : 박막트랜지스터

<15>

도면

도면1

도면2

도면3

도면4a

도면4b

도면4c

도면4d

도면4e

도면4f

도면4g

도면5a

도면5b

도면5c

도면5d

도면5e

도면5f

도면5g

도면6a

도면6b