(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4281036号

(P4281036)

(45) 発行日 平成21年6月17日(2009.6.17)

(24) 登録日 平成21年3月27日(2009.3.27)

(51) Int.Cl.

F 1

H02J 7/02 (2006.01)

H02J 7/02

H

G01R 19/165 (2006.01)

G01R 19/165

M

G01R 31/36 (2006.01)

G01R 31/36

A

請求項の数 3 (全 9 頁)

(21) 出願番号

特願2000-365270 (P2000-365270)

(22) 出願日

平成12年11月30日 (2000.11.30)

(65) 公開番号

特開2002-171681 (P2002-171681A)

(43) 公開日

平成14年6月14日 (2002.6.14)

審査請求日

平成19年11月1日 (2007.11.1)

(73) 特許権者 304021440

株式会社ジーエス・ユアサコーポレーション

京都府京都市南区吉祥院西ノ庄猪之馬場町

1番地

(72) 発明者 小西 大助

京都府京都市南区吉祥院西ノ庄猪之馬場町

1番地 日本電池株式会社内

審査官 矢島 伸一

最終頁に続く

(54) 【発明の名称】組電池装置

(57) 【特許請求の範囲】

## 【請求項 1】

複数の単位電池が直列接続されてなる組電池と、前記各単位電池毎にサンプルホールド用スイッチを介して並列に設けられた複数のコンデンサと、該複数のコンデンサの両極間の電圧を測定する電圧検出手段とを備え、かつ上記複数のコンデンサが互いに直列接続されてコンデンサ群が構成され、上記電圧検出手段には、前記複数の各コンデンサの両極から引き出された複数の計測ラインが接続され、それら計測ラインに選択スイッチが備えられ、前記サンプルホールド用スイッチを一斉にオンすることにより、前記各単位電池の電圧を前記各複数のコンデンサに同時にホールドし、上記電圧検出手段が、各コンデンサ両端電圧を低電位側コンデンサから順次電圧検出手段に入力すると共に、計測済みコンデンサを零電圧に放電させるよう選択スイッチをオンオフ制御し、前記各コンデンサの両極間の電圧を検出するよう構成していることを特徴とする組電池装置。

## 【請求項 2】

上記サンプルホールド用スイッチをオン状態から一斉にオフさせるスイッチ制御手段を備えていることを特徴とする請求項 1 記載の組電池装置。

## 【請求項 3】

上記電圧検出手段には、前記各コンデンサの両極から引き出された複数の計測ラインがバッファアンプを介して接続され、前記バッファアンプの出力が電圧検出手段に対して規定電圧範囲以上の過電圧となって印加されることを防止するための過電圧リミッタ回路が、バッファアンプと電圧検出手段との間に設けられていることを特徴とする請求項 1 また

は 2 記載の組電池装置。

**【発明の詳細な説明】**

**【0001】**

**【発明の属する技術分野】**

本発明は、複数の単位電池を直列接続して構成された組電池装置において、各単位電池の電圧を検出する回路構成に特徴を有するものに関する。

**【0002】**

**【従来の技術】**

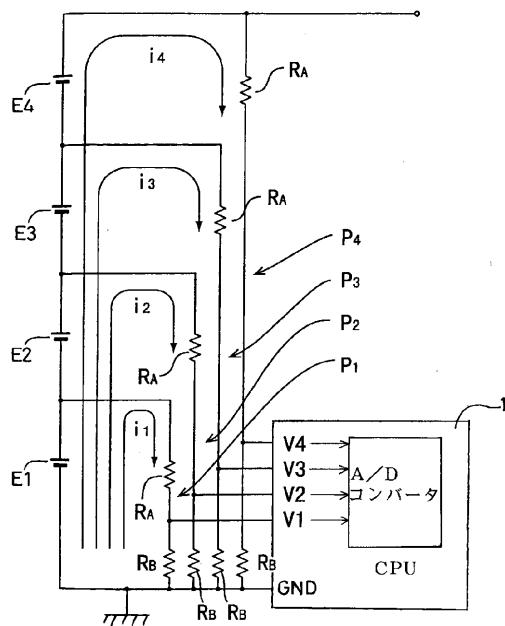

例えば、電気自動車の動力用バッテリーは多数の単位電池を直列接続して所要の高電圧を確保した組電池により構成されている。このような電池システムでは、各単位電池の電圧にはばらつきが生ずると、電池システムの信頼性が低下するおそれがあるため、各単位電池の電圧を検出して、各単位電池が所定の状態にあるか否かを監視するようにしている。10

**【0003】**

各単位電池の電圧を検出するためには、一般に、図 5 に示すような構成が利用される。ここでは、単位電池は図面の簡略化のために 4 個のみ図示しており、各単位電池 E 1 ~ E 4 の例えれば正極側の出力端子と、グランドライン GND との間に抵抗 RA, RB を直列接続してなる分圧回路 P 1 ~ P 4 が接続されると共に、各分圧回路 P 1 ~ P 4 における抵抗 RA, RB 間の共通接続点は、電圧検出用の CPU 1 に接続されている。この CPU 1 では、20

各単位電池 E 1 の電圧 V 1 と、単位電池 E 1 と E 2 とを合わせた電圧 V 2 と、単位電池 E 1 ~ E 3 を合わせた電圧 V 3 と、単位電池 E 1 ~ E 4 を合わせた電圧 V 4 とを、順次にサンプリングして検出すると共に、これら V 1 ~ V 2 を CPU 1 に備えた A / D 変換器にてデジタル信号化し、次式に従って各単位電池 E 1 ~ E 4 の電圧 VE1 ~ VE4 を求める。なお、下式において k は分圧比で決まる比例常数である。

**【0004】**

$$VE1 = k \cdot V 1$$

$$VE2 = k \cdot (V 2 - V 1)$$

$$VE3 = k \cdot (V 3 - V 2)$$

$$VE4 = k \cdot (V 4 - V 3)$$

**【0005】**

**【発明が解決しようとする課題】**

ところで、上述の組電池装置では、最終的に検出したいものは、各単位電池 E 1 ~ E 4 の個々の電圧であるが、そのために複数の単位電池が直列した大電圧 (V 2 ~ V 4) を検出し、それらの大電圧同士の差に基づいて単位電池の個々の電圧を算出している。このため、CPU 1 の分解能が十分に発揮されず、検出精度が低下するという問題が生じる。即ち、CPU 1 における A / D 変換器の分解能を例えれば 10 ビットとした場合に、1 つの単位電池の電圧を直に A / D 変換器に取り込むときと、単位電池を 4 つ直列した大電圧を A / D 変換器に取り込むときとを比較すると、前者では、1 つの単位電池の電圧に  $2^{10}$  の分解能を割り当てる事ができるが、後者では、1 つの単位電池の電圧に  $2^{10} / 4$  の分解能しか割り当てる事ができず、前者に比べて後者は分解能が低下し、従って、単位電池の個々の電圧の検出精度が低くなる。3040

**【0006】**

また、上述の組電池装置では、上記電圧 V 1 ~ V 4 を順次にサンプリングして検出しているので、例えば、最初に検出した単位電池の検出電圧に対し、最後に検出した単位電池の検出電圧には、検出タイミングのずれに伴う電圧変動分が含まれることとなり、単位電池同士の正確な電圧差を求められない。一方、上記電圧 V 1 ~ V 4 を、一度に検出すべく、同時に複数の電圧検出を行うことが可能な CPU (A / D コンバータ) を設けると、コストがかかってしまう。

**【0007】**

さらに、上述したシステムでは、各分圧回路 P 1 ~ P 4 に流れる放電電流 i 1 ~ i 4 により、各単位電池 E 1 ~ E 4 の容量にはばらつきが発生する。すなわち、図 5 に示すように、放50

電電流  $i_1$  は単位電池  $E_1$  にのみ流れるが、放電電流  $i_2$  は単位電池  $E_1, E_2$  の双方に流れ、放電電流  $i_3$  は単位電池  $E_1, E_2, E_3$  に流れる…、という関係になっているため、グランドライン GND により近い単位電池  $E_1, E_2 \dots$  には、より多くの電流が常時流れることになる。このため、グランドラインに近い単位電池ほど容量を低下させてしまうのである。

#### 【0008】

本発明は上記事情に鑑みてなされたもので、その目的は、組電池を構成する各単位電池の電圧を高い精度で検出することが可能な組電池装置を提供することにある。

#### 【0009】

##### 【課題を解決するための手段】

請求項 1 の発明に係る組電池装置は、複数の単位電池が直列接続されてなる組電池と、前記各単位電池毎にサンプルホールド用スイッチを介して並列に設けられた複数のコンデンサと、該複数のコンデンサの両極間の電圧を測定する電圧検出手段とを備え、かつ上記複数のコンデンサが互いに直列接続されてコンデンサ群が構成され、上記電圧検出手段には、前記複数の各コンデンサの両極から引き出された複数の計測ラインが接続され、それら計測ラインに選択スイッチが備えられ、前記サンプルホールド用スイッチを一斉にオンすることにより、前記各単位電池の電圧を前記各複数のコンデンサに同時にホールドし、上記電圧検出手段が、各コンデンサ両端電圧を低電位側コンデンサから順次電圧検出手段に入力すると共に、計測済みコンデンサを零電圧に放電させるよう選択スイッチをオンオフ制御し、前記各コンデンサの両極間の電圧を検出するよう構成されていることを特徴とする。請求項 2 の発明に係る組電池装置は、請求項 1 記載の組電池装置において、上記サンプルホールド用スイッチをオン状態から一斉にオフさせるスイッチ制御手段を備えていることを特徴とする。

#### 【0010】

請求項 3 の発明に係る組電池装置は、請求項 1 または 2 に記載の組電池装置において、上記電圧検出手段には、前記各コンデンサの両極から引き出された複数の計測ラインがバッファアンプを介して接続され、前記バッファアンプの出力が電圧検出手段に対して規定電圧範囲以上の過電圧となって印加されることを防止するための過電圧リミッタ回路が、バッファアンプと電圧検出手段との間に設けられていることを特徴とする。

#### 【0011】

##### 【発明の作用及び効果】

<請求項 1 の発明> 請求項 1 の構成によれば、各単位電池毎に設けられたサンプルホールド用スイッチを一斉にオンすると、各単位電池の電圧が、各複数のコンデンサの両極間の電圧と同じになり、この両極間の電圧を電圧検出手段により測定することにより、各単位電池の電圧が測定される。これにより、各単位電池に分圧回路を接続しなくて済むから、従来のような、分圧回路に流れる放電電流によって各単位電池の容量にばらつきが発生するというようなことを防止できる。また、コンデンサが単位電池毎に設けられている為、サンプルホールド用スイッチの開閉のタイミングを調整することで、同じ時点での各単位電池の電圧を測定することが可能となる。さらに、各コンデンサの両極が順次に電圧検出手段に接続されて、そこにホールドされた単位電池一つ当たりの電圧が、電圧検出手段（例えは A/D 入力を有する電圧検出手段）によって検出される。これにより、電圧検出手段が有する分解能の全てを使って、単位電池一つ当たりの電圧を検出することが可能となり、従来のように、複数の単位電池が直列した大電圧に分解能を割り当てなければならないものに比べて、検出精度が向上する。

#### 【0012】

##### <請求項 2 の発明>

請求項 2 の構成によれば、スイッチ制御手段によりサンプルホールド用スイッチをオン状態から一斉にオフさせることにより、各コンデンサの両極間に各単位電池の同時刻における電圧がホールドされて単位電池の同時刻の電圧を検出することが可能となり、従来問題となっていた、検出タイミングのずれに伴う電圧変動分が検出結果に含まれなくなり、高

10

20

30

40

50

精度の電圧検出が可能となる。また、電圧測定中にはすべてのコンデンサが同時に単位電池から切斷されるので、電圧測定に伴う単位電池への影響を無くした状態での電圧測定が可能となる。

#### 【0013】

##### <請求項3の発明>

請求項3の構成によれば、各コンデンサの両極が順次に電圧検出手段に接続されて、そこにホールドされた単位電池一つ当たりの電圧が、電圧検出手段（例えばA/D入力を有する電圧検出手段）によって検出される。これにより、電圧検出手段が有する分解能の全てを使って、単位電池一つ当たりの電圧を検出することが可能となり、従来のように、複数の単位電池が直列した大電圧に分解能を割り当てなければならないものに比べて、検出精度が向上する。さらに、過電圧リミッタ回路により、所定個数以上のコンデンサが直列に電圧検出手段に接続されることがなくなり、電圧検出手段が過電圧の印加から保護される。

10

#### 【0014】

##### 【発明の実施の形態】

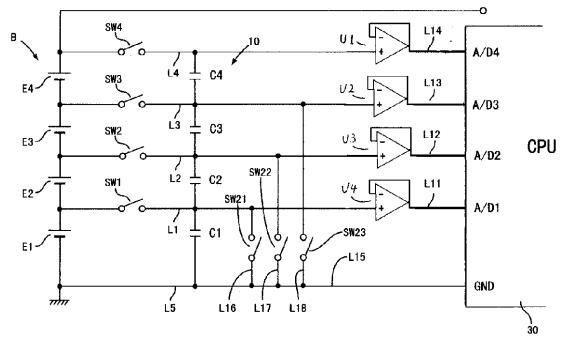

以下、本発明を、例えば電気自動車の動力用バッテリーシステムに適用した一実施形態について図1～4を参照しつつ、説明する。

#### 【0015】

図1は、本発明実施形態の組電池装置の基本回路構成図である。本発明における組電池に相当するバッテリーBは、図1に示すように、例えば4つの単位電池E1～E4を直列接続してなる。本実施形態の組電池装置では、上記4つの単位電池E1～E4に対応させて、4つのコンデンサC1～C4を直列接続したコンデンサ群10が備えられ、このコンデンサ群10とバッテリーBとの間では、互いに同じ順位に配置された各コンデンサC1～C4の両極と各単位電池E1～E4の両極とが、並列ラインL1～L5で接続されている。

20

#### 【0016】

すなわち、バッテリーBの正極は、並列ラインL4によって、コンデンサ群10の一端に接続されており、また、バッテリーBの負極は、並列ラインL5によってコンデンサ群10の他端に接続されている。さらに、バッテリーBのうち隣り合った単位電池同士の共通接続点とコンデンサ群10のうち隣り合ったコンデンサ同士の共通接続点とが並列ラインL1～L3で接続されている。

30

#### 【0017】

上記並列ラインL1～L4には、それぞれサンプルホールド用スイッチSW1～SW4が設けられている。このサンプルホールド用スイッチは、回路の開閉機能を有していれば基本的にどのようなスイッチでも良いが、下記図2や図3に示す構造のスイッチを好適に用いることができる。

#### 【0018】

本実施形態の組電池装置には、電圧検出手段として、A/Dコンバータを内蔵したCPU30が備えられている。このCPU30には、4つのA/D変換用の入力端子A/D1～A/D4と、1つのGND端子とが備えられ、これら各端子に各コンデンサC1～C4の両極から引き出された計測ラインがバッファアンプU1～U4を介して接続されている。

40

#### 【0019】

すなわち、前記した並列ラインL5を延長した計測ラインL15がCPU30のGND端子に接続され、前記した並列ラインL1～L4がバッファアンプに入力され、さらにこの計測ラインL11～L14が、CPU30の入力端子A/D1～A/D4にそれぞれ接続されている。

#### 【0020】

また、コンデンサに直接接続している計測ラインL16～L18には、選択スイッチSW21～SW23が設けられ、CPU30からの信号を受けてオンオフ制御されるようになっている。

50

**【 0 0 2 1 】**

本発明の組電池装置は、基本的には以上のような回路構成を採用することにより実施することができる。

**【 0 0 2 2 】**

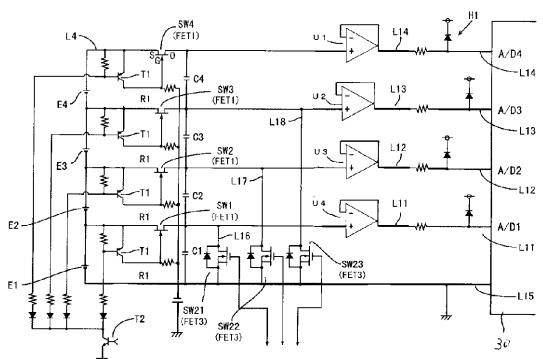

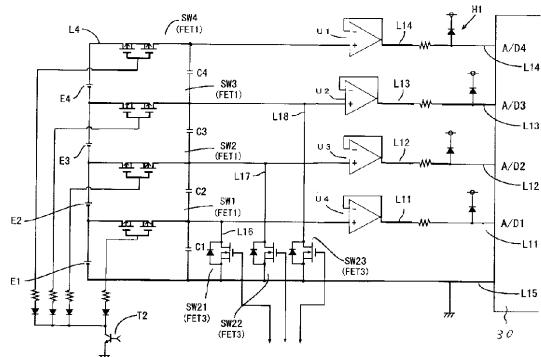

本発明の組電池装置を実使用上より好ましい状態で実施するには、例えば、図2、図3に示す回路構成を用いる。

**【 0 0 2 3 】**

図2、図3に示す組電池装置では、図1で示した基本回路構成に加え、バッファアンプU1～U4とCPU30との間に、抵抗とクランプダイオードとからなる過電圧リミッタ回路H1が設けられている。このように、計測ラインL11～L14の途中に、過電圧リミッタ回路H1を設けることにより、CPU30には一定以上の電圧がかからず、CPUの保護機能が果たされる。なお、コンデンサ端子とクランプダイオードとの間にバッファが介された構成となっているため、コンデンサにサンプルホールドした電圧のクランプダイオードへの流れ込みは防止されている。

**【 0 0 2 4 】**

また、図2、図3に示す組電池装置では、コンデンサに直接接続している計測ラインL16～L18に設けられた選択スイッチSW21～SW23が、NチャネルのMOS型FET3で構成され、これらFET3のゲートが、図示しないバイアス回路に接続され、このバイアス回路に備えた例えばトランジスタがCPU30から2値信号を受けてオンオフされ、もってFET3が別々にオンオフされるように構成されている。

**【 0 0 2 5 】**

さらに、図2に示す組電池装置では、サンプルホールド用スイッチが、いずれもNチャネルの接合型FET1で構成されており、隣り合った並列ラインの間には、それぞれトランジスタT1のエミッタ・コレクタが接続されており、これら各トランジスタT1のコレクタに各FET1のゲートが接続されている。さらに、各トランジスタT1のバイアス回路は、ひとまとめにされて1つのトランジスタT2に接続され、このトランジスタT2が次述するCPU30（スイッチ制御手段に相当する）から2値信号を受けてオンオフされることで、全部のトランジスタT1が一斉にオンオフする。これにより、後の動作説明で詳説するように全部のFET1が一斉にオンオフされる。また、各FET1のゲート回路は、抵抗を介してひとまとめにされて負電源に接続され、これにより漏れ電流が防止されている。負電源により下げる電位は-0.5V以下とするのが良い。

**【 0 0 2 6 】**

また、図3に示す組電池装置では、サンプルホールド用スイッチが、いずれもPチャネルのMOS型のFET1で構成されており、各FET1のバイアス回路は、ひとまとめにされて1つのトランジスタT2に接続され、このトランジスタT2が次述するCPU30（スイッチ制御手段に相当する）から2値信号を受けてオンオフされることで、全部のFET1が一斉にオンオフされる。

**【 0 0 2 7 】**

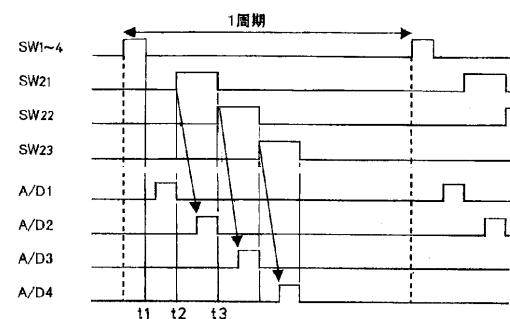

次に、図4のタイムチャートを参照しながら、本発明組電池装置の動作を上記図1に示す実施形態に基づいて説明する。

**【 0 0 2 8 】**

CPU30は、タイムチャートに示すように、所定周期で上記した各サンプルホールド用スイッチ及び選択スイッチをオンオフ制御している。

**【 0 0 2 9 】**

まず、組電池装置のスイッチ制御手段となるCPU30を起動すると、全てのスイッチがオフされた状態となる。この状態から、まず最初に、並列ラインL1～L4に設けたSW1～SW4が一斉にオンして、各単位電池E1～E4及び各コンデンサC1～C4の両極同士が導通接続される。

**【 0 0 3 0 】**

例えば、図2に示す装置では、CPU30によってトランジスタT2がオンされて、単位

10

20

30

40

50

電池 E 1 ~ E 4 每に配した全部のトランジスタ T 1 にバイアス電流が流れ、それらトランジスタ T 1 がオンする。すると、各 FET 1 のゲートの電位がソースの電位まで持ち上げられて、ゲート・ソース電圧 VGS が 0 V となり、全部の FET 1 がオンして、並列ライン L 1 ~ L 4 が導通状態となり、もって上記したように、各单位電池 E 1 ~ E 4 及び各コンデンサ C 1 ~ C 4 の両極同士が導通接続される。

#### 【 0 0 3 1 】

すると、コンデンサ C 1 ~ C 4 に電荷が流れ込み、対応した単位電池と同じ電圧が各コンデンサの両極間に発生する。また、このとき、コンデンサ群 10 と CPU 30 を繋ぐ計測ライン L 12 ~ L 14 上のバッファアンプの出力が制御電源電位にクランプされているため、単位電池を 2 つ以上繋げた大電圧が、CPU 30 の入力端子 (A/D 2 ~ A/D 4) に印加されることはない。10

#### 【 0 0 3 2 】

次いで、SW 1 ~ SW 4 が一斉にオフされる（ホールド期間）。例えば、図 2 に示す装置では、CPU 30 からの 2 値信号が例えば L レベルになり、トランジスタ T 2 がオフして、全トランジスタ T 1 がオフする。すると、各 FET 1 のゲートとソース間に、単位電池の電圧が印加された状態となり、FET 1 が一斉にオフする。

#### 【 0 0 3 3 】

これにより、各单位電池 E 1 ~ E 4 と各コンデンサ C 1 ~ C 4 とが一斉に非導通状態となり、コンデンサ C 1 ~ C 4 に流れ込んだ電荷は、どこにも逃げる経路がなくなり、同時刻 (SW 1 ~ SW 4 をオフした瞬間の時刻。図 4 の時刻 t 1 参照) の各单位電池 E 1 ~ E 4 の電圧が、各コンデンサ C 1 ~ C 4 にホールドされる。20

#### 【 0 0 3 4 】

次いで、コンデンサ群 10 のうち低電位側のコンデンサ C 1 から、順次に、その両極間の電位を CPU 30 に取り込む動作に移行する。すなわち、まず最初に、CPU 30 の GND 端子と入力端子 A/D 1 との間の電圧が取り込まれる。ここで、GND 端子と入力端子 A/D 1 とに両極を接続されたコンデンサ C 1 には、単位電池 E 1 の電圧がホールドされているから、その単位電池 E 1 の電圧が CPU 30 に取り込まれることとなり、これがデジタルデータ化されかつ所定のソフト処理を経て電圧値として検出される。

#### 【 0 0 3 5 】

このデータの取り込みが終了すると (図 4 の時刻 t 2 参照) 、スイッチ SW 21 (図 2 の場合、FET 3) がオンして、計測ライン L 16 と L 15 とが導通接続される。これにより、コンデンサ C 1 に蓄えられた電荷が放電されると共に、コンデンサ C 2 の負極が CPU 30 の GND 端子に導通接続される。30

#### 【 0 0 3 6 】

次いで、バッファアンプを介して、コンデンサ C 2 の正極が入力端子 A/D 2 に導通接続される。そして、この状態で、GND 端子と入力端子 A/D 2 との間の電圧が、CPU 30 に取り込まれてデジタルデータ化される。これにより、コンデンサ C 2 の両極間にホールドされた単位電池 E 2 の電圧が検出される。

#### 【 0 0 3 7 】

このデータの取り込みが終了すると (図 4 の時刻 t 3 参照) 、SW 22 (図 2 の場合、FET 3) がオンする。これにより、コンデンサ C 2 の正極が GND に導通接続されて、コンデンサ C 2 に蓄えられた電荷が放電されると共に、コンデンサ C 3 の負極が GND 端子に導通接続される。次いで、コンデンサ C 3 の正極がバッファアンプを介して入力端子 A/D 3 に導通接続され、この状態で、GND 端子と入力端子 A/D 3 との間に印加された電圧が、CPU 30 に取り込まれる。これにより、コンデンサ C 3 の両極間にホールドされた単位電池 E 3 の電圧が検出される。40

#### 【 0 0 3 8 】

以下、同様にして、コンデンサ C 4 の両極間の電圧が CPU 30 に取り込まれ、もって、コンデンサ C 4 の両極間にホールドされた単位電池 E 4 の電圧が検出される。

#### 【 0 0 3 9 】

10

20

30

40

50

このようにして、各コンデンサ C 1 ~ C 4 の両極間にホールドされた各単位電池 E 1 ~ E 4 の同時刻における電圧が、順次に C P U 3 0 に取り込まれて検出され、例えば、各単位電池の電圧の差が所定の電圧差に収まっているか否かが監視される。

#### 【 0 0 4 0 】

このように本実施形態によれば、複数の単位電池 E 1 ~ E 4 の同時刻の電圧を検出することが可能となり、従来問題となっていた、検出タイミングのずれに伴う電圧変動分が検出結果に含まれなくなり、高精度の電圧検出が可能となる。しかも、同時に複数の電圧検出を行える C P U を備えて同じ課題を解決した電圧検出回路に比べて、低コストで製造することができる。

#### 【 0 0 4 1 】

また、C P U 3 0 に、各単位電池 E 1 ~ E 4 の一つ当たりの電圧を取り込む構成としたから、C P U 3 0 の分解能（例えば、10ビット）を、単位電池 1 つの電圧に割り当てることができ、従来のように、複数の単位電池が直列した大電圧に分解能の全てを割り当てたものに比べて、検出精度が向上する。

#### 【 0 0 4 2 】

さらに、本発明によれば、各単位電池 E 1 ~ E 4 に分圧回路を接続しなくて済むから、従来のように、分圧回路に流れる放電電流によって、各単位電池の容量にばらつきが発生することもない。その上、コンデンサは、分圧回路に必要な抵抗に比べて温度の影響を受けにくく、この点においても、検出精度の向上が図られる。

#### 【 図面の簡単な説明 】

【 図 1 】 本発明の一実施形態の組電池装置の基本回路構成図。

【 図 2 】 本発明の一実施形態の組電池装置の詳細回路構成図。

【 図 3 】 本発明の一実施形態の組電池装置の詳細回路構成図。

【 図 4 】 C P U によるオンオフタイミングを示したタイムチャート。

【 図 5 】 従来の組電池装置の回路構成図。

#### 【 符号の説明 】

1 0 ... コンデンサ群

3 0 ... C P U ( 電圧検出手段、スイッチ制御手段 )

B ... バッテリー ( 組電池 )

C 1 ~ C 4 ... コンデンサ

E 1 ~ E 4 ... 単位電池

L 1 ~ L 5 ... 並列ライン

L 1 1 ~ 1 8 ... 計測ライン

S W 1 ~ S W 4 ... サンプルホールド用スイッチ

S W 2 1 ~ S W 2 3 ... 選択スイッチ

U 1 ~ U 4 ... バッファアンプ

10

20

30

【図1】

【図2】

【図3】

【図4】

【図5】

---

フロントページの続き

(56)参考文献 特許第4206574(JP,B2)

特開2000-171532(JP,A)

特開2000-059217(JP,A)

特開平11-248755(JP,A)

特開平11-055865(JP,A)

(58)調査した分野(Int.Cl., DB名)

G01R 19/00-19/32

G01R 31/32-31/36

H02J 7/00- 7/12

H02J 7/34- 7/36