(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7629413号**

**(P7629413)**

(45)発行日 令和7年2月13日(2025.2.13)

(24)登録日 令和7年2月4日(2025.2.4)

(51)国際特許分類

F I

|         |                  |         |        |

|---------|------------------|---------|--------|

| H 0 4 N | 19/12 (2014.01)  | H 0 4 N | 19/12  |

| H 0 4 N | 19/176 (2014.01) | H 0 4 N | 19/176 |

| H 0 4 N | 19/136 (2014.01) | H 0 4 N | 19/136 |

| H 0 4 N | 19/46 (2014.01)  | H 0 4 N | 19/46  |

請求項の数 15 (全51頁)

|                   |                                  |          |                                                                 |

|-------------------|----------------------------------|----------|-----------------------------------------------------------------|

| (21)出願番号          | 特願2021-566255(P2021-566255)      | (73)特許権者 | 595020643<br>クワアルコム・インコーポレイテッド<br>QUALCOMM INCORPORATED<br>TEDE |

| (86)(22)出願日       | 令和2年5月14日(2020.5.14)             |          | アメリカ合衆国、カリフォルニア州 9<br>2121-1714、サン・ディエゴ、<br>モアハウス・ドライブ 5775     |

| (65)公表番号          | 特表2022-531913(P2022-531913<br>A) | (74)代理人  | 110003708<br>弁理士法人鈴榮特許綜合事務所                                     |

| (43)公表日           | 令和4年7月12日(2022.7.12)             | (74)代理人  | 100108855<br>弁理士 蔵田 昌俊                                          |

| (86)国際出願番号        | PCT/US2020/032866                | (74)代理人  | 100158805<br>弁理士 井関 守三                                          |

| (87)国際公開番号        | WO2020/236509                    | (74)代理人  | 100112807<br>弁理士 岡田 貴志                                          |

| (87)国際公開日         | 令和2年11月26日(2020.11.26)           |          | 最終頁に続く                                                          |

| 審査請求日             | 令和5年4月14日(2023.4.14)             |          |                                                                 |

| (31)優先権主張番号       | 62/849,689                       |          |                                                                 |

| (32)優先日           | 令和1年5月17日(2019.5.17)             |          |                                                                 |

| (33)優先権主張国・地域又は機関 | 米国(US)                           |          |                                                                 |

| (31)優先権主張番号       | 15/931,271                       |          |                                                                 |

| (32)優先日           | 令和2年5月13日(2020.5.13)             |          |                                                                 |

|                   | 最終頁に続く                           |          | 最終頁に続く                                                          |

(54)【発明の名称】 ビデオエンコードのための0化パターンに基づく低周波数非分離変換シグナリング

**(57)【特許請求の範囲】****【請求項1】**

ビデオデータをデコードする方法において、前記ビデオデータの変換ブロック中の最後の有意係数の位置を決定することと、前記変換ブロックに対する低周波数非分離変換(L F N S T)インデックスの値を決定することと、ここにおいて、前記0化領域内の各変換係数は、前記変換ブロックにL F N S Tが適用されるときに、0化されることが想定され、前記変換ブロックの前記0化領域は、前記変換ブロックのL F N S T領域内の第1の0化領域と、前記L F N S T領域外の前記変換ブロックの第2の0化領域との両方を含み、前記L F N S Tインデックスの値を決定することは、前記変換ブロック中の前記最後の有意係数の位置が、前記変換ブロックの前記0化領域中にある場合、前記L F N S Tインデックスの値が0であると推測することを含み、0の前記L F N S Tインデックスの値は、前記L F N S Tが前記変換ブロックに適用されていないことを示す。

前記L F N S Tインデックスの値にしたがって、前記変換ブロックを逆変換することと、を備える方法。

**【請求項2】**

前記L F N S Tインデックスの値は、L F N S Tが前記変換ブロックに適用されているか否かを示し、適用されている場合には、適用されているL F N S Tのタイプを示す請求項1記載の方法。

**【請求項 3】**

前記 L F N S T インデックスの値が 0 であると推測することは、

前記 L F N S T インデックスの値を示すシンタックス要素を受信することなく、前記 L F N S T インデックスの値が 0 であると推測することを備える請求項 1 記載の方法。

**【請求項 4】**

前記変換ブロックを逆変換することは、

1 つ以上の分離変換により、前記変換ブロックを逆変換することを備える請求項 1 記載の方法。

**【請求項 5】**

前記 L F N S T インデックスの値を決定することは、

10

前記変換ブロック中の前記最後の有意係数の位置が、前記変換ブロックの 0 化領域中にない場合、前記 L F N S T インデックスを示すシンタックス要素を受信することと、

前記 L F N S T インデックスの値を決定するために、前記シンタックス要素をデコードすることと、

を備え、

前記変換ブロックを逆変換することは、

前記 L F N S T インデックスにより示される L F N S T により、前記変換ブロックの前記 L F N S T 領域を逆変換することと、

前記 L F N S T により、前記変換ブロックの前記 L F N S T 領域を逆変換した後に、1 つ以上の分離変換により、前記変換ブロックを逆変換することと、

を備える請求項 1 記載の方法。

20

**【請求項 6】**

前記ビデオデータの変換ブロック中の前記最後の有意係数の位置を決定することは、

前記変換ブロック中の前記最後の有意係数の X 位置および Y 位置を示す 1 つ以上のシンタックス要素をデコードすることを備える請求項 1 記載の方法。

**【請求項 7】**

前記変換ブロックを逆変換することは、残差ブロックを作成するために、前記変換ブロックを逆変換することを備え、

前記方法は、

前記残差ブロックに対する予測的ブロックを決定することと、

30

デコードされたブロックを作成するために、前記予測的ブロックを前記残差ブロックと組み合わせることと、

をさらに備え、前記方法は、

前記デコードされたブロックを含むピクチャーを表示することをさらに備える、

請求項 1 記載の方法。

**【請求項 8】**

ビデオデータをデコードするように構成されている装置において、

前記ビデオデータの変換ブロックを記憶するように構成されているメモリと、

前記メモリと通信する 1 つ以上のプロセッサとを具備し、

前記 1 つ以上のプロセッサは、

40

前記ビデオデータの変換ブロック中の最後の有意係数の位置を決定することと、

前記変換ブロックの 0 化領域に対する前記最後の有意係数の位置に基づいて、前記変換ブロックに対する低周波数非分離変換 (L F N S T) インデックスの値を決定することと、

ここにおいて、前記 0 化領域内の各変換係数は、前記変換ブロックに L F N S T が適用されるときに、0 化されることが想定され、前記変換ブロックの 0 化領域は、前記変換ブロックの L F N S T 領域内の第 1 の 0 化領域と、前記 L F N S T 領域外の前記変換ブロックの第 2 の 0 化領域との両方を含み、前記 L F N S T インデックスの値を決定するために、前記 1 つ以上のプロセッサは、前記変換ブロック中の前記最後の有意係数の位置が、前記変換ブロックの前記 0 化領域中にある場合、前記 L F N S T インデックスの値が 0 であると推測するように構成されており、0 の前記 L F N S T インデックスの値は、前記 L F

50

N S T が前記変換ブロックに適用されていないことを示す、

前記 L F N S T インデックスの値にしたがって、前記変換ブロックを逆変換することと、

を行うように構成されている、装置。

**【請求項 9】**

前記 L F N S T インデックスの値は、L F N S T が前記変換ブロックに適用されている

か否かを示し、適用されている場合には、適用されている L F N S T のタイプを示す請求

項 8 記載の装置。

**【請求項 10】**

前記 L F N S T インデックスの値が 0 であると推測するために、前記 1 つ以上のプロセ

ッサは、

前記 L F N S T インデックスの値を示すシンタックス要素を受信することなく、前記 L

F N S T インデックスの値が 0 であると推測するように構成されている請求項 8 記載の裝

置。

**【請求項 11】**

前記変換ブロックを逆変換するために、前記 1 つ以上のプロセッサは、

1 つ以上の分離変換により、前記変換ブロックを逆変換するように構成されている請求

項 8 記載の装置。

**【請求項 12】**

前記 L F N S T インデックスの値を決定するために、前記 1 つ以上のプロセッサは、

前記変換ブロック中の前記最後の有意係数の位置が、前記変換ブロックの 0 化領域中

ない場合、前記 L F N S T インデックスを示すシンタックス要素を受信することと、

前記 L F N S T インデックスの値を決定するために、前記シンタックス要素をデコード

することと、

を行うように構成されており、

前記変換ブロックを逆変換するために、前記 1 つ以上のプロセッサは、

前記 L F N S T インデックスにより示される L F N S T により、前記変換ブロックの前

記 L F N S T 領域を逆変換することと、

前記 L F N S T により、前記変換ブロックの前記 L F N S T 領域を逆変換した後に、1

つ以上の分離変換により、前記変換ブロックを逆変換することと、

を行うように構成されている請求項 8 記載の装置。

**【請求項 13】**

前記ビデオデータの変換ブロック中の前記最後の有意係数の位置を決定するために、前

記 1 つ以上のプロセッサは、

前記変換ブロック中の前記最後の有意係数の X 位置および Y 位置を示す 1 つ以上のシン

タックス要素をデコードするように構成されている請求項 8 記載の装置。

**【請求項 14】**

前記変換ブロックを逆変換するために、前記 1 つ以上のプロセッサは、

残差ブロックを作成するために、前記変換ブロックを逆変換するように構成され、

前記 1 つ以上のプロセッサは、

前記残差ブロックに対する予測的ブロックを決定することと、

デコードされたブロックを作成するために、前記予測的ブロックを前記残差ブロックと

組み合わせることと、

を行うように構成されており、

前記装置は、前記デコードされたブロックを含むピクチャーを表示するように構成され

ているディスプレイをさらに備える、請求項 8 記載の装置。

**【請求項 15】**

非一時的コンピュータ読取可能記憶媒体において、

実行されるときに、ビデオデータをデコードするように構成されている 1 つ以上のプロ

セッサに、

前記ビデオデータの変換ブロック中の最後の有意係数の位置を決定することと、

10

20

30

40

50

前記変換ブロックの0化領域に対する前記最後の有意係数の位置に基づいて、前記変換ブロックに対する低周波数非分離変換（L F N S T）インデックスの値を決定することと、ここにおいて、前記0化領域内の各変換係数は、前記変換ブロックにL F N S Tが適用されるときに、0化されることが想定され、前記変換ブロックの前記0化領域は、前記変換ブロックのL F N S T領域内の第1の0化領域と、前記L F N S T領域外の前記変換ブロックの第2の0化領域との両方を含み、前記L F N S Tインデックスの値を決定することは、前記変換ブロック中の前記最後の有意係数の位置が、前記変換ブロックの前記0化領域中にある場合、前記L F N S Tインデックスの値が0であると推測することを含み、0の前記L F N S Tインデックスの値は、前記L F N S Tが前記変換ブロックに適用されていないことを示す、

10

前記L F N S Tインデックスの値にしたがって、前記変換ブロックを逆変換することと、を行わせる命令を記憶している非一時的コンピュータ読取可能記憶媒体。

【発明の詳細な説明】

【相互参照】

【0 0 0 1】

[ 0 0 0 1 ]

本出願は、2019年5月17日に出願された米国仮出願第62/849689号の利益を主張する、2020年5月13日に出願された米国特許出願第15/931271号に対する優先権を主張し、これらのそれぞれの全内容は、参照により本明細書に組み込まれている。

【技術分野】

【0 0 0 2】

[ 0 0 0 2 ]

本開示は、ビデオエンコーディングおよびビデオデコーディングに関連する。

【背景】

【0 0 0 3】

[ 0 0 0 3 ]

デジタルビデオ能力は、デジタルテレビ、デジタルダイレクトブロードキャストシステム、ワイヤレスブロードキャストシステム、パーソナルデジタルアシスタント（P D A）、ラップトップまたはデスクトップコンピュータ、タブレットコンピュータ、e - ブックリーダ、デジタルカメラ、デジタル記録デバイス、デジタルメディアプレーヤ、ビデオゲームデバイス、ビデオゲームコンソール、セルラまたは衛星無線電話機、いわゆる「スマートフォン」、ビデオ電話会議デバイス、ビデオストリーミングデバイス、および、これらに類するものを含む、幅広い範囲のデバイスに組み込むことができる。デジタルビデオデバイスは、M P E G - 2、M P E G - 4、I T U - T H . 2 6 3、I T U - T H . 2 6 4 / M P E G - 4、パート10、高度ビデオコーディング（A V C）、I T U - T H . 2 6 5 / 高効率ビデオコーディング（H E V C）、および、このような標準規格の拡張によって規定される標準規格に記述されているもののような、ビデオコーディング技法を実現する。ビデオデバイスは、このようなビデオコーディング技法を実現することによって、より効率的にデジタルビデオ情報を送信、受信、エンコード、デコード、および／または、記憶してもよい。

【0 0 0 4】

[ 0 0 0 4 ]

ビデオコーディング技法は、ビデオシーケンスに内在する冗長を低減または取り除くために、空間的（イントラピクチャー）予測、および／または、時間的（インターピクチャー）予測を含んでいる。ロックベースのビデオコーディングに対して、ビデオスライス（例えば、ビデオピクチャーまたはビデオピクチャーの一部分）は、コーディングツリユニット（C T U）、コーディングユニット（C U）および／またはコーディングノードとして呼ばれることがあるかもしれないビデオブロックに区分してもよい。ピクチャーのイントラコード化された（I）スライスにおけるビデオブロックは、同じピクチャーにお

10

20

30

40

50

ける隣接ブロック中の参照サンプルに関する空間的予測を使用してエンコードされる。ピクチャーのインターフォーマット（PまたはB）スライスにおけるビデオブロックは、同じピクチャーにおける隣接ブロック中の参照サンプルに関する空間的予測、または、他の参照ピクチャーにおける参照サンプルに関する時間的予測を使用してもよい。ピクチャーは、フレームとして呼ばれることがあり、参照ピクチャーは参照フレームとして呼ばれることがある。

#### 【概要】

##### 【0005】

[0005]

一般的に、本開示は、現代のビデオ圧縮標準規格の基本要素である変換コーディングのための技法を説明している（M. Wien, 高効率ビデオコーディング：コーディングツールおよび仕様、シュプリンガー出版、ベルリン、2015年）。本開示の技法は、デコードингのために複数の変換候補の中から選択された変換を指定するために、ビデオコーデックにおいて使用することができるさまざまな変換シグナリング方法を含んでいる。特に、本開示は、低周波数非分離変換（L NST）インデックスの値を複数の値の中から推測するための技法を説明している。推測することは、エンコードされたビデオビットストリーム内で値を示すシンタックス要素を受信することなく、複数の値の中から値を決定することを意味する。

10

##### 【0006】

[0006]

L NSTインデックスの値は、変換ブロックにL NSTが適用されているか否かを、適用されているときには、適用されることになるL NSTのタイプを示している。L NSTは、変換ブロックのL NST領域に適用される非分離変換である。L NST領域は、変換ブロックの変換係数のサブセットであってもよく、変換ブロックの低周波数成分（例えば、変換ブロックの左上隅）を含んでいてもよい。いくつかの適用例では、L NSTを適用するときには、L NST領域内のいくつかの変換係数が0に設定される（例えば、0化される）。加えて、L NST領域外にある変換ブロック中の変換係数も0化されるかもしれない。

20

##### 【0007】

[0007]

変換ブロックに対するL NSTインデックスの値を決定する前に、ビデオデコーダは、変換ブロック中の最後の有意係数の位置を決定するように構成されていてもよい。変換ブロックの変換係数が走査順序にしたがって順序付けられ／走査されるとき、変換ブロック中の最後の有意係数は、変換ブロックの最後の非0変換係数を指しているかもしれない。例えば、ビデオデコーダは、予め決定されている走査順序に沿った最後の有意（すなわち、非0）係数の位置（例えば、変換ブロック中のX座標およびY座標）を示すシンタックス要素を受信してデコードしてもよい。最後の有意係数の位置が、ビデオエンコーダによりL NSTが適用された場合に0化されるであろう変換ブロックの一部（L NST領域中またはL NST領域外のいずれか）中にあることが決定された場合には、ビデオデコーダは、LN STインデックスの値が0である（すなわち、L NSTは適用されていない）と推測してもよい。すなわち、ビデオデコーダは、L NSTが適用された場合に0化されているであろう位置における変換ブロック中に非0係数が存在することを決定した場合には、L NSTが適用されていないことを決定してもよい。

30

##### 【0008】

[0008]

このようにして、ビデオエンコーダは、最後の有意係数の位置が、L NSTが適用された場合に0化されるであろう変換ブロックの一部（L NST領域中またはL NST領域外のいずれか）中にあるケースでは、L NSTインデックスの値を示すシンタックス要素を発生させて、シグナリングする必要はない。したがって、シグナリングオーバーヘッドは低減されるかもしれない、コーディング効率は増加するかもしれない。本開示の提

40

50

案する技法は、シグナリングオーバーヘッドを低減させるかもしれないので、本開示の技法は、コーディング効率を改善するかもしれません、HEVCの拡張と、バーサタイルビデオコーディング(VVC)またはH.266のような次世代のビデオコーディング標準規格とを含む、LFNSTを使用する高度ビデオコーデックにおいて使用することができる。

#### 【0009】

[0009]

1つの例では、本開示は、ビデオデータをデコードする方法を説明し、方法は、ビデオデータの変換ブロック中の最後の有意係数の位置を決定することと、変換ブロックの0化領域に対する最後の有意係数の位置に基づいて、変換ブロックに対するLFNSTインデックスの値を決定し、変換ブロックの0化領域は、変換ブロックのLFNST領域内の第1の領域と、LFNST領域外の変換ブロックの第2の領域との両方を含むことと、LFNSTインデックスの値にしたがって、変換ブロックを逆変換することとを含んでいる。

10

#### 【0010】

[0010]

別の例では、本開示は、ビデオデータをデコードするように構成されている装置を説明し、装置は、ビデオデータの変換ブロックを記憶するように構成されているメモリと、メモリと通信する1つ以上のプロセッサとを具備し、1つ以上のプロセッサは、ビデオデータの変換ブロック中の最後の有意係数の位置を決定するようにと、変換ブロックの0化領域に対する最後の有意係数の位置に基づいて、変換ブロックに対するLFNSTインデックスの値を決定し、変換ブロックの0化領域は、変換ブロックのLFNST領域内の第1の領域と、LFNST領域外の変換ブロックの第2の領域との両方を含むようにと、LFNSTインデックスの値にしたがって、変換ブロックを逆変換するように構成されている。

20

#### 【0011】

[0011]

別の例では、本開示は、ビデオデータをデコードするように構成されている装置を説明し、装置は、ビデオデータの変換ブロック中の最後の有意係数の位置を決定する手段と、変換ブロックの0化領域に対する最後の有意係数の位置に基づいて、変換ブロックに対するLFNSTインデックスの値を決定し、変換ブロックの0化領域は、変換ブロックのLFNST領域内の第1の領域と、LFNST領域外の変換ブロックの第2の領域との両方を含む手段と、LFNSTインデックスの値にしたがって、変換ブロックを逆変換する手段とを具備している。

30

#### 【0012】

[0012]

別の例では、本開示は、非一時的コンピュータ読取可能記憶媒体を説明し、非一時的コンピュータ読取可能記憶媒体は、実行されるときに、ビデオデータをデコードするように構成されている1つ以上のプロセッサに、ビデオデータの変換ブロック中の最後の有意係数の位置を決定させ、変換ブロックの0化領域に対する最後の有意係数の位置に基づいて、変換ブロックに対するLFNSTインデックスの値を決定させ、変換ブロックの0化領域は、変換ブロックのLFNST領域内の第1の領域と、LFNST領域外の変換ブロックの第2の領域との両方を含み、LFNSTインデックスの値にしたがって、変換ブロックを逆変換させる命令を記憶している。

40

#### 【0013】

[0013]

1つ以上の例の詳細が、添付の図面および以下の説明に記載されている。他の特徴、目的および利点は、説明、図面および特許請求の範囲から明らかになるであろう。

#### 【図面の簡単な説明】

#### 【0014】

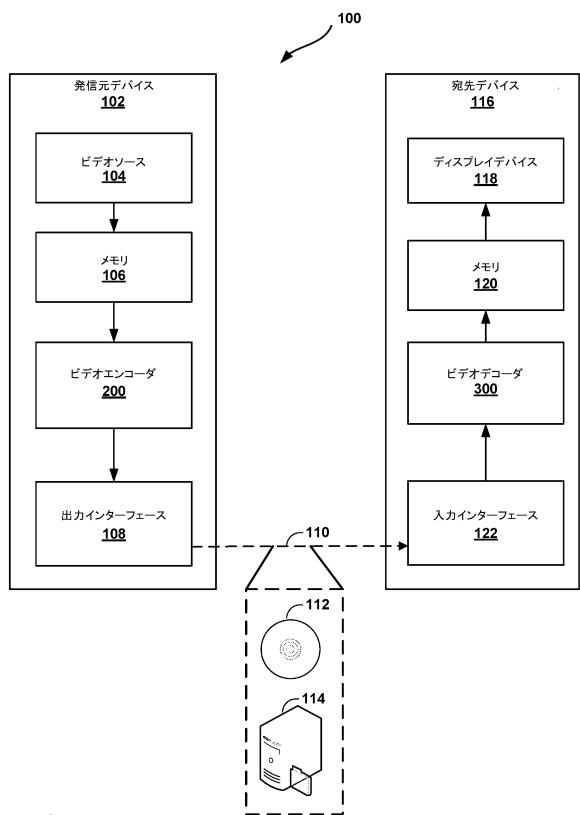

【図1】[0014] 図1は、本開示の技法を実行してもよい、例示的なビデオエンコーディングおよびデコーディングシステムを図示するブロック図である。

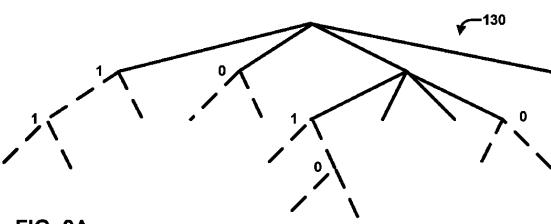

【図2A】[0015] 図2Aは、例示的な4分ツリー-2分ツリー(QTBT)構造と

50

、対応するコーディングツリーユニット(CTU)とを図示する概念図である。

【図2B】図2Bは、例示的な4分ツリー2分ツリー(QTBT)構造と、対応するコーディングツリーユニット(CTU)とを図示する概念図である。

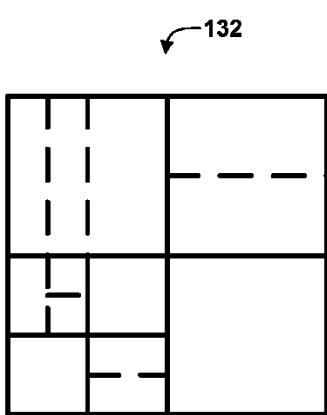

【図3】[0016] 図3は、本開示の技法を実行してもよい、例示的なビデオエンコーダを図示するブロック図である。

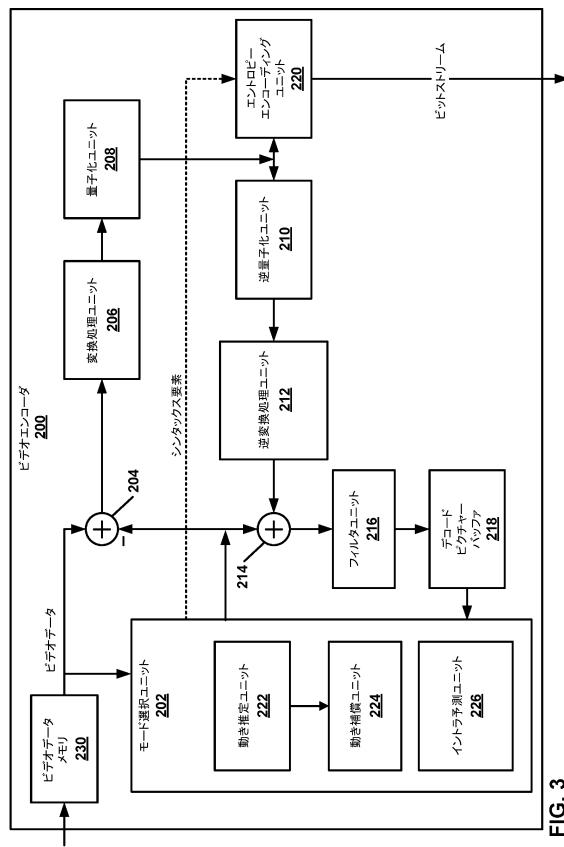

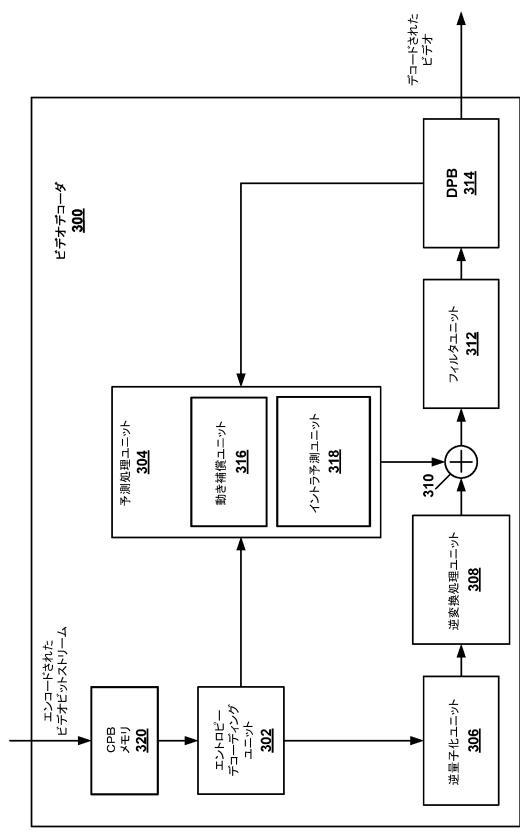

【図4】[0017] 図4は、本開示の技法を実行してもよい、例示的なビデオデコーダを図示するブロック図である。

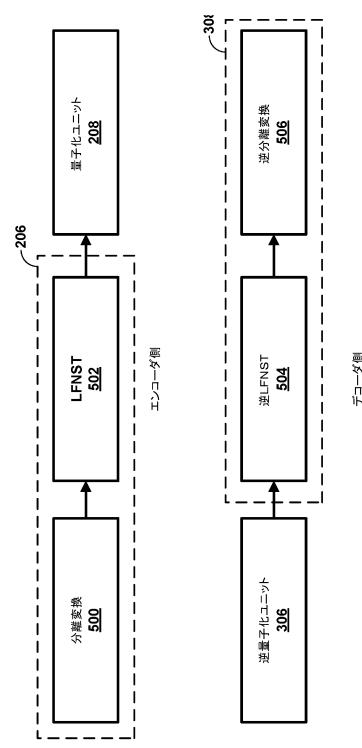

【図5】[0018] 図5は、エンコーダおよびデコーダにおける例示的な低周波数非分離変換(LFNST)を図示するブロック図である。

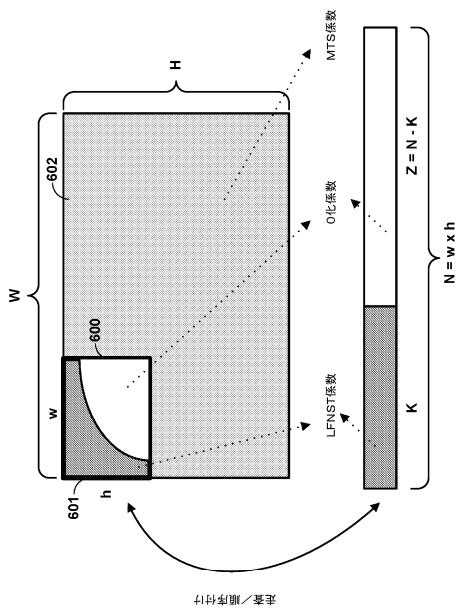

【図6】[0019] 図6は、0化有りの、変換ブロックにLFNSTを適用した後に得られる変換係数を図示する概念図である。 10

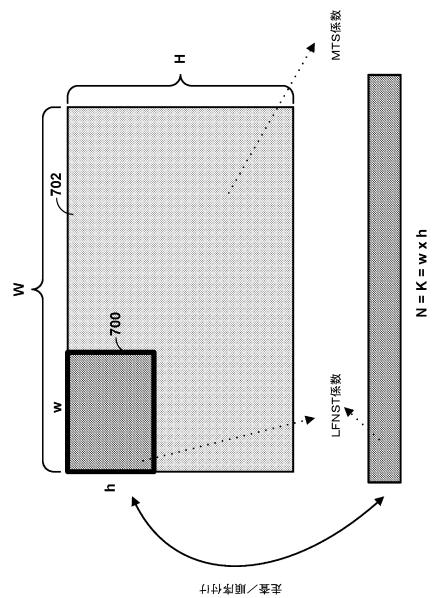

【図7】[0020] 図7は、0化なしの、変換ブロックにLFNSTを適用した後に得られる変換係数を図示する概念図である。

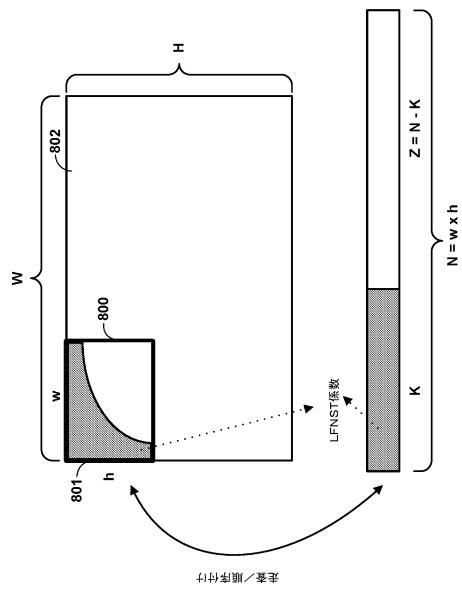

【図8】[0021] 図8は、0化有りの、変換ブロックに例示的なLFNSTを適用した後に得られる変換係数を図示する概念図である。

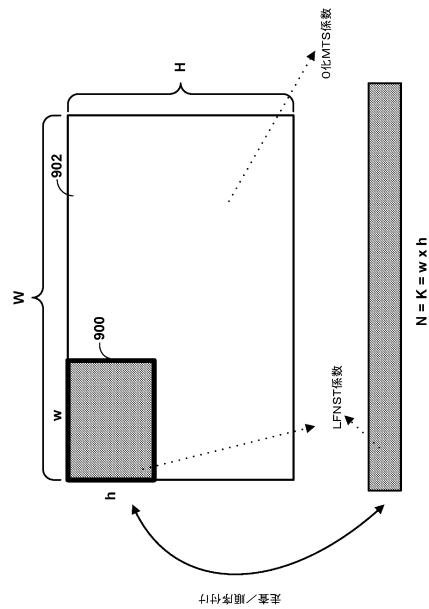

【図9】[0022] 図9は、0化なしの、変換ブロックに例示的なLFNSTを適用した後に得られる変換係数を図示する概念図である。

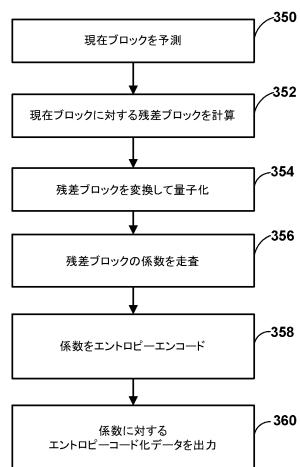

【図10】[0023] 図10は、本開示の例示的なエンコーディング方法を図示するフロー チャートである。

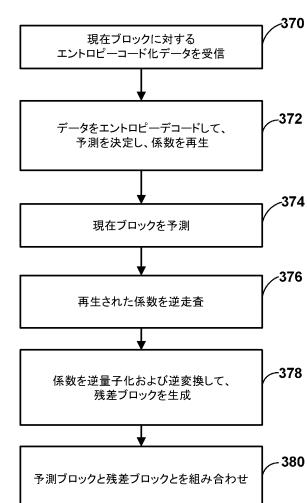

【図11】[0024] 図11は、本開示の例示的なデコーディング方法を図示するフロー チャートである。 20

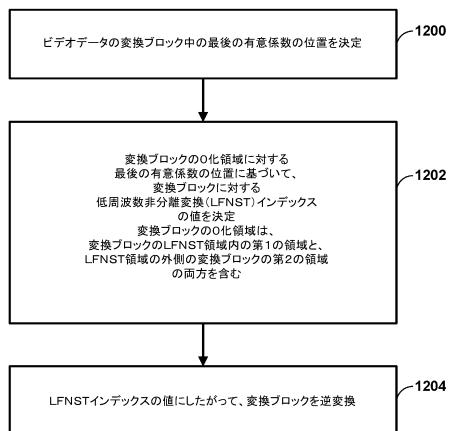

【図12】[0025] 図12は、本開示の別の例示的なデコーディング方法を図示するフロー チャートである。

#### 【詳細な説明】

【0015】

[0026]

本開示の技法は、デコーディングのために複数の変換候補の中から選択された変換を指定するために、ビデオコーデックにおいて使用することができるさまざまな変換シグナリング方法を含んでいる。特に、本開示は、低周波数非分離変換(LFNST)インデックスの値を推測する技法を説明している。推測することは、エンコードされたビデオビットストリーム中で値を示すシンタックス要素を受信することなく値を決定することを意味する。 30

【0016】

[0027]

LFNSTインデックスの値は、変換ブロックにLFNSTが適用されているか否かと、適用されているときには、適用されることとなるLFNSTのタイプを示している。LFNSTは、変換ブロックのLFNST領域に適用される非分離変換である。LFNST領域は、変換ブロックの変換係数のサブセットであってもよく、変換ブロックの低周波数成分(例えば、変換ブロックの左上隅)を含んでいてもよい。いくつかの適用例では、LFNSTを適用するときには、LFNST領域内のいくつかの変換係数が0に設定される(例えば、0化される)。加えて、LFNST領域外にある変換ブロック中の変換係数も0化されるかもしれない。 40

【0017】

[0028]

変換ブロックに対するLFNSTインデックスの値を決定する前に、ビデオデコーダは、変換ブロック中の最後の有意係数の位置を決定するように構成されていてもよい。例えば、ビデオデコーダは、予め決定されている走査順序に沿った最後の有意(すなわち、非0)係数の位置(例えば、変換ブロック中のX座標およびY座標)を示すシンタックス要素を受信してデコードしてもよい。最後の有意係数の位置が、ビデオエンコーダによりLFNSTが適用された場合に0化されるであろう変換ブロックの一部(LFNST領域中

10

20

30

40

50

または L F N S T 領域外のいずれか) 中にあることが決定された場合には、ビデオデコーダは、L N F S T インデックスの値が 0 である(すなわち、L F N S T は適用されていない)と推測してもよい。すなわち、ビデオデコーダは、L F N S T が適用された場合に 0 化されているであろう(例えば、変換係数は 0 値を有するであろう)位置における変換ブロック中に非 0 係数が存在することを決定した場合には、L F N S T が適用されていないことを決定してもよい。

**【 0 0 1 8 】**

**[ 0 0 2 9 ]**

このようにして、ビデオエンコーダは、最後の有意係数の位置が、L F N S T が適用された場合に 0 化されるであろう変換ブロックの一部(L F N S T 領域中または L F N S T 領域外のいずれか) 中にあるケースでは、L F N S T インデックスの値を示すシンタックス要素を発生させて、シグナリングする必要はない。したがって、シグナリングオーバーヘッドは低減されるかもしれません、コーディング効率は増加するかもしれません。

10

**【 0 0 1 9 】**

**[ 0 0 3 0 ]**

図 1 は、本開示の技法を実行してもよい、例示的なビデオエンコーディングおよびデコーディングシステム 100 を図示するブロック図である。本開示の技法は、一般的に、ビデオデータをコード化(エンコードおよび/またはデコード)することに向けられている。一般的に、ビデオデータは、ビデオを処理するための任意のデータを含んでいる。したがって、ビデオデータは、生のコード化されていないビデオ、エンコードされたビデオ、デコードされた(例えば、再構築された)ビデオ、および、シグナリングデータのようなビデオメタデータを含んでいてもよい。

20

**【 0 0 2 0 】**

**[ 0 0 3 1 ]**

図 1 に示すように、システム 100 は、この例では、宛先デバイス 116 によってデコードされ、表示されるべき、エンコードされたビデオデータを提供する、発信元デバイス 102 を含んでいる。特に、発信元デバイス 102 は、コンピュータ読取可能媒体 110 を介して、ビデオデータを宛先デバイス 116 に提供する。発信元デバイス 102 および宛先デバイス 116 は、デスクトップコンピュータ、ノートブック(すなわち、ラップトップ)コンピュータ、タブレットコンピュータ、セットトップボックス、スマートフォンのような電話ハンドセット、テレビジョン、カメラ、ディスプレイデバイス、デジタルメディアプレーヤ、ビデオゲームコンソール、ビデオストリーミングデバイス、または、これらに類するものを含む、広範囲のデバイスのうちのいずれを含んでいてもよい。いくつかのケースでは、発信元デバイス 102 および宛先デバイス 116 は、ワイヤレス通信のために備えられてもよく、したがって、ワイヤレス通信デバイスとして呼ばれることがある。

30

**【 0 0 2 1 】**

**[ 0 0 3 2 ]**

図 1 の例では、発信元デバイス 102 は、ビデオソース 104 と、メモリ 106 と、ビデオエンコーダ 200 と、出力インターフェース 108 とを含んでいる。宛先デバイス 116 は、入力インターフェース 122 と、ビデオデコーダ 300 と、メモリ 120 と、ディスプレイデバイス 118 とを含んでいる。本開示によると、発信元デバイス 102 のビデオエンコーダ 200 および宛先デバイス 116 のビデオデコーダ 300 は、変換コーディングのための技法を適用するように構成されていてもよい。したがって、発信元デバイス 102 はビデオエンコーディングデバイスの例を表す一方で、宛先デバイス 116 はビデオデコーディングデバイスの例を表している。他の例では、発信元デバイスおよび宛先デバイスは、他のコンポーネントまたは構成を含んでいてもよい。例えば、発信元デバイス 102 は、外部カメラのような外部ビデオソースからビデオデータを受け取ってもよい。同様に、宛先デバイス 116 は、統合されたディスプレイデバイスを含むよりもむしろ、外部ディスプレイデバイスとインターフェースしていてもよい。

40

50

## 【0022】

## [0033]

図1に示されているシステム100は1つの例にすぎない。一般的に、任意のデジタルビデオエンコーディングおよび／またはデコーディングデバイスが、変換コーディングのための技法を実行してもよい。発信元デバイス102および宛先デバイス116は、発信元デバイス102が宛先デバイス116への送信のためにコード化されたビデオデータを発生させる、このようなコーディングデバイスの例にすぎない。本開示は、データのコーディング（エンコーディングおよび／またはデコーディング）を実行するデバイスとして「コーディング」デバイスに言及する。したがって、ビデオエンコーダ200およびビデオデコーダ300は、コーディングデバイスの例を、特に、それぞれビデオエンコーダおよびビデオデコーダを表している。いくつかの例では、発信元デバイス102および宛先デバイス116は、発信元デバイス102および宛先デバイス116のそれぞれがビデオエンコーディングコンポーネントとビデオデコーディングコンポーネントとを含むように、実質的に対称的に動作してもよい。したがって、システム100は、例えば、ビデオストリーミング、ビデオ再生、ビデオブロードキャスティング、または、ビデオ電話に対する、発信元デバイス102と宛先デバイス116との間の一方向または双方向ビデオ送信をサポートしてもよい。

10

## 【0023】

## [0034]

一般的に、ビデオソース104は、ビデオデータ（すなわち、生のコード化されていないビデオデータ）のソースを表し、ビデオデータの（「フレーム」としても呼ばれる）シーケンシャルな一連のピクチャーを、ピクチャーに対するデータをエンコードするビデオエンコーダ200に提供する。発信元デバイス102のビデオソース104は、ビデオカメラのようなビデオキャプチャデバイス、以前にキャプチャされた生のビデオを含んでいるビデオアーカイブ、および／または、ビデオコンテンツプロバイダからビデオを受け取るためのビデオフィードインターフェースを含んでいてもよい。さらなる代替として、ビデオソース104は、ソースビデオとしてのコンピュータグラフィックスベースのデータを、または、ライブビデオとアーカイブビデオとコンピュータ発生ビデオとの組み合わせを発生させてもよい。各ケースにおいて、ビデオエンコーダ200は、キャプチャされた、事前キャプチャされた、または、コンピュータが発生させたビデオデータをエンコードする。ビデオエンコーダ200は、（ときには「表示順序」として呼ばれる）受け取った順序から、コーディングのためのコーディング順序にピクチャーを再構成してもよい。ビデオエンコーダ200は、エンコードされたビデオデータを含むビットストリームを発生させてもよい。発信元デバイス102は、その後、例えば、宛先デバイス116の入力インターフェース122による受け取りおよび／または取り出しのために、出力インターフェース108を介して、コンピュータ読取可能媒体110上に、エンコードされたビデオデータを出力してもよい。

20

## 【0024】

## [0035]

発信元デバイス102のメモリ106および宛先デバイス116のメモリ120は、汎用メモリを表している。いくつかの例では、メモリ106、120は、生のビデオデータ、例えば、ビデオソース104からの生ビデオと、ビデオデコーダ300からの生のデコードされたビデオデータとを記憶してもよい。追加的にまたは代替的に、メモリ106、120は、例えば、ビデオエンコーダ200およびビデオデコーダ300それぞれによって実行可能なソフトウェア命令を記憶していてもよい。この例では、メモリ106およびメモリ120は、ビデオエンコーダ200およびビデオデコーダ300とは別個に示されているが、ビデオエンコーダ200およびビデオデコーダ300はまた、機能的に同様または同等の目的のために内部メモリを含んでいてもよいことを理解すべきである。さらに、メモリ106、120は、例えば、ビデオエンコーダ200から出力され、ビデオデコーダ300に入力される、エンコードされたビデオデータを記憶してもよい。いくつかの

30

40

50

例では、メモリ 106、120 の一部分は、1つ以上のビデオバッファとして割り振られ、例えば、生のデコードされたおよび / またはエンコードされたビデオデータを記憶してもよい。

**【 0 0 2 5 】**

**[ 0 0 3 6 ]**

コンピュータ読取可能媒体 110 は、発信元デバイス 102 から宛先デバイス 116 へとエンコードされたビデオデータを転送することが可能な任意のタイプの媒体またはデバイスを表していてもよい。1つの例では、コンピュータ読取可能媒体 110 は、発信元デバイス 102 が、例えば、無線周波数ネットワークまたはコンピュータベースのネットワークを介して、エンコードされたビデオデータをリアルタイムで宛先デバイス 116 に直接送信することを可能にする通信媒体を表している。ワイヤレス通信プロトコルのような通信標準規格にしたがって、出力インターフェース 108 は、エンコードされたビデオデータを含む送信信号を変調してもよく、入力インターフェース 122 は、受け取った送信信号を復調してもよい。通信媒体は、無線周波数 (RF) スペクトルまたは1つ以上の物理送信ラインのような、何らかのワイヤレスまたはワイヤード通信媒体を含んでいてもよい。通信媒体は、ローカルエリアネットワーク、ワイドエリアネットワーク、または、インターネットのようなグローバルネットワークのような、パケットベースのネットワークの一部を形成していてもよい。通信媒体は、ルータ、スイッチ、基地局、または、発信元デバイス 102 から宛先デバイス 116 への通信を容易にするのに役立つかもしれない他の何らかの機器を含んでいてもよい。

10

**【 0 0 2 6 】**

**[ 0 0 3 7 ]**

いくつかの例では、発信元デバイス 102 は、出力インターフェース 108 から記憶デバイス 112 にエンコードされたデータを出力してもよい。同様に、宛先デバイス 116 は、入力インターフェース 122 を介して、記憶デバイス 112 からのエンコードされたデータにアクセスしてもよい。記憶デバイス 112 は、ハードドライブ、ブルーレイ（登録商標）ディスク、DVD、CD-ROM、フラッシュメモリ、揮発性または不揮発性メモリ、あるいは、エンコードされたビデオデータを記憶するための他の何らかの適切なデジタル記憶媒体のような、さまざまな分散またはローカルにアクセスされるデータ記憶媒体のいずれかを含んでいてもよい。

20

**【 0 0 2 7 】**

**[ 0 0 3 8 ]**

いくつかの例では、発信元デバイス 102 は、エンコードされたビデオデータを、ファイルサーバ 114 に、または、発信元デバイス 102 によって発生させたエンコードされたビデオデータを記憶してもよい別の中間記憶デバイスに出力してもよい。宛先デバイス 116 は、ストリーミングまたはダウンロードを介して、ファイルサーバ 114 からの記憶されているビデオデータにアクセスしてもよい。ファイルサーバ 114 は、エンコードされたビデオを記憶することと、宛先デバイス 116 にエンコードされたビデオを送信することとができる、任意のタイプのサーバデバイスであってもよい。ファイルサーバ 114 は、（例えば、ウェブサイトに対する）ウェブサーバ、ファイル転送プロトコル (FTP) サーバ、コンテンツ配信ネットワークデバイス、または、ネットワーク接続記憶 (NAS) デバイスを表していてもよい。宛先デバイス 116 は、インターネット接続を含む任意の標準的なデータ接続を通して、ファイルサーバ 114 からのエンコードされたビデオデータにアクセスしてもよい。これは、ファイルサーバ 114 上に記憶されている、エンコードされたビデオデータにアクセスするのに適している、ワイヤレスチャネル（例えば、Wi-Fi 接続）、ワイヤード接続（例えば、デジタル加入者線 (DSL)、ケーブルモデム等）、または、その両方の組み合わせを含んでいてもよい。ファイルサーバ 114 および入力インターフェース 122 は、ストリーミング送信プロトコル、ダウンロード送信プロトコル、または、これらの組み合わせにしたがって動作するように構成されている。

30

40

50

## 【0028】

## [0039]

出力インターフェース108および入力インターフェース122は、ワイヤレス送信機/受信機、モデム、ワイヤードネットワーキングコンポーネント（例えば、イーサネット（登録商標）カード）、さまざまなIEEE802.11標準規格のいずれかにしたがって動作するワイヤレス通信コンポーネント、または、他の物理コンポーネントを表してもよい。出力インターフェース108および入力インターフェース122がワイヤレスコンポーネントを含んでいる例では、出力インターフェース108および入力インターフェース122は、4G、4G-LTE（登録商標）（ロングタームエボリューション）、LTEアドバンスト、5G、または、これらに類するもののようなセルラ通信標準規格にしたがって、エンコードされたビデオデータのようなデータを転送するように構成されてもよい。出力インターフェース108および入力インターフェース122がワイヤレス送信機および/またはワイヤレス受信機を含んでいるいくつかの例では、出力インターフェース108および入力インターフェース122は、IEEE802.11仕様、IEEE802.15仕様（例えば、ZigBee（商標））、Bluetooth（登録商標）（商標）標準規格、または、これらに類するもののような他のワイヤレス標準規格にしたがって、エンコードされたビデオデータのようなデータを転送するように構成されてもよい。いくつかの例では、発信元デバイス102および/または宛先デバイス116は、それぞれのシステムオンチップ（SOC）デバイスを含んでいてもよい。例えば、発信元デバイス102は、ビデオエンコーダ200および/または出力インターフェース108に備わる機能性を実行するためのSOCデバイスを含んでいてもよく、宛先デバイス116は、ビデオデコーダ300および/または入力インターフェース122に備わる機能性を実行するSOCデバイスを含んでいてもよい。

10

20

30

## 【0029】

## [0040]

本開示の技法は、無線テレビ放送、ケーブルテレビ送信、衛星テレビ送信、HTTPを通した動的アダプティブストリーミング（DASH）のようなインターネットストリーミングビデオ送信、データ記憶媒体上にエンコードされたデジタルビデオ、データ記憶媒体上に記憶されているデジタルビデオのデコーディング、または、他のアプリケーションのような、さまざまなマルチメディアアプリケーションのうちのいずれかをサポートするビデオコーディングに適用してもよい。

40

## 【0030】

## [0041]

宛先デバイス116の入力インターフェース122は、コンピュータ読取可能媒体110（例えば、通信媒体、記憶デバイス112、ファイルサーバ114、または、これらに類するもの）からエンコードされたビデオビットストリームを受け取る。エンコードされたビデオビットストリームは、ビデオブロックまたは他のコード化されたユニット（例えば、スライス、ピクチャー、ピクチャーのグループ、シーケンス、または、これらに類するもの）の特性および/または処理を記述する値を有するシンタックス要素のような、ビデオエンコーダ200によって規定され、ビデオデコーダ300によっても使用されるシグナリング情報を含んでいてもよい。ディスプレイデバイス118は、デコードされたビデオデータのデコードされたピクチャーをユーザに表示する。ディスプレイデバイス118は、液晶ディスプレイ（LCD）、プラズマディスプレイ、有機発光ダイオード（OLED）ディスプレイ、または、別のタイプのディスプレイデバイスのような、さまざまなディスプレイデバイスのうちのいずれかを表してもよい。

## 【0031】

## [0042]

図1には示されていないが、いくつかの例では、ビデオエンコーダ200およびビデオデコーダ300は、それぞれオーディオエンコーダおよび/またはオーディオデコーダと統合されていてもよく、適切なMUX-DEMUXユニットあるいは他のハードウェアお

50

および／またはソフトウェアを含んでいて、共通のデータストリームにおけるオーディオおよびビデオの両方を含む多重化されたストリームを取り扱ってもよい。適用可能である場合には、MUX - DEMUXユニットは、ITU . H . 223マルチプレクサプロトコル、または、ユーザデータグラムプロトコル(UDP)のような他のプロトコルにしたがつてもよい。

#### 【0032】

##### [0043]

ビデオエンコーダ200およびビデオデコーダ300はそれぞれ、1つ以上のマイクロプロセッサ、デジタル信号プロセッサ(DSP)、特定用途向け集積回路(ASIC)、フィールドプログラマブルゲートアレイ(FPGA)、ディスクリート論理、ソフトウェア、ハードウェア、ファームウェア、または、これらの組み合わせのような、さまざまに適したエンコーダおよび／またはデコーダ回路のいずれかとして実現してもよい。技法が部分的にソフトウェアで実現されるとき、デバイスは、適切な、非一時的コンピュータ読み取り可能媒体においてソフトウェアに対する命令を記憶していてもよく、1つ以上のプロセッサを使用して、ハードウェアにおいて命令を実行して、本開示の技法を実行してもよい。ビデオエンコーダ200およびビデオデコーダ300のそれぞれは、1つ以上のエンコーダまたはデコーダ中に含まれていてもよく、エンコーダまたはデコーダのどちらかは、それとのデバイスにおいて、組み合わされたエンコーダ／デコーダ(CODEC)の一部として統合されていてもよい。ビデオエンコーダ200および／またはビデオデコーダ300を含むデバイスは、集積回路、マイクロプロセッサ、および／または、セルラ電話機のようなワイヤレス通信デバイスを含んでいてもよい。

10

#### 【0033】

##### [0044]

ビデオエンコーダ200およびビデオデコーダ300は、高効率ビデオコーディング(HEVC)としても呼ばれるITU - T H . 265のようなビデオコーディング標準規格に、または、マルチビューおよび／またはスケーラブルビデオコーディング拡張のような、高効率ビデオコーディング(HEVC)に対する拡張にしたがって動作してもよい。代替的に、ビデオエンコーダ200およびビデオデコーダ300は、共同調査テストモデル(JEM)またはバーサタイルビデオコーディング(VVC)としても呼ばれるITU - T H . 266のような、他のプロプライエタリまたは業界標準規格にしたがって動作してもよい。VVC標準規格のドラフトは、プロスラにおける「バーサタイルビデオコーディング(ドラフト5)」、ITU - T SG16WP3およびISO / IEC JTC1 / SC29 / WG11のジョイントビデオエキスパートチーム(JVET)、第14回ミーティング：スイス国ジュネーブ、2019年3月19日～27日、JVET - M1001 - v5(以下「VVCドラフト5」)で説明されている。しかしながら、本開示の技術は、何らかの特定のコーディング標準規格には限定されない。

20

30

#### 【0034】

##### [0045]

一般的に、ビデオエンコーダ200およびビデオデコーダ300は、ピクチャーのブロックベースコーディングを実行してもよい。「ブロック」という用語は、一般的に、処理される(例えば、エンコードされる、デコードされる、または、そうでなければ、エンコーディングおよび／またはデコーディングプロセスにおいて使用される)データを含む構造を指している。例えば、ブロックは、ルミナンスデータおよび／またはクロミナンスデータのサンプルの2次元行列を含んでいてもよい。一般的に、ビデオエンコーダ200およびビデオデコーダ300は、YUV(例えば、Y、Cb、Cr)フォーマットで表されるビデオデータをコード化してもよい。すなわち、ピクチャーのサンプルに対する赤、緑および青(RGB)データをコード化するよりもむしろ、ビデオエンコーダ200およびビデオデコーダ300は、ルミナンス成分とクロミナンス成分とをコード化してもよく、クロミナンス成分は、赤の色相と青の色相の両方のクロミナンス成分を含んでいてもよい。いくつかの例では、ビデオエンコーダ200は、エンコーディングの前に、受け取った

40

50

R G B フォーマットされたデータを Y U V 表現に変換し、ビデオデコーダ 3 0 0 は、 Y U V 表現を R G B フォーマットに変換する。代替的に、（図示されていない）前処理ユニットおよび後処理ユニットがこれらの変換を実行してもよい。

#### 【 0 0 3 5 】

##### [ 0 0 4 6 ]

本開示は、一般的に、ピクチャーのデータをエンコードまたはデコードするプロセスを含むように、ピクチャーのコーディング（例えば、エンコーディングおよびデコーディング）に言及しているかもしれない。同様に、本開示は、ブロックに対するデータをエンコードまたはデコードするプロセス、例えば、予測および／または残差コーディングを含むように、ピクチャーのブロックのコーディングに言及しているかもしれない。エンコードされたビデオビットストリームは、一般的に、コーディング決定（例えば、コーディングモード）とブロックへのピクチャーの区分とを表す、シンタックス要素に対する一連の値を含んでいる。したがって、ピクチャーまたはブロックをコード化することへの言及は、一般的に、ピクチャーまたはブロックを形成するシンタックス要素に対する値をコード化することとして理解すべきである。

10

#### 【 0 0 3 6 】

##### [ 0 0 4 7 ]

H E V C は、コーディングユニット（ C U ）、予測ユニット（ P U ）および変換ユニット（ T U ）を含む、さまざまなブロックを規定する。H E V C にしたがうと、（ビデオエンコーダ 2 0 0 のような）ビデオコーダは、4 分ツリー構造にしたがって、コーディングツリーユニット（ C T U ）を C U に区分する。すなわち、ビデオコーダは、 C T U および C U を 4 つの等しい、オーバーラップしない正方形に区分し、4 分ツリーの各ノードは、ゼロまたは 4 つの子ノードのいずれかを有する。子ノードのないノードは、「リーフノード」として呼ばれることがあり、このようなリーフノードの C U は、1 つ以上の P U および／または 1 つ以上の T U を含んでいてもよい。ビデオコーダは、 P U と T U とをさらに区分してもよい。例えば、 H E V C では、残差 4 分ツリー（ R Q T ）は T U の区分を表している。H E V C では、 P U はインター予測データを表す一方で、 T U は残差データを表している。イントラ予測される C U は、イントラモードインジケーションのようなイントラ予測情報を含んでいる。

20

#### 【 0 0 3 7 】

30

##### [ 0 0 4 8 ]

別の例として、ビデオエンコーダ 2 0 0 およびビデオデコーダ 3 0 0 は、 V V C にしたがって動作するように構成されていてもよい。V V C によると、（ビデオエンコーダ 2 0 0 のような）ビデオコーダは、ピクチャーを複数のコーディングツリーユニット（ C T U ）に区分する。ビデオエンコーダ 2 0 0 は、4 分ツリー - 2 分ツリー（ Q T B T ）構造またはマルチタイプツリー（ M T T ）構造のようなツリー構造にしたがって、 C T U を区分してもよい。Q T B T 構造は、 H E V C の C U と P U と T U との間の分離のような、複数の区分タイプの概念を除去する。Q T B T 構造は、4 分ツリー区分にしたがって区分される第 1 のレベルと、2 分ツリー区分にしたがって区分される第 2 のレベルと、の 2 つのレベルを含んでいる。Q T B T 構造のルートノードは C T U に対応する。2 分ツリーのリーフノードは、コーディングユニット（ C U ）に対応する。

40

#### 【 0 0 3 8 】

##### [ 0 0 4 9 ]

M T T 区分構造では、4 分ツリー（ Q T ）区分、2 分ツリー（ B T ）区分、および／または、（ターナリーツリー（ T T ）とも呼ばれる）3 分ツリー（ T T ）区分の 1 つ以上のタイプを使用して、ブロックを区分してもよい。3 分またはターナリーツリー区分は、ブロックが 3 つのサブブロックに分割される区分である。いくつかの例では、3 分またはターナリーツリー区分は、中心を通して元のブロックを分けずに、ブロックを 3 つのサブブロックに分ける。M T T における区分タイプ（例えば、 Q T 、 B T および T T ）は、対称または非対称であってもよい。

50

【0039】

[0050]

いくつかの例では、ビデオエンコーダ200およびビデオデコーダ300は、単一のQTB TまたはMTT構造を使用して、ルミナンス成分とクロミナンス成分のそれぞれを表してもよい一方で、他の例では、ビデオエンコーダ200およびビデオデコーダ300は、ルミナンス成分のために1つのQTB T / MTT構造と、両方のクロミナンス成分のために別のQTB T / MTT構造（または、それぞれのクロミナンス成分のために2つのQTB T / MTT構造）のように、2つ以上のQTB TまたはMTT構造を使用してもよい。

【0040】

[0051]

10

ビデオエンコーダ200およびビデオデコーダ300は、HEVC毎の4分ツリー区分、QTB T区分、MTT区分、または、他の区分構造を使用するように構成されていてもよい。説明のために、本開示の技法の説明は、QTB T区分に関して提示する。しかしながら、本開示の技法はまた、4分ツリー区分、MTT区分、または、他のタイプの区分も同様に使用するように構成されているビデオコーダに適用してもよいことを理解されたい。

【0041】

[0052]

いくつかの例では、CTUは、ルーマサンプルのコーディングツリープロック(CTB)、3つのサンプルアレイを有するピクチャーのクロマサンプルの2つの対応するCTB、あるいは、モノクロームピクチャーまたはサンプルをコード化するために使用される3つの別個の色平面およびシンタックス構造を使用してコード化されるピクチャーのサンプルのCTBを含んでいる。成分のCTBへの分割が区分であるように、CTBは、Nのいくつかの値に対するサンプルのN×Nブロックであってもよい。成分は、4：2：0、4：2：2または4：4：4の色フォーマットでピクチャーを構成する3つのアレイ（ルーマおよび2つのクロマ）のうちの1つからのアレイまたは単一のサンプル、あるいは、モノクロームフォーマットでピクチャーを構成するアレイまたはサンプルのアレイの単一のサンプルである。いくつかの例では、CTBのコーディングブロックへの分割が区分であるように、コーディングブロックは、MおよびNのいくつかの値に対するサンプルのM×Nブロックである。

20

【0042】

[0053]

30

ブロック（例えば、CTUまたはCU）は、ピクチャー中でさまざまな方法でグループ化されてもよい。1つの例として、ブリックは、ピクチャー中の特定のタイル内のCTU行の矩形領域を指しているかもしれない。タイルは、ピクチャー中の特定のタイル列および特定のタイル行内のCTUの矩形領域であるかもしれない。タイル列は、ピクチャーの高さに等しい高さと、（例えば、ピクチャーパラメータセット中のような）シンタックス要素により指定される幅とを有するCTUの矩形領域を指している。タイル行は、（例えば、ピクチャーパラメータセット中のような）シンタックス要素により指定される高さと、ピクチャーの幅に等しい幅とを有するCTUの矩形領域を指している。

【0043】

[0054]

40

いくつかの例では、タイルは、それぞれがタイル内に1つ以上のCTU行を含んでいるかもしれない複数のブリックに区分されてもよい。複数のブリックに区分されないタイルは、ブリックとして呼ばれることがある。しかしながら、タイルの真のサブセットであるブリックは、タイルとして呼ばれないかもしれない。

【0044】

[0055]

ピクチャー中のブリックは、スライスで配置されるかもしれない。スライスは、単一のネットワークアブストラクションレイヤ（NAL）ユニット中に排他的に含まれているかもしれないピクチャーの整数個のブリックであってもよい。いくつかの例では、スライスは

50

、多数の完全なタイルまたは1つのタイルの完全なブリックの連続するシーケンスのみのいずれかを含んでいる。

#### 【0045】

[0056]

本開示は、「 $N \times N$ 」および「 $N$ バイ $N$ 」を交換可能に使用して、垂直寸法および水平寸法に関する(CUまたは他のビデオブロックのような)ブロックのサンプル寸法、例えば、 $16 \times 16$ サンプルまたは $16$ バイ $16$ サンプルを指すかもしれない。一般的に、 $16 \times 16$ のCUは、垂直方向に16個のサンプルを有し( $y = 16$ )、水平方向に16個のサンプルを有する( $x = 16$ )。同様に、 $N \times N$ のCUは、一般的に、垂直方向にN個のサンプルを有し、水平方向にN個のサンプルを有し、Nは非負整数値を表している。CU中のサンプルは、行および列に配置されていてもよい。さらに、CUは、必ずしも水平方向に垂直方向と同じ数のサンプルを有する必要はない。例えば、CUは $N \times M$ のサンプルを含んでいてもよく、Mは必ずしもNに等しいとは限らない。

10

#### 【0046】

[0057]

ビデオエンコーダ200は、予測および/または残差情報を、ならびに、他の情報を表す、CUに対するビデオデータをエンコードする。予測情報は、CUに対する予測プロックを形成するために、CUがどのように予測されるべきかを示している。残差情報は、一般的に、エンコーディング前のCUのサンプルと予測プロックとの間のサンプル毎の差分を表している。

20

#### 【0047】

[0058]

CUを予測するために、ビデオエンコーダ200は、一般的に、インター予測またはイントラ予測を通して、CUに対する予測プロックを形成してもよい。インター予測は、一般的に、以前にコード化されたピクチャーのデータからCUを予測することを指す一方で、イントラ予測は、一般的に、同じピクチャーの以前にコード化されたデータからCUを予測することを指している。インター予測を実行するために、ビデオエンコーダ200は、1つ以上の動きベクトルを使用して、予測プロックを発生させててもよい。ビデオエンコーダ200は、一般的に、動きサーチを実行して、例えば、CUと参照プロックとの間の差分について、CUに密接に一致する参照プロックを識別してもよい。ビデオエンコーダ200は、絶対差分の和(SAD)、二乗差分の和(SSD)、平均絶対差分(MAD)、平均二乗差分(MSD)、または、他のこのような差分計算を使用して、差分メトリックを計算し、参照プロックが現在CUに密接に一致するか否かを決定してもよい。いくつかの例では、ビデオエンコーダ200は、単方向予測または双方向予測を使用して、現在CUを予測してもよい。

30

#### 【0048】

[0059]

VVCのいくつかの例はまた、インター予測モードと見なしてもよいアフィン動き補償モードを提供する。アフィン動き補償モードでは、ビデオエンコーダ200は、ズームインまたはズームアウト、回転、透視動き、または、他の不規則な動きタイプのような、並進しない動きを表す2つ以上の動きベクトルを決定してもよい。

40

#### 【0049】

[0060]

イントラ予測を実行するために、ビデオエンコーダ200は、イントラ予測モードを選択して、予測プロックを発生させてもよい。VVCのいくつかの例は、さまざまな方向性モードとともに、planarモードおよびDCモードを含む、67個のイントラ予測モードを提供する。一般的に、ビデオエンコーダ200は、現在プロックのサンプルを予測する、現在プロック(例えば、CUのプロック)に隣接するサンプルを記述するイントラ予測モードを選択する。ビデオエンコーダ200がラスター走査順序(左から右、上から下)でCTUおよびCUをコード化すると仮定すると、このようなサンプルは、一般的に

50

、現在ブロックと同じピクチャー中で、現在ブロックの上、左上または左にあってもよい。

#### 【0050】

##### [0061]

ビデオエンコーダ200は、現在ブロックに対する予測モードを表すデータをエンコードする。例えば、インター予測モードに対して、ビデオエンコーダ200は、さまざまな利用可能なインター予測モードのうちのどれが使用されるかを表すデータとともに、対応するモードに対する動き情報をエンコードしてもよい。単方向または双方向インター予測に対して、例えば、ビデオエンコーダ200は、高度動きベクトル予測(AMVP)モードまたはマージモードを使用して、動きベクトルをエンコードしてもよい。ビデオエンコーダ200は、類似するモードを使用して、アフィン動き補償モードに対する動きベクトルをエンコードしてもよい。

10

#### 【0051】

##### [0062]

ブロックのイントラ予測またはインター予測のような予測に続いて、ビデオエンコーダ200は、ブロックに対する残差データを計算してもよい。残差ブロックのような残差データは、ブロックと、対応する予測モードを使用して形成された、ブロックに対する予測ブロックとの間の、サンプル毎の差分を表している。ビデオエンコーダ200は、1つ以上の変換を残差ブロックに適用して、サンプルドメインの代わりに変換ドメインにおいて、変換されたデータを生成させてもよい。例えば、ビデオエンコーダ200は、離散コサイン変換(DCT)、整数変換、ウェーブレット変換、または、概念的に類似する変換を残差ビデオデータに適用してもよい。さらに、ビデオエンコーダ200は、モード依存非分離2次変換(MDNSSST)、信号依存変換、カルーネンレーベ変換(KLT)、または、これらに類するもののような、第1の変換に続く2次変換を適用してもよい。ビデオエンコーダ200は、1つ以上の変換の適用に続いて、変換係数を生成させる。

20

#### 【0052】

##### [0063]

上述のように、変換係数を生成させるための任意の変換に続いて、ビデオエンコーダ200は、変換係数の量子化を実行してもよい。量子化は、一般的に、変換係数が量子化されて、変換係数を表すために使用されるデータの量を場合によっては低減させ、さらなる圧縮を提供するプロセスを指している。量子化プロセスを実行することによって、ビデオエンコーダ200は、変換係数のいくつか、または、すべてに関係するビット深度を低減させてもよい。例えば、ビデオエンコーダ200は、量子化の間にn - ビット値をm - ビット値に切り捨ててもよく、nはmよりも大きい。いくつかの例では、量子化を実行するために、ビデオエンコーダ200は、量子化されるべき値のビット単位の右シフトを実行してもよい。

30

#### 【0053】

##### [0064]

量子化に続いて、ビデオエンコーダ200は、変換係数を走査し、量子化された変換係数を含む2次元行列から1次元ベクトルを生成させてもよい。走査は、より高いエネルギー(したがって、より低い周波数)の変換係数をベクトルの前部に配置し、より低いエネルギー(したがって、より高い周波数)の変換係数をベクトルの後部に配置するように設計されていてもよい。いくつかの例では、ビデオエンコーダ200は、予め規定された走査順序を利用して、量子化変換係数を走査し、シリアル化ベクトルを生成させ、その後、ベクトルの量子化変換係数をエントロピーエンコードしてもよい。他の例では、ビデオエンコーダ200は、適応走査を実行してもよい。量子化変換係数を走査して1次元ベクトルを形成した後、ビデオエンコーダ200は、例えば、コンテキスト適応バイナリ算術コーディング(CABAC)にしたがって、1次元ベクトルをエントロピーエンコードしてもよい。ビデオエンコーダ200はまた、ビデオデータをデコードする際に、ビデオエンコーダ300によって使用するために、エンコードされたビデオデータに関するメタデータを記述するシンタックス要素に対する値をエントロピーエンコードしてもよい。

40

50

【 0 0 5 4 】

[ 0 0 6 5 ]

C A B A C を実行するために、ビデオエンコーダ 2 0 0 は、コンテキストモデル内のコンテキストを送信されるべきシンボルに割り当ててもよい。コンテキストは、例えば、シンボルの隣接する値がゼロ値にされているか否かに関連していてもよい。確率決定は、シンボルに割り当てられているコンテキストに基づいていてもよい。

【 0 0 5 5 】

[ 0 0 6 6 ]

ビデオエンコーダ 2 0 0 はさらに、例えば、ピクチャーヘッダ中で、ロックヘッダ中で、スライスヘッダ中で、あるいは、シーケンスパラメータセット ( S P S ) 、ピクチャーパラメータセット ( P P S ) 、または、ビデオパラメータセット ( V P S ) のような他のシンタックスデータ中で、ビデオデコーダ 3 0 0 への、ロックベースのシンタックスデータ、ピクチャーベースのシンタックスデータ、および、シーケンスベースのシンタックスデータのようなシンタックスデータを発生させてもよい。ビデオデコーダ 3 0 0 は、同様に、このようなシンタックスデータをデコードして、対応するビデオデータをどのようにデコードするかを決定してもよい。

10

【 0 0 5 6 】

[ 0 0 6 7 ]

このようにして、ビデオエンコーダ 2 0 0 は、エンコードされたビデオデータを含む、例えば、ロック ( 例えば、 C U ) へのピクチャーの区分と、ロックに対する予測および / または残差情報を記述する、シンタックス要素を含む、ビットストリームを発生させてもよい。最終的に、ビデオデコーダ 3 0 0 は、ビットストリームを受け取り、エンコードされたビデオデータをデコードしてもよい。

20

【 0 0 5 7 】

[ 0 0 6 8 ]

一般的に、ビデオデコーダ 3 0 0 は、ビデオエンコーダ 2 0 0 によって実行されたプロセスとは逆のプロセスを実行して、ビットストリームのエンコードされたビデオデータをデコードする。例えば、ビデオデコーダ 3 0 0 は、ビデオエンコーダ 2 0 0 の C A B A C エンコーディングプロセスと、逆ではあるが、実質的に類似する方法で、 C A B A C を使用して、ビットストリームのシンタックス要素に対する値をデコードしてもよい。シンタックス要素は、 C T U にピクチャーを区分するための区分情報と、 Q T B T 構造のような、対応する区分構造にしたがって、各 C T U を区分することとを規定して、 C T U の C U を規定していくてもよい。シンタックス要素は、ビデオデータのロック ( 例えば、 C U ) に対する予測および残差情報をさらに規定していくてもよい。

30

【 0 0 5 8 】

[ 0 0 6 9 ]

残差情報は、例えば、量子化変換係数によって表されていてもよい。ビデオデコーダ 3 0 0 は、ロックの量子化された変換係数を逆量子化および逆変換して、ロックに対する残差ロックを再生させてもよい。ビデオデコーダ 3 0 0 は、シグナリングされた予測モード ( イントラ予測またはインター予測 ) と、関連する予測情報 ( 例えば、インター予測に対する動き情報 ) とを使用して、ロックに対する予測ロックを形成する。ビデオデコーダ 3 0 0 は、その後、 ( サンプル毎のベースで ) 予測ロックと残差ロックとを組み合わせて、元のロックを再生させてもよい。ビデオデコーダ 3 0 0 は、デブロッキングプロセスを実行することのような、追加の処理を実行して、ロックの境界に沿った視覚的アーティファクトを低減させてもよい。

40

【 0 0 5 9 】

[ 0 0 7 0 ]

本開示の技法によれば、ビデオエンコーダ 2 0 0 およびビデオデコーダ 3 0 0 は、ビデオデータのロック中の標準的に規定されている 0 係数のパターンに基づいて、低周波数非分離変換インデックスまたはフラグの値をシグナリングしない / 推測するようにと、低

50

周波数非分離変換インデックスまたはフラグにしたがって、ビデオデータのブロックを変換するように構成されていてもよい。例えば、ビデオエンコーダ300は、ビデオデータの変換ブロック中の最後の有意係数の位置を決定するようにと、変換ブロックの0化領域に対する最後の有意係数の位置に基づいて、変換ブロックに対するL F N S T インデックスの値を決定し、変換ブロックの0化領域は、変換ブロックのL F N S T 領域内の第1の領域と、L F N S T 領域外の変換ブロックの第2の領域との両方を含むようにと、L F N S T インデックスの値にしたがって、変換ブロックを逆変換するように構成されていてもよい。

#### 【0060】

[0071]

10

本開示は、一般的に、シンタックス要素のような、ある情報を「シグナリングすること」に関連しているかもしれない。「シグナリング」という用語は、一般的に、シンタックス要素のおよび／またはエンコードされたビデオデータをデコードするのに使用される他のデータの値の通信に関連しているかもしれない。すなわち、ビデオエンコーダ200は、ビットストリーム中でシンタックス要素に対する値をシグナリングしてもよい。一般的に、シグナリングは、ビットストリーム中で値を発生させることを指している。上述のように、発信元デバイス102は、実質的にリアルタイムで、または、宛先デバイス116による後の取り出しのために、シンタックス要素を記憶デバイス112中に記憶させるときに起こるかもしれないような、リアルタイムではなく、ビットストリームを宛先デバイス116に転送してもよい。

20

#### 【0061】

[0072]

図2Aおよび図2Bは、例示的な4分ツリー2分ツリー(Q T B T)構造130と、対応するコーディングツリーユニット(C T U)132とを図示する概念図である。実線は4分ツリー分割を表し、点線は2分ツリー分割を表している。2分ツリーの各分割(すなわち、非リーフ)ノードにおいて、どの分割タイプ(すなわち、水平または垂直)が使用されるかを示すために1つのフラグがシグナリングされ、この例では、0が水平分割を示し、1が垂直分割を示している。4分ツリー分割に対して、4分ツリーノードは、ブロックを等しいサイズで4つのサブブロックに水平および垂直に分割するので、分割タイプを示す必要はない。したがって、Q T B T 構造130の領域ツリーレベルに対する(分割情報のような)シンタックス要素(すなわち、実線)と、Q T B T 構造130の予測ツリーレベルに対する(分割情報のような)シンタックス要素(すなわち、破線)を、ビデオエンコーダ200はエンコードしてもよく、ビデオデコーダ300は、デコードしてもよい。Q T B T 構造130の終端リーフノードにより表されるC Uに対する予測データおよび変換データのようなビデオデータを、ビデオエンコーダ200はエンコードしてもよく、ビデオデコーダ300は、デコードしてもよい。

30

#### 【0062】

[0073]

一般的に、図2BのC T U 132は、第1および第2のレベルにおけるQ T B T 構造130のノードに対応するブロックのサイズを規定するパラメータと関係しているかもしれない。これらのパラメータは、(サンプル中のC T U 132のサイズを表す)C T U サイズと、(M i n Q T S i z e、最小許容4分ツリーリーフノードサイズを表す)最小4分ツリーサイズと、(M a x B T S i z e、最大許容2分ツリールートノードサイズを表す)最大2分ツリーサイズと、(M a x B T D e p t h、最大許容2分ツリー深度を表す)最大2分ツリー深度と、(M i n B T S i z e、最小許容2分ツリーリーフノードサイズを表す)最小2分ツリーサイズとを含んでいてもよい。

40

#### 【0063】

[0074]

C T U に対応するQ T B T 構造のルートノードは、Q T B T 構造の第1のレベルにおいて4つの子ノードを有してもよく、それぞれが4分ツリー区分にしたがって、区分されて

50

いてもよい。すなわち、第1のレベルのノードは、（子ノードを有さない）リーフノードであるか、または、4つの子ノードを有していてもよい。Q T B T構造130の例は、親ノードと、分岐に対する実線を有する子ノードとを含むようなノードを表している。第1のレベルのノードが最大許容2分ツリールートノードサイズ（M a x B T S i z e）より大きくない場合には、ノードは、それぞれの2分ツリーによりさらに区分することができる。分割により得られたノードが最小許容2分ツリーリーフノードサイズ（M i n B T S i z e）または最大許容2分ツリー深度（M a x B T D e p t h）に達するまで、1つのノードの2分ツリー分割を繰り返すことができる。Q T B T構造130の例は、分岐に対して破線を有するようなノードを表している。2分ツリーリーフノードは、コーディングユニット（C U）として呼ばれ、これは、何らかのさらなる区分なく、予測（例えば、イントラピクチャーまたはインターピクチャー予測）および変換に対して使用される。上記で説明したように、C Uは、「ビデオブロック」または「ブロック」として呼ばれることがある。

#### 【0064】

##### [0075]

Q T B T区分構造の1つの例では、C T Uサイズは $128 \times 128$ （ルーマサンプルおよび2つの対応する $64 \times 64$ クロマサンプル）として設定され、M i n Q T S i z eは $16 \times 16$ として設定され、M a x B T S i z eは $64 \times 64$ として設定され、（幅および高さの両方に対して）M i n B T S i z eは4として設定され、M a x B T D e p t hは4として設定される。まず、C T Uに対して4分ツリー区分を適用して、リーフ4分ツリーノードを発生させる。リーフ4分ツリーノードは、 $16 \times 16$ （すなわち、M i n Q T S i z e）から $128 \times 128$ （すなわち、C T Uサイズ）までのサイズを有していてもよい。リーフ4分ツリーノードが $128 \times 128$ である場合には、サイズがM a x B T S i z e（すなわち、この例では、 $64 \times 64$ ）を超えることから、ノードは、2分ツリーにより、さらに分割されないだろう。そうでなければ、リーフ4分ツリーノードは、2分ツリーにより、さらに区分されるであろう。したがって、4分ツリーリーフノードはまた、2分ツリーに対するルートノードであり、0としての2分ツリー深度を有する。2分ツリー深度がM a x B T D e p t h（この例では、4）に達するときには、それ以上の分割は許されない。2分ツリーノードがM i n B T S i z e（この例では、4）に等しい幅を有するときには、それ以上の水平分割は許されないことを意味する。同様に、M i n B T S i z eに等しい高さを有する2分ツリーノードは、その2分ツリーノードに対してそれ以上の垂直分割は許されないことを意味する。上述したように、2分ツリーのリーフノードはC Uと呼ばれ、さらなる区分なしで、予測および変換にしたがって、さらに処理される。

#### 【0065】

##### [0076]

図3は、本開示の技法を実行してもよい、例示的なビデオエンコーダ200を図示するプロック図である。図3は、説明の目的のために提供されており、本開示において広く例示し説明しているような技法の限定と見なすべきではない。説明の目的のために、本開示は、開発中のH . 265（HEVC）ビデオコーディング標準規格およびH . 266（VCC）ビデオコーディング標準規格のような、ビデオコーディング標準規格の状況で、ビデオエンコーダ200を説明している。しかしながら、本開示の技法は、これらのビデオコーディング標準規格には限定されず、一般的に、ビデオエンコーディングおよびデコーディングに適用可能である。

#### 【0066】

##### [0077]

図3の例では、ビデオエンコーダ200は、ビデオデータメモリ230と、モード選択ユニット202と、残差発生ユニット204と、変換処理ユニット206と、量子化ユニット208と、逆量子化ユニット210と、逆変換処理ユニット212と、再構築ユニット214と、フィルタユニット216と、デコードピクチャーバッファ（D B P）218

と、エントロピーエンコーディングユニット220とを含んでいる。ビデオデータメモリ230と、モード選択ユニット202と、残差発生ユニット204と、変換処理ユニット206と、量子化ユニット208と、逆量子化ユニット210と、逆変換処理ユニット212と、再構築ユニット214と、フィルタユニット216と、DBP218と、エントロピーエンコーディングユニット220のいずれかまたはすべてを、1つ以上のプロセッサ中で、または、処理回路中で実現してもよい。さらに、ビデオエンコーダ200は、これらまたは他の機能を実行するために、追加または代替のプロセッサまたは処理回路を含んでいてもよい。

【0067】

[0078]

10

ビデオデータメモリ230は、ビデオエンコーダ200のコンポーネントによってエンコードされるべきビデオデータを記憶していてもよい。ビデオエンコーダ200は、例えば、ビデオソース104(図1)からのビデオデータメモリ230中に記憶されているビデオデータを受け取ってもよい。DPB218は、ビデオエンコーダ200による後続のビデオデータの予測において使用するための参照ビデオデータを記憶する参照ピクチャーメモリとして機能してもよい。ビデオデータメモリ230およびDPB218は、同期ダイナミックランダムアクセスメモリ(DRAM)(SDRAM)を含むDRAM、磁気抵抗RAM(MRAM)、抵抗RAM(RRAM(登録商標))、または、他のタイプのメモリデバイスのような、さまざまなメモリデバイスのうちのいずれかによって形成されてもよい。ビデオデータメモリ230およびDPB218は、同じメモリデバイスまたは別個のメモリデバイスによって提供されていてもよい。さまざまな例では、ビデオデータメモリ230は、図示するように、ビデオエンコーダ200の他のコンポーネントとともにオンチップであってもよく、または、これらのコンポーネントに対してオフチップであってもよい。

【0068】

[0079]

20

本開示では、ビデオデータメモリ230への参照は、そのように具体的に説明されない限り、ビデオエンコーダ200に対して内部であるメモリ、または、そのように具体的に説明されない限り、ビデオエンコーダ200に対して外部であるメモリに限定されるものとして解釈すべきではない。むしろ、ビデオデータメモリ230への参照は、ビデオエンコーダ200がエンコードするために受け取るビデオデータ(例えば、エンコードされるべき現在ブロックに対するビデオデータ)を記憶する参照メモリとして理解すべきである。図1のメモリ106はまた、ビデオエンコーダ200のさまざまなユニットからの出力の一時記憶装置を提供してもよい。

30

【0069】

[0080]

図3のさまざまなユニットは、ビデオエンコーダ200によって実行される動作の理解を助けるために図示されている。ユニットは、固定機能回路、プログラマブル回路、または、これらの組み合わせとして実現してもよい。固定機能回路は、特定の機能性を提供する回路を指し、実行できる動作に対して予め設定される。プログラマブル回路は、さまざまなタスクを実行するようにプログラムでき、実行できる動作において柔軟な機能性を提供できる回路を指している。例えば、プログラマブル回路は、ソフトウェアまたはファームウェアの命令によって規定される方法でプログラマブル回路を動作させるソフトウェアまたはファームウェアを実行してもよい。固定機能回路は、(例えば、パラメータを受け取るまたはパラメータを出力するために)ソフトウェア命令を実行するかもしれないが、固定機能回路が実行する動作のタイプは一般的に不变である。いくつかの例では、ユニットのうちの1つ以上は、別個の回路ブロック(固定機能またはプログラマブル)であってよく、いくつかの例では、1つ以上のユニットは集積回路であってよい。

40

【0070】

[0081]

50

ビデオエンコーダ200は、プログラマブル回路から形成される、算術論理ユニット( A L U )、基本機能ユニット( E F U )、デジタル回路、アナログ回路、および／または、プログラマブルコアを含んでいてもよい。ビデオエンコーダ200の動作がプログラマブル回路によって実行されるソフトウェアを使用して実施される例では、メモリ106( 図1 )は、ビデオエンコーダ200が受け取って実行するソフトウェアのオブジェクトコード、すなわち命令を記憶していてもよく、または、ビデオエンコーダ200内の( 図示されていない )別のメモリがこのようなオブジェクトコードを記憶していてもよい。

#### 【 0 0 7 1 】

##### [ 0 0 8 2 ]

ビデオデータメモリ230は、受け取ったビデオデータを記憶するように構成されている。ビデオエンコーダ200は、ビデオデータメモリ230からビデオデータのピクチャーを取り出し、ビデオデータを残差発生ユニット204およびモード選択ユニット202に提供してもよい。ビデオデータメモリ230中のビデオデータは、エンコードされるべき生のビデオデータであってもよい。

10

#### 【 0 0 7 2 】

##### [ 0 0 8 3 ]

モード選択ユニット202は、動き推定ユニット222と、動き補償ユニット224と、イントラ予測ユニット226とを含んでいる。モード選択ユニット202は、他の予測モードにしたがってビデオ予測を実行するための追加の機能ユニットを含んでいてもよい。例として、モード選択ユニット202は、パレットユニット、( 動き推定ユニット222および／または動き補償ユニット224の一部であってもよい ) イントラロックユニット、アフィンユニット、線形モデル( LM ) ユニット、または、これらに類するものを含んでいてもよい。

20

#### 【 0 0 7 3 】

##### [ 0 0 8 4 ]

モード選択ユニット202は、一般的に、複数のエンコーディングパスを調整して、エンコーディングパラメータの組み合わせをテストし、結果として、このような組み合わせに対するレート歪み値を得る。エンコーディングパラメータは、 C T U の C U への区分、 C U に対する予測モード、 C U の残差データに対する変換タイプ、 C U の残差データに対する量子化パラメータ等を含んでいてもよい。モード選択ユニット202は、最終的に、他のテストされた組み合わせよりも良好なレート歪み値を有するエンコーディングパラメータの組み合わせを選択してもよい。

30

#### 【 0 0 7 4 】

##### [ 0 0 8 5 ]

ビデオエンコーダ200は、ビデオデータメモリ230から取り出されたピクチャーを一連の C T U に区分し、スライス内に 1 つ以上の C T U をカプセル化してもよい。モード選択ユニット202は、上記で説明した Q T B T 構造、 M T T 構造または H E V C の 4 分ツリー構造のようなツリー構造にしたがって、ピクチャーの C T U を区分してもよい。上記で説明したように、ビデオエンコーダ200は、ツリー構造にしたがって C T U を区分することから 1 つ以上の C U を形成してもよい。このような C U は、一般的に、「ビデオブロック」または「ブロック」として呼ばれることがある。

40

#### 【 0 0 7 5 】

##### [ 0 0 8 6 ]

一般的に、モード選択ユニット202はまた、そのコンポーネント( 例えば、動き推定ユニット222、動き補償ユニット224、および、イントラ予測ユニット226 )を制御して、現在ブロック( 例えば、現在 C U 、または、 H E V C では、 P U と T U とのオーバーラップする部分 )に対する予測ブロックを発生させる。現在ブロックのインター予測のために、動き推定ユニット222は、動きサーチを実行して、 1 つ以上の参照ピクチャー( 例えば、 D P B 2 1 8 中に記憶されている 1 つ以上の以前にコード化されたピクチャー )中の 1 つ以上の密接に一致する参照ブロックを識別してもよい。特に、動き推定ユニ

50

ット 222 は、例えば、絶対差分の和 (S A D)、二乗差分の和 (S S D)、平均絶対差分 (M A D)、平均二乗差分 (M S D)、または、これらに類するものにしたがって、潜在的参照ブロックが現在ブロックにどれだけ類似しているかを表す値を計算してもよい。動き推定ユニット 222 は、一般的に、現在ブロックと考慮されている参照ブロックとの間のサンプル毎の差分を使用して、これらの計算を実行してもよい。動き推定ユニット 222 は、現在ブロックに最も密接に一致する参照ブロックを示す、これらの計算から結果的に生じる最低値を有する参照ブロックを識別してもよい。

#### 【 0076 】

##### [ 0087 ]

動き推定ユニット 222 は、現在ピクチャー中の現在ブロックの位置に対する、参照ピクチャー中の参照ブロックの位置を規定する、1つ以上の動きベクトル (M V) を形成してもよい。動き推定ユニット 222 は、その後、動きベクトルを動き補償ユニット 224 に提供してもよい。例えば、単方向インター予測に対して、動き推定ユニット 222 は単一の動きベクトルを提供するかもしれない一方で、双方向インター予測に対して、動き推定ユニット 222 は2つの動きベクトルを提供するかもしれない。

10

#### 【 0077 】

##### [ 0088 ]

動き補償ユニット 224 は、その後、動きベクトルを使用して、予測ブロックを発生させてもよい。例えば、動き補償ユニット 224 は、動きベクトルを使用して、参照ブロックのデータを取り出してもよい。別の例として、動きベクトルが小数サンプル精度を有する場合には、動き補償ユニット 224 は、1つ以上の補間フィルタにしたがって、予測ブロックに対する値を補間してもよい。さらに、双方向インター予測に対して、動き補償ユニット 224 は、それぞれの動きベクトルによって識別された2つの参照ブロックに対するデータを取り出し、例えば、サンプル毎の平均化または重み付き平均化を通してのように、取り出されたデータを組み合わせてもよい。

20

#### 【 0078 】

##### [ 0089 ]

別の例として、イントラ予測またはイントラ予測コーディングに対して、イントラ予測ユニット 226 は、現在ブロックに隣接するサンプルから予測ブロックを発生させてもよい。例えば、方向モードに対して、イントラ予測ユニット 226 は、一般的に、隣接サンプルの値を数学的に組み合わせ、現在ブロックに渡って規定された方向でこれらの計算された値を格納して、予測ブロックを生成させてもよい。別の例として、D C モードに対して、イントラ予測ユニット 226 は、現在ブロックに対する隣接サンプルの平均を計算し、予測ブロックの各サンプルに対するこの結果として得られる平均を含むように予測ブロックを発生させてもよい。

30

#### 【 0079 】

##### [ 0090 ]

モード選択ユニット 202 は、予測ブロックを残差発生ユニット 204 に提供する。残差発生ユニット 204 は、ビデオデータメモリ 230 から現在ブロックの生のコード化されていないバージョンを受け取り、モード選択ユニット 202 から予測ブロックを受け取る。残差発生ユニット 204 は、現在ブロックと予測ブロックとの間のサンプル毎の差分を計算する。結果として得られるサンプル毎の差分は、現在ブロックに対する残差ブロックを規定する。いくつかの例では、残差発生ユニット 204 はまた、残差ブロック中のサンプル値間の差分を決定して、残差パルスコード変調 (R D P C M) を使用して、残差ブロックを発生させてもよい。いくつかの例では、残差発生ユニット 204 は、バイナリ減算を実行する1つ以上の減算器回路を使用して形成されていてもよい。

40

#### 【 0080 】

##### [ 0091 ]

モード選択ユニット 202 が C U を P U に区分する例では、各 P U は、ルーマ予測ユニットおよび対応するクロマ予測ユニットに関係していてもよい。ビデオエンコーダ 200

50

およびビデオデコーダ 300 は、さまざまなサイズを有する PU をサポートしていてよい。上記で示したように、CU のサイズは、CU のルーマコーディングブロックのサイズを指していてもよく、PU のサイズは、PU のルーマ予測ユニットのサイズを指していてもよい。特定の CU のサイズが  $2N \times 2N$  であると仮定すると、ビデオエンコーダ 200 は、イントラ予測に対する  $2N \times 2N$  または  $N \times N$  の PU サイズと、インター予測に対する  $2N \times 2N$ 、 $2N \times N$ 、 $N \times 2N$ 、 $N \times N$ 、または、これらに類する対称 PU サイズとをサポートしていてよい。ビデオエンコーダ 200 およびビデオデコーダ 300 はまた、インター予測のために、 $2N \times nU$ 、 $2N \times nD$ 、 $nL \times 2N$ 、および、 $nR \times 2N$  の PU サイズに対する非対称区分をサポートしていてよい。

【0081】

10

[0092]

モード選択ユニット 202 が CU を PU にさらに区分しない例では、各 CU は、ルーマコーディングブロックおよび対応するクロマコーディングブロックに関係していてよい。上記のように、CU のサイズは、CU のルーマコーディングブロックのサイズを指していてよい。ビデオエンコーダ 200 およびビデオデコーダ 120 は、 $2N \times 2N$ 、 $2N \times N$ 、または、 $N \times 2N$  の CU サイズをサポートしていてよい。

【0082】

[0093]

イントラブロックコピー モードコーディング、アフィンモードコーディング、および、線形モデル (LM) モードコーディングのような、他のビデオコーディング技法に対して、いくつかの例として、モード選択ユニット 202 は、コーディング技法に関するそれぞれのユニットを介して、エンコードされている現在ブロックに対する予測ブロックを発生させる。パレットモードコーディングのようないくつかの例では、モード選択ユニット 202 は、予測ブロックを発生させず、代わりに、選択されたパレットに基づいて、ブロックを再構築する方法を示すシンタックス要素を発生させてよい。このようなモードでは、モード選択ユニット 202 は、これらのシンタックス要素を、エンコードされるようにエントロピーエンコーディングユニット 220 に提供してもよい。

20

【0083】

[0094]

上記で説明したように、残差発生ユニット 204 は、現在ブロックおよび対応する予測ブロックに対するビデオデータを受け取る。残差発生ユニット 204 は、その後、現在ブロックに対する残差ブロックを発生させる。残差ブロックを発生させるために、残差発生ユニット 204 は、予測ブロックと現在ブロックとの間のサンプル毎の差分を計算する。

30

【0084】

[0095]

変換処理ユニット 206 は、残差ブロックに 1 つ以上の変換を適用して、(ここでは「変換係数ブロック」として呼ばれる) 変換係数のブロックを発生させる。変換処理ユニット 206 は、残差ブロックにさまざまな変換を適用して、変換係数ブロックを形成してもよい。例えば、変換処理ユニット 206 は、離散コサイン変換 (DCT)、方向変換、カルーネンレーベ変換 (KLT)、または、概念的に類似する変換を、残差ブロックに適用してもよい。いくつかの例では、変換処理ユニット 206 は、残差ブロックに対して複数の変換、例えば、回転変換のような、1 次変換と 2 次変換とを実行してもよい。いくつかの例では、変換処理ユニット 206 は、残差ブロックに変換を適用しない。

40

【0085】

[0096]

以下により詳細に説明するように、いくつかの例では、変換処理ユニット 206 は、(例えば、複数の変換選択 (MTS) 技法を使用して) 低周波数非分離変換 (LFNST) と、1 つ以上の分離変換の両方をビデオデータの変換ブロックに適用するように構成されていてよい。変換処理ユニット 206 は、LFNST を適用する前に、最初に、1 つ以上の分離変換を適用してもよい。いくつかの例では、変換処理ユニット 206 は、分離変

50

換を適用した後に得られる変換ブロックの変換係数のサブセットに L F N S T を適用する。 L F N S T が適用される変換ブロックの変換係数のサブセットは、 L F N S T 領域として呼ばれることがある。 L F N S T 領域は、変換ブロックの最も低い周波数変換係数を表す変換ブロックの左上部分であってもよい。

#### 【 0 0 8 6 】

##### [ 0 0 9 7 ]

L F N S T を適用することに関連して、変換処理ユニット 2 0 6 は、 L F N S T 領域中の結果として生じる変換係数の一部分に 0 化プロセスを適用するようにさらに構成されていてもよい。 0 化プロセスは、単に、特定の領域中の各変換係数の値が 0 値を有するようになる。 1 つの例では、変換処理ユニット 2 0 6 は、 L F N S T 領域のより高い周波数エリア（例えば、右下隅）中の変換係数を 0 化してもよい。 加えて、いくつかの例では、変換処理ユニット 2 0 6 はまた、 L F N S T 領域外にある変換ブロック中の変換係数（例えば、いわゆる M T S 領域中の変換係数）を 0 化してもよい。

10

#### 【 0 0 8 7 】

##### [ 0 0 9 8 ]

変換処理ユニット 2 0 6 が変換ブロックに L F N S T を適用した場合には、ビデオエンコーダ 2 0 0 は、 L F N S T インデックスシンタックス要素を発生させてシグナリングしてもよい。 L F N S T インデックスシンタックス要素の値は、 L F N S T を実行するときに使用される、複数の変換の中からの特定の変換を示していてもよい。他の例では、 L F N S T インデックスは、 L F N S T が適用されなかったこと（例えば、 0 の L F N S T インデックス値）を示していてもよい。ビデオエンコーダ 2 0 0 は、 L F N S T が適用されているときに、 L F N S T インデックスを発生させるように構成されていてもよい。 L F N S T が適用されていないときには、ビデオエンコーダ 2 0 0 は、 L F N S T インデックスをシグナリングするか否かを決定するように構成されていてもよい。

20

#### 【 0 0 8 8 】

##### [ 0 0 9 9 ]

例えば、ビデオエンコーダ 2 0 0 は、最後の有意（例えば、非 0 ）変換係数の位置が、 L F N S T が適用されている場合に通常は 0 化されるであろう変換ブロック中の位置にあるケースでは、 L F N S T インデックスをシグナリングしないことを決定してもよい。これは、ビデオエンコーダ 2 0 0 が、最後の有意係数の位置を示す 1 つ以上のシンタックス要素を発生させ、エンコードされたビデオビットストリーム中でシグナリングするからである。ビデオデコーダ 3 0 0 は、最初に、最後の有意係数の位置を受信してデコードすることになるので、ビデオデコーダ 3 0 0 は、最後の有意係数の位置が、変換ブロックの 0 化領域中にある場合には、 L F N S T が実行されていないことを示す L F N S T インデックスを受信する必要がない。むしろ、ビデオデコーダ 3 0 0 は、最後の有意係数の位置に基づいて、 L F N S T インデックスの値が 0 であり、 L F N S T が適用されていないことを推測（例えば、明示的なシンタックス要素なしで決定）してもよい。 L F N S T がビデオエンコーダ 2 0 0 により適用されていないが、最後の有意係数の位置が 0 化領域中にならない場合には、いくつかの例では、ビデオエンコーダ 2 0 0 は、 L F N S T インデックスをシグナリングする。

30

#### 【 0 0 8 9 】

##### [ 0 1 0 0 ]

量子化ユニット 2 0 8 は、変換係数ブロック中の変換係数を量子化して、量子化された変換係数ブロックを生成させてもよい。量子化ユニット 2 0 8 は、現在ブロックに関係する量子化パラメータ（ Q P ）値にしたがって、変換係数ブロックの変換係数を量子化してもよい。ビデオエンコーダ 2 0 0 は（例えば、モード選択ユニット 2 0 2 を介して）、 C U に関係する Q P 値を調節することによって、現在ブロックに関係する変換係数ブロックに適用される量子化の程度を調節してもよい。量子化は、情報の損失をもたらすかもしれない。したがって、量子化された変換係数は、変換処理ユニット 2 0 6 によって生成された元の変換係数よりも低い精度を有するかもしれない。

40

50

## 【0090】

[0101]

逆量子化ユニット210および逆変換処理ユニット212は、逆量子化および逆変換をそれぞれ量子化された変換係数ブロックに適用して、変換係数ブロックから残差ブロックを再構築してもよい。再構築ユニット214は、再構築された残差ブロックと、モード選択ユニット202によって発生させた予測ブロックとに基づいて、（潜在的にある程度の歪みを有するが）現在ブロックに対応する再構築されたブロックを生成させてもよい。例えば、再構築ユニット214は、再構築された残差ブロックのサンプルを、モード選択ユニット202によって発生させた予測ブロックからの対応するサンプルに追加して、再構築されたブロックを生成させてもよい。

10

## 【0091】

[0102]

フィルタユニット216は、再構築されたブロックに対して1つ以上のフィルタ動作を実行してもよい。例えば、フィルタユニット216は、デブロッキング動作を実行して、CUのエッジに沿ったブロックキネスアーティファクトを低減させてもよい。いくつかの例では、フィルタユニット216の動作はスキップしてもよい。

## 【0092】

[0103]

ビデオエンコーダ200は、再構築されたブロックをDPB218中に記憶させる。例えば、フィルタユニット216の動作が必要とされない例では、再構築ユニット214は、再構築されたブロックをDPB218中に記憶させてもよい。フィルタユニット216の動作が必要とされる例では、フィルタユニット216は、再構築されフィルタされたブロックをDPB218中に記憶させてもよい。動き推定ユニット222および動き補償ユニット224は、再構築された（そして、潜在的にフィルタ処理された）ブロックから形成された参照ピクチャーをDPB218から取り出して、後にエンコードされるピクチャーのブロックをインター予測してもよい。加えて、イントラ予測ユニット226は、現在ピクチャーのDPB218中の再構築されたブロックを使用して、現在ピクチャー中の他のブロックをイントラ予測してもよい。

20

## 【0093】

[0104]

一般的に、エントロピーエンコーディングユニット220は、ビデオエンコーダ200の他の機能的なコンポーネントから受け取ったシンタックス要素をエントロピーエンコードしてもよい。例えば、エントロピーエンコーディングユニット220は、量子化ユニット208からの量子化された変換係数ブロックをエントロピーエンコードしてもよい。別の例として、エントロピーエンコーディングユニット220は、モード選択ユニット202からの予測シンタックス要素（例えば、インター予測に対する動き情報またはイントラ予測に対するイントラモード情報）をエントロピーエンコードしてもよい。エントロピーエンコーディングユニット220は、ビデオデータの別の例であるシンタックス要素に関して、1つ以上のエントロピーエンコーディング動作を実行して、エントロピーエンコードされたデータを発生させてもよい。例えば、エントロピーエンコーディングユニット220は、データに、コンテキスト適応可変長コーディング（C A V L C）動作、C A B A C動作、可変対可変（V2V）長コーディング動作、シンタックスベースのコンテキスト適応バイナリ算術コードディング（S B A C）動作、確率区間分化エントロピー（P I P E）コーディング動作、指数ゴロムエンコーディング動作、または、別のタイプのエントロピーエンコーディング動作を実行してもよい。いくつかの例では、エントロピーエンコーディングユニット220は、シンタックス要素がエントロピーエンコードされないバイパスモードで動作してもよい。

40

## 【0094】

[0105]

ビデオエンコーダ200は、スライスまたはピクチャーのブロックを再構築するのに必

50

要とされるエントロピーエンコードされたシンタックス要素を含むビットストリームを出力してもよい。特に、エントロピーエンコーディングユニット 220 は、ビットストリームを出力してもよい。

#### 【0095】

[0106]

上記で説明している動作は、ブロックに関して説明している。このような説明は、ルーマコーディングブロックおよび / またはクロマコーディングブロックに対する動作として理解すべきである。上述したように、いくつかの例では、ルーマコーディングブロックおよびクロマコーディングブロックは、CU のルーマ成分およびクロマ成分である。いくつかの例では、ルーマコーディングブロックおよびクロマコーディングブロックは、PU のルーマ成分およびクロマ成分である。

10

#### 【0096】

[0107]

いくつかの例では、ルーマコーディングブロックに関して実行される動作は、クロマコーディングブロックに対して繰り返す必要はない。1つの例として、ルーマコーディングブロックに対する動きベクトル (MV) および参照ピクチャーを識別する動作は、クロマブロックに対する MV および参照ピクチャーを識別するために繰り返す必要はない。むしろ、ルーマコーディングブロックに対する MV をスケーリングして、クロマブロックに対する MV を決定してもよく、参照ピクチャーは同じであってもよい。別の例として、イントラ予測プロセスは、ルーマコーディングブロックおよびクロマコーディングブロックに対して同じであってもよい。

20

#### 【0097】

[0108]

以下により詳細に説明するように、ビデオエンコーダ 200 は、ビデオデータを記憶するように構成されているメモリと、回路中で実現され、ビデオデータのブロック中の標準的に規定されている 0 系数のパターンに基づいて、低周波数非分離変換インデックスまたはフラグの値を推測する（例えば、エンコードまたはシグナリングしない）ようにと、低周波数非分離変換インデックスまたはフラグにしたがって、ビデオデータのブロックを変換するように構成されている 1 つ以上の処理ユニットとを含む、ビデオデータをエンコードするように構成されているデバイスの 1 つの例を表している。

30

#### 【0098】

[0109]

図 4 は、本開示の技法を利用してよい、例示的なビデオデコーダ 300 を図示するブロック図である。図 4 は、説明の目的のために提供されており、本開示で広く例示し説明しているような技法には限定されない。説明の目的で、本開示は、JEM、VVC および HEVC の技法にしたがうビデオデコーダ 300 を説明している。しかしながら、本開示の技法は、他のビデオコーディング標準規格にしたがって構成されているビデオコーディングデバイスによって実行してもよい。

#### 【0099】

[0110]

図 4 の例では、ビデオデコーダ 300 は、コード化ピクチャーバッファ (CPB) メモリ 320 と、エントロピーデコーディングユニット 302 と、予測処理ユニット 304 と、逆量子化ユニット 306 と、逆変換処理ユニット 308 と、再構築ユニット 310 と、フィルタユニット 312 と、デコードピクチャーバッファ (DPB) 314 とを含んでいる。CPB メモリ 320 と、エントロピーデコーディングユニット 302 と、予測処理ユニット 304 と、逆量子化ユニット 306 と、逆変換処理ユニット 308 と、再構築ユニット 310 と、フィルタユニット 312 と、DPB 314 のいずれかまたはすべてを、1 つ以上のプロセッサ中で、または、処理回路中で実現してもよい。さらに、ビデオデコーダ 300 は、これらまたは他の機能を実行するために、追加または代替のプロセッサまたは処理回路を含んでいてもよい。

40

50

【0100】

[0111]

予測処理ユニット304は、動き補償ユニット316とイントラ予測ユニット318とを含んでいる。予測処理ユニット304は、他の予測モードにしたがって予測を実行するための追加ユニットを含んでいてもよい。例として、予測処理ユニット304は、パレットユニット、（動き補償ユニット316の一部を形成していてもよい）イントラブロックコピーユニット、アフィンユニット、線形モデル（LM）ユニット、または、これらに類するものを含んでいてもよい。他の例では、ビデオデコーダ300は、より多い、より少ない、または、異なる機能的コンポーネントを含んでいてもよい。

【0101】

[0112]

CPBメモリ320は、ビデオデコーダ300のコンポーネントによってデコードされるべき、エンコードされたビデオビットストリームのようなビデオデータを記憶してもよい。CPBメモリ320中に記憶されるビデオデータは、例えば、コンピュータ読み取り可能媒体110（図1）から取得されてもよい。CPBメモリ320は、エンコードされたビデオビットストリームからのエンコードされたビデオデータ（例えば、シンタックス要素）を記憶するCPBを含んでいてもよい。また、CPBメモリ320は、ビデオデコーダ300のさまざまなユニットからの出力を表す一時データのような、コード化されたピクチャーのシンタックス要素以外のビデオデータを記憶してもよい。DPB314は、一般的に、デコードされたピクチャーを記憶し、エンコードされたビデオビットストリームの後続のデータまたはピクチャーをデコードするときに、ビデオデコーダ300が、このデコードされたピクチャーを、参照ビデオデータとして出力および／または使用してもよい。CPBメモリ320およびDPB314は、同期ダイナミックランダムアクセスメモリ（DRAM）（SDRAM）を含むDRAM、磁気抵抗RAM（MRAM）、抵抗RAM（RRAM（登録商標））、または、他のタイプのメモリデバイスのような、さまざまなメモリデバイスのいずれかによって形成されていてもよい。CPBメモリ320およびDPB314は、同じメモリデバイスまたは別個のメモリデバイスによって提供されてもよい。さまざまな例では、CPBメモリ320は、ビデオデコーダ300の他のコンポーネントとともにオンチップであるか、または、これらのコンポーネントに対してオフチップであってもよい。

【0102】

[0113]

追加的にまたは代替的に、いくつかの例では、ビデオデコーダ300は、メモリ120（図1）からコード化されたビデオデータを取り出してもよい。すなわち、メモリ120は、CPBメモリ320を用いて上記で説明したようなデータを記憶していてもよい。同様に、ビデオデコーダ300の機能性のいくつかまたはすべてが、ビデオデコーダ300の処理回路によって実行されるソフトウェアで実現されるとき、メモリ120は、ビデオデコーダ300によって実行されるべき命令を記憶していてもよい。

【0103】

[0114]

図4に示されているさまざまなユニットは、ビデオデコーダ300によって実行される動作の理解を助けるために図示されている。ユニットは、固定機能回路、プログラマブル回路、または、これらの組み合わせとして実現してもよい。図3と同様に、固定機能回路は、特定の機能性を提供する回路を指し、実行できる動作に対して予め設定される。プログラマブル回路は、さまざまなタスクを実行するようにプログラムでき、実行できる動作において柔軟な機能性を提供できる回路を指している。例えば、プログラマブル回路は、ソフトウェアまたはファームウェアの命令によって規定される方法でプログラマブル回路を動作させるソフトウェアまたはファームウェアを実行してもよい。固定機能回路は、（例えば、パラメータを受け取るまたはパラメータを出力するために）ソフトウェア命令を実行するかもしれないが、固定機能回路が実行する動作のタイプは一般的に不变である。

10

20

30

40

50

いくつかの例では、ユニットのうちの1つ以上は、別個の回路ブロック（固定機能またはプログラマブル）であってもよく、いくつかの例では、1つ以上のユニットは集積回路であってもよい。

**【0104】**

[0115]

ビデオデコーダ300は、ALU、EFU、デジタル回路、アナログ回路、および／または、プログラマブル回路から形成されているプログラマブルコアを含んでいてもよい。ビデオデコーダ300の動作がプログラマブル回路上で実行するソフトウェアによって実行される例では、オンチップまたはオフチップメモリが、ビデオデコーダ300が受け取って実行するソフトウェアの命令（例えば、オブジェクトコード）を記憶していくてもよい。

10

**【0105】**

[0116]

エントロピーデコーディングユニット302は、CPBからエンコードされたビデオデータを受け取り、ビデオデータをエントロピーデコードして、シンタックス要素を再生させてもよい。予測処理ユニット304、逆量子化ユニット306、逆変換処理ユニット308、再構築ユニット310、および、フィルタユニット312は、ビットストリームから抽出されたシンタックス要素に基づいて、デコードされたビデオデータを発生させてもよい。

**【0106】**

[0117]

一般的に、ビデオデコーダ300は、ブロック毎のベースでピクチャーを再構築する。ビデオデコーダ300は、各ブロックに対して個別に再構築動作を実行してもよい（現在再構築されている、すなわち、デコードされているブロックは、「現在ブロック」として呼ばれることがある）。

20

**【0107】**

[0118]

エントロピーデコーディングユニット302は、量子化された変換係数ブロックの量子化された変換係数を規定するシンタックス要素とともに、量子化パラメータ（QP）および／または変換モードインジケーションのような変換情報をエントロピーデコードしてもよい。逆量子化ユニット306は、量子化変換係数ブロックに関するQPを使用して、量子化の程度を、そして、同様に逆量子化ユニット306が適用する逆量子化の程度を決定してもよい。逆量子化ユニット306は、例えば、ビット単位の左シフト演算を実行して、量子化変換係数を逆量子化してもよい。それによって、逆量子化ユニット306は、変換係数を含む変換係数ブロックを形成してもよい。

30

**【0108】**

[0119]

逆量子化ユニット306が変換係数ブロックを形成した後、逆変換処理ユニット308は、変換係数ブロックに1つ以上の逆変換を適用して、現在ブロックに関する残差ブロックを発生させてもよい。例えば、逆変換処理ユニット308は、変換係数ブロックに、逆DCT、逆整数変換、逆カルーネンレーベ変換（KLT）、逆回転変換、逆方向変換、または、別の逆変換を適用してもよい。

40

**【0109】**

[0120]

以下により詳細に説明するように、いくつかの例では、逆変換処理ユニット308は、（例えば、複数の変換選択（MTS）技法を使用して）逆低周波数非分離変換（LFNST）と、1つ以上の逆分離変換の両方をビデオデータの変換ブロックに適用するように構成されていてもよい。逆変換処理ユニット308は、1つ以上の逆分離変換を適用する前に、最初に、逆LFNSTを適用してもよい。いくつかの例では、逆変換処理ユニット308は、逆量子化の後に得られる変換ブロックの変換係数のサブセットに逆LFNSTを適用する。逆LFNSTが適用される変換ブロックの変換係数のサブセットは、LFNS

50

T 領域として呼ばれることがある。L F N S T 領域は、変換ブロックの最も低い周波数変換係数を表す変換ブロックの左上部分であってもよい。

#### 【0 1 1 0】

##### [ 0 1 2 1 ]

図3を参照して上記で説明したように、ビデオエンコーダ200の変換処理ユニット206は、L F N S T 領域中の結果として生じる変換係数の一部分に0化プロセスを適用するように構成していてもよい。0化プロセスは、単に、特定の領域中の各変換係数の値が0値を有するようにする。1つの例では、変換処理ユニット206はまた、L F N S T 領域のより高い周波数エリア（例えば、右下隅）中の変換係数を0化してもよい。加えて、いくつかの例では、変換処理ユニット206はまた、L F N S T 領域外にある変換ブロック中の変換係数（例えば、いわゆるM T S 領域中の係数）を0化してもよい。したがって、逆変換処理ユニット308は、L F N S T が適用されているときには、変換ブロックのあるエリア中の変換係数を0化する（または、0化動作が確実に生じる）ように構成されていてもよい。

10

#### 【0 1 1 1】

##### [ 0 1 2 2 ]

図3を参照して上記で説明したように、変換処理ユニット206が、変換ブロックにL F N S T を適用した場合には、ビデオエンコーダ200は、L F N S T インデックスシンタックス要素を発生させてシグナリングしてもよい。複数の値の中からのL F N S T インデックスシンタックス要素の値は、L F N S T を実行するときに使用される、複数の変換の中からの特定の変換を示していてもよい。他の例では、L F N S T インデックスは、L F N S T が適用されなかつたことを示していてもよい（例えば、0のL F N S T インデックス値）。ビデオエンコーダ200は、L F N S T が適用されているときには、L F N S T インデックスを発生させるように構成されていてもよい。L F N S T が適用されていないときには、ビデオエンコーダ200は、L F N S T インデックスをシグナリングするか否かを決定するように構成されていてもよい。同様に、図4を参照すると、ビデオデコーダ300の逆変換処理ユニット308は、いくつかの状況では、エンコードされたビデオビットストリーム中でL F N S T インデックスを受信しないように構成されていてもよい。代わりに、ビデオデコーダ300の逆変換処理ユニット308は、いくつかの事例では、L F N S T インデックスの値を推測してもよい。

20

#### 【0 1 1 2】

##### [ 0 1 2 3 ]

例えば、ビデオエンコーダ200は、最後の有意（例えば、非0）変換係数の位置が、L F N S T が適用されている場合に通常は0化されるであろう変換ブロック中の位置にあるケースでは、L F N S T インデックスをシグナリングしないことを決定してもよい。これは、ビデオエンコーダ200が、最後の有意係数の位置を示す1つ以上のシンタックス要素を発生させ、エンコードされたビデオビットストリーム中でシグナリングするからである。ビデオデコーダ300が、最初に、最後の有意係数の位置を受信してデコードするので、ビデオデコーダ300は、最後の有意係数の位置が変換ブロックの0化領域中にある場合には、L F N S T が実行されていないことを示すL F N S T インデックスを受信する必要がない。むしろ、ビデオデコーダ300の逆変換処理ユニット308は、L F N S T インデックスの値が0であり、L F N S T が適用されていないことを推測（例えば、明示的なシンタックス要素なしで決定）してもよい。

30

#### 【0 1 1 3】

##### [ 0 1 2 4 ]

さらに、予測処理ユニット304は、エントロピーデコーディングユニット302によってエントロピーデコードされた予測情報シンタックス要素にしたがって、予測ブロックを発生させる。例えば、現在ブロックがインター予測されることを予測情報シンタックス要素が示す場合、動き補償ユニット316が予測ブロックを発生させてよい。このケースでは、予測情報シンタックス要素は、参照ブロックを取り出すべきD P B 314中の参

40

50

照ピクチャーとともに、現在ピクチャー中の現在ブロックのロケーションに対する、参照ピクチャー中の参照ブロックのロケーションを識別する動きベクトルを示していくてもよい。動き補償ユニット316は、一般的に、動き補償ユニット224（図3）に関して説明した方法と実質的に類似する方法で、インター予測プロセスを実行してもよい。

#### 【0114】

##### [0125]

別の例として、現在ブロックがイントラ予測されることを予測情報シンタックス要素が示している場合、イントラ予測ユニット318は、予測情報シンタックス要素によって示されているイントラ予測モードにしたがって、予測ブロックを発生させてもよい。再度説明すると、イントラ予測ユニット318は、一般的に、イントラ予測ユニット226（図3）に関して説明した方法と実質的に類似する方法で、イントラ予測プロセスを実行してもよい。イントラ予測ユニット318は、現在ブロックに対する隣接するサンプルのデータをD PB 314から取り出してもよい。

10

#### 【0115】

##### [0126]

再構築ユニット310は、予測ブロックと残差ブロックとを使用して、現在ブロックを再構築してもよい。例えば、再構築ユニット310は、残差ブロックのサンプルを予測ブロックの対応するサンプルに追加して、現在ブロックを再構築してもよい。

20

#### 【0116】

##### [0127]

フィルタユニット312は、再構築されたブロックに対して1つ以上のフィルタ動作を実行してもよい。例えば、フィルタユニット312は、デブロッキング動作を実行して、再構築されたブロックのエッジに沿ったブロッキネスアーティファクトを低減させてもよい。フィルタユニット312の動作は、必ずしもすべての例において実行する必要はない。

30

#### 【0117】

##### [0128]

ビデオデコーダ300は、再構築されたブロックをD PB 314中に記憶させてもよい。例えば、フィルタユニット312の動作が必要とされない例では、再構築ユニット310が、再構築されたブロックをD PB 314に記憶させてもよい。フィルタユニット312の動作が必要とされる例では、フィルタユニット312が、再構築されフィルタされたブロックをD PB 314に記憶させてもよい。上記で説明したように、D PB 314は、イントラ予測に対する現在ピクチャーと、後続の動き補償のための以前にデコードされたピクチャーとのサンプルのような参照情報を、予測処理ユニット304に提供してもよい。さらに、ビデオデコーダ300は、図1のディスプレイデバイス118のようなディスプレイデバイス上での後続の提示のために、D PB 314からデコードされたピクチャー（例えば、デコードされたビデオ）を出力してもよい。

30

#### 【0118】

##### [0129]

このようにして、以下でより詳細に説明するように、ビデオデコーダ300は、ビデオデータを記憶するように構成されているメモリと、回路中で実現され、ビデオデータのブロック中の標準的に規定されている0係数のパターンに基づいて、低周波数非分離変換インデックスまたはフラグの値を推測する（例えば、デコードしない）ようにと、低周波数非分離変換インデックスまたはフラグにしたがって、ビデオデータのブロックを逆変換するように構成されている1つ以上の処理ユニットとを含む、ビデオデコーディングデバイスの例を表している。

40

#### 【0119】

##### [0130]

1つの例では、ビデオデコーダ300は、ビデオデータの変換ブロック中の最後の有意係数の位置を決定するようにと、変換ブロックの0化領域に対する最後の有意係数の位置に基づいて、変換ブロックに対する低周波数非分離変換（L F N S T）インデックスの値

50

を決定し、変換ブロックの0化領域は、変換ブロックのL F N S T領域内の第1の領域と、L F N S T領域外の変換ブロックの第2の領域の両方を含むようにと、L F N S Tインデックスの値にしたがって、変換ブロックを逆変換するように構成されていてもよい。

【0120】

[0131]

#### 変換関連ツールの概要

[0132]

H E V Cより前の例示的なビデオコーディング標準規格では、ビデオエンコーディングおよびビデオデコーディングにおいて、固定された分離変換または固定された分離逆変換のみが使用され、タイプ2離散コサイン変換(D C T - 2)が、垂直方向と水平方向の両方で使用されている。H E V Cでは、D C T - 2に加えて、タイプ7離散サイン変換(D S T - 7)も、固定された分離変換として、 $4 \times 4$ ブロックに対して用いられている。

【0121】

[0133]

以下の同時係続中の米国特許および米国特許出願、2019年5月28日に発行された米国特許第10306229号、2018年1月18日に公開された米国特許公開第2018/0020218号、および、2019年12月5日に公開された米国特許公開第2019/0373261号は、複数の変換選択(M T S)技法を説明している。M T Sは、以前は適応多重変換(A M T)と呼ばれていたことに留意されたい。M T S技法は、一般的に、以前に説明されていたA M T技法と同じである。米国特許公開第2019/0373261号中で説明されているM T Sの例は、ジョイントビデオエキスパートチーム(J V E T)のジョイントエクスペリメンタルモデル7.0(J E M - 7.0)において採用されており、後に、M T Sの簡略化バージョンがV V Cにおいて採用されている(例えば、<http://www.hhi.fraunhofer.de/fields-of-competence/image-processing/research-groups/image-video-coding/hevc-high-efficiency-video-coding/transform-coding-using-the-residual-quadtree-reqt.html>を参照されたい)。

【0122】

[0134]

一般的に、M T Sを使用して、変換係数の変換ブロックをエンコードまたはデコードするときには、ビデオエンコーダ200およびビデオデコーダ300は、使用すべき複数の分離変換のうちの1つ以上の分離変換を決定してもよい。分離変換のより多くの選択を含めることにより、選択される変換が、コード化されているコンテンツにより適合されるかもしれない、コーディング効率が増加するかもしれない。

【0123】

[0135]

図5は、エンコーダ側およびデコーダ側(例えば、ビデオエンコーダ200およびビデオデコーダ300)における例示的な低周波数非分離変換(L F N S T)の図であり、L F N S Tの使用は、コーデックにおける分離変換と量子化との間に新しいステージを導入する。図5中に示されているように、エンコーダ側(例えば、ビデオエンコーダ200)において、変換処理ユニット206は、最初に、変換ブロックに分離変換500を適用して、変換係数を得てもよい。変換処理ユニット206は、その後、変換ブロックの変換係数の一部分(例えば、L F N S T領域)にL F N S T502を適用してもよい。上記で説明したように、変換処理ユニット206は、L F N S Tに関連して0化プロセスを適用してもよい。量子化ユニット208は、その後、エントロピーエンコーディングの前に、結果的に得られた変換係数を量子化してもよい。

【0124】

[0136]

デコーダ側(例えば、ビデオデコーダ300)において、逆量子化ユニット306が、

10

20

30

40

50

最初に、変換ブロック中のエントロピードコードされた変換係数を逆量子化する（図4参照）。その後、ビデオデコーダ300の逆変換処理ユニット308が、変換ブロックのL<sub>FNST</sub>領域に逆L<sub>FNST</sub>504を適用する。その後、逆変換処理ユニット308が、逆L<sub>FNST</sub>の結果に逆分離変換506を適用して、残差ブロックを生成させる。

#### 【0125】

[0137]

（例えば、図5中に図示されているような）例示的なL<sub>FNST</sub>は、MTSのコーディング効率をさらに改善するためにJEM-7.0において使用され、L<sub>FNST</sub>のインプリメンテーションは、2017年2月14日に出願された米国特許第10448053号中で説明されている例示的なハイパーキューブギブン変換（HyGT）に基づいている。10

2016年9月20日に出願された米国特許第10491922号、2017年3月30日に公開された米国特許公開第2017/0094314号、2017年2月14日に出願された米国特許第10349085号、2019年3月25日に出願された米国特許出願第16/354007号は、他の例示的な設計およびさらなる詳細を説明している。近年、L<sub>FNST</sub>は、VVC標準規格で採用されている（JVET-N0193、低減された2次変換（RST）（CE6-3.1）、オンラインで入手可能：[http://phoenix.it-sudparis.eu/jvet/doc\\_end\\_user/documents/14\\_Geneva/wg11/JVET-N0193-v5.zip](http://phoenix.it-sudparis.eu/jvet/doc_end_user/documents/14_Geneva/wg11/JVET-N0193-v5.zip)を参照）。L<sub>FNST</sub>は、以前は非分離2次変換（NST）または2次変換と呼ばれていた。20

#### 【0126】

[0138]

現在VVCにおける0化プロセス

[0139]

VVCドラフト5におけるL<sub>FNST</sub>設計では、エンコーダ（例えば、ビデオエンコーダ200）は、K個の最低周波数変換係数をそのまま維持する0化動作を実行するように構成されていてもよい（例えば、K個の最低周波数変換係数の値は0化されない）。K個の最低周波数変換係数は、サイズN（例えば、8×8 L<sub>FNST</sub>領域に対してN=64）のL<sub>FNST</sub>により変換される。デコーダ（例えば、ビデオデコーダ300）は、（K個のL<sub>FNST</sub>係数としても呼ばれる）それらのK個の係数のみを使用することにより、分離係数（例えば、MTS係数）を再構築する。VVCドラフト5では、このような0化プロセスは、標準的に、サイズ4×4および8×8のL<sub>FNST</sub>に対してのみ行われ、デコーダは、残りのN-K個のより高い周波数変換係数の値が0の値を有するように設定され、K個のL<sub>FNST</sub>係数が再構築のために使用されることを暗黙的に推測する（シグナリングを受信することなく、仮定または決定する）。30

#### 【0127】

[0140]

図6は、0化されたサイズH×Wの変換ブロック602に、サイズNのL<sub>FNST</sub>を適用した後に得られた変換係数の代表的な図であり、N個の変換係数のうちのZ個の変換係数が0化され、K個の係数が維持されている。図6中に示されるように、ビデオエンコーダ200は、（例えば、MTS技法を使用して）変換ブロック602に分離変換を適用して、MTS係数を得る。ビデオエンコーダ200は、その後、変換ブロック602の（h×wのサイズを有する）L<sub>FNST</sub>領域600にL<sub>FNST</sub>を適用する。L<sub>FNST</sub>領域600の暗い領域601は、維持されているK個の係数（例えば、L<sub>FNST</sub>係数）である。L<sub>FNST</sub>領域600の白い領域は、0化されているZ(N-K)個の係数（0化された係数）である。40

#### 【0128】

[0141]

2016年9月20日に出願された米国特許第10491922号、2017年3月30日に公開された米国特許公開第2017/0094314号、および、2019年1月

10

20

30

40

50

31日に出願された米国仮出願第62/799410号で説明されているように、LFNSTは、最初に、LFNST領域（例えば、図6中のLFNST領域600）である2-Dサブブロックを、予め規定されている走査／順序付けを介して、変換係数の1-Dリスト（または、ベクトル）に変換し、その後、変換係数のサブセット（例えば、0化されていない変換係数）に変換を適用することにより実行されてもよい。

#### 【0129】

[0142]

図7は、何らかの0化なしで得られた分離変換係数(MTS)およびLFNST係数の例を示している。図7中に示されているように、ビデオエンコーダ200は、（例えば、MTS技法を使用して）(H×Wのサイズを有する)変換ブロック702に分離変換を適用して、MTS係数を得る。ビデオエンコーダ200は、その後、変換ブロック702の（例えば、h×wのサイズを有する）LFNST領域700にLFNSTを適用する。図7の例では、LFNST領域700のすべてのN個の係数（例えば、LFNST係数）は、維持されている。すなわち、図7の例では、0化は実行されていない。

10

#### 【0130】

[0143]

本開示は、以前のLFNST技法に関連するシグナリングオーバーヘッドおよび複雑性の問題を取り扱うかもしれないさまざまな技法を説明している。本開示の技法は、(i) LFNSTインデックス/フラグのシグナリングオーバーヘッドを低減し、(ii) 分離変換係数に対して0化を拡張することによりLFNSTプロセスを簡略化するかもしれない。分離変換係数に対する0化領域を拡張することは、VVC様コーデック（例えば、ビデオデコーダ300）が、既存の係数コーディング関連シンタックス（例えば、有意（例えば、非0）係数の最後の位置を決定するために使用されるシンタックス）に基づいて、LFNSTインデックス/フラグを推測することを可能にする。

20

#### 【0131】

[0144]

本開示で説明されているシグナリング方法は、LFNSTを参照して説明されているが、本開示の技法はLFNSTに限定されず、他の変換関連シンタックスのシグナリングを低減させるために適用することができる。

30

#### 【0132】

[0145]

### LFNSTシグナリング技法

[0146]

ビデオエンコーダ200およびビデオデコーダ300は、以下のLFNSTシグナリング技法を個々にまたは何らかの組み合わせで使用するように構成されていてもよい。本開示のコンテキストでは、シグナリングは、ビデオエンコーダ200が、1つ以上のシンタックス構造（例えば、ヘッダまたはパラメータセット）中の1つ以上のシンタックス要素および/またはフラグをエンコードすることを指しているかもしれない。相互的に、ビデオデコーダ300は、このようなシンタックス要素および/またはフラグを受信してデコードしてもよい。いくつかの例では、ビデオデコーダ300は、ビットストリーム中でこれらを明示的に受信することなく、いくつかのシンタックス要素および/またはフラグの値を推測するように構成されていてもよい。

40

#### 【0133】

[0147]

いくつかの例では、ビデオエンコーダ200およびビデオデコーダ300は、標準的0化有りで、LFNSTを適用するように構成されている。このコンテキストでは、標準的0化は、変換ブロックのどの領域（例えば、LFNST領域の内側と外側の両方）が0化されるかを規定している。標準的0化は、予め規定されているセットの条件（例えば、ブロックサイズ、ブロック形状、および/または、分離変換を示すMTSインデックス/フラグのような変換関連シンタックス）に基づいて、ビデオエンコーダ200とビデオデコ

50

ーダ 300 の両方において適用される。ビデオエンコーダ 200 およびビデオデコーダ 300 が、標準的 0 化有りで、LFNST を適用するように構成されているときには、ビデオデコーダ 300 は、標準的に規定されている 0 系数のパターンに基づいて、LFNST インデックス / フラグを直接的に推測するように構成されていてもよい。このようなことから、ビデオエンコーダ 200 は、LFNST インデックス / フラグをシグナリングする必要がない。

#### 【0134】

##### [0148]

例えば、0 化領域のパターン / 形状（例えば、図 6 中の LFNST 領域 600 の白色領域を参照）は、予め規定されているセットのルール（例えば、ブロックサイズ、ブロック形状、および / または、MTS インデックス / フラグのような変換関連シンタックス）に依存して、変化してもよい。ビデオデコーダ 300 は、観測されたパターンに基づいて、LFNST インデックス / フラグの値を推測するように構成されていてもよく、LFNST インデックス / フラグは、ビデオエンコーダ 200 により明示的にシグナリングされないかもしれない。いくつかの例では、LFNST フラグは、LFNST が適用されているか否か（例えば、LFNST フラグ = 1）、または、LFNST が適用されていないか否か（LFNST フラグ = 0）を示していてもよい。他の例では、LFNST インデックスは、LFNST が適用されていないこと（LFNST インデックス = 0）を示していてもよく、または、LFNST が適用されているときには、適用されることになる特定のタイプの LFNST を示していてもよい（LFNST インデックス > 0）。

10

#### 【0135】

##### [0149]

1 つの例では、LFNST が使用されるときに 0 化されることが想定される位置の中に非 0 系数があることをビデオデコーダ 300 が決定する場合には、ビデオデコーダ 300 は、LFNST が適用されていないことを推測（例えば、LFNST インデックスの値が 0 であることを推測）してもよい。このケースでは、ビデオデコーダ 300 は、LFNST インデックス / フラグの値を 0 として推測してもよく、0 は LFNST を適用していないことに対応している。例えば、最後の非 0 系数の位置が変換ブロックの 0 化領域中にある場合には、ビデオデコーダ 300 は、LFNST インデックスの値が 0 であることを決定してもよい。以下で説明するように、0 化領域は、変換ブロックの LFNST 領域内の 0 化領域および / または変換ブロックの LFNST 領域外の 0 化領域であってもよい。

20

#### 【0136】

##### [0150]

ビデオエンコーダ 200 が、最後の有意係数の位置を示す 1 つ以上のシンタックス要素を発生させて、エンコードされたビデオビットストリーム中でシグナリングするかもしれないことから、ビデオデコーダ 300 は、最後の有意係数の位置を決定するように構成されていてもよい。ビデオデコーダ 300 は、最初に（例えば、LFNST を適用するか否かを決定する前に）、最後の有意係数の位置を受信してデコードするので、ビデオデコーダ 300 は、最後の有意係数の位置が、変換ブロックの 0 化領域中にある場合には、LFNST が実行されていないことを示す LFNST インデックスを受信する必要がない。むしろ、ビデオデコーダ 300 は、LFNST インデックスの値が 0 であり、LFNST が適用されていないことを推測（例えば、明示的なシンタックス要素なしで決定）してもよい。

30

#### 【0137】

##### [0151]

VVC ドラフト 5 では、（例えば、図 6 中に図示されているように）変換ブロックの  $4 \times 4$  および  $8 \times 8$  の LFNST 領域に対して標準的 0 化が使用され、LFNST 領域内の係数のサブセットが標準的に 0 化される。2019年1月31日に出願された同時係属中の米国仮出願第 62/799410 号で説明されているように、LFNST 領域外の分離変換係数（例えば、LFNST 領域外の MTS 係数）もまた、（例えば、図 8 中に図示さ

40

50

れているように ) 0 化されてもよい。図 8 は、サイズ N の L F N S T を適用し、( サイズ H × W を有する ) 変換ブロック 8 0 2 の ( サイズ h × w を有する ) L F N S T 領域 8 0 0 中の Z 個の係数 ( 例えば、最も高い周波数係数 ) を 0 化し、L F N S T 領域 8 0 0 の外側の M T S 係数も 0 化することにより得られる L F N S T 係数の図である。L F N S T 領域 8 0 0 の暗い領域 8 0 1 は、維持されている K 個の係数 ( 例えば、L F N S T 係数 ) である。

#### 【 0 1 3 8 】

[ 0 1 5 2 ]

このケースでは、ビデオエンコーダ 2 0 0 およびビデオデコーダ 3 0 0 はまた、以下のように、0 化パターンを活用して、L F N S T インデックス / フラグを推測するようにおよび / またはシグナリングしないようにすることができる。1 つの例では、ビデオデコーダ 3 0 0 は、0 化領域中に少なくとも 1 つの非 0 係数がある場合には、L F N S T が適用されていないことを推測し、例えば、0 として、対応する L F N S T インデックス / フラグ値を導出してもよい。図 8 では、0 化領域は、変換ブロック 8 0 2 の L F N S T 領域 8 0 0 の内側と、変換ブロック 8 0 2 の L F N S T 領域 8 0 0 の外側の両方であってもよい。

10

#### 【 0 1 3 9 】

[ 0 1 5 3 ]

別の例では、ビデオデコーダ 3 0 0 は、既存のサイド情報を使用して、L F N S T インデックス / フラグの値を推測してもよい。例えば、ビデオデコーダ 3 0 0 は、既存の最後の有意係数位置の情報 ( 例えば、最後の有意係数の位置を示すシンタックス要素 ) を使用して、L F N S T インデックス / フラグの値を推測してもよい。V V C では、ビデオエンコーダ 2 0 0 は、それぞれ、X および Y ( 水平および垂直 ) 方向における最後の有意係数の位置を示す 2 つのシンタックス要素をシグナリングするように構成されていてもよい。最後の有意係数の位置を示すシンタックス要素は、0 化領域中に非 0 ( 有意 ) 係数があるか否かを示してもよい。

20

#### 【 0 1 4 0 】

[ 0 1 5 4 ]

特定の例として、最後の有意係数の位置のシグナリング ( すなわち、変換ブロック中の ( X , Y ) 座標 ) が、0 化領域中のロケーション ( 例えば、図 8 中のように L F N S T 領域の内側または外側のいずれか ) を指す場合には、ビデオデコーダ 3 0 0 は、例えば、0 として L F N S T インデックス / フラグの値を推測してもよく、L F N S T は適用されない。いくつかの例では、最後の有意係数の位置は、2 - D 座標 ( X , Y ) の代わりに、1 次元で規定されていてもよい ( 例えば、L F N S T 係数の 1 - D リストに対するインデックスを使用して規定することができる ) 。

30

#### 【 0 1 4 1 】

[ 0 1 5 5 ]

したがって、上記の例に鑑みて、ビデオデコーダ 3 0 0 は、ビデオデータの変換ブロック中の最後の有意係数の位置を決定するように構成されていてもよい。例えば、ビデオデコーダ 3 0 0 は、変換ブロック中の最後の有意係数の X 位置および Y 位置を示す 1 つ以上のシンタックス要素をデコードするように構成されていてもよい。ビデオデコーダ 3 0 0 は、その後、変換ブロックの 0 化領域に対する最後の有意係数の位置に基づいて、変換ブロックに対する低周波数非分離変換 ( L F N S T ) インデックスの値を決定してもよい。

40

#### 【 0 1 4 2 】

[ 0 1 5 6 ]

図 8 の例によれば、変換ブロックの 0 化領域は、変換ブロック 8 0 2 の L F N S T 領域 8 0 0 内の第 1 の領域 ( 例えば、L F N S T 領域 8 0 0 の白色エリア ) と、L F N S T 領域 ( 8 0 0 ) 外の変換ブロック 8 0 2 の第 2 の領域との両方を含んでいる。L F N S T インデックスの値は、L F N S T が変換ブロックに適用されているか否かと、適用されている場合には、適用されている L F N S T のタイプとを示している。

#### 【 0 1 4 3 】

50

## [ 0 1 5 7 ]

具体的な例では、ビデオデコーダ 300 は、変換ブロック中の最後の有意係数の位置が、変換ブロックの 0 化領域中にあるケースでは、LFNST インデックスの値が 0 であると推測してもよく、0 の LFNST インデックスの値は、LFNST が変換ブロックに適用されていないことを示している。すなわち、ビデオデコーダ 300 は、LFNST インデックスの値を示すシンタックス要素を受信することなく、LFNST インデックスの値が 0 であると推測するように構成されていてもよい。

## 【 0 1 4 4 】

## [ 0 1 5 8 ]

別の例では、LFNST インデックスの値を決定するために、ビデオデコーダ 300 は、変換ブロック中の最後の有意係数の位置が、変換ブロックの 0 化領域中にはないケースでは、LFNST インデックスを示すシンタックス要素を受信するようにと、シンタックス要素をデコードして、LFNST インデックスの値を決定するように構成されていてよい。

10

## 【 0 1 4 5 】

## [ 0 1 5 9 ]

ビデオデコーダ 300 は、その後、LFNST インデックスの値にしたがって、変換ブロックを逆変換してもよい。1つの例では、変換ブロックを逆変換するために、ビデオデコーダ 300 は、LFNST インデックスにより示される LFNST により変換ブロックの LFNST 領域を逆変換し、LFNST により変換ブロックの LFNST 領域を逆変換した後に、1つ以上の分離変換で変換ブロックを逆変換してもよい。別の例では、ビデオデコーダ 300 は、LFNST を適用しないかもしれません、その代わりに、1つ以上の分離変換のみにより変換ブロックを逆変換してもよい。LFNST が使用されるか否かにかかわらず、ビデオデコーダ 300 は、変換ブロックを逆変換して、残差ブロックを作成し、( 例えは、インター予測またはイントラ予測のような予測技法を使用して ) 残差ブロックに対する予測的ブロックを決定し、予測的ブロックを残差ブロックと組み合わせて、デコードされたブロックを作成してもよい。

20

## 【 0 1 4 6 】

## [ 0 1 6 0 ]

LFNST 係数に対して 0 化が使用されないケースに対して、ビデオエンコーダ 200 およびビデオデコーダ 300 は、図 9 中に示されるように、LFNST 領域外にある分離変換係数( 例えは、LFNST 領域外の MTS 係数 ) に 0 化を依然として適用してもよい。図 9 は、サイズ N の LFNST を適用し、( H × W のサイズを有する ) 変換ブロック 902 の( h × w のサイズを有する ) LFNST 領域 900 外の MTS 係数のみを 0 化することによる、LFNST 係数の図である。その後、ビデオエンコーダ 200 およびビデオデコーダ 300 は、上記で説明した方法の 1 つまたは組み合わせを使用することにより、非 0 ( 有意 ) 係数の位置に依存して、LFNST インデックス / フラグの値を推測してもよい。

30

## 【 0 1 4 7 】

## [ 0 1 6 1 ]

図 10 は、現在ブロックをエンコードするための方法の例を図示するフローチャートである。現在ブロックは、現在 CU を含んでいてもよい。ビデオエンコーダ 200 ( 図 1 および図 3 ) に関して説明したが、図 10 の方法と類似する方法を実行するように他のデバイスが構成されていてもよいことを理解されたい。

40

## 【 0 1 4 8 】

## [ 0 1 6 2 ]

この例では、ビデオエンコーダ 200 は、最初に現在ブロックを予測する( 350 )。例えは、ビデオエンコーダ 200 は、現在ブロックに対する予測ブロックを形成してもよい。ビデオエンコーダ 200 は、その後、現在ブロックに対する残差ブロックを計算してもよい。( 352 )。残差ブロックを計算するために、ビデオエンコーダ 200 は、現在

50

ブロックに対する元のエンコードされていないブロックと予測ブロックとの間の差分を計算してもよい。ビデオエンコーダ 200 は、その後、残差ブロックの係数を変換および量子化してもよい(354)。次に、ビデオエンコーダ 200 は、残差ブロックの量子化された変換係数を走査してもよい(356)。走査の間、または、走査に続いて、ビデオエンコーダ 200 は、係数をエントロピーエンコードしてもよい(358)。例えば、ビデオエンコーダ 200 は、CAVLC または CABAC を使用して、係数をエンコードしてもよい。ビデオエンコーダ 200 は、その後、ブロックのエントロピーコード化されたデータを出力してもよい(360)。

## 【0149】

[0163]

10

図 11 は、ビデオデータの現在ブロックをデコードするための例示的な方法を図示するフロー チャートである。現在ブロックは、現在 CU を含んでいてもよい。ビデオデコーダ 300(図 1 および図 4) に関して説明したが、図 11 の方法と類似する方法を実行するように他のデバイスが構成されていてもよいことを理解されたい。

## 【0150】

[0164]

ビデオデコーダ 300 は、現在ブロックに対応する残差ブロックの係数に対する、エントロピーコード化予測情報およびエントロピーコード化データのような、現在ブロックに対するエントロピーコード化データを受け取ってもよい(370)。ビデオデコーダ 300 は、エントロピーコード化データをエントロピーデコードして、現在ブロックに対する予測情報を決定し、残差ブロックの係数を再生させてもよい(372)。ビデオデコーダ 300 は、例えば、現在ブロックに対する予測情報をにより示されているイントラ予測モードまたはインター予測モードを使用して現在ブロックを予測して、現在ブロックに対する予測ブロックを計算してもよい(374)。ビデオデコーダ 300 は、その後、再生された係数を逆走査して、量子化された変換係数のブロックを生成させてもよい(376)。ビデオデコーダ 300 は、その後、係数を逆量子化および逆変換して、残差ブロックを生成させてもよい(378)。ビデオデコーダ 300 は、最終的に、予測ブロックと残差ブロックとを組み合わせることにより、現在ブロックをデコードしてもよい(380)。

20

## 【0151】

[0165]

30

図 12 は、本開示の例示的なデコーディング方法を図示するフロー チャートである。図 12 の技法は、図 11 のプロセス 378 をさらに規定している。図 12 の技法は、逆変換処理ユニット 308 を含む、ビデオデコーダ 300 の 1 つ以上の構造ユニットにより実行してもよい。

## 【0152】

[0166]

40

本開示の 1 つの例では、ビデオデコーダ 300 は、ビデオデータの変換ブロック中の最後の有意係数の位置を決定するように構成されていてもよい(1200)。例えば、ビデオデコーダ 300 は、変換ブロック中の最後の有意係数の X 位置および Y 位置を示す 1 つ以上のシンタクス要素をデコードするように構成されていてもよい。ビデオデコーダ 300 は、その後、変換ブロックの 0 化領域に対する最後の有意係数の位置に基づいて、変換ブロックに対する低周波数非分離変換(LFNST) インデックスの値を決定してもよい(1202)。

## 【0153】

[0167]

図 8 の例によれば、変換ブロックの 0 化領域は、変換ブロック 802 の LFNST 領域 800 内の第 1 の領域(例えば、LFNST 領域 800 の白色エリア)と、LFNST 領域 800 外の変換ブロック 802 の第 2 の領域との両方を含んでいる。LFNST インデックスの値は、LFNST が変換ブロックに適用されているか否かと、適用されている場合には、適用されている LFNST のタイプとを示している。

50

## 【0154】

[0168]

具体的な例では、ビデオデコーダ300は、変換ブロック中の最後の有意係数の位置が、変換ブロックの0化領域中にあるケースでは、LFNSTインデックスの値が0であると推測してもよく、0のLFNSTインデックスの値は、LFNSTが変換ブロックに適用されていないことを示している。すなわち、ビデオデコーダ300は、LFNSTインデックスの値を示すシンタックス要素を受信することなく、LFNSTインデックスの値が0であると推測するように構成されていてもよい。

## 【0155】

[0169]

別の例では、LFNSTインデックスの値を決定するために、ビデオデコーダ300は、変換ブロック中の最後の有意係数の位置が、変換ブロックの0化領域中にはないケースでは、LFNSTインデックスを示すシンタックス要素を受信するようにと、シンタックス要素をデコードして、LFNSTインデックスの値を決定するように構成されていてよい。

10

## 【0156】

[0170]

ビデオデコーダ300は、その後、LFNSTインデックスの値にしたがって、変換ブロックを逆変換してもよい(1204)。1つの例では、変換ブロックを逆変換するために、ビデオデコーダ300は、LFNSTインデックスにより示される複数のLFNSTのうちの1つにより変換ブロックのLFNST領域を逆変換し、LFNSTにより変換ブロックのLFNST領域を逆変換した後に、1つ以上の分離変換により変換ブロックを逆変換してもよい。別の例では、ビデオデコーダ300は、LFNSTを適用しないかもしれません、その代わりに、1つ以上の分離変換のみにより変換ブロックを逆変換してもよい。LFNSTが使用されるか否かにかかわらず、ビデオデコーダ300は、変換ブロックを逆変換して、残差ブロックを作成し、(例えば、インター予測またはイントラ予測のような予測技法を使用して)残差ブロックに対する予測的ブロックを決定し、予測的ブロックを残差ブロックと組み合わせて、デコードされたブロックを作成してもよい。

20

## 【0157】

[0171]

本開示の他の例示的な例を以下で説明する。

30

## 【0158】

[0172]

例1 - ビデオデータをコード化する方法において、方法は、ビデオデータのブロック中の標準的に規定されている0係数のパターンに基づいて、低周波数非分離変換インデックスまたはフラグの値を推測することと、低周波数非分離変換インデックスまたはフラグにしたがって、ビデオデータのブロックを変換することを含む方法。

## 【0159】

[0173]

例2 - ビデオデータのブロック中の標準的に規定されている0係数のパターンは、ビデオデータのブロックの0化領域のパターンである例1記載の方法。

40

## 【0160】

[0174]

例3 - 低周波数非分離変換インデックスまたはフラグの値を推測することは、非0係数がビデオデータのブロックの0化領域中にあるケースでは、低周波数非分離変換インデックスまたはフラグの値が0であると推測することを含む例2記載の方法。

## 【0161】

[0175]

例4 - 低周波数非分離変換インデックスまたはフラグの値を推測することは、非0係数がビデオデータのブロックの0化領域中にあることを最後の有意係数位置の情報が示すケ

50

ースでは、低周波数非分離変換インデックスまたはフラグの値が 0 であると推測することを含む例 2 記載の方法。

【0162】

[0176]

例 5 - コーディングは、デコーディングを含む例 1 ~ 4 のいずれか 1 例記載の方法。

【0163】

[0177]

例 6 - コーディングは、エンコーディングを含む例 1 ~ 4 のいずれか 1 例記載の方法。

【0164】

[0178]

例 7 - ビデオデータをコード化するためのデバイスにおいて、デバイスが、例 1 ~ 6 のいずれか 1 例の方法を実行する 1 つ以上の手段を具備するデバイス。

【0165】

[0179]

例 8 : 1 つ以上の手段が、回路中で実現されている 1 つ以上のプロセッサを備える例 7 記載のデバイス。

【0166】

[0180]

例 9 : ビデオデータを記憶するメモリをさらに具備する例 7 または 8 のいずれか 1 例記載のデバイス。

【0167】

[0181]

例 10 : デコードされたビデオデータを表示するように構成されているディスプレイをさらに具備する例 7 ~ 9 のいずれか 1 例記載のデバイス。

【0168】

[0182]

例 11 : デバイスが、カメラ、コンピュータ、移動体デバイス、ブロードキャスト受信機デバイス、または、セットトップボックスのうちの 1 つ以上を具備する例 7 ~ 10 のいずれか 1 例記載のデバイス。

【0169】

[0183]

例 12 : デバイスが、ビデオデコーダを具備する例 7 ~ 11 のいずれか 1 例記載のデバイス。

【0170】

[0184]

例 13 : デバイスが、ビデオエンコーダを具備する例 7 ~ 12 のいずれか 1 例記載のデバイス。

【0171】

[0185]

例 14 - 実行されるときに、1 つ以上のプロセッサに例 1 ~ 6 のいずれか 1 例記載の方法を実行させる命令を記憶しているコンピュータ読取可能記憶媒体。

【0172】

[0186]

例に依存して、ここで説明した技法のうちのいずれかのある動作またはイベントは、異なるシーケンスで実行でき、追加してもよく、マージしてもよく、または、完全に省略してもよい（例えば、説明した動作またはイベントのすべてが本技法の実施のために必要であるとは限らない）ことを認識されたい。さらに、ある例では、動作またはイベントは、シーケンシャルよりもむしろ、例えば、マルチスレッド処理、割り込み処理、または、複数のプロセッサを通して、同時に実行してもよい。

【0173】

10

20

30

40

50

## [ 0 1 8 7 ]

1つ以上の例において、説明した機能は、ハードウェア、ソフトウェア、ファームウェア、または、これらの任意の組み合わせで実現してもよい。ソフトウェアで実現される場合には、機能は、1つ以上の命令またはコードとしてコンピュータ読取可能媒体上に記憶されてもよく、あるいは、1つ以上の命令またはコードとしてコンピュータ読取可能媒体上で送信されてもよく、ハードウェアベースの処理ユニットによって実行してもよい。コンピュータ読取可能媒体はまた、例えば、通信プロトコルにしたがって、コンピュータプログラムの1つの場所から別の場所への転送を容易にする何らかの媒体を含む通信媒体、または、データ記憶媒体のような有形の媒体に対応するコンピュータ読取可能記憶媒体を含んでいてもよい。このように、コンピュータ読取可能媒体は、一般的に、(1) 有形コンピュータ読取可能記憶媒体、または、(2) 信号または搬送波のような通信媒体に對応していてもよい。データ記憶媒体は、本開示で説明した技法を実現するための命令、コードおよび／またはデータ構造を取り出すために、1つ以上のコンピュータまたは1つ以上のプロセッサによってアクセスすることができる任意の利用可能な媒体であってもよい。コンピュータプログラム製品は、コンピュータ読取可能媒体を含んでいてもよい。

## 【 0 1 7 4 】

## [ 0 1 8 8 ]

限定ではなく例として、このようなコンピュータ読取可能記憶媒体は、RAM、ROM、EEPROM（登録商標）、CD-ROMまたは他の光学ディスク記憶媒体、磁気ディスク記憶媒体または他の磁気記憶デバイス、フラッシュメモリ、あるいは、命令またはデータ構造の形態で望ましいプログラムコードを記憶するために使用され、コンピュータによってアクセスすることができる他の何らかの媒体のうちの1つ以上を備えることができる。また、任意の接続は、コンピュータ読取可能媒体と適切に呼ばれる。例えば、命令が、ウェブサイトから、サーバから、あるいは、同軸ケーブル、光ファイバケーブル、撲り対、デジタル加入者線（DSL）、または、赤外線、無線、マイクロ波のようなワイヤレステクノロジーを使用している他の遠隔ソースから送信される場合、同軸ケーブル、光ファイバケーブル、撲り対、DSL、または、赤外線、無線およびマイクロ波のようなワイヤレステクノロジーは、媒体の定義に含まれる。しかしながら、コンピュータ読取可能記憶媒体およびデータ記憶媒体は、接続、搬送波、信号、または、他の一時的な媒体を含まないが、代わりに、非一時的な、有形の記憶媒体に向けられていることを理解すべきである。ここで使用するようなディスク（disk および disc）は、コンパクトディスク（CD）、レーザーディスク（登録商標）、光ディスク、デジタル汎用ディスク（DVD）、フロッピー（登録商標）ディスク、および、ブルーレイ（登録商標）ディスクを含むが、通常、ディスク（disk）はデータを磁気的に再生する一方で、ディスク（disc）はデータをレーザにより光学的に再生する。上記の組み合わせも、コンピュータ読取可能媒体の範囲内に含むべきである。

## 【 0 1 7 5 】

## [ 0 1 8 9 ]

命令は、1つ以上のデジタル信号プロセッサ（DSP）、汎用マイクロプロセッサ、特定用途集積回路（ASIC）、フィールドプログラマブルゲートアレイ（FPGA）、または、他の同等な集積またはディスクリート論理回路のような1つ以上のプロセッサによって実行してもよい。したがって、ここで使用されるように、用語「プロセッサ」および「処理回路」は、前述の構造、または、ここで説明した技術のインプリメンテーションに適した他の何らかの構造のいずれかを指してもよい。加えて、いくつかの態様では、ここで説明した機能性は、エンコードおよびデコードするように構成されている専用のハードウェアおよび／またはソフトウェアモジュール内に提供してもよく、あるいは、組み合わされたコーデック中に組み込んでよい。また、技法は、1つ以上の回路または論理エレメントにおいて、完全に実現することができる。

## 【 0 1 7 6 】

## [ 0 1 9 0 ]

10

20

30

40

50

本開示の技法は、ワイヤレスハンドセット、集積回路（I C）またはI Cのセット（例えば、チップセット）を含む、幅広い種類のデバイスまたは装置において実施してもよい。さまざまなコンポーネント、モジュール、または、ユニットは、開示した技法を実行するように構成されているデバイスの機能的な態様を強調するためにここ説明しているが、それらは、異なるハードウェアユニットによる実現を必ずしも要求するわけではない。むしろ、上記で説明したように、さまざまなユニットは、コーデックハードウェアユニットにおいて組み合わされるか、または、適切なソフトウェアおよび／またはファームウェアとともに、上記で説明したような1つ以上のプロセッサを含む、相互動作可能ハードウェアユニットの集合によって提供されてもよい。

【0177】

10

[0191]

さまざまな例を説明してきた。これらおよび他の例は、以下の特許請求の範囲の範囲中にある。

以下に、本願の出願当初の特許請求の範囲に記載された発明を付記する。

[C1]

ビデオデータをデコードする方法において、

前記ビデオデータの変換ブロック中の最後の有意係数の位置を決定することと、

前記変換ブロックの0化領域に対する前記最後の有意係数の位置に基づいて、前記変換ブロックに対する低周波数非分離変換（L F N S T）インデックスの値を決定し、前記変換ブロックの0化領域は、前記変換ブロックのL F N S T領域内の第1の領域と、前記L F N S T領域外の前記変換ブロックの第2の領域との両方を含むことと、

前記L F N S Tインデックスの値にしたがって、前記変換ブロックを逆変換することとを含む方法。

[C2]

前記L F N S Tインデックスの値は、L F N S Tが前記変換ブロックに適用されているか否かを示し、適用されている場合には、適用されているL F N S Tのタイプを示すC1記載の方法。

[C3]

前記L F N S Tインデックスの値を決定することは、

前記変換ブロック中の前記最後の有意係数の位置が、前記変換ブロックの0化領域中にあるケースでは、前記L F N S Tインデックスの値が0であると推測し、0の前記L F N S Tインデックスの値は、前記L F N S Tが前記変換ブロックに適用されていないことを示すことを含むC1記載の方法。

[C4]

前記L F N S Tインデックスの値が0であると推測することは、

前記L F N S Tインデックスの値を示すシンタックス要素を受信することなく、前記L F N S Tインデックスの値が0であると推測することを含むC3記載の方法。

[C5]

前記変換ブロックを逆変換することは、

1つ以上の分離変換により、前記変換ブロックを逆変換することを含むC3記載の方法。

[C6]

前記L F N S Tインデックスの値を決定することは、

前記変換ブロック中の前記最後の有意係数の位置が、前記変換ブロックの0化領域中にならないケースでは、前記L F N S Tインデックスを示すシンタックス要素を受信することと、前記シンタックス要素をデコードして、前記L F N S Tインデックスの値を決定することとを含むC1記載の方法。

[C7]

前記変換ブロックを逆変換することは、

前記L F N S Tインデックスにより示されるL F N S Tにより、前記変換ブロックの前記L F N S T領域を逆変換することと、

20

30

40

50

前記 L F N S T により、前記変換ブロックの前記 L F N S T 領域を逆変換した後に、1つ以上の分離変換により、前記変換ブロックを逆変換することとを含む C 6 記載の方法。

[ C 8 ]

前記ビデオデータの変換ブロック中の前記最後の有意係数の位置を決定することは、前記変換ブロック中の前記最後の有意係数の X 位置および Y 位置を示す 1 つ以上のシンタックス要素をデコードすることを含む C 1 記載の方法。

[ C 9 ]

前記変換ブロックを逆変換することは、前記変換ブロックを逆変換して、残差ブロックを作成することとを含み、

前記方法は、

10

前記残差ブロックに対する予測的ブロックを決定することと、

前記予測的ブロックを前記残差ブロックと組み合わせて、デコードされたブロックを作成することとをさらに含む C 1 記載の方法。

[ C 10 ]

前記デコードされたブロックを含むピクチャーを表示することをさらに含む C 9 記載の方法。

[ C 11 ]

ビデオデータをデコードするように構成されている装置において、

前記ビデオデータの変換ブロックを記憶するように構成されているメモリと、

20

前記メモリと通信する 1 つ以上のプロセッサとを具備し、

前記 1 つ以上のプロセッサは、

ビデオデータの変換ブロック中の最後の有意係数の位置を決定するようにと、

前記変換ブロックの 0 化領域に対する前記最後の有意係数の位置に基づいて、前記変換ブロックに対する低周波数非分離変換 (L F N S T) インデックスの値を決定し、前記変換ブロックの 0 化領域は、前記変換ブロックの L F N S T 領域内の第 1 の領域と、前記 L F N S T 領域外の前記変換ブロックの第 2 の領域との両方を含むようにと、

前記 L F N S T インデックスの値にしたがって、前記変換ブロックを逆変換するように構成されている装置。

[ C 12 ]

前記 L F N S T インデックスの値は、L F N S T が前記変換ブロックに適用されているか否かを示し、適用されている場合には、適用されている L F N S T のタイプを示す C 1 1 記載の装置。

30

[ C 13 ]

前記 L F N S T インデックスの値を決定するために、前記 1 つ以上のプロセッサは、前記変換ブロック中の前記最後の有意係数の位置が、前記変換ブロックの 0 化領域中にあるケースでは、前記 L F N S T インデックスの値が 0 であると推測し、0 の前記 L F N S T インデックスの値は、前記 L F N S T が前記変換ブロックに適用されていないことを示すように構成されている C 1 1 記載の装置。

[ C 14 ]

前記 L F N S T インデックスの値が 0 であると推測するために、前記 1 つ以上のプロセッサは、

40

前記 L F N S T インデックスの値を示すシンタックス要素を受信することなく、前記 L F N S T インデックスの値が 0 であると推測するように構成されている C 1 3 記載の装置。

[ C 15 ]

前記変換ブロックを逆変換するために、前記 1 つ以上のプロセッサは、

1 つ以上の分離変換により、前記変換ブロックを逆変換するように構成されている C 1 3 記載の装置。

[ C 16 ]

前記 L F N S T インデックスの値を決定するために、前記 1 つ以上のプロセッサは、前記変換ブロック中の前記最後の有意係数の位置が、前記変換ブロックの 0 化領域中にはない

50

ケースでは、前記 L F N S T インデックスを示すシンタックス要素を受信するようにと、前記シンタックス要素をデコードして、前記 L F N S T インデックスの値を決定するように構成されている C 1 1 記載の装置。

[ C 1 7 ]

前記変換ブロックを逆変換するために、前記 1 つ以上のプロセッサは、前記 L F N S T インデックスにより示される L F N S T により、前記変換ブロックの前記 L F N S T 領域を逆変換するようにと、前記 L F N S T により、前記変換ブロックの前記 L F N S T 領域を逆変換した後に、1 つ以上の分離変換により、前記変換ブロックを逆変換するように構成されている C 1 6 記載の装置。

10

[ C 1 8 ]

前記ビデオデータの変換ブロック中の前記最後の有意係数の位置を決定するために、前記 1 つ以上のプロセッサは、前記変換ブロック中の前記最後の有意係数の X 位置および Y 位置を示す 1 つ以上のシンタックス要素をデコードするように構成されている C 1 1 記載の装置。

[ C 1 9 ]

前記変換ブロックを逆変換するために、前記 1 つ以上のプロセッサは、前記変換ブロックを逆変換して、残差ブロックを作成するように構成され、前記 1 つ以上のプロセッサは、前記残差ブロックに対する予測的ブロックを決定するようにと、前記予測的ブロックを前記残差ブロックと組み合わせて、デコードされたブロックを作成するように構成されている C 1 1 記載の装置。

20

[ C 2 0 ]

前記デコードされたブロックを含むピクチャーを表示するように構成されているディスプレイをさらに具備する C 1 9 記載の装置。

[ C 2 1 ]

ビデオデータをデコードするように構成されている装置において、前記ビデオデータの変換ブロック中の最後の有意係数の位置を決定する手段と、前記変換ブロックの 0 化領域に対する前記最後の有意係数の位置に基づいて、前記変換ブロックに対する低周波数非分離変換 (L F N S T) インデックスの値を決定し、前記変換ブロックの 0 化領域は、前記変換ブロックの L F N S T 領域内の第 1 の領域と、前記 L F N S T 領域外の前記変換ブロックの第 2 の領域との両方を含む手段と、前記 L F N S T インデックスの値にしたがって、前記変換ブロックを逆変換する手段とを具備する装置。

30

[ C 2 2 ]