(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6788607号

(P6788607)

(45) 発行日 令和2年11月25日(2020.11.25)

(24) 登録日 令和2年11月4日(2020.11.4)

(51) Int.Cl.

F 1

H01L 21/8239 (2006.01)

H01L 27/105 (2006.01)H01L 27/105 448

H01L 27/105 449

請求項の数 4 (全 11 頁)

(21) 出願番号 特願2017-552102 (P2017-552102)

(86) (22) 出願日 平成28年4月14日 (2016.4.14)

(65) 公表番号 特表2018-513559 (P2018-513559A)

(43) 公表日 平成30年5月24日 (2018.5.24)

(86) 國際出願番号 PCT/JP2016/002025

(87) 國際公開番号 WO2016/170759

(87) 國際公開日 平成28年10月27日 (2016.10.27)

審査請求日 平成31年4月12日 (2019.4.12)

(31) 優先権主張番号 14/695,835

(32) 優先日 平成27年4月24日 (2015.4.24)

(33) 優先権主張国・地域又は機関

米国(US)

(73) 特許権者 316005926

ソニーセミコンダクタソリューションズ株

式会社

神奈川県厚木市旭町四丁目14番1号

(74) 代理人 110001357

特許業務法人つばさ国際特許事務所

(72) 発明者 角野 潤

アメリカ合衆国 ニュージャージー州 O

7656 パークリッジ ソニー ドライ

ブ 1 ソニー エレクトロニクス イン

ク内

審査官 宮本 博司

最終頁に続く

(54) 【発明の名称】階段型コンタクトソケット領域を形成する方法

## (57) 【特許請求の範囲】

## 【請求項1】

階段型コンタクトソケット領域を形成する方法であって、

複数の平面電極および複数の絶縁層を含むスタックを提供する工程であって、隣接する

複数の平面電極が絶縁層によって互いに分離される工程と、

前記スタック上にマスクを配置する工程と、

前記マスクの下にない前記複数の絶縁層内の第1の絶縁層の第1の部分をエッチングし

て、前記複数の平面電極内の第1の平面電極の第1の部分を露出させる工程と、

マスクをブルバックする工程と、

マスクをブルバックした後、マスクをブルバックすることによって露出した第1の絶縁

層の第2の部分をエッチングし、第1の平面電極の第1の部分の一部をエッチングし、複

数の絶縁層に含まれる第2の絶縁層の第1の部分をエッチングする工程と

を含み、

エッチングにより形成された第2の絶縁層の端部が傾斜しており、第1の平面電極の端

部から、第1の平面電極の端部と第2の平面電極の端部との間に延びている

階段型コンタクトソケット領域を形成する方法。

## 【請求項2】

前記第1の絶縁層の端部は傾斜している

請求項1に記載の階段型コンタクトソケット領域を形成する方法。

## 【請求項3】

10

20

前記第1および第2の平面電極の端部は垂直である

請求項1または請求項2に記載の階段型コンタクトソケット領域を形成する方法。

【請求項4】

各接続導体は、平面電極の上面および端面に電気的に接続されている

請求項1ないし請求項3のいずれか一項に記載の階段型コンタクトソケット領域を形成する方法。

【発明の詳細な説明】

【技術分野】

【0001】

本出願は、2015年4月24日に提出された米国優先権特許出願U.S.14/695835の利益を主張するものであり、その各々の内容全体が参照により本明細書に組み込まれる。

10

【0002】

本開示は、3次元メモリのソケット構成に関し、特に、3次元メモリのソケットの面積効率を改善することに関する。

【背景技術】

【0003】

メモリデバイスは、幅広い分野で使われている。例えば、ソリッドステートメモリは、コンピューティングデバイスに関連するプログラム命令およびデータの長期または短期記憶に使用することができる。メモリ密度、アクセス速度、および信頼性は、ソリッドステートメモリの設計において重要な考慮事項である。最近のソリッドステートメモリの設計には、3次元アーキテクチャが使用されている。このような設計により、メモリ密度を高めることができる。加えて、そのような設計は、抵抗性ランダムアクセスメモリ(ReRAM)、および相変化ランダムアクセスメモリ(PCMまたはPRAM)に関連して使用するのに適している。

20

【発明の概要】

【発明が解決しようとする課題】

【0004】

3次元(3D)メモリ構造では、ビット線(BL)およびワード線(WL)を含む信号線は、メモリ構造の周辺部のソケット領域とメモリアレイ自体との間に延在する。より詳細には、メモリアレイの第1の側の第1のソケット領域は、ビット線に関連する電極またはコンタクトを含み、メモリアレイの第2の側の第2のソケット領域は、ワード線に関連する電極またはコンタクトを含むことができる。他の構成では、メモリアレイの第1および第2の対向する側のソケット領域をビット線に関連付けることができ、メモリアレイの第3および第4の対向する側のソケット領域をワード線に関連付けることができる。メモリアレイに含まれるメモリセルの数が増加するにつれて、対応する信号線(すなわち、ビット線および/またはワード線)の数が増加する。さらに、ビット線およびワード線のサイズにおける物理的制約により、メモリ構造の占有面積は、メモリアレイの面積に比べてますます大きくなる。この問題は、メモリセルのサイズおよびメモリセルピッチのサイズの減少、およびメモリアレイの密度の増加によって悪化する。

30

【0005】

ソケット領域によって占有されるメモリ構造の領域もまた、メモリ構造内のデッキまたは層の数が増加するにつれて、メモリアレイが占有するメモリ構造の領域に対して増加する。より詳細には、従来のソケット構造では、異なる水平電極に対応する異なるデッキまたは層が階段型の配置で配置される。これらの異なる層は、垂直導体によってアクセスされる。その結果、水平電極の数を増加させるためには、ソケット領域のサイズを大きくする必要がある。すなわち、「階段構造」内の「階段」の数を増やす必要があり、これは、メモリアレイから遠ざかる方向にソケット領域の長さが所与の電極接触サイズに対して比例して増加する。さらに、水平電極と垂直導体との間に確立される接点のサイズは、様々な要因によって制約される。例えば、適切な電気的接触、したがって適切に低い電気抵抗

40

50

を提供するために、最小接触面積を維持する必要がある。さらに、垂直導体を所望の接触領域に整列させる能力は、製造公差によって制限されることがあり、従って、最小の接触面積マージンを必要とする。したがって、メモリセル面積密度が増加するにつれて、接続領域またはソケット領域によって占められる総面積の割合がますます大きくなる傾向にある。

#### 【0006】

このような問題のために、メモリ構造の全体サイズの減少は、メモリアレイ自体のサイズの減少に伴わず、3次元メモリ構造の提供に関連するコストは比較的高いままである。

#### 【課題を解決するための手段】

#### 【0011】

本開示の実施形態による方法は、対応するソケット領域が、従来の配置に従って構成された階段状のコンタクトと比較して縮小された面積を有することを可能にする階段型のコンタクト構成を提供する。このような方法によれば、ブルバックプロセスを用いて階段構造において階段状の平面電極を連続的に露出させる。隣接する平面電極の間に配置された誘電体層は、各誘電体層の端部の少なくとも一部が、下に横たわる水平電極の端部と上に横たわる水平電極の端部との間の領域にあるようにエッチングされる。少なくともいくつかの実施形態によれば、各誘電体層の端部は傾斜している。本開示の実施形態による方法は、さらに、電極の上面の一部と電極の端面の一部の両方に接触する接続導体を設けることを含むことができる。

#### 【0014】

本開示の実施形態によれば、階段状コンタクトソケット領域を形成する方法が提供される。この方法は、複数の平面電極と、複数の絶縁層とを有するスタックを提供するステップを含み、隣接する平面電極は、絶縁層によって互いに分離される。マスクがスタック上に配置され、マスクの下にない第1の絶縁層の第1の部分がエッチングされて、複数の平面電極内の第1の平面電極の第1の部分が露出される。次に、マスクをブルバックする。この方法はさらに、マスクをブルバックし、第1絶縁層の第2部分をエッチングし、第1平面電極の第1部分をエッチングし、第2絶縁層の第1部分をエッチングすることを含む。エッチングによって形成された第2絶縁層の端部は、傾斜しており、第1平面電極の端部から第1平面電極の端部と第2平面電極の端部との間に延びている。

10

20

30

#### 【0015】

本開示の実施形態のさらなる特徴および利点は、特に添付の図面と併せて以下の説明からより容易に明らかになるであろう。

#### 【図面の簡単な説明】

#### 【0016】

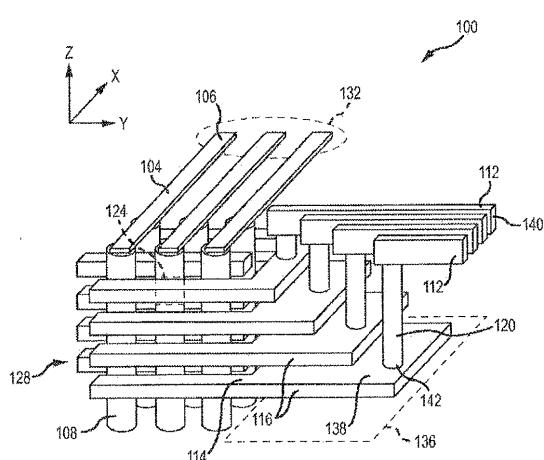

【図1】例示的な3次元メモリ構造の斜視図である。

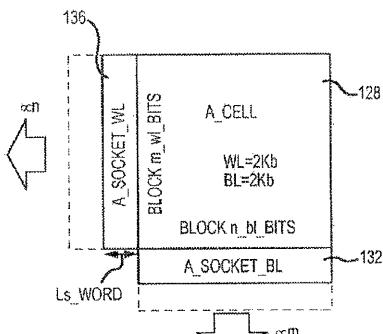

【図2】平面図における3次元メモリ構造の領域を示す。

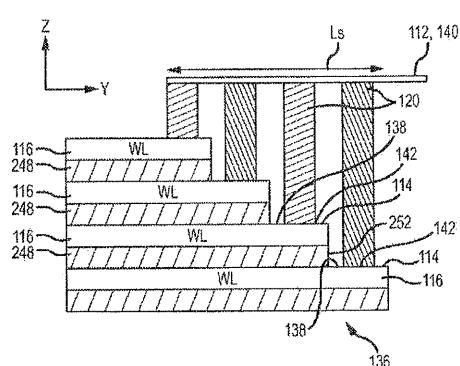

【図3】立面図における従来技術の3次元メモリ構造を示す。

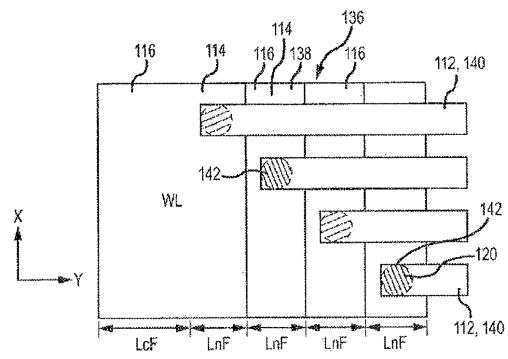

【図4】図3の従来技術の3次元メモリ構造を平面図で示している。

【図5】本開示の実施形態による立体メモリ構造を立面図で示している。

40

【図6】平面図における図5の3次元メモリ構造を示す。

【図7】基準3次元メモリ構造の面積効率と比較した、本発明の実施形態による例示的な3次元メモリ構造の面積効率を示すグラフである。

【図8】本開示の実施形態による方法の態様を示すフローチャートである。

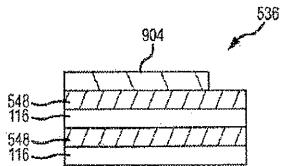

【図9A】本開示の実施形態による階段接触構造を形成するためのプロセスのステップを示す。

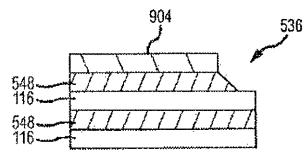

【図9B】本開示の実施形態による階段接触構造を形成するためのプロセスのステップを示す。

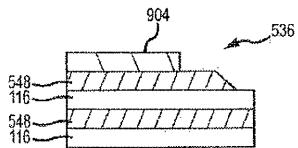

【図9C】本開示の実施形態による階段接触構造を形成するためのプロセスのステップを示す。

50

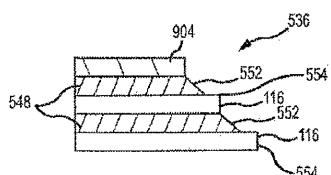

【図9D】本開示の実施形態による階段接触構造を形成するためのプロセスのステップを示す。

【発明を実施するための形態】

【0017】

図1は、例示的な3次元メモリ構造100を示す。より詳細には、垂直メモリアレイの形態の3次元メモリ構造100が示されている。メモリ構造100は、垂直メモリ素子108の端部に電気的に接続された複数のビット線104を含む。メモリ構造100はまた、複数のワード線112および複数の水平または平面電極116を含む。各ワード線112は、水平電極またはデッキ116の上面114に、直接または接続導体120を介して接続される。水平電極116は、一般に、xおよびy方向に延びる平面内に配置される。メモリセル124は、水平電極116に隣接する垂直メモリ素子108の領域に形成され、一般にメモリ構造のメモリアレイ128内に含まれる。さらに、メモリアレイ128は、3次元(x, y, z)に延びるボリューム内に含まれる。

【0018】

例示的なメモリ構造100において、ビット線104は、メモリアレイ領域128の一方の側に隣接するビット線ソケット領域132内でアクセスできるように延びている。他の実施形態によれば、ビット線104は、2つのビット線ソケット領域132が提供されるように、メモリアレイ領域128の反対側に延びている。ビット線ソケット領域132内でアクセス可能なビット線コンタクトまたはビット106の数は、この例ではビット線104の数に等しい。同様に、ワード線112は、メモリアレイ領域128の側に隣接するワード線ソケット領域136から延びている。他の実施形態によれば、ワード線ソケット領域136は、メモリアレイ128の追加の側に設けることができる。ワード線コンタクトまたはビット140の数は、この例では、ビット線112の数に等しい。コンタクト142において接続導体120に電気的に接続された水平電極116の接続部分138が階段型配置に配置されているので、ワード線ソケット領域136によって囲まれた領域は、突起として示されている。異なる水平電極またはデッキ116の接続部138は、メモリアレイ領域128から異なる距離に配置されている。

【0019】

メモリ構造100内のメモリセル124の数が増加すると、ビット線108および/またはワード線112の数も増加する。この例では、増加した数の水平電極またはデッキ116を可能にすることによって、ワード線112の数は、一般に高密度メモリアレイ領域128をサポートするビット線104の数よりも多い。さらに、例示的な従来技術のメモリ構造100のような3次元メモリ構造は、3次元に配置されたメモリセル124を有し、ビット線132およびワード線136のソケット領域は、水平電極116に平行な平面内で、接続を完了する。その結果、メモリセル124の数が増加すると、特に水平電極またはデッキ116の数が増加するにつれて、ビット線132およびワード線136のソケット領域によって占められるメモリ構造の総面積の割合がますます大きくなる。

【0020】

図2に示すように、ワード線ソケット領域136の長さ $L_{s\_w o r d}$ は、水平電極116の数(n)が増加するにつれて増加し、接続導体120が水平電極116にアクセスすることを可能にする。水平電極116は、階段接触配置に配置されている。したがって、デッキまたは水平電極116の数が増加すると、メモリアレイ128の面積密度が増加し、ワード線ソケット領域136が占める面積も増加する。同様に、ビット線104の数(m)が増加すると、ビット線ソケット領域132が占める面積が増加する。加えて、所与のソケット領域132, 136の配置に対して、ソケット領域132, 136によって占有されるメモリ構造100の全体面積は、デッキ116の数、従って所与のメモリセル領域128内のメモリセル124の数が増加するにつれて増加する。さらに、ソケット領域132, 136が占める面積の、メモリ構造100の総面積の占める割合は、メモリセル領域128の密度が増加するにつれて、ますます大きくなる。本開示を考慮した当業者によって理解されるように、面積効率の低下は、垂直メモリ構造に含まれるソケット領域

10

20

30

40

50

132, 136の数に関係なく生じる。

#### 【0021】

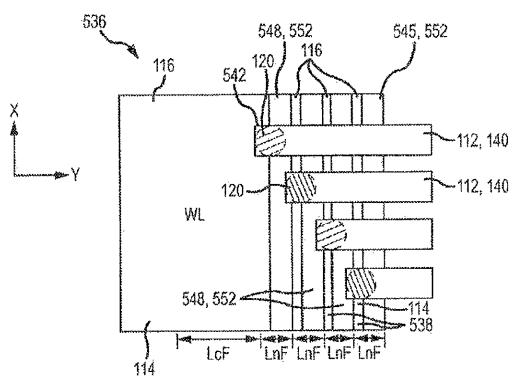

図3は、図1に示されたメモリ構造100のような例示的なメモリ構造の一部を、 $x$ 方向に沿った視線から、従来技術のワード線ソケット領域136を包含して示す。図4は、図3に示されたメモリ構造100のワード線ソケット領域136の部分を、 $z$ 軸または方向に沿った視線からの平面図で示す。図示されているように、ワード線ソケット領域136は、階段型コンタクト領域を含むことができる。さらに、水平電極116のコンタクト領域138と接続導体120との間の各コンタクト142は、水平電極116の上面114上に完全に配置される。 $y$ 軸に平行な方向におけるワード線ソケット領域136の長さは、デッキ116の数に比例し、この例では、以下の式で与えられる。

10

$$L_s = \{ L_c + L_n n \} F$$

ここで、 $L_s$ はソケット長さ、 $L_c$ は一定の長さ係数、 $L_n$ は長さデッキ116の数に依存する係数、 $n$ はデッキ116の数、 $F$ はメモリセル領域128のハーフピッチである。

#### 【0022】

図3に示すように、各水平電極116は、誘電体または絶縁層248によって隣接する水平電極116から分離されている。各絶縁層248は、垂直（すなわち、水平電極116の上面114に垂直または90度、さらに、 $z$ 方向に平行）な端部表面252を有し、絶縁層248上の水平電極116よりも $y$ 方向には伸びていない。従って、各水平電極116の平面上部表面114の一部分は、対応する接続導体120とのコンタクト142が形成されるコンタクト領域138として利用可能である。しかし、隣接する接続導体120の間の $y$ 方向、より詳細には、選択された水平電極116に電気的に接続された接続導体120と、選択された水平電極116の両側の水平電極116との間に、維持されなければならない位置合わせマージンまたは空間要素は、相対的に大きくなり、相対的に大きい $L_n F$ によって与えられる間隔をもたらす。

20

#### 【0023】

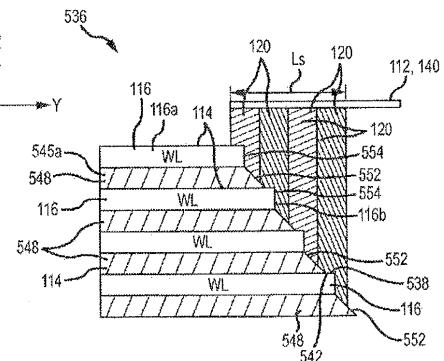

図5は、図1に示されたメモリ構造100などの3次元メモリ構造の一部を示しており、本開示の実施形態に従って構成されたワード線ソケット領域536を、 $x$ 方向に沿った視線からの図である。図6は、図5に示されたメモリ構造100のワード線ソケット領域536の部分を $z$ 軸に沿った視線からの平面図で示す。ソケット領域536は、平面電極116の端部が階段式に配置されている点で従来のソケット領域136に類似している。電極はスタックの下側ほど $y$ 方向に伸びている。さらに、各平面電極116は、隣接する誘電体層の間に介在する絶縁層または誘電体層548によって隣接する電極から分離されている。図示されているように、垂直導体120と接続導体120との間の間隔は $y$ 方向に縮小されている。すなわち、アライメントマージンまたは長さ係数は、図3および図4に示した従来技術の構成に比べて減少している。例えば、従来の構成では、 $y$ 方向の接続導体120間のアライメントマージンを一定に保つ必要があったが、アライメントマージンを小さくして本開示の実施形態を構成することができる。本開示の少なくともいくつかの実施形態によれば、アライメントマージンをゼロにすることができる。さらに他の実施形態によれば、アライメントマージンは、接続導体120が $x$ 方向で互いに分離されている限り、 $y$ 方向で互いに重なり合うように、負であってもよい。その結果、本開示の実施形態は、従来技術による垂直導体120間の間隔と比較して、垂直導体120の中心線間の間隔を減少させることができる。従って、所与の数のデッキ116および他のすべての係数が等しい場合、本開示の実施形態に従って構成されたソケット領域536の長さは、従来技術に従って構成されたソケット領域136のソケット長さよりも短くなる。この減少した間隔は、隣接する水平電極116間の誘電体層548の端面552のテープ状または傾斜状の構成によって可能になる。

30

#### 【0024】

本開示の実施形態によれば、誘電体層548（例えば、誘電体層548a）の $y$ 方向において最も遠い範囲に対応する、またはそれを含む端面552は、誘電体層548の直上にある水平電極116（例えば、水平電極116a）の $y$ 方向における最も遠い範囲と、

40

50

誘電体層 548 の直下にある水平電極 116（例えば、水平電極 116b）との間の点に伸びている。特に、水平電極 116a の端面 554 と上に横たわる水平電極 116 の端面 554 との間に、下にある水平電極 116 の上面 114 の一部分が、誘電体層 548 によって部分的に覆われている。さらに、この例では、各誘電体層 548 の端面 552 は、誘電体層 548 を覆う水平電極 116 の底面の端部に対応する点から、下にある水平電極 116 の端面 554 に向かう点（ただし、下にある水平電極 116 の端面 554 までではない）に伸びるように傾斜している。したがって、接触領域 542 として利用可能な下にある水平電極 116 の上面 114 の覆われていない部分 538 は、誘電体層の端部が垂直である構成と比べて減少している。言い換えれば、本開示の実施形態では、重なり合う水平電極 116 によって重なり合わない、下にある水平電極 116 の上面 114 の領域は、介在誘電体層 548 の傾斜端部 552 によって部分的に覆われる。この構成の結果、アライメント許容誤差、したがってアライメントマージン要件は、従来の構成に比べて低減されるか、または完全に排除される。特に、整列していない垂直導体 120 は、ターゲット水平電極 116 の下にある誘電体層 548 によって、ターゲット水平電極 116 の直下の水平電極 116 に接触することが防止される。すなわち、少なくともある範囲にわたって、整列していない垂直導体 120 の影響をなくすことができる。このようにして得られたアラインメントマージン要件の減少の結果として、所与のスペーシングファクタおよびデッキ 116 の数に対して、本発明の実施形態のソケット領域の長さ  $L_s$  を、垂直な誘電体層の端部を有する従来の構成と比べて減らすことができる。

## 【0025】

10

加えて、ターゲット水平電極 116 のエッジ部分 554 は、コンタクト領域 542 の一部として利用可能である。従って、水平電極 116 と、関連する垂直導体 120 との間の適切な低電気抵抗を含むがこれに限定されない電気的性能を、上面 538 の覆われていない部分の面積が従来の構成に比べて縮小されていても維持することができる。少なくともいくつかの実施形態によれば、垂直導体は、ターゲット水平電極 116 のいずれかの側の誘電体層 548 の一部と接触するようにサイズ調整され、整列される。

## 【0026】

20

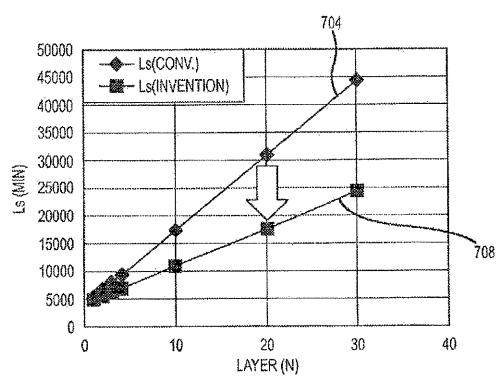

図 7 は、従来技術に従って構成されたワード線ソケット領域 136 の長さ（プロット 704）と、本開示の実施形態に従って構成されたワード線ソケット領域 536 の長さ（プロット 708）とを比較するグラフである。より詳細には、異なる数の層 116 を有する 3 次元メモリ構造のワード線ソケット領域 136, 536 の長さ ( $L_s$ ) が示されている。この例では、所与の一定の長さ係数およびセル領域の所与のハーフピッチについて、本開示の実施形態に従って構成されたワード線ソケット領域 536 の長さが、従来技術に従って構成されたワード線ソケット領域 136 の長さが増加する速度よりも遅い速度で、デッキの数 ( $n$ ) とともに増加することが分かる。これにより、メモリ構造の小型化を図ることができる。

30

## 【0027】

30

さらに、本開示の実施形態に従って構成されたワード線ソケット領域 536 を利用する 3 次元メモリ構造の面積効率は、従来の構成よりも大きくすることができる。特に、3 次元メモリ構造の面積効率は、メモリアレイの面積にソケット領域の面積を加えたメモリアレイの面積の比として評価することができる。より具体的には、面積効率は以下のように表すことができる。

40

## 【数 1】

$$Eff = \frac{A_c}{(A_c + A_{\text{first\_socket\_region}} + A_{\text{second\_socket\_region}})} = \frac{A_c}{(A_c + A_s)}$$

ここで、 $Eff$  はメモリ構造の面積効率、 $A_c$  はメモリセル領域の面積、 $A_{\text{first\_socket\_region}}$  は第 1 のソケット領域の面積、 $A_{\text{second\_socket\_region}}$  は第 2 のソケット領域の面積、 $A_s$  はビット線およびワード線ソケット領域の総面積である。例えば、図 2 を参照すると、面積効率は、メモリアレイ領域 12

50

8の面積をメモリアレイ領域128に等しい面積で除したものに、ピット線ソケット領域132の面積にワード線ソケット領域136, 536の面積を加えたものを加えたものに等しい。これらの領域のすべてが水平電極またはデッキ116にほぼ平行な平面内にある。したがって、ソケット領域が階段接触領域を取り囲む場合、そのソケット領域の面積は、領域の水平面への投影によって与えられる。ワード線ソケット領域536に、図5および図6に示すような傾斜縁部552を有する誘電体層548を設けることによって、本開示の実施形態の結果として生じる3次元メモリ構造500の面積効率は、従来の構成に比べて改善され得る。

#### 【0028】

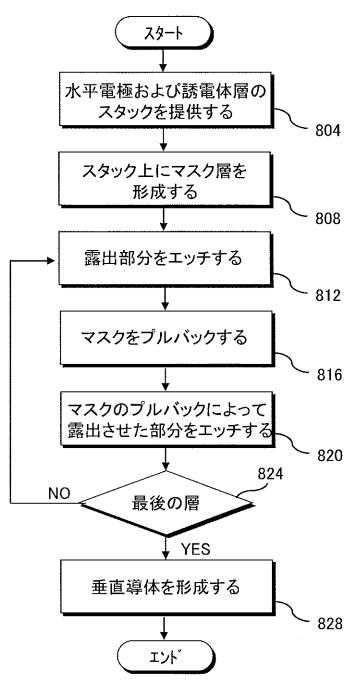

本開示の実施形態によれば、従来の技術または構成と比較して縮小領域内にソケット領域を設ける方法が提供される。図8は、そのような方法のプロセスステップを示すフローチャートを示し、プロセスステップの実行中の異なるステージにおけるソケット構造536を図9A～図9Dに示す。この方法は、誘電体層548によって隣接する平面電極116から分離された平面または水平電極116のスタックを提供するステップ(ステップ804)を含むことができる。次いで、マスクが下の誘電体層の一部を露出させないように、上部誘電体層548上にマスク層を形成することができる(ステップ808)。図9Aは、マスク904を追加した後のソケット領域536を示す。誘電体層548の露出部分をエッチングすることができる(ステップ812)。エッチングの初期段階後のソケット領域536が図9Bに示されている。次いで、マスク904をブルバックすることができる(ステップ816)。マスク904をブルバックした後のソケット領域536は、図9Cに示されている。次に、前のエッチングステップで露出した平面電極116および次の誘電体層548をエッチングし、上部誘電体層548をさらにエッチングすることができる(ステップ820)。ステップ820の完了後のソケット領域536が図9Dに示されている。このブルバックプロセスは、最後の平面電極116の一部が露出するまで継続することができる。本開示の実施形態によれば、エッチングプロセスの間、誘電体層548は、下にある平坦な電極116の上面に直角にエッチングされるのではなく、傾斜した表面を作り出すために先細にされる。誘電体層548が「ブルバックされる」量は、上にある平面電極116が「ブルバックされる」量より少なくともよい。ステップ824において、最後の平面電極116に到達したかどうかの判定を行うことができる。そうでない場合、プロセスはステップ816に戻ることができる。

#### 【0029】

最後の電極に達した後、少なくとも1つの垂直導体120が各平面電極116に接続されるように、垂直導体120または接続導体120を形成することができる(ステップ828)。垂直導体120を形成する工程の間に、平面電極116と、関連する垂直導体120との間の接触領域552は、水平電極116の上面114の一部分を、平面電極116の端面554の一部分として含む。本開示を考慮した当業者によって理解され得るように、傾斜電極532を有する誘電体層548を設けることにより、垂直導体120が、ターゲット平面電極116の下の平面電極116に電気的に接触することが防止される。このため、従来の階段型コンタクト構成と比較して、所定の製造公差に必要なアライメントマージンを小さくすることができる。各平面電極116を垂直導体120に電気的に接続した後、プロセスを終了することができる。

#### 【0030】

本開示の実施形態は、3次元メモリ構造に関連する従来のソケット領域構成と比較して縮小された領域を占有することができるソケット領域構成を説明したが、本開示の実施形態は、このような構造に関連しての使用に限定されない。特に、本明細書で開示されるソケット領域は、コンタクトが階段型構造に配置される任意の電気構造に関連して利用され得る。より詳細には、本開示の実施形態は、階段型配置に配置された電気接点に対してアライメントマージンを低減することができる構成を提供する。

#### 【0031】

本開示の実施形態の様々な特徴および構成要素は、「垂直」と「水平」基準方向に

10

20

30

40

50

関連して説明した便宜上のものである。一般に、「垂直」は、様々な図に描かれた基準座標系のz軸に平行な方向を指す。「水平」方向は、一般に、基準座標系のxおよびy方向にある平面に対応する。座標系の絶対配向、従って、「垂直」および「水平」成分または特徴の絶対的な向きは、必ずしも固定されているとは限らない。したがって、本開示の実施形態によれば、座標系の向きは絶対座標系内に固定されていない。

### 【0032】

本発明の前述の説明は、例示および説明のために提示されたものである。さらに、この説明は、本発明をここに開示された形態に限定することを意図するものではない。従って、関連技術の技術または知識の範囲内で、上記の教示に相応する変形および変更は、本発明の範囲内である。上述した実施形態は、本発明を実施するために現在知られている最良の形態を説明するものであり、当業者がそのような実施形態、または、本発明の特定の用途または使用によって必要とされる様々な変更を伴う他の実施形態で本発明を利用できるようにすることを意図している。添付の特許請求の範囲は、従来技術によって許容される範囲で代替の実施形態を含むと解釈されることが意図される。

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図 8】

【図 9 A】

【図 9 B】

【図 9 C】

【図 9 D】

---

フロントページの続き

(56)参考文献 特開2010-027870(JP,A)

特開2007-266143(JP,A)

特開2015-056452(JP,A)

欧州特許出願公開第01434258(EP,A2)

特開2011-211039(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/8239

H01L 27/105