(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5358734号

(P5358734)

(45) 発行日 平成25年12月4日(2013.12.4)

(24) 登録日 平成25年9月6日(2013.9.6)

(51) Int.Cl.

G 11 C 11/15 (2006.01)

F 1

G 11 C 11/15 14 O

請求項の数 11 (全 12 頁)

(21) 出願番号 特願2012-503520 (P2012-503520)

(86) (22) 出願日 平成22年3月25日 (2010.3.25)

(65) 公表番号 特表2012-522329 (P2012-522329A)

(43) 公表日 平成24年9月20日 (2012.9.20)

(86) 國際出願番号 PCT/US2010/028628

(87) 國際公開番号 WO2010/117654

(87) 國際公開日 平成22年10月14日 (2010.10.14)

審査請求日 平成25年3月15日 (2013.3.15)

(31) 優先権主張番号 12/414,452

(32) 優先日 平成21年3月30日 (2009.3.30)

(33) 優先権主張国 米国(US)

(73) 特許権者 500373758

シーゲイト テクノロジー エルエルシー

アメリカ合衆国、95014 カリフォルニア州、クパチーノ、サウス・ディ・アンザ・ブールバード、10200

(74) 代理人 110001195

特許業務法人深見特許事務所

(72) 発明者 チェン、イラン

アメリカ合衆国、55437 ミネソタ州、エデン・プレーリー、フェートン・ドライブ、10124

(72) 発明者 リー、ハイ

アメリカ合衆国、55347 ミネソタ州、エデン・プレーリー、フェートン・ドライブ、10124

最終頁に続く

(54) 【発明の名称】不揮発性メモリセルの予測的予加熱

## (57) 【特許請求の範囲】

## 【請求項1】

第1のブロックアドレスと関連付けられる未処理不揮発性第1のメモリセルに論理状態を書込むステップと、

書込むステップの間に不揮発性第2のメモリセルに熱的前処理を同時に適用するステップとを備え、第2のメモリセルは第1のブロックアドレスに応答して選択される第2のブロックアドレスと関連付けられる、方法。

## 【請求項2】

制御回路と、第1のブロックアドレスと関連付けられる未処理不揮発性第1のメモリセルと、第2のブロックアドレスと関連付けられる未処理第2の不揮発性メモリセルとを備える装置であって、制御回路は、第2のメモリセルに熱的前処理を同時に適用しながら第1のメモリセルに論理状態を書込むように構成され、第2のメモリセルは第1のブロックアドレスに応答して選択されて前記熱的前処理される、装置。 10

## 【請求項3】

第1および第2のメモリセルはメモリセルの行および列を備えるアレイに配置され、第1のメモリセルは第1の行および第1の列上に配設され、第2のメモリセルは異なる第2の行および異なる第2の列上に位置決めされる、請求項2に記載の装置。

## 【請求項4】

制御回路は、書き込みコマンドを受信して第1のブロックアドレスにある第1のメモリセルに論理状態を書き込み、かつ第1のブロックアドレスを用いて第2のブロックアドレスを同 20

定して第2のメモリセルに対するその後の書き込みコマンドの将来の受信を予測するようにさらに構成される、請求項2に記載の装置。

**【請求項5】**

第1のメモリセルは、第1のブロックアドレスを有し、かつ第1の複数の隣接するメモリセルを備える第1のアドレス指定可能メモリブロックの部分を形成し、制御回路は、第1の複数の隣接するメモリセルの各々への選択された論理状態の書き込みを命令し、第2のメモリセルは、第2のブロックアドレスを有し、かつ第2の複数の隣接するメモリセルを備える第2のアドレス指定可能メモリブロックの部分を形成し、制御回路は、第2の複数の隣接するメモリセルの各々への熱的前処理電流の印加を命令する、請求項2に記載の装置。

10

**【請求項6】**

第1のメモリブロックはデータ記憶アレイの第1の行に沿って配置され、第2のメモリブロックはデータ記憶アレイの異なる第2の行に沿って配置される、請求項5に記載の装置。

**【請求項7】**

第1のブロックアドレスはブロックアドレスNとして特徴付けられ、第2のブロックアドレスはブロックアドレスN+1として特徴付けられる、請求項5に記載の装置。

**【請求項8】**

第1および第2のメモリセルはデータキャッシュ中のメモリセルとして特徴付けられ、第1のブロックアドレスはデータキャッシュの第1のキャッシュ線Nとして特徴付けられ、第2のブロックアドレスはデータキャッシュの第2のキャッシュ線N-1として特徴付けられる、請求項2に記載の装置。

20

**【請求項9】**

熱的前処理の結果、第2のメモリセルの温度が上昇し、制御回路は、第2のメモリセルが上昇した前記温度を保持する間、前記第2のメモリセルに熱的前処理を同時に適用した後に第2のメモリセルに第2の論理状態を書込むようにさらに構成される、請求項2に記載の装置。

**【請求項10】**

予め定められた時間間隔の終わりに制御回路に指示を与えるタイミング機構をさらに備え、制御回路は、前記指示に応答して、第2のメモリセルに対する前記熱的前処理のさらなる適用を打ち切る、請求項2に記載の装置。

30

**【請求項11】**

タイミング機構は、RC電圧減衰を用いて予め定められた時間間隔の終わりを示す抵抗-容量結合型(RC)回路を備える、請求項10に記載の装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

**背景**

データ記憶デバイスは一般的に、高速かつ効率的な態様でデータを記憶し、検索するように動作する。いくつかの記憶デバイスは、個別のデータビットの記憶に固体メモリセルの半導体アレイを利用する。そのようなメモリセルは揮発性または不揮発性であり得る。

40

**【背景技術】**

**【0002】**

揮発性メモリセルは一般的に、動作電力がデバイスに供給され続ける限りにのみメモリに記憶されたデータを保持する一方で、不揮発性メモリセルは一般的に、動作電力の印加がなくてもメモリ中のデータ記憶を保持する。

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0003】**

これらおよび他の種類のデータ記憶デバイスにおいて、特にメモリセルへのデータの書

50

込に関してメモリセル動作の効率を高めることが望ましいことがしばしばある。

【課題を解決するための手段】

【0004】

概要

本発明のさまざまな実施形態は、一般的に、熱的前処理を用いてスピン注入磁化反転型ランダムアクセスメモリ(STRAM)メモリセルなどの不揮発性メモリセルにデータを書込むための方法および装置に向けられている。

【0005】

いくつかの実施形態に従うと、方法は一般的に、第1のブロックアドレスと関連付けられる未処理不揮発性第1のメモリセルに論理状態を書込むステップを備える。熱的前処理は、第1のブロックアドレスに応答して選択される第2のブロックアドレスと関連付けられる不揮発性第2のメモリセルに同時に適用される。10

【0006】

さらなる実施形態に従うと、装置は一般的に、制御回路と、第1のブロックアドレスと関連付けられる未処理不揮発性第1のメモリセルと、第2のブロックアドレスに関連付けられる未処理第2の不揮発性メモリセルとを備える。制御回路は、第2のメモリセルに熱的前処理を同時に適用しつつ第1のメモリセルに論理状態を書込むように構成され、第2のメモリセルは第1のブロックアドレスに応答して選択されて当該熱的前処理される。

【0007】

以下の詳細な考察および添付の図面に鑑みて、本発明のさまざまな実施形態を特徴付けるこれらおよび他の特徴および利点を理解することができる。20

【図面の簡単な説明】

【0008】

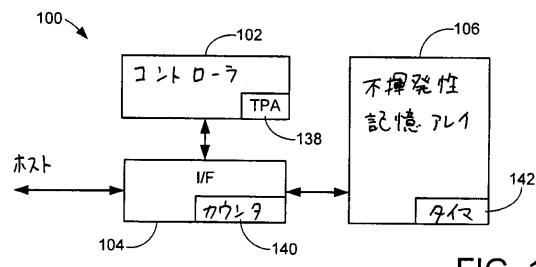

【図1】本発明のさまざまな実施形態に従って構築されかつ動作される例示的なデータ記憶デバイスの一般化された機能図である。

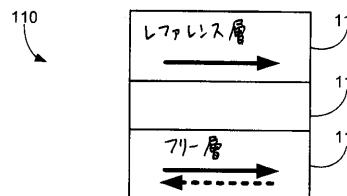

【図2】スピン注入磁化反転型ランダムアクセスメモリ(STRAM)メモリセルの磁性トンネル接合(MTJ)の例示的な構築を示す図である。

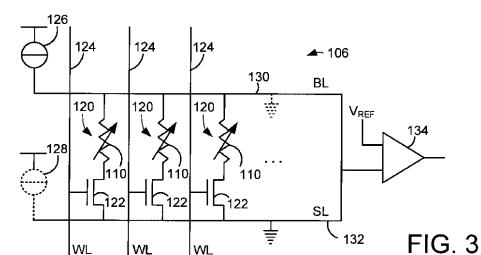

【図3】図2に構成されるようなSTRAMメモリセルを用いる図1のアレイの部分の概略図である。

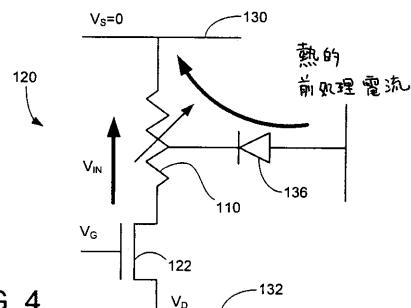

【図4】熱的前処理ダイオードを有する、図1のアレイの部分の別の概略図である。30

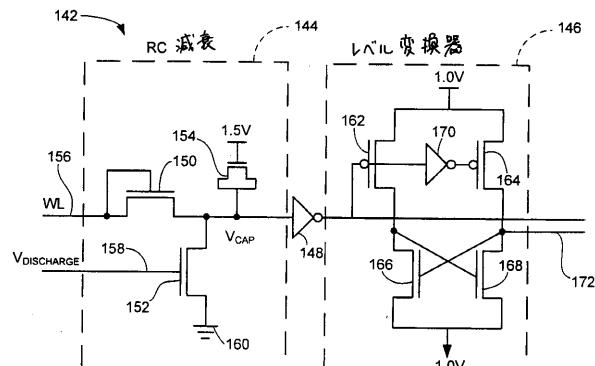

【図5】本発明のさまざまな実施形態に従うタイミング回路の概略図である。

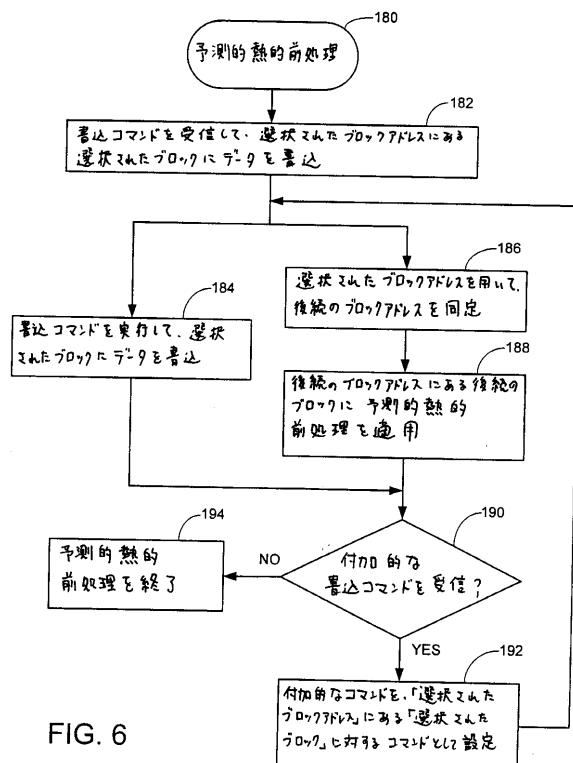

【図6】予測的熱的前処理ルーチンのフロー図である。

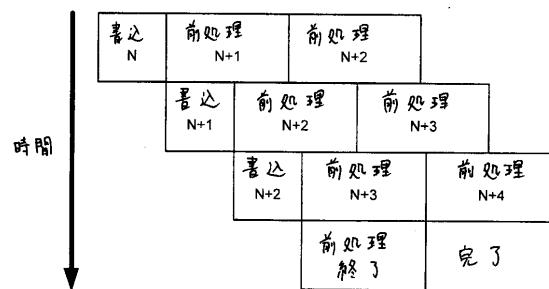

【図7】いくつかの実施形態に従うデータ書き動作において選択的にメモリセルを前処理するためのタイミング図である。

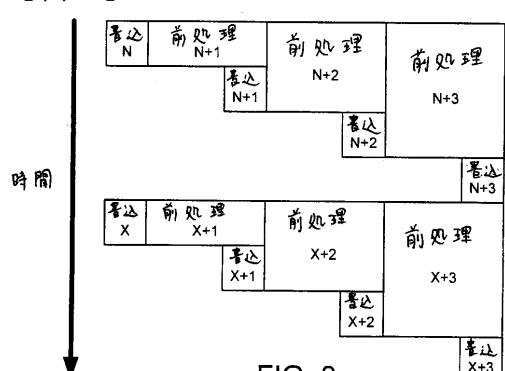

【図8】さらなる実施形態に従うデータ書き動作において選択的にメモリセルを前処理するためのタイミング図である。

【図9】連想記憶装置(CAM)として構成される図1のデバイスのキャッシュメモリ構造のブロック図である。

【図10】いくつかの実施形態に従う図9のCAMのメモリセルを選択的に前処理するためのタイミング図である。40

【図11】いくつかの実施形態に従う図9のCAMのメモリセルを選択的に前処理するためのタイミング図である。

【発明を実施するための形態】

【0009】

詳細な説明

図1は、本発明のさまざまな実施形態を有利に実践することができる例示的な環境を図示する、データ記憶デバイス100の機能ブロック図を提供する。デバイス100は、最上位レベルコントローラ102と、インターフェイス(I/F)回路104と、不揮発性データ記憶アレイ106とを含む。I/F回路104は、コントローラ102の命令の下で動作してアレイ106とホストデバイス(図示せず)との間でユーザデータを転送する50

。いくつかの実施形態では、デバイスはソリッドステートドライブ( S S D )として特徴付けられ、コントローラ 102 はプログラマブルマイクロコントローラであり、アレイ 106 は不揮発性メモリセル( ユニットセル )のアレイを備える。

#### 【 0010 】

アレイ 106 の例示的なメモリセル構築を図 2 に示す。図 2 のメモリセルは磁性トンネル接合( M T J ) 110 を有するスピン注入磁化反転型ランダムアクセスメモリ( S T R A M )構成を有するが、他のセル構成を用いることができる。M T J 110 は、固定されたレファレンス層 112 と、介在するトンネル( バリア )層 116 によって分離されるプログラマブルフリー層 114 ( 記録層 ) とを含む。

#### 【 0011 】

レファレンス層 114 は、図 2 に示される関連の矢印で示されるような選択された方向への固定された磁化の向きを有する。この固定された磁化の向きは、別個の磁石( 図示せず )へのピニングを介してなど、多数のやり方で確立できる。フリー層 114 は、レファレンス層 114 の選択された方向に平行( 実線の矢印 )または逆平行( 点線の矢印 )であり得る選択的にプログラム可能な磁性の向きを有する。

10

#### 【 0012 】

フリー層 114 の磁化がレファレンス層 112 の磁化と実質的に同じ方向( 平行 )に向いている場合は、M T J 110 の低抵抗状態が達成される。M T J 110 を平行な低抵抗状態に向けるため、レファレンス層 112 の磁化方向がフリー層 114 の磁性の向きを設定するように書き電流がM T J 110 を通過する。電子は電流の方向と反対方向に流れるので、書き電流の方向がフリー層 114 からレファレンス層 112 へ通り、電子がレファレンス層 112 からフリー層 114 に移動する。

20

#### 【 0013 】

M T J 110 の高抵抗状態は、フリー層 114 の磁化方向がレファレンス層 112 と実質的に反対の逆平行の向きで確立される。M T J 110 を逆平行の抵抗状態に向けるには、スピン偏極電子が反対方向にフリー層 114 に流れ込むように書き電流がレファレンス層 112 からフリー層 114 へM T J 110 を通過する。

#### 【 0014 】

M T J のプログラマブル抵抗の各々に対して異なる論理状態が割当てられる。いくつかの実施形態では、低抵抗平行状態は論理 0 を表わすのに用いられ、高抵抗逆平行状態は論理 1 を表わすのに用いられる。M T J が複数のビットを記憶するように構成される場合、付加的なプログラム状態を用いることができる。たとえば、プログラムされた抵抗 R 1 < R 2 < R 3 < R 4 を、それぞれマルチビット値「 00 」、「 01 」、「 10 」、および「 11 」を記憶するのに用いることができる。

30

#### 【 0015 】

図 3 は、不揮発性メモリセル 120 を有する、図 1 のアレイ 106 の部分を示す。各メモリセル 120 は、金属酸化物半導体電界効果トランジスタ( M O S F E T )として特徴付けられる、スイッチングデバイス 122 に結合される、図 2 に記載されるような M T J 110 を含む。セル 120 は、ワード線 W L 124 をアサートして関連のセルトランジスタ 122 をドレイン - ソース導通状態にすることによって個別にアクセスされる。

40

#### 【 0016 】

プログラミング( 書込 )電流は、それぞれ書き電流ドライバ 126 、 128 によって生成される。書き電流は、ビット線 B L 130 とソース線 S L 132 との間を通過して、選択された M T J 110 を所望のプログラム状態にプログラミングする。選択されたセル 120 のプログラム状態を後で読出すため、関連の W L 124 がアサートされ、読み出電流が読み出電流ドライバ( 別個に図示せず )を通され、セル 110 両端の電圧降下を確立する。この電圧降下はセンス増幅器 134 によって検知され、入力参照電圧 V<sub>REF</sub> と比較される。センス増幅器 134 の出力状態( たとえば、ハイ、ロー )は、選択されたセル 110 の M T J 120 のプログラム状態を示す。

#### 【 0017 】

50

M T J 1 2 0 のプログラム状態を切換える、特に逆平行（高抵抗）状態に切換えるには、プログラミング電流の大きさが大きいものである必要があり得る。これは、比較的大きなセルトランジスタ 1 2 2 の使用を要する可能性があり、このことは達成可能なメモリアレイ密度を限定してしまう。大きなプログラミング電流を使用すると、アレイの動的電力消費もより高くなる結果になり得、コストの高いオンチップ電力供給システムを要し得る。

#### 【 0 0 1 8 】

1 2 0 などの S T R A M M T J のためのスイッチング電流を以下のように表わすことができる。

#### 【 0 0 1 9 】

##### 【 数 1 】

$$\frac{J}{J_c} = 1 - \frac{K_b T}{E} \ln \frac{\tau}{\tau_0} \quad [1]$$

#### 【 0 0 2 0 】

式中、  $J$  はスイッチング電流密度であり、  $J_c$  は 0 K での臨界スイッチング電流密度であり、  $E$  は磁性切換のためのエネルギー障壁であり、  $\tau$  はスイッチング時間であり、  $\tau_0$  は熱的スイッチングのための試行時間であり、  $T$  は K での温度である。スイッチング電流の低減は、駆動パルス幅  $\tau$  の持続時間を増大させることによって吸収可能であるが、このことは全体的なデータスループット率を低減する可能性がある。

#### 【 0 0 2 1 】

スイッチング電流要件を減じる別のやり方は、スイッチングイベントの前に M T J の熱的前処理または局所化加熱によって M T J の温度  $T$  を上昇させることである。しかしながら、多数のセルに対して熱的前処理を大規模に適用すると全体的な電力要件が増大してしまう可能性があり、結果的に、実際には書き込みされない多くのセルの加熱が行なわれてしまうかもしれない。

#### 【 0 0 2 2 】

したがって、本発明のさまざまな実施形態は一般的に、不揮発性アレイ中のメモリセルの確率的（予測的）熱的前処理を提供することに向けられる。以下に説明するように、書き込み動作を受ける第 1 のメモリセルのアドレスを用いて、近い将来に書き込み動作を受け得る第 2 のメモリセルの次のアドレスを予測する。熱的前処理は、第 1 のメモリセルへの状態の書き込みと同時に第 2 のメモリセルに適用される。

#### 【 0 0 2 3 】

このように、第 2 のメモリセルが後で書き込み動作を受ける場合、第 2 のメモリセルに対する書き込み動作は熱的に補助される。すなわち、書き込み動作は第 2 のメモリセルが上昇した温度にある間に行なわれ、これによりプログラム状態を切換えるのに要するスイッチング電流の大きさが小さくなる。

#### 【 0 0 2 4 】

第 2 のメモリセルのアドレスを用いて、熱的に前処理される第 3 のメモリセルに対する書き込み動作を予測することができ、以降も同様である。いくつかの実施形態では、この態様で熱的前処理を用いると、電流要件および書き込み電流パルス幅の両者を低減することができ、これはデータスループット率の向上および減少した電力消費に繋がる。

#### 【 0 0 2 5 】

予測的熱的前処理は、書き込みデータが受信されたメモリセルのアドレスに基づき得る。いくつかの実施形態では、アドレスが N である選択された論理データブロックのセルに対する書き込みコマンドの結果、近い将来ブロック N, N + 1, N + 2 ... に順次書き込みされ得る順次書き込み動作が進行するという推論的予測に基づき、データブロック N + 1 中のセルに対する前処理の適用がなされる可能性がある。

#### 【 0 0 2 6 】

論理データブロック N, N + 1, N + 2 ... は、ホストレベル論理ブロックアドレス ( L )

10

20

30

40

50

B A ) と関連付けられるデータ ( たとえば 512 バイトのユーザデータ ) のアドレス指定可能セクタなどのメモリセルの任意の好適なグループ分けであり得る。データブロックは、32KB メモリユニット中の 1024 バイトのデータ ( 32 行 × 8192 列など ) または同じ行のメモリセルの部分などのアレイ中のメモリセルの行を構成し得る。データブロックは個別のセルとしても規定することができる。

#### 【 0027 】

前処理されたセルは 1 つ以上のアレイ内の任意の選択された場所に位置することができ、前処理を受けなかった書き込みセル ( すなわち、「未処理」または「非前処理」セル ) の初期の組に必ずしも隣接しているわけではないかも知れない。確率的に前処理されているメモリセルの組は、連続した論理アドレス、異なるワード線の論理アドレス、または単一のワード線によって接続されるセルの数未満の多数の論理アドレスを有するメモリセルを備え得る。最初の書き込みブロック N は未処理であり、したがってより遅い速度および / またはより高い電流で書き込まれるが、前処理されたブロック N + 1 などの各々はその後、より高い速度および / またはより低い電流で書き込まれ、その結果、全体的にデータ転送速度がより速くなり、電力消費がより小さくなる。

#### 【 0028 】

再び図 3 を参照して、熱的前処理は、第 2 ( および後続の ) メモリセルに比較的小さな駆動電流を印加することによってなど、多数のやり方で適用可能である。たとえば、図 3 の第 1 の MTJ 110 への書き込み動作は、関連の WL の部分的アサートによってなど、第 2 の MTJ 110 への比較的小さな電流の印加をトリガし得る。

10

#### 【 0029 】

これに代えて、熱的前処理は、選択されると MTJ 110 の温度を上昇させるように構成されるさまざまな構成要素を利用することができます。図 4 は、さらなる実施形態に従う図 1 のメモリアレイ 106 の部分のための構成を示す。図 4 の回路構成は図 3 に記載のものとほぼ同様であり、同じ参考番号を同様の構成要素に用いている。

20

#### 【 0030 】

図 4 では、ダイオード 136 などの熱的補助機構がそれぞれの MTJ 110 に結合され、書き込み動作の前のそれに対する加熱電流の印加を容易にする。ダイオード 136 は、ツェナーダイオード、ショットキーダイオード、およびエサキダイオードなどの、しかしこれらに限定されない任意の数の好適な形態を取ることができる。選択された MTJ 110 が前処理候補として同定される場合、好適な源 ( 図示せず ) によって低レベルの電流がダイオードを通してセル 120 に供給され、MTJ 110 の局所化加熱を与える。

30

#### 【 0031 】

多数の異なる方策を実現して熱的前処理を適用する範囲を限定することができる。いくつかの実施形態では、システムが外部信号を生成して熱処理シーケンスを終了することができる。図 1 の 102 などのコントローラは、書き込み命令および関連の書き込みデータがホストから受信されるたびに先取り前処理シーケンスを維持する熱的前処理アルゴリズム ( TPA ) 138 を実現することができる。

#### 【 0032 】

たとえば、書き込みデータの各受信ブロック毎に、コントローラ 102 は、アレイ 106 に対して、熱的前処理されるべきいくつかの選択された数の付加的な連続したブロックを同定することができ、このことはホストからそれ以上書き込み命令が受信されなくなるまで継続する。コントローラ 102 は書き込み動作が終了することをアレイ 106 にさらに信号で知らせることができ、これによりいずれの進行中の前処理動作も終了する。

40

#### 【 0033 】

代替的な実施形態では、タイミング制御のために、図 1 のカウンタ回路 140 で示されるものなどのカウンタを各メモリブロック ( または複数の隣接するメモリブロック ) 每に追加することができる。書き込み命令の継続した受信によりタイマを再始動させることができる、または新しいタイマを用いてカウントを開始することができる。多数のカウントされたクロックサイクルが予め定められた経過時間しきい値に達すると、適用され

50

た熱的補助を除去することができる。

#### 【0034】

図1のアレイ106中のタイミング回路142を介して別のタイミング制御機構を実現可能である。図5に示されるように、いくつかの実施形態では、タイミング回路142は、RC遅延による電圧放電を検出するように一般的に動作し、減衰するRC電圧が予め定められたしきい値に達すると熱的前処理のそれ以上の適用を終了するRCベースの回路として特徴付けられ得る。

#### 【0035】

図5のタイミング回路142は減衰回路144とレベル変換器146とを含む。インバータ148はそれぞれの減衰回路144とレベル変換器146との間に結合される。減衰回路144は、トランジスタ150、152と、コンデンサ154とを含む。コンデンサ154は、レール電圧(この場合1.5V)およびワード線WL156に関連して電圧 $V_{CAP}$ を蓄積する。放電線158は、 $V_{DISCHARGE}$ 入力を介した接地160への $V_{CAP}$ 電圧のRC放電を容易にする。

10

#### 【0036】

レベル変換器146は、トランジスタ162、164、166および168と、レール電圧1.0Vと-1.0Vとの間に示されるように交差接続されたインバータ170とを含む。コンデンサ154に蓄積された電圧 $V_{CAP}$ がインバータ150のしきい値入力を一旦下回ると、経路172上の出力の変化がプレチャージ動作の終了を信号で知らせる。本明細書中で企図されるようなこれらおよび他の関連のタイミング機構において経過時間間隔を予め規定することができ、データが書き込まれていないあらゆる前処理されたセルの時間間隔の終わりに前処理が終了されることが認められる。これは電力消費を低減するようさら働く。というのも、不要な前処理電流の発生を低減することができるからである。

20

#### 【0037】

図6は、さまざまな実施形態に従って実行されるステップを一般的に図示する、予測的熱的前処理ルーチン180を記載する。図6のルーチンは、図1のコントローラ102などの好適な制御回路によって実行されることが企図される。ステップ182で、書き込みコマンドは、図1の100などのデバイスによって受信され、選択されたブロックアドレスにある選択されたブロックにある106などのアレイにデータを書込む。デバイスは、ステップ184で書き込みコマンドを実行し、選択されたブロックアドレスを同時に用いて、近い将来書き込み動作を受けるかもしれない後続のブロックアドレス(または複数のアドレス)を同定するように進める、ステップ186。デバイスは、ステップ184で選択されたブロックに書き込む間に、ステップ188で、後続のブロックアドレス(または複数のアドレス)に熱的前処理を同時に適用するように進める。

30

#### 【0038】

決定ステップ188は、付加的な書き込みコマンドがホストによって受信されたか否かを判断する。このコマンドは、後続のブロックアドレスまたは何らかの他のブロックアドレスに対するものであり得る。そうである場合、ルーチンはステップ190に移ってもよく、ここで、付加的な書き込みコマンドは、「選択されたブロックアドレス」にある「選択されたブロック」として扱われ、示されるようにフローが戻る。ルーチンは、付加的な書き込みコマンドが受信されなくなるまでこのように継続し、この時点でそれ以上の前処理が終了される、ステップ192。

40

#### 【0039】

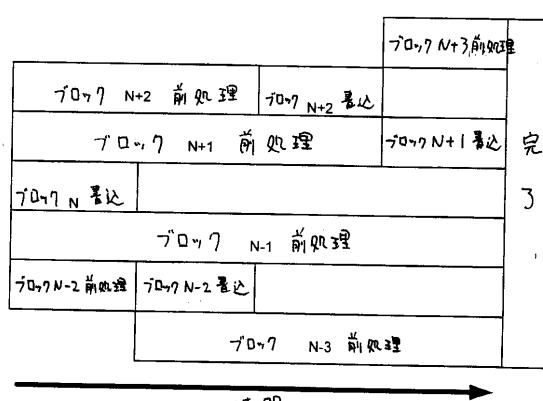

図7は、いくつかの実施形態に従うアレイ中の予測的前処理のための、図6のルーチン180に対応するタイミングシーケンスを与える。第1のメモリブロックNにデータを書き込む際、熱的前処理は次のメモリブロックN+1およびN+2に同時に適用される。ブロックN+1へのその後の書き込み動作の結果、ブロックN+2の継続した前処理+後続のブロックN+3の同時の前処理が行なわれ、以降も同様である。この処理は必要に応じて継続するまたはタイムアウトになり得る。

50

**【 0 0 4 0 】**

図 8 は代替的なタイミングシーケンスを示す。第 1 のメモリブロック N への書き動作の結果、選択された範囲のブロック N + 1、N + 2 および N + 3 に予測的熱的前処理が適用される。熱的処理は、書き動作がこれらのブロックの各々に対して実行されるまたはタイムアウト条件が宣言されるまで、これらのブロックの各々に適用されたままとなる。

**【 0 0 4 1 】**

なお、これらの他のブロックに対するその後の書きの実行はさらなる前処理の作業をトリガするわけではなく、たとえば、前処理されたブロック N + 1、N + 2 または N + 3 への書きは、ブロック N + 4、N + 5 などのさらなる前処理をトリガするように働かないことが留意される。むしろ、設定されたブロックの範囲はまず初期未処理ブロックアドレスに基づいて前処理され、これらのブロックに対して書きが実行されるか、または適切なタイムアウト期間の終わりに前処理が終了する。前処理を経た所与のブロックへの実際の書きは、そのブロックのさらなる前処理を終了させるように働いてもよい。しかしながら、特に複数の更新された書きが予期される（または検出される）場合は、そのようなことが必ずしも要件とされるわけではない。

10

**【 0 0 4 2 】**

図 8 の異なるブロック X への新たな書きコマンドの受信の結果、同様に、ブロック X + 1、X + 2、および X + 3 にデータが書き込まれるまたはタイムアウト条件が宣言されるまで、これらに対して連続した熱的前処理が適用される。

20

**【 0 0 4 3 】**

メモリアレイ中への順次書きは、予期される増分していく書きシーケンス（たとえば、ブロック N、N + 1、N + 2、N + 3 …）にしばしば基づくことが企図される一方で、上記方策は他の条件に適合可能であることが認められる。ブロックアドレスが減少していくシーケンス（たとえば、ブロック N、N - 1、N - 2、N - 3）が検出されてもよく、その結果、ブロックの予測的前処理はアドレスが減少していく方向に行なわれる。順番になつていなない書きコマンドを受信すると、所与の範囲内の関連のブロックの十分な時間的および空間的局所性を考慮して、その範囲内の他のブロックへの予測的前処理が選択される結果となり得る。

**【 0 0 4 4 】**

デバイス 100 が維持するファイル割当テーブル（FAT）または他のデータ構造は、さもなければ非ローカルなアドレスを有するブロックのための論理関連性情報を与えてよい。たとえば、所与のデータ構造は、ブロック N、N + 2、N + 6、N + 17 などのブロックのグループングのより高レベルの関連性を与えてよい。このように、たとえば N + 2 などのグループ内の選択されたブロックに対する書き動作は、そのようなデータ構造（たとえば、ブロック N、N + 6、N + 17 …）によって同定されるような他のアドレスにある他のブロックについての前処理決定をもたらし得る。

30

**【 0 0 4 5 】**

以上の考察は 106 などのメモリアレイ中のセルに対する予測的書き前処理の適用を企図したが、そのような前処理はキャッシュなどの他の種類のメモリ構造中のセルに容易に適用可能である。認められるように、100 などのデバイスはそのようなキャッシュを利用して、ホストとアレイ 106 との間の転送の際にデータの中間記憶を提供することができる。

40

**【 0 0 4 6 】**

1 つのそのようなキャッシュは I / F 104 中のデータバッファであり得、これは、アレイ 106 への符号化および記憶を待っている入力ユーザデータを一時的に記憶し、ホストへの転送を待っているアレイから検索されたリードバックデータを記憶する。局所化キャッシュは、L1、L2 および / または L3 キャッシュなどのコントローラレベルに設けられて、データおよび / またはプログラミング命令もしくはステータスデータなどの情報を制御してもよい。

**【 0 0 4 7 】**

50

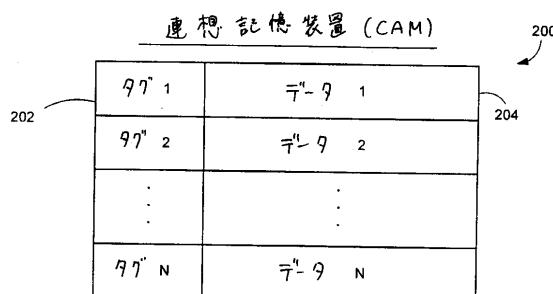

図9は、連想記憶装置（C A M）構成を有する連想記憶200（キャッシュ）の機能的表示を与える。C A Mベースの連想記憶は、コンピュータシステムキャッシュ、ネットワークルータ、およびさまざまな埋込アプリケーションなどの多数の適用例における広範な使用を見出した。

#### 【0048】

キャッシュ200は、各々がインデックスフィールド202およびワードデータフィールド204を有する多数のキャッシュ線（行）を有するように配置される。インデックスフィールド202は、フィールド204中の関連のワードデータの識別子として働くタグデータを記憶する。タグデータは任意の数の所望の形態を取ることができ、（アレイ106などのメモリ中の別の場所のロックアドレスなどの）ワードデータの何らかの他のアドレスと関連付けられるマルチビット値として表現することができる。10

#### 【0049】

キャッシュ200は一般的に、それぞれのインデックスフィールド202中のタグデータと迅速に比較される入力サーチデータを証明することによって、データ検索動作の際にアクセスされる。一致が見つかると、関連のワードデータフィールド204から対応のワードデータが出力される。キャッシュ200のサイズおよび配置に依存して、単一のクロックサイクルにわたってサーチを実行することができ、C A M構造を多くの他のハードウェアまたはソフトウェアベースのサーチシステムよりも高速にする。

#### 【0050】

200などのキャッシュ中のデータにはしばしば、データが記憶されるキャッシュ中の場所に対する時間的局所性が与えられる。これは、データが与えられたシーケンスに関連して、データがキャッシュ内で順に順序付けられ得るからである。さらに、複数のデータ行は、負荷要件に依存して、データ群がキャッシュに移動されるのと同時にキャッシュされてもよい。このように、特定的なキャッシュ線に対する書き動作の後に、近い将来、書き込まれたキャッシュ線に先行するおよび／またはその後続のキャッシュ線に対してその後の書き動作が行なわれてもよい。20

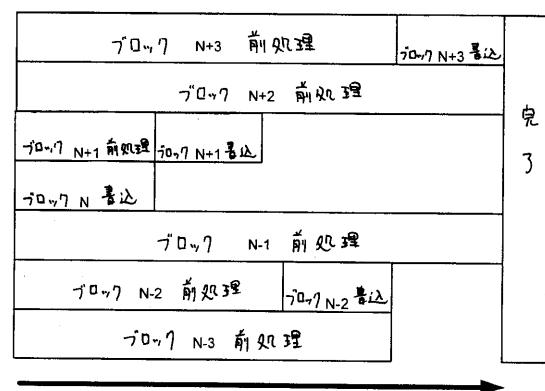

#### 【0051】

図10のタイミング図に従って、200などのキャッシュに前処理を適用可能である。図10では、書きコマンドが実行され、選択されたワードデータ線204に新たなデータが書き込まれる。これらのデータは、本明細書中ではアドレスNと称される関連のロックアドレスを有する。アドレスNは、局所化キャッシュアドレス（たとえばインデックスフィールド202を介した行インジケータ）であってもよく、または、ホストレベルのLBA、アレイレベルの行ロックアドレスなどのグローバルロックアドレスであってもよい。30

#### 【0052】

図10では、キャッシュ200中のロックNへのデータの書きの結果、ロックNのアドレスに先行するおよびそれに引き続くロック、すなわちロックN-2、N-1、N+1、およびN+2に対する予測的熱的前処理動作が同時に実行される。非対称範囲（たとえばロックN-3からN+4など）を含む他の範囲を用いることができる。キャッシュ200へのデータの書きの結果、アレイ106の場合のように、既存のデータの上書きが行なわれてもよいことが認められる。40

#### 【0053】

ロックN-2に対するデータのその後の書きはロックN-3の同時前処理を開始させ、ロックN+2に対するデータのその後の書きはロックN+3の前処理を開始させる。以前のように、書き込まれた第1のロック（ロックN）は未処理であり、したがってよりゆっくりである、および／またはより高い書き電流を要するが、前処理により前処理ロックのその後の書き効率がより高くなる。図1、図4、および図5中の以上で論じたさまざまな機構138、140、および／または142などの好適なタイミング機構を用いて、書き動作が一旦停止するとさらなる前処理の作業を止める。

#### 【0054】

図11は、200などのキャッシュにデータを書込むための代替的なタイミングシーケンスを与える。図11で、未処理ブロックNに対する初期の書込の結果、ブロックN-3からN+3のより大きな範囲の前処理が行なわれる。しかしながら、これらの他のブロックへのその後の書込は、それ以上の前処理の作業をトリガしない。以前のように、前処理は能動的に終了されるまで継続する。

#### 【0055】

当業者には認められ得るように、本明細書中に図示されるさまざまな実施形態は、前処理されたメモリセルに対するデータの書込によるメモリセル効率および精度の両者において利点を与える。将来の書込動作の予測に基づいて前処理されるべきセルのみを賢明に選択することにより、実質的な電力および時間の節約を経験することができる。タイミング機構を用いることにより、変化するデータ負荷条件に応答してそれ以上の前処理を終了するやり方を設けることによって、電力および時間の節約がさらに与えられる。本明細書中で論じたさまざまな実施形態は数多くの潜在的な適用例を有し、ある分野の電子媒体またはデータ記憶デバイスの種類に限定されるものではない。

10

#### 【0056】

添付の請求項の目的のため、「同時に」という用語などは、そのような動作が個別に異なる時間に開始または終了したとしても、時間的に重なる動作を記載する上記考査と矛盾しないと解釈される。「未処理」という用語などは、メモリセルへの書込動作直前に熱的前処理が適用されていないメモリセルを記載する上記考査と矛盾しないと解釈される。

20

#### 【0057】

以上の説明において、本発明のさまざまな実施形態の数多くの特性および利点を発明のさまざまな実施形態の構造および機能の詳細とともに述べたが、この詳細な説明は例証のためのみのものであり、添付の請求項に表現される用語の広い一般的な意味によって示される全範囲に、詳細、特に本発明の原則の範囲内の部品の構造および配置の点で変更がなされてもよいことを理解すべきである。

#### 【図1】

FIG. 1

#### 【図4】

FIG. 4

#### 【図5】

FIG. 5

#### 【図2】

FIG. 2

#### 【図3】

FIG. 3

【図 6】

【図 7】

【図 8】

【図 9】

【図 10】

【図 11】

---

フロントページの続き

(72)発明者 リュウ , ハリー・ホンギュ

アメリカ合衆国、55311 ミネソタ州、メープル・グローブ、シックスティフィフス・アベニ

ュ・ノース、18540

(72)発明者 ディミトロフ , ディミタール・ブイ

アメリカ合衆国、55439 ミネソタ州、エディナ、シックスティエイトス・ストリート・ウェ

スト、5709

(72)発明者 ワン , アラン・シュグアン

アメリカ合衆国、55346 ミネソタ州、エデン・プレーリー、アシュビー・レーン、1653

5

(72)発明者 ワン , シャオビン

アメリカ合衆国、55317 ミネソタ州、チャンハッセン、ブラフ・リッジ・コート、180

審査官 滝谷 亮一

(56)参考文献 特開2002-245774 (JP, A)

特開2004-172614 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G11C 11/15