(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2012년02월27일

(11) 등록번호 10-1112046

(24) 등록일자 2012년01월27일

(51) Int. Cl.

H01L 21/336 (2006.01)

(21) 출원번호 10-2006-7008094

(22) 출원일자(국제출원일자) 2004년10월08일

심사청구일자 2009년10월07일

(85) 번역문제출일자 2006년04월26일

(65) 공개번호 10-2006-0108629

(43) 공개일자 2006년10월18일

(86) 국제출원번호 PCT/US2004/033251

(87) 국제공개번호 WO 2005/048339

국제공개일자 2005년05월26일

(30) 우선권주장

10/699,887 2003년11월04일 미국(US)

(56) 선행기술조사문현

US20020130354 A1\*

US06583469 B1

US20020140039 A1

\*는 심사관에 의하여 인용된 문현

(73) 특허권자

글로벌파운드리즈 인크.

케이만 아일랜드 케이와이1-1104 그랜드 케이만

어그랜드 하우스 피.오.박스 309 메이플즈 코포레

이트 서비스 리미티드

(72) 발명자

태버리 사이러스 이.

미국 캘리포니아 95050 산타 클라라 면로 #366

2250

아메드 쉬브리 에스.

미국 캘리포니아 95134 산 호세 엘란 빌리지 레인

#105 350

(뒷면에 계속)

(74) 대리인

박장원

전체 청구항 수 : 총 9 항

심사관 : 박근용

(54) 자기 정렬된 다마신 게이트

(57) 요약

금속-산화물 반도체 전계-효과 트랜지스터(MOSFET)(200)를 형성하기 위한 방법은 기판상의 핀 영역, 소스 영역 및 드레인 영역을 패턴화하는 단계와, 상기 핀 영역에 핀(310)을 형성하는 단계와, 그리고 상기 핀 영역에 마스크(320)를 형성하는 단계를 포함한다. 상기 방법은 마스크(320)를 식각하여 MOSFET(200)의 채널 영역(330)을 노출하는 단계와, 핀(310)을 식각하여 채널 영역(330)에서 핀(310) 폭을 얇게 하는 단계와, 핀(310) 위에 게이트를 형성하는 단계와, 그리고 게이트, 소스 영역 및 드레인 영역에 접촉들을 형성하는 단계를 더 포함한다.

## 대 표 도

(72) 발명자

바이노스키 매튜 에스.

미국 캘리포니아 94306 팔로 알토 에머슨 스트리트

2607

다크쉬나-머피 스리칸테스바라

미국 뉴욕 12590 와펑거스 폴스 타운뷰 드라이브

258

크리보카 피크 조란

미국 캘리포니아 95050 산타 클라라 데 바로나 플

레이스 2321

---

왕 하이홍

미국 캘리포니아 95035 밀피타스 아파트 티303 밀

몬트 드라이브1775

양 치유

미국 캘리포니아 95129 산 호세 리틀 존 웨이 1144

유 빈

미국 캘리포니아 95014 쿠파르티노 포피 웨이 1373

## 특허청구의 범위

### 청구항 1

금속-산화물 반도체 전계-효과 트랜지스터(MOSFET)(200)를 형성하는 방법에 있어서,

기판 상에 핀(fin)(310)을 형성하는 단계와;

상기 기판 상에 마스크(320)를 형성하는 단계와;

상기 마스크(320)를 식각하여 상기 MOSFET(200)의 채널 영역(330)을 노출하는 단계와;

상기 채널 영역(330)에서 상기 핀(310)의 폭을 얇게 하는 단계와, 여기서 상기 핀(310)의 폭을 얇게 하는 단계는 불소(F) 플라즈마 공정을 사용하여 상기 핀(310)의 하나 이상의 표면들을 식각하는 것을 포함하며; 그리고

상기 핀(310) 위에 게이트를 형성하는 단계를 포함하여 구성되며, 여기서 상기 게이트는 상기 핀(310)의 각 측부 상에서 연장(extending)되며,

상기 마스크를 형성하는 단계는 상기 기판 위에 다마신 물질을 중착하는 단계를 포함하는 것을 특징으로 하는 MOSFET 형성 방법.

### 청구항 2

제 1 항에 있어서,

상기 기판 상에 핀(310)을 형성하는 단계 이전에,

핀 영역, 소스 영역 및 드레인 영역을 패터닝(patterning)하는 단계를 더 포함하는 것을 특징으로 하는 MOSFET 형성 방법.

### 청구항 3

제 2 항에 있어서,

상기 핀(310) 위에 게이트를 형성하는 단계 이후에,

상기 기판 상에 실리사이드 물질을 형성하는 단계와; 그리고

상기 실리사이드 물질을 통하여 게이트 접촉부, 소스 접촉부 및 드레인 접촉부를 형성하는 단계를 더 포함하는 것을 특징으로 하는 MOSFET 형성 방법.

### 청구항 4

삭제

### 청구항 5

제 1 항에 있어서, 상기 게이트를 형성하는 단계는,

상기 다마신 물질을 식각하여 게이트 영역을 형성하는 단계와;

상기 핀(310)의 측면들상에 게이트 유전체(510)를 형성하는 단계와; 그리고

게이트 전극 물질(520)을 중착하여 상기 게이트 영역을 적어도 부분적으로 채우는 단계를 포함하는 것을 특징으로 하는 MOSFET 형성 방법.

### 청구항 6

제 1 항에 있어서, 상기 핀(310)의 폭을 얇게 하는 단계는,

상기 핀(310)의 폭을 측부 당(per side) 100Å 내지 200Å을 제거하는 단계를 포함하는 것을 특징으로 하는 MOSFET 형성 방법.

**청구항 7**

금속-산화물 반도체 전계-효과 트랜지스터(MOSFET)(200)를 형성하는 방법에 있어서,

기판 상에 핀 영역, 소스 영역 및 드레인 영역을 패터닝하는 단계와;

상기 핀 영역에 핀(310)을 형성하는 단계와;

상기 핀 영역에 마스크(320)를 형성하는 단계와;

상기 MOSFET(200)의 채널 영역(330)을 노출하기 위해 상기 마스크(320)를 식각하는 단계와;

상기 채널 영역(330)에서 상기 핀(310)의 폭을 얇게 하기 위해 상기 핀(310)을 식각하는 단계와, 여기서 상기 핀(310)의 폭을 얇게 하기 위해 상기 핀(310)을 식각하는 단계는, 상기 핀(310)을 식각하기 위해 불소(F) 플라즈마 공정을 사용하는 단계와 상기 핀(310)을 식각하기 위해 브롬화수소(HBr) 기반 플라즈마 화학제를 사용하는 단계 중 적어도 하나를 포함하며;

상기 핀(310) 위에 게이트를 형성하는 단계와; 그리고

상기 게이트, 상기 소스 영역 및 상기 드레인 영역에 접촉부들(610 내지 630)을 형성하는 단계를 포함하여 구성되며,

상기 마스크(320)를 형성하는 단계는 상기 기판 위에 다마신 물질을 증착하는 단계를 포함하는 것을 특징으로 하는 MOSFET 형성 방법.

**청구항 8**

삭제

**청구항 9**

제 7 항에 있어서, 상기 게이트를 형성하는 단계는,

상기 다마신 물질을 식각하여 게이트 영역을 형성하는 단계와;

상기 핀(310)의 측면들상에 게이트 유전체(510)를 형성하는 단계와; 그리고

게이트 전극 물질(520)을 증착하여 상기 게이트 영역을 적어도 부분적으로 채우는 단계를 포함하는 것을 특징으로 하는 MOSFET 형성 방법.

**청구항 10**

제 7 항에 있어서, 상기 핀(310)을 식각하는 단계는,

상기 핀(310)의 폭을 측부 당 100Å 내지 200Å을 제거하는 단계를 포함하는 것을 특징으로 하는 MOSFET 형성 방법.

**청구항 11**

금속-산화물 반도체 전계-효과 트랜지스터(MOSFET)(200)를 형성하는 방법에 있어서,

기판 상에 핀(310)을 형성하는 단계와;

상기 기판상에 마스크(320)를 형성하는 단계와;

상기 MOSFET(200)의 채널 영역(330)을 노출하기 위해 상기 마스크(320)를 식각하는 단계와;

상기 채널 영역(330)에서 상기 핀(310)의 폭을 얇게 하는 단계와, 여기서 상기 핀(310)의 폭을 얇게 하는 단계는 브롬화수소(HBr) 기반 플라즈마 화학제를 사용하여 상기 핀(310)을 식각하는 단계를 포함하며; 그리고

상기 핀(310) 위에 게이트를 형성하는 단계를 포함하여 구성되며, 여기서 상기 게이트는 상기 핀(310)의 각 측부 상에서 연장되며,

상기 마스크(320)를 형성하는 단계는 상기 기판 위에 다마신 물질을 증착하는 단계를 포함하는 것을 특징으로 하는 MOSFET 형성 방법.

## 청구항 12

삭제

## 명세서

## 기술분야

[0001] 본 발명은 일반적으로 반도체 디바이스들에 관한 것으로서, 보다 구체적으로는, 자기 정렬된 다마신 게이트(damascene gate)를 갖는 금속-산화물 반도체 전계-효과 트랜지스터(MOSFET) 디바이스들 및 이러한 디바이스들의 제조 방법들에 관한 것이다.

## 배경기술

[0002] 디바이스 치수들의 스케일링은 집적회로 성능에서의 개선 및 집적회로 비용에서의 감소를 가져오는 주요한 인자가 되었다. 게이트-산화물 두께들 및 소스/드레인(S/D) 접합 깊이들과 관련된 제한들 때문에,  $0.1 \mu\text{m}$  공정 세대 이하의 기준의 벌크 MOSFET 디바이스들의 스케일링이 불가능한 것은 아니지만 어렵게 될 수 있다. 따라서, 새로운 디바이스 구조들 및 새로운 물질들이 FET 성능을 개선하는데에 필요하게 될 것이다.

[0003] 이중-게이트 MOSFET들이 기존의 플래너 MOSFET들을 제거하기 위한 후보 디바이스들을 대표한다. 이중-게이트 MOSFET들에서, 채널을 제어하기 위한 2개의 게이트들의 사용은 단채널 효과들을 크게 억제한다. FinFET은 수직 펀(fin)으로 형성된 채널을 포함하는 이중-게이트 구조이다. FinFET은 비록 이중-게이트 구조이지만, 레이아웃 및 제조 기법들에서 기존의 플래너 MOSFET들과 유사하다. 또한, FinFET은 다른 이중-게이트 구조들과 비교할 때, 일정 범위의 채널 길이들, CMOS 호환성, 및 큰 패킹 밀도를 제공한다.

## 발명의 상세한 설명

[0004] 본 발명의 원리들과 관련된 구현들은 자기 정렬된 게이트 마스크로 형성된 다마신 게이트를 포함하는 FinFET 디바이스들 및 이러한 디스바이들의 제조 방법들을 제공한다.

[0005] 본 발명의 원리들과 관련된 일 양상에서, 금속-산화물 전계-효과 트랜지스터(MOSFET)를 형성하기 위한 방법은 기판상에서 펀(310) 영역, 소스 영역 및 드레인 영역을 패턴화하는 단계와; 상기 펀(310) 영역에 펀(310)을 형성하는 단계와; 그리고 상기 펀(310) 영역에 마스크를 형성하는 단계를 포함한다. 상기 방법은 상기 마스크를 식각하여 상기 MOSFET의 채널 영역을 노출하는 단계와, 상기 펀(310)을 식각하여 상기 채널 영역에서 상기 펀(310)의 폭을 얇게 하는 단계와, 상기 펀 위에 게이트를 형성하는 단계와, 그리고 상기 게이트, 상기 소스 영역 및 상기 드레인 영역에 접촉들(contact)을 형성하는 단계를 더 포함한다.

[0006] 본 발명의 원리들과 관련된 다른 양상에서, MOSFET 형성 방법은 기판상에 펀(310)을 형성하는 단계와; 상기 기판상에 마스크를 형성하는 단계와; 상기 마스크를 식각하여 상기 MOSFET의 채널 영역을 노출하는 단계와; 상기 채널 영역에서 상기 펀(310)의 폭을 얇게 하는 단계와; 그리고 상기 펀 위에 게이트를 형성하는 단계를 포함하며, 여기서 상기 게이트는 상기 펀의 각 측부 상에서 연장(extending)된다.

[0007] 본 발명의 원리들과 관련된 또 다른 양상에서, MOSFET는 기판상에 형성된 대략  $100\text{ \AA}$  내지  $400\text{ \AA}$ 의 폭을 갖는 펀(310)과, 상기 펀의 측면들 상에 형성된 게이트 유전체(dielectric)와, 그리고 상기 펀을 덮어 형성된 게이트 전극을 포함한다.

## 실시예

[0014] 본 발명과 관련된 구현들의 하기의 상세한 설명은 첨부 도면들을 참조로 하여 행해진다. 서로 다른 도면들에서의 동일한 참조번호들은 동일하거나 유사한 요소들을 나타낸다. 또한, 하기의 상세한 설명은 본 발명을 제한하지 않는다. 대신에, 본 발명의 범주는 첨부된 청구범위 및 그 균등물들에 의해 정의된다.

[0015] 본 발명의 원리들과 관련된 구현들은 자기 정렬된 다마신 게이트를 포함하는 FinFET 디바이스들 및 이 디바이스들을 제조하는 방법들을 제공한다. 이러한 FinFET 디바이스들은 여러 이점들을 갖는다. 예컨대, 단지 펀(310)의 활성 영역만이 최소 채널 길이에 있으며, 이는 소스/드레인 저항을 감소시킨다. 또한, 게이트는 최소 채널 영역에 자기 정렬되며, 이는 디바이스의 기생 소스/드레인 저항을 크게 감소시킨다. 전통적인 FinFET 방식들에서, 협 채널은 통상적으로 게이트-대-펀(310) 오버레이 공차를 고려하도록 게이트 길이보다 훨씬 길다. 또한, 게이

트 패턴화가 플래너 기판상에서 수행되는데(예를 들어, 연마 다마신 물질), 이는 어그레시브 리소그래피 (aggressive lithography) 방식들의 초점 깊이가 폐 낮아지는 경향이 있기 때문에 리소그래피 마진을 증가시킨다. 또한, 레지스트 코팅이 평탄화된 표면상에 있기 때문에, 토포그래피 (topography)에서의 레지스트 두께 변화들로 인한 임계 치수 변화(즉, CD swing)를 피할 수 있다.

[0016]

### 예시적인 MOSFET

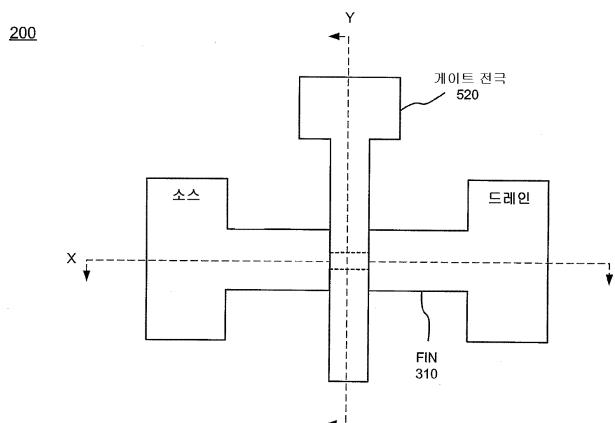

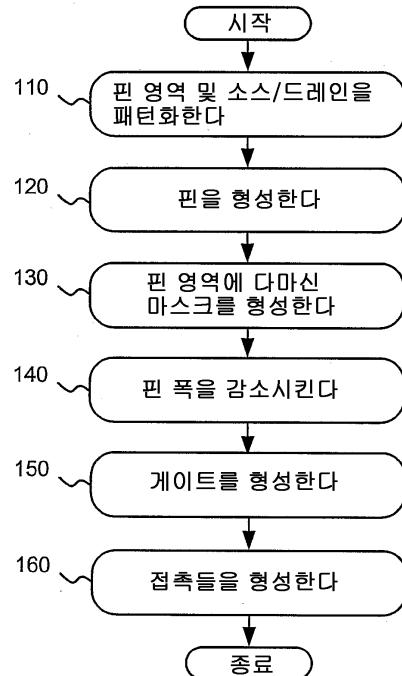

도 1은 본 발명의 원리들과 관련된 구현에 따라 MOSFET를 제조하는 예시적인 공정을 도시한다. 도 2A 내지 6C는 도 1에 관하여 설명되는 공정에 따라 제조된 MOSFET의 예시적인 평면도 및 단면도들을 도시한다.

[0018]

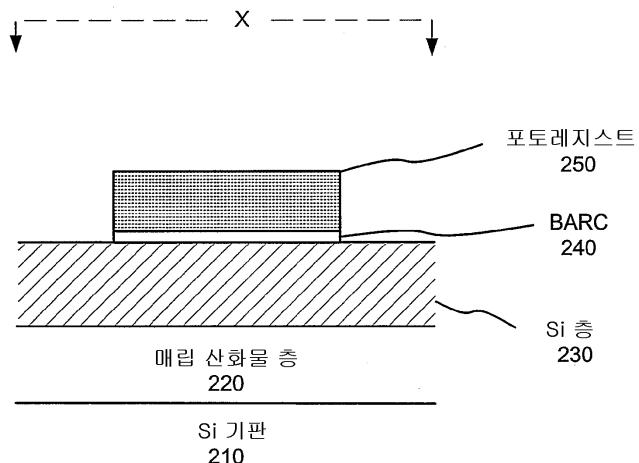

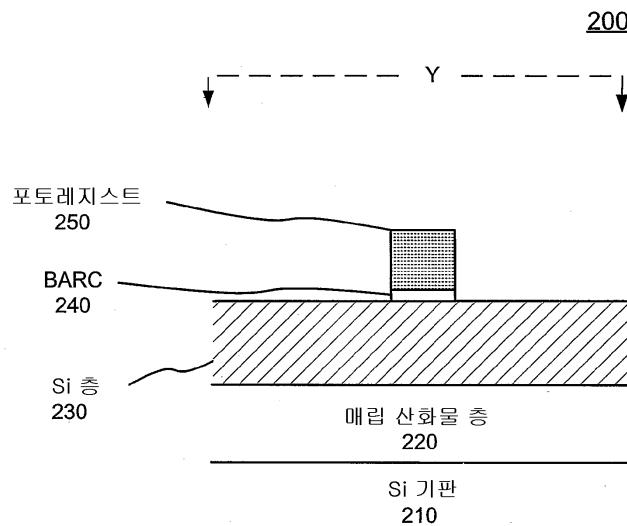

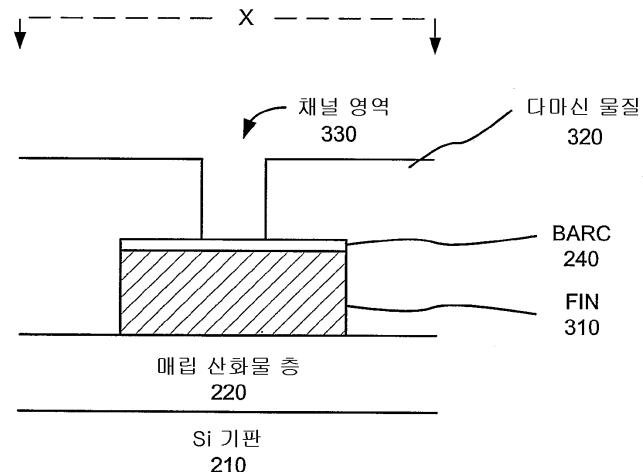

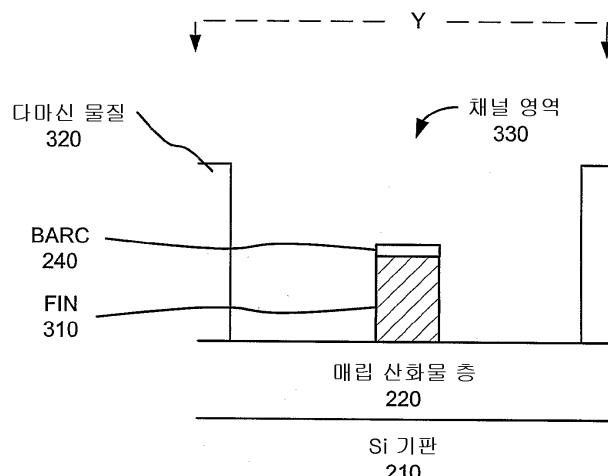

도 1 및 도 2A 내지 2C를 참조하면, 공정은 반도체 디바이스(200)로부터 시작한다. 도 2A 및 2B의 단면도들에서 도시된 바와같이, 반도체 디바이스(200)가 실리콘(Si) 기판(210), 매립된 산화물 층(220) 및 이 매립된 산화물 층(220) 상의 실리콘 층(230)으로 구성되는 실리콘 온 인슬레이터(SOI) 구조를 포함할 수 있다. 매립된 산화물 층(220) 및 실리콘 층(230)은 종래 방식으로 기판(210)상에 형성될 수 있다. 매립된 산화물 층(220)의 두께는 예를 들어, 대략 1,000Å 내지 10,000Å의 범위일 수 있다. 실리콘층(230)의 두께는, 예를 들어, 대략 400Å 내지 1,500Å의 범위일 수 있다. 두께 증가는 디바이스 폭 증가(즉, 펀(310)의 측벽을 따라 많은 전류가 흐르게 된다) 및 이에 따른 높은 구동 전류(MOSFET에서,  $I \propto W/L$ )를 야기하기 때문에, 실리콘 두께는 가능한한 두껍게 될 수 있다. 통상적으로, 종래 FinFET 방식에서 두꺼운 실리콘 두께를 사용하는 것은 어려운데, 그 이유는 이것 역시 게이트 리소그래피 단계에서 더 큰 단계 및 불충분한 리소그래피 마진을 야기하기 때문이다.

[0019]

실리콘층(230)이 펀을 형성하는데에 사용된다. 대안적인 구현들에서, 기판(210)과 층(230)은 게르마늄과 같은 다른 반도체 물질들, 또는 실리콘-게르마늄과 같은 반도체 물질들의 조합들을 포함할 수 있다. 매립된 산화물층(220)은 실리콘 산화물 또는 다른 타입들의 유전체 물질들을 포함할 수 있다.

[0020]

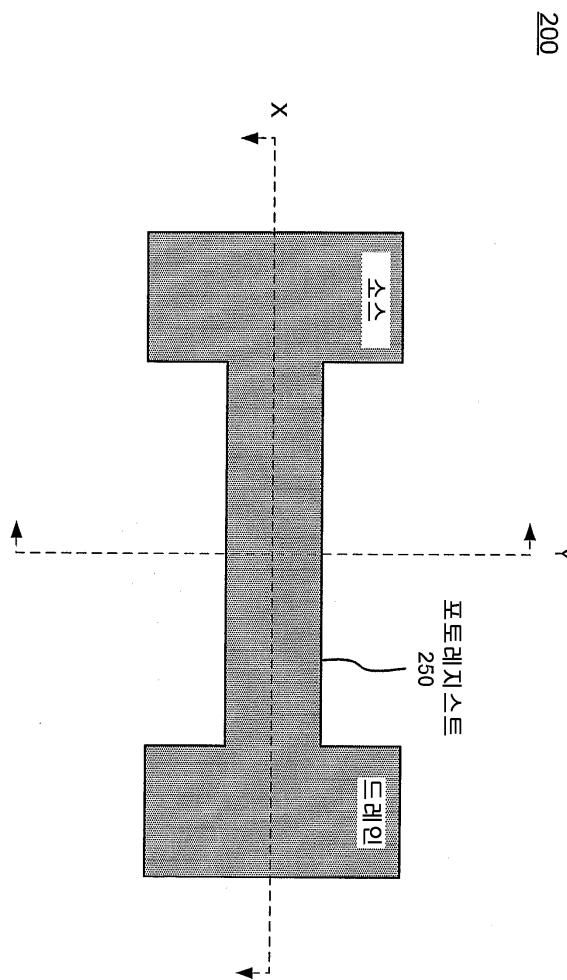

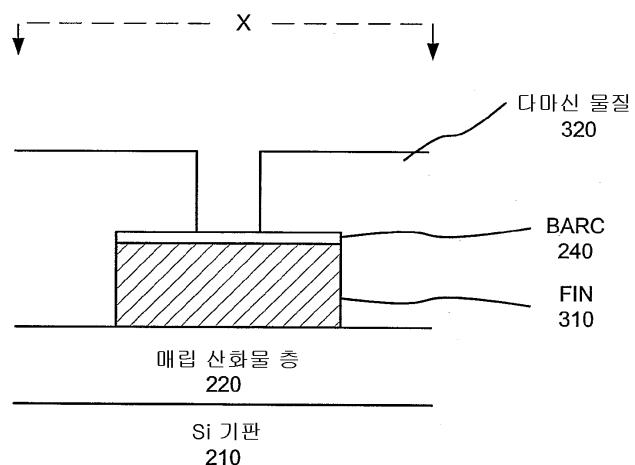

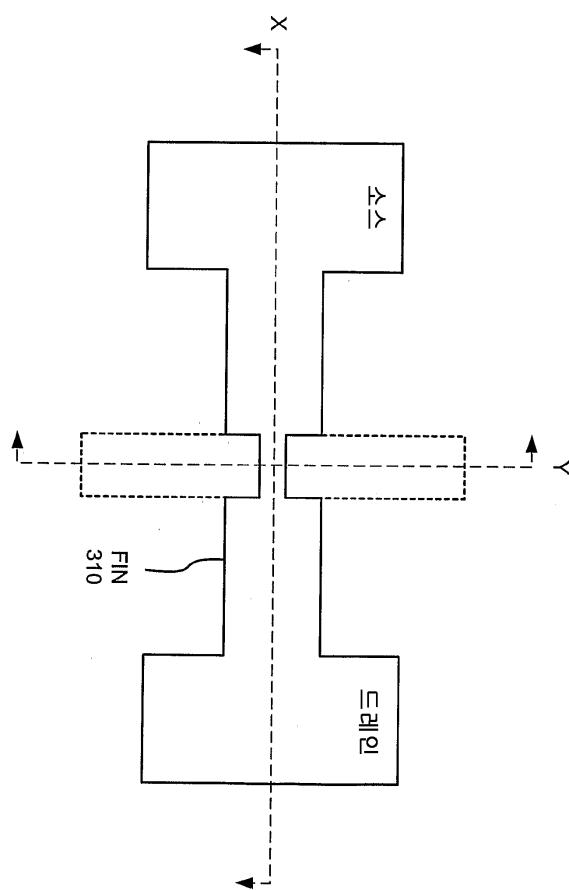

실리콘 질화물, 또는 다른 타입의 물질이 실리콘층(230) 상에 형성될 수 있으며, 이는 도 2A 및 2B에서 도시된 바와같이 후속 공정을 위한 바닥부 반사방지 코팅(BARC)(240)으로서 작용할 수 있다. BARC 층(240) 두께는 대략 150Å 내지 350Å의 범위가 될 수 있다. 도 2A 내지 2C에 도시된 바와같이, 포토레지스트(250)(또는 유사한 것)이 증착되고 패턴화되어 큰 펀(310) 영역 및 소스 및 드레인 영역들의 형성을 용이하게 한다(동작단계 110). 포토레지스트(210)가 대략 1,000Å 내지 4,000Å 범위의 두께로 증착될 수 있다. 도 2C는 도 2A 내지 2B의 반도체 디바이스(200)의 평면도를 도시한다. 도 2A의 단면도는 도 2C의 라인(X)을 따라 절취한 것이고, 도 2B의 단면도는 도 2C의 라인(Y)을 따라 절취한 것이다.

[0021]

실리콘층(230)이 도 3A 및 3B에 도시된 바와같이 식각되어 펀(310)을 형성한다(동작단계 120). 예컨대, 포토레지스트(250) 아래에 위치되지 않은 실리콘층(230)의 일부가 식각될 수 있으며, 이는 매립된 산화물층(220) 상에서 종료한다. 이후에, 포토레지스트(250)는 제거된다. 도 3B에 도시된 바와같이, 펀(310)의 폭이 대략 500Å 내지 800Å의 범위가 될 수 있다.

[0022]

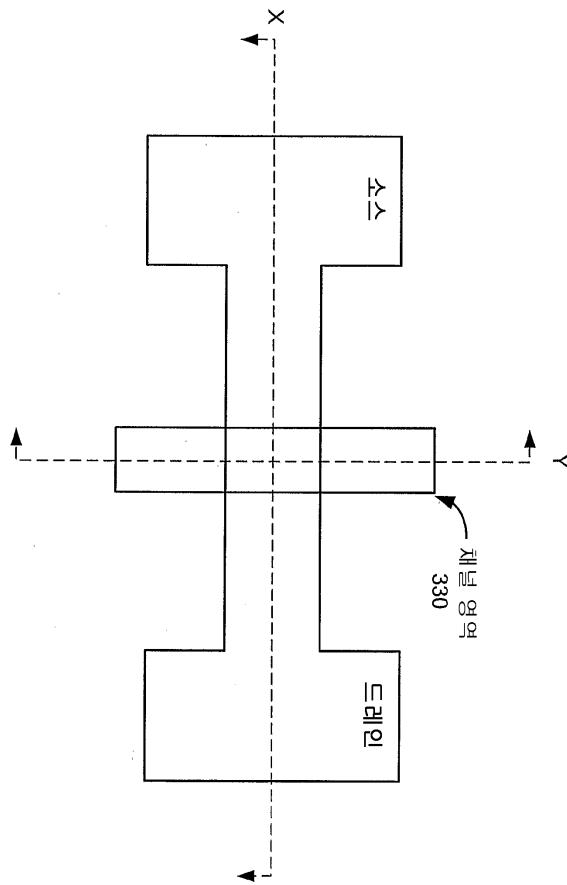

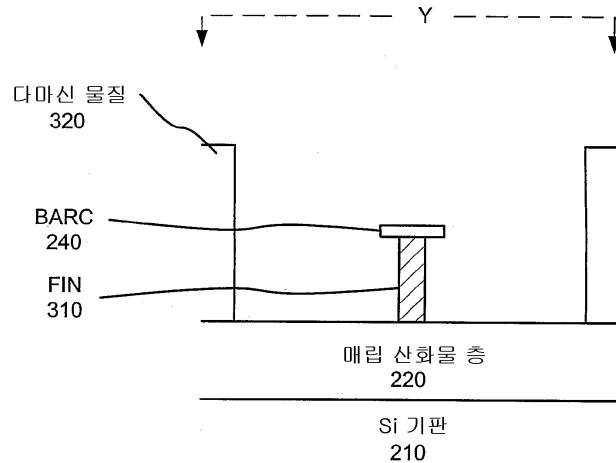

도 3A 내지 3C에 도시된 바와같이, 다마신 마스크가 펀(310) 영역에 형성될 수 있다(동작단계 130). 도 3A 및 3B에 도시된 바와같이, 예컨대, 실리콘 산화물, 실리콘 질화물, SiCOH 등과 같은 다마신 물질(320)이 (펀(310) 및 BARC(240)를 둘러싸기 위해) 대략 800Å 내지 2,200Å 범위의 두께로 반도체 디바이스(200) 위에 증착되며, 이후에 공지의 기법들을 사용하여 연마될 수 있다. 다마신 물질(320)은 후속 공정에 대한 BARC로서 작용할 수 있다. 도 3A 내지 3C에 도시된 바와같이, 이후에, 다마신 물질(320)은 게이트 개구(opening)에서 채널 영역(330)을 노출하기 위해 게이트 마스크를 사용하여 식각될 수 있다. 도 3C에 도시된 바와같이, 채널 영역(330)의 폭은 대략 300Å 내지 500Å의 범위가 될 수 있다. 채널 영역(330)을 노출하는데에 사용되는 게이트 마스크는 기술분야의 당업자에게 공지된 어그레시브 리소그래피 및 패턴화 기법들을 사용하여 생성될 수 있다.

[0023]

도 4A 내지 4C에 도시된 바와같이, 이후에, 펀(310)의 폭은 감소될 수 있다(동작 단계 140) 하나 이상의 식각 기법들이 채널 영역(330)에서 펀(310)을 측방향으로 식각하는데에 사용될 수 있다. 예컨대, Si의 열적 산화 및 이에 후속되는 묽은 플로오르화수소 딥핑(dilute HF dipping)이 사용될 수 있다. 다른 타입들의 식각이 대안적 으로 사용될 수 있다. 예컨대, Si는 다운스트림 F 플라즈마에서 식각될 수 있거나(여기서, 산화물에 대한 F 종(species)에서의 Si 식각의 화학적 선택도가 매우 높다), HBr 기반 플라즈마 화학제(plasma chemistry)들에서의 측방향 Si 식각이 사용될 수 있다.

[0024]

제거된 실리콘량은 도 4B에 도시된 바와같이 측부 당(per side) 100Å 내지 200Å의 범위가 될 수 있다. 펀(310)의 결과적인 폭은 대략 100Å 내지 400Å의 범위가 될 수 있다. BARC(240)는 도 4B에서 도시된 바와같이 본 발명의 원리들과 관련된 구현들에서 남게 될 수 있다. 다른 구현들에서, BARC(240)는 제거될 수 있다. 도 4C

는 핀(310)이 채널 영역(330)에서 얇게 된 이후의 반도체 디바이스(200)의 평면도이다.

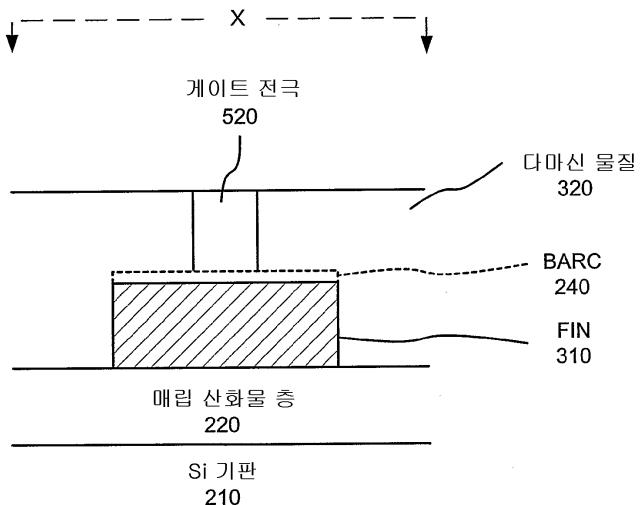

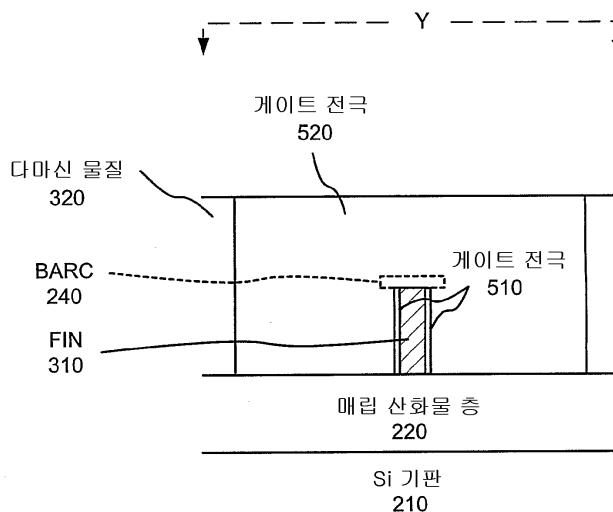

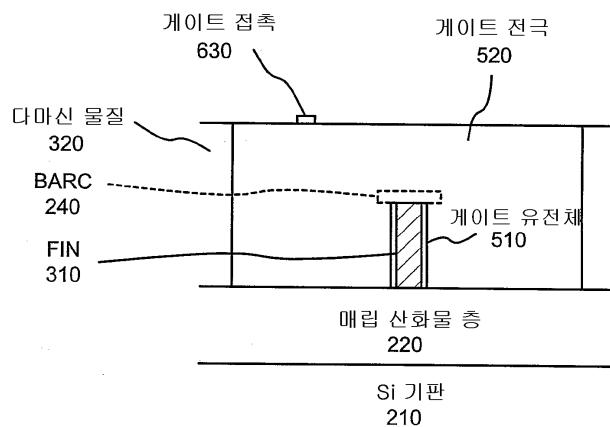

[0025] 이후에, 도 5A 내지 5C에 도시된 바와같이, 게이트가 형성될 수 있다(동작 단계 150). 예를 들어, 도 5B에 도시된 바와같이, 게이트 유전체 물질(510)이 핀(310)의 측면들상에 증착되거나 열적으로 성장할 수 있다. 게이트 유전체 물질(510)은 산화물(예를 들어, 실리콘 이산화물), 실리콘 옥시-나이트라이드(silicon oxy-nitride)와 같은 종래의 유전체 물질들, 또는  $HfO_2$ 와 같은 높은 유전 상수(하이 K) 물질들을 포함할 수 있다. 다른 구현들에서, 실리콘 질화물 또는 다른 물질들이 게이트 유전체를 형성하는데에 사용될 수 있다. 게이트 유전체 물질(510)은 대략  $10\text{ \AA}$  내지  $20\text{ \AA}$  범위의 두께로 형성될 수 있다.

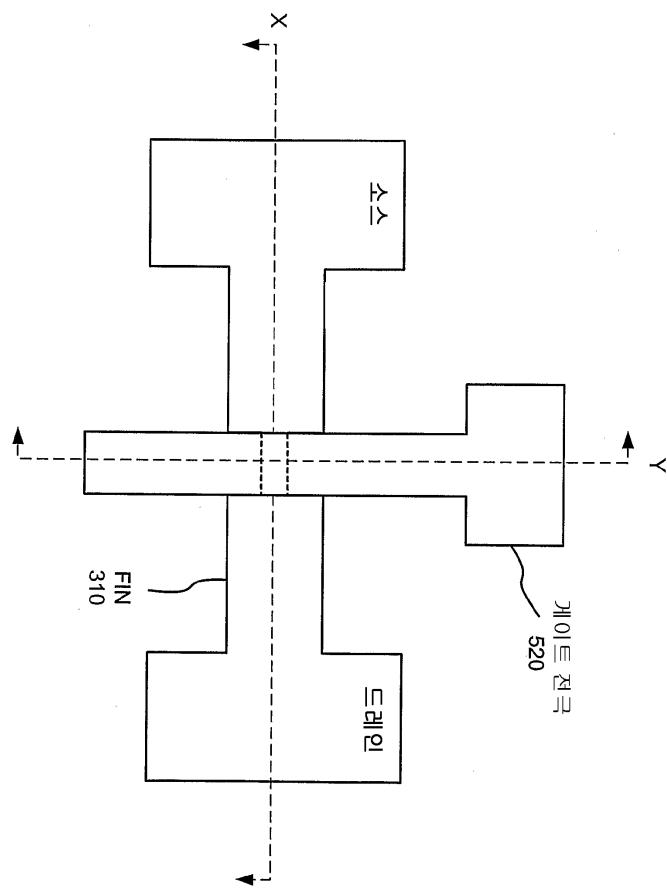

[0026] 이후에, 도 5A 내지 5B에 도시된 바와같이, 게이트 전극 물질(520)이 반도체 기판(200) 위에 증착되어 연마될 수 있다. 도 5A 및 5B에 도시된 바와같이, 게이트 전극 물질(520)이 다마신 물질(320) 위의 임의의 게이트 물질을 제거하기 위해 (예를 들어, 화학적-기계적 연마(CMP)를 통해) 연마될 수 있다. 다수의 물질들이 게이트 전극 물질(520)을 위해 사용될 수 있다. 예컨대, 게이트 전극 물질(520)은 폴리크리스탈라인 실리콘 또는 게르마늄이나 실리콘과 게르마늄의 조합들과 같은 다른 타입들의 도전성 물질, 또는 W, WN, TaN, TiN 등과 같은 금속들을 포함할 수 있다. 도 5B에 도시된 바와같이, 게이트 전극 물질(520)은 대략  $700\text{ \AA}$  내지  $2,100\text{ \AA}$  범위의 두께로 형성될 수 있는데, 이는 대략적으로 다마신 물질(320)의 두께(그 일부는 연마 때문에 상실되었음)와 일치될 수 있다. 도 5C는 게이트 전극(520)이 형성된 이후의 반도체(200)의 평면도를 도시한다. 도 5C에서 점선들은 핀(310)의 얇은 부분을 나타낸다. 간략화를 위해, 게이트 유전체 층(510)은 도 5C에 도시하지 않았다.

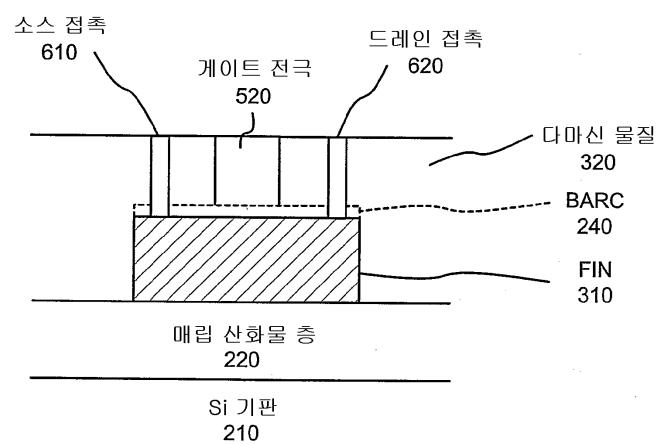

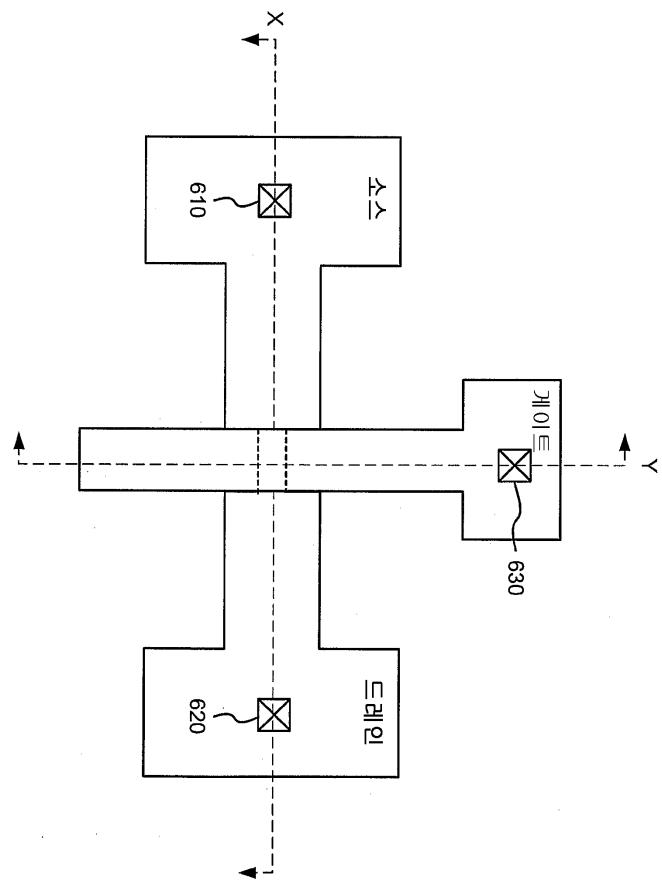

[0027] 이후에, 도 6A 내지 6C에 도시된 바와같이, 소스, 드레인 및 게이트 접촉들이 형성될 수 있다(동작 단계 160). 예를 들어, 하나의 구현에서, 도 6A에 도시된 바와같이, 큰 접촉 영역들이 핀(310) 위의 게이트의 양 측부 상에서 개방될 수 있다. 소스 및 드레인 접촉 영역들(610 및 620)은 핀(310) 위에 남아 있는 다마신 물질(320)의 여분량을 통해 식각하고, 또한 BARC(240)를 제거함으로써 개방될 수 있다. 게이트 접촉 영역(630)이 또한 게이트 전극(520)상에 형성될 수 있다. 이러한 접촉 영역들(610 내지 630)이 핀(310)과 소스/드레인의 실제 치수들보다 클 수도 있다.

[0028] 이후에,  $CoSi_2$  또는  $NiSi$  실리사이드화와 같은 실리사이드화가 이 개구들에서 발생할 수 있다.  $CoSi_2$  또는  $NiSi$  실리사이드화는 단지 폴리실리콘(즉, 게이트에서) 또는 실리콘(즉, 소스/드레인에서)이 있으며, 핀(310) 영역(폭넓은 핀)이 노출되는 경우에만 발생한다. (어떤 실리콘도 없는 경우에) 반응하지않은 코발트나 니켈은 오늘 날 산업계에 의해 사용중인 전형적인 자기-정렬된 실리사이드 구성들에서 수행되는 때에 식각될 수 있다.

[0029] 다른 구현에서, 다마신 물질(320) 및 BARC(240)는 핀(310)의 최상부와 소스/드레인으로부터 제거될 수 있다. 이후에, 측벽 스페이서가 게이트와 핀(310)의 측면들상에 형성될 수 있다. 다음으로, 최상부에(즉, 게이트 상에, 그리고 노출된 핀(310) 채널 상에) 노출된 실리콘이나 폴리실리콘에 있는 경우에, 코발트나 니켈과 같은 실리사이드 물질이 증착되어 자기 정렬된 실리사이드를 형성할 수 있다.

[0030] 따라서, 결과적인 반도체 디바이스(200)는 핀(310)의 양 측부 상에 형성된 자기 정렬된 다마신 게이트를 포함할 수 있다. 핀(310)은 도 6C의 점선들에 의해 도시된 바와같이 얇아지게 된다.

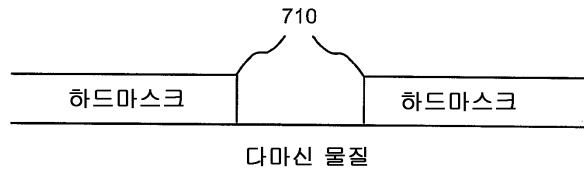

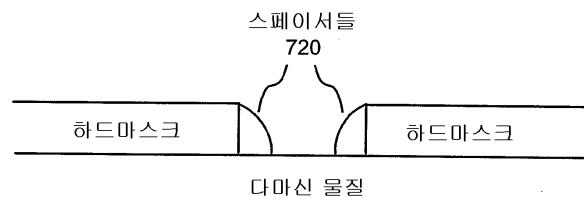

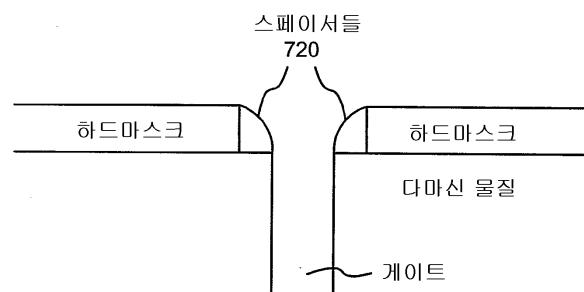

[0031] 본 발명의 원리들과 관련된 다른 구현에 따르면, 게이트 길이를 작아지게 하기 위해 다마신 게이트의 전사(transfer)를 위한 스페이서들이 형성될 수 있다. 도 7A 내지 7C는 본 발명의 원리들과 관련된 대안의 구현에 따라 스페이서들을 형성하는 예시적인 공정을 예시한다. 도 7A 내지 7C에 도시된 바와같이, 하드마스크(710)가 개방되며(도 7A), 스페이서들(720)이 형성되며(도 7B), 그리고 다마신 게이트의 전사가 개구에서 수행될 수 있다(도 7C). 다마신 게이트 개구 내부에 스페이서 형성은 (상술된 바와같이) 작은 공간들의 프린팅(printing)을 용이하게 하여, 작은 게이트 길이 디바이스들을 형성시킬 수 있다. 스페이서 기법은 포토리소그래피 축소화 만에 의하여 달성될 수 있는 것보다 작은 공간들의 형성을 가능하게 한다.

[0032] 다른 구현에서, 모두가 본원에서 참조로서 포함되는 다마신 게이트 축소 기법들이 있는데, 이는 공동계류종이며, 공동으로 양도된 출원들: 2003년 6월 12일 출원된 "FINFET GATE FORMATION USING REVERSE TRIM AND OXIDE POLISH"(Serial No. 10/459,589)(Docket No. H1122), 2002년 12월 17일 출원된 "FINFET GATE FORMATION USING REVERSE TRIM OF DUMMY GATE"(Serial No. 10/320,536)(Docket No.H1121), 및 2003년 8월 4일 출원된 "ETCH STOP LAYER FOR ETCHING FINFET GATE OVER A LARGE TOPOGRAPHY"(Serial No. 10/632,989)(Docket No.H1172)이다.

[0033] 또 다른 구현에서, 상술된 폴리실리콘 공정 대신에 금속 게이트 전극이 사용될 수 있다.

[0034]

### 다른 구현들

[0035]

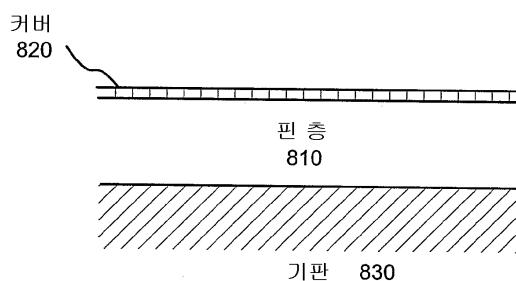

종래 기술분야에서, 공정 동안에 핀(310)의 측면들(즉, 측벽들)에서 발생할 수 있는 손상을 제거하는 것이 필요하다. 도 8A 내지 8C는 핀(310) 측벽 손상을 제거하는 예시적 공정을 도시한다. 도 8A에 도시된 바와같이, 반도체 디바이스(800)는 기판(830)상에 형성된 핀(310) 층(810)과 커버층(820)을 포함할 수 있다. 핀(310) 층(810)은 실리콘이나 게르마늄, 또는 반도체 물질들의 조합들과 같은 반도체 물질을 포함할 수 있다. 예를 들어, 커버층(820)은 실리콘 질화물 물질 또는 제조 공정 동안에 핀(310) 층(810)을 보호할 수 있는 일부 다른 타입의 물질을 포함할 수 있다.

[0036]

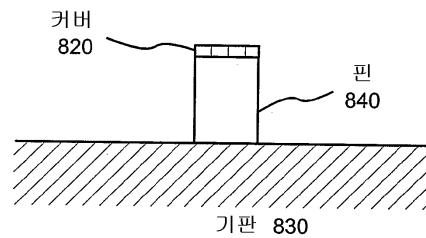

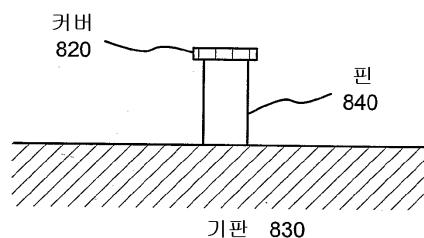

도 8B에 도시된 바와같이, 핀(310) 층(810) 및 커버층(820)은 종래 전식 식각 기법을 사용하여 식각되어 핀(310)(840)을 형성할 수 있다. 이후에, 도 8C에 도시된 바와같이, 종래의 습식 식각 기법이 핀(310) 측벽 손상을 제거하는데에 사용될 수 있다. 습식 식각 동안에, 핀(310)(840) 폭이 측면당 대략 20Å 내지 40Å로 얇게 될 수 있다. 또한, 실리콘의 습식 식각은 일부 매립된 산화물의 손실을 발생시킬 수 있는데, 이는 습식 식각을 할 때에 실리콘 대 실리콘 이산화물(silicon to silicon dioxide)의 양호한 선택성을 얻기 힘들기 때문이다.

[0037]

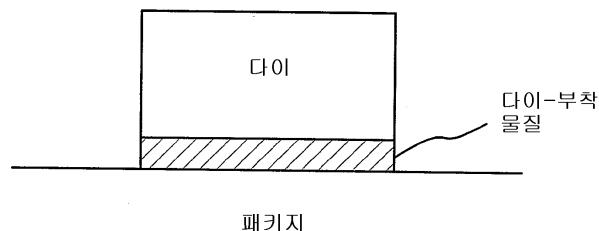

또한, 종래 기술분야에서 FinFET 디바이스의 이동성을 개선시킬 필요가 있다. 도 9는 FinFET 디바이스의 이동성 개선을 위한 예시적 공정을 도시한다. 도 9에 도시된 바와같이, 다이(die)-부착 물질이 패키지 상에 형성될 수 있다. 다이-부착 물질은 FinFET 채널에서 응력(변형)을 유도하도록 선택될 수 있다. 이후에, 도 9에 도시된 바와같이, 다이가 다이-부착 물질에 부착될 수 있다. 실리콘 FinFET 채널에서 유도된 인장 응력은 정공 이동도 개선을 야기할 수 있는데, 이는 PMOS FinFET 성능을 크게 개선시키는 것을 도울 수 있다. 실리콘층에서의 잔여 응력이 인장 되도록 다이-부착 물질 및 공정이 이루어질 수 있다. 예컨대, (핫) 다이-부착/솔더/범프(bump) 공정 이후에, 패키지 물질이 실리콘층만큼 신속하게 축소되지 않는 경우에, 실리콘층은 저온으로 냉각되는 때에 인장 응력에 있을 수 있다.

### 산업상 이용 가능성

[0038]

본 발명의 원리들과 관련된 구현들은 자기 정렬된 게이트 마스크로 형성된 다마신 게이트를 포함하는 FinFET 디바이스들 및 이러한 디바이스들의 제조 방법들을 제공한다. 이러한 FinFET 디바이스들은 여러 이점들을 갖는다. 예를 들어, 단지 핀(310)의 활성 영역만이 최소 채널 길이에 있으며, 게이트는 최소 채널에 자기 정렬되며, 그리고 평면의 기판상에서 게이트 패턴화가 수행된다(예를 들어, 연마 다마신 물질).

[0039]

본 발명의 예시적 실시예들에 대한 상기 설명은 예시 및 설명을 제공하지만, 이는 발명 전체를 뜻하거나 발명을 개시된 것으로만 국한하려는 것이 아니다. 상기 개시의 관점에서 다양한 변형들 및 변화들이 가능할 수 있거나, 본 발명의 실시로부터 획득될 수 있다.

[0040]

예를 들어, 상기 설명들에서, 본 발명과 관련된 구현들의 완전한 이해를 위해, 특정 물질들, 구조들, 화학물질들, 공정들 등과 같은 많은 특정의 상세사항들이 제시되었다. 하지만, 본원에서 특정적으로 제시된 상세사항들에 의존함이 없이, 이러한 구현들 및 다른 구현들이 실시될 수 있다. 다른 경우들에서, 본 발명의 요지를 불필요하게 모호하게 하지 않기 위해, 잘 알려진 공정 구조들은 상세히 설명하지 않았다. 본 발명을 실시함에 있어서, 종래 증착, 포토리소그래픽 및 식각 기법들이 이용될 수 있으며, 이에 따라 이러한 기법들의 상세사항들이 본원에서 상세히 제시되지 않았다.

[0041]

일련의 동작단계들이 도 1에 관하여 설명되었지만, 동작들의 순서는 본 발명과 관련된 다른 구현들에서 바뀌어 질 수 있다. 게다가, 서로 의존되지 않는 동작들이 병행 실시될 수 있다.

[0042]

본 출원의 상세한 설명에서 사용된 어떤 요소, 동작, 또는 명령도 명시적으로 기술하지 않는한 본 발명에서 중요하거나 필수적인 것으로서 고려되지 않아야 한다. 또한, 상세한 설명에서 단수 의미의 용어는 하나 또는 그 이상의 복수의 의미를 지닐 수도 있다. 오직 단수 의미의 용어는 하나 또는 유사한 용어로 표현하였다. 본 발명의 범위는 특히 청구범위 및 이의 균등물에 의해 한정되어야 할 것이다.

### 도면의 간단한 설명

[0008]

본 명세서에 포함되며, 그 일부를 구성하는 첨부 도면들은 본 발명을 설명하는 상세한 설명과 함께 본 발명의 실시예를 예시한다.

[0009]

도 1은 본 발명의 원리들과 관련된 구현에 따라 MOSFET를 제조하는 예시적인 공정을 도시한다.

- [0010] 도 2A 내지 6C는 도 1에서 설명된 공정에 따라 제조된 MOSFET의 예시적 평면도 및 단면도들을 도시한다.

- [0011] 도 7A 내지 7C는 본 발명의 원리들과 관련된 다른 구현에 따라 스페이서들을 형성하는 공정을 도시한다.

- [0012] 도 8A 내지 8C는 펈(310) 측벽 손상을 제거하기 위한 예시적인 공정을 도시한다.

- [0013] 도 9는 FinFET 디바이스의 이동성을 개선하기 위한 예시적인 공정을 도시한다.

## 도면

### 도면1

### 도면2A

#### 200

도면2B

도면2C

도면3A

200

도면3B

200

도면3C

200

도면4A

200

도면4B

200

도면4C

200

## 도면5A

200

## 도면5B

200

도면5C

200

도면6A

200

도면6B

200

↓ ----- Y ----- ↓

도면6C

200

도면7A

도면7B

도면7C

도면8A

800

도면8B

800

도면8C

800

도면9

파키지