(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5020479号

(P5020479)

(45) 発行日 平成24年9月5日(2012.9.5)

(24) 登録日 平成24年6月22日(2012.6.22)

(51) Int.Cl.

HO2M 3/28 (2006.01)

F 1

HO2M 3/28

H

請求項の数 2 (全 10 頁)

(21) 出願番号 特願2005-159067 (P2005-159067)

(22) 出願日 平成17年5月31日 (2005.5.31)

(65) 公開番号 特開2006-340429 (P2006-340429A)

(43) 公開日 平成18年12月14日 (2006.12.14)

審査請求日 平成20年5月30日 (2008.5.30)

前置審査

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 110001243

特許業務法人 谷・阿部特許事務所

(74) 復代理人 100115624

弁理士 濱中 淳宏

(74) 復代理人 100120581

弁理士 市原 政喜

(72) 発明者 中田 康裕

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

審査官 今井 貞雄

最終頁に続く

(54) 【発明の名称】電源装置

## (57) 【特許請求の範囲】

## 【請求項 1】

互いに絶縁された1次巻線と2次巻線を有するトランスと、

前記トランスの1次巻線に流れる電流をスイッチングするスイッチング手段と、

前記トランスの2次巻線の出力を整流及び平滑する整流平滑手段と、

前記整流平滑手段によって整流及び平滑された前記トランスの2次側の出力電圧と基準電圧を比較することにより、フィードバック信号を出力するフィードバック手段と、

前記フィードバック手段からの前記フィードバック信号に応じて前記スイッチング手段のオン時間を制御するオン時間制御手段と、

前記出力電圧が供給される負荷の動作を制御するコントローラと、

前記コントローラからの指示に応じて、前記負荷が動作している動作状態から前記負荷が動作していない待機状態に切り換わる場合に、前記コントローラから出力される発振停止信号に応じて前記フィードバック手段の前記フィードバック信号を制御することにより、前記スイッチング手段の発振を停止する発振停止手段と、を有し、

前記動作状態において、前記オン時間制御手段からの信号に応じて前記スイッチング手段を連続的にオンオフし、

前記待機状態において、前記コントローラは、前記スイッチング手段を間欠的にオンオフするために、前記トランスの2次側の出力電圧を監視し、監視した前記出力電圧に応じて前記発振停止手段に前記発振停止信号を出力し、前記発振停止手段が前記フィードバック手段のフィードバック信号を制御することにより、前記スイッチング手段をオフし、前

10

20

記スイッチング手段をオフした後、監視した前記出力電圧が前記動作状態における出力電圧よりも小さい閾値電圧を下回ると前記発振停止信号を停止することにより前記スイッチング手段をオンするように前記発振停止信号の出力を制御することを特徴とする電源装置。

### 【請求項 2】

前記出力電圧は複数の負荷に供給され、前記動作状態とは、前記複数の負荷のすべてが動作している状態であり、前記待機状態とは、前記複数の負荷の一部が動作していない状態であることを特徴とする請求項 1 に記載の電源装置。

### 【発明の詳細な説明】

#### 【技術分野】

10

#### 【0001】

本発明は、電源装置に関する。

#### 【背景技術】

#### 【0002】

機器待機時の消費電力を削減する技術としては、例えば、特許文献 1 に記載の技術が知られている。この技術によれば、プリンタがプリント状態か非プリント状態かによって、次のような制御が行われる。すなわち、非プリント時においても使用される制御部に電源を供給する第 1 の電源手段と、プリント時に使用される駆動部に電源を供給する第 2 の電源手段と、を備えた画像形成装置において、第 2 の電源手段の出力電圧を切り替え制御可能とし、非プリント状態において第 2 の電源手段の出力電圧を低下させる。

20

#### 【0003】

また、特許文献 2 に記載の技術によれば、機器の休止時において、次のような制御が行われる。すなわち、機器の休止時においては、マイクロコントローラから、電源装置のフィードバック部のオプトカプラの電流を、断続的強制的に増大させ、電源装置の動作を断続的に停止させ、これにより、発振周波数の上昇を防ぎ、電源装置の変換効率低下を防いでいる。

#### 【0004】

これは、電源装置が備えるスイッチング素子のスイッチング損失を低下させることにより、効率を上昇させる手段である。機器の休止時においては、電源装置の負荷が軽くなるにもかかわらず、スイッチング素子のスイッチング回数が減少しないか、又は増加してしまうことを防ぐことにより、損失を低下させている。

30

#### 【0005】

【特許文献 1】特開 2002 - 19232 号公報

【特許文献 2】特開 2003 - 284340 号公報

【特許文献 3】特開 2004 - 153871 号公報

### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0006】

これら個別の手段を組み合わせると、回路が複雑になり経済的ではない。例えば、特許文献 3 においては、機器の休止時において、電源手段の出力電圧を低下させ、かつ電源装置の動作を断続的に停止させる手段が提案されているが、回路が複雑になっている。

40

#### 【0007】

そこで、本発明は、上記のような問題点を解決し、スイッチングレギュレータおよびマイクロコントローラを備えた機器であって、負荷の動作状態、待機状態、非動作状態等の状態において、スイッチングレギュレータを安価に電源変換効率良く制御することができる機器を提供することを目的とする。

### 【課題を解決するための手段】

#### 【0008】

本発明に係る電源装置は、互いに絶縁された 1 次巻線と 2 次巻線を有するトランスと、前記トランスの 1 次巻線に流れる電流をスイッチングするスイッチング手段と、前記トラン

50

ンスの2次巻線の出力を整流及び平滑する整流平滑手段と、前記整流平滑手段によって整流及び平滑された前記トランスの2次側の出力電圧と基準電圧を比較することにより、フィードバック信号を出力するフィードバック手段と、前記フィードバック手段からの前記フィードバック信号に応じて前記スイッチング手段のオン時間を制御するオン時間制御手段と、前記出力電圧が供給される負荷の動作を制御するコントローラと、前記コントローラからの指示に応じて、前記負荷が動作している動作状態から前記負荷が動作していない待機状態に切り換わる場合に、前記コントローラから出力される発振停止信号に応じて前記フィードバック手段の前記フィードバック信号を制御することにより、前記スイッチング手段の発振を停止する発振停止手段と、を有し、前記動作状態において、前記オン時間制御手段からの信号に応じて前記スイッチング手段を連続的にオンオフし、前記待機状態において、前記コントローラは、前記スイッチング手段を間欠的にオンオフするために、前記トランスの2次側の出力電圧を監視し、監視した前記出力電圧に応じて前記発振停止手段に前記発振停止信号を出力し、前記発振停止手段が前記フィードバック手段のフィードバック信号を制御することにより、前記スイッチング手段をオフし、前記スイッチング手段をオフした後、監視した前記出力電圧が前記動作状態における出力電圧よりも小さい閾値電圧を下回ると前記発振停止信号を停止することにより前記スイッチング手段をオンするように前記発振停止信号の出力を制御することを特徴とする。

## 【発明の効果】

## 【0013】

本発明によれば、上記のように構成したので、スイッチングレギュレータおよびマイクロコントローラを備えた機器において、負荷の動作状態、待機状態、非動作状態等の状態において、スイッチングレギュレータを安価に電源変換効率良く制御することができる。

10

## 【発明を実施するための最良の形態】

## 【0014】

以下、本発明の実施の形態を図面を参照して詳細に説明する。

## 【0015】

## &lt;第1の実施の形態&gt;

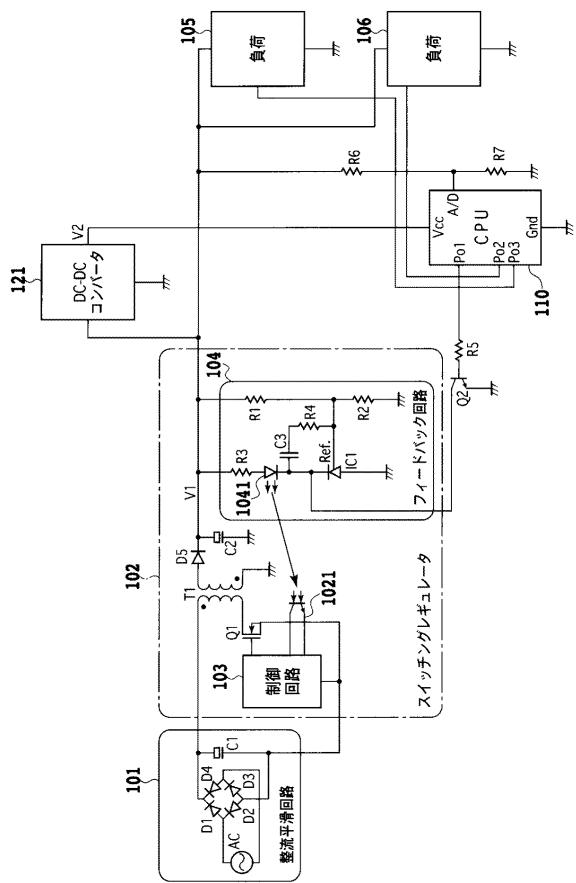

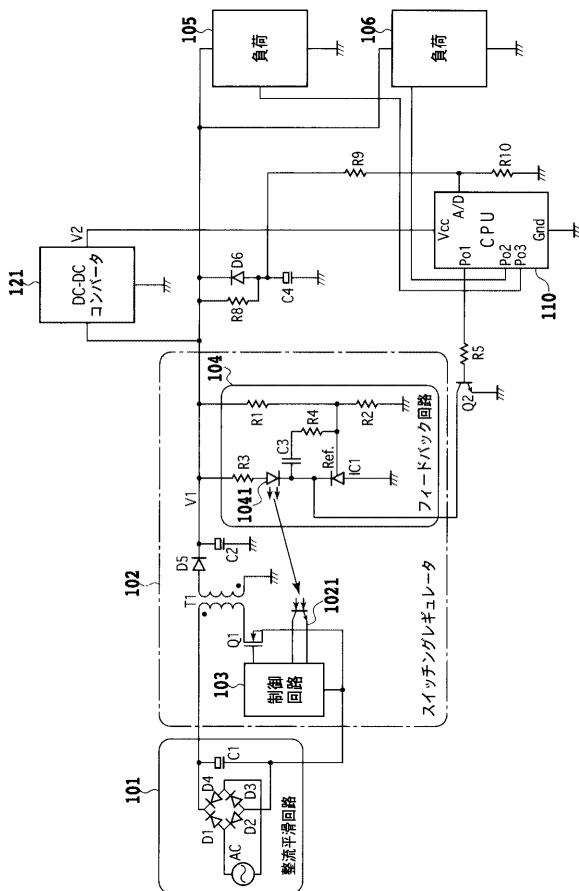

図1は本発明の第1の実施の形態を示す。図1において、101は整流平滑回路であり、商用電源A Cから入力された交流電圧を、整流ダイオードD 1～D 4と平滑コンデンサC 1で、直流電圧に変換する。

20

## 【0016】

102はスイッチングレギュレータである。Q 1はメインスイッチング素子としてのMOSFET、T 1は絶縁トランスであり、103はMOSFET Q 1の制御回路である。制御回路103は、フォトトランジスタ1021のトランジスタ電流に応じて、MOSFET Q 1のオン時間の長さを決定する。フォトトランジスタ1021のトランジスタ電流が少なければ、オン時間は長い。フォトトランジスタ1021のトランジスタ電流が多いければ、オン時間は短くなり、所定の値以上となると、オンしなくなる。オフ時間は、絶縁トランスT 1の蓄積エネルギーが放出される期間である。絶縁トランスT 1の出力は、ダイオードD 5とコンデンサC 2により整流平滑される。コンデンサC 2間電圧がスイッチングレギュレータ102の2次側出力電圧V 1となる。本実施の形態は、フライバック電源の例であるが、特にこの例に限定されるものではない。

30

## 【0017】

104はフィードバック回路であり、スイッチングレギュレータ102の出力電圧V 1と、シャントレギュレータIC 1のRef端子の入力電圧との誤差を增幅し、フォトカプラー(LED1041とフォトトランジスタ1021)により構成されている。)を介して1次側にフィードバックするものである。2次側出力電圧V 1は、抵抗R 1と抵抗R 2により分圧され、シャントレギュレータIC 1のRef端子に入力されている。シャントレギュレータIC 1は、内蔵の基準電圧とRef端子の電圧とを比較し、カソード電圧に反映する。スイッチングレギュレータ102の出力電圧V 1とシャントレギュレータIC 1のカソード電圧との差電圧と、抵抗R 3と、により決定される電流が、ダイオード電流と

40

10

20

30

40

50

して L E D 1 0 4 1 を流れ、このダイオード電流に応じた電流が、L E D 1 0 4 1 と光結合されているフォトトランジスタ 1 0 2 1 (スイッチングレギュレータ 1 0 2 の)を流れる。シャントレギュレータ I C 1 のカソード電圧は、R e f 端子の電圧が内蔵基準電圧よりも高ければ低下し、低ければ上昇するように動作する。なお、コンデンサ C 3 と抵抗 R 4 は、位相補償用に設けられている。

#### 【0018】

スイッチングレギュレータ 1 0 2 の出力電圧 V 1 は、フィードバック回路 1 0 4 により、シャントレギュレータ I C 1 の内蔵基準電圧の (R 1 + R 2) / R 2 に制御される。

#### 【0019】

1 2 1 は降圧型 D C - D C コンバータであり、スイッチングレギュレータ 1 0 2 の出力電圧 V 1 を C P U 1 1 0 の電源電圧である V 2 に降圧する。10

#### 【0020】

1 0 5、1 0 6 はスイッチングレギュレータ 1 0 2 の負荷である。負荷 1 0 5 は機器が動作中にしか電源供給を必要としない負荷であって、例えばプリンタの場合の紙搬送用モータが挙げられる。負荷 1 0 6 は機器が動作中及び待機中ともに電源供給を必要とする負荷であって、例えば操作パネルなどが挙げられる。なお、機器の中には、機器が省エネルギー モードに入ると、負荷 1 0 5 及び負荷 1 0 6 がともに電源供給を必要としない機器もある。

#### 【0021】

C P U 1 1 0 は機器の制御をつかさどる。V c c は駆動電源端子、G n d はグランド端子であり、P o 2、P o 3 は出力ポートであり、負荷 1 0 5、負荷 1 0 6 を制御する。A / D はアナログデジタル変換ポート(以下「A / D ポート」という。)であり、スイッチングレギュレータ 1 0 2 の出力電圧 V 1 を抵抗 R 6 及び抵抗 R 7 で分圧した電圧が入力される。P o 1 は出力ポートである。20

#### 【0022】

C P U 1 1 0 の出力ポート P o 1 が論理ローレベル(以下「L」という。)の場合、トランジスタ Q 2 はオフであり、フィードバック回路 1 0 4 は、スイッチングレギュレータ 1 0 2 の出力電圧を、シャントレギュレータ I C 1 の内蔵基準電圧の (R 1 + R 2) / R 2 になるように制御する。他方、この出力ポート P o 1 が論理ハイレベル(以下「H」という。)のとき、トランジスタ Q 2 はオンとなって、シャントレギュレータ I C 1 のカソード電圧がグランド電圧になる。その結果、シャントレギュレータ I C 1 は動作しなくなるが、L E D 1 0 4 1 のダイオード電流は、トランジスタ Q 2 を介して流れるので、増大し、このL E D 1 0 4 1 と光結合されているフォトトランジスタ 1 0 2 1 のトランジスタ電流が増大する。このトランジスタ電流の電流値は、制御回路 1 0 3 がM O S F E T Q 1 をオンさせなくなる値に設定されている。30

#### 【0023】

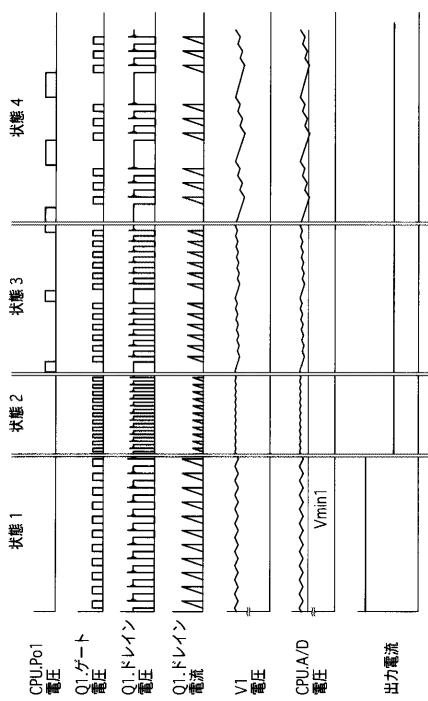

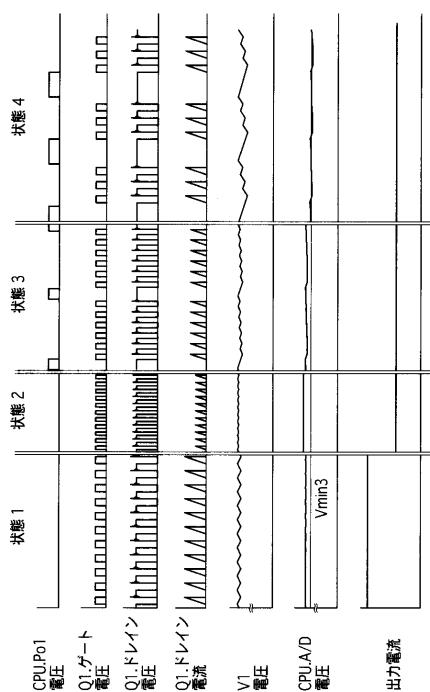

次に、図 2 ~ 図 4 を参照して、図 1 の回路の各状態における動作を説明する。図 2 ~ 図 4 は、それぞれ、上から順に、C P U 1 1 0 の出力ポート P o 1 の状態、M O S F E T Q 1 のゲート電圧波形、ドレイン電圧波形、ドレイン電流波形、スイッチングレギュレータ 1 0 2 の出力電圧 V 1 の電圧波形、C P U 1 1 0 の A / D ポートの入力電圧、スイッチングレギュレータ 1 0 2 の出力電流波形を示す。図 2 ~ 図 4 は一連の時系列の動きを示す。図示の状態 1 ~ 状態 5 に従って以下説明する。40

#### 【0024】

状態 1： 機器動作状態であり、負荷 1 0 5 及び負荷 1 0 6 はともに動作している。このとき、スイッチングレギュレータ 1 0 2 は最大出力状態である。スイッチングレギュレータ 1 0 2 の出力電圧 V 1 と、シャントレギュレータ I C 1 のカソード電圧との差電圧と、抵抗 R 3 と、により決定されたダイオード電流に応じて、すなわち、L E D 1 0 4 1 と光結合されているフォトトランジスタ 1 0 2 1 をトランジスタ電流が流れる。そして、制御回路 1 0 3 は、このトランジスタ電流に応じて M O S F E T Q 1 のオンデューティを制御し、スイッチングレギュレータ 1 0 2 の出力電圧 V 1 を制御する。50

## 【0025】

状態2：機器は待機状態であって、負荷106のみが動作し、負荷105は動作していない。したがって、スイッチングレギュレータ102の出力電流は、状態1より減少している。フィードバック回路104の働きにより、シャントレギュレータIC1のカソード電圧は上昇し、LED1041のダイオード電流が減少し、このLED1041と光結合されているフォトトランジスタのトランジスタ電流が減少するので、MOSFET Q1のオン時間が短くなる。MOSFET Q1のスイッチング回数が状態1より多いため、損失が増加している期間である。

## 【0026】

状態3：機器は状態2と同じく待機状態である。CPU110は出力ポートPo1を断続的にHにしている。出力ポートPo1がHの間、トランジスタQ2はオンになり、シャントレギュレータIC1のカソード電圧がグランド電圧になる。すると、シャントレギュレータIC1は動作しなくなるが、LED1041のダイオード電流は、トランジスタQ2を介して流れるので、増大し、このLED1041と光結合されているフォトトランジスタ1021のトランジスタ電流が増大する。この出力ポートPo1がHの間、MOSFET Q1はオフ状態となり、出力電圧V1は負荷106の負荷電流により低下していく。

## 【0027】

一方、出力ポートPo1がLの間は、シャントレギュレータIC1は動作する。出力ポートPo1がHからLに移行したとき、出力電圧V1は内蔵基準電圧の( $R_1 + R_2$ )/ $R_2$ よりも低いためLED1041のダイオード電流は状態2の時よりも減少し、このLED1041と光結合されているフォトトランジスタのトランジスタ電流が減少する。したがって、MOSFET Q1のオン時間が、状態2より、長くなる。

## 【0028】

CPU110は、A/Dポートに入力された電圧、すなわち出力電圧V1を抵抗R6と抵抗R7で分圧した電圧をモニタしている。CPU110はプログラムコードで設定された所定の値Vmin1を下回るまで、出力ポートPo1のHのデューティを増大させる。なお、 $V_{min1} \times (R_6 + R_7) / R_7$ は負荷106が十分動作できる電圧に設定しなければならない。

## 【0029】

状態4：機器は状態2と同じく待機状態である。CPU110の出力ポートPo1のHのデューティが、状態3に比べて、大きい。CPU110のA/Dポートの電圧は所定の値Vmin1を下回る期間が発生している。CPU110は機器の状態が変化しない限り、この状態を維持する。状態2に比べて、MOSFET Q1のスイッチング回数が大幅に減少し、状態2に比べてスイッチングレギュレータ102は効率の良い状態である。図示しないが、CPU110が、この状態から機器の動作状態に遷移させる場合には、CPU110は出力ポートPo1をL状態に固定してから機器の状態を遷移させる。

## 【0030】

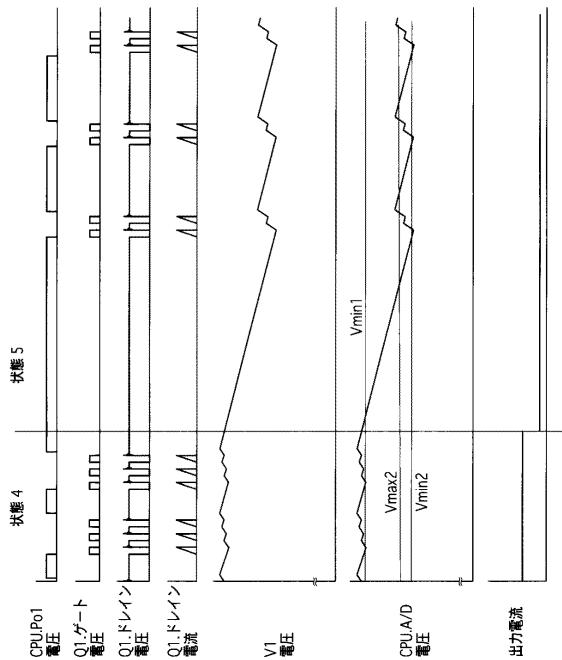

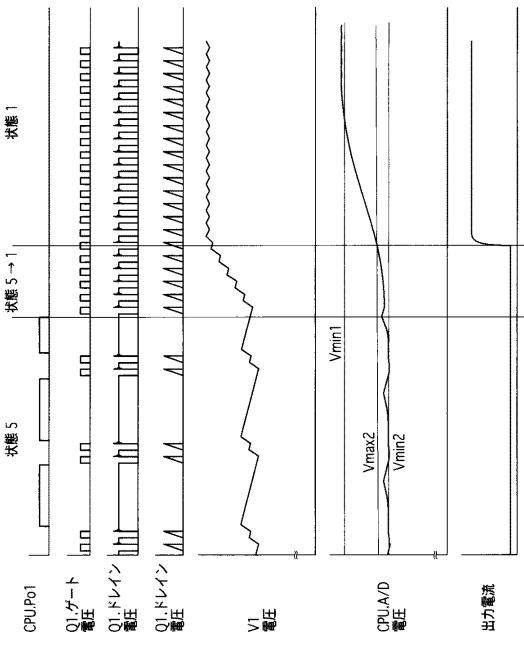

状態5：機器は省エネルギー mode に移行し、負荷105及び負荷106は共に動作していない。この状態5では、スイッチングレギュレータ102の出力は降圧型DC-DCCコンバータ121にのみ電力を供給している。降圧型DC-DCCコンバータ121は、入力電圧が、図中、 $V_{min2} \times (R_6 + R_7) / R_7$ 以上であれば、動作可能であり、入力電圧が低いほど効率がよい。CPU110は、A/Dポートの入力電圧がVmin2を下回るまでの間、出力ポートPo1をHとし、Vmin2からVmax2を上回るまでの間、出力ポートPo1をLとする。

## 【0031】

MOSFET Q1のスイッチング回数は状態4に比べて大幅に減少し、かつ降圧型DC-DCCコンバータ121の効率も上昇し、損失のきわめて少ない状態である。

## 【0032】

状態5 状態1：機器を省エネルギー mode から動作状態に移行させる場合の遷移状

10

20

30

40

50

態である。C P U 1 1 0 は機器を動作状態に移行させるために出力ポート P o 1 を L 状態に維持する。しかしながら、出力電圧 V 1 が V min2、V max2 近傍にあるため、直ちに負荷 1 0 5、負荷 1 0 6 を動作させることができない。C P U 1 1 0 は A / D ポートの電圧をモニタし、V min1 を上回ったのを確認し、負荷 1 0 5、負荷 1 0 6 を動作させ、機器を動作状態に移行させる。

#### 【 0 0 3 3 】

以上説明したように、本実施の形態においては、機器の動作状態に応じて M O S F E T Q 1 のスイッチング回数が増大しないように制御でき、スイッチングレギュレータ 1 0 2 の損失を抑えることができる。

#### 【 0 0 3 4 】

なお、C P U 1 1 0 の出力ポート P o 1 の設定は、プログラムコードで逐次指定しても良いし、P W M 出力のように周波数とデューティを指定しても良い。

#### 【 0 0 3 5 】

また、本実施の形態では、アナログデジタル変換機能を C P U 1 1 0 の内蔵のタイプとしたが、別回路のアナログデジタル回路を用い、その出力を C P U 1 1 0 に入力しても良い。

#### 【 0 0 3 6 】

< 第 2 の実施の形態 >

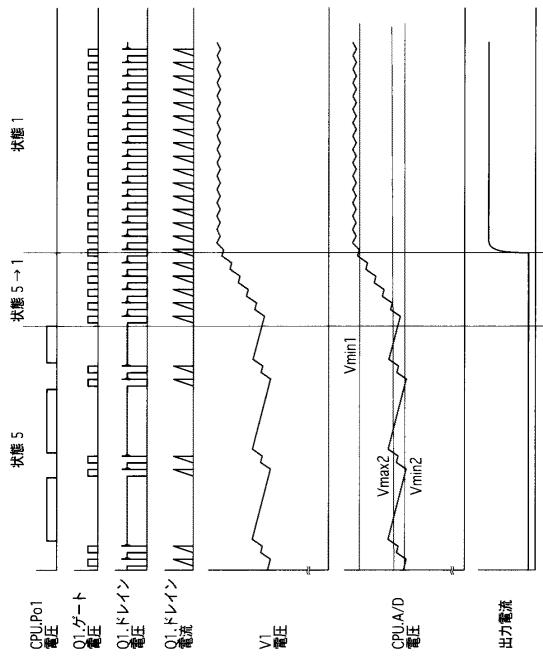

図 5 は本発明の第 2 の実施の形態を示す。本実施の形態は、第 1 の実施の形態との比較でいえば、C P U 1 1 0 の A / D ポートに接続される回路の構成が異なる。

#### 【 0 0 3 7 】

すなわち、第 1 の実施の形態においては、C P U 1 1 0 の A / D ポートには、2 次側出力電圧 V 1 を抵抗 R 6 と抵抗 R 7 で分圧した電圧を入力するようにした。また、C P U 1 1 0 におけるアナログデジタル変換機能の変換速度は、高速なものが要求されており、スイッチングレギュレータのスイッチング周波数が一般的な数 1 0 k H z である場合には、少なくとも数 1 0 k H z の変換周期が必要であった。

#### 【 0 0 3 8 】

これに対して、本実施の形態では、抵抗 R 8 と、ダイオード D 6 と、コンデンサ C 4 により、充放電の時定数の異なるフィルタ回路を構成し、C P U 1 1 0 の A / D ポートには、

コンデンサ C 4 間電圧を抵抗 R 9 及び抵抗 R 1 0 で分圧して得られた電圧を、入力するようにした。

#### 【 0 0 3 9 】

図 6 ~ 図 8 を参照して本回路の各状態の動作を説明する。図 6 ~ 図 8 の各波形は図 2 ~ 図 4 と同一部分の波形である。

#### 【 0 0 4 0 】

状態 1 ~ 状態 3 : 第 1 の実施の形態と同じである。C P U 1 1 0 の A / D ポートの入力電圧は、このフィルタ回路の影響により、2 次側出力電圧 V 1 の低電圧側に偏った波形となる。

#### 【 0 0 4 1 】

状態 4 : 第 1 の実施の形態と同じである。C P U 1 1 0 の A / D ポートの入力電圧は、このフィルタ回路の影響により、2 次側出力電圧 V 1 の低電圧側に偏っているため、V min1 を下回る期間が長い。したがって、C P U 1 1 0 の A / D ポートが、遅くとも C P U 1 1 0 が V min1 を下回っていると検出できるようになる。

#### 【 0 0 4 2 】

状態 5 : 機器の状態は第 1 の実施の形態と同じである。C P U 1 1 0 の A / D ポートの入力電圧は、このフィルタ回路の影響により、2 次側出力電圧 V 1 の低電圧側に偏っている。したがって、V min2 の検出はできるが、第 1 の実施の形態での V max2 にあたる電圧は検出できない。C P U 1 1 0 は、出力ポート P o 1 の L 期間をあらかじめ定めた時間とし、H 期間を調整することにより、C P U 1 1 0 の A / D ポートの入力電圧が低下した電

10

20

30

40

50

圧をV<sub>min2</sub>になるように制御する。

**【0043】**

状態5 状態1：機器の状態は第1の実施の形態と同じである。CPU110は機器を動作状態に移行させるため、出力ポートP01をL状態に維持する。しかしながら、2次側出力電圧V1がV<sub>min2</sub>、V<sub>max2</sub>の近傍にあるため、直ちに負荷105、負荷106を動作させることができない。

**【0044】**

またそのうえ、CPU110のA/Dポートの入力電圧は、このフィルタ回路の影響によりなかなか上昇しない。

**【0045】**

したがって、CPU110のA/Dポートの入力電圧をモニタして、状態5から状態1へ移行する場合、本実施の形態では、第1の実施の形態に比べて、時間がかかる。時間短縮のため、状態移行完了を、CPU110のA/Dポートの入力電圧にかかわらず、決められた時間で行うこともできる。

**【図面の簡単な説明】**

**【0046】**

【図1】本発明の第1の実施の形態に係る回路を示す回路図である。

【図2】図1の回路の動作波形図である。

【図3】図1の回路の動作波形図である。

【図4】図1の回路の動作波形図である。

【図5】本発明の第2の実施の形態に係る回路を示す回路図である。

【図6】図5の回路の動作波形図である。

【図7】図5の回路の動作波形図である。

【図8】図5の回路の動作波形図である。

**【符号の説明】**

**【0047】**

101 平滑整流回路

102 スイッチングレギュレータ

103 制御回路

104 フィードバック回路

105、106 負荷

110 CPU

121 DC - DCコンバータ

1021 フォトトランジスタ

1041 LED

Q1 MOSFET

T1 トランジスタ

IC1 シャントレギュレータ

10

20

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

(56)参考文献 特開平09-140128(JP,A)

特開2004-201449(JP,A)

特開2004-072878(JP,A)

特開2004-153871(JP,A)

(58)調査した分野(Int.Cl., DB名)

H02M 3/28