(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2013-0085998

(43) 공개일자 2013년07월30일

- (51) 국제특허분류(Int. C11.)

*H01Q 1/24* (2006.01) *H01Q 1/38* (2006.01)

- (21) 출원번호 10-2013-0005995

- (22) 출원일자 2013년01월18일

- 심사청구일자 없음

- (30) 우선권주장

1250571 2012년01월20일 프랑스(FR)

- (71) 출원인

톰슨 라이센싱

프랑스 92130 이씨레물리노 잔 다르크 뤼 1-5

- (72) 발명자

로 이네 똥, 도미니꼬

프랑스 35 576 쎄송 쎄비네 쎄 에스 176 16 자크

데 양 블랑 아브뉘 데 양 블랑 975 페끄니꼴로르

에르 에 데 프랑스

미나르, 필립쁘

프랑스 35 576 쎄송 쎄비네 쎄 에스 176 16 자크

데 양 블랑 아브뉘 데 양 블랑 975 페끄니꼴로르

에르 에 데 프랑스

로베르, 장-뤽

프랑스 35 576 쎄송 쎄비네 쎄 에스 176 16 자크

데 양 블랑 아브뉘 데 양 블랑 975 페끄니꼴로르

에르 에 데 프랑스

- (74) 대리인

백만기, 양영준, 전경석

전체 청구항 수 : 총 4 항

(54) 발명의 명칭 인쇄 회로 기판 상에 실장된 안테나들의 격리의 향상

### (57) 요 약

본 발명은 동일한 기판(1) 상에 적어도 하나의 안테나(2, 3), 프로세싱 회로, 및 상기 프로세싱 회로를 덮는 커버(4)를 포함하는 회로에 관한 것이다. 상기 회로는 상기 안테나(3)와 상기 커버(4) 사이에, 상기 기판 상에 및 부분적으로 상기 커버 상에 부분적으로 실현된 적어도 하나의 격리 요소(6, 6')를 포함한다.

대 표 도 - 도1

## 특허청구의 범위

### 청구항 1

동일한 기판(1) 상에 적어도 하나의 안테나(2, 3), 프로세싱 회로, 및 상기 프로세싱 회로를 덮는 커버(4)를 포함하는 회로로서,

상기 안테나(3)와 상기 커버(4) 사이에, 상기 기판 상에 및 부분적으로 상기 커버 상에 부분적으로 실현된 슬롯 라인에 의해 형성되는 적어도 하나의 격리 요소(6, 6')를 포함하는 것을 특징으로 하는 회로.

### 청구항 2

제1항에 있어서, 상기 슬롯 라인(6, 6')은 제3 슬롯 라인(7)에 의해 상호접속되는 제1 슬롯 라인(6a, 6'a) 및 제2 슬롯 라인(6b, 6'b)을 포함하는 것을 특징으로 하는 회로.

### 청구항 3

제1항에 있어서, 상기 제1 및 제2 슬롯 라인들은 제1 길이, 상기 보드 상에서 각각 L1 및 L2와, 제2 길이, 상기 커버 상에서 각각 L'1 및 L'2를 갖고, L1 + L'1은 L2 + L'2와 동일하거나 또는 상이한 것을 특징으로 하는 회로.

### 청구항 4

제1항 또는 제2항에 있어서, 상기 제1 및 제2 슬롯 라인들의 길이는  $\lambda g/4$ 에 가깝고,  $\lambda g$ 는 동작 주파수에서의 파장인 것을 특징으로 하는 회로.

## 명세서

### 기술 분야

[0001] 본 발명은 일반적으로 무선 시스템들에서 이용되는 인쇄 회로 기판들에 관한 것이다. 본 발명은 더욱 구체적으로는, 동일한 기판 상에 적어도 하나의 안테나 및 차폐 커버와 같은 커버에 의해 덮이는 프로세싱 회로를 포함하는 기판들에 관한 것이다.

### 배경 기술

[0002] 무선 통신 분야에서, 사용 증가는 전송 회로들의 용량을 증가시키고 커버리지(coverage)를 향상시키기 위하여 MIMO(Multiple Input Multiple Output) 회로들의 사용이 증가하고 있다. 그 결과, 보다 많은 수의 안테나가 사용되고 있다. 안테나들이 인쇄 회로 기판 또는 PCB 상에 직접 인쇄되거나 배치될 때, 이것은 접지면에서, 다른 안테나들의 거동뿐만 아니라 안테나들 근처에 배치된 프로세싱 회로들의 거동에 영향을 미칠 가능성이 있는 전류들을 유발한다. 따라서 안테나들의 성능을 악화시키지 않고 전류 누설을 제한하기 위하여 요소들을 서로 격리하는 것이 필요하다. 또한, MIMO 시스템들의 경우에, 안테나들은 MIMO 시스템에 대해 최적의 성능을 제공하기 위해 요구되는 신호로부터 역상관(decorrelation)의 레벨을 획득하기 위해 강하게 격리되어야 한다. 그러나, 기판 상의 공간이 제한되고, 격리 제약들은 매우 강하다. 또한, 몇몇 주파수 대역들에서 동작하는 시스템들의 경우에, 대역들 간의 격리는 주파수 대역에서의 모든 라디오들(radios)의 올바른 공존을 보장하는 데 가장 빈번하게 요구된다.

[0003] 또한, 방사 레벨들을 줄임으로써, 전자기 간섭들 및 무선 주파수들을 줄이기 위해 프로세싱 회로의 꼭대기에 고정되는 차폐 커버들이 빈번하게 이용된다. 이러한 이용은, 현재의 무선 시스템들이 대체로 멀티 대역 및 멀티 모드이기 때문에, 점점 더 빈번하고, 이것은 더 큰 간섭 문제들을 초래하게 된다. 또한, 무선 장치들의 소형화 및 동일한 기판 상의 복수의 회로들의 접촉에 대한 경향은 향상된 격리 및 차폐를 요구한다. 또한, 무선 주파수들 및 전자기파들의 레벨들에 관한 조절은 점점 더 제한적이다.

[0004] 안테나들의 상호 결합(mutual coupling)을 줄이고 표면 전류 누설을 제한하기 위해 2개의 안테나 사이에 슬롯들을 이용하는 것이, 특히, 미국 특허 2003/0193437에 알려져 있다. 그러나, 이러한 타입의 격리는 슬롯들의 길이가  $\lambda/4$ 와 두드러지게(noticeably) 동일하기 때문에 표면을 요구하고,  $\lambda$ 는 회로의 동작 주파수에서

파장이다. 따라서, 2.4GHz의 동작 주파수에 대해서, 파장은 약 30mm이다.

## 발명의 내용

### 해결하려는 과제

[0005] 그러므로 본 발명은 인쇄 회로 기판의 사이즈를 증가시키지 않고 부가적인 컴포넌트들 또는 기계 부품들을 추가하지 않고 요구되는 격리가 획득될 수 있게 하는 위의 문제들에 대한 저비용 해결책을 제안한다.

### 과제의 해결 수단

[0006] 본 발명은 동일한 기판 상에 적어도 하나의 안테나, 프로세싱 회로 및 상기 프로세싱 회로를 덮는 커버를 포함하는 회로로서, 상기 안테나와 상기 커버 사이에, 상기 기판 상에 및 부분적으로 상기 커버 상에 부분적으로 실현된 슬롯 라인에 의해 형성된 적어도 하나의 격리 요소를 포함하는 것을 특징으로 하는 회로에 관한 것이다.

[0007] 일 실시예에 따르면, 상기 슬롯 라인은 제3 슬롯 라인에 의해 상호접속되는 제1 및 제2 슬롯 라인을 포함한다. 상기 제1 및 제2 슬롯 라인들은 제1 길이, 상기 보드 상에서 각각 L1 및 L2와, 제2 길이, 상기 커버 상에서 각각 L'1 및 L'2를 갖고, L1 + L'1은 L2 + L'2와 동일하거나 상이하다. 상기 제1 및 제2 슬롯 라인의 길이는  $\lambda_g/4$ 에 가깝고,  $\lambda_g$ 는 동작 주파수에서 파장이다.

### 도면의 간단한 설명

[0008] 본 발명의 다른 특성 및 이점들은 첨부된 도면을 참조하여 실현되는 실시예의 설명을 읽으면 알 수 있을 것이다.

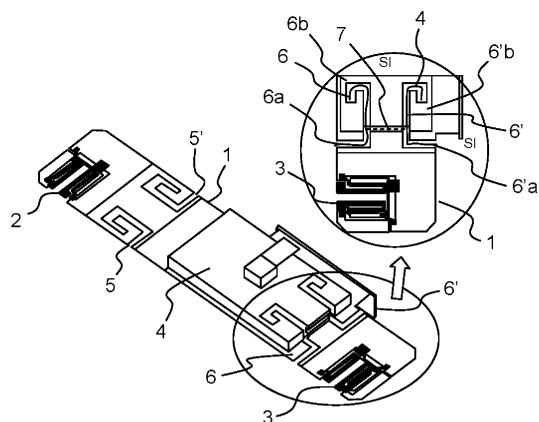

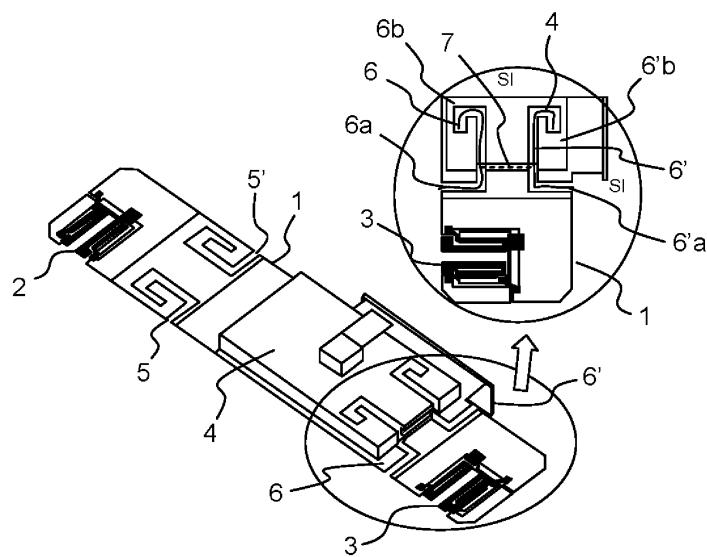

도 1은 본 발명의 실시예의 개략적인 투시도이고, 원형 부분은 본 발명이 실현되는 기판의 일부분의 확대도이다.

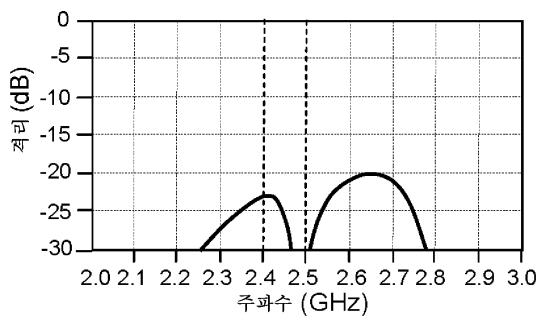

도 2는 본 발명에 따른 격리 요소 없이 도 1의 2개의 안테나 사이의 격리의 레벨을 도시한다.

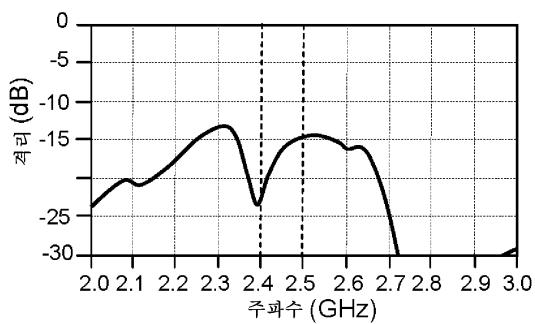

도 3은 본 발명에 따른 격리 요소를 갖는 2개의 안테나 사이의 격리의 레벨을 나타내는 곡선이다.

### 발명을 실시하기 위한 구체적인 내용

[0009] 본 발명은 셋톱박스 내로 접적될 수 있는 2x2 MIMO 회로를 갖는 2.4GHz의 대역에서 동작하는 2개의 안테나를 포함하는 애플리케이션에서 이용되는 인쇄 회로 기판을 언급하는 것에 의해 설명된다. 그러나, 이 실시예는 정보를 위해서만 제공되는 것이고 본 발명의 범위를 떠나지 않고 많은 방식으로 수정될 수 있다는 것이 이 기술분야의 통상의 기술자에게 분명하다. 본 발명은 모바일 장치들, 태블릿들, 게이트웨이들 등과 같은 무선 방식에서 동작하는 많은 장치에서 이용될 수 있다.

[0010] 도 1에 도시된 바와 같이, 기판(1) 상에 2개의 안테나(2 및 3)가 기판의 각각의 단에 실현되었다. 2개의 안테나(2 및 3) 사이에는 2개의 안테나에 의해 수신되고 방출되는 신호들을 위한 프로세싱 회로가 동일한 기판(1) 상에 실장되었다. 이 프로세싱 회로는 안테나들의 프로세싱 회로들을 격리하면서 전자기 간섭들 및 무선 주파수 간섭들을 줄이기 위해 차폐 커버(4)에 의해 덮인다.

[0011] 알려진 방식으로, 차폐 커버(4)는 일반적으로 스템핑(stamping)해서 컴포넌트들과 동일한 조립 절차 동안에 기판에 고정됨으로써, 즉, 컴포넌트 표면 실장 기술을 이용함으로써, 만들어진다. 커버는 컴포넌트들의 검사 및 수리를 가능하게 하기 위해 단일 부분에서 또는 2개의 부분에서 실현될 수 있다.

[0012] 도 1에 도시된 바와 같이, 안테나들 중 하나, 즉, 도시된 실시예에서의 안테나(2)는 상기 기판의 에지들을 따라 인쇄 회로 기판(1) 상에 직접 실현되는 2개의 격리 슬롯들(5, 5')에 의해 커버(4)로부터 격리된다. 그러나, 도 1에 도시된 바와 같이, 제2 안테나(3)는 커버(4) 근처에 배치된다. 인쇄 회로 기판의 표면을 증가시키지 않도록 하기 위해서, 도 1의 확대부에 도시된 바와 같이, 본 발명에 따라, 안테나(3)와 커버(4) 사이의 격리 요소는 기판(1) 상에 및 부분적으로 커버(4) 상에 부분적으로 실현된다. 더욱 정확한 방식으로, 확대부에 도시된 바와 같이, 격리 수단은 각각 2개의 부분, 즉, 6a, 6b, 6'a 및 6'b를 갖는 2개의 슬롯 라인들(6 및 6')에 의해 구성되고, 부분(6a 및 6'a)은 인쇄 회로 기판(1)에 실현되고, 부분(6b 및 6'b)은 커버(4)에 실현된다. 이들 2개의 슬롯 라인(6 및 6')이 인쇄 회로의 레벨에서 단락 회로로 되는 것을 방지하기 위해서, 그것들은 슬롯(7)에 의해 상호접속된다.

- [0013] 요구되는 격리를 획득하기 위해서, 각각의 슬롯(6, 6')의 총 길이는  $\lambda g/4$ 와 두드러지게(noticeably) 동일하도록 선택되고, 여기서  $\lambda g$ 는 동작 주파수에서 파장이다. 따라서, 부분들(6a 및 6'a)이 각각 길이들(L1 및 L2)을 갖는 경우 및 부분들(6b 및 6'b)이 각각 길이들(L'1 및 L'2)을 갖는 경우, 슬롯들(6 및 6')의 총 길이는  $L1 + L'1 @ L2 + L'2 @ \lambda g/4$ 로 되어야 한다. 그러나,  $L1 + L'1 \neq L2 + L'2$ 로 되는 해결책들이 또한 발명의 범위 내에 있다.

- [0014] 도 1에 도시된 바와 같은 장치는 명칭 HFSS(Ansys) 하에서 알려진 3D 전자기 시뮬레이션 툴로 시뮬레이션되었다. 제1 시뮬레이션은 본 발명에 따른 격리 요소 없이 실현되었고, 제2 시뮬레이션은 도 1에 도시된 바와 같은 격리 요소를 갖고 실현되었다.

- [0015] 도 2에 도시된 바와 같이, 본 발명에 따른 격리 요소 없이, 2.4GHz의 대역에서 격리 레벨은 최악의 경우에 약 14dB임을 알 수 있다.

- [0016] 도 3에 도시된 바와 같이, 2개의 안테나 사이의 격리 응답은 이제 2.4GHz의 대역에서 약 -20dB이고, 이것은 5dB 보다 많은 증가를 나타낸다. 안테나(3)가 여기(excited)될 때에 표면 전류들의 라인은 이를 격리 요소들 없이 획득된 결과에 대하여 격리 요소들(6 및 6')의 효율성을 보여준다. 따라서 2개의 안테나 간의 결합의 감소가 획득되고, 안테나(3)의 거동은 기판 상의 그것의 위치 및 시스템의 전체 접지에 그것의 접지면을 접속하는 방식에 덜 민감하다.

- [0017] 격리 요소를 실현하는 슬롯 라인들은 격리 레벨 또는 격리 대역을 증가시키는 그러한 방식으로 동일한 또는 상이한 길이를 가질 수 있다는 것이 이 기술분야의 통상의 기술자에게 분명하다. 또한, 슬롯들은 그것들의 위치와 호환되는 L 형태 또는 C 형태 또는 임의의 다른 형태를 가질 수 있다.

### 부호의 설명

- [0018]

- 1: 인쇄 회로 기판

- 2, 3: 안테나

- 4: 커버

- 5, 5': 격리 슬롯

- 6, 6': 격리 요소

- 6a, 6'a: 제1 슬롯 라인

- 6b, 6'b: 제2 슬롯 라인

- 7: 제3 슬롯 라인

## 도면

## 도면1

## 도면2

## 도면3