(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4406535号

(P4406535)

(45) 発行日 平成22年1月27日(2010.1.27)

(24) 登録日 平成21年11月13日(2009.11.13)

(51) Int.Cl.

F 1

|             |           |            |      |

|-------------|-----------|------------|------|

| HO1L 27/04  | (2006.01) | HO1L 29/78 | 657A |

| HO1L 29/78  | (2006.01) | HO1L 29/78 | 652G |

| HO1L 29/06  | (2006.01) | HO1L 29/78 | 652N |

| HO1L 29/47  | (2006.01) | HO1L 29/78 | 652P |

| HO1L 29/872 | (2006.01) | HO1L 29/78 | 653A |

請求項の数 7 (全 21 頁) 最終頁に続く

(21) 出願番号

特願2003-5271(P2003-5271)

(22) 出願日

平成15年1月14日(2003.1.14)

(65) 公開番号

特開2004-221218(P2004-221218A)

(43) 公開日

平成16年8月5日(2004.8.5)

審査請求日

平成17年7月6日(2005.7.6)

(73) 特許権者 000002037

新電元工業株式会社

東京都千代田区大手町2丁目2番1号

(74) 代理人 100102875

弁理士 石島 茂男

(74) 代理人 100106666

弁理士 阿部 英樹

(72) 発明者 黒崎 徹

埼玉県飯能市南町10番13号 新電元工

業株式会社飯能工場内

(72) 発明者 宍戸 寛明

埼玉県飯能市南町10番13号 新電元工

業株式会社飯能工場内

最終頁に続く

(54) 【発明の名称】ショットキーダイオード付きトランジスタ

## (57) 【特許請求の範囲】

## 【請求項 1】

第1導電型の単結晶層を有する半導体装置であって、前記単結晶層の内部の表面側に形成された第2導電型のベース拡散領域と、前記単結晶層のベース拡散領域の底面よりも深い部分であるドレイン領域と、前記ベース拡散領域の内部の表面側に形成され、前記ベース拡散領域によって前記ドレイン領域とは絶縁された第1導電型のソース拡散領域と、

前記単結晶層に、前記ベース拡散領域の深さよりも深く形成された溝であって、前記ソース拡散領域と、前記ソース拡散領域と前記ドレイン領域との間に位置するベース拡散領域と、前記ドレイン領域とに接觸する位置に配置されたゲート溝と、

前記ゲート溝内部の側面に位置し、上部が前記ソース拡散領域と接觸し、下部が前記ドレイン領域と接觸し、中間部が前記ベース拡散領域と接觸して配置されたゲート絶縁膜と、

前記ゲート溝の内部に位置し、前記ソース拡散領域から前記ドレイン領域の範囲に亘って、前記ゲート絶縁膜と接觸して配置されたゲート電極プラグとを有し、

前記ゲート電極プラグに電圧を印加し、前記ベース拡散領域の前記ゲート絶縁膜と接觸する部分に反転層を形成すると、前記ソース拡散領域と前記ドレイン領域とが前記反転層で接続されるように構成されたトランジスタと、

前記単結晶層に形成され前記ベース拡散領域と接觸した逆阻止溝と、

前記逆阻止溝と前記逆阻止溝とで挟まれた部分の前記単結晶層である整流領域の表面に

10

20

形成され、前記整流領域とショットキー接合を形成するショットキー電極膜とを有するシヨットキーダイオードと、

前記各逆阻止溝の内部には、第2導電型の半導体材料から成り、前記整流領域とp n接合を形成し、前記ベース拡散領域に印加される電圧が印加される逆阻止領域が配置されて形成されたp nダイオードと、

を有し、

前記ゲート溝内部の底面と前記ゲート電極プラグとの間の位置には、第2導電型の半導体材料から成る埋込領域が前記ゲート電極プラグとは絶縁された状態で配置され、

前記ゲート溝と前記逆阻止溝の深さは同一にされ、前記埋込領域と前記逆阻止領域の底部は前記ゲート溝と前記逆阻止溝の底面にそれぞれ接触された半導体装置。

10

**【請求項2】**

前記トランジスタと前記ショットキーダイオードを複数有する請求項1記載の半導体装置。

**【請求項3】**

前記ソース拡散領域と前記ベース拡散領域に接続されたソース電極膜を有し、

前記ソース電極膜と前記ショットキーディオードとは互いに接続された請求項1又は請求項2のいずれか1項記載の半導体装置。

**【請求項4】**

前記逆阻止溝は平面形状が四角リング状に形成され、前記整流領域を取り囲んで配置された請求項1乃至請求項3のいずれか1項記載の半導体装置。

20

**【請求項5】**

前記埋込領域は浮遊電位に置かれた請求項1乃至請求項4のいずれか1項記載の半導体装置。

**【請求項6】**

前記ゲート溝内の底面上に、前記埋込領域と前記ベース拡散領域とに接觸した第2導電型の接続領域を配置し、前記接続領域によって、前記埋込領域と前記ベース拡散領域とが電気的に接続された請求項1乃至請求項4のいずれか1項記載の半導体装置。

**【請求項7】**

前記単結晶層には、同心状に配置されたリング状のガード溝が複数本形成され、前記各ガード溝内部には、第2導電型の前記半導体材料から成り、前記単結晶層とp n接合を形成するガード領域が配置され、

30

前記ゲート溝と前記逆阻止溝とは、最内周の前記ガード溝によって取り囲まれた請求項1乃至請求項6のいずれか1項記載の半導体装置。

**【発明の詳細な説明】**

**【0001】**

**【発明の属する技術分野】**

本発明は半導体装置にかかり、特に、活性領域を溝内に配置された半導体単結晶で囲んだ半導体装置に関する。

**【0002】**

**【従来の技術】**

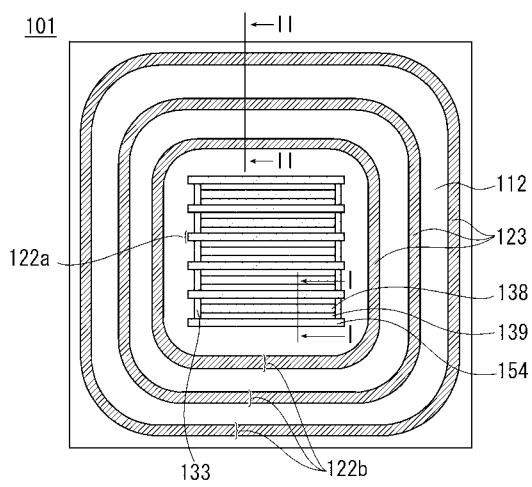

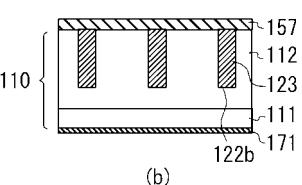

図33は従来技術のMOSFET101の拡散構造を説明するための平面図であり、図34(a)、(b)は、そのI-I線とII-II線の切断面図である。

40

**【0003】**

このMOSFET101は、n型のエピタキシャル層から成り、n<sup>+</sup>型のシリコン単結晶から成る基板111と、該基板111上にエピタキシャル成長によって形成された単結晶層112とを有している。

**【0004】**

基板111の単結晶層112とは反対側の面には、金属薄膜から成るドレイン電極膜171が配置されている。

**【0005】**

50

単結晶層 112 の略中央位置には、不純物拡散によって形成された p 型のベース拡散領域 133 が配置されている。

【 0006 】

そのベース拡散領域 133 を分断するように、細長の活性溝 122a が複数本互いに平行に配置されている。ベース拡散領域 133 内の位置であって各活性溝 122a の片側又は両側に隣接する部分には、不純物拡散によって n 型のソース拡散領域 139 が形成されている。

【 0007 】

隣接する二本の活性溝 122a の間では、二個のソース拡散領域 139 が互いに所定間隔で対向する位置に配置されており、その二個のソース拡散領域 139 の間の部分には、不純物拡散によって p<sup>+</sup>型のオーミック領域 138 が形成されている。

10

【 0008 】

活性溝 122a 及びベース拡散領域 133 の周囲には、幅が細く、四角リング形状のガード溝 122b が複数本同心状に配置されており、従って、活性溝 122a 及びベース拡散領域 133 は、各ガード溝 122b によって同心状に取り囲まれた状態になっている。

【 0009 】

各活性溝 122a の内周側面及び底面には、ゲート絶縁膜 151 が形成されている。このゲート絶縁膜 151 で囲まれた領域内は、ポリシリコン材料から成るゲート電極プラグ 158 が充填されている。

【 0010 】

他方、ガード溝 122b の内周側面及び底面には、ゲート絶縁膜 151 は形成されておらず、各ガード溝 122b の内部は、エピタキシャル法によって成長された p 型のシリコン単結晶から成るガード溝内充填物 123 によって充填されている。

20

【 0011 】

ゲート電極プラグ 158 やガード溝内充填物 123 の上には、酸化膜 157 が配置されている。この酸化膜 157 は、パターニングにより、ソース拡散領域 139 とオーミック領域 138 の上の部分に開口が形成されており、ソース拡散領域 139 の一部表面とオーミック領域 138 の一部表面は、その開口底面に露出されている。

【 0012 】

それら露出した領域の表面と酸化膜 157 の表面には、金属薄膜から成るソース電極 161 が形成されている。

30

【 0013 】

ベース拡散領域 133 は、ソース拡散領域 139 よりも下方位置でゲート絶縁膜 151 に接触しており、その接触した部分を反転領域とすると、n チャネル型 MOS トランジスタの場合、ソース電極 161 を接地電位に接続し、ドレイン電極膜 171 に正電圧を印加し、ベース拡散領域 133 と単結晶層 112 との間の p-n 接合を逆バイアスさせた状態で、ゲート電極プラグ 158 にしきい値電圧以上の正電圧を印加すると、ベース拡散領域 133 の反転領域の部分が n 型に反転し、その反転層によってソース拡散領域 139 と単結晶層 112 とが接続され、電流が流れれる。

【 0014 】

40

逆に、ドレイン電極膜 171 が接地電位に接続され、ソース電極 161 に正電圧が印加されると、ベース拡散領域 133 と単結晶層 112 との間の p-n 接合が順バイアスされ、その p-n 接合を通って電流が流れてしまう。

【 0015 】

その状態から、ベース拡散領域 133 と単結晶層 112 との間の p-n 接合が逆バイアスされても、p-n 接合に、逆方向回復時間の間電流が流れ続け MOSFET 101 が制御不能になる。

【 0016 】

これを防止するために、ベース拡散領域 133 と単結晶層 112 との間の p-n 接合と並列にショットキーダイオードを外付けしていたが、コスト高になるため、解決が望まれて

50

いる。

**【0017】**

**【発明が解決しようとする課題】**

本発明は上記半導体装置の不都合を解決するために創作されたものであり、その目的は、逆方向回復時間の短いトランジスタを提供することにある。

**【0018】**

**【課題を解決するための手段】**

上記課題を解決するために、請求項1記載の発明は、第1導電型の単結晶層を有する半導体装置であって、前記単結晶層の内部の表面側に形成された第2導電型のベース拡散領域と、前記単結晶層のベース拡散領域の底面よりも深い部分であるドレイン領域と、前記ベース拡散領域の内部の表面側に形成され、前記ベース拡散領域によって前記ドレイン領域とは絶縁された第1導電型のソース拡散領域と、前記単結晶層に、前記ベース拡散領域の深さよりも深く形成された溝であって、前記ソース拡散領域と、前記ソース拡散領域と前記ドレイン領域との間に位置するベース拡散領域と、前記ドレイン領域とに接觸する位置に配置されたゲート溝と、前記ゲート溝内部の側面に位置し、上部が前記ソース拡散領域と接觸し、下部が前記ドレイン領域と接觸し、中間部が前記ベース拡散領域と接觸して配置されたゲート絶縁膜と、前記ゲート溝の内部に位置し、前記ソース拡散領域から前記ドレイン領域の範囲に亘って、前記ゲート絶縁膜と接觸して配置されたゲート電極プラグとを有し、前記ゲート電極プラグに電圧を印加し、前記ベース拡散領域の前記ゲート絶縁膜と接觸する部分に反転層を形成すると、前記ソース拡散領域と前記ドレイン領域とが前記反転層で接続されるように構成されたトランジスタと、前記単結晶層に形成され前記ベース拡散領域と接觸した逆阻止溝と、前記逆阻止溝と前記逆阻止溝とで挟まれた部分の前記単結晶層である整流領域の表面に形成され、前記整流領域とショットキー接合を形成するショットキー電極膜とを有するショットキーダイオードと、前記各逆阻止溝の内部には、第2導電型の半導体材料から成り、前記整流領域とpn接合を形成し、前記ベース拡散領域に印加される電圧が印加される逆阻止領域が配置されて形成されたpnダイオードと、を有し、前記ゲート溝内部の底面と前記ゲート電極プラグとの間の位置には、第2導電型の半導体材料から成る埋込領域が前記ゲート電極プラグとは絶縁された状態で配置され、前記ゲート溝と前記逆阻止溝の深さは同一にされ、前記埋込領域と前記逆阻止領域の底部は前記ゲート溝と前記逆阻止溝の底面にそれぞれ接觸された半導体装置である。

請求項2記載の発明は、前記トランジスタと前記ショットキーダイオードを複数有する請求項1記載の半導体装置である。

請求項3記載の発明は、前記ソース拡散領域と前記ベース拡散領域に接続されたソース電極膜を有し、前記ソース電極膜と前記ショットキー電極膜とは互いに接続された請求項1又は請求項2のいずれか1項記載の半導体装置である。

請求項4記載の発明は、前記逆阻止溝は平面形状が四角リング状に形成され、前記整流領域を取り囲んで配置された請求項1乃至請求項3のいずれか1項記載の半導体装置である。

請求項5記載の発明は、前記埋込領域は浮遊電位に置かれた請求項1乃至請求項4のいずれか1項記載の半導体装置である。

請求項6記載の発明は、前記ゲート溝内の底面上に、前記埋込領域と前記ベース拡散領域とに接觸した第2導電型の接続領域を配置し、前記接続領域によって、前記埋込領域と前記ベース拡散領域とが電気的に接続された請求項1乃至請求項4のいずれか1項記載の半導体装置である。

請求項7記載の発明は、前記単結晶層には、同心状に配置されたリング状のガード溝が複数本形成され、前記各ガード溝内部には、第2導電型の前記半導体材料から成り、前記単結晶層とpn接合を形成するガード領域が配置され、前記ゲート溝と前記逆阻止溝とは、最内周の前記ガード溝によって取り囲まれた請求項1乃至請求項6のいずれか1項記載の半導体装置である。

**【0019】**

10

20

30

40

50

本発明は上記のように構成されており、ショットキー接合が、互いに平行な逆阻止溝で挟まれてあり、逆阻止溝内部に配置された逆阻止領域から、ショットキー接合の下方に向けて空乏層が伸びるようになっている。

**【0020】**

ショットキー接合の逆阻止溝に沿った方向の長さは逆阻止溝よりも短くなっている。ショットキー接合の両側に、逆阻止溝内部の逆阻止領域がはみ出て位置するようになっている。逆阻止領域と整流領域との間ではpn接合が形成されており、相対して位置する逆阻止溝から空乏層が広がり、ショットキー接合の下方で空乏層同士が接触した場合、ショットキー接合が空乏層で覆われ、等価的に、逆バイアス状態のpn接合と逆バイアス状態のショットキー接合が直列接続された状態になる。

10

**【0021】**

その直列接続回路の耐圧は逆阻止領域と整流領域の間のpn接合の耐圧で決まるので、ショットキー接合の耐電圧よりも大きくなる。

**【0022】**

逆阻止溝は、ゲート溝やガード溝と一緒に形成されており、各溝の深さは等しくなっている。ゲート溝の底部には、ドレイン領域とpn接合を形成する埋込領域が配置されている。

**【0023】**

埋込領域に隣接する他の埋込領域があった場合、その間の距離aは互いに等しくなっている。

20

**【0024】**

また、埋込領域に隣接する逆阻止領域があった場合、埋込領域と逆阻止領域の間の距離bは互いに等しくなっており、且つ、距離aと距離bも互いに等しくなっている。

**【0025】**

従って、相対向して位置する逆阻止領域同士の空乏層が接触するような逆電圧が印加されたときには、埋込領域から広がった空乏層は、他の埋込領域から広がった空乏層や逆阻止領域から広がった空乏層と接触するので、トランジスタの耐圧も高くなっている。

**【0026】**

**【発明の実施の形態】**

以下で図面を参照し、本発明の実施例について説明する。

30

本実施例及び後述する各実施例では、第1導電型がn型であれば第2導電型はp型であり、第1導電型がp型であれば第2導電型はn型である。本発明にはその両方の場合が含まれる。

**【0027】**

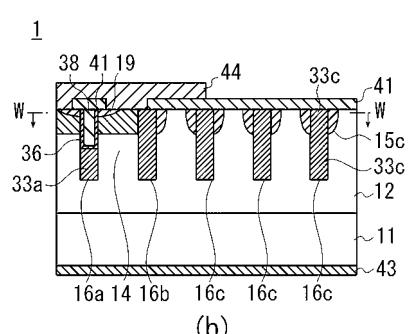

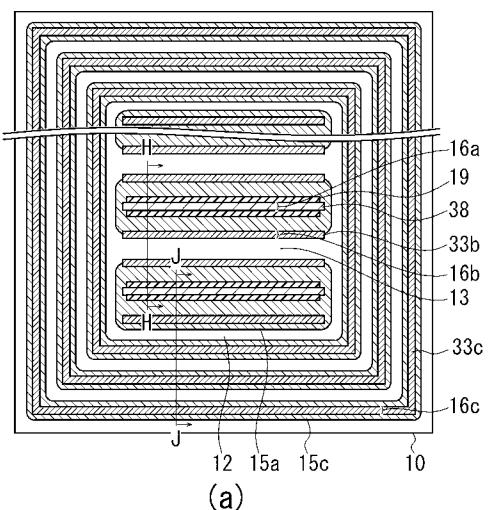

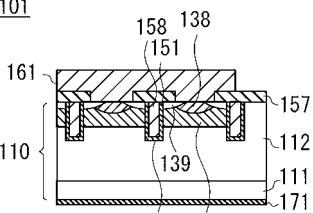

図22(a)は、本発明の一例の半導体装置1の活性領域の拡散構造を示す縦断面図であり、図22(b)は、活性領域と、その活性領域を取り囲む耐圧領域の拡散構造を示す縦断面図である。

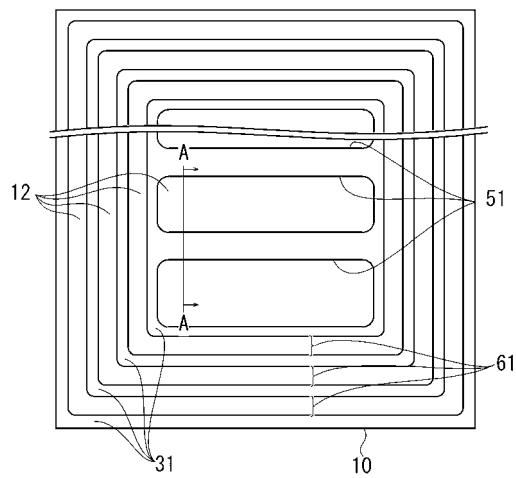

**【0028】**

図31(a)は、図22(a)のV-V線の横断面図と図22(b)のW-W線の横切断面図に相当する図面であり、逆に、図22(a)、(b)は、それぞれ図31(a)のH-H線、J-J線の縦切断面図に相当する図面である。

40

**【0029】**

図22(a)、(b)の符号11は、シリコン単結晶等の半導体材料から成る第1導電型の半導体基板を示している。

**【0030】**

半導体基板11上には、半導体基板11と同じか、又は異なる半導体材料がエピタキシャル成長法によって成長され、第1導電型の単結晶層12が形成されている。

**【0031】**

単結晶層12内部の表面近傍位置には、複数個のベース拡散領域15aが配置されている。各ベース拡散領域15aは、第2導電型であり、単結晶層12とpn接合を形成して

50

いる。符号 1 4 は、ベース拡散領域 1 5 a の下方に位置する単結晶層 1 2 から成るドレイン領域である。

【 0 0 3 2 】

単結晶層 1 2 にはエッチングによって細長い直角四角形形状のゲート溝 1 6 a と逆阻止溝 1 6 b と、四角リング状のガード溝 1 6 c が形成されている。

【 0 0 3 3 】

それらの溝のうち、ゲート溝 1 6 a はベース拡散領域 1 5 a の中央に 1 本又は二本以上配置されている。ここでは 1 本であるが、二本以上配置される場合は、互いに平行に配置される。逆阻止溝 1 6 b は、ゲート溝 1 6 a の両側に、ゲート溝 1 6 a に対して平行に配置されている。10

【 0 0 3 4 】

ガード溝 1 6 c はベース拡散領域 1 5 a の周囲に、ベース拡散領域 1 5 a を取り囲んで配置されている。

【 0 0 3 5 】

各溝 1 6 a ~ 1 6 c は、同一工程で形成されており、同じ深さ及び同じ幅にされている。また、各溝 1 6 a ~ 1 6 c の深さはベース拡散領域 1 5 a よりも深く、且つ、半導体基板 1 1 には達しない程度の深さである。

【 0 0 3 6 】

各溝 1 6 a ~ 1 6 c のうち、逆阻止溝 1 6 b とガード溝 1 6 c の内部には、エピタキシャル成長によって形成された第 2 導電型の半導体材料が底面から上端部まで配置されており、その半導体材料によって、逆阻止領域 3 3 b とガード領域 3 3 c とがそれぞれ形成されている。20

【 0 0 3 7 】

他方、ゲート溝 1 6 a の内部では、下部にだけその半導体材料が配置されており、その半導体材料によって、埋込領域 3 3 a が構成されている。

【 0 0 3 8 】

ここでは半導体材料はシリコン単結晶であるが、他の半導体の単結晶であってもよく、ポリシリコンのような多結晶であってもよい。

【 0 0 3 9 】

符号 1 3 は、逆阻止領域 3 3 b で挟まれた単結晶層 1 2 の領域から成る整流領域である。30

【 0 0 4 0 】

ゲート溝 1 6 a 内部の上部の半導体材料が存しない部分は、ゲート溝 1 6 a の底面及び側面にはゲート絶縁膜 3 6 が配置されている。ゲート絶縁膜 3 6 は、単結晶層 1 2 を熱酸化処理して形成する酸化物や、他の方法によって形成する窒化物膜等を用いることができる。

【 0 0 4 1 】

ゲート溝 1 6 a 内部のゲート絶縁膜 3 6 で囲まれた領域には、ゲート電極プラグ 3 8 が配置されている。

【 0 0 4 2 】

ベース拡散領域 1 5 a の内部の表面近傍位置であって、ゲート絶縁膜 3 6 と接触する位置には、第 1 導電型のソース拡散領域 1 9 が配置されている。40

【 0 0 4 3 】

ベース拡散領域 1 5 a とソース拡散領域 1 9 の表面は露出され、その表面にソース電極膜 4 4 が配置されている。

【 0 0 4 4 】

半導体基板 1 1 の裏面には、ドレイン電極膜 4 3 が配置されており、第 1 導電型が n 型である n チャネル M O S F E T の場合、ソース電極膜 4 4 を接地させ、ドレイン電極膜 4 3 に正電圧を印加した状態で、ゲート電極プラグ 3 8 にしきい値電圧以上の正電圧を印加すると、ベース拡散領域 1 5 a のゲート絶縁膜 3 6 と接した部分が第 1 導電型に反転する50

。その反転によって第1導電型の反転層が形成され、反転層で、ソース拡散領域19とドレイン領域14とが接続され、反転層を通ってドレイン領域14からソース拡散領域19に電流が流れる。

#### 【0045】

このとき、ベース拡散領域15aとドレイン領域14との間のpn接合は逆バイアスされており、pn接合には電流は流れない。

#### 【0046】

整流領域13は、二本の逆阻止領域33bによって挟まれており、且つ、整流領域13の表面は露出され、ショットキー電極膜45と接触している。ここでは、ショットキー電極膜45はソース電極膜44と一緒に形成され、ソース電極膜44に接続されている。

10

#### 【0047】

ショットキー電極膜45は、整流領域13とショットキー接合を形成する材料が選択されており、そのショットキー接合の極性は、ベース拡散領域15aと単結晶層12との間のpn接合が逆バイアスされる場合には、ショットキー接合も逆バイアスされ、pn接合が順バイアスされる場合には、ショットキー接合も順バイアスされるようになっている。

#### 【0048】

逆阻止領域33bはソース電極膜44と接触し、その結果、逆阻止領域33bには、ベース拡散領域15aやソース拡散領域19に印加される電圧が印加される。

#### 【0049】

逆阻止領域33bは第2導電型であり、整流領域13を含む単結晶層12とpn接合を形成している。ベース拡散領域15aと単結晶層12とが逆バイアスされるときには、逆阻止領域33bと整流領域13との間のpn接合も逆バイアスされる。従って、ショットキー電極膜45と整流領域13の間に形成されるショットキー接合が逆バイアスされるときには逆阻止領域33bと単結晶層12との間に形成されるpn接合も逆バイアスされる。

20

#### 【0050】

逆バイアスにより、ショットキー接合から整流領域13内の深さ方向に向けて空乏層が広がる場合には、逆阻止領域33bから整流領域13内に向けて横方向に空乏層が広がる。

#### 【0051】

整流領域13を挟んで隣接する逆阻止領域33b間の距離は、逆阻止領域33bの深さよりも小さくされており、ショットキー接合から広がった空乏層が、逆阻止領域33bの底部に達するよりも小さい電圧で、逆阻止領域33bから広がった空乏層同士が互いに接触する。その結果、整流領域13の内部はpn接合から広がった空乏層で満たされる。

30

#### 【0052】

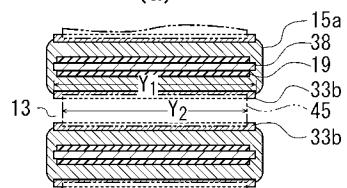

逆阻止領域33bの長さ方向に沿ったショットキー電極膜45の長さは、細長の逆阻止領域33bの長さよりも小さくされている。図31(b)は、その様子を示す平面図であり、逆阻止領域33bの長さ $Y_1$ の方が、ショットキー電極膜45の長さ $Y_2$ よりも長くなっている。

#### 【0053】

従って、逆阻止領域33bの両端部分は、ショットキー電極膜45よりもはみ出しており、逆阻止領域33bの端部と、それに相対する逆阻止領域33bの端部との間の位置では、ショットキー電極膜45が配置されておらず、ショットキー接合は形成されていない。

40

#### 【0054】

従って、対向する逆阻止領域33bから広がった空乏層が互いに接触したときには、ショットキー接合は、pn接合から広がった空乏層で覆われる。この状態では、等価回路上、逆バイアスされたショットキー接合と逆バイアスされたpn接合とは直列に接続された状態になる。

#### 【0055】

50

一般に、ショットキー接合の逆方向の耐電圧は、p n接合の逆方向耐電圧に比べて小さいが、単結晶層12とショットキー電極膜45の間の逆方向耐電圧は、p n接合の耐電圧の大きさ以上になる。

#### 【0056】

埋込領域33aは、ソース拡散領域19やドレイン領域14とは電気的に接続されておらず、浮遊電位に置かれている。逆バイアス状態のときベース拡散領域15aや逆阻止領域33bから単結晶層12の深さ方向に広がった空乏層が埋込領域33aに達すると、埋込領域33aの電位が安定し、埋込領域33aからも単結晶層12内に向けて空乏層が広がるようになる。

#### 【0057】

活性領域内で、各溝16a～16cの底部とベース拡散領域15aの底部間の部分では、その部分の第1導電型の領域(整流領域13を含む単結晶層12)が全部空乏化したときに、同じ部分の第2導電型の領域(埋込領域33aと逆阻止領域33bの底部)も全部空乏化するように、第1、第2の導電型の不純物総量が設定されている。各溝16a～16c間に広がった空乏層は、更に各溝16a～16cの底部から半導体基板11に向けて均等に広がる。

#### 【0058】

ガード領域33cは、ソース拡散領域19やドレイン領域14とは電気的に接続されておらず、浮遊電位に置かれている。ベース拡散領域15aや逆阻止領域33bから単結晶層12の横方向に向けて広がった空乏層が、ガード領域33cに達すると、ガード領域33cの電位が安定し、ガード領域33cからも更に横方向外側に向けて空乏層が広がる。

#### 【0059】

結局、埋込領域33a及び逆阻止領域33bやガード領域33cが設けられているため、空乏層が大きく広がり、耐圧が高くなっている。

#### 【0060】

上記のように、ベース拡散領域15aと単結晶層12との間のp n接合は、通常では逆バイアス状態に置かれているが、ドレイン電極膜43とソース電極膜44の電位が逆転し、ベース拡散領域15aと単結晶層12との間のp n接合が順バイアスされる場合は、ショットキー接合も順バイアスされる。

#### 【0061】

p n接合とショットキー接合は並列接続されており、p n接合の順方向導通電圧よりもショットキー接合の順方向導通電圧の方が低いため、ショットキー接合に電流が流れ、p n接合は、導通したショットキー接合の順方向導通電圧によってクランプされ、電流は流れない。

#### 【0062】

その状態からソース電極膜44とドレイン電極膜43の電圧の極性が反転し、ショットキー接合が順バイアス状態から逆バイアス状態になると、ショットキー接合の逆方向回復時間の経過後、電流は停止する。

#### 【0063】

ショットキー接合の逆方向回復時間はp n接合の逆方向回復時間に比べて非常に短時間なので、電流が停止するまでの時間は短い。

#### 【0064】

なお、p n接合には順方向電流が流れていないので、p n接合の逆方向回復時間は、電流が停止する時間に影響を与えない。

#### 【0065】

次に、本発明の半導体装置の製造工程を説明する。特に断らない限り、絶縁膜や金属膜のパターニングはフォトレジスト工程とエッチング工程によって行うが、その説明は省略する。また、下記の各工程によって裏面に薄膜が形成される場合があるが、特に断らない限り、その説明は省略する。

#### 【0066】

10

20

30

40

50

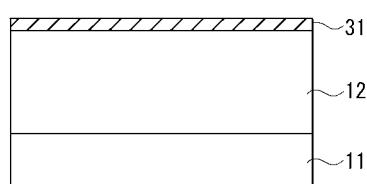

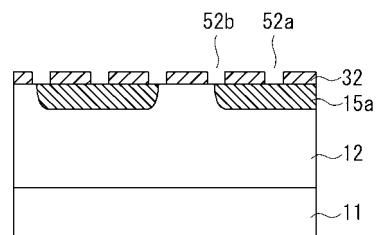

図1は、第1導電型の半導体基板11上に、第1導電型の単結晶層12がエピタキシャル成長によって形成され、更に、単結晶層12表面に、絶縁膜31が形成された状態の断面図を示している。ここでは、半導体基板11と単結晶層12はn型のシリコン単結晶であるが、他の半導体の単結晶であってもよい。また、この絶縁膜31及び後述する絶縁膜は、この例ではシリコン酸化膜であるが、シリコン窒化膜等の他の絶縁膜であってもよい。

#### 【0067】

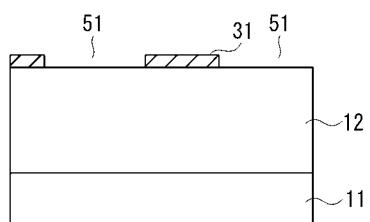

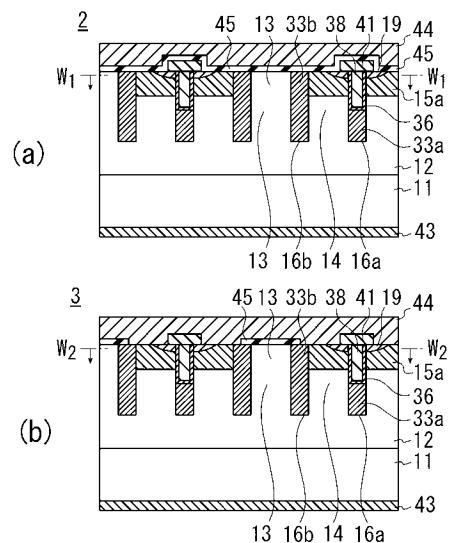

次に、絶縁膜31をパターニングする。図24はその状態の平面図であり、そのパターニングにより、絶縁膜31には、四角リング状であって、同心状に複数本配置されたリング状開口61と、最内周のリング状開口61で囲まれた複数の長方形のベース開口51が形成される。

#### 【0068】

この図24及び後述する各平面図中の符号10は、一枚の半導体基板11上に形成される複数個の半導体装置1の境界を示している。一の半導体装置1の境界10と、同じ半導体基板11上の他の半導体装置1の境界10間は、互いに一定距離だけ離間しており、境界10と境界10との間の位置が切断されることで、複数の半導体装置1同士が分離されるようになっている。最外周のリング状開口61の外周は、境界10から一定距離だけ離れている。

#### 【0069】

各ベース開口51は互いに平行に配置されている。また、各ベース開口51の四辺のうちの一辺は、リング状開口61の二辺に対して平行になっている。図2は、図24のA-A線切断面図である。

#### 【0070】

ベース開口51とリング状開口61の底面には、単結晶層12が露出されており、絶縁膜31の上方から、ホウ素等の第2導電型の不純物を打ち込むと、ベース開口51の底面下に位置する単結晶層12の内部表面近傍部分に第2導電型の高濃度不純物領域が形成される。

#### 【0071】

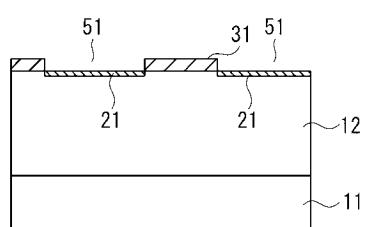

図3の符号21は、ベース開口51底面下に形成された高濃度不純物領域を示している。

#### 【0072】

次に、熱処理を行い、高濃度不純物領域21を拡散させると、ベース開口51とリング状開口61の下方位置に、ベース開口51の形状とリング状開口61の形状に近似した第2導電型のベース拡散領域と補助拡散領域とがそれぞれ形成される。

#### 【0073】

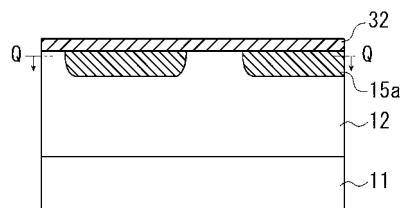

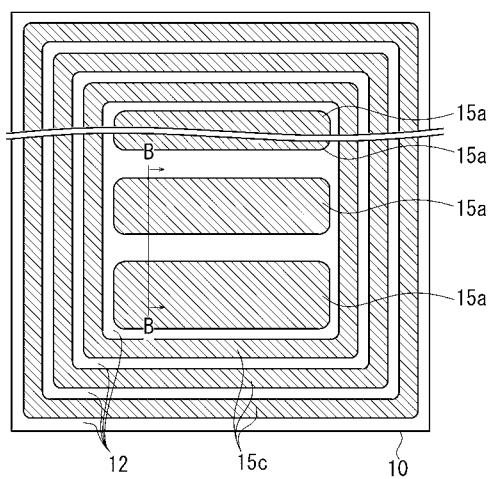

図25の符号15aはベース拡散領域を示しており、符号15cは、補助拡散領域を示している。図4は、図25のB-B線縦断面図に相当し、逆に、図25は、図4のQ-Q線横断面図に相当する。

#### 【0074】

図4の符号32は、第2導電型の高濃度不純物領域21を拡散させた後に観察される酸化物膜を示しており、ベース拡散領域15aや補助拡散領域15cを含む単結晶層12の表面は、酸化物膜32によって覆われている。

#### 【0075】

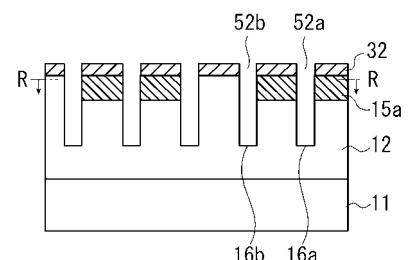

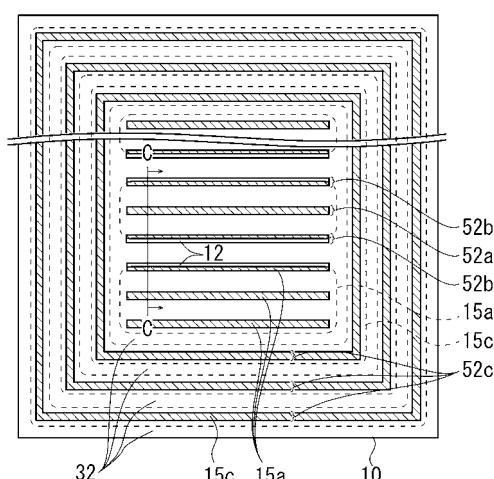

その状態から酸化物膜32をパターニングし、図26に示すように、ベース拡散領域15a上に位置し、平面形状が細長で長方形形状のゲート溝用窓開部52aと、逆阻止溝用窓開部52bとを形成し、補助拡散領域15cの幅方向中央に位置し、平面形状が四角リング状であって、ゲート溝用窓開部52a及び逆阻止溝用窓開部52bを取り囲む位置に、ガード溝用窓開部52cを形成する。

#### 【0076】

ゲート溝用及び逆阻止溝用窓開部52a、52bは各ベース拡散領域15aの長辺に対

10

20

30

40

50

して平行であり、ゲート溝用窓開部 52a は、各ベース拡散領域 15a の幅方向略中央位置に 1 乃至 2 本以上ずつ(本例では 1 本)配置され、逆阻止溝用窓開部 52b は、各ベース拡散領域 15a の相対する長辺上の位置、又は長辺近傍であってベース拡散領域 15a 内の位置に配置されている。

#### 【0077】

従って、ゲート溝用窓開部 52a と逆阻止溝用窓開部 52b は互いに平行であり、且つ、1 乃至 2 本以上のゲート溝用窓開部 52a は、2 本の逆阻止溝用窓開部 52b の間に位置している。

#### 【0078】

また、ガード溝用窓開部 52c は直角四角形であり、ゲート溝用窓開部 52a と逆阻止溝用窓開部 52b は、ガード溝用窓開部 52c の平行な二辺に対して平行になっている。 10

#### 【0079】

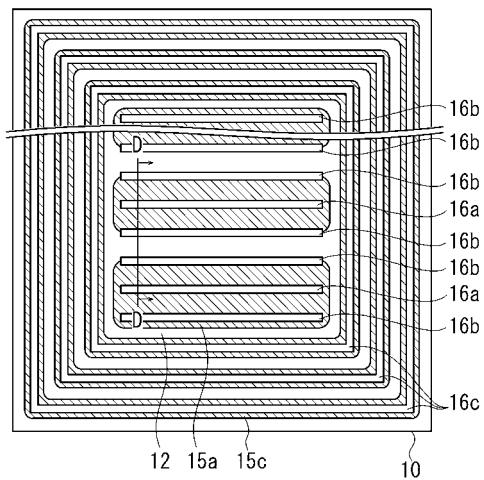

図 5 は、図 26 の C - C 線切断面図である。各溝用窓開部 52a ~ 52c の底面には、ベース拡散領域 15a の表面、又はベース拡散領域 15a の表面と単結晶層 12 の表面とが露出されており、酸化物膜 32 をマスクとして単結晶層 12 のエッチングを行うと、図 6、図 27 に示すように、ゲート溝用、逆阻止溝用、及びガード溝用窓開部 52a ~ 52c の底面下に、それぞれゲート溝 16a、逆阻止溝 16b、及びガード溝 16c がそれぞれ形成される。

#### 【0080】

図 6 は、図 27 の D - D 線切断面図に相当する図面であり、図 27 は、図 6 の R - R 線切断面図に相当する図面である。 20

#### 【0081】

各溝 16a ~ 16c の断面形状は長方形であり、深さはベース拡散領域 15a や 補助拡散領域 15c よりも深いため、各溝 16a ~ 16c の底面は、ベース拡散領域 15a の底面や 補助拡散領域 15c の底面と、半導体基板 11 の間に位置している。

#### 【0082】

ガード溝 16c の幅は、補助拡散領域 15c の幅よりも狭く、ガード溝 16c は、補助拡散領域 15c の幅方向中央に位置しているため、各補助拡散領域 15c は、中央部分が掘削され、外周部分と内周部分に二分される。

#### 【0083】

なお、各溝 16a ~ 16c は同一工程で形成されるため、同一深さになっている。また各溝 16a ~ 16c の幅と、各溝 16a ~ 16c 間の間隔は等しくされている。 30

#### 【0084】

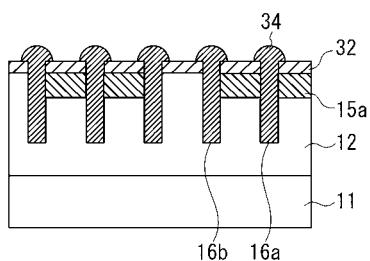

次に、エピタキシャル成長法によって、各溝 16a ~ 16c の内部側面及び底面に露出する単結晶層 12 (ベース拡散領域 15a や 補助拡散領域 15c を含む。以下同じ。) の表面に第 2 導電型の半導体単結晶を成長させると、各溝 16a ~ 16c の内部は、その半導体単結晶によって充填される。ここでは、半導体単結晶としてシリコン単結晶が用いられている。

#### 【0085】

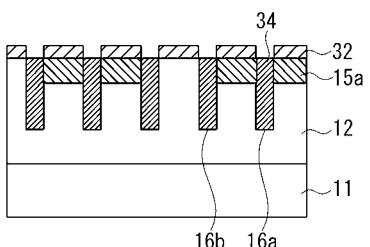

図 7 はその状態を示す図であり、符号 34 は、その各溝 16a ~ 16c 内に充填された充填物を示している。 40

#### 【0086】

本発明の半導体装置では、各溝 16a ~ 16c の開口の平面形状が直角四角形になっており、底面と側面から均一に半導体単結晶が成長し、内部が隙間なく充填される。

#### 【0087】

各溝 16a ~ 16c 内の充填物 34 は、各溝 16a ~ 16c の底面と側面に露出する単結晶層 12 に密着している。

#### 【0088】

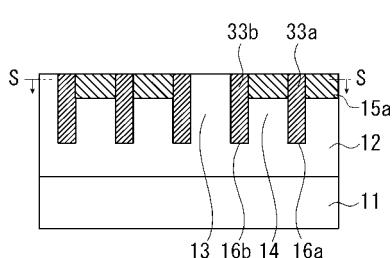

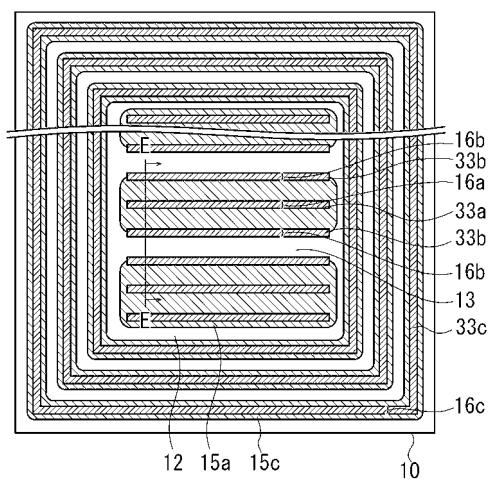

ここでは充填物 34 は、酸化物膜 32 の表面よりも高い位置まで盛り上がっており、エッチングにより、図 8 に示すように、単結晶層 12 よりも上の部分を除去し、次いで、図 50

9に示すように、酸化物膜32を除去すると、各溝16a～16cの間に位置する単結晶層12の表面が露出する。図9のS-S線切断面図を図28に示す。図9は、この図28のE-E線切断面図に相当する。

#### 【0089】

図9及び図28の符号33a～33cは、ゲート溝16a、逆阻止溝16b、ガード溝16c内に位置する充填物34から成る、埋込領域と、逆阻止領域と、ガード領域をそれぞれ示している。

#### 【0090】

この状態では、埋込領域33aと逆阻止領域33bとは、ベース拡散領域15aと接触しており、ガード領域33cは、補助拡散領域15cに接触している。

10

#### 【0091】

符号13は、ベース拡散領域15aや補助拡散領域15cが形成されていない単結晶層12の部分であり、一の逆阻止領域33bと他の逆阻止領域33bで挟まれた整流領域を示している。

#### 【0092】

また、符号14は、ベース拡散領域15a底面の単結晶層12の部分であり、埋込領域33bとpn接合を形成し、空乏層が広がるドレイン領域を示している。

#### 【0093】

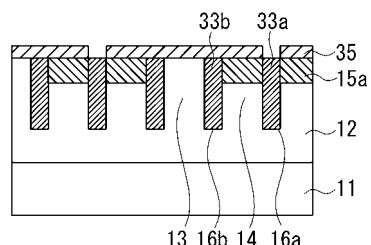

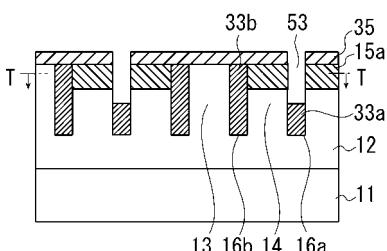

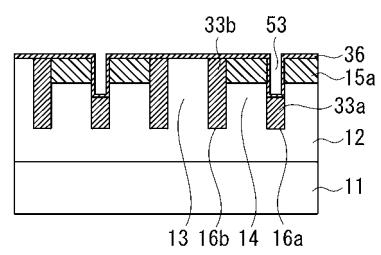

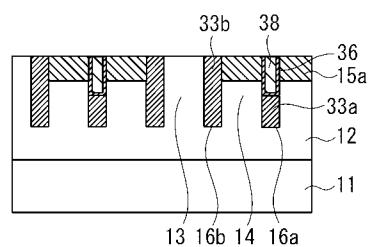

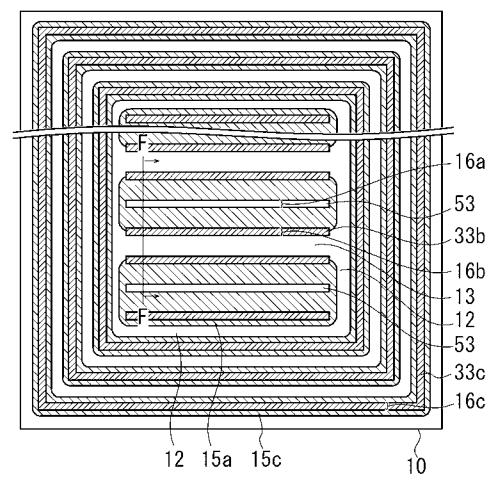

次に、図10に示すように、酸化物膜35を単結晶層12表面に形成し、パターニングして埋込領域33aの表面だけを露出させ、酸化物膜35をマスクとして単結晶層12のエッティングを行い、埋込領域33aの上部を除去すると、図11と、そのT-T線切断面図の図29に示すように、ゲート溝16aの底部に埋込領域33aが残り、その上部に溝残部53が形成される。逆阻止領域33bやガード領域33cはエッティングされず、変化はない。

20

#### 【0094】

埋込領域33aの上部はベース拡散領域15aの底面よりも低い位置までエッティングされており、埋込領域33aはベース拡散領域15aとは接触していない。従って、溝残部53の側面の上部には、上部にベース拡散領域15aが露出し、その下部にはドレイン領域14が露出している。溝残部53の底面には、埋込領域33aの上部が露出している。

30

#### 【0095】

次に、図12に示すように、熱酸化により、溝残部53の側面と底面を含む単結晶層12の表面にゲート絶縁膜36を形成する。ゲート絶縁膜36は、溝残部53が閉塞されない膜厚にする。この状態では、溝残部53は、開口部分を除き、ゲート絶縁膜36によって囲まれている。

#### 【0096】

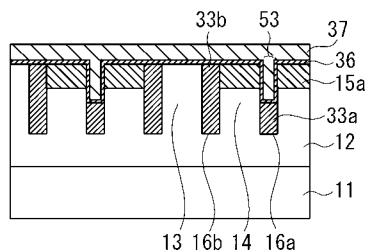

次に、図13に示すように、ゲート絶縁膜36上に導電性を有するポリシリコン37を堆積させ、溝残部53内をポリシリコン37で埋める。

#### 【0097】

次に、エッティング工程により、溝残部53内のポリシリコン37を残しながら、ポリシリコン37のゲート絶縁膜36の表面上に露出する部分を、一部を除いてエッティング除去すると、図14に示すように、溝残部53内にゲート電極プラグ38が形成される。ポリシリコン37のゲート絶縁膜36上に残った部分は図示されていないが、各ゲート溝16a内のゲート電極プラグ38に接続されており、後述するゲート電極パッドと接続される接続部分である。

40

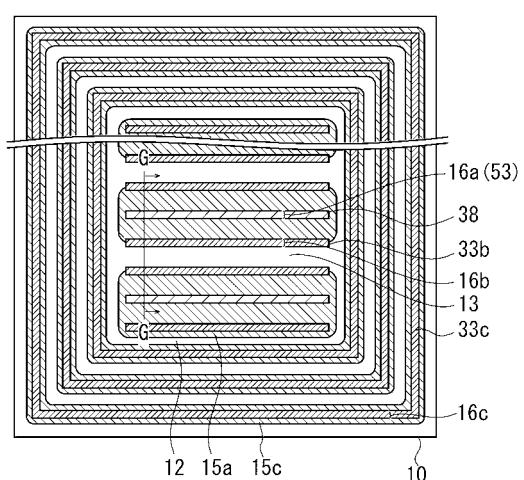

#### 【0098】

図30は、図14のU-U線切断面図である。図30では、ゲート絶縁膜36は省略してある。図14は、図30のG-G線断面図に相当する。

#### 【0099】

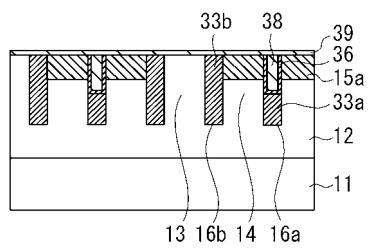

次に、単結晶層12上に位置し、露出されているゲート絶縁膜36をエッティングし、単結晶層12上のゲート絶縁膜36を除去すると、図15に示すように、ベース拡散領域1

50

5 a や整流領域 1 3 の表面と、逆阻止領域 3 3 b が露出する。この状態では、ゲート溝 1 6 a の底面には、埋込領域 3 3 a が配置され、ゲート溝 1 6 a の埋込領域 3 3 a よりも上の位置には、ゲート絶縁膜 3 6 を介してゲート電極プラグ 3 8 が配置されている。ゲート電極プラグ 3 8 は、ゲート絶縁膜 3 6 を介してベース拡散領域 1 5 a とドレイン領域 1 4 に接している。

#### 【0100】

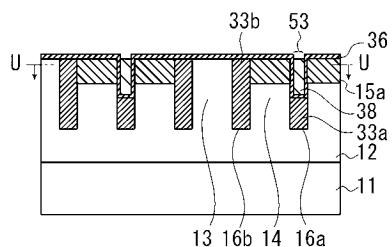

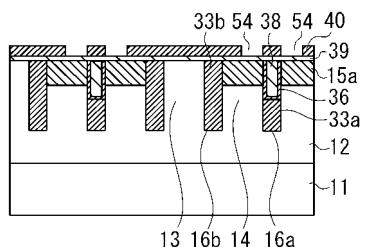

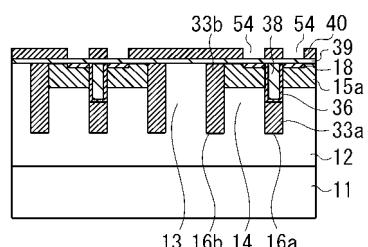

次に、図 1 6 に示すように、熱酸化法によって、ベース拡散領域 1 5 a や整流領域 1 3 上に薄い酸化膜 3 9 を形成した後、その表面に、図 1 7 に示すように、パターニングしたレジスト膜 4 0 を配置する。

#### 【0101】

このレジスト膜 4 0 は、各ゲート溝 1 6 a の両側に、ゲート溝 1 6 a の長手方向に沿った細長い開口 5 4 を有している。開口 5 4 の幅はベース拡散領域 1 5 a の幅よりも狭く、逆阻止溝 1 6 b には達していない。

#### 【0102】

その状態で、レジスト膜 4 0 の上方から第 1 導電型の不純物を照射すると、不純物は薄い酸化膜 3 9 を透過し、図 1 8 に示すように、開口 5 4 底面の位置に第 1 導電型の不純物の高濃度領域 1 8 が形成される。

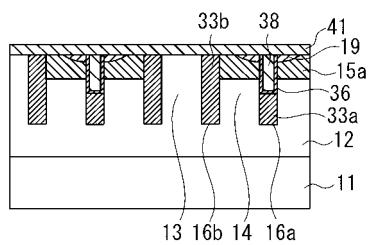

#### 【0103】

次に、レジスト膜 4 0 を除去した後、熱処理し、高濃度領域 1 8 中の第 1 導電型の不純物を拡散させると、図 1 9 に示すように、ゲート溝 1 6 a の長手方向両側の位置に、ゲート絶縁膜 3 6 と接触してソース拡散領域 1 9 が形成される。ソース拡散領域 1 9 はベース拡散領域 1 5 a よりも浅くなっている。ゲート絶縁膜 3 6 は、上端部でソース拡散領域 1 9 と接触し、その下方位置でベース拡散領域 1 5 a とドレイン領域 1 4 に接触している。ゲート電極プラグ 3 8 は、ソース拡散領域 1 9 とベース拡散拡散領域 1 5 a とドレイン領域 1 4 とに、ゲート絶縁膜 3 6 を介して接している。

#### 【0104】

図 1 9 の符号 4 1 は、ソース拡散領域 1 9 を形成する際に形成される酸化膜である。

#### 【0105】

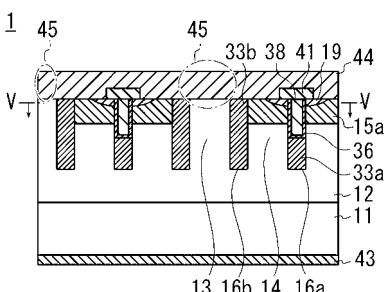

次に、その酸化膜 4 1 をパターニングし、図 2 0 に示すように、ゲート電極プラグ 3 8 の上部に酸化膜 4 1 を残し、ソース拡散領域 1 9 と、ベース拡散領域 1 5 a と、整流領域 1 3 と、逆阻止領域 3 3 b の表面の全部又は一部を露出させた後、スパッタ法や蒸着法等により、その表面に金属薄膜 4 2 を形成する。

#### 【0106】

この金属薄膜 4 2 は、ソース拡散領域 1 9 と、ベース拡散領域 1 5 a と、整流領域 1 3 と、逆阻止領域 3 3 b の表面に接触しており、整流領域 1 3 とはショットキー接合を形成し、他の領域 1 9 、 1 5 a 、 3 3 b とはオーミック接合を形成する金属であり、ソース拡散領域 1 9 と、ベース拡散領域 1 5 a と、逆阻止領域 3 3 b とは、この金属薄膜 4 2 によって短絡されている。また、金属薄膜 4 2 は、図示されていないゲート電極プラグ 3 8 の接続部分に接続されている。

#### 【0107】

整流領域 1 3 と金属薄膜 4 2 とが形成するショットキー接合は、金属薄膜 4 2 と基板 1 1 との間に電圧が印加され、ベース拡散領域 1 5 a とドレイン領域 1 4 との間の p n 接合が順バイアスされるときに順バイアスされ、逆バイアスされるときに逆バイアスされる極性になっている。

#### 【0108】

従って、ベース拡散領域 1 5 a とドレイン領域 1 4 との間の p n 接合と、金属薄膜 4 2 と整流領域 1 3 との間のショットキー接合は、並列接続されている。

#### 【0109】

次に、金属薄膜 4 2 を二分割し、ゲート電極プラグ 3 8 の接続部分に接続された金属薄膜 4 2 の一部領域を、ベース拡散領域 1 5 a やソース拡散領域 1 9 に接続された領域から

10

20

30

40

50

分離し、ゲート電極パッドとする。また、後者をソース電極膜とする。

**【0110】**

次に、図22(a)、(b)に示すように、半導体基板11の裏面に半導体基板11とオーミック接合を形成するドレイン電極膜43を形成すると、本発明の半導体装置1が得られる。

**【0111】**

同図(a)、(b)の符号44はゲート電極パッドから分離された金属薄膜42のうち、ソース拡散領域19やベース拡散領域15aと接続されたソース電極膜を示しており、符号45は、整流領域13と接触し、ショットキー接合を形成するショットキー電極膜を示している。なお、上述したように、この図22(a)のV-V線、及び同図(b)のW-W線の横断面図に相当する図面は、図31(a)に示されている。10

**【0112】**

次に、上記ソース電極膜44やショットキー電極膜45上に保護膜を形成し、ソース電極膜44の一部領域をソース電極パッドとし、ソース電極パッドとゲート電極パッドを露出させた後、同一半導体基板11上に形成された複数の半導体装置1を分割し、各半導体装置1のドレイン電極膜43をリードフレームに接触させて、それぞれリードフレームに搭載した後、ソース電極パッドとゲート電極パッドをワイヤーボンディングによってリードに接続し、半導体装置1を樹脂封止した後、リードを切断して個別に分離すると、樹脂封止された半導体装置1が得られる。

**【0113】**

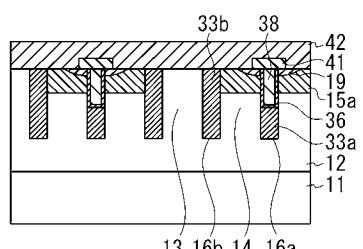

なお、図23(a)の半導体装置2のように、先ず、整流領域13とショットキー接合を形成し、他の領域19、15a、33bとはオーミック接合を形成するショットキー電極膜45を成膜した後、その表面に、低抵抗のソース電極膜44を形成してもよい。20

**【0114】**

また、図23(b)の半導体装置3のように、最初に成膜したショットキー電極膜45をパターニングし、ソース拡散領域19やベース拡散領域15aを露出させた後、ソース電極膜44を形成してもよい。

**【0115】**

また、上記例では、図11において、埋込領域33aの上部をベース拡散領域15aの底面よりも低い位置までエッチングする際にゲート溝16aの長さ方向の全範囲の上部をエッチングしたが、ゲート溝16aは細長であるから、ゲート溝16aの長さ方向の一部をマスクし、その部分の埋込領域33aをエッチングせずに残すことが可能である。30

**【0116】**

この場合、例えば、図示はしないが、ゲート溝16aの両端部分だけを酸化物膜32で覆っておき、露出部分をベース拡散領域15aよりも深い位置までエッチングすると、エッチングされなかった部分は、ゲート溝16aの下端部から上端部まで埋込領域33aが残る。

**【0117】**

その埋込領域33aはベース拡散領域15aに接触しているため、その部分が接続領域となり、上部がエッチング除去された埋込領域33aがベース拡散領域15aに接続される。上記実施例が、埋込領域33aが浮遊電位に置かれていたのに対し、この場合は、埋込領域33aはベース拡散領域15aと同じ電位になり、埋込領域33aからは、ベース拡散領域15aと一緒に空乏層が広がる。40

**【0118】**

上記各実施例では、逆阻止溝16bは細長い直角四角形形状であり、整流領域13を挟んでいたが、四辺が直角四角形形状の四角リング状に形成し、整流領域13を取り囲むようにしてもよい。

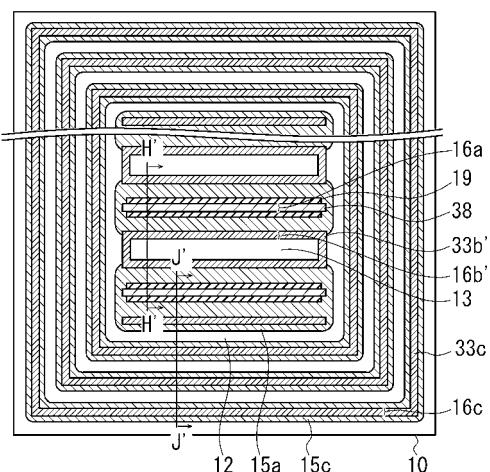

**【0119】**

図32の符号4は、その四角リング形状の逆阻止溝16b'を有する半導体装置4を示しており、この逆阻止溝16b'の内部にも、第2導電型の半導体材料が充填され、整流

10

20

30

40

50

領域 1 3 を取り囲む逆阻止領域 3 3 b' が形成されている。ショットキー電極膜 4 5 は、逆阻止領域 3 3 b' で囲まれた整流領域 1 3 と接触し、ショットキー接合を形成しているが、逆阻止領域 3 3 b' の外側に位置する単結晶層 1 2 の表面とは接触していない。

【 0 1 2 0 】

なお、この半導体装置 4 の H' - H' 線、 J' - J' 線の切断面図は、図 3 1 ( a ) の H - H 線、 J - J 線の切断面図と同じ、図 2 2 ( a )、( b )である。

【 0 1 2 1 】

上記のように、本発明の半導体装置には、整流領域 1 3 が、互いに分離された逆阻止溝 1 6 b で挟まれる場合の他、リング状に成形された逆阻止溝 1 6 b' やコ字型形状に接続された逆阻止溝の二辺以上の辺で挟まれた場合も含まれる。

10

【 0 1 2 2 】

【発明の効果】

ショットキーダイオードがあるため、逆方向の回復が速く、また、逆阻止領域により、ショットキーダイオードの耐圧が高くなっている。

【図面の簡単な説明】

【図 1 】本発明の一例の半導体装置の製造工程を説明するための活性領域の切断面図( 1 )

【図 2 】本発明の一例の半導体装置の製造工程を説明するための活性領域の切断面図( 2 )

【図 3 】本発明の一例の半導体装置の製造工程を説明するための活性領域の切断面図( 3 )

【図 4 】本発明の一例の半導体装置の製造工程を説明するための活性領域の切断面図( 4 )

【図 5 】本発明の一例の半導体装置の製造工程を説明するための活性領域の切断面図( 5 )

20

【図 6 】本発明の一例の半導体装置の製造工程を説明するための活性領域の切断面図( 6 )

【図 7 】本発明の一例の半導体装置の製造工程を説明するための活性領域の切断面図( 7 )

【図 8 】本発明の一例の半導体装置の製造工程を説明するための活性領域の切断面図( 8 )

【図 9 】本発明の一例の半導体装置の製造工程を説明するための活性領域の切断面図( 9 )

【図 1 0 】本発明の一例の半導体装置の製造工程を説明するための活性領域の切断面図( 1 0 )

【図 1 1 】本発明の一例の半導体装置の製造工程を説明するための活性領域の切断面図( 1 1 )

【図 1 2 】本発明の一例の半導体装置の製造工程を説明するための活性領域の切断面図( 1 2 )

30

【図 1 3 】本発明の一例の半導体装置の製造工程を説明するための活性領域の切断面図( 1 3 )

【図 1 4 】本発明の一例の半導体装置の製造工程を説明するための活性領域の切断面図( 1 4 )

【図 1 5 】本発明の一例の半導体装置の製造工程を説明するための活性領域の切断面図( 1 5 )

【図 1 6 】本発明の一例の半導体装置の製造工程を説明するための活性領域の切断面図( 1 6 )

【図 1 7 】本発明の一例の半導体装置の製造工程を説明するための活性領域の切断面図( 1 7 )

40

【図 1 8 】本発明の一例の半導体装置の製造工程を説明するための活性領域の切断面図( 1 8 )

【図 1 9 】本発明の一例の半導体装置の製造工程を説明するための活性領域の切断面図( 1 9 )

【図 2 0 】本発明の一例の半導体装置の製造工程を説明するための活性領域の切断面図( 2 0 )

【図 2 1 】本発明の一例の半導体装置の製造工程を説明するための活性領域の切断面図( 2 1 )

【図 2 2 】( a )：本発明の一例の半導体装置の製造工程を説明するための活性領域の切断面図( 2 1 ) ( b )：それに対応する活性領域周囲の断面図

50

【図23】(a)、(b)：本発明の半導体装置の他の例を説明するための活性領域の断面図

【図24】図2の状態の平面図

【図25】図4の状態に対応する横方向の断面図

【図26】図5の状態の平面図

【図27】図6の状態に対応する横方向の断面図

【図28】図9の状態に対応する横方向の断面図

【図29】図11の状態に対応する横方向の断面図

【図30】図14の状態に対応する横方向の断面図

【図31】(a)：図22(a)、(b)に対応する横方向の断面図 (b)：逆阻止領域とショットキー電極の長さの大小を説明するための図

10

【図32】本発明の第四例の半導体装置の平面図

【図33】従来技術のMOSFETの拡散構造を説明するための平面図

【図34】(a)：そのI-I線切断面図 (b)：II-II線切断面図

【符号の説明】

1~4 .....半導体装置

1 2 .....単結晶層

1 3 .....整流領域

1 4 .....ドレイン領域

1 5 a .....ベース拡散領域

1 6 a .....ゲート溝

20

1 6 b、1 6 b' .....逆阻止溝

1 6 c .....ガード溝

1 9 .....ソース拡散領域

3 3 a .....埋込領域

3 3 b、3 3 b' .....逆阻止領域

3 3 c .....ガード領域

3 6 .....ゲート絶縁膜

3 8 .....ゲート電極プラグ

4 3 .....ドレイン電極膜

4 4 .....ソース電極膜

30

4 5 .....ショットキー電極膜

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図10】

【図8】

【図11】

【図9】

【図12】

【図13】

【図16】

【図14】

【図17】

【図15】

【図18】

【図19】

【図22】

(a)

(b)

【図21】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

1

(a)

(b)

【図32】

4

J' 12 15a 15c 10

【図33】

101

【図34】

101

(a)

101

(b)

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 21/336 (2006.01) H 01 L 29/48 F

H 01 L 29/78 6 5 8 E

(72)発明者 九里 伸治

埼玉県飯能市南町10番13号 新電元工業株式会社飯能工場内

(72)発明者 大島 宏介

埼玉県飯能市南町10番13号 新電元工業株式会社飯能工場内

(72)発明者 北田 瑞枝

埼玉県飯能市南町10番13号 新電元工業株式会社飯能工場内

審査官 恩田 春香

(56)参考文献 特開2002-373989 (JP, A)

特開2001-244462 (JP, A)

特開2002-203966 (JP, A)

特開2001-284604 (JP, A)

特開平11-154748 (JP, A)

特開2002-050773 (JP, A)

特開平09-055507 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 29/78

H01L 21/336