(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4036270号

(P4036270)

(45) 発行日 平成20年1月23日(2008.1.23)

(24) 登録日 平成19年11月9日(2007.11.9)

(51) Int.C1.

F 1

GO 6 F 12/06 (2006.01)

GO 6 F 12/06 550 A

請求項の数 12 (全 15 頁)

|               |                        |

|---------------|------------------------|

| (21) 出願番号     | 特願平9-502375            |

| (86) (22) 出願日 | 平成8年6月5日(1996.6.5)     |

| (65) 公表番号     | 特表平11-507457           |

| (43) 公表日      | 平成11年6月29日(1999.6.29)  |

| (86) 國際出願番号   | PCT/SE1996/000748      |

| (87) 國際公開番号   | W01996/042055          |

| (87) 國際公開日    | 平成8年12月27日(1996.12.27) |

| 審査請求日         | 平成15年3月28日(2003.3.28)  |

| (31) 優先権主張番号  | 9502113-5              |

| (32) 優先日      | 平成7年6月9日(1995.6.9)     |

| (33) 優先権主張国   | スウェーデン(SE)             |

(73) 特許権者

テレフォンアクティエボラゲット エルエム エリクソン

スウェーデン国、ストックホルム、エスイー 164、83 (番地なし)

(74) 代理人

特許業務法人湘洋内外特許事務所

(72) 発明者

セーデルクイスト、イングマー

スウェーデン国、リンチエビング エス-583 37、グラスパレヴァーゲン

6

審査官 田中 秀人

(56) 参考文献 特開昭60-262280 (JP, A)

最終頁に続く

(54) 【発明の名称】メモリ構造

## (57) 【特許請求の範囲】

## 【請求項 1】

少なくとも1つの記憶場所にバイト以上の長さを持つベクトルを記憶させるメモリ構造において、

並列に配置されている複数のメモリブロックを備え、

各メモリブロックは、入力バッファを介して互いにカスケード結合され、これにより、情報を異なるメモリブロックのいくつかの入力バッファを介して直列的に次々と供給でき、前記メモリブロックは、それぞれ、隣接して配置されているメモリブロックと接続されていて、

前記複数のメモリブロックは、各々、

前記ベクトルの一部を記憶する、複数のメモリフィールドと、

データの入力を受け付ける入力バッファと、

前記メモリブロックの動作を制御する制御ロジックと、を有し、

前記ベクトルは、該ベクトルを構成する情報の連続順が分断しないで記憶されるように、前記複数のメモリブロックの中の一方の端部に配置されているメモリブロックのメモリフィールドに該ベクトルの始点が配置されると共に、該一方の端部に配置されたメモリブロックから他方の端部に配置されているメモリブロックに向けて、該ベクトルの長さに応じて、該並列に配置されている各メモリブロックのメモリフィールドに該ベクトルの一部が配置されていく、

前記データを記憶するメモリのアドレスの指定は、前記一方の端部に配置されているメモリ

10

20

リブロックの入力バッファに前記ベクトルを入力する際に行われるものであって、さらには、

1以上の前記メモリブロックを任意に組み合わせることが可能に構成されていることを特徴とするメモリ構造。

【請求項2】

請求項1に記載のメモリ構造であって、

前記入力バッファは、シフトレジスタと同様なデータの直列入力をを行い、

前記メモリフィールドは、前記入力バッファからの情報が直列的または並列的に入力されるように構成されていて、

前記制御ロジックは、入力バッファを介しての前記メモリフィールドへの情報の入力を制御し、

前記各メモリブロックは、入力バッファを介して互いにカスケード結合され、これにより、情報を異なるメモリブロックの幾つかの入力バッファを介して直列的に次々と供給でき、各メモリブロックの制御ロジックは、それ自体のメモリブロックが情報で満たされるときに、次のメモリブロックの制御ロジックに通報するように配置されており、これにより次のメモリブロックの制御ロジックが当該メモリブロックのメモリフィールドに情報の書き込みを行なうことができること

を特徴とするメモリ構造。

【請求項3】

請求項1または2に記載のメモリ構造であって、

前記メモリブロックは、

前記メモリに記憶されているベクトルが、該ベクトルを構成する情報の連続順が分断しないで出力されるための、シフトレジスタの機能を有する出力バッファを備えることを特徴とするメモリ構造。

【請求項4】

請求項3に記載のメモリ構造であって、

前記出力バッファは、シフトレジスタと同様、前記メモリフィールドに記憶されたデータの直列的出力をを行い、

前記各メモリブロックの制御ロジックは、前記出力バッファを介してメモリフィールドの情報の出力を制御し、かつ、それ自体のメモリブロックの情報が空になると次のメモリブロックの制御ロジックに通報するように配置され、これにより、該次のメモリブロックのメモリフィールドから情報を読取る処理を行うことができること

を特徴とするメモリ構造。

【請求項5】

請求項3～4のいずれか一項に記載のメモリ構造であって、

前記メモリブロックのメモリフィールドと前記入力バッファとの間の転送は、該メモリブロックにある制御ロジックにより並列的に行なわれ、

前記メモリブロックのメモリフィールドと前記出力バッファとの間の転送は、該メモリブロックにある制御ロジックにより並列的に行なわれること

を特徴とするメモリ構造。

【請求項6】

請求項3～5のいずれか一項に記載のメモリ構造であって、

前記入力バッファは、前記情報が入力中に、異なるメモリブロック間でいかなるハンドシェーク作動もなく、異なるメモリブロックの入力バッファに連続的に該情報を転送されるように配置され、

前記出力バッファは、前記情報が出力中に、異なるメモリブロック間でいかなるハンドシェーク作動もなく、異なるメモリブロックの出力バッファに連続的に転送されるように配置されていること

を特徴とするメモリ構造。

【請求項7】

10

20

30

40

50

請求項 3 ~ 6 のいずれか一項に記載のメモリ構造であって、前記各メモリプロックの入力バッファは、隣接するメモリプロックの入力バッファと出力バッファとは、互いに並列に配置されかつ互いに独立的に制御でき、前記各メモリプロックの出力バッファは、隣接するメモリプロックの出力バッファと互いに並列に配置されかつ互いに独立的に制御でき、これにより、メモリの記憶場所への情報の入力と、該記憶場所からの情報の出力とを略同じタイミングに行なうことができることを特徴とするメモリ構造。

【請求項 8】

請求項 3 ~ 7 のいずれか一項に記載のメモリ構造であって、

前記各メモリプロックの出力バッファは、

10

前記メモリフィールドからのデータを受け付けて記憶する中間バッファと、

前記中間バッファから転送されたデータを受け付け、該受け付けたデータを隣接するメモリプロックの出力バッファに出力するシフトレジスタと、

選択的なクロックパルス数により、前記メモリフィールドから前記中間バッファへの書き込み期間に対する、前記中間バッファからシフトレジスタへの読み取り期間の位相シフトを行なう手段と、を有すること

を特徴とするメモリ構造。

【請求項 9】

請求項 8 に記載のメモリ構造であって、

前記位相シフト手段は、所望の位相遅延に等しい遅延をもつ調節可能な遅延回路を有することを特徴とするメモリ構造。

20

【請求項 10】

請求項 1 ~ 9 のいずれか一項に記載のメモリ構造であって、

前記各メモリプロックは、

前記メモリフィールドからの情報を受け付けて記憶する処理バッファと、

前記処理バッファに記憶された情報に所定の処理を行う信号処理ユニットと、を備え、

前記各メモリプロックの信号処理ユニットは、自身と異なるメモリプロックの信号処理ユニットが行う処理と並列的に、前記メモリフィールドから読み出した情報を処理することができる構成正在すること

を特徴とするメモリ構造。

30

【請求項 11】

請求項 10 に記載のメモリ構造であって、

前記信号処理ユニットが処理した情報は、処理後にメモリプロックのメモリフィールドに再記憶させることができること

を特徴とするメモリ構造。

【請求項 12】

請求項 10 または 11 に記載のメモリ構造であって、

前記信号処理ユニットが処理した情報は、メモリプロックからの情報と結果とを組み合わせる結果ユニットに転送できること

を特徴とするメモリ構造。

40

【発明の詳細な説明】

本発明は、請求の範囲第 1 項の前提部に記載の形式のメモリ構造に関する。

発明の背景

メモリの開発は、コンピュータプロセッサの開発と同時に行なわれている。このことは、プロセッサの開発がメモリの開発を案内してきたといえる。従って、メモリの情報は、一定数のビットからなるビット群（以下、バイトと呼ぶ）に任意に分割され、殆どの場合、前に選択された情報とは独立してアドレスされる。このため、メモリへの情報の書き込みまたは読み取りを行なうには、アドレスデコーダは、或るアクセス時間内にメモリ内の任意位置に到達できなくてはならない。データ転送速度はアクセス時間に反比例する。アクセス時間は、本来的に、メモリに使用される製造技術の種類に基づいて定まる。回路のサイズ

50

および複雑さを最小にするため、VLSI技術（VLSI = Very Large Scale Integration、大規模集積回路）が使用されかつ努力がなされている。所与の技術にとって、メモリのサイズは、信号の伝播速度により常に制限される。同時に、メモリが増大するとアドレスデコーダの複雑さも増大するため、従来技術では、大きなメモリ領域は長いアクセス時間を伴うという関係がある。データ処理速度に対する要望は常に増大している。アドレスデコーダの複雑さが増大しつつ伝播速度が一定であるため、全記憶スペース、すなわち情報が記憶されるアドレス指定可能表面は、コンピュータ速度の増大につれて常に減少する。

遠隔通信、レーダ、コンピュータ用大メモリ等の近年非常に重要になっている多くの使用分野では、情報は、バイトの形態ではなく、ベクトルと呼ばれるバイト列として取り扱われる。現代のデジタルホンシステムおよびデータ通信システムでは、情報のパケット（ATM）が使用されている。レーダでは、情報はパルスの形態をなしている。デジタル化の後は、パルスは、出発点と長さとにより定義される大きなベクトルであると考えられる。多くの用途では、連結バイトの大きなブロックが同じ様（例えば、ワードプロセッサではテキストのブロック）で取り扱われる。他の例は、コンピュータのスワップメモリである。これらでは、一般に、全体として大量の情報（ベクトル）が取り扱われ、バイトレベルでのアドレス指定は使用されていない。

発明の目的本発明の目的は、ベクトルの記憶ができるメモリ構造を作ることにある。

本発明の他の目的は、ベクトルの読み取りおよび／または書き込みを行なうため、記憶場所への高速かつ連続アクセスが可能なメモリ構造を作ることにある。

本発明の他の目的は、ベクトルの読み取りが行なわれているのと同時に、およびベクトルの読み取りとは独立して、ベクトルの書き込みが行なえるメモリ構造を作ることにある。

本発明の他の目的は、ベクトルの読み取りと殆ど同時にベクトルの書き込みが行なえるメモリ構造を作ることにある。

本発明の他の目的は、書き込まれたデータの取出し時間を、クロック期間内に確実に制御できるメモリ構造を作ることにある。

本発明の他の目的は、コンピュータの現在のメモリ構造形式の補足物として使用できるメモリ構造を作ることにある。

本発明の他の目的は、記憶されたベクトルを、複数のベクトル記憶場所により並列処理して、処理されたベクトルを再位置決めし、または処理結果を取り出すことができるメモリ構造を作ることにある。

#### 発明の簡単な要約

上記目的は、請求の範囲第1項の特徴部に記載のメモリ構造により達成される。本発明の他の特徴および他の長所は、他の請求の範囲の記載に示されている。

本発明によれば、構成（configuration）後のメモリの各記憶場所が、大きなベクトルの長さに適合した長さを有し、かつ情報の入力から延び、そして、メモリ内に深く入るように並列に配置され、これにより各ベクトルは、メモリの入力によりベクトルの始点をもつ連続順で、非分割記憶されるように配置され、これにより、アドレス指定がメモリへの入力に行なわれるよう配置されている。メモリの記憶場所に中断されない順序で情報を入力するための、シフトレジスタのように機能する手段が設けられている。

メモリは、好ましくは横方向に分割されてメモリブロックを形成し、これにより、全ての記憶場所の各々が各メモリブロックの一部を有する。メモリの記憶場所が、1つ以上のメモリブロックを一緒に結合することにより拡大できる。各メモリブロックは、シフトレジスタのように機能する手段としての、

シフトレジスタと同様なデータの直列入力をもつ入力バッファと、

記憶場所としての、

入力バッファからの情報が連続的に入力される多数のデータメモリフィールドとからなる。

この点において、制御ロジックが各メモリブロックに配置され、制御ロジックは、入力バッファを介してのメモリフィールドへの情報の入力を制御し、これにより、メモリブロック

10

20

30

40

50

クは、各々がそなえる入力バッファを介して互いにカスケード結合される。これにより、情報を、異なるメモリブロックの多数のバッファを介して直列的にかつ段階的に供給できる。各メモリブロックの制御ロジックは、それ自体のメモリブロックが情報で満たされるか、これらの全ての情報が読取られるときに、次のメモリブロックの制御ロジックに通報するように配置されており、これにより次のメモリブロックの制御ロジックが当該メモリブロックへの情報の書き込みの仕事を行なうことができる。メモリの記憶場所からの非分割順序（undivided order）での情報の出力のための、シフトレジスタのように機能する手段を設けることができる。また、異なるメモリブロックに並列的に記憶されたデータの処理手段を設けることもできる。

本発明の長所

10

本発明によるメモリ構造は、連続的にかつ極めて高速に情報のデータ転送を行なえる、大きくかつ拡大可能な記憶スペースを設けることができる。ベクトル用記憶スペース、従ってメモリサイズの拡大は、外部から見たメモリとのインターフェースが不变であるので、データ転送速度に影響を与えることなく行なうことができる。

本発明によるメモリ構造では、現在の30～100メガバイト／秒に匹敵する約0.5～1ギガバイト／秒で連続データ転送を行なうことができる。これは、同じ基本技術を使用したものよりも10倍速いことを意味する。これらのメモリ構造は、使用される技術により左右されるものではなく、任意の記憶技術（RAM、磁気メモリ、光メモリ等）に使用できる。

#### 【図面の簡単な説明】

20

以下、本発明を添付図面を参照してより詳細に説明する。

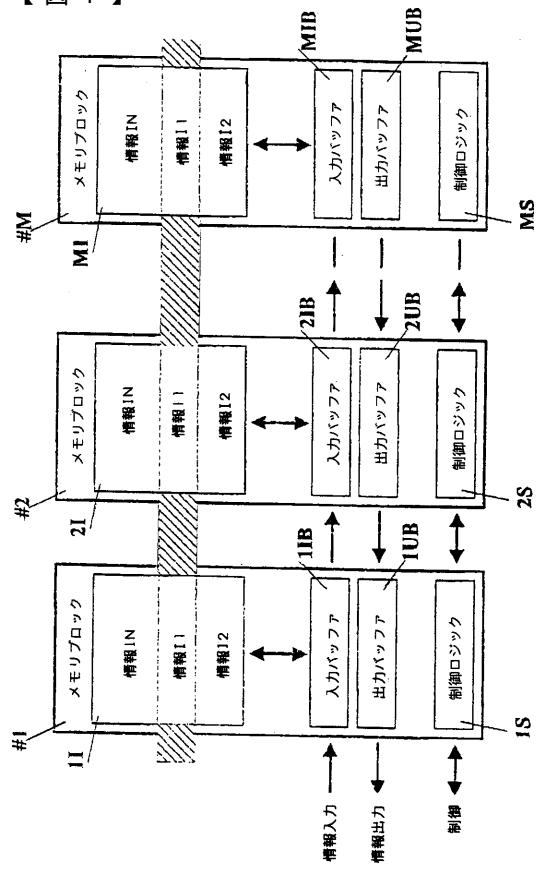

第1図は、本発明によるメモリ構造の原理を示す概略図である。

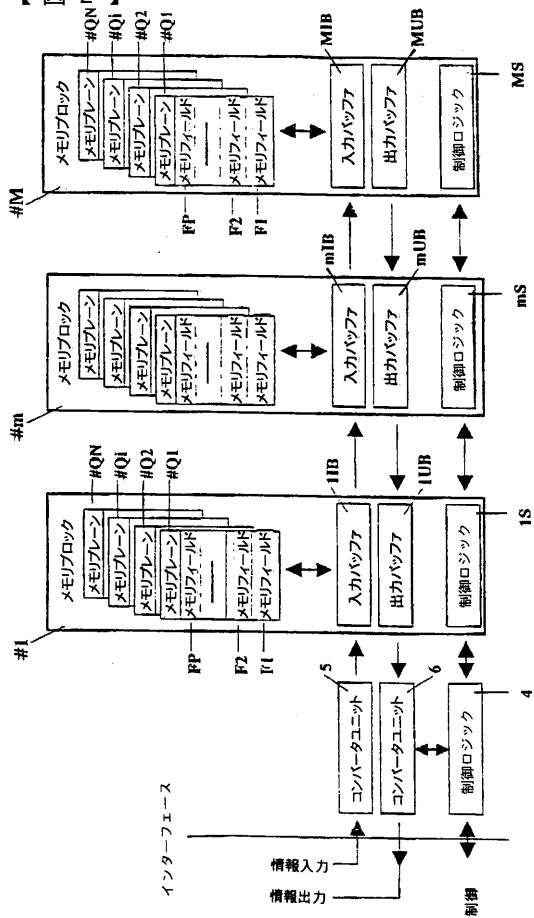

第2図は、本発明によるメモリ構造の第1実施例を示す図面である。

第3図は、メモリブロックの内部構造を第2図より詳細に示す図面である。

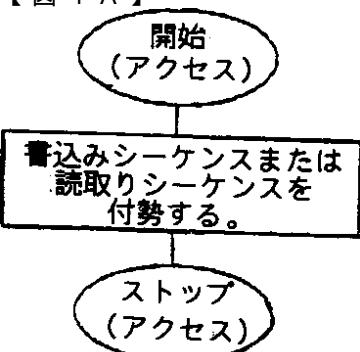

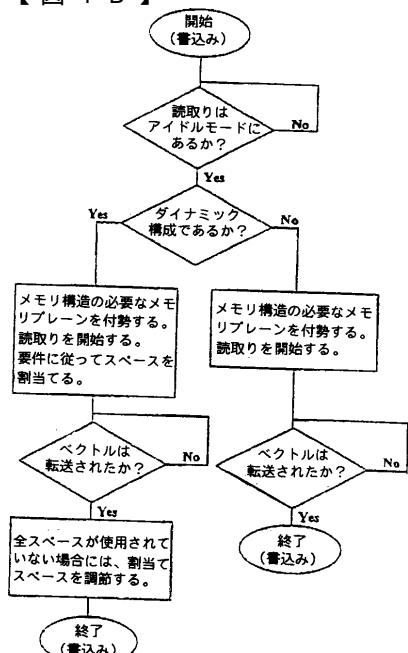

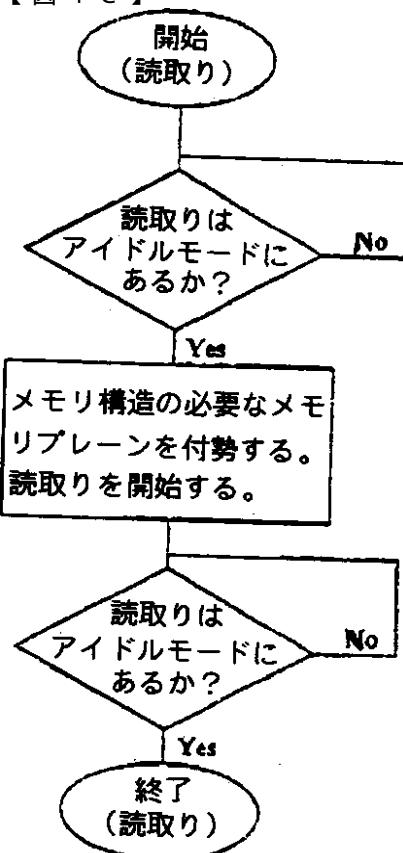

第4図は、メモリの全制御ロジックを示すフローチャートである。

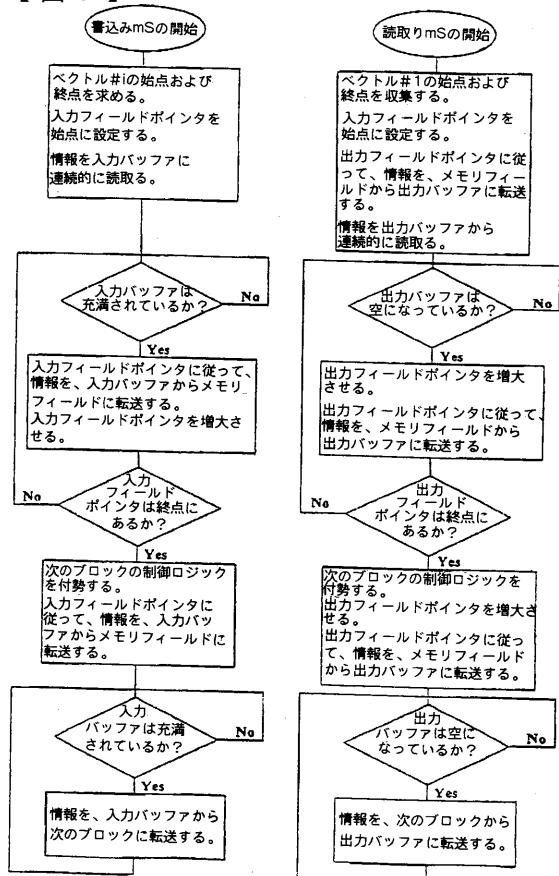

第5図は、メモリブロックの制御ロジックを示すフローチャートである。

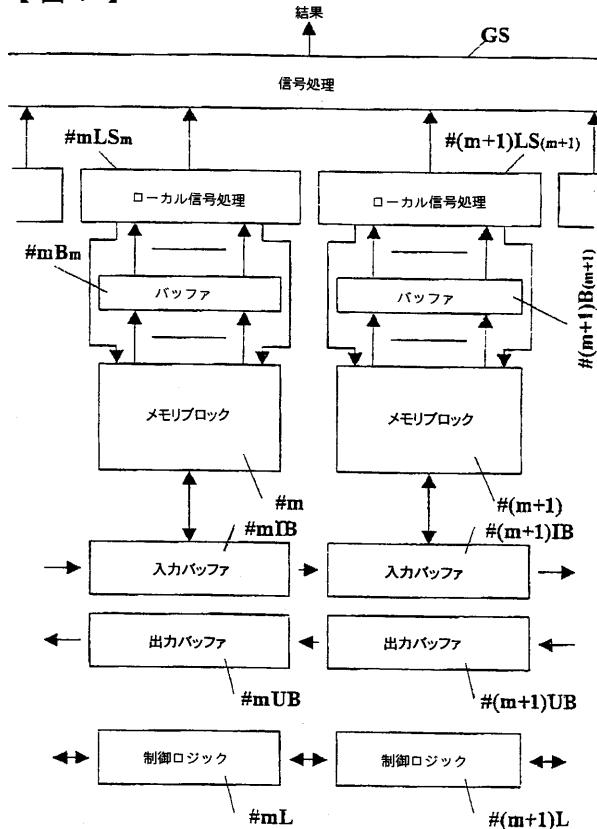

第6図は、本発明によるメモリ構造の第2実施例を示す図面である。

第7図は、本発明によるメモリ構造の第3実施例を示す図面である。

#### 実施例の説明

##### 定義

30

**記憶情報：** 記憶情報とは、外部から見て、各々が連続的にかつ非分割の形態で処理される複数のベクトルをいう。

**ベクトル：** 一つのかたまりとして処理されるべき情報の全連続量をいう。ベクトルは、出発点又は識別情報（identity）および長さの補助により、外部から定義される。

**バイト群：** メモリフィールドのサイズに適合するベクトルの一部をいう。ベクトルは、バイト群の合計として説明できる。

**メモリ構造：** 第2図のシステム全体をいう。メモリ構造は、1つ以上のメモリブロックと、コンバータユニット5、6と、制御ロジック4とからなる。

**メモリブロック：** 最も近くのメモリ構造とのみ通信する明確な機能をもつユニットをいう（第2図参照）。メモリ構造は、新しいメモリブロックの全数に従って常に拡大される。

40

**記憶場所：** メモリ構造の全メモリ領域の一部（構成後に、現在のベクトルの長さに適合される）をいう。各記憶場所は、メモリ構造内部で、メモリブロック#1から分配されている（第1図参照）。

**メモリプレーン：** 構成後に或るベクトル（識別情報）に割り当てられるメモリブロックの一部をいう。

**メモリフィールド：** 一つのかたまりとして処理されるべきメモリプレーンの一部をいう。メモリフィールドのサイズは、入力／出力バッファのサイズに等しい。

#### 図面の説明

第1図は、互いにカスケード結合された多数のメモリブロック#1、#2…#Mを示

50

す。各メモリブロックは、情報部 1 I、2 I・・・M I と、入力バッファ 1 I B、2 I B・・・M I B と、出力バッファ 1 U B、2 U B・・・M U B と、制御ロジック 1 S、2 S・・・M S を有している。各メモリブロックは別々のチップに設けることができ、選択した個数のチップを互いに一体接続して、選択した大きさのメモリを形成することができる。また、1つのチップに幾つかのメモリブロックを設けて、幾つかの多ブロックチップを一体にカスケード結合することもできる。メモリ内の各記憶場所は、大きなベクトルの長さに適合する長さを有する。ブロックは、並列に配置され、これにより、各ベクトルは、入力バッファを介してメモリの入力／出力にベクトルの始点を持つ、ベクトルを構成する情報の連続順が非分割となるように記憶され、かつ同様に、その必要がある場合には出力バッファを介して連続順に出力されるように配置されている（第7図の実施例を参照）

10 アドレス指定は、メモリの入力／出力に対して行なわれる。

第2図に示す実施例では、メモリ構造は、カスケード結合された多数のユニットすなわちメモリブロック # 1 ~ # M と、制御ロジック 4 と、適当なコンバータユニット 5、6 を有する。ここに示す各メモリブロックは、互いに前後に位置する幾つかのメモリプレーン # 1 I - # 1 N および M 1 - # M N を有し、各メモリプレーンは多数のメモリフィールド F 1 ~ F P を有する。ここで説明で留意すべきは、メモリ内の特定メモリフィールドは、どのメモリブロックおよびどのメモリプレーンに属するかを識別する基準（例えば、メモリブロック # m のメモリプレーン Q i のメモリフィールド F j の場合には、# m、Q i、F j ) を有する。この基準システムは、全体を通じて適用されている。

20

しかしながら、実際のメモリブロックは、各々、表面上の異なる位置に拡がって配置されたプレーン、または、各々、メモリフィールドとして次々に配置されたプレーンをもつ表面構造にすることができ、これにより、例えば幾つかのブロックをもつチップの場合には、メモリブロック # 2 / メモリプレーン # Q 1 でのメモリフィールドは、メモリブロック # 1 / メモリプレーン # Q 1 でのメモリフィールドに直接連続するように配置されることは明白である。

20

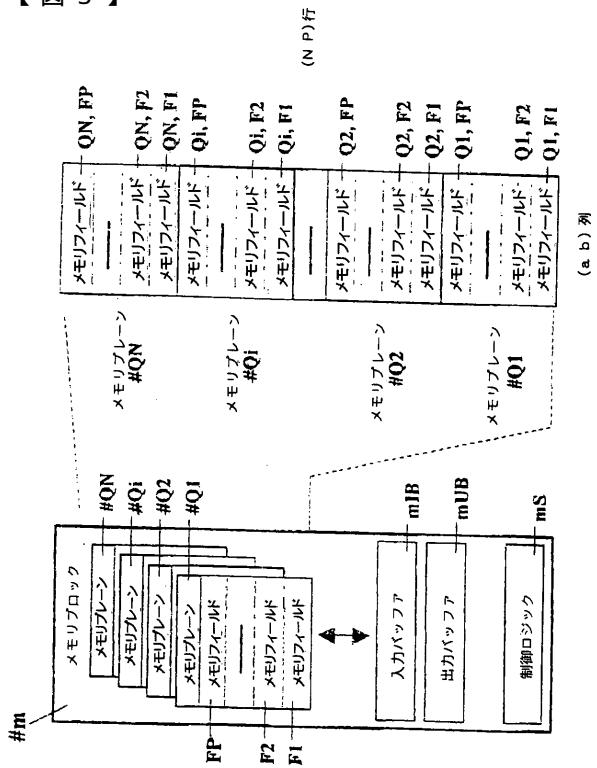

第3図から分かるように、メモリ構造は、幾つかのアドレス指定可能な記憶場所すなわちメモリプレーン Q 1 ~ Q i ~ Q N ( i = 1 ~ N ) を有する。各メモリブロック # m は、アドレス指定可能な各メモリプレーン Q i に割り当てられる多数のメモリフィールド F 1 ~ F P を有する。

各メモリブロック # m は、物理的に、W m 行（第3図の N × P に相当）および a × b 列に編成される。各行はメモリフィールドを形成しかつ多数のバイト群すなわちワード（a）（各ワードは適当なビット数（b）を有する）を保有している。従ってメモリブロック # m は、W m × a × b ビットの大きさになる。メモリ構造は、( W 1 + W 2 + ··· + W M ) × a × b ビットの全サイズを有する。また、a、b および W がメモリブロック間で変化する特別な場合を考えることもできるが、ここでは取り上げない。

30

長さ L I ワードをもつベクトル V i が、L i / a 部分ベクトルとして、メモリフィールド「# 1, Q i, F 1」・···・「# 1, Q i, F P」；「# 2, Q i, F 1」・···・「# 2, Q i, F P」；···；「# M, Q i, F 1」・···・「# M, Q i, F P」に記憶される。

構成（configuration）の後、L i = a × ( O i1 + O i2 + ··· + O iM ) ワードは有効である。ここで、O i m とは、メモリプレーンの中の行の数、すなわち、メモリブロック # m の中のメモリプレーン Q i のメモリフィールドの総数をいう。従って、ベクトル V i の大きさは、a × b × ( O i1 + O i2 + ··· + O iM ) ビットとなる。各メモリブロックは、行の数が、常にメモリフィールドの数の合計に等しくなる ( W m = O 1 m + O 2 m + ··· + O N m )。

40

同時に、異なる長さのベクトルをメモリ構造に記憶させることができる。

メモリ構造は、種々の態様に構成できる。外部から見て、ベクトルは出発点（識別情報）# 1 Q i F 1 からのみアドレスされる。ここで、i は 1 と N との間の任意の数、F 1 は、メモリブロック # 1 のメモリプレーン Q i の第 1 メモリフィールドである。ベクトル L i の長さは構成により定められ、構成はスタティックでもダイナミックでもよい。

スタティック構成では、全ての O i m が予め定められる。制御ロジック 4 は、記憶位置 M

50

$i$  の数  $N$  並びにそれぞれの記憶場所  $L_i$  の長さの知識を有する。メモリブロックの制御ロジック  $1S - MS$  は、それぞれのメモリブロックについて、出発点 #  $1QiF1$  および長さ  $Oim$  の知識を有する。終点 #  $mQiFj$  は、出発点および長さにより間接的に定められる。

ダイナミック構成では、現在のメモリプレーンまたは記憶場所  $Q_i$  の長さが書き込み中に変化される。情報ベクトルは、長さに関する情報並びに他のグローバル情報によって続けられるように外部から仮定される。あるいは、この情報は、ベクトル  $V_i$  のヘッドとして、第 1 バイト群内に見出すこともできる。次に制御ロジックは、メモリ構造内にいかにして更に入るかに従って、この情報を読み取り、使用しつつ変化させる。ヘッドの後、情報は連続的に続く。

スタティック構成では、記憶場所  $Q_i$  から読み取られまたは記憶場所  $Q_i$  に書き込まれる情報ベクトルが、構成に等しい長さを有すると仮定する。スタティック構成では、ヘッドは省略できる。

どのメモリブロック #  $i$  も、入力情報のため、メモリプレーン内の各記憶メモリフィールドのために多数の記憶ビットを有するバッファ記憶を備えた入力バッファ  $iIB$  と、出力情報のため、入力バッファと同じバッファ記憶サイズを備えた出力バッファ  $iUB$  を有する。メモリプレーン内の、従ってメモリプレーン内のメモリフィールド（単一または複数）内の情報の書き込みおよび読み取りを制御するための制御ロジック  $iS$  が更に存在する。本発明に従って、インターフェース 5、6（第 2 図参照）を介してメモリ構造に接続されるコンピュータユニットは、情報入力ポートを介して入力される情報をロードし、かつ情報出力ポートから出力されるベクトルの形態の情報（例えばデータパケット）を取り出す。各ベクトルには、識別情報を含むヘッド、長さ等を設けることができる。あるいは、当業者に明白な他の任意の態様でインターフェースに必要な情報を与えることができる。制御ロジック 4 はインターフェースに接続され、メモリから読み取られたものに従ってメモリを制御する。また、制御ロジック 4 には、記憶されたベクトルに関するデータを記憶するための内部メモリ（図示せず）を設け、ベクトルおよび新しいベクトルを内部メモリに記憶させることができる。かくして、制御ロジック 4 の影響を受けて、メモリへのアドレス指定が行なわれる。これは第 4 A 図から理解されよう。

第 4 A 図から第 4 C 図は、制御ロジックが作動する方法の一実施例のフローチャートであり、付勢時のもの（第 4 A 図）、メモリへの書き込み時のもの（第 4 B 図）およびメモリから読み取り時のもの（第 4 C 図）である。このフローチャートは非常に明白であるので、種々の段階についての詳しい説明は不要である。

以下に詳述するように、メモリへの入力情報は並列形式（すなわち、例えば 8、16、32 ビットの適当な長さの並列バイトの形態）が適している。純粋なシリアル情報が入力される場合には、コンバータユニット 5 において、ビット形態から並列バイト形態への変換が行なわれる。必要ならば、同様に、コンバータユニット 6 において並列バイトからビットへの変換を行なう。情報入力ポートでの入力情報が連続ビット形態になりかつ情報出力ポートでの情報が並列バイト形態になること（またはこの逆）を妨げるものはなく、この場合には、コンバータユニット 5、6 のうちのいずれか一方のみでよい。

ダイナミック構成（第 4 B 図参照）中、書き込まれるべき各情報ベクトルのヘッドが読み取られる。この情報の一部は、ベクトルがどれほど多くのメモリスペースを占めるかを決定するのに使用され、他の一部は、第 1 メモリブロック # 1 の制御ロジック  $1S$  を付勢して、該制御ロジックに、他のメモリブロック #  $i$  のどれほど多くの従属制御ロジック  $iS$  を付勢する必要があるかの情報を与えるのに使用される。

実際には、記憶されたどのベクトルも、メモリブロック # 1 のプレーン  $Q_i$  の 1 つのメモリフィールド  $F_1$  にその始点を有し、ここからメモリ内へとより深く入る。ベクトルの記憶は单一の連続糸のように行なわれると考えることができる。ベクトルは、この態様において並列に配置され、これらへのアドレス指定が、メモリブロック # 1 の異なるプレーンの始点に行なわれる。実際に、多くのメモリフィールド  $F_1 \sim FP$  が、記憶のための各メモリに使用される。すなわち、全ベクトルが始点から終点まで、メモリブロックからメモ

10

20

30

40

50

リブロックへと、切斷されないシーケンスに配置される。

メモリブロックのどの制御ロジックも、その内部に、これらのメモリプレーンおよびメモリフィールドは空であるか、既に充満されているかを示す情報をもつメモリを有している。記憶すべきベクトルが到達すると、制御ロジック 4 または制御ロジック 1 S において最初のサーチがなされ、利用可能な記憶プレーンを見出す。

メモリブロックの各制御ロジック 1 S ~ M S についてのフローチャートの一実施例を示す第 5 図から明らかなように、情報すなわちベクトルがインターフェース（第 2 図参照）を通過するとき、書き込みが開始する。構成は全てのメモリについて完了する必要はない。なぜならば、これは、メモリ内での情報の下降伝播に従って連続的に遂行されるからである。プレーン  $Q_i$  ( $i$  は、1 と  $N$  との間の数) が空であることが示されていると仮定する。ベクトルは、全ての異なるブロックにおいて常に同じプレーン、例えばプレーン  $Q_x$  (ここで  $x$  は 1 と  $N$  との間の数) すなわち、# 1 Q x ; # 2 Q x ; # M Q x 等に記憶されることに留意すべきである。入力バッファ 1 I B へのベクトルの入力が開始される。そして、入力バッファがバイト群で充満されるやいなや、プレーン # 1 Q x の第 1 記憶メモリフィールド F 1 へのこの転送が行なわれる。入力バッファは、シフトレジスタと同様な態様で充満されるが、メモリフィールドへの出力は直列または並列（好ましくは並列）に行なわれ、これにより入力バッファの全メモリ内容が空にされる。

シフトレジスタと同様に直接再充満 (direct refilling) が行なわれ、その後、プレーン # 1 Q x の最終メモリフィールド F P が充満されるまで、メモリの全内容がプレーン # 1 Q x の次のメモリフィールド F 2 に空にされる。これに関連して、制御ロジック 1 S は、現在書き込みが行なわれているメモリフィールドを与える入力フィールドポインタ（図示せず）を有する。

次に、入力バッファ 1 I B は、入力バッファ 2 I B の充満を、シフトレジスタと同様直列に、すなわち、並列バイトから並列バイトへと、これが満たされるまで始めるように制御される。以下の説明では、バッファとして使用されるシフトレジスタの全直列長さを直列バイトと呼ぶこととする。なぜならば、これは、バッファを充満するのに必要なクロック信号の数を表す（すなわち、並列バイト群の直列長さを表す）からである。

入力バッファが充満されると、入力バッファは、プレーン # 2 Q x の第 1 メモリフィールド F 1 および異なる次のメモリフィールドに充満され、次に、メモリプレーン # 1 Q x と同様に充満される（すなわち、制御ロジックからの入力フィールドポインタにより制御される）。メモリプレーン # 1 Q x が充満されると、メモリブロック # 2 の入力バッファ 2 I B の情報が、次のメモリブロックの入力バッファに転送し続け、次に、ここから、このメモリブロックの次のメモリプレーン # 3 Q x のメモリフィールドに転送し続け、このことが以下同様に行なわれる。いずれの図面にも示されていないが、例えば幾つかのメモリプレーンを同時に動かせるためには、多くの入力バッファおよび出力バッファを設けることができることに留意すべきである。制御ユニットを二重化することもできる。

情報は、連続並列バイトの形態で入力バッファに入力でき、このため、実際に各バッファは各バッファにあるビットと同様な多くの並列シフトレジスタを有することに留意すべきである。並列バイト群という表現は、入力 / 出力バッファを充満するバイト数に使用される。入力バッファがプレーンのメモリフィールドに注がれると、これにより、転送される非常に大量のデータがある。従って各メモリフィールドは、極めて大きな数の並列バイト群を有する。

データは、これが書込まれた後に、直ちにメモリフィールドから読み取られかつ出力される。

第 5 図のフローチャートから明らかなように、読み取り中に、1 つのメモリフィールドの内容が、当該プレーン  $1_i$  の第 1 フィールドの全並列バイト群と並列に、出力バッファ 1 U B に一度に転送されかつ直列にすなわち並列バイトから並列バイトへと出力される。

プレーン # 1 Q i の最終メモリフィールドの次の出力バッファへの転送が行なわれると、制御ロジック 1 S は制御ロジック 2 s を付勢して、第 1 メモリフィールド # 2 Q i の内容を出力バッファ 2 U B に転送する。最終メモリフィールド F P が出力バッファ 1 U B に転

10

20

30

40

50

送されかつこれがその並列バイトの内容を直列に出力した直後に、出力バッファ2UBは、その内容を、並列バイトから並列バイトへと直列に、出力バッファ1UBに出力し、従って、これがバッファ1UBの前の内容の直後に続くようとする。

この方法では、出力された情報に中断が生じない。プレーン#2Qiのメモリフィールドの情報は、出力バッファ2UBに段階的に出力され、制御ロジック2Sからの出力フィールドポインタ（図示せず）により制御され、かつここからバッファ1UBを介して直列的に出力される。プレーン2iの最終メモリフィールドFPに続くメモリフィールドが出力バッファ2UBに転送されると、次のメモリブロックのために制御ロジックが付勢され、メモリフィールド情報がメモリブロック等の出力バッファに転送されるようとする。

上記実施例では、異なるブロックの各出力バッファが、その内容、並列バイト群、並列バイトから並列バイトへと直列的に次の出力バッファに出力する。これは、入力および出力の両方において、制御が並列バイトから並列バイトへと行なわれることを意味する。各並列バイト群は比較的多数の並列バイトを有し、これは、データをもつベクトルの出力の開始が、並列バイト群の長さにより与えられる多数のクロック期間の比較的長い時間間隔で行なわれることを意味する。

しかしながら、データ出力の制御が本発明のメモリが一部を形成するシステムのクロック期間で終了する場合の用途がある。メモリのヘッド論理は、並列バイト群の出力が行なわれることに関する情報および並列バイト群の時間内に正確な所望時間に出力が行なわれるために必要とされる位相変位を有する。

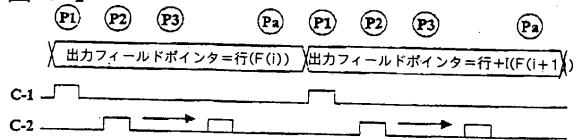

第6図には、これを達成するための制御ロジックを備えたメモリの一実施例が示されている。同じメモリ内容を、独立的に制御可能な時点でシステムの異なる部分に出力することができ、この場合には多くの出力バッファをメモリプレーンに接続することができる。しかしながら、図面には1つのみの出力バッファOUTBUFFが示されているだけである。各出力バッファは中間バッファMBUFFを有し、中間バッファでは、制御中に、内容がシフトレジスタskに転送される。

各出力バッファを機能させる方法は全て同じであり、従って、OUTBUFFに関する説明はこれらの全てに有効である。

メモリブロックのローカル制御装置（local control arrangement）が、メモリプレーンのメモリ内容が出力バッファOUTBUFFを介して出力すべき旨の表示を受けると、このメモリプレーンの第1メモリフィールドが、そのための制御信号C-1により、中間バッファMBUFFにロードダウンされる。実際の出力のための適当なクロック信号で、中間バッファの内容が、シフトレジスタのクロック入力CLKの制御と直接タイミングが合った出力を得るため、制御信号C-2によりシフトレジスタskに転送される。次のメモリフィールドの内容が、中間バッファからシフトレジスタへの転送の直後に、または好ましくは、次の全並列バイト群期間の開始時に、中間バッファMBUFFに転送される。しかしながら、シフトレジスタskへの転送前の期間中、例えば中間メモリからシフトレジスタへの転送の直前のクロック期間中の任意の時点で行なわれる中間バッファへの転送を防止するものは何もない。

上記のように、全メモリブロックがひとたび空になると、更に出力に転送するため、情報が連続的に出力バッファに出力される。このデータは、次のブロックも同じ制御であるため、シフトレジスタを介してメモリの出力に出力されるように次の出力バッファのためのシフトレジスタに接続されたその直列入力上のシフトレジスタskに連続順序で入力する、正しくタイミングがとれた連続直列バイト群として直接帰着する。

第6図の下部には、メモリプレーンのそれぞれのメモリフィールドから中間バッファMBUFFへの転送、次にメモリバッファからシフトレジスタskへの転送を出力するメモリブロックの第1出力バッファOUTBUFFの制御手段の一例が示されている。特定時点で開始するメモリプレーンにおいて、データが、データに関する制御がロジック10に入力されると、これは、最初に、小ゲート回路11を通過後にメモリプレーンの第1メモリフィールドへの出力フィールドポインタに向く。小ゲート回路1は、制御信号CKL/b（ここで、bは、カウンタ12によりカウントされたシフトレジスタSKの並列バイト段

10

20

30

40

50

の数である)の存在において、そのロジックからの信号を通ることを可能にする。出力フィールドポインタは、次の制御信号 C L K / b で次のメモリフィールドに移動し、以下同様に、次の制御信号で次のメモリフィールドに移動する。これは機能 13 で示されている。また、出力フィールドポインタの位相に対する位相変位が、異なる位置 P 1 ~ P a として第 6 図の上部に示されている。ここで、a は、異なるフィールド F i および F ( i + 1 ) におけるメモリフィールドの位置長さであり、これにより、C - 1 は、この実施例では、フィールドポインタの始点になり、C - 2 は、所望位置(例えば P 2 )に制御可能に変位される。

カウンタ 1 2 からの出力は、論理 1 1 からの出力と一緒に、フィールドの変化に関する第 2 論理 1 4 に入力される。次に、論理 1 4 は、図示の実施例に従って、その出力に信号 C - 1 を発生する。この信号 C - 1 は、図示の実施例では、選択されたメモリフィールドから小ゲート回路 1 5 (該回路は、次のクロック信号 C L K で信号を発生する)を介して中間バッファ M B U F F に送られるデータ転送を制御する。また、信号 C - 1 は、遅延ユニット 1 6 の入力にも供給される。10

遅延ユニット 1 6 は、その 1 つの制御入力に、論理 1 0 からの信号 1 7 (該信号はデジタル形態が好ましい)を受け、該信号 1 7 は、シフトレジスタ S K 1 に転送される前に、データの現在の遅延を中間バッファに知らせる。これは、出力フィールドポインタが、出力されるべきメモリプレーンの最終フィールドに到達するまで続く。この場合、論理 1 0 からの論理 1 4 からの信号はもはや生じない。その代わり、最終出力フィールドポインタ位置に続く位置で、論理 1 0 は、その制御ロジックを付勢すべく次のブロックへの出力を与える。20

図示しないが、必要ならば、信号 C - 1 に所望の遅延を与えるため、および / または異なる出力バッファ等に異なる遅延を与えるため、論理 1 0 とは別の制御可能な多くの遅延を設けることができる。

メモリの上記全ての実施例において、入力データおよび出力データはメモリブロックの同じ側でそれぞれ入力および出力される。第 7 図は、記憶された全ベクトルが上記実施例に従って出力されるか、或いは異なるメモリブロックに記憶されたデータの信号処理を同時にすなわち並列的に遂行できる実施例を示す。

記憶された全ベクトルを、出力バッファ # m U B , # ( m + 1 ) U B を介して後で出力するため、信号処理は、例えば、記憶されたテキストストリングの全体に亘る特殊記号の置換に関するものとすることができます。このような場合、データは、処理後に、該データが取り出されたメモリのメモリフィールドに戻し転送される。或いは、より精巧な信号処理を行なうことができる。この実施例の 1 つの長所は、多量の記憶データの信号処理を迅速に遂行できることである。30

特殊文字を検索した結果を得るために、記憶データの或る種の処理を行なうこともできる。このような場合、入力されたベクトルを出力バッファを介して出力する必要はない。従って、これらは、本発明に必ずしも必要なものではない。

どのメモリブロック(例えばメモリブロック # m )も処理バッファ m B m を有し、該処理バッファ m B m は、制御ロジック # m L がその出力バッファと同様にしてメモリフィールド毎にメモリプレーンの内容を送ることができるメモリブロックに接続されている。次に、バッファ # m B m の内容がローカル信号処理ユニット # m L S m に転送され、該ローカル信号処理ユニットでは、特殊な信号処理が行なわれる。次に、処理されたデータは、上記のようにかつ図面に破線で示すように、該データが取り出されたメモリフィールド(单一または複数)に戻し転送されるか、全てのブロックに共通の信号処理ユニット G S (該ユニットは結果を抽出しつつこれを出力する)に転送される。この結果の抽出は、それぞれのメモリブロックに記憶されるものに基づいて、別のメモリプレーン、1つのメモリプレーンのメモリフィールドまたは全メモリブロックで行なうことができる。使用される信号処理の形式は発明の概念とは無関係であるので、1つの実施例、すなわち全メモリブロックまたはメモリブロックのメモリプレーンの実施例のみを示す。40

また、上記方法で、同じメモリブロックの全てのメモリプレーンの処理を行なうことがで50

きる。これが生じる状況は、画像の各線がメモリブロックの異なるメモリプレーンに記憶される画像制作用ビデオ信号を記憶する場合である。本発明は、迅速かつ容易なアクセスができるかつ特定のメモリブロックまたは幾つかの隣接メモリブロックに線が集合された画像の部分の処理を行なうことができる。このため、あらゆる種類の画像の迅速な処理が可能になる。

#### 用例における長所

本発明による方法により記憶するのに特に適したベクトルの例は、ワードプロセッサからのテキストのボリュームである。テキストのボリュームは、ベクトルの始点およびその長さで定められる。しかしながら、実際には、これがどこにあるかを知る必要はない。本発明を用いることの利点は、コンピュータ速度をかなり増大できることである。 10

伝統的に、テキストのボリュームは、例えばハードディスクの異なる場所に分割されて記憶される。記憶情報を保持するには、先ず、1つのセクタをアドレス指定し、ここから情報を取り出し、他のセクタをアドレス指定し、ここから情報を取り出し、以下同様の手順を繰り返す。従って、この場合には非常に多くのアドレス指定と情報待機が必要である。また、伝統的に、近くの位置から情報を取り出すことは比較的高速に行なえる。調査すべきメモリが多いほど、長時間を要する。このため、データ速度は、メモリの大きさおよび情報の拡大度合いに比例して低下する。

本発明では、情報の始点はメモリの入力／出力でのベクトルにありかつストリングのようなものである。すなわち、異なるプレーン # m i , Q j (ここで、j は 1 と N との間の任意の数である)において、ストリングは、入力／出力からメモリ内に深く入る。適当な位置を探すため、新しいベクトルが、中断することなくメモリに入力される。同様に、記憶されたベクトルは、出力が必要な実施例では中断することなく出力される。これは、とにかくアクセス時間を損なうことなく情報量を無限に大きくできることを意味する。ベクトルの終点は、この情報をその内部メモリに記憶するメモリブロックの制御ロジックによりベクトルの書き込みおよび読み取りが行なえる最終メモリブロックのメモリフィールドにマークされる。メモリの同時読み取りおよび書き込みが行なわれる。従って、この制御ロジックは、常に入力および出力の両者の終点を知っており、特に、それぞれの出力バッファからベクトルの終点を出力する間に、終点を他の制御ロジックに信号入力する。

従って、各制御ロジック i S は各情報についてのリストを有し、該リストには、どの情報実態であるかについて、および関連メモリブロックおよびリンクに書込むことができるベクトル部分の始点および終点が記載されている。制御ロジックのこの部分は、ダイナミックメモリより効率的なハードウェアで適当に遂行される。第1図～第5図の実施例の制御ロジックの一実施例は、遅延 16 なくして第6図の実施例と同様に遂行される。メモリは、外部からは通常のメモリのように見える。本発明によるメモリに適用される僅かな制限は、ベクトルの処理中にのみ効率的なことである。本発明のメモリは、コンピュータの通常のメモリの一部に含めることができる。 30

新しいシステムでは、両情報が迅速に見出されかつデータ転送が迅速に行なわれる。メモリブロックはチップの一部で構成できる。すなわち、幾つかのメモリブロックを同一チップに設けることもできるし、別々のチップに設けることもできる。或いは、各メモリブロックは幾つかのチップで、すなわち標準コンポーネンツで製造することができる。これらの全ての可能性は、市場と共に存するものであり、種々のユニットの組合せにフレキシブルに使用できることを意味する。 40

1つの用途のベクトルが非常に長くなり、メモリに記憶できるようにするには幾つかのベクトルに分割しなければならないことが明らかになった場合には、例えば、最終メモリブロックの後に、簡単な方法で特別なメモリブロック(チップ)を接続し、記憶すべきベクトルの記憶スペースを拡大することができる。

他の使用領域は、データが直列ビット形態で到達する電話網であり、この場合には、第1入力バッファに入力される、ビットからバイトに変換するための情報用コンバータユニット 5 が適している。

また、入力バッファは、これらが直列シフトレジスタ(特別な場合)を形成するように編 50

成することもできる。また、入力バッファに直列シフトレジスタを設け、出力バッファに並列シフトレジスタを設けることができ、或いはこの逆の構成にすることもできる。実施上の問題は、データの上り並列化（up-parallelizing）を最初に遂行することを選択する場合にある。これは、将来遠隔通信を考える場合には、起こり得る蓋然性が非常に高い。入力される情報は直列的であり、従って、第1並列変換がメモリの外部のコンポーネント5で遂行される。

各制御ロジック4、mSは、固定プログラムを有する簡単なデータチップの形態に構成できる。或いは、制御ロジックmSはメモリプレーンと一体化させることができる。第4図および第5図は、制御ロジックのフロー・チャートの一設計を示す。このフロー・チャートにより達成される機能は上述した通りであり、これが、このフロー・チャートについて特別な説明をしない理由であり、当業者には直接理解できるであろう。

本発明の範囲内で考え得る多くの変更が請求の範囲に記載されている。

【図1】

【図2】

【図3】

【図4 A】

【図4 B】

【図4 C】

【図5】

【図6】

【図7】

---

フロントページの続き

(58)調査した分野(Int.Cl. , DB名)

G06F 12/00 - 12/06

G06F 13/16 - 13/18

G06F 17/16