(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6315262号

(P6315262)

(45) 発行日 平成30年4月25日(2018.4.25)

(24) 登録日 平成30年4月6日(2018.4.6)

(51) Int.Cl.

H01L 27/146 (2006.01)

F 1

H01L 27/146

D

請求項の数 8 (全 20 頁)

(21) 出願番号 特願2014-121289 (P2014-121289)

(22) 出願日 平成26年6月12日 (2014.6.12)

(65) 公開番号 特開2016-1681 (P2016-1681A)

(43) 公開日 平成28年1月7日 (2016.1.7)

審査請求日 平成29年1月18日 (2017.1.18)

(73) 特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 100121131

弁理士 西川 孝

(74) 代理人 100082131

弁理士 稲本 義雄

(72) 発明者 松谷 弘康

東京都港区港南1丁目7番1号 ソニー株式会社内

審査官 小池 英敏

最終頁に続く

(54) 【発明の名称】 固体撮像素子、固体撮像素子の製造方法、及び、撮像装置

## (57) 【特許請求の範囲】

## 【請求項 1】

透明絶縁基板と、

光電変換を行う画素部が2次元配列された画素領域が形成された半導体基板と、

前記透明絶縁基板と前記半導体基板を、接着層を介して貼り合わせた基板の反りを補正

するために設けられる反り補正膜と

が積層されたキャビティレスのウェハレベルCSP構造として構成され、

前記反り補正膜は、前記半導体基板と前記透明絶縁基板との間に、前記透明絶縁基板、

前記半導体基板、及び、前記接着層についての熱膨張係数、及び、応力の少なくとも一方

を、加熱接合後の基板の反りを補正するために最適化した膜として形成され、

前記半導体基板の前記画素領域内のオンチップレンズ上に、前記オンチップレンズよりも屈折率の小さい透明樹脂層が形成され、

前記反り補正膜の屈折率は、前記透明樹脂層の屈折率と、前記接着層の屈折率との間の

値となる

固体撮像素子。

## 【請求項 2】

前記半導体基板、前記反り補正膜、前記接着層、前記透明絶縁基板の順に積層される

請求項1に記載の固体撮像素子。

## 【請求項 3】

前記反り補正膜は、透明膜である

10

20

請求項 1 に記載の固体撮像素子。

**【請求項 4】**

前記反り補正膜は、前記半導体基板又は前記透明絶縁基板の表面又は裏面に形成される

請求項 1 に記載の固体撮像素子。

**【請求項 5】**

前記透明絶縁基板の熱膨張係数は、3~8ppm/ 度とされ、

前記半導体基板の熱膨張係数は、3ppm/ 度とされ、

前記反り補正膜の熱膨張係数は、0.1~100ppm/ 度とされる

請求項 1 乃至 4 のいずれかに記載の固体撮像素子。

**【請求項 6】**

前記透明樹脂層の屈折率は、1.4程度とされ、

前記接着層の屈折率は、1.5程度とされ、

前記反り補正膜の屈折率は、1.4~1.5程度とされる

請求項 1 乃至 5 のいずれかに記載の固体撮像素子。

**【請求項 7】**

透明絶縁基板、又は、光電変換を行う画素部が2次元配列された画素領域が形成された

半導体基板の表面又は裏面に、前記透明絶縁基板と前記半導体基板を、接着層を介して貼

り合わせた基板の反りを補正するために設けられる反り補正膜を形成する工程と、

前記透明絶縁基板と前記半導体基板を、接着層を介して貼り合わせる工程と

を有する、キャビティレスのウェハレベルCSP構造として構成される固体撮像素子の製

造方法であって、

前記反り補正膜は、前記半導体基板と前記透明絶縁基板との間に、前記透明絶縁基板、

前記半導体基板、及び、前記接着層についての熱膨張係数、及び、応力の少なくとも一方

を、加熱接合後の基板の反りを補正するために最適化した膜として形成され、

前記半導体基板の前記画素領域内のオンチップレンズ上に、前記オンチップレンズよりも屈折率の小さい透明樹脂層が形成され、

前記反り補正膜の屈折率は、前記透明樹脂層の屈折率と、前記接着層の屈折率との間の

値となる

固体撮像素子の製造方法。

**【請求項 8】**

透明絶縁基板と、

光電変換を行う画素部が2次元配列された画素領域が形成された半導体基板と、

前記透明絶縁基板と前記半導体基板を、接着層を介して貼り合わせた基板の反りを補正

するために設けられる反り補正膜と

が積層されたキャビティレスのウェハレベルCSP構造として構成され、

前記反り補正膜は、前記半導体基板と前記透明絶縁基板との間に、前記透明絶縁基板、

前記半導体基板、及び、前記接着層についての熱膨張係数、及び、応力の少なくとも一方

を、加熱接合後の基板の反りを補正するために最適化した膜として形成され、

前記半導体基板の前記画素領域内のオンチップレンズ上に、前記オンチップレンズよりも屈折率の小さい透明樹脂層が形成され、

前記反り補正膜の屈折率は、前記透明樹脂層の屈折率と、前記接着層の屈折率との間の

値となる

固体撮像素子を搭載した撮像装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本技術は、固体撮像素子、固体撮像素子の製造方法、及び、撮像装置に関し、特に、小

型化の要求に応えつつ、基板を貼り合わせることで生じる反りを抑制することができるよ

うにした固体撮像素子、固体撮像素子の製造方法、及び、撮像装置に関する。

**【背景技術】**

10

20

30

40

50

**【0002】**

半導体装置をチップサイズまで小型化したウェハレベルCSP(WCSP: Wafer level Chip Size Package)が知られている。また、特許文献1には、半導体基板上に、接着層を介してガラス基板を貼り合わせた構造が開示されている。

**【先行技術文献】****【特許文献】****【0003】****【特許文献1】特開2009-164314号公報****【発明の概要】****【発明が解決しようとする課題】**

10

**【0004】**

ところで、熱膨張係数の異なる基板同士を接着層で加熱接合した後に、室温に戻ると、反りが発生することが知られている。特許文献1には、半導体基板の表面側に接着層を介してガラス基板を貼り合わせた基板の反りを低減することが開示されているが、その構造上、小型化の要求に応えることができない。そのため、小型化の要求に応えつつも、基板を貼り合わせることで生じる反りを抑制したいという要求がある。

**【0005】**

本技術はこのような状況に鑑みてなされたものであり、小型化の要求に応えつつ、基板を貼り合わせることで生じる反りを抑制することができるようとするものである。

**【課題を解決するための手段】**

20

**【0006】**

本技術の第1の側面の固体撮像素子は、透明絶縁基板と、光電変換を行う画素部が2次元配列された画素領域が形成された半導体基板と、前記透明絶縁基板と前記半導体基板を、接着層を介して貼り合わせた基板の反りを補正するために設けられる反り補正膜とが積層されたキャビティレスのウェハレベルCSP構造として構成され、前記反り補正膜は、前記半導体基板と前記透明絶縁基板との間に、前記透明絶縁基板、前記半導体基板、及び、前記接着層についての熱膨張係数、及び、応力の少なくとも一方を、加熱接合後の基板の反りを補正するために最適化した膜として形成され、前記半導体基板の前記画素領域内のオンチップレンズ上に、前記オンチップレンズよりも屈折率の小さい透明樹脂層が形成され、前記反り補正膜の屈折率は、前記透明樹脂層の屈折率と、前記接着層の屈折率との間の値となる固体撮像素子である。

30

**【0008】**

前記半導体基板、前記反り補正膜、前記接着層、前記透明絶縁基板の順に積層されるようにすることができる。

**【0010】**

前記反り補正膜は、透明膜であるようにすることができる。

**【0011】**

前記反り補正膜は、前記半導体基板又は前記透明絶縁基板の表面又は裏面に形成されるようにすることができる。

前記透明絶縁基板の熱膨張係数は、3~8ppm/ 程度とされ、前記半導体基板の熱膨張係数は、3ppm/ 程度とされ、前記反り補正膜の熱膨張係数は、0.1~100ppm/ 程度とされるようにすることができる。

40

前記透明樹脂層の屈折率は、1.4程度とされ、前記接着層の屈折率は、1.5程度とされ、前記反り補正膜の屈折率は、1.4~1.5程度とされるようにすることができる。

**【0012】**

本技術の第2の側面の固体撮像素子の製造方法は、透明絶縁基板、又は、光電変換を行う画素部が2次元配列された画素領域が形成された半導体基板の表面又は裏面に、前記透明絶縁基板と前記半導体基板を、接着層を介して貼り合わせた基板の反りを補正するために設けられる反り補正膜を形成する工程と、前記透明絶縁基板と前記半導体基板を、接着層を介して貼り合わせる工程とを有する、キャビティレスのウェハレベルCSP構造として

50

構成される固体撮像素子の製造方法であって、前記反り補正膜は、前記半導体基板と前記透明絶縁基板との間に、前記透明絶縁基板、前記半導体基板、及び、前記接着層についての熱膨張係数、及び、応力の少なくとも一方を、加熱接合後の基板の反りを補正するために最適化した膜として形成され、前記半導体基板の前記画素領域内のオンチップレンズ上に、前記オンチップレンズよりも屈折率の小さい透明樹脂層が形成され、前記反り補正膜の屈折率は、前記透明樹脂層の屈折率と、前記接着層の屈折率との間の値となる固体撮像素子の製造方法である。

#### 【0013】

本技術の第3の側面の撮像装置は、透明絶縁基板と、光電変換を行う画素部が2次元配列された画素領域が形成された半導体基板と、前記透明絶縁基板と前記半導体基板を、接着層を介して貼り合わせた基板の反りを補正するために設けられる反り補正膜とが積層されたキャビティレスのウェハレベルCSP構造として構成され、前記反り補正膜は、前記半導体基板と前記透明絶縁基板との間に、前記透明絶縁基板、前記半導体基板、及び、前記接着層についての熱膨張係数、及び、応力の少なくとも一方を、加熱接合後の基板の反りを補正するために最適化した膜として形成され、前記半導体基板の前記画素領域内のオンチップレンズ上に、前記オンチップレンズよりも屈折率の小さい透明樹脂層が形成され、前記反り補正膜の屈折率は、前記透明樹脂層の屈折率と、前記接着層の屈折率との間の値となる固体撮像素子を搭載した撮像装置である。

#### 【0014】

固体撮像素子及び撮像装置は、独立した装置であってもよいし、他の装置に組み込まれるモジュールであってもよい。

#### 【0015】

本技術の第1の側面乃至第3の側面においては、透明絶縁基板と、光電変換を行う画素部が2次元配列された画素領域が形成された半導体基板と、前記透明絶縁基板と前記半導体基板を、接着層を介して貼り合わせた基板の反りを補正するために設けられる反り補正膜とが積層されたキャビティレスのウェハレベルCSP構造として構成されている。また、前記反り補正膜が、前記半導体基板と前記透明絶縁基板との間に、前記透明絶縁基板、前記半導体基板、及び、前記接着層についての熱膨張係数、及び、応力の少なくとも一方を、加熱接合後の基板の反りを補正するために最適化した膜として形成され、前記半導体基板の前記画素領域内のオンチップレンズ上に、前記オンチップレンズよりも屈折率の小さい透明樹脂層が形成され、前記反り補正膜の屈折率が、前記透明樹脂層の屈折率と、前記接着層の屈折率との間の値とされる。

#### 【発明の効果】

#### 【0016】

本技術の第1の側面乃至第3の側面によれば、小型化の要求に応えつつ、基板を貼り合わせることで生じる反りを抑制することができる。

#### 【0017】

なお、ここに記載された効果は必ずしも限定されるものではなく、本開示中に記載されたいずれかの効果であってもよい。

#### 【図面の簡単な説明】

#### 【0018】

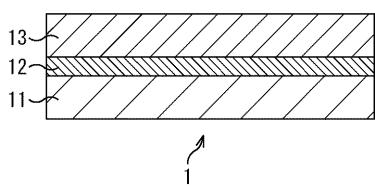

【図1】反り補正を行わない場合における貼り合わせ基板の構造を示す図である。

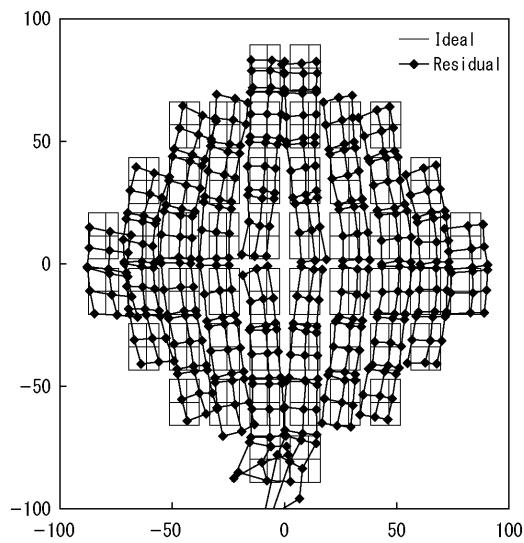

【図2】チップのひずみを模式的に表した図である。

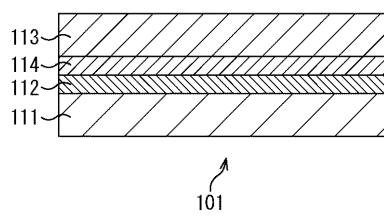

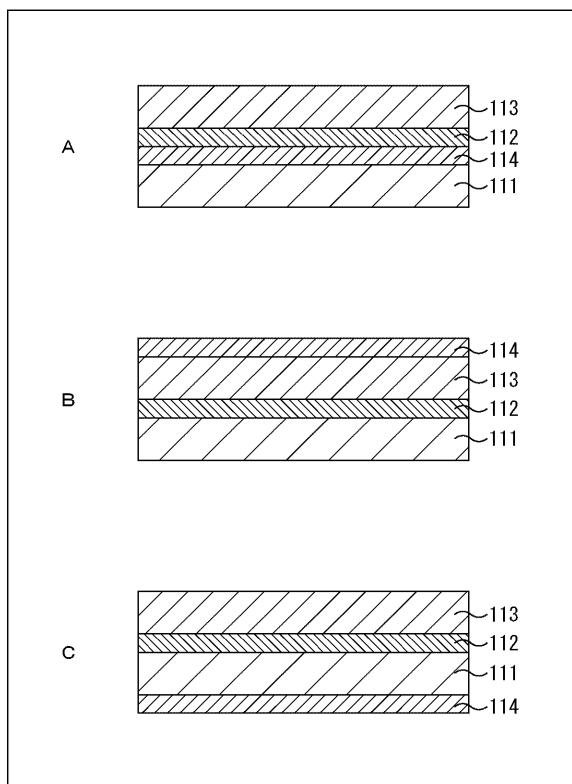

【図3】反り補正を行う場合における貼り合わせ基板の構造を示す図である。

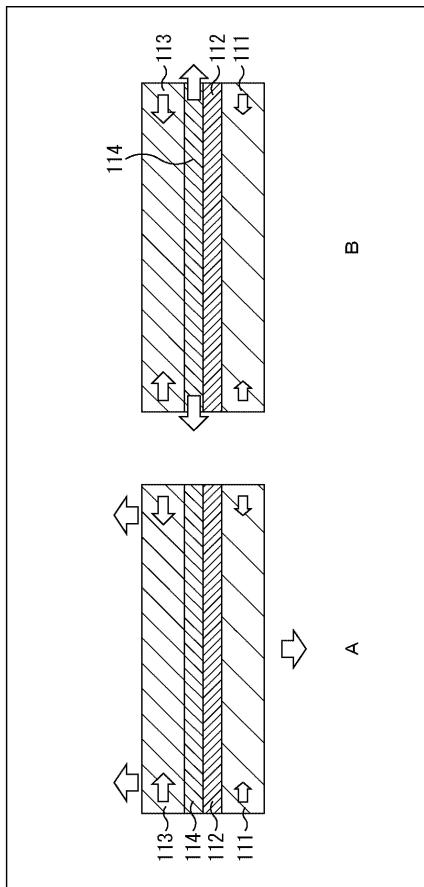

【図4】反り補正膜による反り補正を説明する図である。

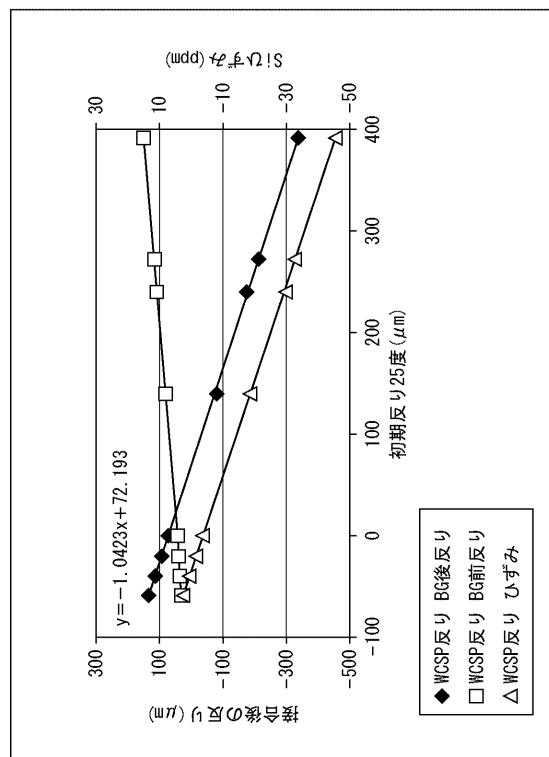

【図5】最適化された反り補正膜を形成するためのシミュレーションの結果を示す図である。

【図6】反り補正を行う場合における貼り合わせ基板の他の構造を示す図である。

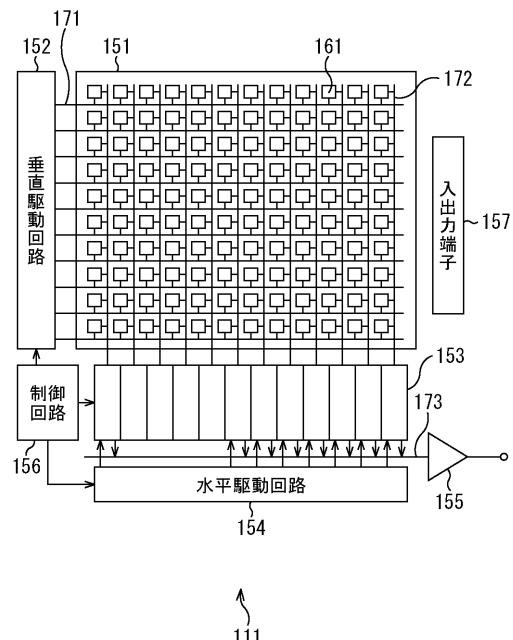

【図7】固体撮像素子を構成する半導体基板の回路構成を示す図である。

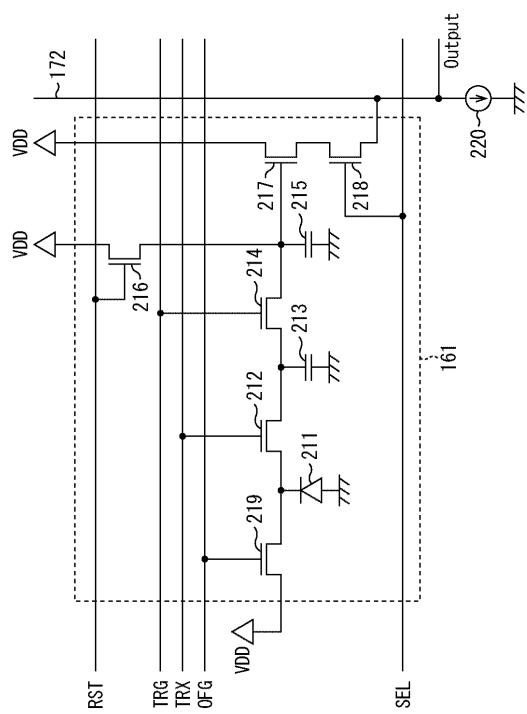

【図8】図7の単位画素の等価回路を示す図である。

10

20

30

40

50

【図9】固体撮像素子の詳細構造を示す図である。

【図10】図9の構造を有する固体撮像素子の製造方法を説明する図である。

【図11】撮像装置の構成例を示す図である。

**【発明を実施するための形態】**

**【0019】**

以下、図面を参照しながら本技術の実施の形態について説明する。なお、説明は以下の順序で行うものとする。

**【0020】**

1. 本技術を適用した反り補正の概念

2. 固体撮像素子の構造例

3. 固体撮像素子の製造方法

4. 撮像装置の構成

10

**【0021】**

<1. 本技術を適用した反り補正の概念>

**【0022】**

(反り補正を行わない場合における貼り合わせ基板の構造)

図1は、本技術を適用した反り補正を行わない場合における貼り合わせ基板の構造を示す図である。

**【0023】**

図1の固体撮像素子1は、半導体基板11とガラス基板13の2つの基板を、接着層12を介して貼り合わせて構成されている。半導体基板11は、例えば、シリコン(Si)で構成されたシリコン基板である。ここで、例えば、半導体基板11の熱膨張係数が、3ppm/°Cとされ、ガラス基板13の熱膨張係数が、3~8ppm/°Cとされる場合に、熱膨張係数の異なる半導体基板11と、ガラス基板13を接着層12により加熱接合すると、室温に戻った際に反りが発生することになる。

20

**【0024】**

ここで、上述の特許文献1には、ガラス基板13の厚みを1~3mmとしているが、反りを低減することが開示されているが、ガラス基板13の厚みを1mm以上とする必要があるため、固体撮像素子1の厚みを1mm以下にすることができず、固体撮像素子1の小型化の要求に応えることができない。すなわち、ガラス基板13の厚みは、薄いほど好ましいが、特許文献1に開示された構造であると、ガラス基板13には、反りを低減するための厚みが必要となる。

30

**【0025】**

また、特許文献1には、半導体基板11とガラス基板13を貼り合わせた基板の反り量を2mm以下に抑制すれば、全体の厚みは問題にならないとの開示がされているが、実際には、選択する接着層12の熱膨張や応力によっても反りが加えられるので、スピンドルへの吸着不良やシリコンデバイス表面にかかる応力によるチップひずみによって、特性不良を起こすこととなる。

**【0026】**

なお、図2に示すように、半導体基板11を、接着層12を介してガラス基板13に貼り合わせた場合に、半導体基板11がガラス基板13に引っ張られて、ひずんでしまうという現象が知られている。図2では、「Ideal」で示した線によって、理想的なチップの形状を表しているが、ガラス基板13に引っ張られてひずむことで、「Residual」で示した線で表すように、各矩形の頂点が黒点の位置にずれて、その形状が、ゆがんだ形状となっている。

40

**【0027】**

このようなガラス基板13を貼り付けることに起因するひずみを抑制するためには、ガラス基板13の厚みを減らすことが効果的である。ここで、上述の特許文献1には、半導体基板11の厚みが50~300μmで、ガラス基板13の厚みが1~3mmとなる構造が開示されており、ガラス基板13の厚みを1mm以上とする必要があるため、ガラス基板13を貼り

50

付けることに起因するひずみの影響が大きくなる。

**【0028】**

以上のように、図1の基板（貼り合わせ基板）の構造を採用した場合に、貼り合わせ基板で生じる反りを抑制しようとすると、その構造上、小型化の要求に応えることができない。そのため、小型化の要求に応えつつも、基板を貼り合わせることで生じる反りを抑制したいという要求がある。

**【0029】**

（反り補正を行う場合における貼り合わせ基板の構造）

図3は、本技術を適用した反り補正を行う場合における貼り合わせ基板の構造を示す図である。

10

**【0030】**

図3において、固体撮像素子101は、半導体基板111とガラス基板113を、接着層112を介して貼り合わせて構成されているが、接着層112とガラス基板113との間に、反り補正膜114を設けている。

**【0031】**

半導体基板111は、例えば、シリコン(Si)で構成されたシリコン基板である。なお、半導体基板111は、シリコン基板に限らず、ゲルマニウム等の単元素であってもよいし、ガリウム砒素やインジウムリン等の化合物半導体であってもよい。半導体基板111には、光電変換を行う画素部が2次元配列された画素領域や、画素部の制御を行う制御回路などが形成されている。ガラス基板113は、半導体基板111の上側に形成される透明絶縁基板である。

20

**【0032】**

反り補正膜114は、半導体基板111とガラス基板113を貼り合わせた基板（貼り合わせ基板）の反りを補正するために設けられる層である。反り補正膜114は、半導体基板111又はガラス基板113の表面又は裏面に、それらの基板の加熱接合後の反りを補正するために、半導体基板111、接着層112、及び、ガラス基板113についての熱膨張係数、及び、応力の少なくとも一方を最適化した膜として形成される。

**【0033】**

すなわち、加熱接合後の反りを補正するために、各基板の熱膨張係数、弾性率、厚み等の物性値を用いることになる。例えば、図4に示すように、半導体基板111とガラス基板113では、熱膨張係数が異なるために基板の縮量が異なって、加熱接合後に反ってしまうため、反り補正膜114を形成することで、その反りを補正するようにしている。

30

**【0034】**

なお、反り補正膜114は、例えば、SiO<sub>2</sub>膜、TEOS膜、SiN膜、SiCO膜、SiC膜の他、SO<sub>2</sub>Gや有機膜（例えば、アクリルやエポキシ）などから形成される。また、反り補正膜114は、半導体基板111に形成された画素領域に光を照射するために、透明膜として形成される。

**【0035】**

ここで、最適化された反り補正膜114の形成方法について説明する。図5は、最適化された反り補正膜114を形成するためのシミュレーションの結果を示す図である。

40

**【0036】**

図5において、横軸は、半導体基板111の反り量（単位：μm）を表しており、図中の右側に向かうほど、その値が大きくなることを示している。また、左側の縦軸は、半導体基板111とガラス基板113を貼り合わせた基板（貼り合わせ基板）の反り量（単位：μm）を表しており、図中の上側に向かうほど、その値が大きくなることを示している。さらに、右側の縦軸は、半導体基板111のひずみ量（単位：ppm）を表しており、図中の上側に向かうほど、その値が大きくなることを示している。

**【0037】**

なお、各軸の反り量（単位：μm）であるが、「0」がフラットな状態を示し、「+」が下に反った状態で、「-」が上に反った状態を示している。また、固体撮像素子101の

50

製造工程では、半導体基板111とガラス基板113を貼り合わせた後に、半導体基板111の薄膜化が行われる。ここでは、薄膜化が行われる前を、「BG前」と称し、薄膜化が行われた後を、「BG後」と称する。

#### 【0038】

ここで、白抜きの四角の点を直線でつないだ折れ線グラフは、半導体基板111とガラス基板113を貼り合わせた後であって、半導体基板111を薄肉化する前(BG前)における基板の反り量の変化を表している。すなわち、図中の横軸が半導体基板111の反り量を表すとともに、図中の左側の縦軸が貼り合わせ基板の反り量を表しているので、半導体基板111の反り量が大きくなると、貼り合わせ基板の反り量も大きくなる。したがって、半導体基板111を「-」側に反らせておくことで、貼り合わせ基板の反りを抑制することができる。10

#### 【0039】

また、黒塗りのひし形の点を直線でつないだ折れ線グラフは、半導体基板111とガラス基板113を貼り合わせた後であって、半導体基板111を薄肉化した後(BG後)における基板の反り量の変化を表している。すなわち、図中の横軸が半導体基板111の反り量を表すとともに、図中の左側の縦軸が貼り合わせ基板の反り量を表しているので、半導体基板111を「-」側に反らせ過ぎると、貼り合わせ基板の反りが大きくなってしまう。

#### 【0040】

すなわち、半導体基板111とガラス基板113の貼り合わせだけを考慮すれば、半導体基板111を「-」側に反らせればよいが、薄肉化までを考慮すると、半導体基板111を「-」側に反らせ過ぎるのはよくないため、反り補正膜114を形成する際には、貼り合わせと薄肉化を考慮して、半導体基板111の初期反りの位置を最適な位置に制御する必要がある。つまり、初期の反りを圧縮応力にしておくことで、半導体基板111とガラス基板113を貼り合わせた後の反りと、薄肉化した後の反りを抑制することができる。

#### 【0041】

さらに、白抜きの三角の点を直線でつないだ折れ線グラフは、半導体基板111のひずみ量の変化を表している。すなわち、図中の右側の縦軸が半導体基板111のひずみ量を表しており、ひずみ量が0に近づくほど、ひずまなくなるので、ひずみ量が0の近傍になるように、半導体基板111の初期反りの位置を最適な位置に制御する必要がある。例えば、図中の横軸の半導体基板111の初期反りの位置を、-50 μmくらい反らせた状態で、ガラス基板113に貼り合わせると、ひずみの影響を受けずに、貼り合わせを行うことができる。30

#### 【0042】

このように、半導体基板111とガラス基板113を貼り合わせたときの反りを抑えるだけでなく、ひずみ量も補正することができる。例えば、上述した図2に示したように、半導体基板111を、接着層112を介してガラス基板113に貼り合わせた場合に、半導体基板111がガラス基板113に引っ張られて、ひずんでしまうという現象が知られているが、反り補正膜114により半導体基板111の初期反りを制御して、ひずみ量の補正を行うことで、ひずみの影響を受けずに、貼り合わせを行うことができる。40

#### 【0043】

以上のような最適化された反り補正膜114を形成することで、半導体基板111とガラス基板113を、接着層112を介して貼り合わせた基板(貼り合わせ基板)の反りを抑制することができる。

#### 【0044】

また、反り補正膜114を用いて反りを補正することから、ガラス基板113の厚みを薄くすることが可能となる。例えば、図3の固体撮像素子101においては、ガラス基板113の厚みを1mm以下にできるとともに、接着層112と反り補正膜114の厚みが1~100 μmとなることが、シミュレーションの結果得られている。50

**【0045】**

そして、図3の固体撮像素子101において、半導体基板111の厚みが50~300μmとなるので、図1の固体撮像素子1と比べて、厚みを減らすことができるため、結果として、基板を貼り合わせることで生じる反りを抑制しながら、小型化の要求にも応えることができる。なお、ガラス基板113の厚みは、半導体基板111のひずみを抑えられるなどの観点からも、薄いほうが好ましい。

**【0046】**

なお、例えば、半導体基板111の熱膨張係数は3ppm/ とされ、ガラス基板113の熱膨張係数は3~8ppm/ とするのが好適であることが、シミュレーションの結果得られている。また、反り補正膜114の厚みは、より薄いほうが好ましい。さらに、接着層112は、応力を持たないようになります。

10

**【0047】**

また、半導体基板111の熱膨張係数と近い、熱膨張係数を有するガラス基板113を用いることは可能であるが、若干の熱膨張係数の違いによる反りでも、半導体プロセスでの搬送トラブルが発生することが想定される。それに対して、本技術では反り補正膜114によって、基板などによる熱膨張係数の違いを吸収できるので、半導体プロセス時の搬送信頼性が向上する。

**【0048】**

さらに、半導体基板111の表面に形成される材料やパターン形状によって、その熱膨張係数が変化するため、その都度、貼り合わせるガラス基板113の熱膨張係数を変更することは困難であって、安定した接合プロセスを構築するのは難しいことが想定される。それに対して、本技術では反り補正膜114によって、基板などによる熱膨張係数の違いを吸収できるので、安定した接合プロセスを構築することができる。

20

**【0049】**

さらにまた、半導体基板111の表面に形成された素子についても、構成する材料やレイアウトにより反りが変化するが、熱膨張係数を細かく制御したガラス基板113を製造することが、コストの面から困難であるため、多品種に適用させることが難しいと想定される。それに対して、本技術では、反り補正膜114によって、熱膨張係数を細かく制御することができるので、多品種に適用することが可能となる。

30

**【0050】**

(反り補正を行う場合における貼り合わせ基板の他の構造)

図6は、本技術を適用した反り補正を行う場合における貼り合わせ基板の他の構造を示す図である。

**【0051】**

上述した説明では、固体撮像素子101としての、貼り合わせ基板(図3等)は、下層から上層に、半導体基板111、接着層112、反り補正膜114、ガラス基板113の順に積層される構造を有しているとして説明したが、例えば、図6A乃至図6Cの構造など、他の構造を採用することができる。

**【0052】**

40

図6Aにおいて、貼り合わせ基板は、下層から上層に、半導体基板111、反り補正膜114、接着層112、ガラス基板113の順に積層される構造を有している。

**【0053】**

図6Bにおいて、貼り合わせ基板は、下層から上層に、半導体基板111、接着層112、ガラス基板113、反り補正膜114の順に積層される構造を有している。

**【0054】**

図6Cにおいて、貼り合わせ基板は、下層から上層に、反り補正膜114、半導体基板111、接着層112、ガラス基板113の順に積層される構造を有している。

**【0055】**

このように、貼り合わせ基板において、反り補正膜114は、半導体基板111又はガ

50

ラス基板 113 の表面又は裏面に形成されて、それらの基板の加熱接合後の反りを補正することになる。なお、以下の説明では、固体撮像素子 101 が、図 6 A の構造を有する場合について説明する。

**【 0 0 5 6 】**

< 2 . 固体撮像素子の構造例 >

**【 0 0 5 7 】**

(半導体基板の回路構成 )

図 7 は、固体撮像素子 101 を構成する半導体基板 111 の回路構成を示す図である。

**【 0 0 5 8 】**

図 7 において、半導体基板 111 は、画素アレイ部 151、垂直駆動回路 152、カラム信号処理回路 153、水平駆動回路 154、出力回路 155、制御回路 156、及び、入出力端子 157 を含んで構成される。

10

**【 0 0 5 9 】**

画素アレイ部 151 には、単位画素 161 が 2 次元アレイ状に配列される。単位画素 161 は、光電変換素子としてのフォトダイオードと、複数の画素トランジスタを有して構成される。なお、単位画素 161 の回路構成例については、図 8 を参照して後述する。

**【 0 0 6 0 】**

垂直駆動回路 152 は、例えばシフトレジスタによって構成され、所定の画素駆動配線 171 を選択して、選択された画素駆動配線 171 に単位画素 161 を駆動するためのパルスを供給し、行単位で単位画素 161 を駆動する。すなわち、垂直駆動回路 152 は、画素アレイ部 151 の各単位画素 161 を行単位で順次垂直方向に選択走査し、各単位画素 161 の光電変換素子において受光量に応じて生成された信号電荷に基づく画素信号を、垂直信号線 172 を通してカラム信号処理回路 153 に供給する。

20

**【 0 0 6 1 】**

カラム信号処理回路 153 は、単位画素 161 の列ごとに配置されており、1 行分の単位画素 161 から出力される信号を画素列ごとにノイズ除去などの信号処理を行う。例えば、カラム信号処理回路 153 は、画素固有の固定パターンノイズを除去するための CDS (Correlated Double Sampling : 相関 2 重サンプリング) 及び AD (Analog Digital) 変換等の信号処理を行う。

**【 0 0 6 2 】**

水平駆動回路 154 は、例えばシフトレジスタによって構成され、水平走査パルスを順次出力することによって、カラム信号処理回路 153 の各々を順番に選択し、カラム信号処理回路 153 の各々から画素信号を水平信号線 173 に出力させる。

30

**【 0 0 6 3 】**

出力回路 155 は、カラム信号処理回路 153 の各々から水平信号線 173 を通して順次に供給される信号に対し、信号処理を行って出力する。出力回路 155 は、例えば、バファリングだけする場合もあるし、黒レベル調整、列ばらつき補正、各種デジタル信号処理などが行われる場合もある。

**【 0 0 6 4 】**

制御回路 156 は、入力クロック信号と、動作モードなどを指令するデータを受け取り、また、半導体基板 111 の内部情報などのデータを出力する。すなわち、制御回路 156 は、垂直同期信号、水平同期信号、及び、マスタクロック信号に基づいて、垂直駆動回路 152、カラム信号処理回路 153、及び、水平駆動回路 154 などの動作の基準となるクロック信号や制御信号を生成する。そして、制御回路 156 は、生成したクロック信号や制御信号を、垂直駆動回路 152、カラム信号処理回路 153、及び、水平駆動回路 154 等に出力する。

40

**【 0 0 6 5 】**

入出力端子 157 は、外部と信号のやりとりを行う。

**【 0 0 6 6 】**

以上のように構成される、図 7 の半導体基板 111 は、CDS処理とAD変換処理を行う力

50

ラム信号処理回路 153 が画素列ごとに配置されたカラムAD方式と呼ばれるCMOS (Complementary Metal Oxide Semiconductor) イメージセンサである。

**【0067】**

(単位画素の回路構成例)

図8は、図7の単位画素161の等価回路を示している。

**【0068】**

図8の単位画素161は、電子式のグローバルシャッタ機能を実現する構成を示している。

**【0069】**

図8において、単位画素161は、フォトダイオード211、第1転送トランジスタ212、メモリ部(MEM)213、第2転送トランジスタ214、FD(フローティング拡散領域)215、リセットトランジスタ216、増幅トランジスタ217、選択トランジスタ218、及び、排出トランジスタ219を有する。10

**【0070】**

フォトダイオード211は、受光量に応じた電荷(信号電荷)を生成し、蓄積する光電変換素子である。フォトダイオード211のアノード端子が接地されているとともに、カソード端子が第1転送トランジスタ212を介してメモリ部213に接続されている。また、フォトダイオード211のカソード端子は、不要な電荷を排出するための排出トランジスタ219とも接続されている。

**【0071】**

第1転送トランジスタ212は、転送信号TRXによりオンされたとき、フォトダイオード211で生成された電荷を読み出し、メモリ部213に転送する。メモリ部213は、FD215に電荷を転送するまでの間、一時的に電荷を保持する電荷保持部である。20

**【0072】**

第2転送トランジスタ214は、転送信号TRGによりオンされたとき、メモリ部213に保持されている電荷を読み出し、FD215に転送する。

**【0073】**

FD215は、メモリ部213から読み出された電荷を信号として読み出すために保持する電荷保持部である。リセットトランジスタ216は、リセット信号RSTによりオンされたとき、FD215に蓄積されている電荷が定電圧源VDDに排出されることで、FD215の電位をリセットする。30

**【0074】**

増幅トランジスタ217は、FD215の電位に応じた画素信号を出力する。すなわち、増幅トランジスタ217は定電流源としての負荷MOS220とソースフォロワ回路を構成し、FD215に蓄積されている電荷に応じたレベルを示す画素信号が、増幅トランジスタ217から選択トランジスタ218を介してカラム信号処理回路153(図7)に出力される。負荷MOS220は、例えば、カラム信号処理回路153内に配置されている。

**【0075】**

選択トランジスタ218は、選択信号SELにより単位画素161が選択されたときオンされ、単位画素161の画素信号を、垂直信号線172を介してカラム信号処理回路153に出力する。40

**【0076】**

排出トランジスタ219は、排出信号OFGによりオンされたとき、フォトダイオード211に蓄積されている不要電荷を定電圧源VDDに排出する。

**【0077】**

なお、転送信号TRX、転送信号TRG、リセット信号RST、排出信号OFG、及び、選択信号SELは、画素駆動配線171を介して垂直駆動回路152から供給される。

**【0078】**

次に、図8の単位画素161の動作について簡単に説明する。

**【0079】**

10

20

30

40

50

まず、露光開始前に、Highレベルの排出信号OFGが排出トランジスタ219に供給されることにより排出トランジスタ219がオンされ、フォトダイオード211に蓄積されている電荷が定電圧源VDDに排出され、全画素のフォトダイオード211がリセットされる。

#### 【0080】

フォトダイオード211のリセット後、排出トランジスタ219が、Lowレベルの排出信号OFGによりオフされると、画素アレイ部151の全画素で露光が開始される。

#### 【0081】

あらかじめ定められた所定の露光時間が経過すると、画素アレイ部151の全画素において、転送信号TRXにより第1転送トランジスタ212がオンされ、フォトダイオード211に蓄積されていた電荷が、メモリ部213に転送される。10

#### 【0082】

第1転送トランジスタ212がオフされた後、各単位画素161のメモリ部213に保持されている電荷が、行単位に、順次、カラム信号処理回路153に読み出される。読み出し動作は、読み出し行の単位画素161の第2転送トランジスタ214が転送信号TRGによりオンされ、メモリ部213に保持されている電荷が、FD215に転送される。

#### 【0083】

そして、選択トランジスタ218が選択信号SELによりオンされることで、FD215に蓄積されている電荷に応じたレベルを示す信号が、増幅トランジスタ217から選択トランジスタ218を介してカラム信号処理回路153に出力される。20

#### 【0084】

以上のように、図8の画素回路を有する単位画素161は、露光時間を画素アレイ部151の全画素で同一に設定し、露光終了後はメモリ部213に電荷を一時的に保持しておいて、メモリ部213から行単位に順次電荷を読み出すグローバルシャッタ方式の動作(撮像)が可能である。

#### 【0085】

なお、単位画素161の回路構成としては、図8に示した構成に限定されるものではなく、例えば、メモリ部213を持たず、いわゆるローリングシャッタ方式による動作を行う回路構成を採用することもできる。

#### 【0086】

##### (固体撮像素子の詳細構造)

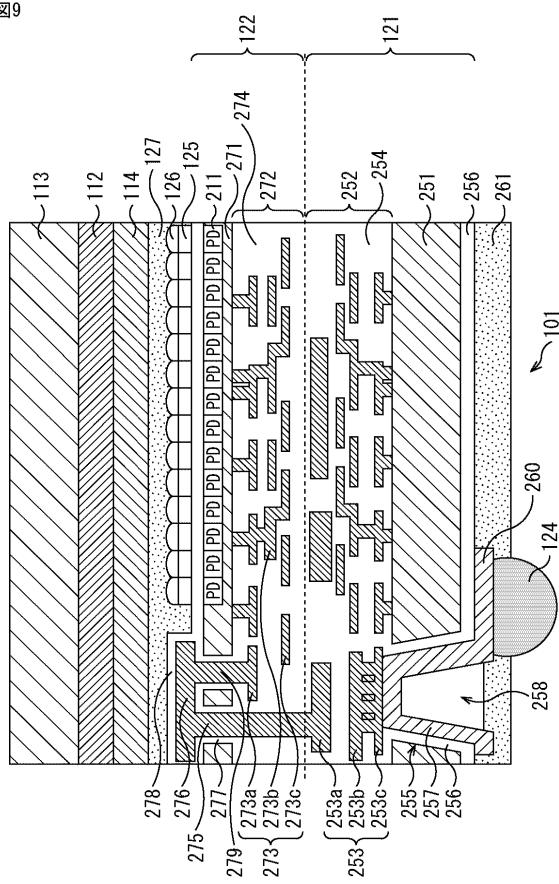

次に、図9を参照して、固体撮像素子101の詳細構造について説明する。図9は、固体撮像素子101の一部分を拡大して示した断面図である。

#### 【0087】

図9において、半導体基板111は、下側基板121と上側基板122とが積層されて構成される。下側基板121には、不図示の外部基板と電気的に接続するための裏面電極であるはんだボール124が複数形成されている。

#### 【0088】

上側基板122の上面には、R(赤)、G(緑)、又は、B(青)のカラーフィルタ125とオンチップレンズ126が形成されている。また、上側基板122は、ガラス基板113と、接着層112、反り補正膜114、及び、透明樹脂層127を介してキャビティレス構造で接続されている。40

#### 【0089】

下側基板121には、シリコン(Si)で構成されたシリコン基板251の上側(上側基板122側)に、多層配線層252が形成されている。この多層配線層252により、例えば、制御回路やロジック回路が構成される。

#### 【0090】

多層配線層252は、上側基板122に最も近い最上層の配線層253a、中間の配線層253b、及び、シリコン基板251に最も近い最下層の配線層253cなどからなる複数の配線層253と、各配線層253の間に形成された層間絶縁膜254とで構成され50

る。

#### 【0091】

複数の配線層253は、例えば、銅(Cu)、アルミニウム(Al)、タンゲステン(W)などを用いて形成され、層間絶縁膜254は、例えば、SiO<sub>2</sub>膜、SiN膜などで形成される。複数の配線層253及び層間絶縁膜254のそれぞれは、全ての階層が同一の材料で形成されていてもよいし、階層によって2つ以上の材料を使い分けてもよい。

#### 【0092】

シリコン基板251の所定の位置には、シリコン基板251を貫通するシリコン貫通孔255が形成されており、シリコン貫通孔255の内壁に、絶縁膜256を介して接続導体257が埋め込まれることにより、シリコン貫通電極(TSV: Through Silicon Via)258が形成されている。絶縁膜256は、例えば、SiO<sub>2</sub>膜やSiN膜などで形成することができる。

10

#### 【0093】

なお、図9に示されるシリコン貫通電極258では、内壁面に沿って絶縁膜256と接続導体257が成膜され、シリコン貫通孔255内部が空洞となっているが、内径によつてはシリコン貫通孔255内部全体が接続導体257で埋め込まれることもある。換言すれば、貫通孔の内部が導体で埋め込まれっていても、一部が空洞となっていてもどちらでもよい。このことは、後述するチップ貫通電極(TCV: Through Chip Via)275などについても同様である。

#### 【0094】

20

シリコン貫通電極258の接続導体257は、シリコン基板251の下面側に形成された再配線260と接続されており、再配線260は、はんだボール124と接続されている。接続導体257及び再配線260は、例えば、銅(Cu)、タンゲステン(W)、ポリシリコンなどで形成することができる。

#### 【0095】

また、シリコン基板251の下面側には、はんだボール124が形成されている領域を除いて、再配線260と絶縁膜256を覆うように、ソルダマスク(ソルダレジスト)261が形成されている。

#### 【0096】

30

一方、上側基板122には、シリコン(Si)で構成されたシリコン基板271の下側(下側基板121側)に、多層配線層272が形成されている。この多層配線層272により、例えば、画素領域の画素回路が構成されている。

#### 【0097】

多層配線層272は、シリコン基板271に最も近い最上層の配線層273a、中間の配線層273b、及び、下側基板121に最も近い最下層の配線層273cなどからなる複数の配線層273と、各配線層273の間に形成された層間絶縁膜274とで構成される。

#### 【0098】

複数の配線層273及び層間絶縁膜274として使用される材料は、上述した配線層253及び層間絶縁膜254の材料と同種のものを採用することができる。また、複数の配線層273や層間絶縁膜274が、1又は2つ以上の材料を使い分けて形成されてもよい点も、上述した配線層253及び層間絶縁膜254と同様である。

40

#### 【0099】

なお、図9の例では、上側基板122の多層配線層272は3層の配線層273で構成され、下側基板121の多層配線層252は4層の配線層253で構成されているが、配線層の総数はこれに限られず、任意の層数で形成することができる。

#### 【0100】

シリコン基板271内には、PN接合により形成されたフォトダイオード211が、単位画素161ごとに形成されている。また、図示は省略されているが、多層配線層272とシリコン基板271には、第1転送トランジスタ212、第2転送トランジスタ214な

50

どの複数の画素トランジスタや、メモリ部 213 なども形成されている。

**【0101】**

カラーフィルタ 125 とオンチップレンズ 126 が形成されていないシリコン基板 271 の所定の位置には、上側基板 122 の配線層 273a と接続されているシリコン貫通電極 279 と、下側基板 121 の配線層 253a と接続されているチップ貫通電極 275 が形成されている。

**【0102】**

チップ貫通電極 275 とシリコン貫通電極 279 は、シリコン基板 271 上面に形成された接続用配線 276 で接続されている。また、シリコン貫通電極 279 及びチップ貫通電極 275 のそれぞれとシリコン基板 271との間には、絶縁膜 277 が形成されている。

10 さらに、シリコン基板 271 の上面には、平坦化膜（絶縁膜）278 を介して、カラーフィルタ 125 やオンチップレンズ 126 が形成されている。

**【0103】**

以上のように、図 9 に示される固体撮像素子 101 の半導体基板 111 は、下側基板 121 の多層配線層 272 側と、上側基板 122 の多層配線層 252 側とを貼り合わせた積層構造となっている。図 9 では、下側基板 121 の多層配線層 272 側と、上側基板 122 の多層配線層 252 側とを貼り合わせ面が、破線で示されている。

**【0104】**

また、固体撮像素子 101 では、上側基板 122 の上面には、カラーフィルタ 125 とオンチップレンズ 126 が形成され、オンチップレンズ 126 上には、表面が平坦化された透明樹脂層 127 が形成されている。ここで、オンチップレンズ 126 の屈折率は 2.0 程度であり、透明樹脂層 127 を構成する有機材料等の屈折率が 1.4 程度であるため、固体撮像素子 101 において、オンチップレンズ 126 による集光性能を確保することができる。

20

**【0105】**

さらに、上側基板 122 は、ガラス基板 113 と、接着層 112、反り補正膜 114、及び、透明樹脂層 127 を介してキャビティレス構造で接続されている。ここで、ガラス基板 113 と接着層 112 の屈折率は 1.5 程度であり、反り補正膜 114 の屈折率は 1.4 ~ 1.5 程度とされる。すなわち、反り補正膜 114 の屈折率（1.4 ~ 1.5 程度）は、半導体基板上の最表面膜となる透明樹脂層 127 の屈折率（1.4 程度）と、接着層 112 の屈折率（1.5 程度）の間の値となって、各層における屈折率の差が小さくなるため、光の反射を防止することができる。

30

**【0106】**

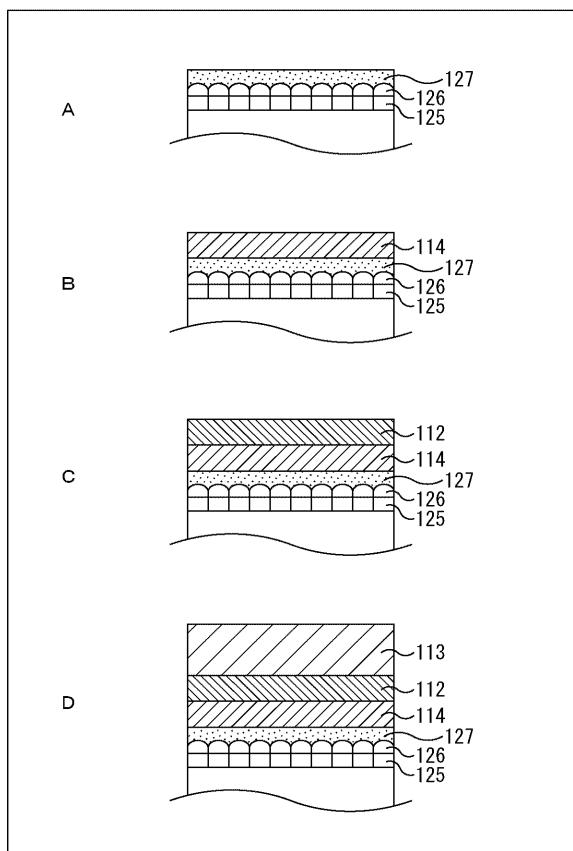

<3. 固体撮像素子の製造方法>

**【0107】**

次に、図 10 を参照して、図 9 の構造を有する固体撮像素子 101 の製造方法について説明する。なお、図 10 においては、上側基板 122 の上面に形成される、カラーフィルタ 125 とオンチップレンズ 126 よりも上層の構成のみを示し、その他の構成については図示を省略している。

**【0108】**

初めに、半製品状態の下側基板 121 と上側基板 122 とが別々に製造される。下側基板 121 としては、シリコン基板（シリコンウエハ）251 の各チップ部となる領域に、多層配線層 252 が形成される。一方、上側基板 122 としては、シリコン基板（シリコンウエハ）271 の各チップ部となる領域に各単位画素 161 のフォトダイオード 211 や画素トランジスタのソース / ドレイン領域が形成される。また、シリコン基板 271 の一方の面に、多層配線層 272 が形成されるとともに、他方の面に、カラーフィルタ 125 とオンチップレンズ 126 が形成される。

40

**【0109】**

そして、製造された下側基板 121 の多層配線層 272 側と、上側基板 122 の多層配線層 252 側とが向き合うように貼り合わされる。また、図 10A に示すように、貼り合

50

わされた下側基板 121 と上側基板 122 のオンチップレンズ 126 が形成されている面全体に、透明樹脂層 127 が塗布される。

#### 【0110】

次に、図 10B に示すように、透明樹脂層 127 上に、半導体基板 111 とガラス基板 113 を貼り合わせた際に発生する反りを補正可能な反り補正膜 114 を形成する。反り補正膜 114 は、透明で、応力を制御することができて、かつ、膜厚の制御範囲の広いP-CVD で形成される膜であることが好ましい。また、反りは、膜厚と膜自体が持つ応力で決まるため、半導体基板 111 の反りとその熱膨張、及び、ガラス基板 113 の反りとその熱膨張を考慮して、膜応力と膜厚から最適な条件が算出される。

#### 【0111】

また、反り補正膜 114 の膜種は、例えば、SiO<sub>2</sub>膜、TEOS膜、SiN膜、SiCO膜、SiCN膜、SiC膜などを用いることができるが、屈折率差のある膜界面で発生する光の反射を考慮すると、透明樹脂層 127 の屈折率（1.4程度）と、ガラス基板 113 と貼り合わせるための接着層 112 の屈折率（1.5程度）との間の屈折率（1.4～1.5程度）であることが好ましい。また、ここでは、P-CVD を用いた例を挙げたが、応力を持つ透明な膜であれば、製法や膜種は問わず、塗布で成膜するSOG や有機膜（例えば、アクリルやエポキシ）を用いるようにしてもよい。

#### 【0112】

次に、図 10C に示すように、反り補正膜 114 上に、ガラス基板 113 と貼り合わせるための接着層 112 が形成される。そして、図 10D に示すように、接着層 112 によってガラス基板 113 が貼り合わされる。なお、固体撮像素子 101 の製造工程では、半導体基板 111 とガラス基板 113 を貼り合わせた後に、半導体基板 111 の薄膜化等の工程が行われるが、簡略化のため、ここではその説明は省略する。

#### 【0113】

なお、図 10において、固体撮像素子 101 の製造方法として、固体撮像素子 101 が、図 6A の構造を有する場合について説明したが、図 6A の構造の代わりに、図 3 の構造や、図 6B 乃至図 6C の構造が採用された場合も同様に、積層される順に各階層が形成されることになる。

#### 【0114】

以上の製造方法により、図 9 の固体撮像素子 101 を製造することができる。

#### 【0115】

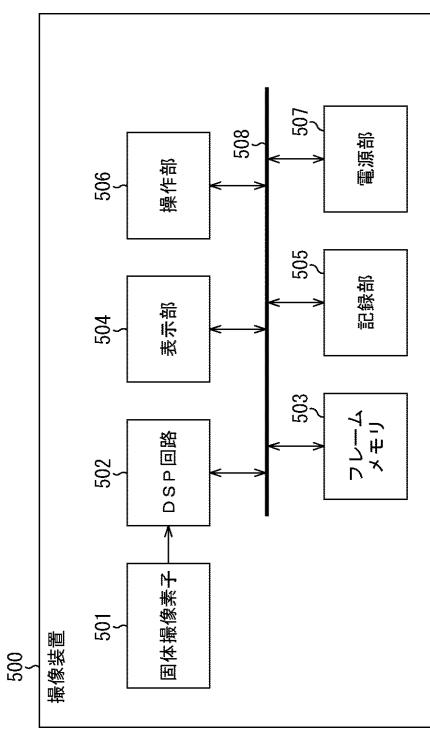

<4. 撮像装置の構成>

#### 【0116】

本技術は、固体撮像素子への適用に限られるものではない。すなわち、本技術は、デジタルスチルカメラやビデオカメラ等の撮像装置や、撮像機能を有する携帯端末装置や、画像読取部に固体撮像素子を用いる複写機など、画像取込部（光電変換素子）に固体撮像素子を用いる電子機器全般に対して適用可能である。

#### 【0117】

図 11 は、電子機器としての撮像装置の構成例を示すブロック図である。

#### 【0118】

図 11 の撮像装置 500 は、図 9 の固体撮像素子 101 の構成が採用される固体撮像素子 501、及び、カメラ信号処理回路であるDSP(Digital Signal Processor)回路 502 を備える。また、撮像装置 500 は、フレームメモリ 503、表示部 504、記録部 505、操作部 506、及び、電源部 507 を備える。DSP回路 502、フレームメモリ 503、表示部 504、記録部 505、操作部 506、及び、電源部 507 は、バスライン 508 を介して相互に接続されている。

#### 【0119】

固体撮像素子 501 は、被写体からの入射光（像光）を取り込んで撮像面上に結像された入射光の光量を画素単位で電気信号に変換して画素信号として出力する。この固体撮像素子 501 として、図 9 の固体撮像素子 101、すなわち、画素領域を含む上側基板 12

10

20

30

40

50

2と、少なくともロジック回路を含む下側基板121を積層することにより小型化された半導体パッケージを用いることができる。

**【0120】**

表示部504は、例えば、液晶パネルや有機EL(Electro Luminescence)パネル等のパネル型表示装置からなり、固体撮像素子501で撮像された動画又は静止画を表示する。記録部505は、固体撮像素子501で撮像された動画又は静止画を、ハードディスクや半導体メモリ等の記録媒体に記録する。

**【0121】**

操作部506は、ユーザによる操作の下に、撮像装置500が持つ様々な機能について操作指令を発する。電源部507は、DSP回路502、フレームメモリ503、表示部504、記録部505及び操作部506の動作電源となる各種の電源を、これら供給対象に對して適宜供給する。

10

**【0122】**

なお、上述した例では、下側基板121と上側基板122とが積層されて構成される半導体基板111がパッケージ化された半導体装置の例として、CMOS固体撮像素子の構成について説明したが、本技術は、固体撮像素子に限らず、その他の用途のパッケージ化された半導体装置に適用することができる。

**【0123】**

例えば、本技術は、可視光の入射光量の分布を検知して画像として撮像する固体撮像素子への適用に限らず、赤外線やX線、あるいは粒子等の入射量の分布を画像として撮像する固体撮像素子や、広義の意味として、圧力や静電容量など、他の物理量の分布を検知して画像として撮像する指紋検出センサ等の固体撮像素子（物理量分布検知装置）全般に対して適用可能である。

20

**【0124】**

本技術の実施の形態は、上述した実施の形態に限定されるものではなく、本技術の要旨を逸脱しない範囲において種々の変更が可能である。例えば、上述した複数の実施の形態の全て又は一部を組み合わせた形態を採用することができる。

**【0125】**

なお、本明細書に記載された効果はあくまで例示であって限定されるものではなく、本明細書に記載されたもの以外の効果があってもよい。

30

**【0126】**

また、本技術は、以下のような構成をとることができる。

**【0127】**

(1)

透明絶縁基板と、

光電変換を行う画素部が2次元配列された画素領域が形成された半導体基板と、

前記透明絶縁基板と前記半導体基板を、接着層を介して貼り合わせた基板の反りを補正するために設けられる反り補正膜と

が積層されて構成される

固体撮像素子。

40

(2)

前記半導体基板の前記画素領域内のオンチップレンズ上に、前記オンチップレンズよりも屈折率の小さい透明樹脂層が形成されている

(1)に記載の固体撮像素子。

(3)

前記半導体基板、前記反り補正膜、前記接着層、前記透明絶縁基板の順に積層されており、

前記反り補正膜の屈折率は、半導体基板上の最表面膜の屈折率と、前記接着層の屈折率との間の値となる

(2)に記載の固体撮像素子。

50

( 4 )

前記反り補正膜は、前記透明絶縁基板、前記半導体基板、及び、前記接着層についての熱膨張係数、及び、応力の少なくとも一方を最適化した膜として形成される

( 1 ) 乃至 ( 3 ) のいずれか一項に記載の固体撮像素子。

( 5 )

前記反り補正膜は、透明膜である

( 1 ) 乃至 ( 4 ) のいずれか一項に記載の固体撮像素子。

( 6 )

前記反り補正膜は、前記半導体基板又は前記透明絶縁基板の表面又は裏面に形成される

( 1 ) に記載の固体撮像素子。

10

( 7 )

透明絶縁基板、又は、光電変換を行う画素部が2次元配列された画素領域が形成された半導体基板の表面又は裏面に、前記透明絶縁基板と前記半導体基板を、接着層を介して貼り合わせた基板の反りを補正するために設けられる反り補正膜を形成する工程と、

前記透明絶縁基板と前記半導体基板を、接着層を介して貼り合わせる工程と

を有する固体撮像素子の製造方法。

( 8 )

透明絶縁基板と、

光電変換を行う画素部が2次元配列された画素領域が形成された半導体基板と、

前記透明絶縁基板と前記半導体基板を、接着層を介して貼り合わせた基板の反りを補正

するために設けられる反り補正膜と

20

が積層されて構成される

固体撮像素子を搭載した撮像装置。

【符号の説明】

【 0 1 2 8 】

101 固体撮像素子, 111 半導体基板, 112 接着層, 113 ガラス

基板, 114 反り補正膜, 125 カラーフィルタ, 126 オンチップレンズ

, 127 透明樹脂層, 151 画素アレイ部, 161 単位画素, 500 撮

像装置, 501 固体撮像素子

【図1】

図1

【図2】

図2

【図3】

図3

【図4】

図4

【図5】

図5

【 図 6 】

図6

【 図 7 】

図7

【 図 8 】

図8

【図9】

图9

【図10】

図10

【図11】

図11

---

フロントページの続き

(56)参考文献 特開2013-038164(JP,A)

特開2009-164314(JP,A)

特開2006-114847(JP,A)

特開2012-204810(JP,A)

特開2008-244032(JP,A)

特開2013-041941(JP,A)

特開2012-175461(JP,A)

特開2012-169489(JP,A)

Jae-Hyun Park et al., A Warpage of Wafer Level Bonding for CIS(CMOS Image Sensor) Device Using Polymer Adhesive, 2009 International Conference on Electronic Packaging Technology & High Density Packaging (ICEPT-HDP), 米国, IEEE, 2009年 8月10日, pp.577-580

(58)調査した分野(Int.Cl., DB名)

H01L 27/146