(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6091273号

(P6091273)

(45) 発行日 平成29年3月8日(2017.3.8)

(24) 登録日 平成29年2月17日(2017.2.17)

(51) Int.Cl.

H01L 31/10 (2006.01)

G02B 6/122 (2006.01)

F 1

H01L 31/10

G02B 6/12A

B

請求項の数 15 (全 36 頁)

(21) 出願番号 特願2013-56803 (P2013-56803)

(22) 出願日 平成25年3月19日 (2013.3.19)

(65) 公開番号 特開2014-183195 (P2014-183195A)

(43) 公開日 平成26年9月29日 (2014.9.29)

審査請求日 平成28年2月12日 (2016.2.12)

(73) 特許権者 000005108

株式会社日立製作所

東京都千代田区丸の内一丁目6番6号

(73) 特許権者 000004237

日本電気株式会社

東京都港区芝五丁目7番1号

(74) 代理人 110001689

青稜特許業務法人

(74) 代理人 110000350

ポレール特許業務法人

(72) 発明者 三浦 真

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所 中央研究所内

最終頁に続く

(54) 【発明の名称】半導体装置とその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体基板と、

前記半導体基板上に形成され、第1の開口部を有する第1の絶縁膜と、

前記第1の開口部直下の前記半導体基板内に形成された第1の溝と、

前記第1の溝内の前記半導体基板上に形成され、前記半導体基板の主成分を成す元素とは異なる元素をその一部に含み、禁制帯幅が前記半導体基板よりも小さい第1の半導体層と、

前記第1の溝内の前記第1の半導体層上に形成され、前記半導体基板の主成分を成す元素とは異なる元素をその一部に含み、禁制帯幅が前記半導体基板よりも小さい第1導電型の第2の半導体層と、

前記第1の開口部内の前記第2の半導体層上に形成され、前記半導体基板の主成分を成す元素と同一元素をその一部に含み、禁制帯幅が前記第1の半導体層及び前記第2の半導体層よりも大きい第1導電側の第3の半導体層と、

前記第1の開口部内の前記第3の半導体層上に形成された金属層とを備え、

前記第1の溝の上部の開口領域は前記第1の開口部を取り囲むように形成され、前記第1の溝の上部では前記第1の絶縁膜からなる庇が形成され、前記第1の溝の側壁は前記半導体基板の(111)面を含み、前記第1の溝の底部は前記半導体基板の(100)面を含み、

前記第1の半導体層は、前記第1の溝底部を構成する前記半導体基板の(100)面と

10

20

、前記第1の溝側壁を構成する半導体基板の(111)面と、前記第1の絶縁膜から成る庇の下部表面と、前記第2の半導体層とに接しており、

前記第2の半導体層は、前記第1の半導体層と、前記第1の絶縁膜から成る庇の下部表面と、前記第3の半導体層とに接しており、

前記第1の半導体層と前記第2の半導体層の界面は、前記第1の半導体層と前記第1の絶縁膜との界面よりも下部に位置し、

前記第3の半導体層と前記金属層の界面は、前記第1の絶縁膜の下部表面と前記第1の絶縁膜の上部表面の間に位置し、

前記第2の半導体層は前記半導体基板から空間的に分離していることを特徴とする半導体装置。

10

**【請求項2】**

前記第1の絶縁膜から成る庇の水平方向の長さは、前記第1の溝の深さに対して10分の1倍以上且つ1倍以下であることを特徴とする請求項1に記載の半導体装置。

**【請求項3】**

前記第2の半導体層と前記第3の半導体層中の不純物濃度は、深さ方向に対してほぼ一定であることを特徴とする請求項1または請求項2に記載の半導体装置。

**【請求項4】**

前記第1の半導体層が受光機能を有することを特徴とする請求項1乃至3のいずれか一項に記載の半導体装置。

**【請求項5】**

前記半導体基板は、前記第1の溝底部の界面において第1導電型を示し、前記半導体装置がダイオードとしての機能を有することを特徴とする請求項1乃至4のいずれか一項に記載の半導体装置。

20

**【請求項6】**

前記半導体基板は、半導体支持基板と、前記半導体支持基板を覆うように形成された絶縁膜と、該絶縁膜上に位置し、導波路状にパターニングされた第1の光導波路とを備えることを特徴とする請求項1乃至5のいずれか一項に記載の半導体装置。

**【請求項7】**

前記半導体基板は、前記第1の光導波路上に、前記第1の光導波路を覆い、前記第1の光導波路の一部表面が露出するような開口を有する絶縁膜と、前記開口内部の前記第1の光導波路上に前記半導体支持基板を構成する元素をその一部に含む第2の光導波路を有していることを特徴とする請求項6に記載の半導体装置。

30

**【請求項8】**

前記第3の半導体層と前記金属層はオーミック接合界面を有することを特徴とする請求項1乃至7のいずれか一項に記載の半導体装置。

**【請求項9】**

前記第3の半導体層と前記金属層はショットキー接合界面を有することを特徴とする請求項1乃至7のいずれか一項に記載の半導体装置。

**【請求項10】**

前記半導体支持基板と前記第1の光導波路はシリコンで構成され、

40

前記第2の光導波路と前記第3の半導体層はシリコンまたはシリコン・ゲルマニウムで構成され、

前記第1の半導体層と前記第2の半導体層はゲルマニウムまたはシリコン・ゲルマニウムで構成され、

前記第1の半導体層と前記第2の半導体層のゲルマニウム組成が、共に前記第2の光導波路と前記第3の半導体層のいずれのゲルマニウム組成よりも大きいことを特徴とする請求項6に記載の半導体装置。

**【請求項11】**

半導体基板上に第1の絶縁膜を形成する工程と、

前記第1の絶縁膜に前記半導体基板が露出した第1の開口部を有する工程と、

50

前記第1の開口部直下の前記半導体基板内に第1の溝を形成する工程と、前記第1の溝内の前記半導体基板上に、前記半導体基板の主成分を成す元素とは異なる元素をその一部に含み、禁制帯幅が前記半導体基板よりも小さい第1の半導体層を形成する工程と、

前記第1の溝内の前記第1の半導体層上に、前記半導体基板の主成分を成す元素とは異なる元素をその一部に含み、禁制帯幅が前記半導体基板よりも小さい第1導電型の第2の半導体層を形成する工程と、

前記第1の開口部内の前記第2の半導体層上に、前記半導体基板の主成分を成す元素と同一元素をその一部に含み、禁制帯幅が前記第1の半導体層及び前記第2の半導体層よりも大きい第1導電側の第3の半導体層を形成する工程と、

前記第1の開口部内の前記第3の半導体層上に金属層を形成する工程とを有し、

前記第1の溝を形成する工程は、前記第1の溝上部の開口領域が前記第1の開口部よりも広くなるよう、水平方向にも前記半導体基板のエッチングを施すことで前記第1の溝上部に前記第1の絶縁膜の庇を形成すると共に、前記第1の溝の底部が前記半導体基板の(100)面を有し、前記第1の溝の側壁が前記半導体基板の(111)面を有するように溝形成条件を調整する工程を含み、

前記第1の半導体層を形成する工程は、前記第1の半導体層が、前記第1の溝底部を構成する前記半導体基板の(100)面と、前記第1の溝側壁を構成する前記半導体基板の(111)面と、前記第1の絶縁膜から成る庇の下部表面とに接すると共に、前記第1の半導体層と前記第2の半導体層の界面が、前記第1の半導体層と前記第1の絶縁膜の界面よりも下部に位置するように前記第1の半導体層の形成条件を調整する工程を含み、

前記第2の半導体層を形成する工程は、前記第2の半導体層が前記第1の半導体層と、前記第1の絶縁膜の庇の下部表面とに接するように前記第2の半導体層の形成条件を調整する工程を含み、

前記第3の半導体層を形成する工程は、前記第3の半導体層と前記金属層の界面が前記第1の絶縁膜の下部表面と前記第1の絶縁膜の上部表面との間に位置するように前記第3の半導体層の形成条件を調整する工程を含むことを特徴とする半導体装置の製造方法。

#### 【請求項12】

前記庇の水平方向の長さは、前記第1の溝の深さに対して10分の1倍以上且つ1倍以下であることを特徴とする請求項11に記載の半導体装置の製造方法。

#### 【請求項13】

前記第2の半導体層と前記第3の半導体層の形成は、不純物を添加したエピタキシャル成長により行い、前記第2の半導体層と前記第3の半導体層中の不純物濃度を、深さ方向に対してほぼ一定とすることを特徴とする請求項11または請求項12に記載の半導体装置の製造方法。

#### 【請求項14】

前記半導体基板には、半導体支持基板と、前記半導体支持基板を覆う絶縁膜と、前記絶縁膜上に形成された単結晶半導体層を有する基板を用い、該絶縁膜上の半導体層を、導波路状にパターニングして第1の光導波路を形成することを特徴とする請求項11乃至13のいずれか一項に記載の半導体装置の製造方法。

#### 【請求項15】

前記半導体支持基板と前記第1の光導波路がシリコンから成る基板を用い、

前記第2の光導波路と前記第3の半導体層をシリコンまたはシリコン・ゲルマニウムとし、

前記第1の半導体層と前記第2の半導体層をゲルマニウムまたはシリコン・ゲルマニウムとし、

前記第1の半導体層と前記第2の半導体層のゲルマニウム組成が、共に前記第2の光導波路と前記第3の半導体層のいずれのゲルマニウム組成よりも大きくすることを特徴とする請求項14に記載の半導体装置の製造方法。

#### 【発明の詳細な説明】

10

20

30

40

50

**【技術分野】****【0001】**

本発明は、受光素子を含む半導体装置とその製造方法に関する。

**【背景技術】****【0002】**

現代の情報化社会の根幹を成すインターネットのプロード・バンド・ネットワークは、光通信が主流となりつつある。光通信システムでは、800 nm ~ 1600 nmの範囲にある近赤外（IR）光が使用されている。特に重要な波長帯は光ファイバの損失が最小となる帯域であり、短距離通信では850 nm、長距離通信では1310 nmと1550 nmが使用されている。これまで、光通信で使用される受光素子・発光素子には、これら長波長帯域で良好な光吸収特性・発光特性を示す砒化ガリウム（GaAs）やインジウム燐（InP）を中心とした化合物半導体が用いられてきた（例えば、特許文献1）。一方で、ネットワークのシステム内における情報処理はシリコン（Si）を主材料とした大規模集積回路（LSI）によって行われてきた。Siは、成熟されたプロセス技術を背景にトランジスタの微細化と高集積化が進んでおり、集積回路には不可欠な材料となっている。このように、これまで光デバイスと電子デバイスにはそれぞれ最適な半導体材料が存在し、それらが各デバイスにおいて良好な特性を有する為の役割を果たしてきた。しかしながら、今後、光通信システムのより一層の普及を促す為にはシステム及びそれを構成するデバイスの低コスト化や、高性能化、更に小型化、低消費電力化が求められることが予想され、複数の基板材料を用いていた従来からの大きな技術革新が求められる。

**【0003】**

上記要求に対して、シリコンチップ上に受光素子、発光素子、光変調器、光導波路等のデバイスを集積させる研究が近年盛んになっている。上記技術により集積回路と光デバイスを1チップ上に集積することが出来、光通信システムの低コスト化や小型・低消費電力化、更にはその基幹となるLSIの高機能化・高付加価値化が可能となり、大きな産業的革新をもたらすことが期待される。Si上に受光素子を混載する方法として、化合物半導体のSi基板上への貼り付け技術またはSi基板上への化合物半導体結晶成長方法が考えられるが、いずれも化合物半導体とSiの間に存在する熱膨張係数と格子定数の大きな差、また化合物半導体の持つ電気的極性が化合物半導体の結晶性を劣化させるため、技術的バリアは高い。SiまたはSi系IV族半導体が受光機能を持てばプロセスバリアは格段に下がり、光デバイス／電子デバイスの融合を容易に行うことが可能である。

**【0004】**

しかし、Siは化合物半導体に比べて受光特性が劣るという欠点がある。受光特性で見ると、Siの禁制帯幅は室温で約1.1 eVであり、1100 nm以上の波長の光を殆ど吸収しない。850 nmの光においても吸収率は悪く、吸収される光の量が1/eに減衰するまでの距離で定義される吸収長は20 μmより大きくなり、実用デバイスとしての使用が困難である。

**【0005】**

このような材料的な不利を解決する手段として、Siと同じIV族半導体のゲルマニウム（Ge）の利用が考えられる。Geは禁制帯幅が室温で約0.6 eVと小さく、800 nm ~ 1600 nmの波長範囲に対して吸収長が2 μm以下であり、実用的な受光素子が形成可能である。更に、GeはSiと同じIV族半導体であることから、Siプロセスとの整合性も良い。従って、Geにより作製した受光素子をSi基板上に作製出来れば、光デバイス／電子デバイスの融合を妨げる物性上／プロセス上の技術バリアを克服することが可能となる。

**【0006】**

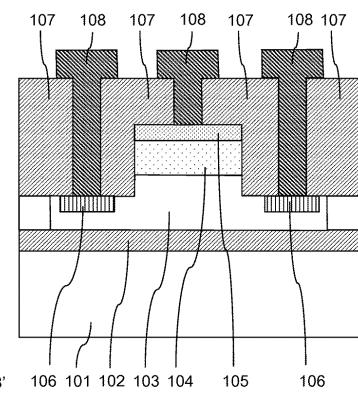

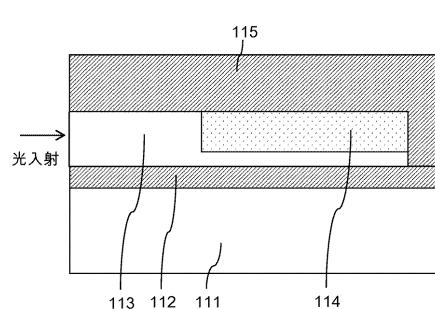

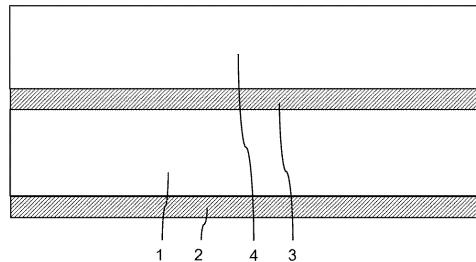

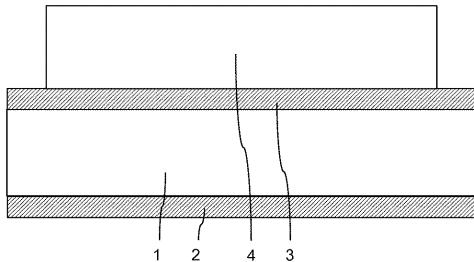

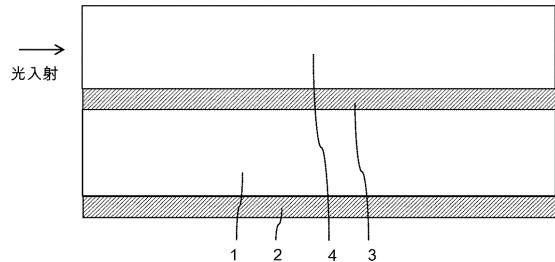

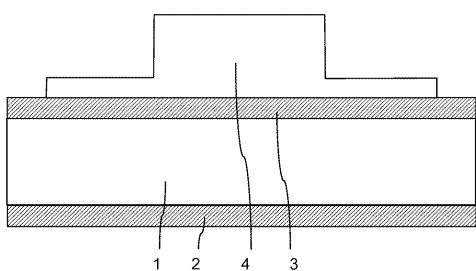

Geを用いた受光素子の例は、例えば非特許文献1～3、特許文献2に開示されている。図4に、従来の受光素子の一例としてSi基板上へのGe受光素子の光入射方向に対して垂直方向の構造例を示す。図4は非特許文献1に基づいて本願発明者らが作成したものではあるが、非特許文献1に開示された図面そのものではない。図4はPIN型受光器構

造となっており、Si層101上に埋め込み二酸化シリコン(SiO<sub>2</sub>)層102とSi膜103を有するSOI(Silicon on Insulator)基板上に、高抵抗のGe膜104が形成されており、p型Si層106とn型Ge層105が金属電極108に接続された構造を有している。SOI層103はSiの光導波路と接続されており、上記光導波路を通して入射された光はGe層104に入射して吸収される。Ge層104は光導波路と接続されたSOI層103の上部に存在するが、GeとSiの光屈折率差により、光はGe層104に入射される。本構造を所謂エバネッセント結合型受光素子という。Ge層104に入射された光はGe層104にて吸収されて電子と正孔が生じ、p型Si層106にマイナス、n型Ge層105にプラスの電極を印加すると上記電子と正孔が加速されてそれぞれn型Ge層105とp型Si層106に吸収され、光電流が流れる。上記電圧印加はp-inダイオードにとって逆バイアスである為、光が入射されていない場合に流れる電流が極めて小さく、光信号のon/offによりそれに追随した電流への信号変換が成される。なお、符号107はSiO<sub>2</sub>層である。

#### 【0007】

Geを用いた受光素子の他の例が、非特許文献2に開示されている。本従来例は、図4におけるn型Ge層105を省略した構造を有しており、金属電極が直接高抵抗のGe層104に接続し、ショットキー接合を形成することを特徴としている。n型Ge層を形成する為のイオン注入工程等が不要になることに加え、Ge層と金属層間のコンタクト抵抗を低減出来る可能性を有している。

#### 【0008】

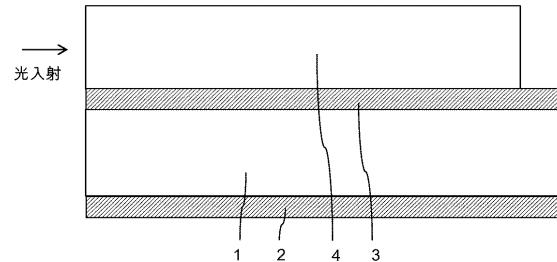

素子の小型化を可能にするバット・ジョイント(Butt-Joint)型の受光素子が、非特許文献3に開示されている。図5Aと図5Bに本従来例のそれぞれ光入射方向と光入射方向に垂直方向の受光素子断面構造を示す。本従来例は、Si光導波路113が掘り込まれた領域に高抵抗Ge光吸收層114が形成され、上記Si光導波路113と高抵抗Ge光吸收層114が端面結合した構造を有している。この為、Si光導波路113から入射した光は進路を変えることなく高抵抗Ge光吸收層114に直接入射される。従ってエバネッセント結合型受光素子に比べて受光効率が高く、素子の小型化が可能になる。本従来例では高抵抗Ge光吸收層114の水平方向の幅を縮小し、Si光導波路113と同一幅としている。本従来例はp型Ge層116と、高抵抗Ge光吸收層114と、n型Ge層117が基板に対して水平方向に配列した横型pin(lateral-pin)構造を有している為、p型Ge層116とn型Ge層117の距離を短縮して高速特性の向上を可能にしている。なお、符号111はSi基板、符号112及び符号115はSiO<sub>2</sub>層、符号118は金属電極である。

#### 【0009】

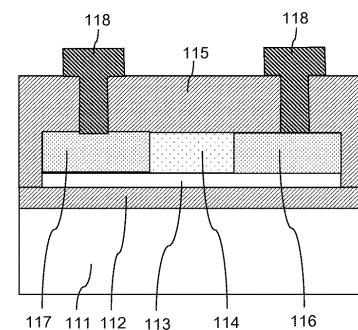

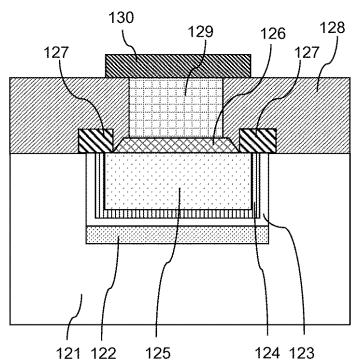

Butt-Joint型受光素子の他の例が、特許文献2に開示されている。図6に本従来例の光入射方向の受光素子断面構造を示す。本従来例は、Si層123とシリコン・ゲルマニウム(SiGe)バッファ層124とGe光吸收層125がSi導波路121中に埋め込まれた構造を有しており、受光層の下部と上部にそれぞれp型Si層122とn型Si層126を配置した縦型pin構造となっている。本従来例も受光効率が高いという利点を活かし、受光断面積を小さく出来ることを特徴としている。受光断面積を縮小する為、Ge光吸收層125の幅をSi導波路121に合わせて短縮するとpinダイオードの容量を小さくすることが出来、低電圧での高周波特性が向上する。この為、素子の低消費電力化が可能になる。

#### 【0010】

上記Butt-Joint型受光器を製造する際のSi光導波路への溝の形成方法は、例えば非特許文献4に開示されている。Si上にSiO<sub>2</sub>層を堆積し、SiO<sub>2</sub>層を一部開口し、Si表面を露出させた後にアルカリ性の水溶液を用いてSiをウェットエッティングし、Si中に溝を形成する手法が開示されている。アルカリ性水溶液の例として、アンモニア水溶液(NH<sub>4</sub>OH)、水酸化カリウム水溶液(KOH)、ヒドラジン-水和物水溶液(H<sub>2</sub>NNH<sub>2</sub>H<sub>2</sub>O)、テトラメチルアンモニウムハイドロオキサイド(TMAH)

10

20

30

40

50

: (C<sub>2</sub>H<sub>3</sub>)<sub>4</sub>N OH) が挙げられている。本従来例では TMAH 水溶液を用いて Si のエッティングを行い、(111) 面から成る側壁と(100) 面から成る底面を有する溝の形成を行っており、エッティングダメージの無い、平坦な Si 面を得た結果が開示されている。

#### 【0011】

非特許文献 5 には、塩化水素 (HCl) ガスを用いた気相エッティングにより Si をエッティングする従来例が開示されている。Si 層上に SiO<sub>2</sub> 層を堆積し、SiO<sub>2</sub> 層を一部開口し、Si 表面を露出させた後に化学気相成長 (Chemical Vapor Deposition: CVD) 装置内にて約 900 の温度で HCl ガスを流入することで、Si を SiO<sub>2</sub> 層に対して選択的にエッティング除去することが出来る結果が開示されている。

10

#### 【0012】

Si 光導波路に形成した溝中に、Ge 光吸收層を選択成長させて埋め込む手法は、例えば非特許文献 3 に開示されている。本従来例では、上部表面に SiO<sub>2</sub> 層を有し、SiO<sub>2</sub> 層の開口部内に溝を有する Si 光導波路に、CVD 法により Ge を SiO<sub>2</sub> に対して選択成長する例が開示されている。Ge 光吸收層の膜厚の最も薄い部分が溝の深さよりも厚くなるまで Ge を成膜し、その後化学機械研磨 (Chemical Mechanical Polishing: CMP) により Ge 光吸收層の表面を平坦化して Ge 光吸收層を Si 光導波路の溝中に埋め込む手法が開示されている。

#### 【先行技術文献】

##### 【特許文献】

20

##### 【0013】

【特許文献 1】特開 2001-189523 号公報

【特許文献 2】国際公開第 09/110632 号パンフレット

##### 【非特許文献】

##### 【0014】

【非特許文献 1】A. Ramaswamy, M. Piels, N. Nunoya, T. Yin and J.E. Bowers, トランズアクションズ・オン・マイクロウェーブ・セオリー・アンド・テクニクス (IEEE Transactions on Microwave Theory and Techniques), 2010年, 58巻, pp. 3336 ~ 3343.

【非特許文献 2】J. Wang and S. Lee, センサーズ (Sensors), 2011年, 11巻, pp. 696 ~ 718.

30

【非特許文献 3】L. Vivien, A. Polzer, D. M. Morini, J. Osmond, J. M. Hartmann, P. Crozat, E. Cassan, C. Kopp, H. Zimmermann and J. M. Fedeli, オプティクス・エクスプレス (OPTICS EXPRESS), 2012年, 20巻, pp. 1096 ~ 1101.

【非特許文献 4】O. Tabata, R. Asahi, H. Funabashi, K. Shimaoka and S. Sugiyama, センサーズ・アンド・アクチュエーターズ (Sensors and Actuators), 1992年, A 34巻, pp. 51 ~ 57.

【非特許文献 5】Y. Bogumilowicz, J. M. Hartmann, R. Truche, Y. Campidelli, G. Holland and T. Billon, セミコンダクター・サイエンス・アンド・テクノロジー (Semiconductor Science and Technology), 2005年, 20巻, pp. 127 ~ 134.

#### 【発明の概要】

40

#### 【発明が解決しようとする課題】

##### 【0015】

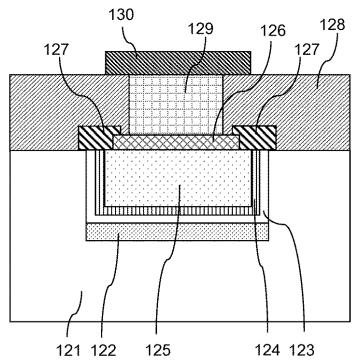

しかしながら、Butt-Joint 型の Ge 受光素子には、下記に示す問題があった。即ち溝を形成した半導体層上に、異種材料を含む半導体層を選択成長させる際の問題点が特許文献 1 に開示されている。Si 溝中への Ge 層の選択成長に関しても、非特許文献 3 に特許文献 1 と同様の現象が開示されている。発明者等は上記文献に開示された結果に基づき、上部表面に SiO<sub>2</sub> 層を有し、SiO<sub>2</sub> 層の開口部内に溝を有する Si 基板に Ge 層を選択成長した場合の断面形状について検討した。その結果を図 7 に示す。Si 基板 131 の溝内に選択成長した Ge 層 133 は、開口部端において側壁 (ファセット) を形成しながら成長し、溝の周辺部で凸形状を有する。この為、溝の周辺部と中心部で膜厚差

50

が発生し、表面を平坦化する処理が必要となる。特許文献1には表面平坦化処理を行う記載が無いが、 $\text{SiO}_2$ 層132と $\text{Si}$ 基板131の側壁との位置関係等を規定しない限り同様の現象が起こり得ると考えられる。従って、従来のButt-Joint型のGe受光素子の製造方法は、エバネッセント結合型受光素子に比べて $\text{Si}$ 光導波路に溝を形成する為のエッチング工程と、Ge光吸收層を成膜した後に表面平坦化を行う為のCMP処理が追加される為、工程数が増大する恐れのあることが判った。

#### 【0016】

又特許文献1には、溝を形成した半導体基板上に、異種材料を含む半導体層を選択成長させる際、表面平坦性を保ったまま成長し、溝を埋め込む手法が開示されている。本従来例は、溝を形成する工程において上記半導体基板を水平方向にもサイドエッチングすることで溝上部の周辺に絶縁膜の庇を形成し、更に上記溝の側壁が(111)面となるようにエッチングを行っている。溝の側壁から成長した半導体層は絶縁膜の庇により半導体基板に垂直方向の成長が妨げられ、溝の周辺部における凸形状の発生が抑制される。また、溝側壁を(111)面とすることで、側壁上の成長速度を溝底部の(100)表面よりも遅くすることが出来、絶縁膜で囲まれた開口部内においても半導体層が溝を埋め込むように成長することを可能にしている。

#### 【0017】

しかし、発明者等が検討した結果、 $\text{Si}$ 基板を用いて溝を形成する場合は、上記溝の庇を形成するようにエッチングを行うことは極めて困難であることが判った。上記特許文献1に開示された従来例は、半導体基板に化合物半導体であるインジウム燐(InP)エッチングは酸性エッチング液を用いたウェットエッチングにより行っているが、 $\text{Si}$ 基板を用いてエッチングを行う従来例では、非特許文献4に開示されているように、溝の側壁は(111)面となるものの、 $\text{Si}$ 基板の水平方向へのサイドエッチングは見られておらず、 $\text{SiO}_2$ 層の庇の形成は見られていない。発明者らがTMAH水溶液を用いて行った $\text{Si}$ 基板のエッチング実験においても、 $\text{SiO}_2$ 層の庇の水平方向の長さは、 $\text{Si}$ 基板に形成した溝の深さの1/10以下であり、溝の周辺部におけるGe層の凸形状の発生を抑制する為には不十分であることが判った。従って、従来技術では $\text{Si}$ 光導波路中にGe光吸收層を埋め込む際はCMPによる表面平坦化が不可避である。

#### 【0018】

$\text{Si}$ 光導波路に溝を形成するエッチング工程が追加されることによる工程数の増大を回避する為の解決方法としては、Ge光吸收層を成膜する為のCVD装置内でGe層の成長前に気相エッチングにより $\text{Si}$ をエッチングする手法が考えられる。しかし、非特許文献5に開示されているように、HCl等のエッチングガスを用いて $\text{Si}$ 基板をエッチングする際、十分なエッチング速度を得る為には約900°C程度の温度でエッチングを行う必要があり、プロセス熱負荷の増大が不純物拡散の増大等を引き起こし、受光素子の高速性を劣化させるといった問題の生じる恐れがある。また、受光素子を他の光デバイスまたはトランジスタ等の $\text{Si}$ 電子デバイスと集積する場合、上記熱負荷が上記デバイスの特性を劣化させる問題も懸念される。更に、上記非特許文献5に開示された断面構造では $\text{Si}$ 基板の水平方向へのサイドエッチングが見られておらず、 $\text{SiO}_2$ 層の庇の形成は困難である。

#### 【0019】

製造工程数の増大と共に問題になると思われるのが、素子を小型化する際に課せられる制限と、受光効率の劣化である。図6の断面構造において、特許文献2に開示されたGe光吸收層125上の電極形成工程では、n型 $\text{Si}$ 層126は、不純物を添加しない $\text{Si}$ 層を形成した後に酸化膜127を堆積し、n型電極領域を規定する為の開口部を形成した後にイオン注入により不純物を注入することで形成される。この為、上記開口部端と $\text{Si}$ 層126の端にはパターニングの際のずれを見込んだ一定の幅を確保する必要がある。また、多結晶 $\text{Si}$ 電極129を形成する際も、酸化膜127に形成した開口部に対して一定の間隔を確保して酸化膜128の開口部幅を規定する必要が生じる。この為、Ge光吸收層125の幅は、多結晶 $\text{Si}$ 電極129の幅に対して少なくともパターニング2回分の合わ

10

20

30

40

50

せすれを見込んだ間隔だけ拡げる必要があり、Ge光吸收層の幅を十分に縮小することが出来ず、素子の小型化とそれに伴う電気容量の低減を十分に行うことが出来ない。また、n型Si層126をイオン注入法により形成する為、不純物を活性化する為のアニール時に不純物がGe光吸收層125内に深く入り込み、Ge光吸收層125の実質的な膜厚を減少させ、受光効率が劣化する。

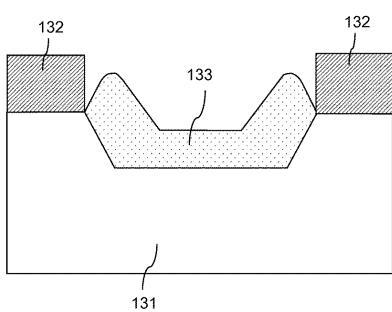

#### 【0020】

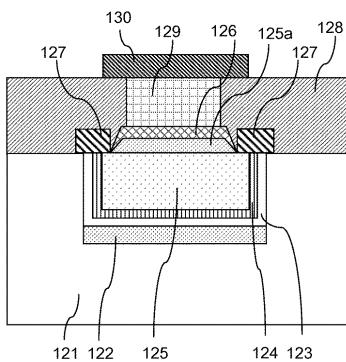

発明者らが危惧した上記課題に対して、従来例から想定され得る解決方法を図8と図9に示す。図8は図6で示した従来例において、n型Si層126への不純物添加をエピタキシャル成長時のドーピングにより行った場合の受光素子断面図である。イオン注入の為のパターニングが不要になる為、パターニング1回分の合わせマージンの確保が不要となる。また、Ge光吸收層125に不純物を拡散させることなく高濃度の不純物をn型Si層126に添加することが可能となるが、高抵抗のGe光吸收層125と高濃度n型のSi層126が接合を形成する為、受光素子動作時にはGe光吸收層125の空乏層領域がn型Si層126との界面近傍まで延びる。Ge光吸收層125上に成長したn型Si層126は、SiとGeの格子定数の違いにより生じた欠陥を内部に含有する。従って、n型Si層126の近傍まで空乏化すると、電圧印加時に上記欠陥部で電子と正孔の再結合電流が発生し、光が入射しない時のリーク電流、即ち暗電流が増大する。上記暗電流の増大を抑制する為、図9に示すようにn型Ge層125aをGe光吸收層125とn型Si層126の間に成長する手法が考えられるが、SiO<sub>2</sub>層127で囲まれた領域に上記n型Ge層125aを選択成長する場合は、上記n型Ge層125aが開口部端においてファセットを形成しながら成長する為、図9に示したように上記開口部端においてn型Si層126と高抵抗Ge光吸收層125の界面が生じ、上記開口部端のn型Si層126直下まで空乏層領域が延びて、上述した暗電流の増大を引き起こす。従って、低暗電流性を確保する為にはn型Si層126をイオン注入にて形成することで受光効率の低下を有る程度犠牲にしなくてはならず、十分な光電流を得る為にはGe光吸收層125の膜厚を厚くする必要がある。これにより、基板に水平方向のみならず、垂直方向にも素子の小型化に対する制限が存在する。なお、符号130は金属電極である。

#### 【0021】

従って、従来の技術では、Butt-Joint型のGe受光素子をエバネッセント結合型受光素子の製造方法とほぼ同程度の工程数で作製することは困難であり、更に素子を小型化する際に制限のあることが判った。

#### 【0022】

本発明は上記の課題を考慮して成されたものであり、その目的とするところは、素子の小型化・高性能化が可能な受光素子を含む半導体装置及びその製造工程数の低減が可能な製造方法を提供することにある。

#### 【課題を解決するための手段】

#### 【0023】

上記目的を達成するための一実施形態として、半導体基板と、

前記半導体基板上に形成され、第1の開口部を有する第1の絶縁膜と、

前記第1の開口部直下の前記半導体基板内に形成された第1の溝と、

前記第1の溝内の前記半導体基板上に形成され、前記半導体基板の主成分を成す元素とは異なる元素をその一部に含み、禁制帯幅が前記半導体基板よりも小さい第1の半導体層と、

前記第1の溝内の前記第1の半導体層上に形成され、前記半導体基板の主成分を成す元素とは異なる元素をその一部に含み、禁制帯幅が前記半導体基板よりも小さい第1導電型の第2の半導体層と、

前記第1の開口領域内の前記第2の半導体層上に形成され、前記半導体基板の主成分を成す元素と同一元素をその一部に含み、禁制帯幅が前記第1の半導体層及び前記第2の半導体層よりも大きい第1導電側の第3の半導体層と、

前記第1の開口領域内の前記第3の半導体層上に形成された金属層とを備え、

10

20

30

40

50

前記第1の溝の上部の開口領域は前記第1の開口部を取り囲むように形成され、前記第1の溝の上部では前記第1の絶縁膜からなる庇が形成され、前記第1の溝の側壁は前記半導体基板の(111)面を含み、前記第1の溝の底部は前記半導体基板の(100)面を含み、

前記第1の半導体層は、前記第1の溝底部を構成する前記半導体基板の(100)面と、前記第1の溝側壁を構成する半導体基板の(111)面と、前記第1の絶縁膜から成る庇の下部表面と、前記第2の半導体層とに接しており、

前記第2の半導体層は、前記第1の半導体層と、前記第1の絶縁膜から成る庇の下部表面と、前記第3の半導体層とに接しており、

前記第1の半導体層と前記第2の半導体層の界面は、前記第1の半導体層と前記第1の絶縁膜との界面よりも下部に位置し、

前記第3の半導体層と前記金属層の界面は、前記第1の絶縁膜の下部表面と前記第1の絶縁膜の上部表面の間に位置し、

前記第2の半導体層は前記半導体基板から空間的に分離していることを特徴とする半導体装置とする。

又、半導体基板上に第1の絶縁膜を形成する工程と、

前記第1の絶縁膜に前記半導体基板が露出した第1の開口部を有する工程と、

前記第1の開口部直下の前記半導体基板内に第1の溝を形成する工程と、

前記第1の溝内の前記半導体基板上に、前記半導体基板の主成分を成す元素とは異なる元素をその一部に含み、禁制帯幅が前記半導体基板よりも小さい第1の半導体層を形成する工程と、

前記第1の溝内の前記第1の半導体層上に、前記半導体基板の主成分を成す元素とは異なる元素をその一部に含み、禁制帯幅が前記半導体基板よりも小さい第1導電型の第2の半導体層を形成する工程と、

前記第1の開口領域内の前記第2の半導体層上に、前記半導体基板の主成分を成す元素と同一元素をその一部に含み、禁制帯幅が前記第1の半導体層及び前記第2の半導体層よりも大きい第1導電側の第3の半導体層を形成する工程と、

前記第1の開口領域内の前記第3の半導体層上に金属層を形成する工程とを有し、

前記第1の溝を形成する工程は、前記第1の溝上部の開口領域が前記第1の開口部よりも広くなるよう、水平方向にも前記半導体基板のエッティングを施すことで前記第1の溝上部に前記第1の絶縁膜の庇を形成すると共に、前記第1の溝の底部が前記半導体基板の(100)面を有し、前記第1の溝の側壁が前記半導体基板の(111)面を有するように溝形成条件を調整する工程を含み、

前記第1の半導体層を形成する工程は、前記第1の半導体層が、前記第1の溝底部を構成する前記半導体基板の(100)面と、前記第1の溝側壁を構成する前記半導体基板の(111)面と、前記第1の絶縁膜から成る庇の下部表面とに接すると共に、前記第1の半導体層と前記第2の半導体層の界面が、前記第1の半導体層と前記第1の絶縁膜の界面よりも下部に位置するように前記第1の半導体層の形成条件を調整する工程を含み、

前記第2の半導体層を形成する工程は、前記第2の半導体層が前記第1の半導体層と、前記第1の絶縁膜の庇の下部表面とに接するように前記第2の半導体層の形成条件を調整する工程を含み、

前記第3の半導体層を形成する工程は、前記第3の半導体層と前記金属層の界面が前記第1の絶縁膜の下部表面と前記第1の絶縁膜の上部表面との間に位置するように前記第3の半導体層の形成条件を調整する工程を含むことを特徴とする半導体装置の製造方法とする。

#### 【発明の効果】

#### 【0024】

本発明によれば、素子の小型化・高性能化が可能な受光素子を有する半導体装置及びその製造工程数の低減が可能な製造方法を提供することができる。

#### 【図面の簡単な説明】

10

20

30

40

50

## 【0025】

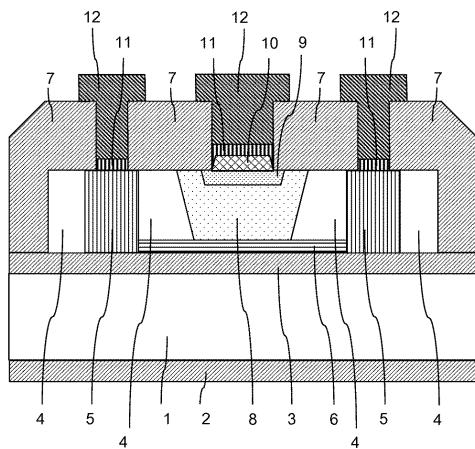

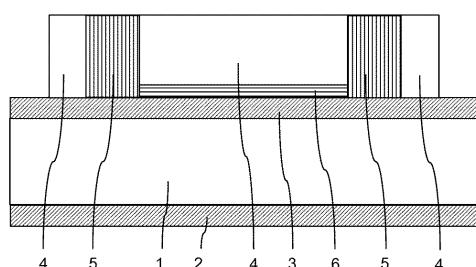

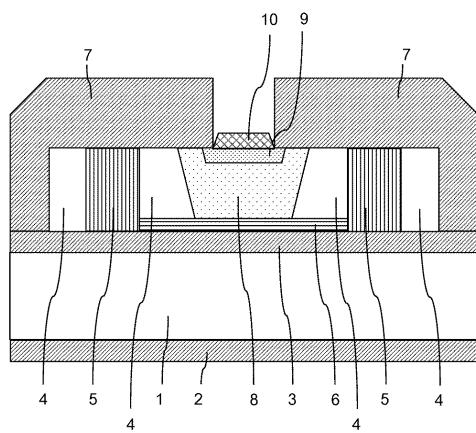

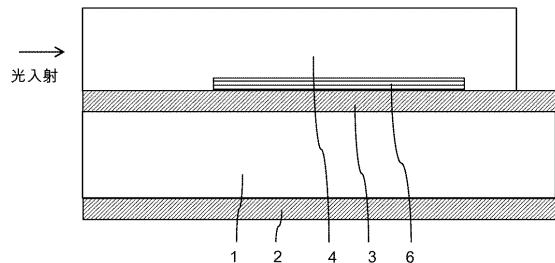

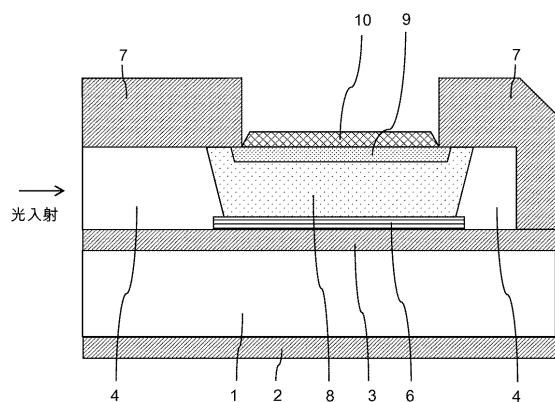

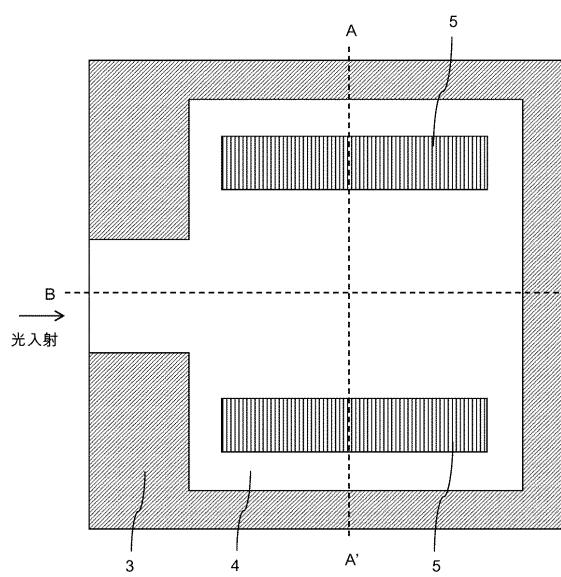

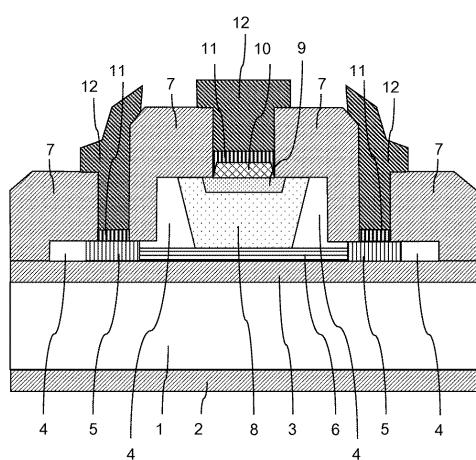

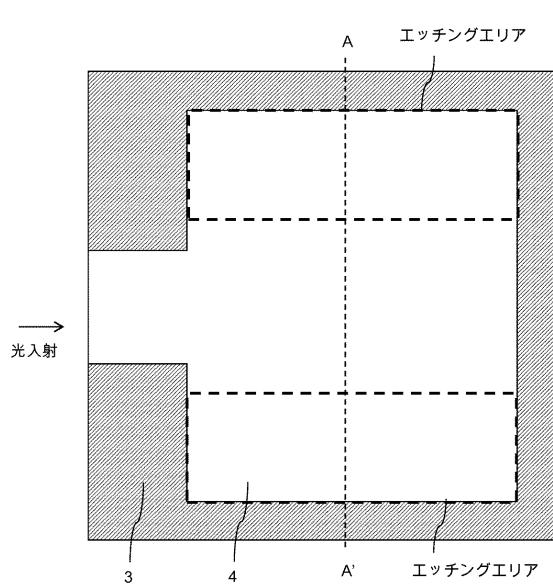

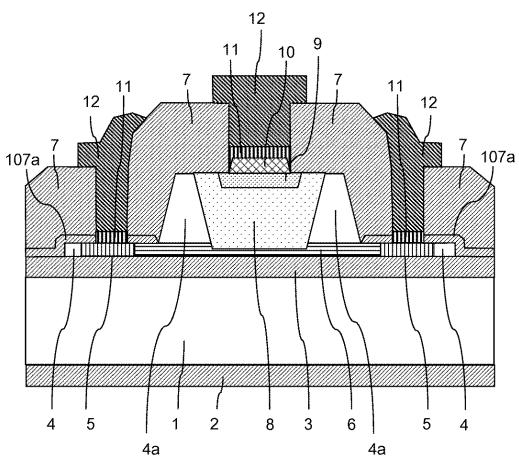

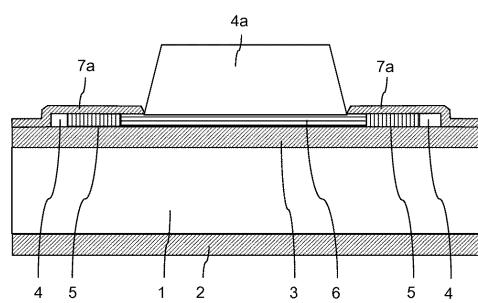

【図1】本発明の第1の実施例に係る半導体装置(受光素子)のAA'線における断面図である。

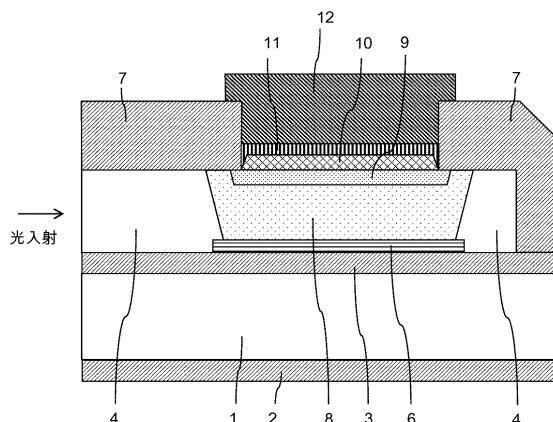

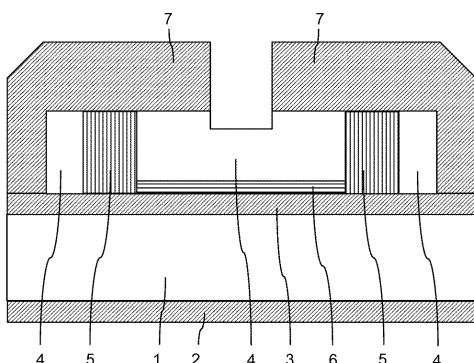

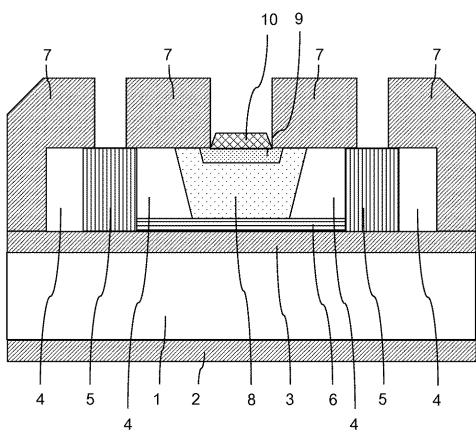

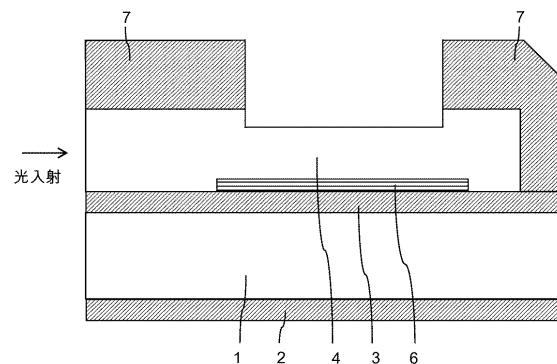

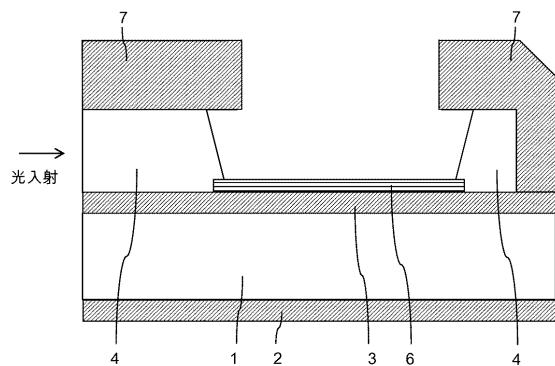

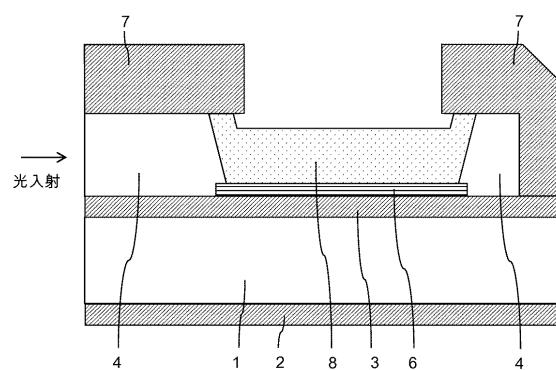

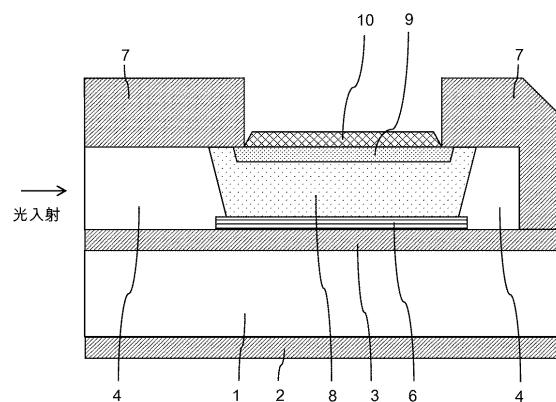

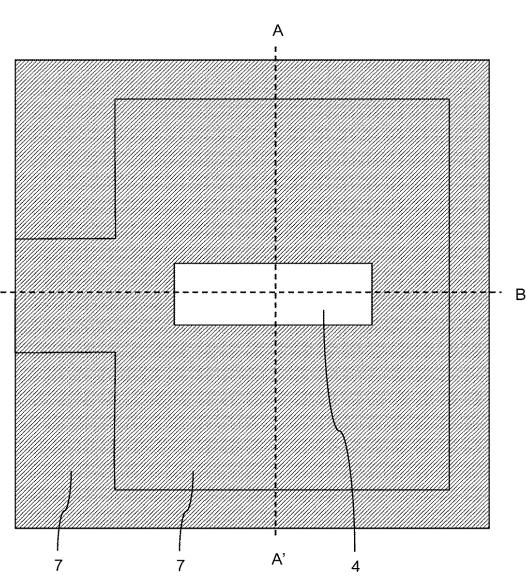

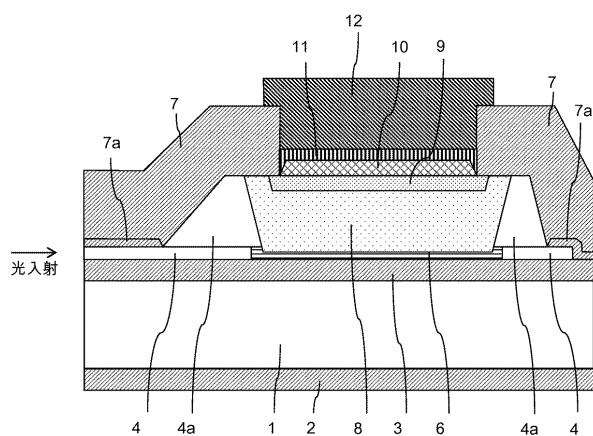

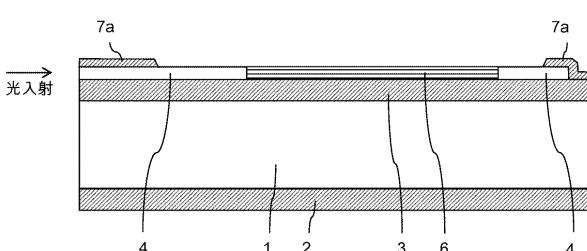

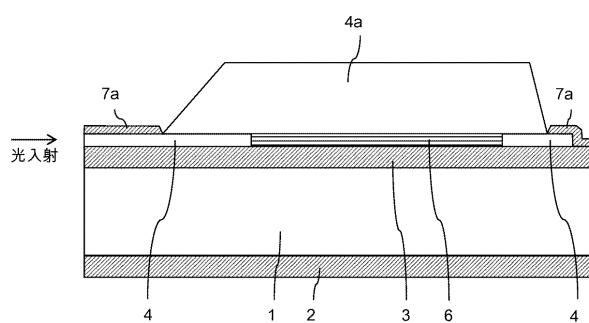

【図2】本発明の第1の実施例に係る半導体装置(受光素子)のBB'線における断面図である。

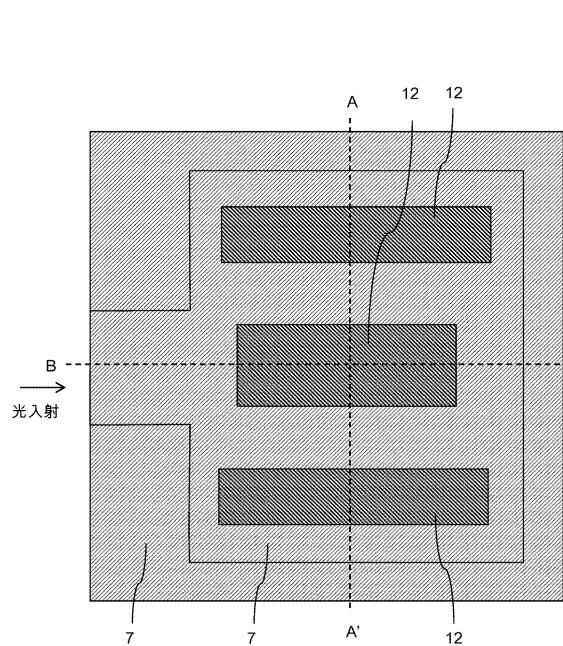

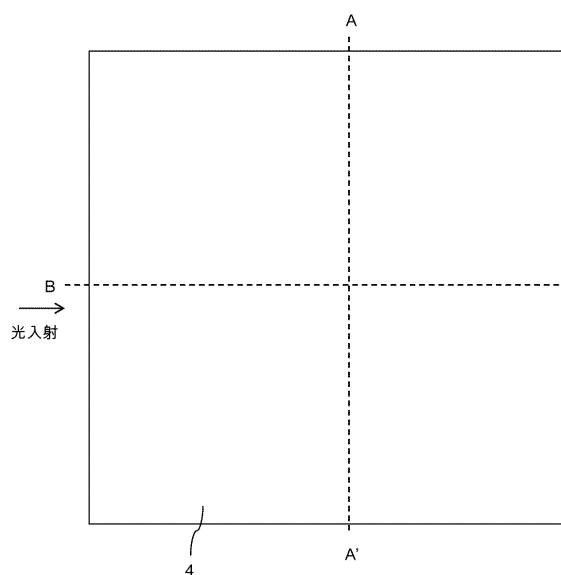

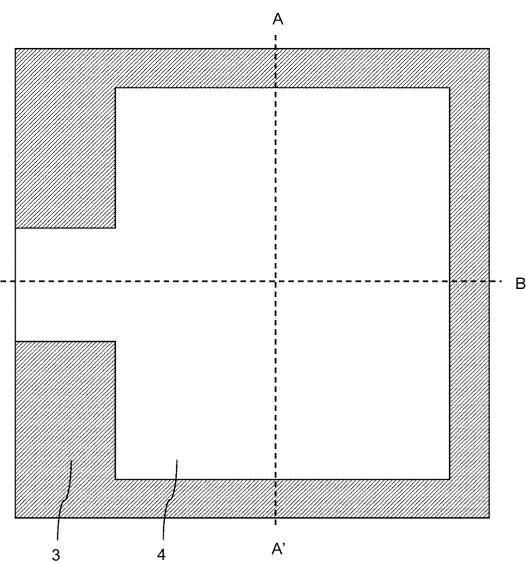

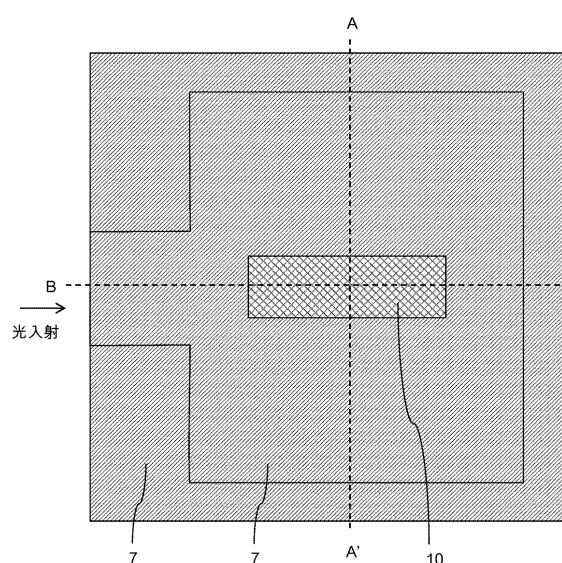

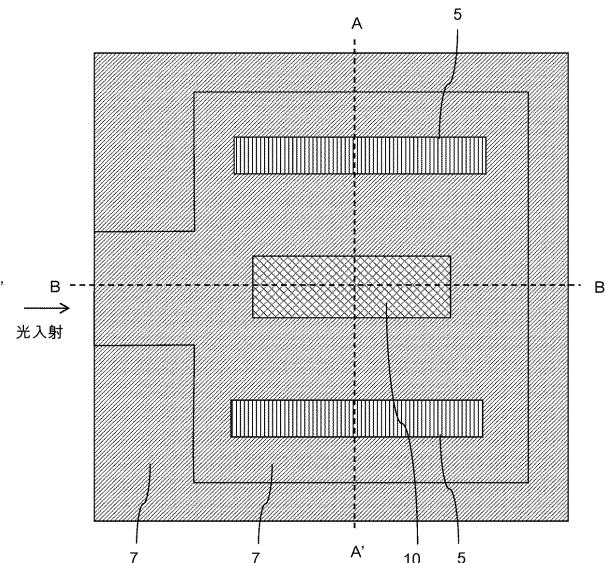

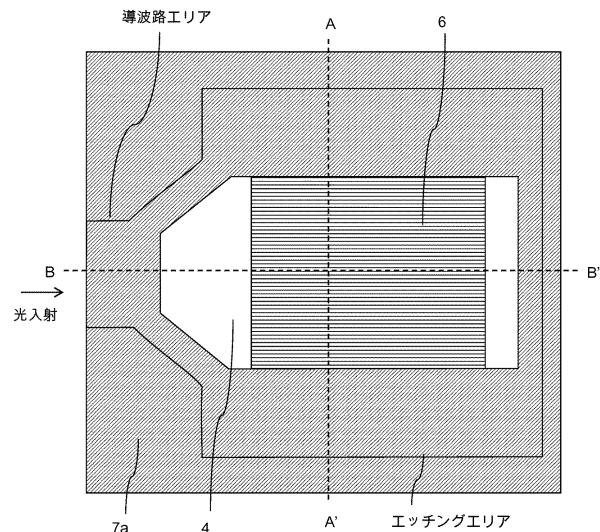

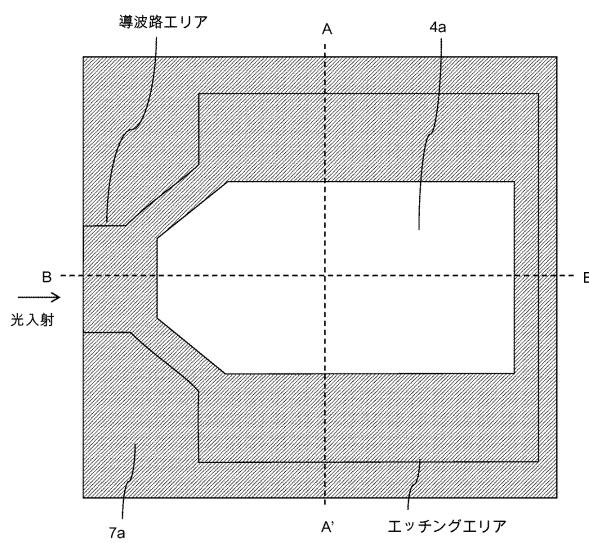

【図3】本発明の第1の実施例に係る半導体装置(受光素子)の平面図である。

【図4】従来の受光素子の一例を示し、光の入射方向に垂直な面を含む断面図(AA'線対応)である。

【図5A】従来の受光素子の他の例を示し、光の入射方向に平行な面を含む断面図(BB'線対応)である。

【図5B】図5Aに示す受光素子において、光の入射方向に垂直な面を含む断面図(AA'線対応)である。

【図6】従来の受光素子の他の例を示し、光の入射方向に垂直な面を含む断面図(AA'線対応)である。

【図7】図6に示す受光素子の課題を説明するための図で、埋め込み成長を行ったGeの形状を示す断面図である。

【図8】図6に示す受光素子において、n型シリコン層126を不純物を添加したエピタキシャル成長により成膜した場合を示す断面図である。

【図9】図6に示す受光素子において、n型ゲルマニウム層125とn型シリコン層126を、不純物を添加したエピタキシャル成長により成膜した場合を示す断面図である。

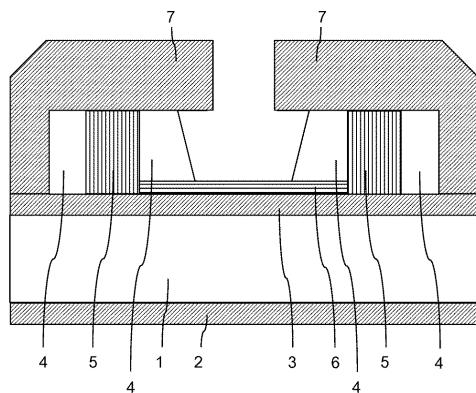

【図10A】第1の実施例に係る半導体装置の製造工程を示すAA'線における断面図である。

【図10B】第1の実施例に係る半導体装置の製造工程を示すAA'線における断面図である。

【図10C】第1の実施例に係る半導体装置の製造工程を示すAA'線における断面図である。

【図10D】第1の実施例に係る半導体装置の製造工程を示すAA'線における断面図である。

【図10E】第1の実施例に係る半導体装置の製造工程を示すAA'線における断面図である。

【図10F】第1の実施例に係る半導体装置の製造工程を示すAA'線における断面図である。

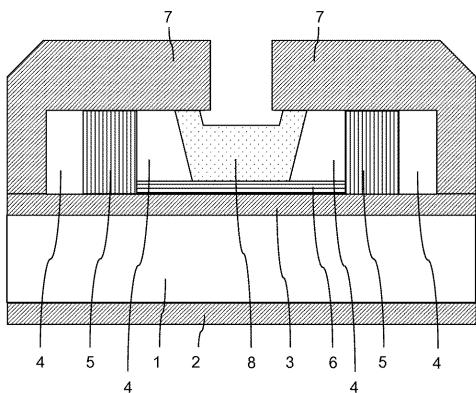

【図10G】第1の実施例に係る半導体装置の製造工程を示すAA'線における断面図である。

【図10H】第1の実施例に係る半導体装置の製造工程を示すAA'線における断面図である。

【図11A】第1の実施例に係る半導体装置の製造工程を示すBB'線における断面図である。

【図11B】第1の実施例に係る半導体装置の製造工程を示すBB'線における断面図である。

【図11C】第1の実施例に係る半導体装置の製造工程を示すBB'線における断面図である。

【図11D】第1の実施例に係る半導体装置の製造工程を示すBB'線における断面図である。

【図11E】第1の実施例に係る半導体装置の製造工程を示すBB'線における断面図である。

【図11F】第1の実施例に係る半導体装置の製造工程を示すBB'線における断面図である。

【図11G】第1の実施例に係る半導体装置の製造工程を示すBB'線における断面図である。

10

20

30

40

50

【図11H】第1の実施例に係る半導体装置の製造工程を示すB B'線における断面図である。

【図12A】第1の実施例に係る半導体装置の製造工程を示す平面図である。

【図12B】第1の実施例に係る半導体装置の製造工程を示す平面図である。

【図12C】第1の実施例に係る半導体装置の製造工程を示す平面図である。

【図12D】第1の実施例に係る半導体装置の製造工程を示す平面図である。

【図12E】第1の実施例に係る半導体装置の製造工程を示す平面図である。

【図12F】第1の実施例に係る半導体装置の製造工程を示す平面図である。

【図12G】第1の実施例に係る半導体装置の製造工程を示す平面図である。

【図12H】第1の実施例に係る半導体装置の製造工程を示す平面図である。

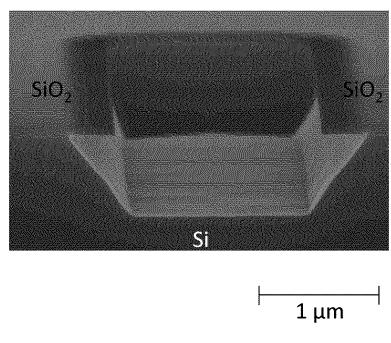

10

【図13】本発明の第1の実施例に係る半導体装置の製造工程において、Si基板に溝を形成したときの断面構造(図10E対応)を含む斜め上方から見た走査型電子顕微鏡(SEM)像である。

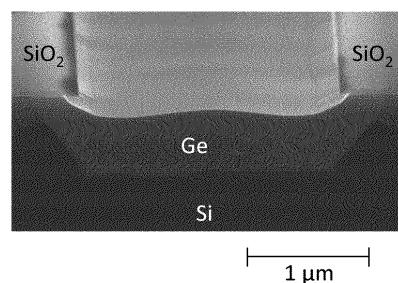

【図14】本発明の第1の実施例に係る半導体装置の製造工程において、Si基板に形成した溝内にGe光吸收層8を埋め込み成長したときの断面構造(図10F対応)を含む斜め上方から見た走査型電子顕微鏡(SEM)像である。

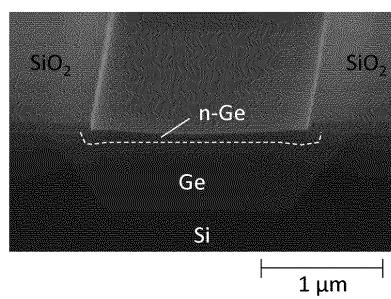

【図15】本発明の第1の実施例に係る半導体装置の製造工程において、Si基板に形成した溝内にGe光吸收層8とn型Ge電極層9を埋め込み成長したときの断面構造(図10Gにおいてn型SiGe保護層10形成前)を含む斜め上方から見た走査型電子顕微鏡(SEM)像である。

20

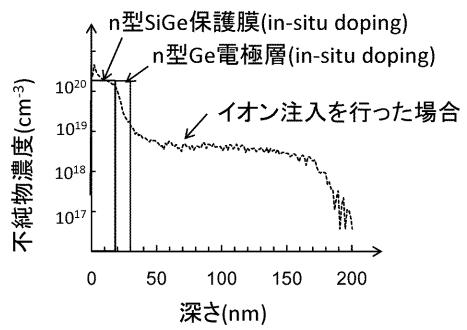

【図16】本発明の第1の実施例に係る半導体装置の製造工程において、n型Ge電極層9とn型SiGe保護層10とを、不純物を添加したエピタキシャル成長により形成した場合と、不純物を添加せずエピタキシャル成長後にイオン注入を行って形成した場合との不純物分布の違いを説明するためのグラフである。

【図17】本発明の第2の実施例に係る半導体装置のAA'線における断面図である。

【図18】第2の実施例に係る半導体装置の製造工程の一部を示すAA'線における断面図である。

【図19】第2の実施例に係る半導体装置の製造工程の一部を示す平面図である。

【図20】本発明の第3の実施例に係る半導体装置のAA'線における断面図である。

【図21】本発明の第3の実施例に係る半導体装置のBB'線における断面図である。

30

【図22A】第3の実施例に係る半導体装置の製造工程の一部を示すAA'線における断面図である。

【図22B】第3の実施例に係る半導体装置の製造工程の一部を示すAA'線における断面図である。

【図23A】第3の実施例に係る半導体装置の製造工程の一部を示すBB'線における断面図である。

【図23B】第3の実施例に係る半導体装置の製造工程の一部を示すBB'線における断面図である。

【図24A】第3の実施例に係る半導体装置の製造工程の一部を示す平面図である。

【図24B】第3の実施例に係る半導体装置の製造工程の一部を示す平面図である。

40

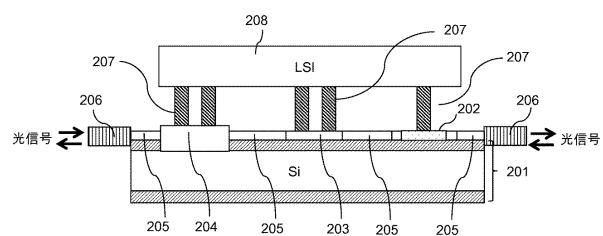

【図25】本発明の第5の実施例に係る半導体装置を示す断面概略図である。

【発明を実施するための形態】

【0026】

以下、本発明の実施例を図面に基づいて詳細に説明する。なお、実施例を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。また、本実施例で紹介する方法以外にも、材料や製造工程の組合せを変える等、多くの変更が可能である事は言うまでもない。

【0027】

以下に具体的な実施例について述べる。図面記載された図は、必ずしも正確に縮尺を合せているわけではなく、論理が明確になるように重要な部分を強調して模式的に描画して

50

ある。

【実施例 1】

【0028】

本発明に関わる半導体装置及びその製造方法の第 1 の実施例として、製造工程数の大幅な削減と、より一層の小型化が可能な Butt-Joint 型 Ge 受光素子及びその製造方法について説明する。

【0029】

図 1 ~ 図 3 は本発明の第 1 の実施例に係る半導体受光装置の断面構造及び平面構造である。図 1 は Si 導波路からの光の入射方向に垂直な断面であり、図 2 は Si 導波路からの光の入射方向を含む断面であり、図 3 は平面図である。図 1 と図 2 は、それぞれ図 3 の A 10 A' 線と B B' 線で切断した場合の断面構造を示している。

【0030】

図 1 ~ 図 3 における符号 1 は Si 基板であり、Si 基板 1 上には約 1 ~ 3  $\mu\text{m}$  の膜厚を有する埋め込み  $\text{SiO}_2$  層 3 が形成されている。Si 基板 1 の裏面にも上記埋め込み  $\text{SiO}_2$  層 3 と同程度の膜厚を有する  $\text{SiO}_2$  層 2 が堆積されていて埋め込み  $\text{SiO}_2$  層 3 が Si 基板 1 に与える圧縮応力を相殺する役割を担っている。埋め込み  $\text{SiO}_2$  層 3 上には Si 層 4 が形成され、上記 Si 層 4 は光導波路と受光素子形成領域の形状に加工されており、受光素子形成領域内の Si 層 4 には低不純物濃度の p 型 Si 層 6 と高不純物濃度の p 型 Si 電極 5 が形成されている。更に Ge 光吸收層 8 と n 型 Ge 電極層 9 が形成されている。上記 Ge 光吸收層 8 は、底部で低濃度 p 型 Si 層 6 と接しており、上記低濃度 p 型 Si 層 6 と Ge 光吸收層 8 、及び n 型 Ge 電極層 9 は p i n 型のダイオード構造を成している。上記 Si 層上にはパターニングされた  $\text{SiO}_2$  層 7 が形成されており、 $\text{SiO}_2$  層 7 に形成された開口部内には n 型 Ge 電極層 9 上に n 型 SiGe 保護膜 10 が形成され、上記開口部内において窒化チタン (TiN) からなる金属層 11 とオーミック接合を形成している。TiN 層 11 とアルミニウム (Al) 12 の積層構造は上記 n 型 SiGe 保護膜 10 上と高濃度 p 型 Si 領域 5 上に形成され、金属電極を成している。

【0031】

本実施例の第一の特徴は、前記  $\text{SiO}_2$  層 7 に形成された開口部に対して、Ge 光吸收層 8 と n 型 Ge 電極層 9 、更に n 型 SiGe 保護膜 10 と金属層 11 が自己整合して形成している点にある。n 型 SiGe 保護膜 10 と金属層 11 の基板に水平方向の幅は上記開口部の幅と一致しており、Ge 光吸收層 8 の幅は上記開口部幅に対して、 $\text{SiO}_2$  層 7 からなる庇の長さだけ広い。後述するように、上記庇の長さは Ge 光吸收層 8 の高さに応じて制御が可能であり、金属電極 11 の幅に対する Ge 光吸收層 8 の幅の拡がりを小さくすることができる。イオン注入及び電極形成のパターニングを必要とする従来技術では、パターニング 2 回分の合わせずれを見込み、金属電極幅に対する十分なマージンを取って Ge 光吸收層幅を設計していた為、本実施例は従来技術に比べ、素子サイズの一層の小型化を可能にする。

【0032】

本実施例の二番目の特徴は、上記溝内に形成した n 型 Ge 電極層 9 にある。上記 n 型 Ge 電極層 9 を  $\text{SiO}_2$  層 7 より下部の溝内に形成し、且つ上記 n 型 Ge 電極層 9 の表面領域が  $\text{SiO}_2$  層 7 で囲まれた開口領域を内包する構造とすることで、n 型 SiGe 保護膜 10 を高抵抗 Ge 光吸收層 8 と分離することができる。これにより、n 型 SiGe 保護膜 10 内の欠陥を空乏層から乖離することができ、低暗電流性を実現出来る。また、n 型 Ge 電極層 9 は、不純物の添加をエピタキシャル成長時に用いる為、不純物の高濃度化と n 型 Ge 電極層 9 の薄膜化が可能である。これにより、イオン注入法で n 型領域を形成する場合に比べて、Ge 光吸收層 8 中で n 型領域が占める割合を低減することが出来、受光効率が向上する。従って、上記 n 型 Ge 電極層 9 を溝内に埋め込むことにより、低暗電流性と受光効率の向上を実現出来る。

【0033】

三番目の特徴として、製造工程数の大幅な削減が挙げられる。後述するように、本実施

10

20

30

40

50

例におけるButt-joint型Ge受光素子は、Ge光吸收層8と、不純物が添加されたn型Ge電極層9とn型SiGe保護膜10を同一装置内で連続して成長することが出来、且つ上記n型電極層9をSi光導波路4に形成した溝を埋め込むように成長することを特徴としている。この為、従来のButt-joint型Ge受光素子の製造工程に比べて、Ge表面の平坦化工程とイオン注入工程、さらにイオン注入領域と電極形成領域のパターニング工程を省略することが出来、製造工程の大幅な削減が可能となる。

#### 【0034】

以上3つの特徴により、本実施例におけるButt-joint型Ge受光素子は、Butt-joint型受光素子の最大の特徴である小型性能をより追及することが出来、更に従来技術で課題となっていた製造工程数の増大を大幅に抑制することが出来る。これ 10 に加え、低暗電流性と受光効率の向上も可能となる。

#### 【0035】

次に、図10A～図10H、図11A～図11H、図12A～図12Hを用いて、本実施例における半導体装置の具体的な製造方法について、詳細に説明する。尚、図10A～図10Hは光の入射方向に対して垂直な断面の構造であり、図11A～図11Hは光の入射方向に対して平行な方向の断面構造を示し、図12A～図12Hは平面図である。図12A～図12Hに示したAA'線及びBB'線で断面を見た図がそれぞれ図10A～図10H、図11A～図11Hに対応する。

#### 【0036】

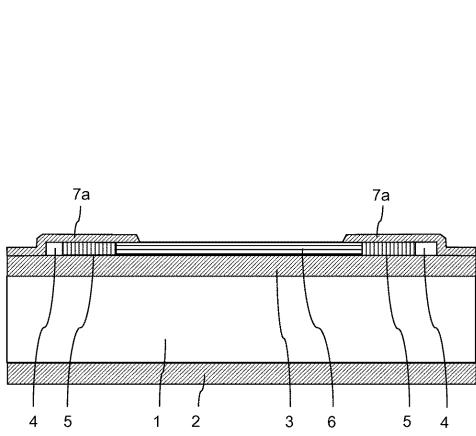

本実施例では、基板にSOI(Silicon on Insulator)基板を用いた。図10A、図1 20 1A、図12Aは受光素子の作製前におけるSOI基板である。Si基板1の表面上及び裏面に約1～3μmの膜厚を有するそれぞれ埋め込みSiO<sub>2</sub>層3及び圧縮応力を相殺する為の裏面SiO<sub>2</sub>層2が形成されており、埋め込みSiO<sub>2</sub>層3上にSOI層4が約200nm形成されている。ここで、SOI層4は光導波路にもなる為、SOI層4の膜厚及び埋め込みSiO<sub>2</sub>層3の膜厚は光を効率的に閉じ込められるように光の波長に応じて設計する。

#### 【0037】

次に、レジストを用いてSOI層4上にパターニングを行い、ウェットエッチングまたはドライエッチングによってSOI層4をエッチングし、光導波路状に加工し、図10B、図11B、図12Bの構造を得る。 30

#### 【0038】

次いで、レジストを用いたパターニングによりSOI層4上の一領域を開口し、上記領域のみに高濃度のp型不純物をイオン注入し、p型Si電極5を形成する。更に再度レジストを用いたパターニングを施す事により受光部下部領域に低濃度のp型不純物をイオン注入し、低濃度p型Si領域6を形成し、図10C、図11C、図12Cの構造を得る。ここで、p型不純物にはII族の元素を用いる。本実施例ではボロン(B)のイオン注入を行ったが、二フッ化ボロン(BF<sub>2</sub>)をイオン注入しても良い。上記高濃度p型Si電極5中へのイオン注入量は、上記電極5中の不純物濃度が $1 \times 10^{20} \text{ cm}^{-3}$ 程度とすれば低抵抗のコンタクトを得ることが可能となる。低濃度p型Si領域6中へのイオン注入条件は、下記に記すように設計する。上記p型Si領域6は、Si光導波路となるSOI層4に埋め込むGe光吸收層の底部と接合を形成する為、上記Ge光吸收層の底部付近で十分な不純物濃度を得られるようにイオン注入深さを設定する。本実施例では、上記Ge光吸收層底部での不純物濃度が $2 \times 10^{18} \text{ cm}^{-3}$ から $1 \times 10^{19} \text{ cm}^{-3}$ 程度となるようにイオン注入量を設定した。上記高濃度p型Si電極5と低濃度p型Si領域6へのイオン注入後は、1000程度の温度で約1秒～10秒程度のアニールを施すことで不純物の活性化を行う。 40

#### 【0039】

次いで、全面にSiO<sub>2</sub>層7を堆積する。SiO<sub>2</sub>層は熱CVD、またはプラズマCVD法により堆積しても良いし、熱酸化法にて形成しても良い。SiO<sub>2</sub>層の膜厚は10nm～1μmの範囲に設定すると良い。更にレジストを用いて受光部形成領域をパターニン 50

グし、ウェットエッティングまたはドライエッティングによってGe光吸收層形成領域を開口して図10D、図11D、図12Dの構造を得る。ここで、上記パターン形状は矩形とし、更に上記矩形形状を成す一辺が[110]方向に配向していると良い。また、SOI層4は数nm～20nm程度オーバーエッティングすると良い。ドライエッティングを行う場合はSiO<sub>2</sub>層7をエッティング除去後、エッティング時間を制御することでSOI層4のオーバーエッティングを行う。ウェットエッティングを用いる場合は、例えばバッファードフッ酸(NH<sub>4</sub>·HF·H<sub>2</sub>O)水溶液を用いたエッティングによりSiO<sub>2</sub>層7を除去し、レジストを除去した後にSOI層4表面を洗浄する工程でSOI層4をエッティングする。具体的には70程度のアンモニア水(NH<sub>4</sub>OH)と過酸化水素水(H<sub>2</sub>O<sub>2</sub>)の混合液にてSOI層4表面を洗浄することで、SOI層4が数nm～20nm程度エッティングされる。上記オーバーエッティングにより、SiO<sub>2</sub>層7の開口時には、露出したSOI層4は(110)面を含む側壁を有する。

#### 【0040】

次に、ウェットエッティングまたは気相エッティングを行い、開口部に露出したSOI層4をSiO<sub>2</sub>層7に対して選択的にエッティング除去して溝を形成し、図10E、図11E、図12Eの構造を得る。ウェットエッティングを行う場合は、アルカリ性の水溶液である、アンモニア水溶液(NH<sub>4</sub>OH)、水酸化カリウム水溶液(KOH)、ヒドラジン-水和物水溶液(H<sub>2</sub>NNH<sub>2</sub>H<sub>2</sub>O)、テトラメチルアンモニウムハイドロオキサイド(TMAH:(CH<sub>3</sub>)<sub>4</sub>NOH)等を用いると良い。本実施例では、2.38%の濃度を有するTMAH水溶液を用いた。上記アルカリ性のエッティング液を用いると、p型低抵抗Si層のエッティング速度を高抵抗Si層のエッティング速度に比べて遅くすることが出来る為、低濃度p型Si領域6をエッティングストップとしたエッティングが可能となる。本実施例では、低濃度p型Si領域6のエッティング速度をSOI層4のエッティング速度に対して少なくとも4分の1倍以下となり、溝の底部に低濃度p型Si領域6が露出した時点で精度良くエッティングを停止することが出来た。気相エッティングを用いる場合の例としては、CVD装置内にて約900の温度でHClガスを流入することで、SiをSiO<sub>2</sub>層に対して選択的にエッティング除去すると良い。エッティング時の圧力は約5Torr～760Torrの範囲で制御する。温度と圧力を制御することで、エッティング速度を再現性良く制御することが出来、低濃度p型Si領域6が露出した構造を得ることが出来る。但し、エッティング温度を高温で行う為、高濃度p型Si領域5または低濃度p型Si領域6における不純物の拡散が大きく、また、低濃度p型Si領域6が露出した後に不純物が外部に拡散し、上記p型Si領域6の不純物濃度が低下する懸念があり、より低い温度でエッティングを行う手法があれば、その手法を用いると良い。上記ウェットエッティングまたは気相エッティングは強い異方性を示す為、いずれの手法を用いた場合でもSi溝の側壁には(111)面が出現する。また、エッティング前のSOI層4に(110)面を含む側壁を形成したことにより、上記ウェットエッティングまたは気相エッティング時に[110]方向へのエッティングが促進され、SOI層4に溝を形成した際は溝上部にSiO<sub>2</sub>層7から成る庇が形成される。上記庇の水平方向の長さは、SiO<sub>2</sub>層7を開口する際のオーバーエッティング量と、形成する溝の深さによって制御することが出来る。本実施例では、上記庇の長さを溝の深さに対して10分の1倍から1倍の範囲で制御出来ることを確認した。図13に上記条件で溝を形成したSi基板断面の走査型電子顕微鏡(Scanning Electron Microscopy:SEM)像を示す。SiO<sub>2</sub>層7から成る庇を有し、約600nmの深さを持つ溝の形成が確認された。この場合の庇の水平方向の長さは約300nmであった。

#### 【0041】

次に、CVD装置を用い、Ge光吸收層8をSiO<sub>2</sub>層7に対して選択的に溝内のSOI層4上に成長する。庇の下部表面が一部埋まるまでGe層8を成膜し、表面に窪みを残した状態で成長を中断し、図10F、図11F、図12Fの構造を得る。詳細な成長条件を下記に示す。まず、露出したSOI層4の表面をフッ化水素酸(HF)水溶液によって洗浄し、Si表面の自然酸化膜及びSiと結合したOH基を除去し、Si表面のダングリングボンドを水素終端させる。次にCVD装置にてGeのエピタキシャル成長を行う。エ

10

20

30

40

50

ピタキシャル成長前には成膜装置にて 800 ~ 900 のアニールを水素雰囲気下で行い、装置導入までの間に Si 表面に形成された自然酸化膜を除去する。次いで、下記に示す手順により Ge を上記 SOI 層 4 上のみに選択的に成膜する。Ge の原料ガスにはモノゲルマン (GeH<sub>4</sub>) を用い、成長時の圧力は 5 Torr ~ 80 Torr に設定した。まず、Ge を 350 程度の低温で約 50 nm エピタキシャル成長し、次いで 550 ~ 700 に温度を上昇させた後、庇の下部表面が一部埋まるまで Ge 層 8 を成膜する。低温で成膜した Ge 層は結晶に不完全性を有している為、歪緩和の際に発生する欠陥は上記低温成膜層内に優先的に発生し、上部の高温成長層の結晶性は良好に保たれる。Ge 層 8 の成膜後には 800 ~ 900 程度の熱処理を 1 分 ~ 10 分行うことで Ge 層 8 内に存在する欠陥を修復し、結晶性を回復させる。上記成膜条件下では (111) 面における Ge の成長速度は (100) 表面の成長速度に比べて遅い為、Ge は SOI 層 4 に形成された溝を埋めるように成長する。この際、SiO<sub>2</sub> 層 7 から成る庇が存在する為、上記溝の側壁から成長した Ge は庇の下部表面で成長が止められ、溝の周辺部において凸形状が出現することは無い。図 14 に上記条件で溝を一部埋め込んだ Ge 光吸收層 8 の成長後の断面 SEM 像を示す。溝の深さ 600 nm に対し、SiO<sub>2</sub> 層の庇は 300 nm であり、そのうち 240 nm の長さに亘り、庇の下部表面が Ge 光吸收層で覆われている形状が得られた。また、上記 SEM 像の Ge 光吸收層上部の窪みの深さは約 150 nm であったが、成長時間を調整することで窪みの深さを 20 nm ~ 150 nm の範囲で精度良く制御出来ることを確認した。本実施例では、上記窪みの深さを 20 nm ~ 100 nm の範囲に設定すると好適である。

#### 【0042】

Ge 光吸收層 8 の成長後、そのまま同一装置内で連続して n 型 Ge 電極層 9、及び n 型 SiGe 保護膜 10 を選択成長し、図 10G、図 11G、図 12G の構造を得る。n 型 Ge 電極層 9 の成長条件は、成長圧力 5 ~ 80 Torr、成長温度 550 ~ 700 の範囲内で行った。n 型不純物を添加する為のドーピングガスとしては、水素またはヘリウムで希釈されたホスフィン (PH<sub>3</sub>) を用いた。上記条件下で成長を行うことにより、n 型不純物である磷 (P) を  $1 \times 10^{19} \text{ cm}^{-3}$  ~  $1 \times 10^{20} \text{ cm}^{-3}$  の濃度範囲で n 型 Ge 電極層 9 中にドーピングすることが出来た。尚、n 型不純物にはヒ素 (As) を用いても良い。この場合、ドーピングガスにはアルシン (AsH<sub>3</sub>) を用いると良い。n 型 Ge 電極層 9 は上部表面が SiO<sub>2</sub> 層 7 の庇の下部表面と一致するまで成長し、SOI 層 4 の溝を埋め込むようにする。この為、n 型 Ge 電極層 9 の膜厚は、Ge 光吸收層 8 の表面上に形成した窪みの深さである、20 nm ~ 100 nm に設定する。図 15 に n 型 Ge 電極層 9 を成膜した後の断面 SEM 像を示す。上記溝は Ge 光吸收層 8 と n 型 Ge 電極層 9 によってほぼ平坦に埋め込まれることを確認した。発明者らは、上記成長条件を用い、且つ上記庇の水平方向の長さを溝深さの 10 分の 1 倍以上且つ 1 倍以下として、上記溝を Ge 光吸收層 8 と n 型 Ge 電極層 9 でほぼ平坦に埋め込むことが出来ることを確認した。n 型 SiGe 保護膜 10 は SiO<sub>2</sub> 層 7 で囲まれた開口部内に選択的に形成し、その表面高さは SiO<sub>2</sub> 層 7 の上部表面と下部表面の間に位置するように調整した。n 型 SiGe 保護膜 10 は、n 型 Ge 電極層 9 表面が酸化されて水溶性の酸化ゲルマニウム (GeO<sub>2</sub>) になるのを防ぐ目的で n 型 Ge 電極層 9 上に形成している。また、n 型 Ge はフェルミ・レベル・ピニング効果により金属とのコンタクト抵抗が一般的に高い為、n 型 SiGe 保護膜 10 を用いることにより、金属との低コンタクト抵抗を実現する目的も有している。この為、上記 SiGe 保護膜の Ge 組成は 10 % ~ 20 % 程度の低い値で調整することが望ましい。n 型 SiGe 保護膜 10 の選択成長条件は、成長圧力 5 ~ 20 Torr、成長温度 550 ~ 700 の範囲内で行った。n 型 SiGe 保護膜 10 の原料ガスには GeH<sub>4</sub> とモノシラン (SiH<sub>4</sub>) を用いたが、Si の原料ガスとして、ジシラン (Si<sub>2</sub>H<sub>6</sub>) やジクロロシラン (SiH<sub>2</sub>Cl<sub>2</sub>) を用いても良い。ドーピングガスには、水素またはヘリウムで希釈された PH<sub>3</sub> を用い、不純物濃度は n 型 Ge 電極層 9 と同程度の  $1 \times 10^{19} \text{ cm}^{-3}$  ~  $1 \times 10^{20} \text{ cm}^{-3}$  の濃度範囲に設定した。尚、ドーピングガスは AsH<sub>3</sub> を用いて As をドーピングしても良い。n 型 SiGe 保護膜の膜厚は、10 ~

10

20

30

40

50

50 nmの範囲に設定した。ここで、n型SiGe保護膜10の代わりにn型Si保護膜を用いても、同様の効果を得ることが出来る。この場合、Si保護膜の成長は、SiH<sub>4</sub>にHC1ガスを添加して選択成長を実現するか、Siを全面に成長した後にHC1ガスにてSiO<sub>2</sub>層7上に堆積したpoly-Si層のみをエッティング除去するか、良好な選択性を持つSiH<sub>2</sub>Cl<sub>2</sub>を原料ガスとして選択成長を行う、等の手法により行う。

#### 【0043】

上記埋め込み成長工程に続いては、高濃度p型Si領域5上にレジストを用いたパターニングを行い上記領域上のSiO<sub>2</sub>層7をドライエッティングまたはウェットエッティングによりエッティング除去してp型Si領域5を露出させ、図10G、図11G、図12Gの構造を得る。

10

#### 【0044】

最後にTiN層11とAl層12の積層金属膜を堆積し、レジストを用いてパターニングを施した後にウェットエッティングまたはドライエッティングを行い、電極を形成して図1、図2、図3に示す受光素子構造を得る。

#### 【0045】

上述したButt-join型Ge受光素子の製造方法によれば、Ge光吸收層8とn型Ge電極層9とn型SiGe保護膜10を同一装置内で連続して成長しており、且つ上記Ge光吸收層8とn型Ge電極層9がSOI層4に形成した溝を埋め込むように成長している為、従来のButt-join型Ge受光素子の製造工程に比べて、Ge表面の平坦化工程とイオン注入工程、さらにイオン注入領域と電極形成領域のパターニング工程を省略することが出来、製造工程の大幅な削減が可能となる。

20

#### 【0046】

また、n型Ge電極層9とn型SiGe保護膜10への不純物添加をエピタキシャル成長時に行っている為、イオン注入時に必要となる活性化アニールが不要となり、n型Ge電極層9を薄くすることが出来る。この為、イオン注入を行った場合に比べてGe光吸收層8内に占めるn型領域の割合を大きく低減出来る。図16に、イオン注入を行った場合と、n型Ge電極層9とn型SiGe保護膜10への不純物添加をエピタキシャル成長時に行った場合のn型不純物であるPの不純物分布を比較する。イオン注入を行った場合、イオン注入深さを可能な限り浅くしても、活性化アニールによって不純物の大きな拡がりが見えており、上記n型領域をエピタキシャル成長により形成したn型Ge電極層9とn型SiGe保護膜10に置き換えることで不純物拡がりを大きく低減出来ることが確認出来た。上述したように、本実施例によれば、Butt-Join型の受光素子において、製造工程数の大幅な削減と素子の更なる小型化を同時に実現出来る。

30

#### 【0047】

本実施例では、光吸收層にGeを用いたが、Siとの混晶であるシリコン・ゲルマニウム(SiGe)を用いても良い。光吸收層にはSiを結晶に多少含ませることで、SOI層4及びn型SiGe保護膜10との格子不整合量を軽減することが出来、結晶欠陥密度低減の観点で多少有利となる。この場合、光吸收層のGeの組成比は受光素子に入射する光の波長によって決定する。波長1550nmの光を利用する場合は、Ge組成を90~100%に設計し、波長1300nmの光を利用する場合は、Ge組成を70%~90%に設計すると長波長の光通信でも感度を保つことが出来、好適である。また、上述したように、n型SiGe保護膜10をn型Si保護膜に置き換えて、本実施例と同様の効果をもたらす事が出来る。

40

#### 【0048】

また、本実施例では絶縁膜としてSiO<sub>2</sub>膜を用いたが、他の絶縁膜を使用しても良い。

#### 【0049】

さらに、本実施例では、受光素子下層をp型、上層をn型としたが、受光素子下層をn型、上層をp型としてもなんら問題はない。

#### 【実施例2】

50

## 【0050】

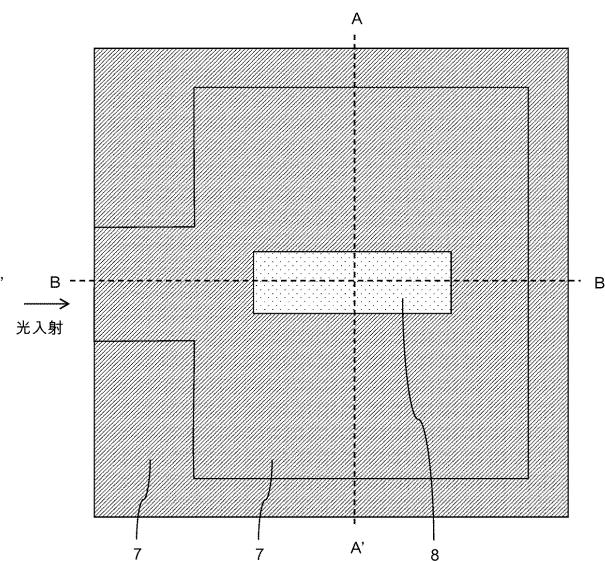

本発明の第2の実施例に係る半導体装置について図17～図19を用いて説明する。なお、実施例1に記載され本実施例に未記載の事項は特段の事情がない限り本実施例にも適用することができる。図17はButt-Joint型Ge受光素子において光の入射方向に垂直方向の断面を示す図である。本実施例は、SOI層4のp型Si電極層5の領域をエッチングし、当該領域のSOI層4の高さを、光が伝播する部分及びGe光吸收層8を有する部分よりも低くすることを特徴としている。上記パターニングを施すことにより、光導波路から入射した光をGe光吸收層8の領域により強く閉じ込めることができ、p型Si電極層5の領域に光が拡がるのを抑制することが出来る。従って、受光効率を向上することが出来、Ge光吸收層8の領域を一層小型化することが可能で、低容量化に優位性を持つ。

10

## 【0051】

本実施例における受光素子の製造方法を、実施例1との相違点に特化して以下に説明する。

## 【0052】

図18と図19は、SOI層4に上記パターニングを行った後の断面と平面を示す図である。図18は光の入射方向に垂直方向の断面を示しており、図19のAA'線における断面図である。上記パターニングは、実施例1の図10B、図11B、図12Bで示したSi光導波路を規定するエッチング後に行い、p型Si電極を形成する領域を開口するようにパターニングを行う。レジストを用いたパターニングを行った後に、ドライエッチングまたはウェットエッチングによりSOI層4をエッチングする。ウェットエッチングを行う場合は、前述したようにアルカリ性水溶液をエッチング液としてエッチングを行う。エッチング後の当該領域のSOI層4の高さはSi光導波路部に比べて約半分になるように調整する。その後、p型不純物の高濃度イオン注入とp型不純物の低濃度イオン注入を行い、高濃度p型Si層5と低濃度p型Si層6を形成する。次いで、実施例1で示した手順に従いSiO<sub>2</sub>層7を堆積後に開口部を形成し、ウェットエッチングまたは気相エッチングを行ってSOI層4中に溝を形成する。その後、Ge光吸收層8、n型Ge電極層9、n型SiGe保護膜10の選択成長を連続して行い、金属電極を形成して図17に示す受光素子構造を得る。

20

## 【0053】

30

Ge光吸收層8、n型Ge電極層9、n型SiGe保護膜10の成長条件及びn型不純物のドーピング条件は実施例1と同一とする。

## 【0054】

実施例1と同様、Ge光吸收層8はSiGe層に変更可能であり、SiO<sub>2</sub>層7を他の絶縁膜に置き換えて良く、またp型領域とn型領域を入れ替えて本実施例と同様の効果を得ることが出来る。

## 【実施例3】

## 【0055】

本発明の第3の実施例について以下説明する。なお、実施例1に記載され本実施例に未記載の事項は特段の事情がない限り本実施例にも適用することができる。

40

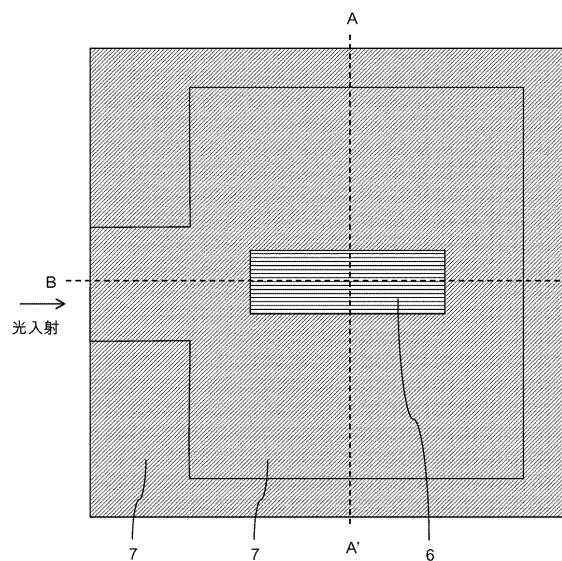

## 【0056】

本実施例では、Ge光吸收層8を形成する領域に、Siを選択的にエピタキシャル成長して光閉じ込め構造を形成するButt-Joint型Ge受光素子を開示する。以下に、本実施例におけるGe受光素子構造及びその製造方法を、実施例1との相違点に特化して説明する。

## 【0057】

図20と図21は、本実施例におけるGe受光素子の、それぞれ光の入射方向に対して垂直な方向と平行な方向の断面図である。本実施例では、SOI層から成るSi光導波路4上にSi層4aを選択成長し、上記Si層4a中にGe光吸收層8を埋め込むことでButt-Joint型受光素子を形成している。Si光導波路4から伝播した光は上記S

50

i選択成長層4aに伝播中心が移り、Si選択成長層4aを伝播した光がGe光吸收層8に高効率で入射する。Ge光吸收層8の厚さを自由に設計することが出来る為、Si光導波路4の厚さが薄い場合でも受光効率の低減を抑制し、またn型電極とp型電極の距離が短縮することによる電気容量の増大を避けることが出来る。なお、符号107aはSiO<sub>2</sub>層である。

#### 【0058】

図22A～図22B、図23A～図23B、図24A～図24Bを用いて、本実施例における半導体装置の具体的な製造方法について、詳細に説明する。ここで、図22A～図22Bは光の入射方向に対して垂直な断面の構造であり、図23A～図23Bは光の入射方向に対して平行な方向の断面構造を示し、図24A～図24Bは平面図である。図24A～図24Bに示したAA'線及びBB'線で断面を見た図がそれぞれ図22A～図22B、図23A～図23Bに対応する。

#### 【0059】

図22A、図23A、図24AはSiを選択成長する際にマスクとなるSiO<sub>2</sub>層7aを堆積し、選択成長用の開口を形成した後の断面図と平面図である。上記SiO<sub>2</sub>層7aの堆積は、実施例1で示した受光素子の製造方法において、高濃度p型Si領域5と低濃度p型Si領域6を形成した後に行うこととする。SiO<sub>2</sub>層7aは熱CVD、またはプラズマCVD法により堆積しても良いし、熱酸化法にて形成しても良い。SiO<sub>2</sub>層7aの膜厚は50nm～100nmの範囲に設定すると良い。Siの選択成長用の開口領域形成は、レジストを用いてパターニングを行った後、ドライエッチングまたはHF水溶液を用いたウェットエッチングによってSi光導波路4が露出するように開口する。ここで、開口部の形状は、図24Aに示すように、光の伝播方向に向かってテーパー状に拡がる形状を有すると良い。これは、後述するように、Si光導波路4から伝播した光を少ない損失でSi選択成長層に伝播させる際に有効となる。尚、図24Aに示したように、上記開口部のテーパー形状に合わせて下地となるSi光導波路4もテーパー形状に加工すると良い。

#### 【0060】

次いで、上記開口部内にSi層4aを選択成長して図22B、図23B、図24Bに示す構造を得る。Si層4aの成長は、成長圧力5～20Torr、成長温度600～800の条件下で、CVD装置にて行う。選択成長条件としては、SiH<sub>4</sub>にHClガスを添加して選択成長を実現するか、Siを全面に成長した後にHClガスにてSiO<sub>2</sub>層7a上に堆積したpoly-Si層のみをエッチング除去するか、良好な選択性を持つSiH<sub>2</sub>C<sub>1</sub>を原料ガスとして選択成長を行う、等の条件を用いる。選択成長したSiは、[110]方向では(111)面を含む側壁を持つが、光の伝播方向は、テーパー状に加工した開口部の形状の影響で(111)面より浅い角度を有するファセット面を持つ。角度が浅い程、光の伝播中心を低損失でSi選択成長層4aに移すことが出来る為、上記開口部のテーパー形状に起因する浅いファセット角は(111)面に比べて優位性を持つ。上記テーパー形状に起因する、基板に水平方向のSi選択成長層4aの幅の拡がりも、光を有効にSi選択成長層4aに閉じ込める際に重要となる。従って、光の伝播中心をSi選択成長層4aに低損失で移し、且つ基板に水平方向に光を有効に閉じ込める為に最適なテーパー形状を設計する。

#### 【0061】

上記Si選択成長層4aを形成した後、実施例1の図10D～図10H、図11D～図11H、図12D～図12Hに示した製造方法を経て、図20と図21に示した受光素子構造を得る。尚、Si選択成長層4aに溝を形成する際は、溝の底面をSOI層4の表面と一致させるか、或いはSOI層4を一部掘り込むようにエッチング時間を調整する。SOI層4を一部掘り込んで溝を形成した場合は、Ge光吸收層8の一部がSi光導波路と同一高さに存在する為、高効率化に有利である。一方、溝の底面をSOI層4の表面と一致させた場合は、低濃度p型Si層6の膜厚を減らす必要がない為、抵抗の増大を抑制することが出来る。

10

20

30

40

50

## 【0062】

尚、本実施例では Si 選択成長層 4 a を成膜する例を開示したが、上記選択成長層は Si Ge 層であっても良い。この場合、Ge の原料ガスには GeH<sub>4</sub> を用い、その他成長条件は Si 選択成長層 4 a と同等の条件を用いる。Ge 組成は約 10 ~ 20 % に設定する。上記選択成長層を Si Ge 層とすることで、Si 導波路 4 から光が入射した際、Si と Si Ge の屈折率差により、光はより高効率で Si Ge 選択成長層に伝播中心を移す事が可能である。また、Si 選択成長層 4 a の成膜時に p 型不純物である B を添加しても良い。上記 Si 選択成長層 4 a を p 型とすることで、Ge 光吸收層 8 で発生した正孔による電流が p 型 Si 領域 5 に流れる際の抵抗を低減することが可能になる。上記 p 型 Si 選択成長層 4 a を形成する際は、上記選択成長層 4 a で光が吸収されないよう、p 型不純物濃度は  $1 \times 10^{18} \text{ cm}^{-3} \sim 1 \times 10^{19} \text{ cm}^{-3}$  の範囲で設定する。 10

## 【0063】

Ge 光吸收層 8、n 型 Ge 電極層 9、n 型 Si Ge 保護膜 10 の成長条件及び n 型不純物のドーピング条件は実施例 1 と同一とする。

## 【0064】

また、実施例 1 と同様、Ge 光吸收層 8 は Si Ge 層に変更可能であり、SiO<sub>2</sub> 層 7 を他の絶縁膜に置き換えても良く、また p 型領域と n 型領域を入れ替えても本実施例と同様の効果を得ることが出来る。

## 【0065】

本実施例では、Ge 吸收層 8 を形成する開口パターンを SiO<sub>2</sub> 層 7 に形成する際、実施例 1 と同様、矩形パターンを用いることとするが、図 24 A に示したように光の伝播方向にテーパー形状を持たせても良い。この場合は Si 光導波路 4 を伝播した光が Si 層 4 a に伝播中心を移す際に効率的に光を Ge 光吸收層 8 に光を入射出来るという利点を持つ。 20

## 【実施例 4】

## 【0066】

本発明に係る半導体装置の第 4 の実施例は、実施例 1 から実施例 3 に示した Butt-Joint 型 Ge 受光素子において、n 型 Si Ge 保護膜 10 と金属層 11 の接合をショットキー接合とした受光素子を示す。 30

## 【0067】

本実施例では、実施例 1 から実施例 3 に示した Butt-Joint 型 Ge 受光素子の n 型 Ge 電極層 9 と n 型 Si Ge 保護膜 10 の n 型不純物濃度を低く設定する事が出来る為、n 型 Ge 電極層 9 中の自由電子による光の吸収を抑制する事が出来る。上記自由電子による光の吸収は電流には寄与しない為、受光効率の低下につながる。従って、本実施例では p i n 型受光素子に比べ、受光効率を向上することが可能である。本実施例において、n 型 Ge 電極層 9 と n 型 Si Ge 保護膜 10 の n 型不純物濃度は約  $1 \times 10^{18} \text{ cm}^{-3}$  から  $1 \times 10^{19} \text{ cm}^{-3}$  に設定した。n 型不純物は P または As とし、ドーピングガスはそれぞれ水素またはヘリウムで希釈された PH<sub>3</sub> または AsH<sub>3</sub> を使用するものとする。

## 【実施例 5】

## 【0068】

本実施例では、これまでの実施例で説明した Ge 受光素子を、Si を用いた光導波路及び光変調器、また化合物半導体を用いたレーザと共に Si 基板上に集積し、更に各素子の電極に LSI を接続して、LSI に搭載した回路により各光素子を駆動する、光・電子集積チップの例を説明する。 40

## 【0069】

図 25 に本実施例に係る半導体装置の概略図を示す。

SOI 基板 201 上に、実施例 1 ~ 実施例 4 に示したいずれかの Ge 受光素子 202 と、Si からなる光変調器 203 が形成され、SOI 基板の Si 支持基板上には化合物半導体レーザ 204 が搭載されており、それぞれが SOI 層からなる光導波路 205 で結合され 50

ている。上記光導波路 205 には光ファイバ 206 が結合しており、SOI 基板 201 外部との光信号の送受信が可能な構造を成している。また、上記 SOI 基板 201 上には、LSI チップ 208 が搭載されている。上記 LSI チップ 208 は Ge 受光素子 202 と光変調器 203、更に化合物半導体レーザ 204 上の金属電極 207 と接続されており、化合物半導体レーザ 204 と光変調器 203 を駆動するドライバ回路、及び Ge 受光素子 202 の信号を受ける增幅回路等が組み込まれている。

【0070】

本実施例は、成熟した微細化技術を有し、且つ汎用性に優れる Si の LSI を光の送受信が可能な Si 基板に集積することで、大容量の情報通信を可能にする光通信機器の小型化及び低価格化を実現可能である。また、情報量の増加とともに増大する消費電力が問題となっている、サーバ等の大容量の情報機器のボード間通信等に適用することにより、大幅な低消費電力化が可能となる。

10

【0071】

尚、図 25 で示した実施例はあくまで概略図であり、図 25 に示す素子間の結合、光ファイバとの結合等は、本実施例を適用するシステム等に応じて広範な自由度を以て適宜設計可能である。

【0072】

以上、本願発明を詳細に説明したが、以下に主な発明の形態を列挙する。

本発明に関わる半導体装置は、半導体基板と、前記半導体基板上に形成され、第 1 の開口部を有する第 1 の絶縁膜と、前記第 1 の開口部直下の前記半導体基板内に形成された第 1 の溝と、前記第 1 の溝内の前記半導体基板上に形成され、前記半導体基板の主成分を成す元素とは異なる元素をその一部に含み、禁制帯幅が前記半導体基板よりも小さい第 1 の半導体層と、前記第 1 の溝内の前記第 1 の半導体層上に形成され、前記半導体基板の主成分を成す元素とは異なる元素をその一部に含み、禁制帯幅が前記半導体基板よりも小さい第 1 導電型の第 2 の半導体層と、前記第 1 の開口領域内の前記第 2 の半導体層上に形成され、前記半導体基板の主成分を成す元素と同一元素をその一部に含み、禁制帯幅が前記第 1 の半導体層及び前記第 2 の半導体層よりも大きい第 1 導電側の第 3 の半導体層と、前記第 1 の開口領域内の前記第 3 の半導体層上に形成された金属層から成り、前記第 1 の溝上部の開口領域は前記第 1 の開口部を取り囲むように形成され、前記第 1 の溝上部では前記第 1 の絶縁膜からなる庇が形成され、前記第 1 の溝は(111)面を含む前記半導体基板の側壁を有していて、前記第 1 の半導体層は、前記第 1 の溝底部に露出した前記半導体基板の(100)面と、(111)面を含む前記半導体基板の側壁と、前記第 1 の絶縁膜から成る庇の下部表面と、前記第 2 の半導体層と接しており、前記第 2 の半導体層は、前記第 1 の半導体層と前記第 1 の絶縁膜から成る庇の下部表面と、前記第 3 の半導体層と接しており、前記第 1 の半導体層と前記第 2 の半導体層の界面は、前記第 1 の半導体層と前記第 1 の絶縁膜の界面よりも下部に位置し、前記第 3 の半導体層と前記金属層の界面は前記第 1 の絶縁膜の下部表面と前記第 1 の絶縁膜の上部表面の間に位置し、前記第 2 の半導体層は前記半導体基板から空間的に分離していることを特徴とすると良い。

20

【0073】

さらに、前記第 1 の絶縁膜から成る庇の水平方向の長さは、前記第 1 の溝の深さに対して 10 分の 1 倍以上且つ 1 倍以下であると尚良い。

30

【0074】

前記第 2 の半導体層と前記第 3 の半導体層中の不純物濃度は、深さ方向に対してほぼ一定であるとより好適である。

【0075】

また、前記第 1 の半導体層が受光機能を有すると良い。

【0076】

さらに、前記半導体基板は、前記第 1 の溝底部の界面において第 1 導電型を示し、前記半導体装置がダイオードとしての機能を有することを特徴とすると尚良い。

【0077】

40

50

前記半導体基板は、半導体支持基板と、前記半導体支持基板を覆う絶縁膜と、該絶縁膜上に位置し、導波路状にパターニングされた第1の光導波路から成ると一層好適である。

【0078】

また、前記半導体基板は、前記第1の光導波路上に、前記第1の光導波路を覆い、前記第1の光導波路の一部表面を露出する開口を有する絶縁膜と、露出した前記第1の光導波路上に前記半導体支持基板を構成する元素をその一部に含む第2の光導波路を有していても良い。

【0079】

前記第3の半導体層と前記金属層はオーミック接合界面を有すると良い。

【0080】

前記第3の半導体層と前記金属層はショットキー接合界面を有しても好適である。

10

【0081】

また、前記半導体支持基板と前記第1の光導波路はシリコンから成り、前記第2の光導波路と前記第3の半導体層はシリコンまたはシリコン・ゲルマニウムから成り、前記半導体犠牲層と前記第1の半導体層と前記第2の半導体層はゲルマニウムまたはシリコン・ゲルマニウムとし、前記第1の半導体層と前記第2の半導体層のゲルマニウム組成が、共に前記第2の光導波路と前記第3の半導体層のいずれのゲルマニウム組成よりも大きいことを特徴とすると良い。

【0082】

本発明に係る半導体装置の製造方法は、半導体基板上に第1の絶縁膜を形成する工程と、前記第1の絶縁膜に前記半導体基板が露出した第1の開口部を有する工程と、前記第1の開口部直下の前記半導体基板内に第1の溝を形成する工程と、前記第1の溝内の前記半導体基板上に、前記半導体基板の主成分を成す元素とは異なる元素をその一部に含み、禁制帯幅が前記半導体基板よりも小さい第1の半導体層を形成する工程と、前記第1の溝内の前記第1の半導体層上に、前記半導体基板の主成分を成す元素とは異なる元素をその一部に含み、禁制帯幅が前記半導体基板よりも小さい第1導電型の第2の半導体層を形成する工程と、前記第1の開口領域内の前記第2の半導体層上に、前記半導体基板の主成分を成す元素と同一元素をその一部に含み、禁制帯幅が前記第1の半導体層及び前記第2の半導体層よりも大きい第1導電側の第3の半導体層を形成する工程と、前記第1の開口領域内の前記第3の半導体層上に金属層を形成する工程から成り、前記第1の溝の形成時は溝上部の開口領域が前記第1の開口部よりも広くなるよう、水平方向にも前記半導体基板のエッチングを施すことで前記第1の溝上部に前記第1の絶縁膜からなる庇を形成し、前記第1の溝は(111)面を含む前記半導体基板の側壁を有するように溝形成条件を調整し、前記第1の半導体層が、前記第1の溝底部に露出した前記半導体基板の(100)面と、(111)面を含む前記半導体基板の側壁と、前記第1の絶縁膜から成る庇の下部表面と接し、前記第1の半導体層と前記第2の半導体層の界面は、前記第1の半導体層と前記第1の絶縁膜の界面よりも下部に位置するように前記第1の半導体層の形成条件を調整し、前記第2の半導体層が、前記第1の半導体層と前記第1の絶縁膜から成る庇の下部表面と接するように前記第2の半導体層の形成条件を調整し、前記第3の半導体層と前記金属層の界面が前記第1の絶縁膜の下部表面と前記第1の絶縁膜の上部表面の間に位置するように前記第3の半導体層の形成条件を調整すると良い。

20

30

40

【0083】

さらに、前記第1の絶縁膜から成る庇の水平方向の長さが、前記第1の溝の深さに対して10分の1倍以上且つ1倍以下となるように前記第1の溝の形成条件を調整すると良い。

【0084】

前記第2の半導体層と前記第3の半導体層の形成は、不純物を添加したエピタキシャル成長により行い、前記第2の半導体層と前記第3の半導体層中の不純物濃度を、深さ方向に対してほぼ一定とするとより好適である。

【0085】

50

前記半導体基板には、半導体支持基板と、前記半導体支持基板を覆う絶縁膜と、前記絶縁膜上に形成された単結晶半導体層を有する基板を用い、該絶縁膜上の半導体層を、導波路状にパターニングして第1の光導波路を形成すると望ましい。

【0086】

また、前記第1の光導波路上に、前記第1の光導波路を覆い、前記第1の光導波路の一部表面を露出する開口を有する絶縁膜を形成し、露出した前記第1の光導波路上に前記半導体支持基板を構成する元素をその一部に含む第2の光導波路を形成しても良い。

【0087】

前記第3の半導体層と前記金属層の接合界面がオーミック接合となるように前記第3の半導体層中の不純物濃度を調整すると良い。

10

【0088】

また、前記第3の半導体層と前記金属層の接合界面がショットキー接合となるように前記第3の半導体層中の不純物濃度を調整しても良い。

【0089】

前記半導体支持基板と前記第1の光導波路がシリコンから成る基板を用い、前記第2の光導波路と前記第3の半導体層をシリコンまたはシリコン・ゲルマニウムとし、前記半導体犠牲層と前記第1の半導体層と前記第2の半導体層をゲルマニウムまたはシリコン・ゲルマニウムとし、前記第1の半導体層と前記第2の半導体層のゲルマニウム組成が、共に前記第2の光導波路と前記第3の半導体層のいずれのゲルマニウム組成よりも大きくするより好適である。

20

【0090】

本発明に係る半導体装置によれば、開口部を有する  $SiO_2$  層が堆積された  $Si$  基板が上記開口部直下に溝を形成しており、上記溝を Ge 光吸收層と n 型 Ge 電極層が埋め込んでおり、更に上記  $SiO_2$  層で囲まれた上記開口部内には上記 n 型 Ge 電極層上に形成された n 型 SiGe 保護膜が存在していて、上記開口部内で金属層との接合を形成した構造を有している。Ge 光吸收層と n 型 Ge 電極層、更に n 型 SiGe 保護膜と金属層がいずれも上記開口領域に自己整合して形成しており、Butt-Joint 型 Ge 受光素子構造において一層の小型化・高速化が可能になる。上記溝上部に上記  $SiO_2$  層からなる庇を形成することで、上記溝を Ge 光吸收層と n 型 Ge 電極層を平坦に埋め込むことを可能にしている為、上記 Ge 光吸收層と n 型 Ge 電極層と n 型 SiGe 保護膜を連続して形成することが出来、従来の Butt-Joint 型 Ge 受光素子に比べて Ge 表面の平坦化工程とイオン注入工程、さらにイオン注入領域と電極形成領域のパターニング工程を省略することが出来、製造工程の大幅な削減が可能となる。また、n 型 Ge 電極層によって n 型 SiGe 保護膜と Ge 光吸收層を分離することで暗電流を低減し、更に n 型 Ge 電極層をエピタキシャル成長により形成することで上記 n 型 Ge 電極層を薄膜化することが出来、受光効率を高めることが出来る。

30

【0091】

従って、工程数が削減され、素子の小型化・高速化を可能にし、且つ良好な受光特性を有する半導体装置の及び半導体装置の製造方法を提供することが出来る。

【0092】

なお、本発明は上記した実施例に限定されるものではなく、様々な変形例が含まれる。例えば、上記した実施例は本発明を分かりやすく説明するために詳細に説明したものであり、必ずしも説明した全ての構成を備えるものに限定されるものではない。また、ある実施例の構成の一部を他の実施例の構成に置き換えることも可能であり、また、ある実施例の構成に他の実施例の構成を加えることも可能である。また、各実施例の構成の一部について、他の構成の追加・削除・置換をすることが可能である。

40

【符号の説明】

【0093】

1 …シリコン基板、2 …二酸化シリコン層、3 …二酸化シリコン層、4 …単結晶シリコン層 (SOI層、光導波路)、4a …単結晶シリコン層 (選択成長層)、5 …高不純物濃度

50

p型単結晶シリコン領域(電極層)、6...低不純物濃度p型単結晶シリコン領域、7...二酸化シリコン層、7a...二酸化シリコン層、8...単結晶ゲルマニウム層(光吸収層)、9...n型単結晶ゲルマニウム電極層層、10...n型単結晶シリコン・ゲルマニウム層(保護膜)、11...窒化チタン層(金属層)、12...アルミニウム層、101...シリコン基板、102...二酸化シリコン層、103...単結晶シリコン層、104...単結晶ゲルマニウム層、105...n型単結晶ゲルマニウム層、106...p型単結晶シリコン領域、107...二酸化シリコン層、108...金属電極、111...シリコン基板、112...二酸化シリコン層、113...単結晶シリコン層、114...単結晶ゲルマニウム層、115...二酸化シリコン層、116...p型単結晶ゲルマニウム領域、117...n型単結晶ゲルマニウム領域、118...金属電極、121...シリコン基板(導波路)、122...p型単結晶シリコン領域、123...単結晶シリコン層、124...単結晶シリコン・ゲルマニウム層、125...単結晶ゲルマニウム層、125a...n型単結晶ゲルマニウム層、126...n型単結晶シリコン層、127...二酸化シリコン層、128...二酸化シリコン層、129...n型多結晶シリコン層、130...金属電極、131...シリコン基板、132...二酸化シリコン層、133...単結晶ゲルマニウム層、201...SOI(Silicon on Insulator)基板、202...ゲルマニウム受光素子、203...シリコン光変調器、204...化合物半導体レーザ、205...シリコン光導波路、206...光ファイバ、207...金属電極、208...LSIチップ。

【 図 1 】

1

【 図 2 】

图2

【図3】

図3

【図4】

図4

【図5A】

図5A

【図5B】

図5B

【図6】

図6

【図7】

図7

【図8】

図8

【図9】

図9

【図10A】

図10A

【図10B】

図10B

【図10C】

図10C

【図10D】

図10D

【図10E】

図10E

【図10F】

図10F

【図10G】

図10G

【図10H】

図10H

【図 11 A】

図11A

【図 11 B】

図11B

【図 11 C】

図11C

【図 11 D】

図11D

【図11E】

図11E

【図11F】

図11F

【図11G】

図11G

【図11H】

図11H

【図12A】

図12A

【図12B】

図12B

【図12C】

図12C

【図12D】

図12D

【図12E】

図12E

【図12F】

図12F

【図12G】

図12G

【図12H】

図12H

【図13】

図13

【図14】

図14

【図15】

図15

【図16】

図16

【図17】

図17

【図18】

図18

【図19】

図19

【図20】

図20

【図21】

図21

【図22A】

図22A

### 【図22B】

22B

【図23A】

23A

【図23B】

図23B

【図24A】

図24A

【図24B】

図24B

【図25】

図25

---

フロントページの続き

(72)発明者 藤方 潤一

東京都港区芝五丁目7番1号 日本電気株式会社内

審査官 吉岡 一也

(56)参考文献 特開平08-316449 (JP, A)

特表2010-536170 (JP, A)

特開昭51-107768 (JP, A)

特開昭62-156831 (JP, A)

特開昭57-180147 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 31/10