(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-21968

(P2008-21968A)

(43) 公開日 平成20年1月31日(2008.1.31)

| (51) Int.Cl.                 | F 1        | テーマコード (参考) |

|------------------------------|------------|-------------|

| <b>H01L 27/10</b> (2006.01)  | H01L 27/10 | 451         |

| <b>H01L 27/105</b> (2006.01) | H01L 27/10 | 448         |

| <b>H01L 45/00</b> (2006.01)  | H01L 45/00 | Z           |

| <b>H01L 49/00</b> (2006.01)  | H01L 49/00 | Z           |

| <b>G11C 13/00</b> (2006.01)  | G11C 13/00 | A           |

審査請求 未請求 請求項の数 18 O L (全 15 頁)

(21) 出願番号 特願2007-121187 (P2007-121187)

(22) 出願日 平成19年5月1日 (2007.5.1)

(31) 優先権主張番号 10-2006-0065469

(32) 優先日 平成18年7月12日 (2006.7.12)

(33) 優先権主張国 韓国 (KR)

(71) 出願人 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区梅灘洞 416

(74) 代理人 100064908

弁理士 志賀 正武

(74) 代理人 100089037

弁理士 渡邊 隆

(74) 代理人 100108453

弁理士 村山 靖彦

(74) 代理人 100110364

弁理士 実広 信哉

最終頁に続く

(54) 【発明の名称】不揮発性メモリ素子の動作方法

(57) 【要約】 (修正有)

【課題】低い動作電流で動作し、高集積化の可能な不揮発性メモリ素子のマルチビット動作方法を提供する。

【解決手段】第1埋め込み電極112を第1ビットラインBL1として利用し、第2埋め込み電極114を第2ビットラインBL2として利用し、そして、ゲート電極132をワードラインとして利用し、第1抵抗層122及び第2抵抗層124に2ビットのデータをプログラムするステップと、第1抵抗層122及び第2抵抗層124にプログラムされた2ビットのデータを読み取るステップとを含む不揮発性メモリ素子の動作方法である。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

半導体基板と、

前記半導体基板の表面の付近にそれぞれ形成され、可変抵抗状態を保存する第1抵抗層及び第2抵抗層と、

前記第1抵抗層の下側の前記半導体基板の部分に形成され、前記第1抵抗層と連結された第1埋め込み電極と、

前記第2抵抗層の下側の前記半導体基板の部分に形成され、前記第2抵抗層と連結された第2埋め込み電極と、

前記半導体基板上に形成され、前記第1抵抗層及び第2抵抗層上を横切って延びるゲート電極と、

前記半導体基板と前記ゲート電極との間のゲート絶縁膜と、を備える不揮発性メモリ素子の動作方法であって、

前記第1埋め込み電極を第1ビットラインとして利用し、前記第2埋め込み電極を第2ビットラインとして利用し、前記ゲート電極をワードラインとして利用して、前記第1抵抗層及び第2抵抗層に2ビットのデータをプログラムするステップと、前記第1抵抗層及び第2抵抗層にプログラムされた2ビットのデータを読み取るステップと、を含むことを特徴とする不揮発性メモリ素子の動作方法。

**【請求項 2】**

前記2ビットのデータをプログラムするステップは、前記第1抵抗層及び第2抵抗層の抵抗をそれぞれ二つの状態に変化させて行うことを特徴とする請求項1に記載の不揮発性メモリ素子の動作方法。

**【請求項 3】**

前記プログラムするステップで前記第1抵抗層の抵抗変化は、

前記第1ビットラインにプログラム電圧を印加し、前記第2埋め込み電極と前記第1抵抗層とを連結する深いチャネルが形成されるように、前記ワードラインにターンオン電圧を印加して行うことを特徴とする請求項2に記載の不揮発性メモリ素子の動作方法。

**【請求項 4】**

前記プログラムするステップで前記第2抵抗層の抵抗変化は、

前記第2ビットラインにプログラム電圧を印加し、前記第1埋め込み電極と前記第2抵抗層とを連結する深いチャネルが形成されるように、前記ワードラインにターンオン電圧を印加して行うことを特徴とする請求項2に記載の不揮発性メモリ素子の動作方法。

**【請求項 5】**

前記2ビットのデータを読み取るステップは、

前記埋め込み電極の一つと隣接した抵抗層の一つとを連結するように深いチャネルを形成し、前記第1ビットラインと前記第2ビットラインとの間の両方向電流値を順次に測定するステップを含むことを特徴とする請求項1に記載の不揮発性メモリ素子の動作方法。

**【請求項 6】**

前記2ビットのデータを読み取るステップは、

前記第1抵抗層と前記第2抵抗層とを連結するように浅いチャネルを形成し、前記第1ビットラインと前記第2ビットラインとの間の少なくとも一方向電流値を測定するステップを含むことを特徴とする請求項1に記載の不揮発性メモリ素子の動作方法。

**【請求項 7】**

前記一方向電流値を測定するステップは、少なくとも二つのレベルの読み取り電圧で繰り返されることを特徴とする請求項6に記載の不揮発性メモリ素子の動作方法。

**【請求項 8】**

前記第1抵抗層及び前記第2抵抗層に保存されたデータを同時に消去するステップをさらに含むことを特徴とする請求項1に記載の不揮発性メモリ素子の動作方法。

**【請求項 9】**

10

20

30

40

50

前記データを同時に消去するステップは、

前記第1抵抗層と前記第2抵抗層とを連結するように浅いチャンネルを形成し、前記第1ビットラインと前記第2ビットラインとの間に消去電圧を印加するステップを含むことを特徴とする請求項8に記載の不揮発性メモリ素子の動作方法。

【請求項10】

前記第1抵抗層及び第2抵抗層は、 $Nb_2O_5$ 、クロムがドーピングされた $SiTiO_3$ 、 $ZrO_x$ 、GST( $GeSb_xTe_y$ )、 $NiO$ 、 $ZnO$ 、 $TiO_2$ 及び $HfO$ からなる群から選択された少なくとも一つをそれぞれ含むことを特徴とする請求項1に記載の不揮発性メモリ素子の動作方法。

【請求項11】

半導体基板と、

前記半導体基板の表面の付近にそれぞれ形成され、可変抵抗状態を保存する複数の抵抗層と、

前記複数の抵抗層の下側の前記半導体基板の部分にそれぞれ形成され、前記複数の抵抗層とそれぞれ連結された複数の埋め込み電極と、

前記複数の抵抗層上を横切って延びるゲート電極と、

前記半導体基板と前記ゲート電極との間のゲート絶縁膜と、を備える不揮発性メモリ素子の動作方法であって、

前記複数の埋め込み電極を複数のビットラインとして利用し、前記ゲート電極をワードラインとして利用して、前記複数の抵抗層のうち、隣接する二つの抵抗層に2ビットのデータをプログラムするステップと、前記隣接する二つの抵抗層にプログラムされた2ビットのデータを読み取るステップと、を含むことを特徴とする不揮発性メモリ素子の動作方法。

【請求項12】

前記2ビットのデータをプログラムするステップは、前記隣接する二つの抵抗層の抵抗をそれぞれ二つの状態に変化させて行うことを特徴とする請求項11に記載の不揮発性メモリ素子の動作方法。

【請求項13】

前記プログラムするステップで、前記隣接する二つの抵抗層の一つの抵抗変化は、

前記二つの抵抗層のうちの一つと隣接した前記埋め込み電極の一つとを連結する深いチャンネルを形成し、前記二つの抵抗層のうちの一つに連結されたビットラインにプログラム電圧を印加するステップを含むことを特徴とする請求項12に記載の不揮発性メモリ素子の動作方法。

【請求項14】

前記2ビットのデータを読み取るステップは、

前記隣接した二つの抵抗層のうちの一つと隣接した前記埋め込み電極の一つとを連結するように深いチャンネルを形成し、前記隣接した二つの抵抗層に連結されたビットライン間の両方向電流値を順次に測定するステップを含むことを特徴とする請求項12に記載の不揮発性メモリ素子の動作方法。

【請求項15】

前記2ビットのデータを読み取るステップは、

前記隣接した二つの抵抗層を連結するように浅いチャンネルを形成し、前記隣接した二つの抵抗層に連結されたビットライン間の少なくとも一方向電流値を測定するステップを含むことを特徴とする請求項12に記載の不揮発性メモリ素子の動作方法。

【請求項16】

前記一方向電流値を測定するステップは、少なくとも二つのレベルの読み取り電圧で行われることを特徴とする請求項15に記載の不揮発性メモリ素子の動作方法。

【請求項17】

前記複数の抵抗層のうち、連結した所定数の抵抗層に保存されたデータを同時に消去するステップをさらに含むことを特徴とする請求項11に記載の不揮発性メモリ素子の動作

10

20

30

40

50

方法。

【請求項 1 8】

前記データを同時に消去するステップは、

前記連続した所定数の抵抗層を連結するように浅いチャンネルを形成し、前記連続した所定数の抵抗層の両端部の抵抗層に連結されたビットラインに消去電圧を印加するステップを含むことを特徴とする請求項 1 5 に記載の不揮発性メモリ素子の動作方法。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、半導体素子に係り、特に、抵抗ノードを利用した不揮発性メモリ素子の動作方法に関する。 10

【背景技術】

【0 0 0 2】

不揮発性メモリ素子、例えば、相転移メモリ素子 (Phase-change Random Access Memory: PRAM) または抵抗メモリ素子 (Resistive Random Access Memory: RRAM) は、抵抗ノードの可変抵抗状態を利用して動作する。最近、高容量のデータ処理を要する半導体製品の増加によって、このような不揮発性メモリ素子の集積度の向上または動作ビットの向上が要求されている。例えば、マルチビットで動作可能な不揮発性メモリ素子への必要性が増大しつつある。 20

【0 0 0 3】

一方、不揮発性メモリ素子は、前述のように、高容量化されると同時に高速度化されている。すなわち、高容量のデータを処理するためには、データの高速処理が要求されている。したがって、不揮発性メモリ素子の動作速度の上昇、例えば、フラッシュメモリ素子のようなブロック消去またはフラッシュ消去特性が要求されている。

【0 0 0 4】

また、不揮発性メモリ素子の集積度の向上によって、動作電流を減少させるための努力が行われている。しかし、抵抗ノードを利用した不揮発性メモリ素子は、比較的に高い動作電流を必要としている。動作電流の減少は、抵抗ノードの可変抵抗の状態に影響を及ぼしうる。したがって、従来の不揮発性メモリ素子は、動作電流を減少させるのに当って限界を有している。 30

【0 0 0 5】

例えば、PRAMは、相転移抵抗体の結晶状態の変化による抵抗変化を利用してデータを保存する。しかし、PRAMの結晶状態を変化させるためには、高い電流密度が必要であり、これにより、動作電流が増加するという問題がある。このような動作電流の増加は、短チャンネル効果を誘発して、PRAM素子の集積度の向上に障害となりうる。したがって、相転移抵抗体の結晶状態の変化領域を縮小させて、少ない動作電流で高い電流密度を得ようとする努力が行われている。

【発明の開示】

【発明が解決しようとする課題】

【0 0 0 6】

本発明が解決しようとする技術的課題は、前述の問題点を克服するためのものであって、低い動作電流で動作し、高集積化の可能な不揮発性メモリ素子のマルチビット動作方法を提供するところにある。

【課題を解決するための手段】

【0 0 0 7】

前記技術的課題を解決するための本発明の一形態に係る不揮発性メモリ素子の動作方法が提供される。前記不揮発性メモリ素子は、半導体基板と、前記半導体基板の表面の付近にそれぞれ形成され、可変抵抗状態を保存する第1抵抗層及び第2抵抗層と、前記第1抵抗層の下側の前記半導体基板の部分に形成され、前記第1抵抗層と連結された第1埋め込

10

20

30

40

50

み電極と、前記第2抵抗層の下側の前記半導体基板の部分に形成され、前記第2抵抗層と連結された第2埋め込み電極と、前記半導体基板上に形成され、前記第1抵抗層及び第2抵抗層上を横切って延びるゲート電極と、前記半導体基板と前記ゲート電極との間のゲート絶縁膜とを備える。前記不揮発性メモリ素子の動作方法は、前記第1埋め込み電極を第1ビットラインとして利用し、前記第2埋め込み電極を第2ビットラインとして利用し、前記ゲート電極をワードラインとして利用する。そして、前記不揮発性メモリ素子の動作方法は、前記第1抵抗層及び第2抵抗層に2ビットのデータをプログラムするステップと、前記第1抵抗層及び第2抵抗層にプログラムされた2ビットのデータを読み取るステップと、を含む。

【0008】

前記本発明の一側面によれば、前記2ビットのデータをプログラムするステップは、前記第1抵抗層及び第2抵抗層の抵抗をそれぞれ二つの状態に変化させて行える。

【0009】

前記本発明の他の側面によれば、前記2ビットのデータを読み取るステップは、前記第1抵抗層及び前記第2抵抗層の抵抗値の変化による前記第1ビットラインと前記第2ビットラインとの間の電流の変化を測定して行える。

【0010】

前記本発明のさらに他の側面によれば、前記2ビットのデータを読み取るステップは、前記埋め込み電極の一つと隣接した抵抗層の一つとを連結するように深いチャンネルを形成し、前記第1ビットラインと前記第2ビットラインとの間の両方向電流値を順次に測定するステップを含みうる。

【0011】

前記本発明のさらに他の側面によれば、前記不揮発性メモリ素子の動作方法は、前記第1抵抗層及び前記第2抵抗層に保存されたデータを同時に消去するステップをさらに含みうる。

【0012】

前記技術的課題を解決するための本発明の他の形態に係る不揮発性メモリ素子の動作方法が提供される。前記不揮発性メモリ素子は、半導体基板と、前記半導体基板の表面の付近にそれぞれ形成され、可変抵抗状態を保存する複数の抵抗層と、前記複数の抵抗層の下側の前記半導体基板の部分にそれぞれ形成され、前記複数の抵抗層とそれぞれ連結された複数の埋め込み電極と、前記複数の抵抗層上を横切って延びるゲート電極と、前記半導体基板と前記ゲート電極との間のゲート絶縁膜とを備える。前記不揮発性メモリ素子の動作方法は、前記複数の埋め込み電極を複数のビットラインとして利用し、前記ゲート電極をワードラインとして利用する。そして、前記不揮発性メモリ素子の動作方法は、前記複数の抵抗層のうち、隣接する二つの抵抗層に2ビットのデータをプログラムするステップと、前記隣接する二つの抵抗層にプログラムされた2ビットのデータを読み取るステップと、を含む。

【発明の効果】

【0013】

本発明に係る不揮発性メモリ素子の動作方法によれば、動作電流、例えば、プログラム電流を低くすることができる。

【0014】

また、本発明に係る不揮発性メモリ素子の動作方法によれば、一つの単位セルで2ビットのデータを処理できる。

【0015】

また、本発明に係る不揮発性メモリ素子の動作方法によれば、ブロック消去またはフラッシュ消去が可能であり、したがって、動作速度が向上しうる。

【発明を実施するための最良の形態】

【0016】

以下、添付した図面を参照して、本発明に係る望ましい実施形態を説明することによつ

10

20

30

40

50

て本発明を詳細に説明する。しかし、本発明は、以下で開示される実施形態に限定されるものではなく、相異なる多様な形態で具現され、単に、本実施形態は、本発明の開示を完全にし、当業者に発明の範疇を完全に知らせるために提供されるものである。図面における構成要素は、説明の便宜のために、その大きさが誇張されている。

【0017】

本発明の実施形態に係る不揮発性メモリ素子は、抵抗ノードまたは抵抗層を利用してデータを保存できる。したがって、本発明の実施形態に係る不揮発性メモリ素子は、その抵抗ノードまたは抵抗層の種類によって、他の名称で呼ばれうる。例えば、本発明の実施形態に係る不揮発性メモリ素子は、P R A M またはR R A M を備えうるが、本発明の範囲は、このような名称に制限されない。

10

【0018】

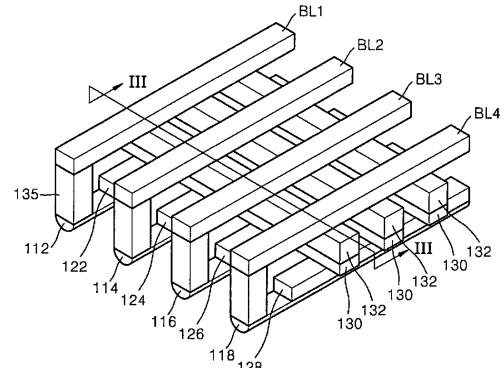

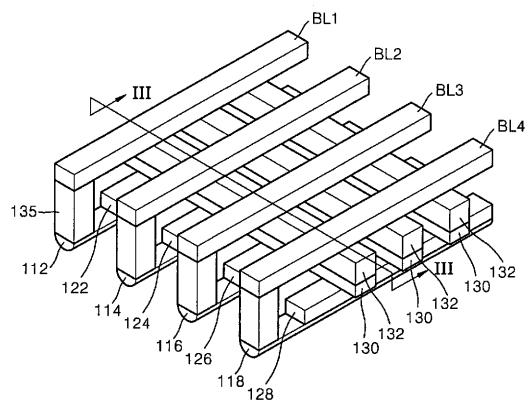

図1は、本発明の一実施形態に係る不揮発性メモリ素子を示す概略的な斜視図であり、図2は、図1の不揮発性メモリ素子のI I I - I I I 線による断面図である。

【0019】

図1及び図2に示すように、不揮発性メモリ素子は、半導体基板102を備える。ただし、図1には、説明の便宜のために、半導体基板102が示されていない。半導体基板102は、シリコン(Si)ウェーハ、ゲルマニウム(Ge)ウェーハまたは金属-絶縁体遷移(Metal-Insulator Transition; MIT)物質を含みうる。例えば、MIT物質は、遷移金属酸化物、例えば、 $V_2O_5$ 、 $TiO_x$ を含みうる。このようなMIT物質は、所定の臨界電圧以上の電圧が印加されれば、絶縁体から金属に変化しうる。このようなMIT物質は、複数層の半導体素子の形成に利用されうる。

20

【0020】

複数の抵抗層122、124、126、128は、半導体基板102の表面の付近にそれぞれ形成される。複数の埋め込み電極112、114、116、118は、抵抗層122、124、126、128の下側の半導体基板102の部分にそれぞれ形成される。ゲート電極132は、半導体基板102上に形成され、抵抗層122、124、126、128を横切って延びるように配置されうる。ゲート絶縁膜130は、半導体基板102とゲート電極132との間に介在されうる。選択的に、ビットラインBL1、BL2、BL3、BL4が半導体基板102上に更に形成されうる。

30

【0021】

例えば、埋め込み電極112、114、116、118は、半導体基板102内に埋め込まれた形態で提供されうる。埋め込み電極112、114、116、118は、その機能または配置によって多様な形態として呼ばれ、その名称によって本発明の範囲が制限されない。例えば、埋め込み電極112、114、116、118は、順次にソースS及びドレインDと呼ばれてもよく、または埋め込み電極112、114、116、118は、その位置上の配置によって下部電極と呼ばれてもよい。

【0022】

例えば、埋め込み電極112、114、116、118は、半導体基板102に不純物をドーピングして形成されうる。この場合、半導体基板102が第1導電型の不純物でドーピングされた場合、埋め込み電極112、114、116、118は、第1導電型と逆である第2導電型の不純物でドーピングされうる。これにより、埋め込み電極112、114、116、118及び半導体基板102は、ダイオード接合を形成できる。第1導電型及び第2導電型は、n型及びp型からそれぞれ選択された何れか一つでありうる。

40

【0023】

他の例として、埋め込み電極112、114、116、118は、金属層または金属シリサイド層を備えうる。この場合、埋め込み電極112、114、116、118は、半導体基板102とショットキー接合を形成できる。このようなショットキー接合により、埋め込み電極112、114、116、118と半導体基板102との間の電流の流れは、整流の特性を有しうる。

【0024】

50

ゲート絶縁膜 130 は、ゲート電極 132 を半導体基板 102 と絶縁させる役割が行える。さらに、ゲート絶縁膜 130 が抵抗層 122、124、126、128 上にさらに延びることによって、抵抗層 122、124、126、128 をゲート電極 132 とさらに絶縁させる役割が行える。ゲート絶縁膜 130 の厚さは、動作電圧によって適切に選択され、図 1 及び図 2 に示すサイズにより制限されない。例えば、ゲート電極 132 は、導電性物質、例えば、ポリシリコン層、または金属層を備えうる。

#### 【0025】

ビットライン BL1、BL2、BL3、BL4 は、層間絶縁膜 160 を介在してゲート電極 132 上に形成される。ビットライン BL1、BL2、BL3、BL4 は、埋め込み電極 112、114、116、118 のそれぞれとプラグ 135 を介して連結される。例えば、ビットライン BL1、BL2、BL3、BL4 は、ゲート電極 132 の延長方向とは異なる方向、例えば、埋め込み電極 112、114、116、118 と平行な方向に延びうる。例えば、ビットライン BL1、BL2、BL3、BL4 は、金属層を備えうる。

10

#### 【0026】

複数の抵抗層 122、124、126、128 は、可変抵抗状態を保存し、このような可変抵抗状態は、データビットとして保存されうる。例えば、抵抗層 122、124、126、128 は、低抵抗状態及び高抵抗状態を有し、このような低抵抗状態及び高抵抗状態は、それぞれデータ状態 “0” または “1” に対応しうる。抵抗層 122、124、126、128 を二つ以上組合せば、2 ビット以上のデータ状態を形成することもある。例えば、二つの抵抗層を利用すれば、(0, 0)、(0, 1)、(1, 0) 及び (1, 1) 状態の 2 ビットのデータ状態が形成されうる。

20

#### 【0027】

例えば、抵抗層 122、124、126、128 は、両端に印加された電圧によって、その抵抗状態が変わる物質を含み、例えば、Nb<sub>2</sub>O<sub>5</sub>、クロム (Cr) がドーピングされた SrTiO<sub>3</sub>、ZrO<sub>x</sub>、GST (GeSb<sub>x</sub>Te<sub>y</sub>)、NiO、ZnO、TiO<sub>2</sub> 及び HfO からなる群から選択された少なくとも一つ以上をそれぞれ含みうる。例えば、GST は、その結晶状態の変化によってその抵抗が変わるという点で PRAM に利用されうる。他の例として、Nb<sub>2</sub>O<sub>5</sub>、クロム (Cr) がドーピングされた SrTiO<sub>3</sub>、NiO または ZnO は、結晶状態の変化なしにその抵抗が変わるという点で RRAM に利用されうる。

30

#### 【0028】

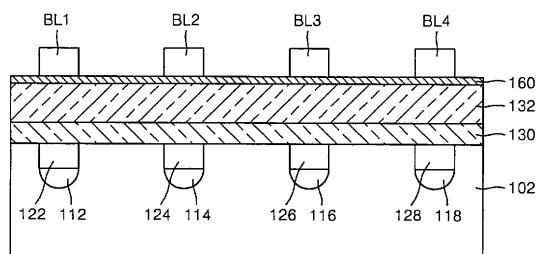

図 3 に示すように、RRAM 素子に利用される抵抗層の電圧 - 電流特性を例示的に更に詳細に説明する。図 3 は、抵抗層として NiO を例としたグラフであって、抵抗層の物質によっては、他の形状のグラフが形成されうる。ただし、印加された電圧によって抵抗が変わりうるという点では共通する。

#### 【0029】

図 3 に示すように、抵抗層に初期電圧が印加されれば (P10)、セット電圧、例えば、NiO の場合、4.5 V までは電流がほとんど流れない。すなわち、抵抗層は、高い抵抗値を表す (リセット状態)。しかし、セット電圧を超えると、電流が急増する。一旦、セット電圧以上の電圧が加えられた後、再び 0 から電圧を印加すれば (P20)、高い電流が流れる。すなわち、抵抗層は、低い抵抗値を表す (セット状態)。しかし、再びリセット電圧以上に電圧が増加すれば、電流は急減する (P30)。すなわち、抵抗層の抵抗が再びリセット状態の高い抵抗値に還元される。以後、セット電圧に至る前まで電圧を上昇させ続ければ (P40)、初期リセット状態と同じ経路を示す。

40

#### 【0030】

すなわち、抵抗層は、臨界電圧、例えば、セット電圧またはリセット電圧を境界として比抵抗が変わり、このような比抵抗の変化は、印加電圧がなくなった後にも、一定の範囲の電圧区内では維持される。したがって、抵抗層は、不揮発性メモリ素子の記録媒体として利用されうる。

#### 【0031】

50

図3の抵抗層に関する説明は、RRAMに利用されるものを例として説明したものであり、PRAMに利用される抵抗層は、他の方で抵抗変化を経験できる。PRAMに利用される抵抗層は、相転移抵抗層と呼ばれ、このような相転移抵抗層は、構造の変化、例えば、非晶質状態及び結晶質状態への遷移を通じて抵抗状態が変化しうる。このような相転移抵抗層の抵抗変化の特性は、当業者には周知のものであるので、その詳細な説明を省略する。

【0032】

一方、前述の実施形態で、抵抗層122、124、126、128のうち、隣接した一对、例えば、第1抵抗層122及び第2抵抗層124が単位セルの構造を形成できる。この場合、第1埋め込み電極112、第2埋め込み電極114、第1ビットラインBL1及び第2ビットラインBL2が、このような単位セルの構造の一部となりうる。

10

【0033】

本発明の実施形態に係る不揮発性メモリ素子は、図1及び図2に示す配置に制限されない。したがって、不揮発性メモリ素子は、一つの単位セルの構造を含んでもよく、または複数の単位セルの構造を含んでもよい。すなわち、抵抗層122、124、126、128、埋め込み電極112、114、116、118、及びビットラインBL1、BL2、BL3、BL4は、単に対として提供され、その数が本発明の範囲を制限しない。

【0034】

以下では、前述の不揮発性メモリ素子の動作特性を説明する。

20

【0035】

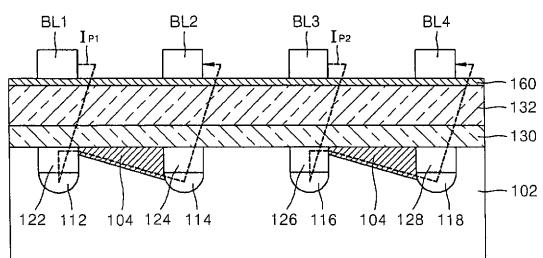

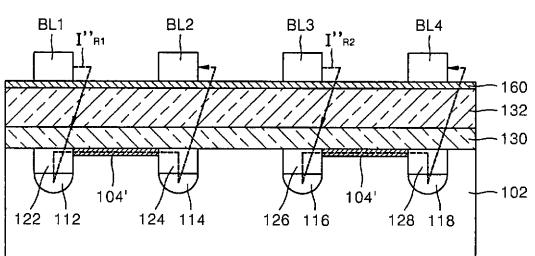

図4及び図5は、本発明の一実施形態に係る不揮発性メモリ素子のプログラム動作を示す断面図である。

【0036】

図4及び図5に示すように、この実施形態で、第1抵抗層122及び第2抵抗層124が一つの単位セルを形成し、第3抵抗層126及び第4抵抗層128が他の単位セルを形成する。図4及び図5には、二つの単位セルが同時に動作するものとして図示されているが、二つの単位セルが別途に動作してもよい。さらに、単位セルの構成は他の形態で提供され、例えば、第2抵抗層124及び第3抵抗層126が一つの単位セルを形成するように提供されてもよい。一方、ゲート電極132は、ワードラインとして利用されうる。

30

【0037】

図4に示すように、二つの単位セルからそれぞれ選択された一つの抵抗層、例えば、第1抵抗層122及び第3抵抗層126のプログラム動作が例示的に説明される。このプログラム動作で、第1抵抗層122の右側部分及び第3抵抗層126の右側部分にデータが保存されうる。このようなデータプログラムは、前述のように、第1抵抗層122及び第3抵抗層126の抵抗をそれぞれ二つの状態に変化させて行える。

【0038】

例えば、第1ビットラインBL1にプログラム電圧を印加し、第2埋め込み電極114と第1抵抗層122とを連結する深いチャンネル104が形成されるように、ワードライン、すなわち、ゲート電極132にターンオン電圧を印加する。深いチャンネル104は、第1ビットラインBL1の付近より第2ビットラインBL2の付近で更に深く形成される。例えば、深いチャンネル104の深さは、ゲート電極132に加えられるターンオン電圧または半導体基板102の不純物の濃度を調節して制御できる。

40

【0039】

これにより、プログラム電流 $I_{p1}$ は、第1ビットラインBL1から第1埋め込み電極112、第1抵抗層122、深いチャンネル104及び第2埋め込み電極114を経て、第2ビットラインBL2の方向に流れる。深いチャンネル104が、第1抵抗層122と第2埋め込み電極114とを連結するために、相対的に抵抗の高い第2抵抗層124を経るプログラム電流 $I_{p1}$ の量は無視できる。

【0040】

同様に、第3ビットラインBL3にプログラム電圧を印加し、第4埋め込み電極118

50

と第3抵抗層126とを連結する深いチャンネル104が形成されるように、ワードライン、すなわち、ゲート電極132にターンオン電圧を印加する。これにより、プログラム電流 $I_{P_2}$ は、第3ビットラインBL3から第3埋め込み電極116、第3抵抗層126、深いチャンネル104及び第4埋め込み電極118を経て第4ビットラインBL4の方向に流れる。

【0041】

したがって、第1抵抗層122及び第3抵抗層126にプログラム電流が流れ、第1抵抗層122及び第3抵抗層126の抵抗が変わりうる。例えば、プログラム以前を低抵抗状態、例えば“0”状態とすれば、プログラムによって第1抵抗層122及び第3抵抗層126は、高抵抗状態、例えば“1”状態になりうる。例えば、プログラム電圧は、相転移抵抗を非晶質状態にするための電圧でありうる。しかし、データ状態“0”及び“1”は、その逆に表示されてもよい。

10

【0042】

結果的に、図4のプログラム動作により、二つの単位セルは、それぞれ(0, 0)状態から(1, 0)状態に変換しうる。例えば、(0, 0)状態は、単位セル内の二つの抵抗層、例えば、第1抵抗層122及び第2抵抗層124または第3抵抗層126及び第4抵抗層128が何れも低抵抗状態である場合を表す。(1, 0)状態は、単位セル内の左側抵抗層、例えば、第1抵抗層122または第3抵抗層126が高抵抗状態であり、右側抵抗層、例えば、第2抵抗層124または第4抵抗層128が低抵抗状態である場合を表す。

20

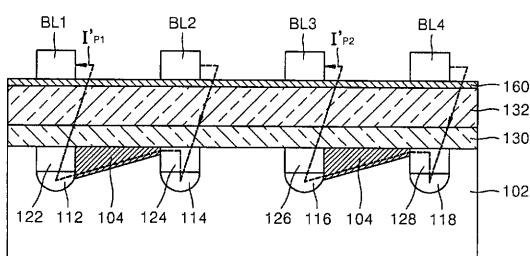

【0043】

図5に示すように、二つの単位セルからそれぞれ選択された異なる抵抗層、例えば、第2抵抗層124及び第4抵抗層128のプログラム動作が例示的に説明される。このプログラム動作で、第2抵抗層124の左側部分及び第4抵抗層128の左側部分にデータが保存されうる。図5のプログラム動作は、図4のプログラム動作で電流方向を逆方向にすることによって行える。

【0044】

例えば、第2ビットラインBL2及び第4ビットラインBL4にプログラム電圧を印加し、第1埋め込み電極112と第2抵抗層124、または第3埋め込み電極116と第4抵抗層128、をそれぞれ連結する深いチャンネル104が形成されるように、ワードライン、すなわち、ゲート電極132にターンオン電圧を印加する。

30

【0045】

これにより、プログラム電流 $I'_{P_1}$ は、第2ビットラインBL2から第1ビットラインBL1の方向に流れ、プログラム電流 $I'_{P_2}$ は、第4ビットラインBL4から第3ビットラインBL3の方向に流れ。これにより、第2抵抗層124及び第4抵抗層128にプログラム電流が流れ、第2抵抗層124及び第4抵抗層128の抵抗が変わりうる。

【0046】

結果的に、図5のプログラム動作により、二つの単位セルは、それぞれ(0, 0)状態から(0, 1)状態に変換しうる。(0, 1)状態は、単位セル内の右側抵抗層、例えば、第2抵抗層124または第4抵抗層128が高抵抗状態であり、左側抵抗層、例えば、第1抵抗層122または第3抵抗層126が低抵抗状態である場合を表す。

40

【0047】

一方、二つの単位セルに図4及び図5のプログラム動作を順次に行えば、二つの単位セルは、それぞれ(0, 0)状態から、(1, 0)状態を経て(1, 1)状態に変換しうる。(1, 1)状態は、単位セル内の二つの抵抗層、例えば、第1抵抗層122及び第2抵抗層124、または第3抵抗層126及び第4抵抗層128が何れも高抵抗状態である場合を表す。したがって、図4及び/または図5のプログラム動作を利用すれば、単位セルは、それぞれ四つの状態、すなわち(0, 0)、(1, 0)、(0, 1)及び(1, 1)の状態を有し、したがって、2ビットのデータを保存できる。

【0048】

50

前述のプログラム動作で、抵抗層の抵抗変化領域は、深いチャンネル104と接する局部的な部分になる。したがって、低いプログラム電流 $I_{p1}$ 、 $I_{p2}$ 、 $I'_{p1}$ 、 $I'_{p2}$ のみでプログラム動作が行われうる。

【0049】

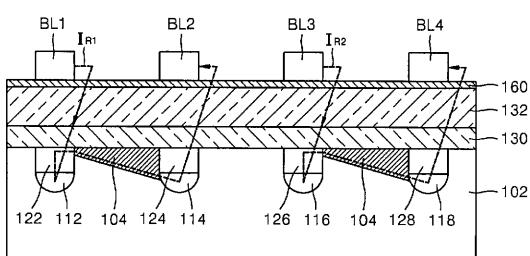

図6及び図7は、本発明の一実施形態に係る読み取り動作を示す断面図である。

【0050】

図6に示すように、第1ビットラインBL1及び第3ビットラインBL3に読み取り電圧をそれぞれ印加し、第2埋め込み電極114と第1抵抗層122、または第4埋め込み電極118と第3抵抗層126とをそれぞれ連結する深いチャンネル104が形成されるように、ワードライン、すなわち、ゲート電極132にターンオン電圧を印加する。読み取り電圧は、抵抗層122、124、126、128の抵抗変化を招かないように低い電圧であってもよく、したがって、プログラム電圧より低くてもよい。

10

【0051】

これにより、読み取り電流 $I_{R1}$ は、第1ビットラインBL1から第1埋め込み電極112、第1抵抗層122、深いチャンネル104及び第2埋め込み電極114を経て、第2ビットラインBL2の方向に流れる。読み取り電流 $I_{R2}$ は、第3ビットラインBL3から第3埋め込み電極116、第3抵抗層126、深いチャンネル104及び第4埋め込み電極118を経て、第4ビットラインBL4の方向に流れる。

20

【0052】

したがって、読み取り電流 $I_{R1}$ 、 $I_{R2}$ のレベルから、それぞれ第1抵抗層122及び第3抵抗層126の抵抗レベルが求められうる。前述のように、第2抵抗層124及び第4抵抗層128にはほとんど読み取り電流 $I_{R1}$ 、 $I_{R2}$ が流れないと想定されるため、第1抵抗層122及び第3抵抗層126の抵抗レベルがそれぞれ求められうる。これにより、第1抵抗層122及び第3抵抗層126のそれぞれのデータ状態、すなわち、“0”または“1”状態が読み取られうる。

20

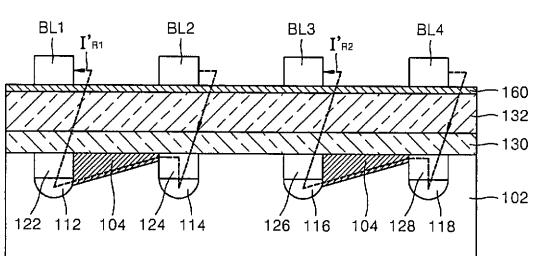

【0053】

図7に示すように、第2ビットラインBL2及び第4ビットラインBL4に読み取り電圧をそれぞれ印加し、第1埋め込み電極112と第2抵抗層124、または第3埋め込み電極116と第4抵抗層128とをそれぞれ連結する深いチャンネル104が形成されるように、ワードライン、すなわち、ゲート電極132にターンオン電圧を印加する。

30

【0054】

これにより、読み取り電流 $I'_{R1}$ は、第2ビットラインBL2から第2埋め込み電極114、第2抵抗層124、深いチャンネル104及び第1埋め込み電極112を経て、第1ビットラインBL1の方向に流れる。読み取り電流 $I'_{R2}$ は、第4ビットラインBL4から第4埋め込み電極118、第4抵抗層128、深いチャンネル104及び第3埋め込み電極116を経て、第3ビットラインBL3の方向に流れる。したがって、読み取り電流 $I'_{R1}$ 、 $I'_{R2}$ のレベルから、それぞれ第2抵抗層124及び第4抵抗層128の抵抗レベルが求められうる。これにより、第2抵抗層124及び第4抵抗層128のそれぞれのデータ状態、すなわち、“0”または“1”状態が読み取られうる。

40

【0055】

したがって、図6及び図7に示すように、深いチャンネル104を形成し、第1ビットラインBL1と第2ビットラインBL2との間の両方向電流 $I_{R1}$ 、 $I'_{R1}$ を測定することによって、単位セルの第1抵抗層122及び第2抵抗層124にプログラムされた2ビットのデータを読み取ることができる。同様に、深いチャンネル104を形成し、第3ビットラインBL3と第4ビットラインBL4との間の両方向電流 $I_{R2}$ 、 $I'_{R2}$ を測定することによって、単位セルの第3抵抗層126及び第4抵抗層128にプログラムされた2ビットのデータを読み取ることができる。

【0056】

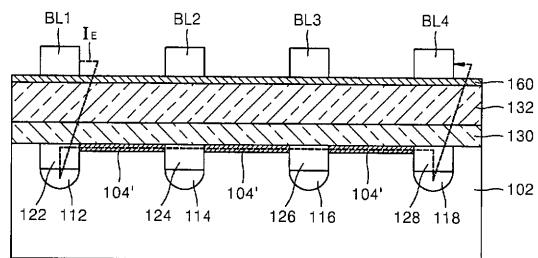

図8は、本発明の他の実施形態に係る不揮発性メモリ素子の読み取り動作を示す断面図である。

50

## 【0057】

図8に示すように、第1ビットラインBL1に読み取り電圧を印加し、第1抵抗層122と第2抵抗層124とを連結するように、半導体基板102に浅いチャンネル104'を形成する。これにより、読み取り電流I"R1は、第1ビットラインBL1から第1埋め込み電極112、第1抵抗層122、浅いチャンネル104'、第2抵抗層124及び第2埋め込み電極114を経て、第2ビットラインBL2に流れる。浅いチャンネル104'は、抵抗層122、124を直接連結し、埋め込み電極112、114を直接連結しないように浅く形成される。例えば、ワードライン、すなわち、ゲート電極132に加えられるターンオン電圧を高めることによって、浅いチャンネル104'を形成できる。

## 【0058】

同様に、第3ビットラインBL3に読み取り電圧を印加し、第3抵抗層126と第4抵抗層128とを連結するように、半導体基板102に浅いチャンネル104'を形成する。これにより、読み取り電流I"R2は、第3ビットラインBL3から第3埋め込み電極116、第3抵抗層126、浅いチャンネル104'、第4抵抗層128及び第4埋め込み電極118を経て、第4ビットラインBL4に流れる。

## 【0059】

読み取り電流I"R1を測定することによって、第1抵抗層122及び第2抵抗層124の抵抗レベル、すなわち、データ状態が同時に求められ、読み取り電流I"R2を測定することによって、第3抵抗層126及び第4抵抗層128の抵抗レベル、すなわち、データ状態が同時に求められうる。なぜなら、第1抵抗層122及び第2抵抗層124のそれぞれの抵抗レベルによって、読み取り電流I"R1が変わり、第3抵抗層126及び第4抵抗層128のそれぞれの抵抗レベルによって、読み取り電流I"R2が変わるためにある。

## 【0060】

このような読み取り電流I"R1、I"R2の差は、浅いチャンネル104'を形成するための閾電圧が半導体基板102に対するソースの電位に依存するためである。ここで、ソースは、浅いチャンネル104'と接する第2埋め込み電極114及び/または第2抵抗層124の端部、または第4埋め込み電極118及び/または第4抵抗層128の端部となりうる。ソースの電位は、第1抵抗層122及び第2抵抗層124の抵抗レベル、または第3抵抗層126及び第4抵抗層128の抵抗レベルによって変わる。

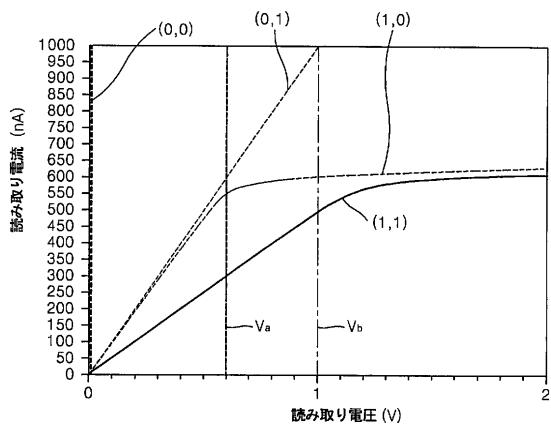

## 【0061】

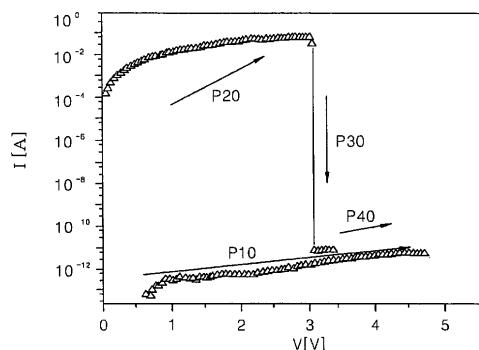

図10は、図8の不揮発性メモリ素子の読み取り動作のシミュレーション結果を示すグラフである。このシミュレーションで、抵抗層の“0”状態の抵抗は、1kとし、“1”状態の抵抗は、1Mとした。

## 【0062】

図10に示すように、読み取り電圧がV<sub>b</sub>であるとき、読み取り電流は、(1, 1)、(1, 0)、(0, 1)及び(0, 0)状態の順に増大した。ただし、(1, 0)及び(1, 1)状態をさらに確実に区分するために、V<sub>a</sub>で読み取り電流をさらに比較できる。例えば、V<sub>a</sub>は、約0.6Vであり、V<sub>b</sub>は、約1Vでありうる。このように、一つまたは二つの読み取り電流を比較することによって、単位セルの抵抗層のデータ状態を読み取ることができる。例えば、データ状態は、測定された読み取り電流値と、既に知られたデータ状態の読み取り電流とを比較することによって分かる。

## 【0063】

図9は、本発明の一実施形態に係る不揮発性メモリ素子の消去動作を示す断面図である。

## 【0064】

図9に示すように、所定数の抵抗層、例えば、抵抗層122、124、126、128のデータが同時に消去されうる。このような消去動作は、ブロック消去またはフラッシュ消去とも呼ばれる。

## 【0065】

10

20

30

40

50

例えば、抵抗層 122、124、126、128 を連結するように、浅いチャンネル 104' を形成し、抵抗層 122、124、126、128 のエッジに位置したビットライン、すなわち、第 1 ビットライン BL 1 と第 4 ビットライン BL 4 との間に消去電圧を印加する。これにより、第 1 ビットライン BL 1 から抵抗層 122、124、126、128 を経て、第 4 ビットライン BL 4 に消去電流  $I_E$  が流れる。

#### 【0066】

消去電流  $I_E$  により、抵抗層 122、124、126、128 のデータは、何れも同時に消去されうる。例えば、抵抗層 122、124、126、128 の抵抗は、低いレベルに変更され、そのデータ状態は、何れも“0”状態になりうる。消去電圧は、選択された抵抗層 122、124、126、128 の数によって変わりうる。

10

#### 【0067】

この実施形態で、抵抗層 122、124、126、128 のデータは、一時に消去され、したがって、非常に速い消去速度を有しうる。

#### 【0068】

以上、本発明の特定の実施形態に関する説明は、例示及び説明を目的として提供された。本発明は、前記実施形態に限定されず、当業者によって、本発明の技術的思想の範囲内で前記実施形態を組み合わせて実施するなど、多様な修正及び変更が可能であるということは言うまでもない。

#### 【産業上の利用可能性】

#### 【0069】

本発明は、不揮発性メモリ素子関連の技術分野に好適に利用されうる。

20

#### 【図面の簡単な説明】

#### 【0070】

【図 1】本発明の一実施形態に係る不揮発性メモリ素子を示す概略的な斜視図である。

【図 2】図 1 の不揮発性メモリ素子の I II I - I II I 線による断面図である。

【図 3】本発明の一実施形態に係る不揮発性メモリ素子の抵抗層の例示的な電圧 - 電流特性を示すグラフである。

【図 4】本発明の一実施形態に係る不揮発性メモリ素子のプログラム動作を示す断面図である。

【図 5】本発明の一実施形態に係る不揮発性メモリ素子のプログラム動作を示す断面図である。

30

【図 6】本発明の一実施形態に係る不揮発性メモリ素子の読み取り動作を示す断面図である。

【図 7】本発明の一実施形態に係る不揮発性メモリ素子の読み取り動作を示す断面図である。

【図 8】本発明の他の実施形態に係る不揮発性メモリ素子の読み取り動作を示す断面図である。

【図 9】本発明の一実施形態に係る不揮発性メモリ素子の消去動作を示す断面図である。

【図 10】図 8 の不揮発性メモリ素子の読み取り動作のシミュレーション結果を示すグラフである。

40

#### 【符号の説明】

#### 【0071】

112、114、116、118 埋め込み電極

122、124、126、128 抵抗層

130 ゲート絶縁膜

132 ゲート電極

135 ブラグ

BL 1、BL 2、BL 3、BL 4 ビットライン

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

(72)発明者 朴 允童

大韓民国京畿道龍仁市器興區農書洞山14-1番地 三星綜合技術院内

(72)発明者 趙 慶來

大韓民国京畿道龍仁市器興區農書洞山14-1番地 三星綜合技術院内

(72)発明者 玄 在雄

大韓民国京畿道龍仁市器興區農書洞山14-1番地 三星綜合技術院内

(72)発明者 邊 成宰

大韓民国京畿道龍仁市器興區農書洞山14-1番地 三星綜合技術院内

F ターム(参考) 5F083 FZ10 GA01 GA05 HA10 JA21 JA35 KA01 KA05 KA11 KA17

LA02 LA12 LA16 MA06 MA20 ZA19 ZA21