RÉPUBLIQUE FRANÇAISE

INSTITUT NATIONAL

DE LA PROPRIÉTÉ INDUSTRIELLE

PARIS

(11) N° de publication :

(A n'utiliser que pour les

commandes de reproduction).

**2 498 031**

A1

**DEMANDE

DE BREVET D'INVENTION**

(21) **N° 81 00570**

(54) Convertisseur de p-codes en grandeur analogique.

(51) Classification internationale (Int. Cl.<sup>3</sup>). H 03 K 13/02, 13/32.

(22) Date de dépôt..... 14 janvier 1981.

(33) (32) (31) Priorité revendiquée :

(41) Date de la mise à la disposition du

public de la demande..... B.O.P.I. — « Listes » n° 28 du 16-7-1982.

(71) Déposant : VINITSKY POLITEKHNICHESKY INSTITUT, résidant en URSS.

(72) Invention de : A. P. Stakhov, A. D. Azarov, V. I. Moiseev, J. N. Uzhvak et V. P. Verkhovoi.

(73) Titulaire : *Idem* (71)

(74) Mandataire : Cabinet Plasseraud,

84, rue d'Amsterdam, 75009 Paris.

Convertisseur de p-codes en grandeur analogique.

La présente invention concerne le matériel électronique de calcul et de mesure et plus particulièrement les convertisseurs de p-codes en grandeur analogique.

5 On désigne, dans ce texte, par p-codes, les p-codes Fibonacci et les codes de p-proportion "d'or", comme précisé ci-après.

L'invention peut être utilisée particulièrement dans les dispositifs de mesure numérique, par exemple 10 pour la mesure de grandeurs électriques. Elle est en outre utilisable en automatique et en télémécanique pour transformer les signaux de sortie d'un organe de commande en actions de commande à appliquer aux organes d'exécution ; elle est applicable également dans le 15 domaine de la radiodétection et dans des appareils à rayons cathodiques pour commander le balayage du faisceau cathodique.

Tout convertisseur numérique analogique doit être soumis à un contrôle métrologique, car on doit s'assurer 20 que ses caractéristiques métrologiques correspondent aux valeurs de consigne. Pour effectuer un tel contrôle, on doit disposer d'un jeu étendu d'étalons dont la réalisation technique est relativement compliquée. D'autre part, le processus lui-même de contrôle 25 métrologique demande un temps considérable.

On connaît par exemple un convertisseur de p-codes en grandeur analogique qui comporte des éléments de commutation en nombre égal à celui des bits du code. La sortie de chacun des éléments de commutation est 30 reliée à l'entrée correspondante d'un additionneur de grandeurs analogiques étalons (de référence), celles-ci étant proportionnelles aux poids des bits de codes. Le convertisseur connu a pour entrée celles des éléments de commutation, sa sortie étant celle de 35 l'additionneur des grandeurs de référence.

Le convertisseur connu fonctionne comme suit.

On applique, aux entrées des éléments de commutation, les signaux correspondant aux bits du code à traduire.

A leur tour, les éléments de commutation, dont les 5 entrées ont reçu les signaux correspondant aux unités dans le code à traduire, mettent en jeu les grandeurs de référence correspondantes, dont la somme représente une grandeur analogique de sortie.

Le contrôle métrologique d'un tel convertisseur 10 revêt un caractère compliqué. Pour réaliser ce contrôle, on doit avoir un grand nombre de grandeurs de référence, difficiles à réaliser au point de vue technique. D'autre part, le convertisseur connu a une fiabilité réduite, car, en cas de défaillance métrologique, ne serait-ce que 15 d'un seul bit, il ne satisfait plus aux caractéristiques métrologiques requises (précision de la conversion, linéarité de la caractéristique de sortie, etc.).

L'invention vise à réaliser un convertisseur de p-codes en grandeur analogique qui, grâce à l'exploitation du caractère non-uniforme de la notation codée 20 d'un même nombre, permette de simplifier le contrôle métrologique et d'accroître la fiabilité.

Le problème posé est résolu à l'aide d'un convertisseur de p-codes en grandeur analogique, comportant des 25 éléments de commutation en nombre égal à celui des bits d'un code, la sortie de chacun desdits éléments de commutation étant couplée à l'entrée correspondante d'un additionneur de grandeur analogiques de référence, proportionnelles au poids des bits de code, la sortie 30 dudit additionneur étant aussi celle du convertisseur et la sortie multiple dudit additionneur étant reliée à la première entrée multiple des éléments de commutation, ledit convertisseur étant caractérisé, selon l'invention, en ce qu'il est doté d'une unité de développement de 35 code, dont la première entrée multiple sert d'entrée multiple au convertisseur et dont la sortie multiple est couplée à la seconde entrée multiple des éléments de commutation, la seconde entrée multiple de l'unité

de développement de code étant connectée à la seconde sortie multiple d'un organe de stockage de numéros des bits défaillants, la première sortie multiple dudit organe étant couplée à l'entrée multiple d'une unité de commande et à la première entrée multiple d'un organe de détermination du type de développement, la seconde entrée multiple de ce dernier étant connectée à la sortie multiple de l'unité de développement de code, la sortie de l'organe de détermination du type de développement étant connectée à la première entrée de l'unité de commande munie d'une entrée de commande et ayant sa première sortie couplée à l'entrée de commande de l'unité de développement de code, sa deuxième sortie couplée à l'entrée de commande de l'organe de stockage des numéros des bits défaillants et sa troisième sortie couplée à l'entrée de commande d'une unité de séparation de la différence des niveaux du signal de sortie, l'entrée de cette dernière étant reliée à la sortie de l'additionneur et la sortie couplée à l'entrée de l'organe de stockage des numéros des bits défaillants et à la seconde entrée de l'unité de commande.

Un tel mode de réalisation du convertisseur selon l'invention permet de simplifier son contrôle métrologique et d'accroître sa fiabilité.

D'autres caractéristiques et avantages de l'invention seront mieux compris à la lecture de la description qui va suivre et en se référant aux dessins annexés sur lesquels :

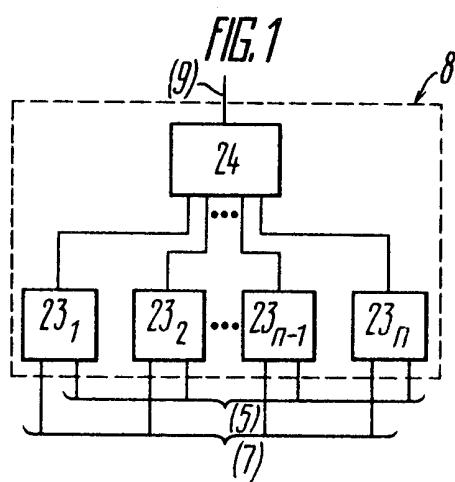

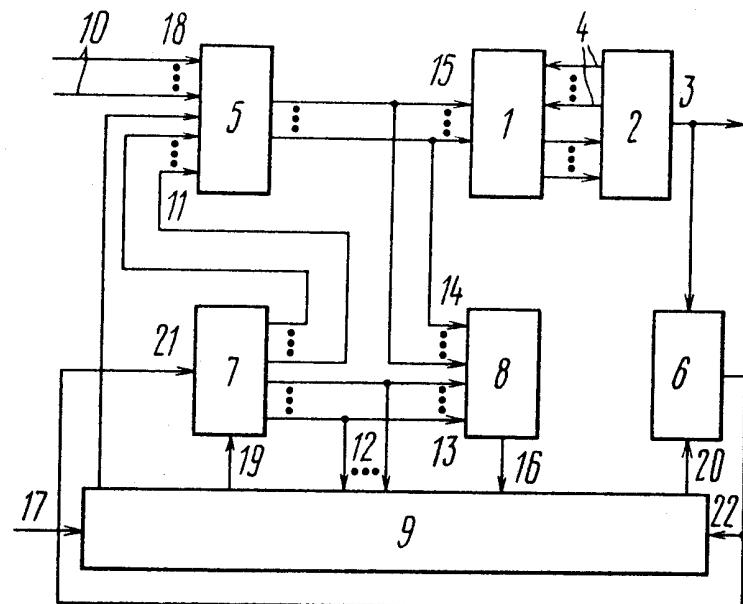

- la figure 1 représente le schéma synoptique général du convertisseur de p-codes en grandeur analogique selon l'invention ;

- la figure 2 représente un exemple de réalisation de l'organe de détermination du type de développement, selon l'invention.

Le convertisseur de p-codes en grandeurs analogiques contient des éléments de commutation 1 en nombre égal à celui des bits de code. La sortie de chacun des

éléments 1 est reliée à l'entrée correspondante d'un additionneur 2 de grandeurs de référence proportionnelles aux poids des bits du p-code.

L'additionneur 2 peut être réalisé par exemple

5 sous forme de sources de courants pondérés.

Une sortie 3 de l'additionneur 2 sert de sortie au convertisseur selon l'invention, tandis qu'une sortie multiple 4 dudit additionneur 2 est couplée à une première entrée multiple des éléments 1.

10 Selon l'invention, le convertisseur est muni d'une unité 5 de développement de code, d'une unité 6 de séparation de la différence des niveaux du signal de sortie de l'additionneur 2, d'un organe 7 de stockage des numéros des bits défaillants, d'un organe 8 de 15 détermination du type de développement et d'une unité de commande 9.

L'unité 5 de développement de code est destinée au stockage et au développement des codes d'entrée au régime de conversion directe ainsi qu'au stockage et au développement 20 des codes correspondants aux poids des bits à contrôler au régime de contrôle métrologique.

Selon le mode préféré de réalisation, l'unité 5 est un dispositif de réduction de p-codes Fibonacci à la forme minimale (voir brevet britannique n° 1 543 302).

25 Une première entrée multiple 10 de l'unité 5 sert d'entrée multiple au convertisseur selon l'invention.

Une seconde entrée multiple 11 de l'unité 5 est connectée à la seconde sortie multiple de l'organe 7.

30 Selon un mode d'exécution, l'organe 7 est un registre assurant le stockage des numéros des bits défaillants.

Il convient de noter que la défaillance d'un bit peut être de deux sortes.

Premièrement, lorsque la grandeur de référence ne 35 peut pas être utilisée complètement pour former la grande analogique de sortie, il y a défaillance du type de "non mise en jeu" (défaillance cataleptique).

Deuxièmement, lorsque la grandeur de référence qui forme le signal analogique de sortie n'est pas proportionnelle au poids du bit de code, il y a défaillance du type de "déréglage" (défaillance paramétrique).

5 La première sortie multiple de l'organe 7 est connectée à une entrée multiple 12 de l'unité 9 et à une première entrée multiple 13 de l'organe 8, une seconde entrée multiple 14 de cet organe étant couplée à la sortie multiple de l'unité 5, celle-ci étant en outre

10 reliée à une seconde entrée multiple 15 des éléments 1.

La sortie de l'organe 8 est connectée à une première entrée 16 de l'unité 9.

L'unité 9 possède en outre une entrée de commande 17 à laquelle un organe de commande extérieur (non représenté) envoie des signaux de changement du régime du travail du convertisseur, objet de l'invention.

15

La première sortie de l'unité 9 est couplée à une entrée de commande 18 de l'unité 5, sa seconde sortie est connectée à une entrée de commande 19 de l'organe 7, sa

20 troisième sortie est couplée à une entrée de commande 20 de l'unité 6, cette dernière ayant son entrée réunie à la sortie 3 et sa sortie reliée à une entrée 21 de l'organe 7 et à une seconde entrée 22 de l'unité 9.

De cette manière, l'unité de commande 9 dont les

25 entrées sont attaquées par des signaux de changement du régime du travail du convertisseur et par des signaux annonçant la présence de bits défaillants au régime de conversion directe, de même qu'au régime de contrôle métrologique, permet d'obtenir l'interaction voulue des

30 unités 5, 6 et 7 au régime désiré de travail.

L'unité 6, dont le signal de sortie annonce la présence de bits défaillants, peut être constituée par un amplificateur différentiel. L'organe 8, qui permet de déterminer le type de développement réalisé par l'unité 5

35 sur un signal venant de l'organe 7, peut avoir la forme d'un circuit logique combinatoire, par exemple pareil à celui représenté à la figure 2.

A titre d'exemple, l'organe 8 comprend des circuits logiques "ET" 23 en nombre égal à celui des bits de code ("n"), une sortie 24 de chacun des circuits 23 étant couplée à l'entrée correspondante 5 d'un circuit "OU" 25 dont la sortie est celle de l'organe 8. Les premières entrées des circuits 23 constituent la première entrée multiple 13 de l'organe 8, tandis que les secondes entrées constituent la seconde entrée multiple 14 dudit organe 8.

10 Le convertisseur, objet de l'invention, fonctionne à deux régimes, à savoir : le régime de contrôle métrologique et le régime de conversion directe du p-code en grandeur analogique, le premier devant précéder le second et le changement de régime s'opérant sur l'instruction appliquée à l'entrée de commande 16.

15 Comme on l'a déjà dit, on entend par p-codes les p-codes Fibonacci et les codes de p-proportion "d'or".

On appelle p-code Fibonacci la notation de tout nombre naturel N sous forme de :

$$20 \quad N = \sum_{i=0}^n a_i \varphi_p(i) , \quad (1)$$

pour :  $a_i \in \{0,1\}$

$\varphi_p(i)$  - poids de l'i-ème bit ou l'i-ème p-nombre Fibonacci à calculer comme suit :

$$25 \quad \varphi_p(i) \begin{cases} 0 & \text{avec } i < 0 \\ 1 & \text{avec } i = 0 \\ \varphi_p(i-1) + \varphi_p(i-p-1) & \text{avec } i > 0 \end{cases} \quad (2)$$

On appelle code de p-proportion "d'or" la notation 30 de tout nombre réel D sous forme de :

$$+ \infty$$

$$D = \sum a_i \alpha_p^i \quad (3)$$

pour  $a_i \in \{0,1\}$

35  $\alpha_p^i$  - poids de e'i-ème bit

$$\alpha_p^i = \alpha_p^{i-1} + \alpha_p^{i-p-1}$$

$a_p^i$  se présente en relation suivante

$$a_p^i = a_p^{i-1} + a_p^{i-p-1} \quad (4)$$

Il existe beaucoup de notations d'un même nombre sous forme (1) et (3), parmi lesquelles il y en a une dans 5 laquelle, à droite de chaque unité, on a au moins p zéros. Une telle forme de notation s'appelle minimale. Le passage de la forme minimale à toute autre forme de représentation du p-code est effectué en accomplissant l'opération de développement du code basée sur les 10 relations (2) et (4). L'opération de développement consiste à remplacer l'unité de l'i-ème bit par les unités dans les bits (i-1) et (i-p-1) si ces derniers contiennent des zéros. L'opération en question a ceci de particulier qu'elle ne modifie pas la valeur du 15 nombre présenté par le code mais seulement la forme du code. L'opération d'analyse est désignée : /↑↑.

Le contrôle métrologique du convertisseur de p-codes en grandeur analogique est effectué en se basant sur la vérification des rapports principaux entre les 20 poids des bits de ce convertisseur qui seront les suivants par exemple pour p=1 :

$$x_e = x_{1-1} + x_{1-2} \quad (5)$$

$$25 \quad x_1 = \sum_{i=0}^{1-2} x_i + x'_{\circ} \quad (6)$$

pour  $x'_{\circ}$  - bit supplémentaire égal en poids au bit inférieur.

$$x_1 = x_{1-1} + x_{1-3} + x_{1-4} \quad (7)$$

En vertu des relations (5, 6, 7) on fait subir aux 30 bits du convertisseur selon l'invention les opérations de développement respectivement des types I, II et III consistant à remplacer l'unité du 1-ème bit par les unités dans les bits de la partie droite des égalités (5), (6), (7).

35 Dans le cas où p=1, le contrôle métrologique se fait comme suit.

Sur ordre de l'unité de commande 9 une unité est inscrite au bit supérieur de l'unité de développement de code 5. Un signal venant de l'unité 9 déclenche l'opération de développement du type I à faire subir à cette 5 unité.

Au cas où il y aurait des bits défaillants, la relation (5) pour ces bits n'est pas remplie et l'unité 6 produit un signal qui est envoyé à l'organe 7 et à l'unité 9. L'unité 7 inscrit chaque fois les 10 unités aux deux bits supérieurs qui participent au développement durant lequel a eu lieu la mise en jeu de l'unité 6 de séparation de la différence des niveaux des signaux de sortie du convertisseur.

Après chaque cas de fonctionnement déclenché par 15 le signal provenant de l'unité 9, l'unité 6 est remise à sa position de départ. Si, au cours de l'exécution du développement, l'unité 6 n'a pas fonctionné une seule fois, l'unité de commande 9, se basant sur les signaux arrivant à l'entrée 12, produit un signal annonçant la 20 fin du contrôle métrologique. Le développement du type I terminé, l'unité 9 délivre un signal en réponse duquel l'organe 7 transfère à l'unité 5 l'inscription de l'unité au k-ème bit, à savoir le bit inférieur des bits supposés défaillants. Sur l'ordre fourni par 25 l'unité 9, on fait subir à cette unité l'opération de développement du type I. S'il y a une réponse de l'unité 6, l'organe 7 enregistre le numéro de ce bit comme un cas de défaillance sous forme de l'unité au k-ème bit. L'unité 5 inscrit l'unité au (k+1)-ème bit et l'organe 8 30 délivre un signal qui autorise le développement du type II. Si, au cours du développement de la k-ème unité, l'unité 6 n'a pas répondu, l'organe 7 n'enregistre pas le numéro de ce bit. Ensuite, sur ordre de l'unité 9, il se produit le développement de l'unité inscrite au 35 (k+1)-ème bit de l'unité 5. Le type du développement à entreprendre est déterminé par l'organe 8. Si, au cours du développement de l'unité inscrite au (k+1)ème bit de

l'unité 5, l'unité 6 a répondu, le numéro de ce bit est enregistré par l'organe 7 en tant que numéro du bit défaillant.

Le choix du type de développement que l'organe 8

5 de détermination du type de développement réalise tout au long du contrôle métrologique est déterminé par l'état de l'organe 7.

Le contrôle métrologique des bits supposés défaillants qui restent se fait de manière analogue.

10 Le contrôle du convertisseur proposé se fait avec la "précision" de un bit si chaque groupe constitué de  $m(1 \leq m \leq p)$  bits défaillants successifs est précédé d'au moins  $(k+1)$  bits supérieurs en bon état, encore que, si le bit supérieur dans le groupe des bits défaillants est 15 en même temps le bit supérieur du convertisseur, selon l'invention, cette condition est superflue. Dans d'autres cas, le contrôle est effectué avec la "précision" de deux et trois bits, à l'exception du  $(p+1)$ -ème bit inférieur parmi les bits défaillants dont les numéros 20 sont toujours déterminés avec la "précision" de un bit.

Ci-après est donné un exemple de contrôle métrologique du convertisseur proposé à sept bits, les poids des bits étant proportionnels à  $p=1$  (nombre Fibonacci), avec les premier et quatrième bits défaillants (voir 25 tableau 1).

Tableau 1

| Temps | Etat de l'organe 7 |   |   |    |    |    |          | Type | Etat de l'organe 7 |   |   |   |   |   |   | Signal de fin de dé- | Signal de fin de dé- |   |   |   |   |         |

|-------|--------------------|---|---|----|----|----|----------|------|--------------------|---|---|---|---|---|---|----------------------|----------------------|---|---|---|---|---------|

|       | 1                  | 2 | 3 | 4  | 5  | 6  | 7 étalon |      | 1                  | 2 | 3 | 4 | 5 | 6 | 7 |                      |                      |   |   |   |   |         |

|       | poids des bits     |   |   |    |    |    |          |      |                    |   |   |   |   |   |   |                      |                      |   |   |   |   | contrô- |

|       | 13                 | 8 | 5 | 3  | 2  | 1  | 1        |      |                    |   |   |   |   |   |   |                      |                      |   |   |   |   | le      |

| 1     | 0                  | 0 | 0 | 0  | 0  | 0  | 0        |      | 0                  | 0 | 0 | 0 | 0 | 0 | 0 |                      | 0                    | 0 | 0 | 0 | 0 | 0       |

| 2     | 1                  | 0 | 0 | 0  | 0  | 0  | 0        |      | 1                  | 1 | 0 | 0 | 0 | 0 | 0 |                      | 0                    | 0 | 0 | 0 | 0 | 0       |

| 3     | 0                  | 1 | 1 | 0  | 0  | 0  | 0        |      | 1                  | 1 | 1 | 1 | 0 | 0 | 0 |                      | 0                    | 0 | 0 | 0 | 0 | 0       |

| 4     | 0                  | 0 | 1 | 0  | 1  | 1  | 0        |      | 0                  | 1 | 1 | 1 | 1 | 0 | 0 |                      | 1                    | 1 | 1 | 1 | 0 | 0       |

| 5     | 0                  | 0 | 0 | 1  | 0  | 1  | 0        |      | 0                  | 0 | 1 | 1 | 1 | 1 | 0 |                      | 0                    | 0 | 0 | 0 | 0 | 0       |

| 6     | 7                  | 8 | 9 | 10 | 11 | 12 | 13       |      | 1                  | 0 | 0 | 0 | 0 | 0 | 0 |                      | 1                    | 1 | 1 | 1 | 0 | 0       |

| 7     | 0                  | 0 | 0 | 1  | 0  | 1  | 0        |      | 0                  | 0 | 1 | 0 | 0 | 0 | 0 |                      | 0                    | 0 | 0 | 0 | 0 | 0       |

| 8     | 0                  | 0 | 0 | 0  | 1  | 0  | 1        |      | 0                  | 0 | 0 | 1 | 0 | 0 | 0 |                      | 1                    | 0 | 0 | 1 | 0 | 0       |

| 9     | 0                  | 0 | 0 | 0  | 0  | 1  | 0        |      | 0                  | 0 | 0 | 0 | 1 | 0 | 0 |                      | 0                    | 0 | 0 | 0 | 1 | 0       |

| 10    | 0                  | 0 | 0 | 0  | 0  | 0  | 1        |      | 0                  | 0 | 0 | 0 | 0 | 1 | 0 |                      | 0                    | 0 | 0 | 0 | 0 | 1       |

| 11    | 0                  | 0 | 0 | 0  | 0  | 0  | 0        |      | 0                  | 0 | 0 | 0 | 0 | 0 | 1 |                      | 0                    | 0 | 0 | 0 | 0 | 0       |

| 12    | 0                  | 0 | 0 | 0  | 0  | 0  | 0        |      | 0                  | 0 | 0 | 0 | 0 | 0 | 0 |                      | 1                    | 0 | 0 | 0 | 0 | 0       |

| 13    | 0                  | 0 | 0 | 0  | 0  | 0  | 0        |      | 0                  | 0 | 0 | 0 | 0 | 0 | 0 |                      | 1                    | 0 | 0 | 1 | 0 | 0       |

| 14    | 0                  | 0 | 0 | 0  | 0  | 0  | 0        |      | 0                  | 0 | 0 | 0 | 0 | 0 | 0 |                      | 1                    | 0 | 0 | 0 | 0 | 0       |

Le contrôle métrologique d'un tel convertisseur se fait avec la "précision" de un bit.

Le convertisseur selon l'invention mis au régime de conversion directe du p-code en grandeur analogique 5 fonctionne comme suit.

L'unité de commande 9 interdit le fonctionnement de l'unité 6 et autorise le travail de l'organe 7, de l'organe 8 et de l'unité 5.

- Le convertisseur n'ayant pas de bits défaillants,

- 10 l'unité 9 interdit l'opération de développement dans l'unité 5 ce qui fait que le code numérique de départ, consigné sous la forme minimale, une fois appliqué à l'entrée 10, est traduit en équivalent analogique par une méthode connue.

- 15 Si le contrôle métrologique a révélé des bits défaillants, l'organe 7 envoie des signaux à l'organe 8, ce dernier formant un signal qui autorise le développement des unités du code de départ dans les bits dont les numéros coïncident avec ceux des bits défaillants

- 20 enregistrés dans l'organe 7. Le convertisseur selon l'invention réalise une conversion correcte d'une grandeur numérique en équivalent analogique si chaque groupe constitué de  $m(1 \leq m \leq p)$  bits défaillants qui se succèdent est suivi d'au moins  $m+1$  bits inférieurs

- 25 en bon état ou bien s'il n'y a pas plus d'un seul groupe constitué de  $m(m=p)$  rangs défaillants.

Dans le cas général, la condition suivante est à satisfaire :

$$S_n - S_n^* \geq S_p$$

30 pour  $S_n$  = somme de tous les poids du convertisseur à n bits

$S_n^*$  = somme de tous les poids de la combinaison de code maximale

$S_p$  = somme des poids de tous les bits défaillants.

35 Le tableau 2 ci-après donne un exemple de conversion du code de départ  $p=1$  Fibonacci en équivalent analogique à l'aide d'un convertisseur à huit bits, avec

le 1<sup>er</sup> bit défaillant.

Tableau 2

| 5  | Code de départ   |    |   |   |   |   |   |   | Etat de l'unité 6 | Signal de fin d'analyse |  |  |

|----|------------------|----|---|---|---|---|---|---|-------------------|-------------------------|--|--|

|    | Numéros des bits |    |   |   |   |   |   |   |                   |                         |  |  |

|    | 1                | 2  | 3 | 4 | 5 | 6 | 7 | 8 |                   |                         |  |  |

|    | 21               | 13 | 8 | 5 | 3 | 2 | 1 | 1 | Poids des bits    |                         |  |  |

| 10 | 1                | 0  | 1 | 0 | 1 | 0 | 0 | 1 | 33                | 1 0 0 0 0 0 0 0 0       |  |  |

| 15 | 0                | 1  | 1 | 1 | 1 | 1 | 1 | 1 | 33                | 1 0 0 0 0 0 0 0 1       |  |  |

Dans un tel convertisseur, la défaillance d'un bit n'affecte pas la conversion correcte du code de départ en équivalent analogique.

20 Le fait d'introduire de nouvelles unités et liaisons accroît le pouvoir discriminateur du contrôle métrologique à un bit près, sans parler de l'augmentation de la fiabilité qui consiste en conversion correcte du code de départ en équivalent analogique en cas de défaillance (du type "non-mise en jeu") de pas plus de q bits.. On y parvient en substituant à la combinaison codée minimale de départ une combinaison équivalente au moyen de développements.

La combinaison codée équivalente ne contient pas 30 d'unités dans les bits défaillants, ce qui permet d'obtenir une grandeur analogique correcte à partir du code de départ.

Cette dernière circonstance permet d'accroître 35 le pourcentage de production dans la fabrication en série d'appareils convertisseurs numériques/analogiques sous forme de grands circuits intégrés en faisant figurer dans la quantité des produits finis les

convertisseurs n'ayant pas plus de q bits défaillants.

Le convertisseur qui vient d'être décrit peut être utilisé en particulier pour les dispositifs de mesure numérique. Il est, d'autre part, applicable en 5 automatique et en télémechanique pour transformer les signaux délivrés par des organes de commande en actions de commande à appliquer aux organes asservis, ainsi que dans la radiodétection pour commander le balayage du faisceau électronique.

10 Bien entendu, l'invention n'est nullement limitée aux modes de réalisation décrits et représentés qui n'ont été donnés qu'à titre d'exemple. En particulier, elle comprend tous les moyens constituant des équivalents techniques des moyens décrits, ainsi que leurs combinaisons, si celles-ci sont exécutées suivant son esprit et 15 mises en oeuvre dans le cadre de la revendication ci-après.

## REVENDICATION

Convertisseur de p-codes en grandeur analogique, comportant des éléments de commutation en nombre égal à celui des bits de code, la sortie de chacun desdits élément 5 éléments couplée à l'entrée correspondante d'un additionneur de grandeurs analogiques de référence, proportionnelles aux poids des bits de code, la sortie dudit additionneur étant aussi celle du convertisseur et la sortie multiple dudit additionneur étant reliée à 10 la première entrée multiple desdits éléments de commutation, caractérisé en ce qu'il est doté d'une unité de développement de code, dont la première entrée multiple sert d'entrée multiple audit convertisseur et dont la sortie multiple est couplée à la seconde entrée 15 multiple des éléments de commutation, la seconde entrée multiple de l'unité de développement code étant connectée à la seconde sortie multiple d'un organe de stockage des numéros des bits défaillants, la première sortie multiple dudit organe étant couplée à l'entrée multiple d'une 20 unité de commande et à la première entrée multiple d'un organe de détermination du type de développement, la seconde entrée multiple de ce dernier étant connectée à la sortie multiple de l'unité de développement de code, la sortie de l'organe de détermination du type de 25 développement étant connectée à la première entrée de l'unité de commande munie d'une entrée de commande et ayant sa première sortie couplée à l'entrée de commande de l'unité de développement de code, sa deuxième sortie couplée à l'entrée de commande de l'organe de stockage 30 des numéros des bits défaillants et sa troisième sortie couplée à l'entrée de commande d'une unité de séparation de la différence des niveaux du signal de sortie, l'entrée de cette dernière étant reliée à la sortie de l'additionneur et la sortie couplée à l'entrée de l'organe de stockage des numéros des bits défaillants et à la seconde 35 entrée de l'unité de commande.

*FIG. 2*