(12)

DEMANDE DE BREVET D'INVENTION

A1

(22) Date de dépôt : 02.12.02.

(30) Priorité : 25.04.02 JP 02124180.

(71) Demandeur(s) : MITSUBISHI DENKI KABUSHIKI

KAISHA — JP.

(43) Date de mise à la disposition du public de la

demande : 31.10.03 Bulletin 03/44.

(72) Inventeur(s) : MAEDA SHIGENOBU, MATSUMOTO

TAKUJI, IWAMATSU TOSHIAKI et IPPOSHI TAKASHI.

(56) Liste des documents cités dans le rapport de

recherche préliminaire : Ce dernier n'a pas été

établi à la date de publication de la demande.

(60) Références à d'autres documents nationaux

apparentés :

(73) Titulaire(s) :

(74) Mandataire(s) : CABINET PLASSERAUD.

(54) DISPOSITIF A SEMICONDUCTEUR ET PROCEDE DE FABRICATION.

(57) Un transistor MOS formé sur une couche SOI (3) com-

porte une pellicule isolante de grille qui comprend une pre-

mière partie (11) et une seconde partie (110) dont

l'épaisseur est supérieure à celle de la première partie. La

seconde partie (110) de la pellicule isolante de grille est for-

mée au moins sous une plage de contact de grille consistant

en un agrandissement de l'électrode de grille (12) dans la

direction de la longueur de grille. Une partie de contact de

corps (BD) est formée dans la surface de la couche SOI (3)

au-delà de l'extrémité de la plage de contact de grille, dans

la direction de la largeur de grille.

## DISPOSITIF A SEMICONDUCTEUR ET PROCEDE DE FABRICATION

La présente invention concerne un dispositif à semiconducteur, et plus particulièrement un procédé de fabrication d'un dispositif à semiconducteur ayant une pellicule d'isolation par tranchée.

5 Un dispositif à semiconducteur (qu'on appellera ci-après un dispositif SOI) ayant une structure SOI formée sur un substrat SOI dans laquelle une pellicule d'oxyde enterrée et une couche "silicium sur isolant" ou SOI (Silicon On Insulator) sont formées sur un substrat en silicium, peut réduire une capacité parasite et est caractérisé par un fonctionnement rapide et stable et une faible consommation de puissance, et il est donc utilisé pour un équipement portable ou similaire.

10 A titre d'exemple, un dispositif SOI a une structure d'isolation par tranchée parfaite (ou FTI pour "full trench isolation") pour isoler électriquement des éléments par une pellicule d'isolation par tranchée parfaite formée en incorporant dans une surface d'une couche SOI une tranchée atteignant une pellicule d'oxyde enterrée, et en enterrant une matière isolante dans la tranchée. Cependant, des porteurs (des trous dans une structure NMOS) générés par un phénomène 15 d'ionisation par chocs s'accumulent dans une région de formation de canal. Par conséquent, divers problèmes apparaissent à cause d'un effet de flottement du substrat; par exemple, il apparaît une non-linéarité d'une caractéristique et une tension de claquage en fonctionnement est dégradée, et en outre un potentiel électrique de la 20 région de formation de canal n'est pas stabilisé, ce qui fait apparaître une dépendance d'un temps de retard vis-à-vis de la fréquence.

25 De ce fait, on a conçu une structure d'isolation par tranchée partielle (ou PTI pour "partial trench isolation") en incorporant une

tranchée dans une surface d'une couche SOI de façon à laisser à la couche SOI une épaisseur prédéterminée entre une partie de fond de la tranchée et une pellicule d'oxyde enterrée, et en enterrant une matière isolante dans la tranchée.

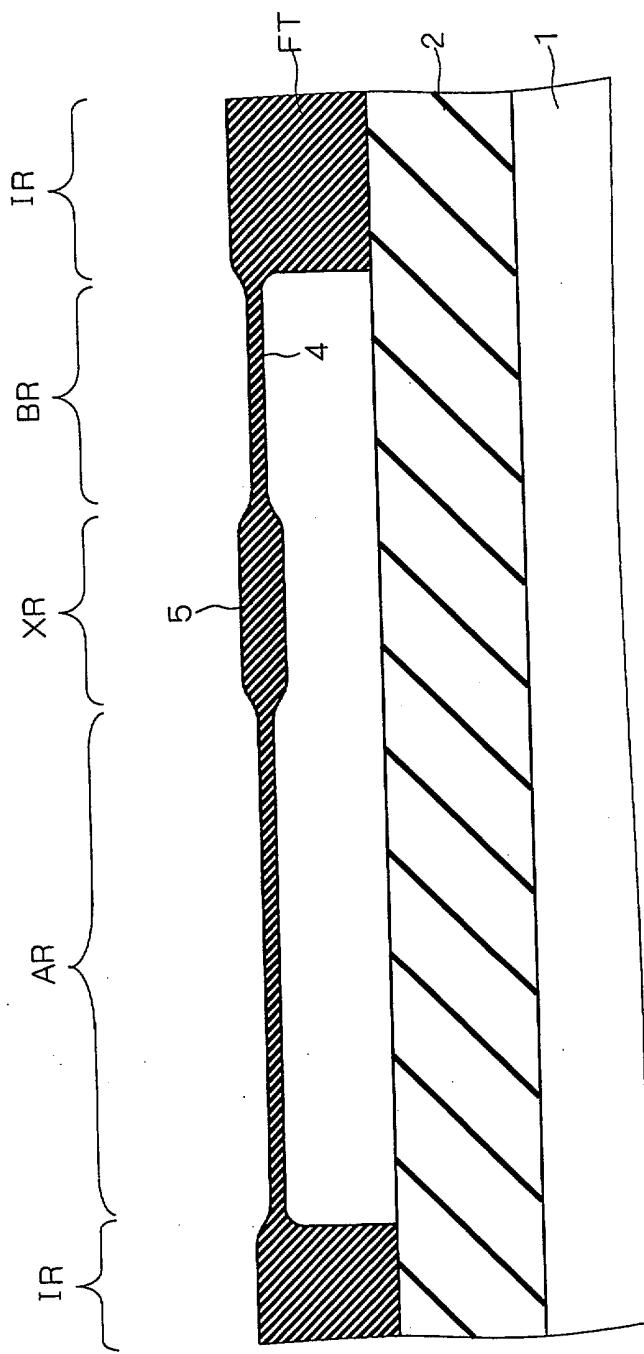

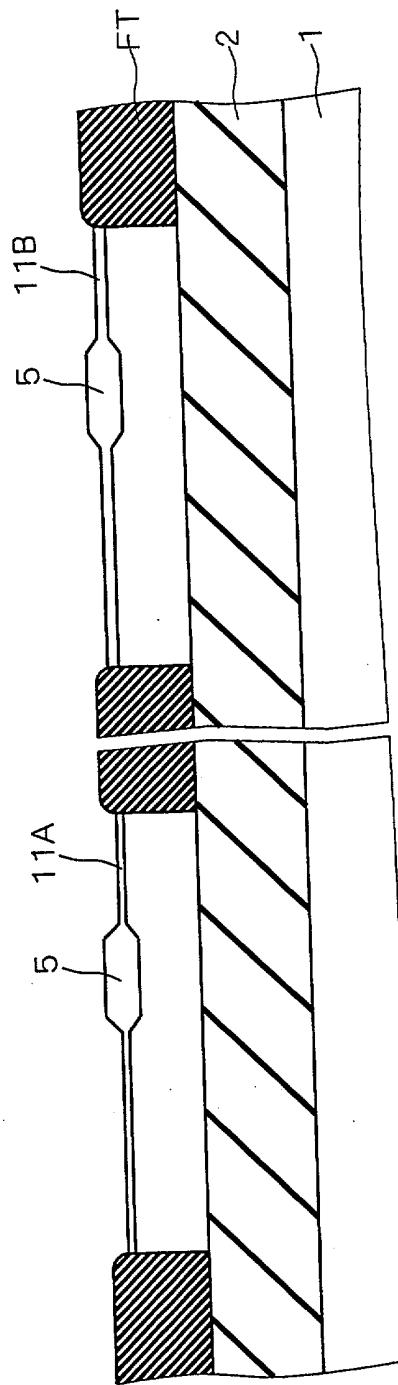

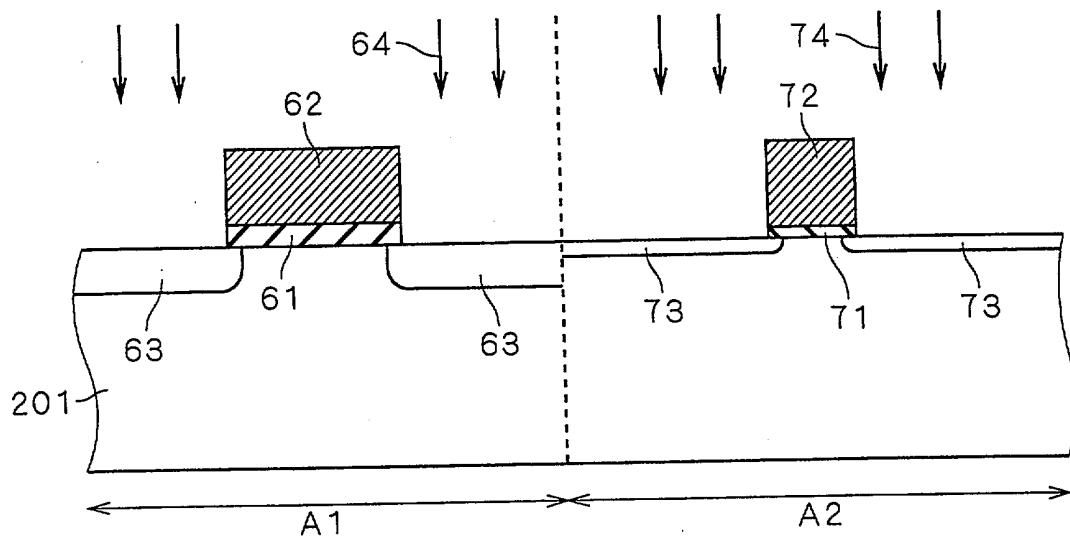

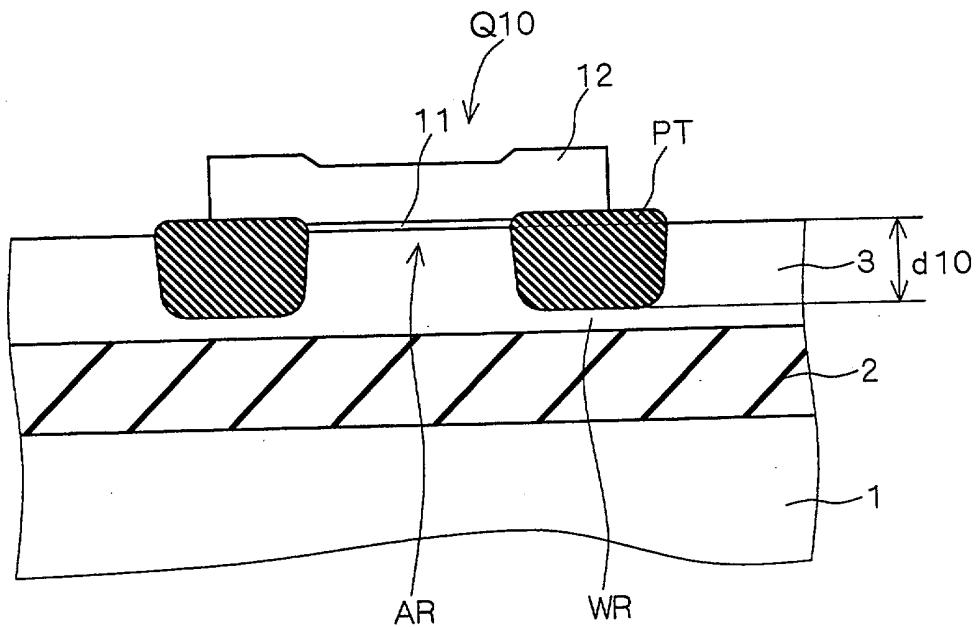

5 La figure 74 montre une structure en coupe d'un transistor MOS Q10 ayant la structure PTI. La figure 74 illustre une structure en coupe dans une direction d'une largeur de grille du transistor MOS Q10.

10 Comme représenté sur la figure 74, une pellicule d'oxyde d'isolation partielle PT est formée dans une surface d'une couche SOI 3 d'un substrat SOI constitué d'un substrat en silicium 1, d'une pellicule d'oxyde enterrée 2 et de la couche SOI 3, et une pellicule d'oxyde de grille 11 et une électrode de grille 12 sont formées séquentiellement sur une région active AR définie par la pellicule 15 d'oxyde d'isolation partielle PT.

La couche SOI 3 est présente entre une partie inférieure de la pellicule d'oxyde d'isolation partielle PT et la pellicule d'oxyde enterrée 2 pour former une région de caisson WR, et des porteurs peuvent circuler à travers la région de caisson WR et on peut empêcher 20 leur accumulation dans une région de formation de canal, et en outre un potentiel électrique de la région de formation de canal peut être fixé par l'intermédiaire de la région de caisson WR (fixation du potentiel de corps). Il y a donc un avantage consistant en ce que divers problèmes ne se manifestent pas à cause de l'effet de flottement 25 du substrat.

Cependant, dans la structure PTI, une profondeur de la pellicule d'oxyde d'isolation partielle PT est définie principalement par gravure pendant la formation d'une tranchée, et elle varie également dans la même tranche ou entre des tranches différentes, à cause 30 d'une variation dans la gravure.

Comme représenté sur la figure 74, la profondeur de la pellicule d'oxyde d'isolation partielle PT est définie comme une profondeur d10 à partir d'une surface principale de la couche SOI 3 jusqu'à une partie inférieure. Par exemple, dans le cas où on fixe comme 35 une valeur nominale  $d10 = 100$  nm, la profondeur de la pellicule

d'oxyde d'isolation partielle PT qui est réellement formée est fixée à  $d_{10} = 100 \text{ nm} \pm 5 \text{ nm}$  et elle varie dans une plage de 95 à 105 nm.

Ce qui précède implique qu'une épaisseur de la région de caisson WR dans une partie inférieure de la pellicule d'oxyde d'isolation partielle PT varie dans une plage de 45 à 55 nm si une épaisseur de la couche SOI 3 est fixée approximativement à 150 nm. Si la valeur nominale de la région de caisson WR est fixée à 50 nm, la variation équivaut à  $\pm 10\%$ .

On décrira davantage en référence aux figures 75 et 76 la 10 gravure qui doit être effectuée au moment de la formation de la tranchée dans la pellicule d'oxyde d'isolation partielle PT.

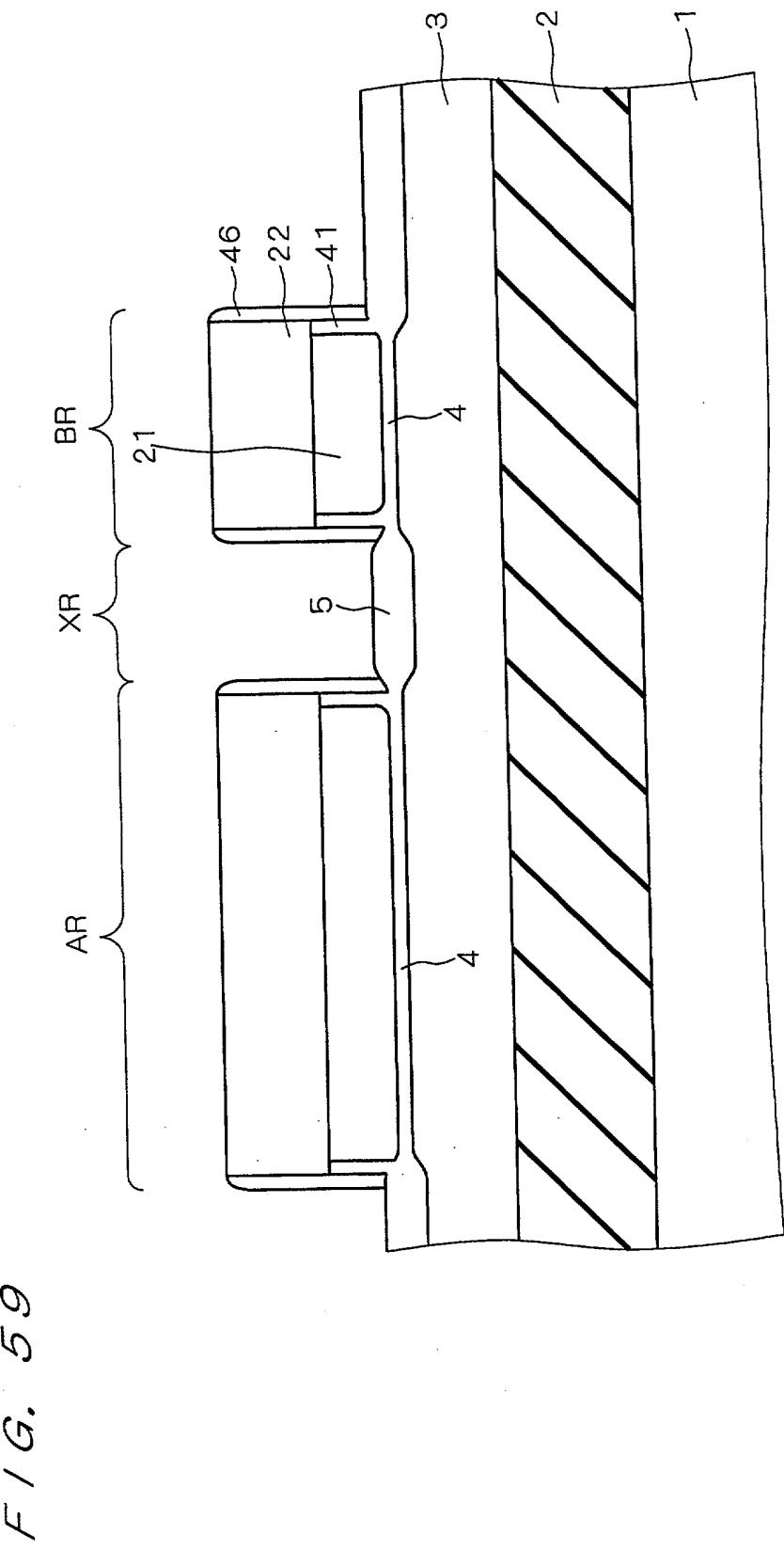

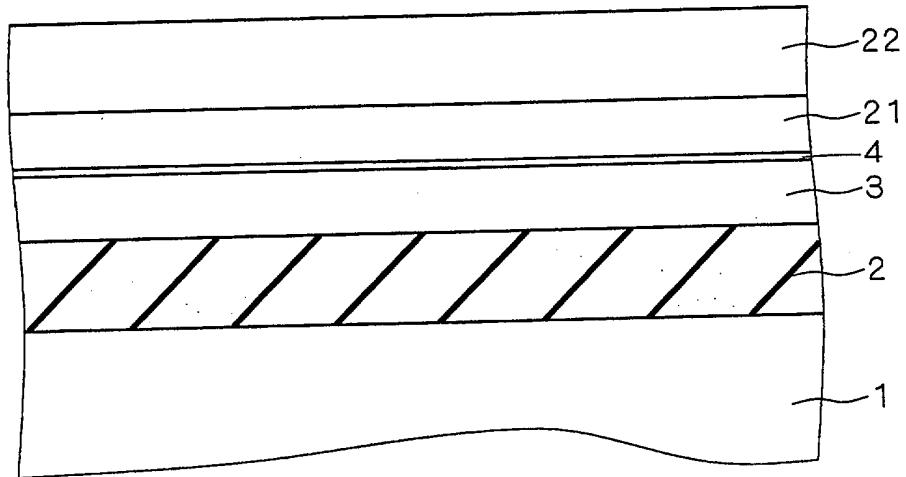

Comme représenté sur la figure 75, en premier lieu, on prépare un substrat SOI et on forme une pellicule d'oxyde 4 sur la couche SOI 3 du substrat SOI.

15 Ensuite, on forme une pellicule de silicium polycristallin 21 sur la pellicule d'oxyde 4 par un procédé de dépôt chimique en phase vapeur ou CVD (Chemical Vapor Deposition), et on forme une pellicule de nitre 22 sur la pellicule de silicium polycristallin 21, par le procédé CVD. La pellicule d'oxyde 4, la pellicule de silicium 20 polycristallin 21 et la pellicule de nitre 22 sont également appelées des pellicules auxiliaires, du fait qu'elles remplissent une fonction auxiliaire pour former une pellicule d'oxyde d'isolation.

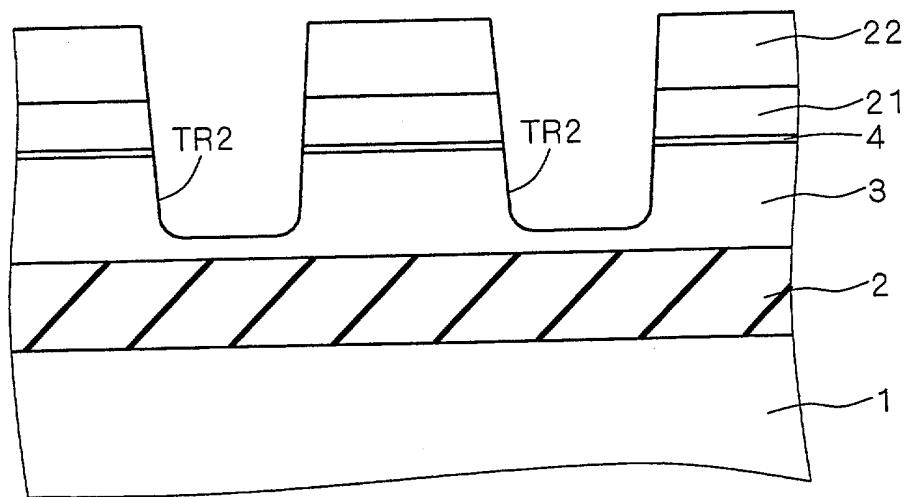

25 Comme représenté sur la figure 76, on enlève ensuite sélectivement la pellicule de nitre 22 et la pellicule de silicium polycristallin 21 par gravure par voie sèche ou gravure par voie humide en utilisant un masque de matière de réserve (non représenté) ayant un motif d'ouverture prédéterminé.

30 En outre, en utilisant en tant que masque de gravure la pellicule de nitre 22 dans laquelle on a défini un motif, on traverse la pellicule d'oxyde 4 et on grave la couche SOI 3 jusqu'à une profondeur prédéterminée pour former une tranchée TR. Dans la gravure, on règle les conditions de gravure de façon que la couche SOI 3 ne soit pas complètement enlevée au point de mettre à nu la pellicule d'oxyde enterrée 2, mais la couche SOI 3 ayant une épaisseur prédéterminée reste dans une partie de fond de la tranchée TR.

Une étendue totale de gravure de la pellicule de nitrure 22, de la pellicule de silicium polycristallin 21, de la pellicule d'oxyde 4 et de la couche SOI 3 est de 200 à 400 nm. Même si une profondeur de la pellicule d'oxyde d'isolation partielle PT est fixée de façon à être faible, par exemple environ 50 nm, l'étendue totale de gravure est de 150 à 350 nm. Par conséquent, l'étendue totale de gravure n'est pas fortement changée. Il en résulte qu'une variation n'est pas fortement changée.

Pour cette raison, dans le cas dans lequel une profondeur de la tranchée TR est fixée à 50 nm pour la couche SOI 3 ayant une épaisseur de 70 nm, l'épaisseur de la région de caisson WR dans la partie inférieure de la pellicule d'oxyde d'isolation partielle PT varie dans une plage d'environ  $\pm$  5 nm. Si la valeur nominale de l'épaisseur de la région de caisson WR est fixée à 20 nm, une variation équivaut à  $\pm$  25%, ce qui ne peut pas être admis. La variation est encore augmentée sous l'effet d'une réduction de l'épaisseur de la couche SOI 3, ce qui fait que la fixation de potentiel de corps de la structure PTI est fortement limitée. Par conséquent, dans la couche SOI mince, il est difficile de former une pellicule d'oxyde d'isolation partielle et il est difficile d'effectuer la fixation de potentiel de corps par la structure PTI.

A titre de procédé pour effectuer la fixation de potentiel de corps autrement qu'avec la fixation de potentiel de corps utilisant la structure PTI, il a en outre été proposé une structure dans laquelle une forme en plan d'une électrode de grille est changée, ou bien on prend en considération une position dans laquelle une partie de contact de corps pour la fixation de potentiel de corps doit être formée.

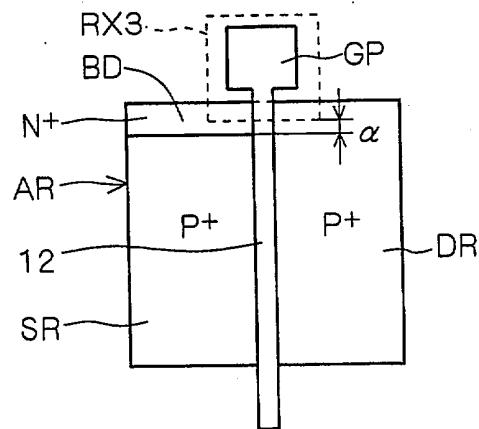

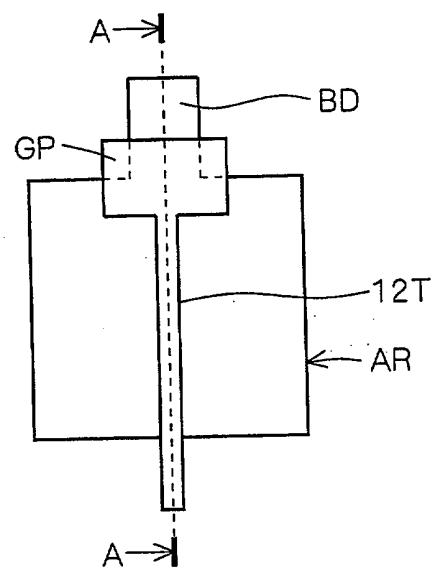

La figure 77 est une configuration en plan d'une électrode de grille qu'on appelle une grille de type T, illustrant une électrode de grille 12T dans laquelle l'une des extrémités dans une direction d'une largeur de grille est fortement agrandie dans une direction d'une longueur de grille, pour constituer une plage de contact de grille GP et qui a une forme en "T", vue en plan.

Une partie de contact de corps BD est formée à l'extérieur

d'un bout d'une partie de tête de la forme en "T" dans l'électrode de grille 12T. Une région d'impureté ayant un type de conductivité inverse de celui d'une région de source-drain est formée dans une surface de la couche SOI 3 dans la partie de contact de corps BD.

5 En outre, une région active AR incluant la région de source-drain, et la partie de contact de corps BD sont formées en continuité.

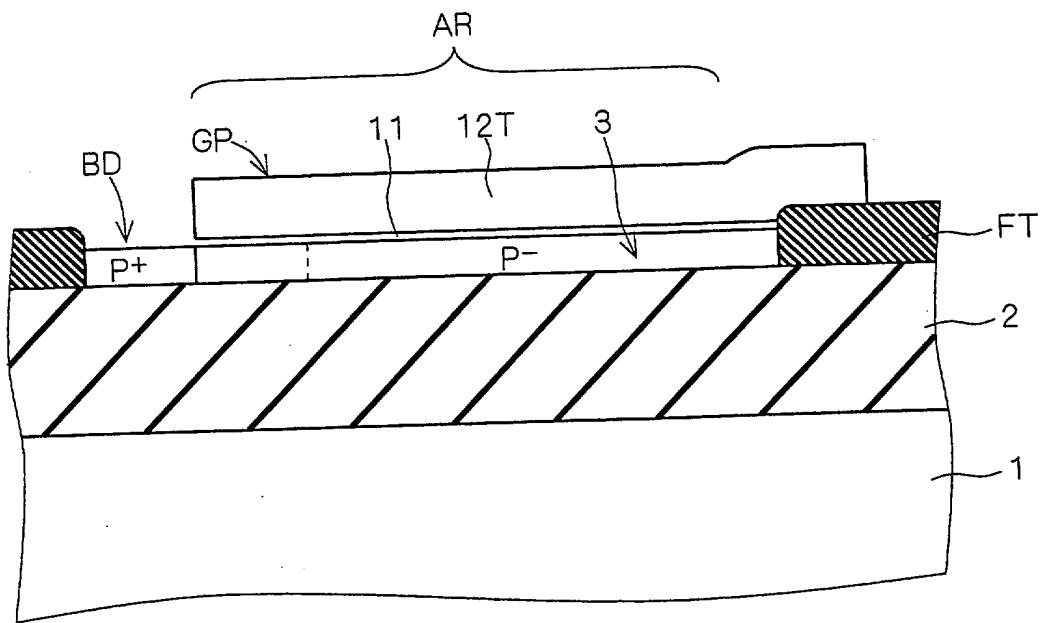

La figure 78 montre une structure d'une coupe selon une ligne A-A sur la figure 77. Comme représenté sur la figure 78, dans le cas dans lequel un transistor MOS a un type de conductivité N, la couche SOI 3 formée sous l'électrode de grille 12T contient une impureté de type P avec une concentration relativement faible ( $P^-$ ), tandis que la partie de contact de corps BD contient l'impureté de type P avec une concentration relativement élevée ( $P^+$ ). La région active AR et la partie de contact de corps BD sont définies par une pellicule d'oxyde d'isolation par tranchée parfaite FT.

10 En employant une telle structure, la région active AR est définie par la pellicule d'oxyde d'isolation par tranchée parfaite FT. Par conséquent, une variation de la profondeur de la tranchée ne se produit pas, ce qui fait qu'une réduction de l'épaisseur de la couche SOI 3 n'occasionne aucun problème. En outre, le potentiel électrique de la région de formation de canal peut être fixé par l'intermédiaire de la partie de contact de corps BD, ce qui permet d'obtenir un fonctionnement stable.

15 Des exemples d'une structure pour produire les mêmes fonctions et effets comprennent une structure qu'on appelle une grille de type en H représentée sur la figure 79 et une structure qu'on appelle une liaison à la source, représentée sur la figure 80.

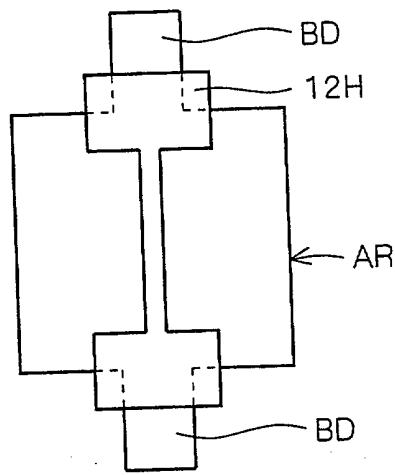

20 Dans la grille de type en H représentée sur la figure 79, les deux extrémités dans une direction d'une largeur de grille sont fortement agrandies dans une direction d'une longueur de grille, et une électrode de grille 12H ayant une forme en H en vue en plan est établie, et deux parties de contact de corps BD sont formées.

25 Dans la structure de liaison à la source représentée sur la figure 80, la partie de contact de corps BD en forme de bande est formée dans une partie d'une région de source SR et une extrémité

de la partie de contact de corps BD est connectée à une région de canal formée sous l'électrode de grille 12.

Cependant, dans le cas où on utilise la structure de grille de type en T ou la structure de grille de type en H, il y a un problème 5 consistant en ce qu'une capacité parasite entre une grille et un drain est augmentée en correspondance avec une augmentation d'une aire d'une électrode de grille, et on ne peut pas obtenir un fonctionnement rapide et stable.

Pour résoudre les problèmes mentionnés ci-dessus, un but 10 de la présente invention est d'effectuer la fixation de potentiel de corps et de parvenir à un fonctionnement rapide et stable dans un dispositif SOI dans lequel une épaisseur d'une couche SOI est réduite.

Un premier aspect de la présente invention porte sur un 15 dispositif à semiconducteur incluant un transistor MOS formé sur une couche SOI d'un substrat SOI dans lequel un substrat semiconducteur, une pellicule isolante enterrée et la couche SOI sont formés séquentiellement, et une partie de contact de corps formée dans une surface de la couche SOI et capable de fixer un potentiel électrique 20 à partir de l'extérieur. Une électrode de grille du transistor MOS a une forme, vue en plan, telle que l'une au moins des extrémités dans une direction d'une largeur de grille est agrandie dans une direction d'une longueur de grille pour constituer une plage de contact de grille, et la partie de contact de corps est formée dans la surface de 25 la couche SOI à l'extérieur de l'extrémité de la plage de contact de grille, dans la direction de la largeur de grille, et elle est connectée électriquement à une région de formation de canal formée sous l'électrode de grille, à travers la couche SOI. En outre, une pellicule isolante de grille du transistor MOS comprend une première partie 30 ayant une première épaisseur et une seconde partie ayant une seconde épaisseur dans la direction de la largeur de grille, la seconde épaisseur étant supérieure à la première épaisseur, et la seconde partie de la pellicule isolante de grille est formée au moins sous la plage de contact de grille.

35 Par exemple, l'épaisseur de la pellicule isolante de grille se

trouvant sous la plage de contact de grille formée sur une grande étendue de la couche SOI est augmentée, et l'épaisseur de la pellicule isolante de grille dans une région dans laquelle un courant circule avec une intensité élevée est réduite. Par conséquent, il est 5 possible de réduire une capacité parasite entre une grille et un drain avec une structure qui permet d'effectuer la fixation de potentiel de corps. Il est donc possible d'obtenir un transistor MOS capable de fonctionner de manière rapide et stable avec une faible consommation de puissance.

10 Un second aspect de la présente invention porte sur un dispositif à semiconducteur incluant un transistor MOS formé sur une couche SOI d'un substrat SOI dans lequel un substrat semiconducteur, une pellicule isolante enterrée et la couche SOI sont formés séquentiellement, et une partie de contact de corps formée dans une 15 surface de la couche SOI et capable de fixer un potentiel électrique à partir de l'extérieur. Une pellicule isolante de grille du transistor MOS comprend une première partie ayant une première épaisseur et une seconde partie ayant une seconde épaisseur dans une direction d'une largeur de grille, la seconde épaisseur étant supérieure à la 20 première épaisseur. En outre, la partie de contact de corps est formée comme une bande en position adjacente à une région de source du transistor MOS dans la surface de la couche SOI, à l'extérieur d'une partie de bord dans la direction de la largeur de grille dans la région de source. Une pellicule isolante ayant la seconde épaisseur, 25 incluant la seconde partie de la pellicule isolante de grille, est formée sur l'une de deux extrémités, dans la direction de la largeur de grille, d'une électrode de grille du transistor MOS dans lequel la partie de contact de corps en forme de bande est incorporée.

30 Dans une structure de liaison à la source, la pellicule isolante de grille épaisse est formée sur la partie de connexion de la partie de contact de corps et de la région de canal, et l'épaisseur de la pellicule isolante de grille dans la région de l'électrode de grille dans laquelle un courant circule avec une intensité élevée, est réduite. Par conséquent, il est possible de réduire une capacité parasite entre une grille et un drain avec une structure qui permet d'ef- 35

fectuer la fixation de potentiel de corps. Il est donc possible d'obtenir un transistor MOS capable de fonctionner de manière rapide et stable avec une faible consommation de puissance.

D'autres caractéristiques et avantages de l'invention seront 5 mieux compris à la lecture de la description qui va suivre de modes de réalisation, donnés à titre d'exemples non limitatifs. La suite de la description se réfère aux dessins annexés, dans lesquels :

La figure 1 est une représentation montrant une structure en plan d'un transistor MOS conforme à un premier mode de réalisation de la présente invention, 10

La figure 2 est une représentation montrant une structure en coupe du transistor MOS conforme au premier mode de réalisation de la présente invention;

Les figures 3 à 7 sont des représentations illustrant un procédé pour fabriquer le transistor MOS conforme au premier mode de 15 réalisation de la présente invention,

Les figures 8 à 11 sont des représentations montrant une structure en plan d'un transistor MOS ayant une structure de liaison à la source conforme à un second mode de réalisation de la présente 20 invention;

La figure 12 est une représentation montrant une structure en coupe d'un transistor MOS conforme à un troisième mode de réalisation de la présente invention,

Les figures 13 à 19 sont des représentations illustrant un procédé pour fabriquer un transistor MOS conforme à un quatrième 25 mode de réalisation de la présente invention,

Les figures 20 à 26 sont des représentations illustrant un exemple appliqué d'un procédé de fabrication conforme au quatrième mode de réalisation de la présente invention;

30 Les figures 27 à 32 sont des représentations illustrant un procédé pour fabriquer un transistor MOS conforme à un cinquième mode de réalisation de la présente invention,

La figure 33 est une représentation détaillée partielle montrant le procédé pour fabriquer un transistor MOS conforme au 35 cinquième mode de réalisation de la présente invention,

La figure 34 est une représentation montrant une étape à laquelle une paroi latérale d'une couche SOI n'est pas oxydée dans le procédé de fabrication d'un transistor MOS conforme au cinquième mode de réalisation de la présente invention,

5 Les figures 35 à 42 sont des représentations illustrant une variante du procédé de fabrication d'un transistor MOS conforme au cinquième mode de réalisation de la présente invention,

Les figures 43 à 46 sont des représentations en plan illustrant le procédé pour fabriquer un transistor MOS conforme au cinquième mode de réalisation de la présente invention,

10 Les figures 47 et 48 sont des représentations illustrant une structure en plan du transistor MOS conforme au cinquième mode de réalisation de la présente invention,

15 La figure 49 est une représentation en plan pour expliquer un avantage du transistor MOS conforme au cinquième mode de réalisation de la présente invention,

La figure 50 est une représentation illustrant une variante de la structure en plan du transistor MOS conforme au cinquième mode de réalisation de la présente invention,

20 La figure 51 est une représentation en plan pour expliquer la création de données de masque dans le transistor MOS conforme au cinquième mode de réalisation de la présente invention,

25 Les figures 52 à 55 sont des représentations illustrant un exemple appliqué d'un procédé de fabrication conforme au cinquième mode de réalisation de la présente invention,

Les figures 56 à 60 sont des représentations illustrant un exemple amélioré du procédé de fabrication conforme au cinquième mode de réalisation de la présente invention,

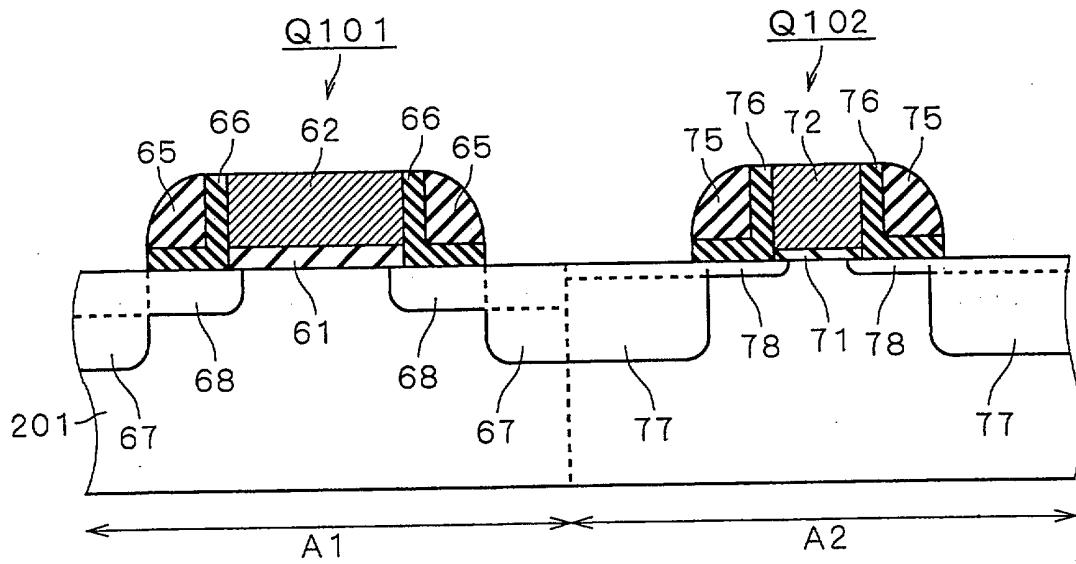

30 La figure 61 est une représentation montrant une structure en plan d'un transistor MOS conforme à un sixième mode de réalisation de la présente invention,

Les figures 62 et 63 sont des représentations montrant une structure en coupe dans le cours de la fabrication du transistor MOS conforme au sixième mode de réalisation de la présente invention,

35 Les figures 64 à 67 sont des représentations illustrant un

procédé pour fabriquer un transistor MOS conforme à un septième mode de réalisation de la présente invention,

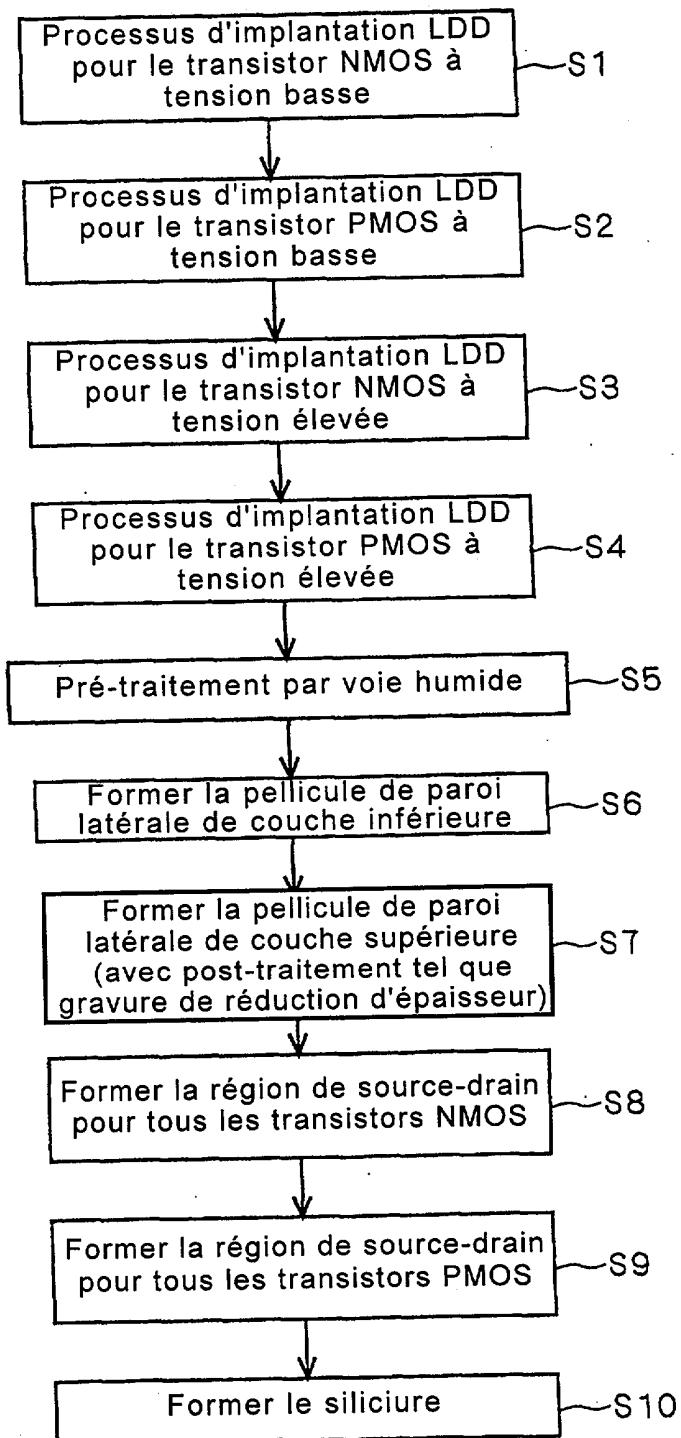

Les figures 68 à 72 sont des représentations illustrant un procédé à double oxyde,

5 La figure 73 est un organigramme pour expliquer le processus à double oxyde,

La figure 74 est une représentation montrant une structure en coupe d'un transistor MOS ayant une structure PTI générale,

10 Les figures 75 et 76 sont des représentations illustrant un procédé pour fabriquer un transistor MOS ayant une structure PTI conforme à l'art antérieur, et

Les figures 77 à 80 sont des représentations montrant une structure en plan d'un transistor MOS conforme à l'art antérieur.

#### A. Premier Mode de Réalisation

15 A-1. Structure du Dispositif

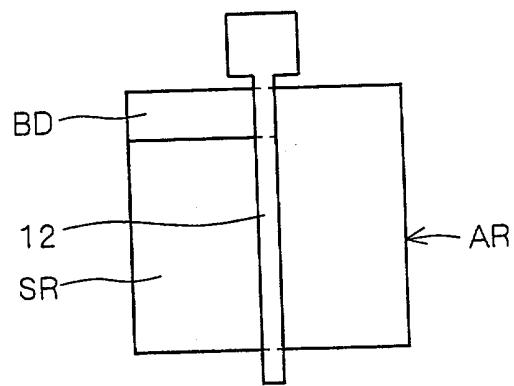

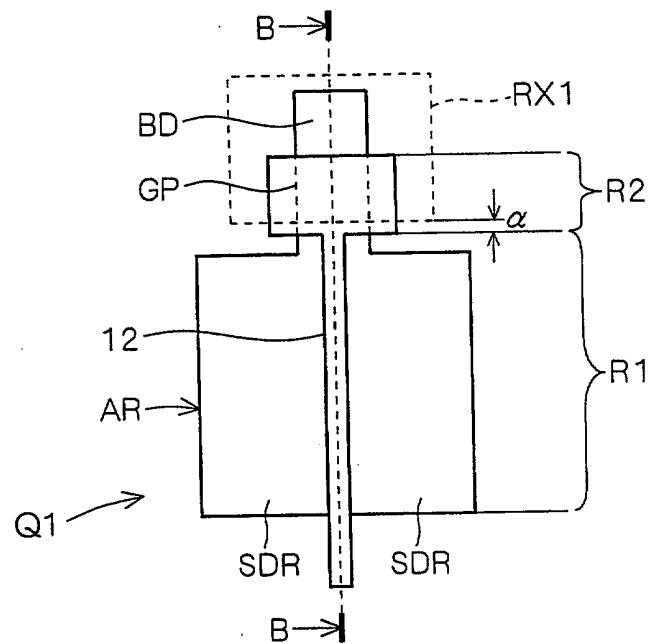

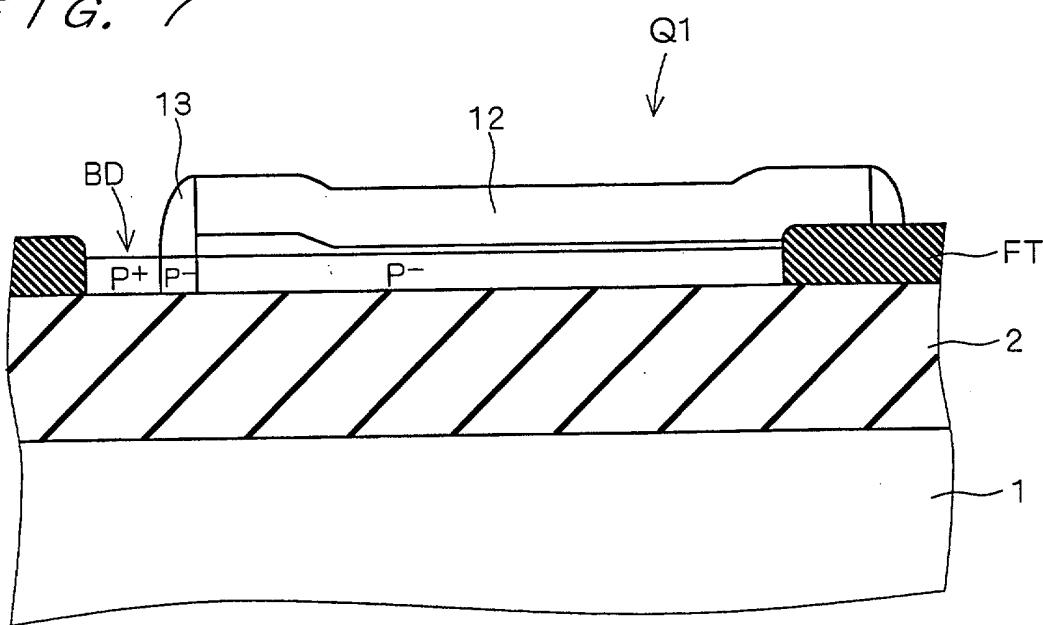

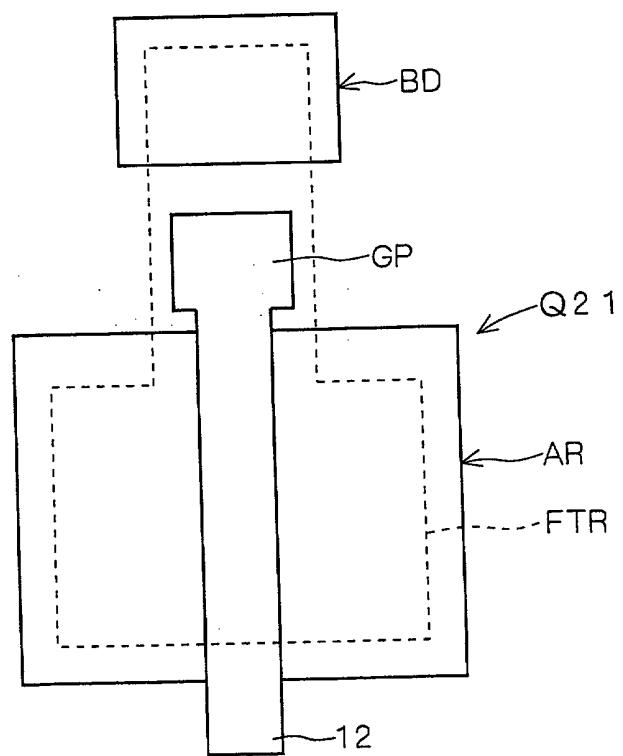

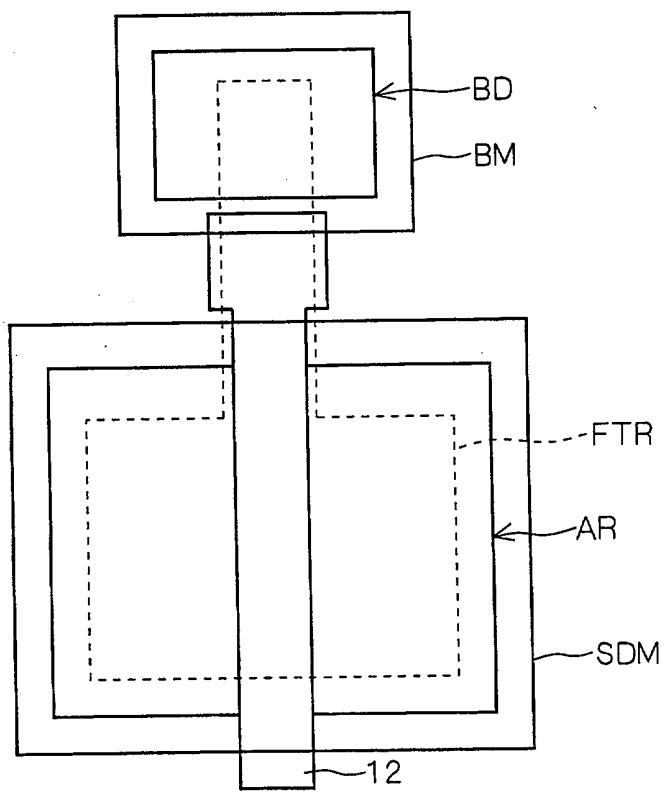

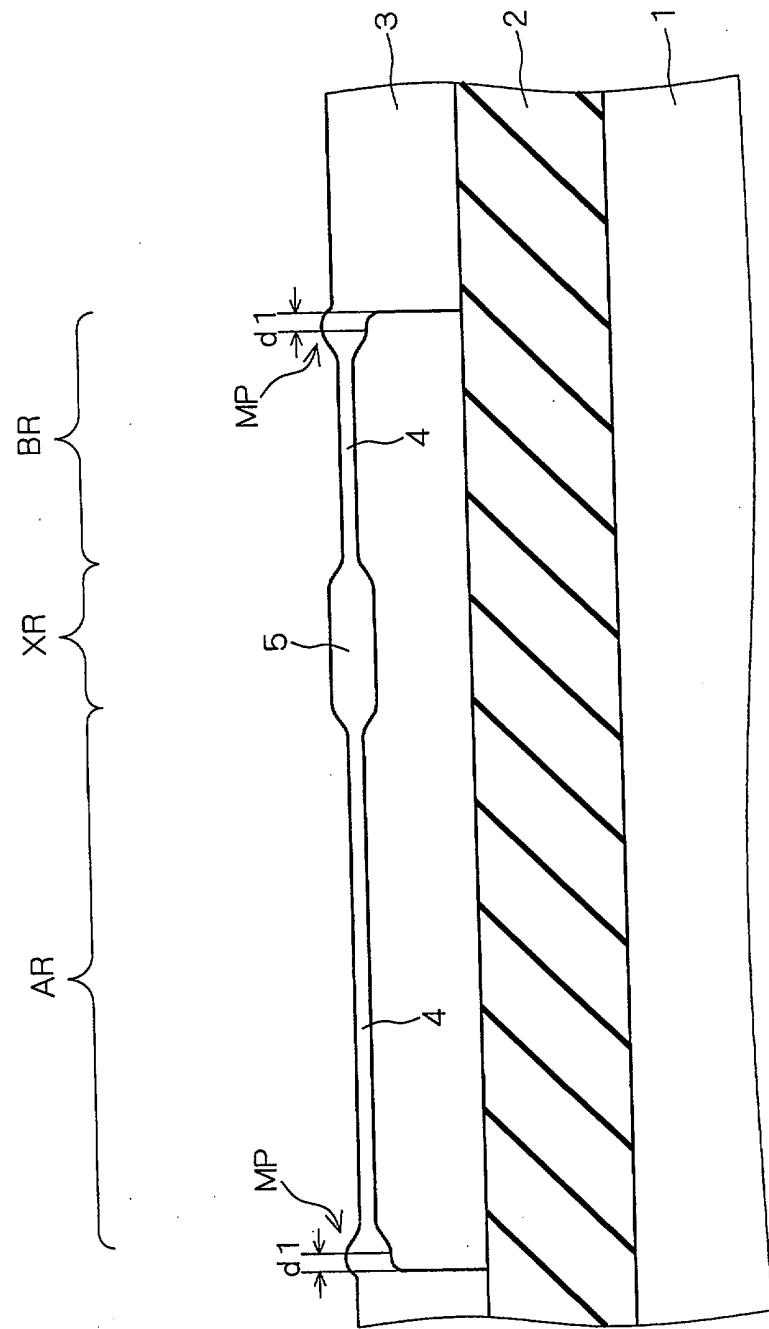

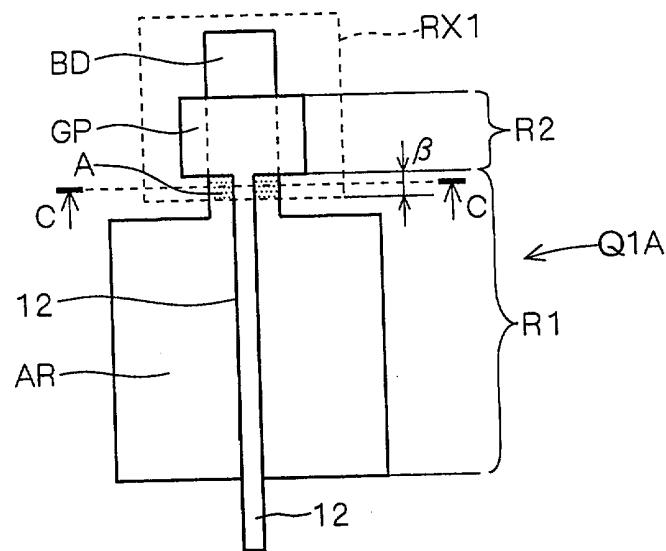

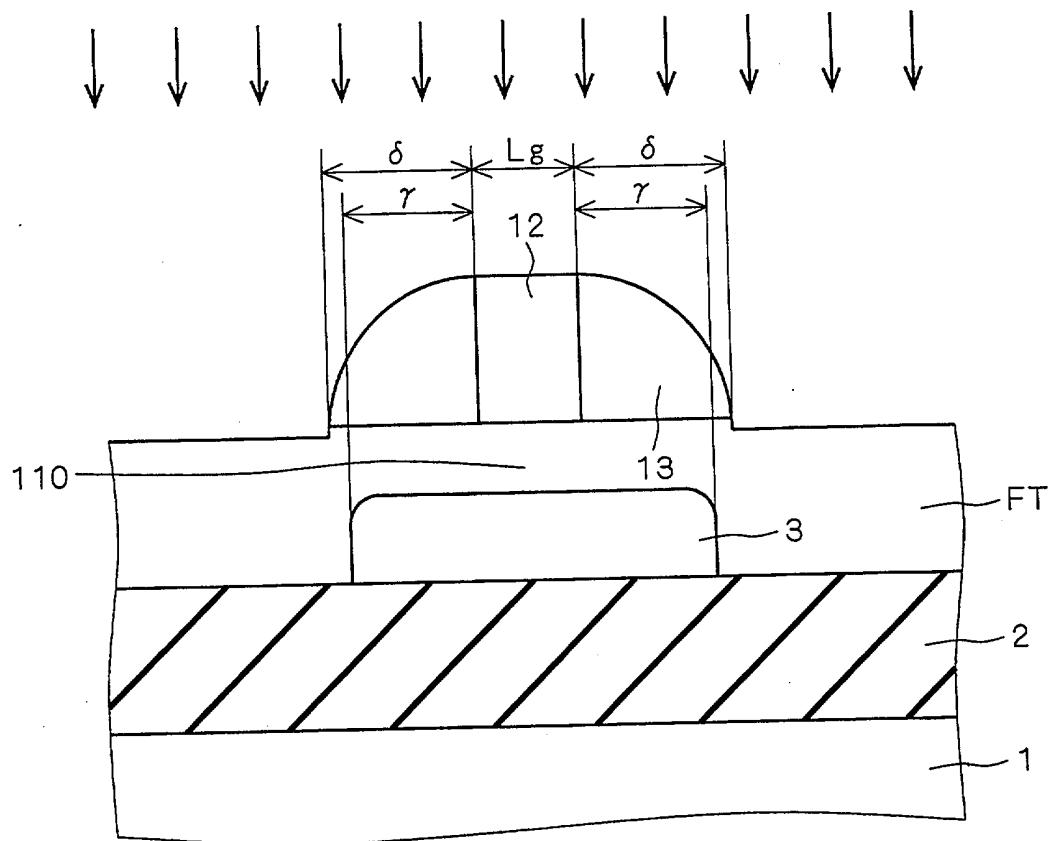

A titre de premier mode de réalisation conforme à la présente invention, la figure 1 montre une configuration en plan d'un transistor MOS Q1 ayant une grille de type T.

20 Comme représenté sur la figure 1, le transistor MOS Q1 comprend une électrode de grille 12 dont l'une des extrémités dans une direction d'une largeur de grille est fortement agrandie dans une direction d'une longueur de grille, et qui a une forme en T, vue en plan.

25 Une partie de tête en forme de T de l'électrode de grille 12 est ce qu'on appelle une plage de contact de grille GP et elle remplit la fonction d'une partie de contact électrique pour l'électrode de grille. Une partie de contact de corps BD est formée à l'extérieur d'un bout de la plage de contact de grille GP. Une région d'impureté ayant un type de conductivité inverse de celui d'une région de 30 source-drain est formée dans une surface d'une couche SOI 3 de la partie de contact de corps BD.

35 En outre, une région active AR incluant une région de source-drain SDR et la partie de contact de corps BD sont formées en continuité, et la plage de contact de grille GP est formée sur la région active AR reliant la région de source-drain SDR et la partie de

contact de corps BD.

Sur la figure 1, R1 indique une région dans laquelle un courant circule avec une intensité élevée et R2 indique une région correspondant à la plage de contact de grille GP dans l'électrode de grille 12.

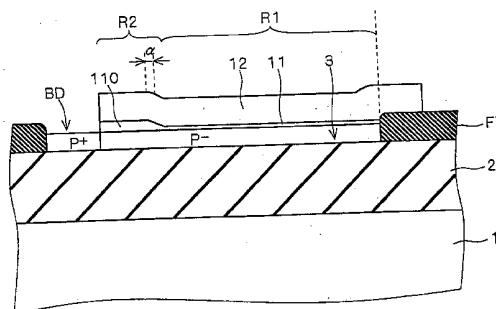

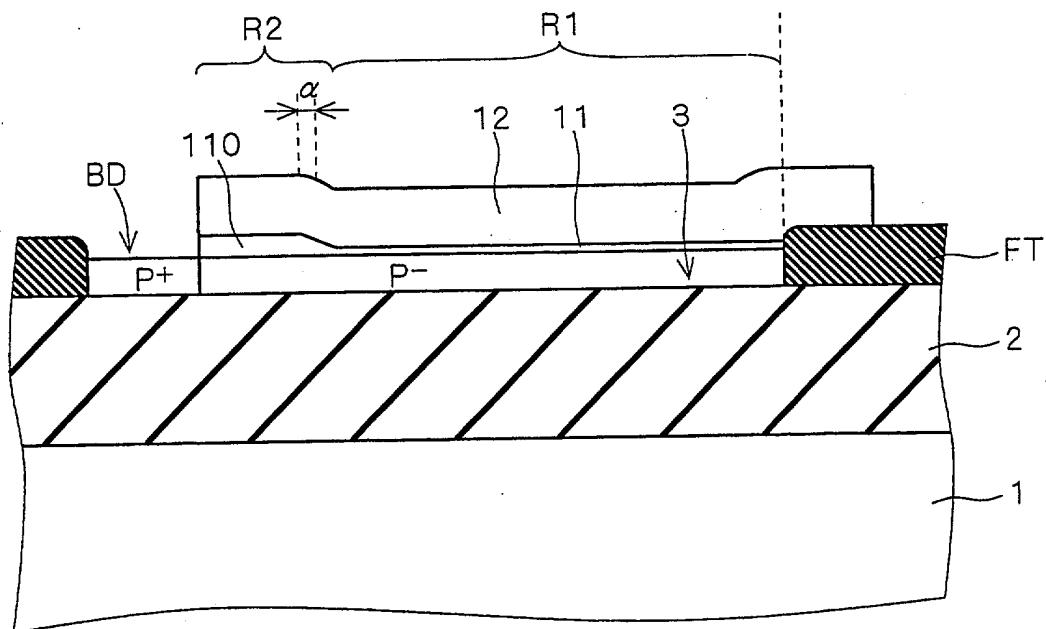

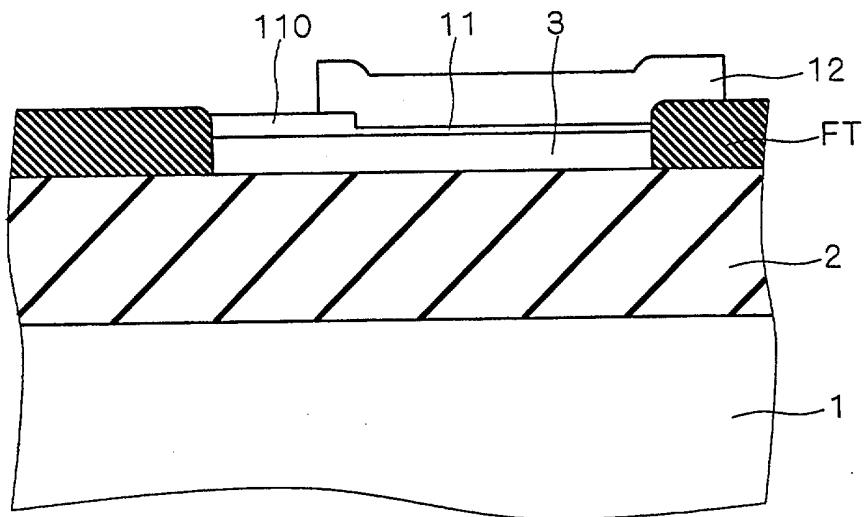

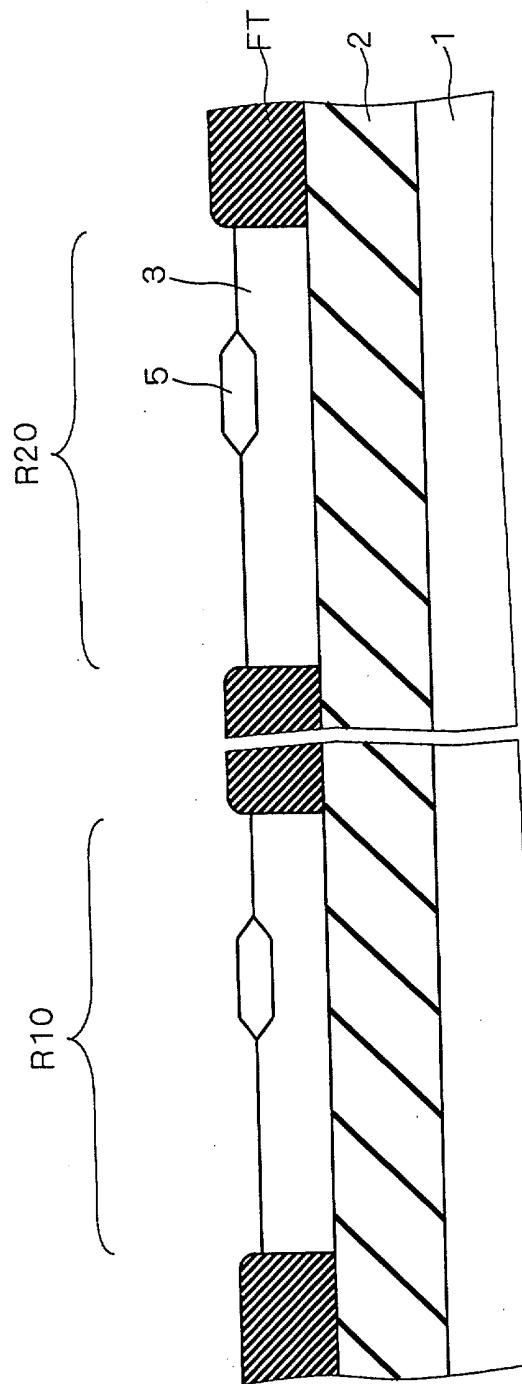

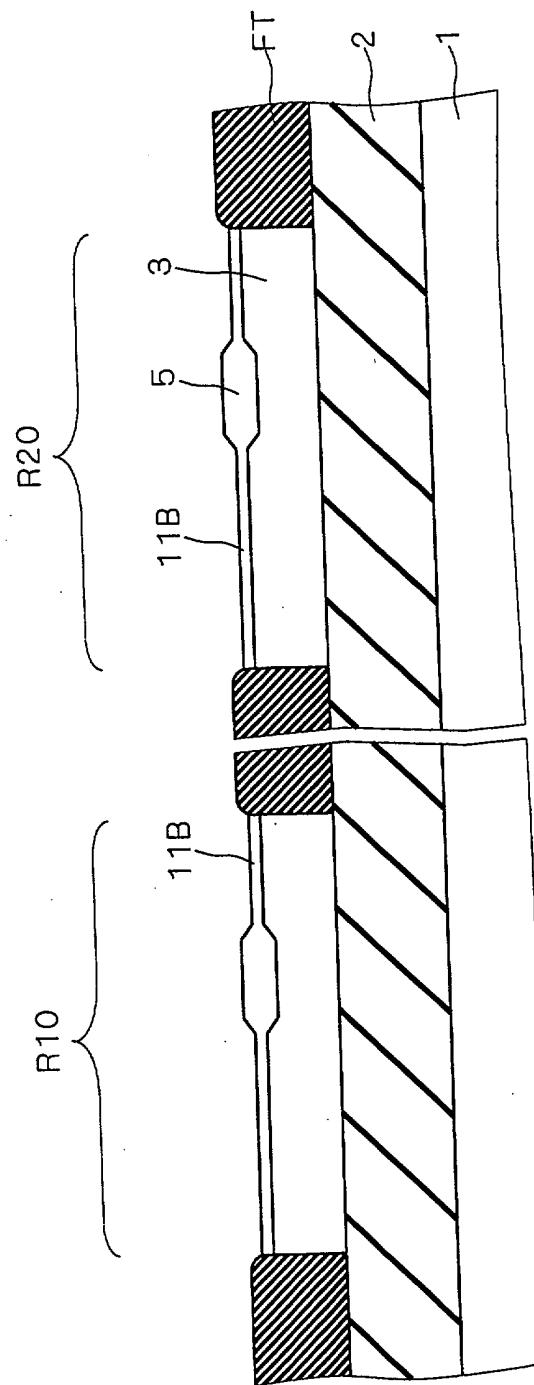

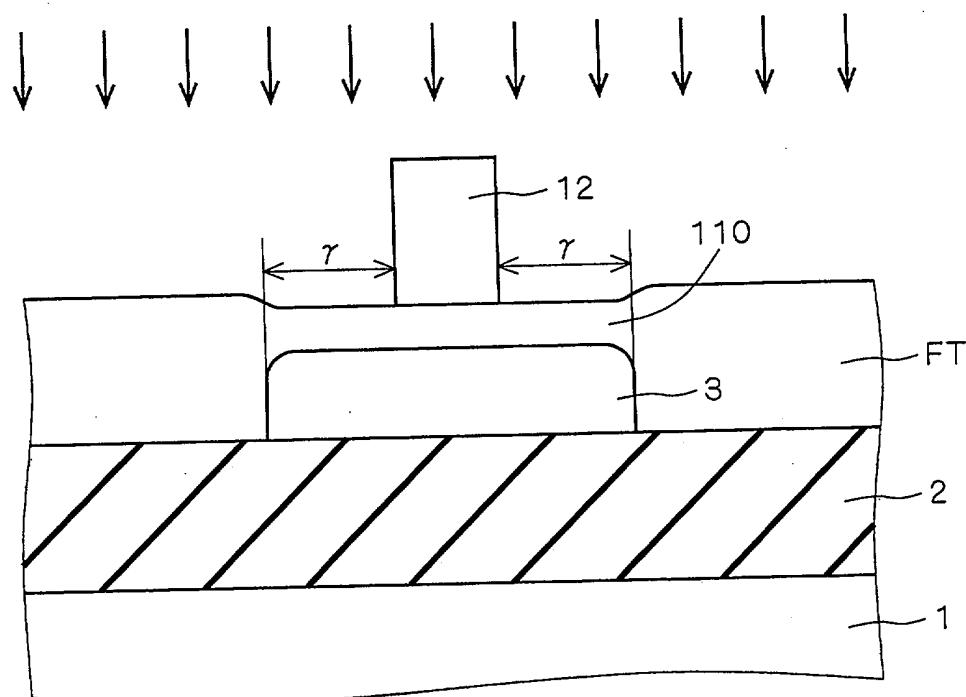

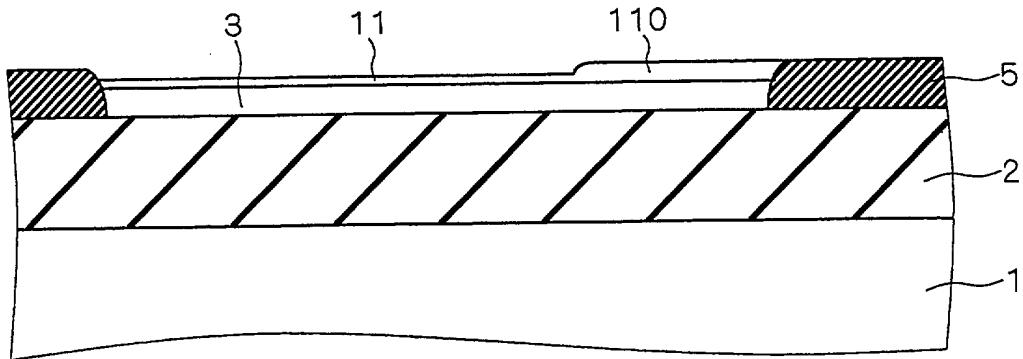

La figure 2 montre une structure d'une coupe selon une ligne B-B sur la figure 1. Comme représenté sur la figure 2, l'électrode de grille 12 est formée sur un substrat SOI constitué d'un substrat en silicium 1, d'une pellicule d'oxyde enterrée 2 et de la couche SOI 3. Dans le cas dans lequel le transistor MOS Q1 a un type de conductivité N, la couche SOI 3 formée sous l'électrode de grille 12 contient une impureté de type P avec une concentration relativement faible ( $P^-$ ), tandis que la partie de contact de corps BD contient une impureté de type P avec une concentration relativement élevée ( $P^+$ ). Dans le cas dans lequel le transistor MOS Q1 a un type de conductivité P, la couche SOI 3 formée sous l'électrode de grille 12 contient une impureté de type N avec une concentration relativement faible ( $N^-$ ), tandis que la partie de contact de corps BD contient une impureté de type N avec une concentration relativement élevée ( $N^+$ ).

Une pellicule isolante de grille 11 ayant une épaisseur de 1 à 5 nm est formée entre une partie de l'électrode de grille 12 autre que la plage de contact de grille GP et la couche SOI 3, et une pellicule isolante de grille 110 ayant une épaisseur de 5 à 15 nm est formée entre la plage de contact de grille GP et la couche SOI 3. La pellicule isolante de grille 11 et la pellicule isolante de grille 110 sont formées en continuité.

Des données de masque pour former la pellicule isolante de grille 110 sont indiquées par RX1 sur la figure 1. En se référant aux données de masque RX1, on note que la pellicule isolante de grille 110 recouvre la partie de contact de corps BD et une périphérie de celle-ci, en plus d'une partie formée sous la plage de contact de grille GP. Les données de masque RX1 ont une forme rectangulaire, vue en plan, et elles sont établies de façon qu'un côté de celles-ci ne recouvre pas complètement un côté du côté de la région de

source-drain de la plage de contact de grille GP, mais soit décalé d'une longueur  $\alpha$  vers le côté de la partie de contact de corps BD. Ceci est établi en considération d'un décalage au moment d'un alignement de masque réel.

5           A-2. Procédé de Fabrication

On décrira ci-dessous en référence aux figures 3 à 7 un procédé de fabrication du transistor MOS Q1.

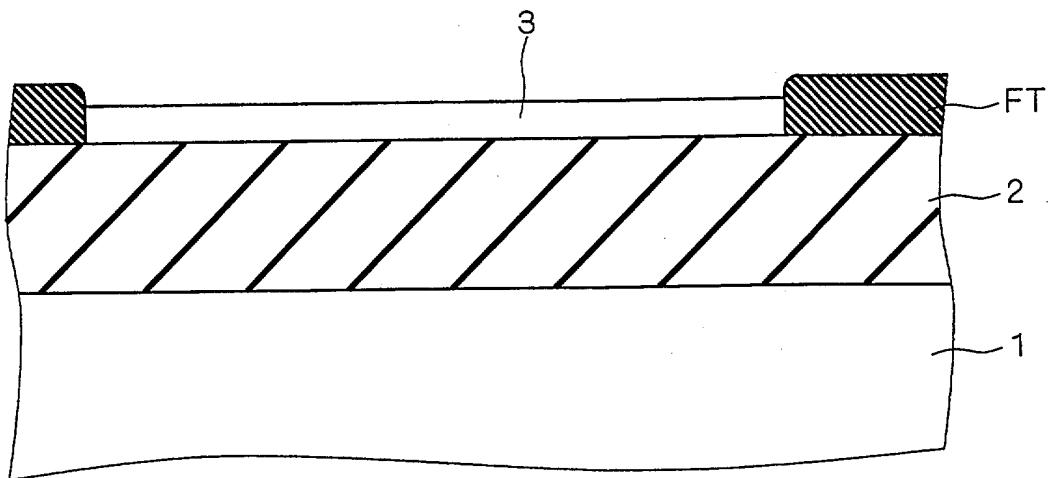

10           En premier lieu, comme représenté sur la figure 3, on prépare un substrat SOI constitué d'un substrat en silicium 1, d'une pellicule d'oxyde enterrée 2 et d'une couche SOI 3, et on forme une pellicule d'oxyde d'isolation par tranchée parfaite FT atteignant la pellicule d'oxyde enterrée 2 à travers la couche SOI 3 du substrat SOI, et on définit ensuite une région active et une région devant être une partie de contact de corps.

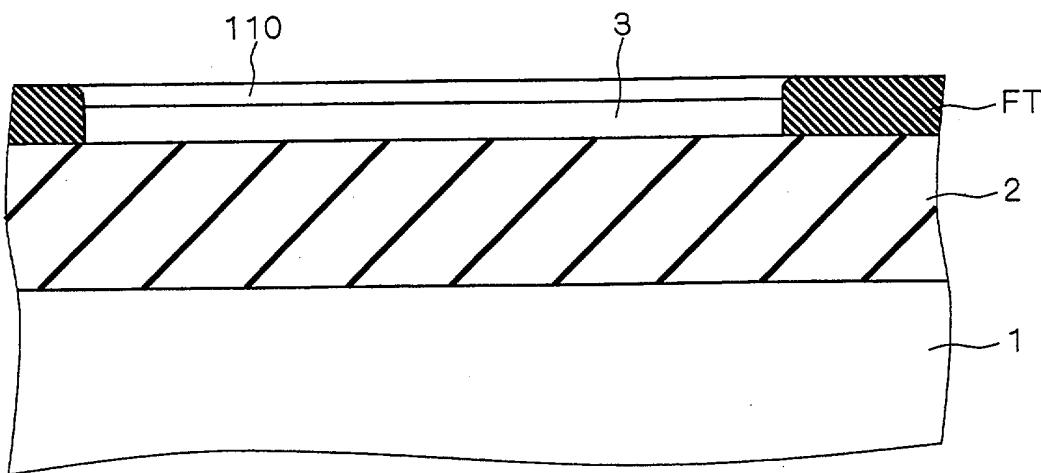

15           A une étape représentée sur la figure 4, on forme ensuite sur une surface complète de la couche SOI 3 une pellicule isolante de grille 110 ayant une épaisseur de 5 à 15 nm.

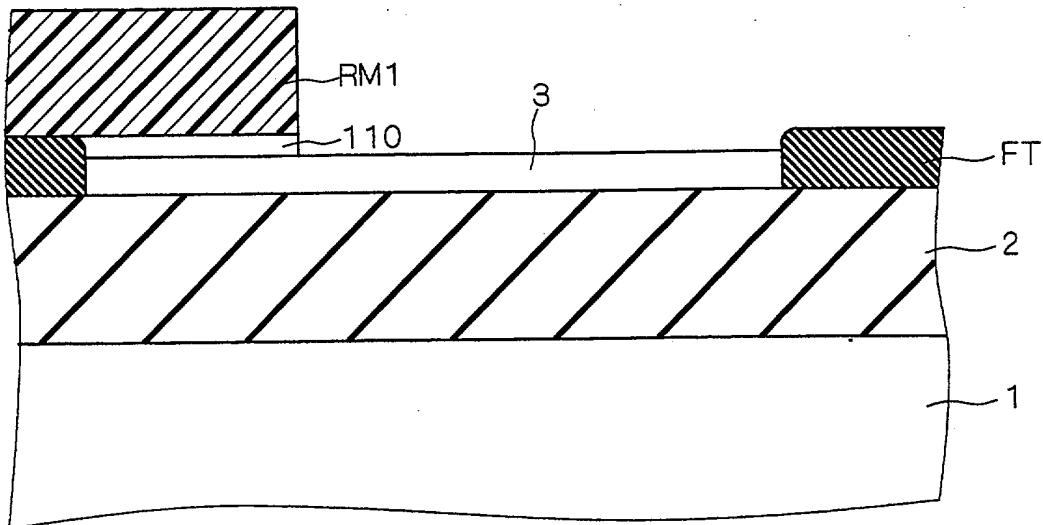

20           Ensuite, à une étape représentée sur la figure 5, on définit un motif dans un masque de matière de réserve RM1, sur la base des données de masque RX1, et on définit une région laissant la pellicule isolante de grille 110. Ensuite, on enlève par gravure par voie humide la pellicule isolante de grille 110 qui n'est pas recouverte par le masque de matière de réserve RM1.

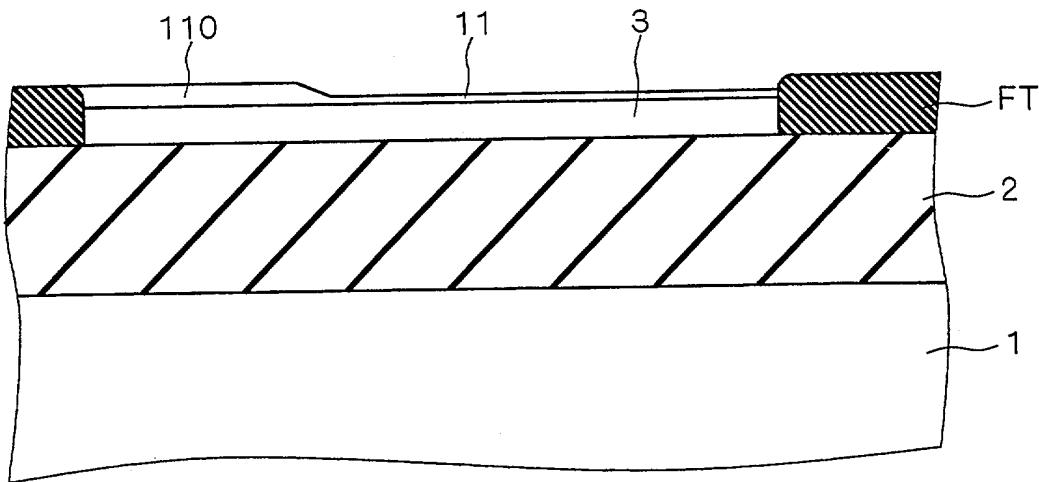

25           Ensuite, on enlève le masque de matière de réserve RM1 et on forme une pellicule isolante de grille 11 ayant une épaisseur de 1 à 5 nm sur la couche SOI 3 à nu, par oxydation thermique, à une étape représentée sur la figure 6.

30           Dans ce qui suit, une pellicule d'oxyde peut être formée par l'oxydation thermique en utilisant un procédé de dépôt chimique en phase vapeur ou CVD (Chemical Vapor Deposition), ou autres. En outre, l'oxydation thermique comprend un procédé d'oxydation thermique rapide ou RTO (Rapid Thermal Oxidation), en plus d'un procédé utilisant un four oxydant. Ces processus et variantes pour la formation d'une pellicule d'oxyde sont simplement appelés ci-après "oxydation" dans certains cas.

A une étape représentée sur la figure 7, on définit ensuite le motif de l'électrode de grille 12 sur les pellicules isolantes de grille 11 et 110. Une pellicule isolante de paroi latérale 13 peut être formée sur une surface latérale de l'électrode de grille 12.

5       Ensuite, on effectue une implantation d'impureté pour former une région de source-drain et une implantation d'impureté pour former la partie de contact de corps BD, de façon àachever le transistor MOS Q1.

#### A-3. Fonction et Effet

10       Comme décrit ci-dessus, dans le transistor MOS Q1 conforme au premier mode de réalisation, une épaisseur d'une pellicule isolante de grille est changée dans la direction de la largeur de grille, et une épaisseur de la pellicule isolante de grille 110 formée sous la plage de contact de grille GP sur une grande étendue de la 15 couche SOI 3 est augmentée, et une épaisseur de la pellicule isolante de grille 11 dans la région R1 dans laquelle un courant circule avec une intensité élevée est réduite. Par conséquent, il est possible d'effectuer la fixation de potentiel de corps et il est possible de réduire une capacité parasite entre une grille et un drain. Il est donc 20 possible d'obtenir un transistor MOS capable de fonctionner de manière rapide et stable avec une faible consommation de puissance.

En outre, la couche SOI 3 a une épaisseur de 10 à 100 nm, correspondant à ce qu'on appelle une couche SOI mince. Du fait que la région active AR et la partie de contact de corps BD sont définies 25 par la pellicule d'oxyde d'isolation par tranchée parfaite FT, un inconvénient n'est pas occasionné par une variation d'une profondeur d'une tranchée.

Par conséquent, dans la couche SOI mince dans laquelle la fixation de potentiel de corps est difficile à effectuer avec une structure PTI, la fixation de potentiel de corps est effectivement accomplie par une pellicule isolante de grille épaisse. Même si la pellicule isolante de grille et la pellicule d'oxyde d'isolation par tranchée sont formées par le même matériau, un motif avec lequel elles sont formées est entièrement différent. Par exemple, alors que la pellicule d'oxyde d'isolation par tranchée n'est pas formée sur la partie de 30 35

contact de corps BD, la pellicule isolante de grille épaisse peut s'étendre jusqu'à la partie de contact de corps BD.

En outre, du fait que les pellicules isolantes de grille 11 et 110 sont formées par l'oxydation thermique, on peut exercer une excellente maîtrise sur l'épaisseur de pellicule et cette dernière varie moins. Par conséquent, il est possible de favoriser une réduction de l'épaisseur de la couche SOI 3 par la formation des pellicules isolantes de grille 11 et 110.

Bien que la grille de type en T ait été illustrée dans le premier mode de réalisation, il est clair qu'il est possible d'augmenter une épaisseur d'une pellicule isolante de grille formée sous deux plages de contact de grille, pour donner une grille de type en H ayant les plages de contact de grille formées aux deux extrémités dans une direction d'une largeur d'une électrode de grille.

15        B. Second Mode de Réalisation

B-1. Structure du Dispositif

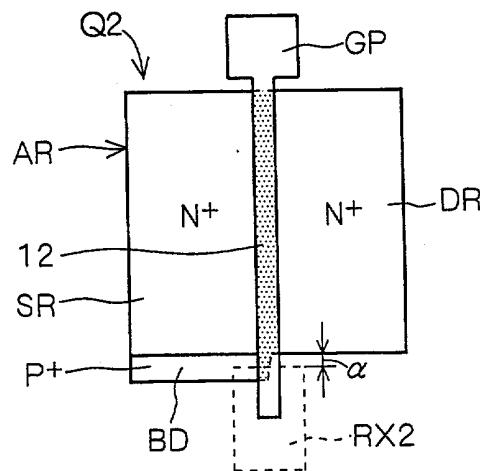

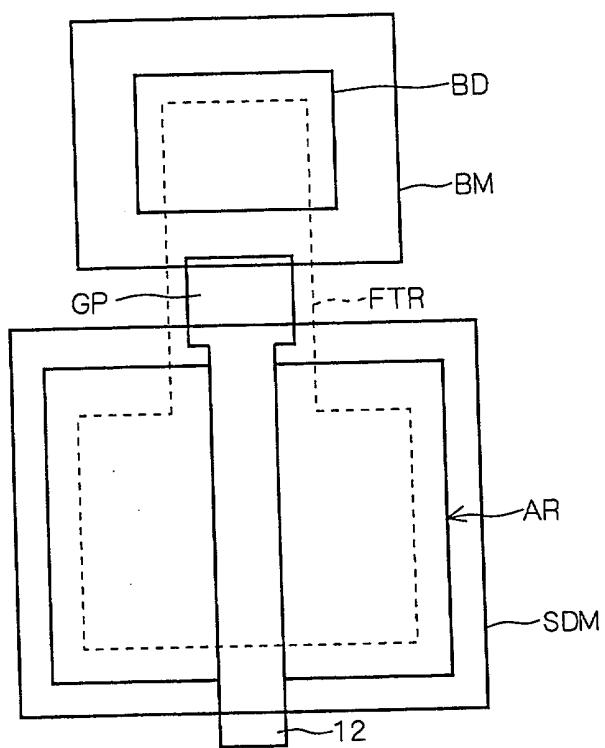

A titre de second mode de réalisation conforme à la présente invention, les figures 8 à 11 montrent des structures en plan de transistors MOS Q2 à Q5 ayant une structure de liaison à la source.

Dans la structure de liaison à la source, une partie de contact de corps BP en forme de bande est formée dans une partie d'une région de source SR, et l'une des extrémités de la partie de contact de corps BD est connectée à une région de canal formée sous une électrode de grille 12. Sur la figure 8, dans le transistor MOS de type N Q2, la partie de contact de corps BD est formée le long de l'extérieur d'une partie de bord d'une région de source, du côté opposé au côté de l'électrode de grille 12 sur lequel une plage de contact de grille GP est formée, et une extrémité de la partie de contact de corps BD est connectée à la région de canal formée sous l'électrode de grille 12. La partie de contact de corps BD a un type de conductivité P.

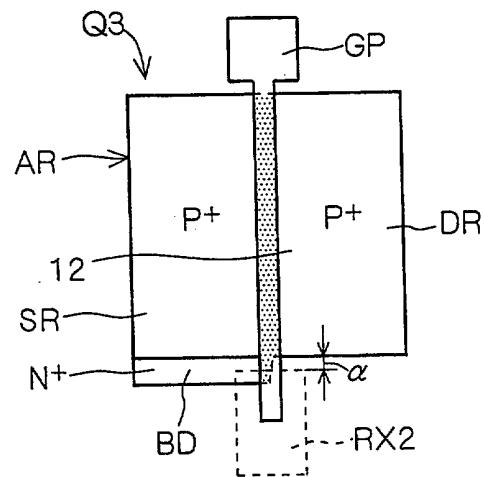

Sur la figure 9, dans le transistor MOS de type P Q3, la partie de contact de corps BD est établie le long de l'extérieur de la partie de bord de la région de source, du côté opposé au côté de

l'électrode de grille 12 sur lequel la plage de contact de grille GP est formée, et l'extrémité de la partie de contact de corps BD est connectée à la région de canal formée sous l'électrode de grille 12. Cette partie de contact de corps BD a une conductivité de type N.

5        Dans les transistors MOS Q2 et Q3, une pellicule isolante de grille dans une région de l'électrode de grille 12 dans laquelle un courant circule avec une intensité élevée, est formée de manière mince, et une pellicule isolante de grille épaisse est formée sur une partie de connexion de la partie de contact de corps BD et de la région de canal. Sur les figures 8 et 9, des données de masque pour former la pellicule isolante de grille épaisse sont indiquées par RX2. Les données de masque RX2 sont établies de façon à présenter un décalage d'une longueur  $\alpha$  à partir de la partie de bord de la région de source vers le côté opposé de la plage de contact de grille GP, 10 en considération d'un décalage au moment de la formation d'un masque.

15

En outre, la région de canal formée en contact avec la partie de contact de corps BD est étendue jusqu'au voisinage d'une partie centrale d'une longueur de grille de l'électrode de grille 12, afin 20 d'empêcher un court-circuit électrique entre une région de drain DR et une région de source SR. Sur les figures 8 et 9, la région de canal est représentée avec des hachures.

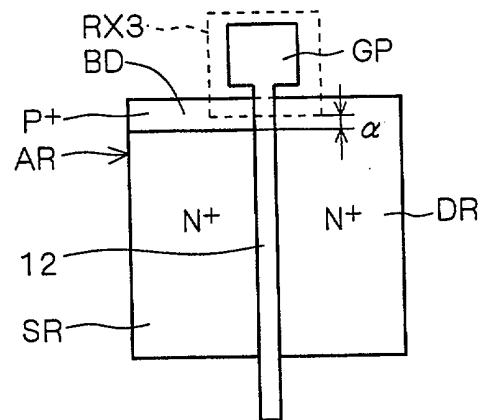

Sur la figure 10, dans le transistor MOS de type N Q4, la partie de contact de corps BD est formée le long de l'extérieur de la 25 partie de bord de la région de source SR du côté de l'électrode de grille 12 duquel la plage de contact de grille GP est formée, et l'extrémité de la partie de contact de corps BD est connectée à la région de canal formée sous l'électrode de grille 12. La partie de contact de corps BD a un type de conductivité P.

30        Sur la figure 11, dans le transistor MOS de type P Q5, la partie de contact de corps BD est formée le long de l'extérieur de la partie de bord de la région de source SR, du côté de l'électrode de grille 12 duquel la plage de contact de grille GP est formée, et l'extrémité de la partie de contact de bord BD est connectée à la région 35 de canal formée sous l'électrode de grille 12. La partie de contact de

corps BD a un type de conductivité N.

Dans les transistors MOS Q4 et Q5, une pellicule isolante de grille dans une région de l'électrode de grille 12 dans laquelle un courant circule avec une intensité élevée est formée de manière 5 mince, et une pellicule isolante de grille épaisse est formée sur une partie de connexion de la partie de contact de corps BD et de la région de canal. Sur les figures 10 et 11, des données de masque pour former la pellicule isolante de grille épaisse sont indiquées par RX3. Les données de masque RX3 sont établies de façon à présenter un décalage d'une longueur  $\alpha$  à partir de la partie de bord de la région 10 de source vers le côté de la plage de contact de grille GP, en considération d'un décalage au moment de la formation de masque.

#### B-2. Fonction et effet

Comme décrit ci-dessus, dans les transistors MOS Q2 à Q5 15 conformes au second mode de réalisation, la pellicule isolante de grille épaisse est formée sur la partie de connexion de la partie de contact de corps BD et de la région de canal, et l'épaisseur de la pellicule isolante de grille est réduite dans la région de l'électrode de grille dans laquelle un courant circule avec une intensité élevée, 20 dans la structure de liaison à la source. Par conséquent, il est possible d'effectuer la fixation de potentiel de corps, et il est possible de réduire une capacité parasite entre une grille et un drain. Il est donc possible d'obtenir un transistor MOS capable de fonctionner de manière rapide et stable avec une faible consommation de puissance.

### 25 C. Troisième Mode de Réalisation

#### C-1. Structure du Dispositif

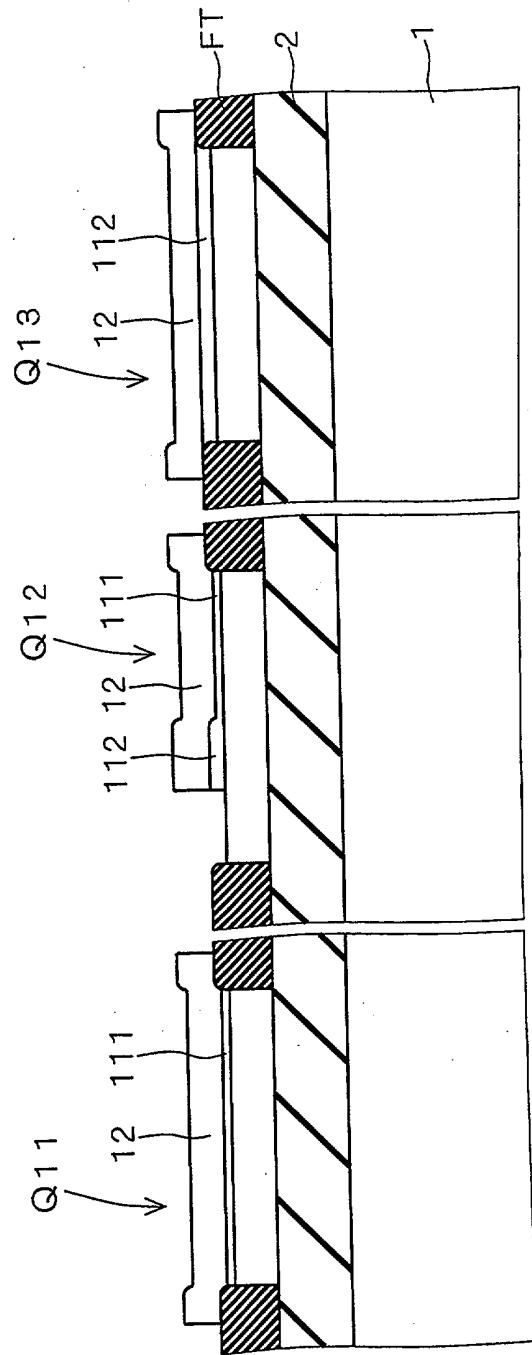

A titre de troisième mode de réalisation conforme à la présente invention, la figure 12 montre des structures en coupe de transistors MOS Q11, Q12 et Q13.

30 Comme représenté sur la figure 12, les transistors MOS Q11 à Q13 sont formés sur un substrat SOI constitué d'un substrat en silicium 1, d'une pellicule d'oxyde enterrée 2 et d'une couche SOI 3.

35 Sur la figure 12, le transistor MOS Q11 a une électrode de grille 12 formée sur la couche SOI 3 définie par une pellicule d'oxyde

d'isolation par tranchée parfaite FT avec une pellicule isolante de grille 111 ayant une relativement faible épaisseur (par exemple une épaisseur de 1 à 5 nm) intercalée entre elles.

En outre, le transistor MOS Q13 a l'électrode de grille 12 formée sur la couche SOI 3 définie par la pellicule d'oxyde d'isolation par tranchée parfaite FT avec une pellicule isolante de grille 112 ayant une relativement grande épaisseur (par exemple une épaisseur de 3 à 15 nm) intercalée entre elles.

Le transistor MOS Q12 a une structure dans laquelle la pellicule isolante de grille 111 ayant une relativement faible épaisseur et la pellicule isolante de grille 112 ayant une relativement grande épaisseur sont formées en continuité sur la couche SOI 3 définie par la pellicule d'oxyde d'isolation par tranchée parfaite FT, dans une direction d'une largeur de grille, et l'électrode de grille 12 est formée sur la couche SOI 3 avec les pellicules isolantes de grille 111 et 112 intercalées entre elles, et une partie de contact de corps BD est formée dans une surface de la couche SOI à l'extérieur d'une extrémité de l'électrode de grille 12 du côté où la pellicule isolante de grille 112 doit être formée.

Le transistor MOS Q11 est un transistor à tension basse, ayant une tension de grille de 0,5 à 2,0 V, par exemple, le transistor MOS Q13 est un transistor à tension élevée ayant une tension de grille de 1,5 à 5,0 V, par exemple, et le transistor MOS Q12 peut accomplir la fixation de potentiel de corps décrite dans les premier et second modes de réalisation.

Ainsi, un procédé pour former sur un substrat semiconducteur commun deux sortes de transistors MOS comportant des pellicules isolantes de grille ayant des épaisseurs différentes, sera appelé un procédé à double oxyde.

Avec le procédé à double oxyde, on a mis en oeuvre de façon pratique la formation d'un transistor de tension basse et d'un transistor de tension élevée incluant des pellicules isolantes de grille ayant différentes épaisseurs sur un substrat SOI commun. Si une étape de formation des pellicules isolantes de grille est également utilisée pour une étape de formation des pellicules isolantes de grille

111 et 112 du transistor MOS Q12, le transistor MOS Q12 peut être formé sans ajouter une nouvelle étape de fabrication. Par conséquent, on peut éviter une augmentation du coût de fabrication.

Le transistor MOS Q12 capable d'effectuer la fixation de potentiel de corps convient pour l'utilisation dans une partie de circuit dans laquelle un fonctionnement rapide et stable est exigé.

De façon plus spécifique, des transistors flottants tels que les transistors MOS Q11 et Q13 ont l'inconvénient d'avoir un effet de corps flottant par lequel une dépendance d'un temps de retard vis-à-vis de la fréquence et une marge temporelle sont augmentés, et ils ne conviennent pas pour un chemin critique dans lequel les conditions temporelles sont importantes. Au contraire, un transistor à potentiel de corps fixé, n'ayant pas un inconvénient tel que l'effet de corps flottant, par exemple le transistor MOS Q12, convient pour l'utilisation dans le chemin critique. En outre, le transistor à potentiel de corps fixé convient également pour un circuit dynamique ou similaire.

Du fait de l'incorporation de la partie de contact de corps BD, il est nécessaire de prévoir une grande région. Dans une partie de circuit dans laquelle le fonctionnement rapide et stable n'est pas exigé, on utilise les transistors flottants tels que les transistors MOS Q11 et Q13, de façon à permettre de réduire une taille d'un circuit intégré à semiconducteur.

On décrira ultérieurement des structures et des procédés de fabrication généraux du transistor à tension basse et du transistor à tension élevée.

#### C-2. Fonction et Effet

Comme dans les transistors MOS Q11 à Q13 décrits ci-dessus, deux sortes de transistors MOS incluant des pellicules isolantes de grille ayant des épaisseurs différentes, et un transistor capable d'accomplir la fixation de potentiel de corps, dans lequel une pellicule isolante de grille ayant une épaisseur relativement faible et une pellicule isolante de grille ayant une épaisseur relativement grande sont établies en continuité dans une direction d'une largeur de grille, sont formés sur un substrat SOI commun. Par conséquent,

il est possible d'obtenir trois sortes de transistors MOS sans ajouter une nouvelle étape de fabrication.

#### D. Quatrième Mode de Réalisation

##### D-1. Procédé de Fabrication

5 Alors que l'étape de formation de la pellicule isolante de grille épaisse 110 est exigée dans le procédé de fabrication du transistor MOS Q1 décrit en référence aux figures 3 à 7, l'étape de formation de la pellicule isolante de grille épaisse peut être omise si on emploie le procédé suivant.

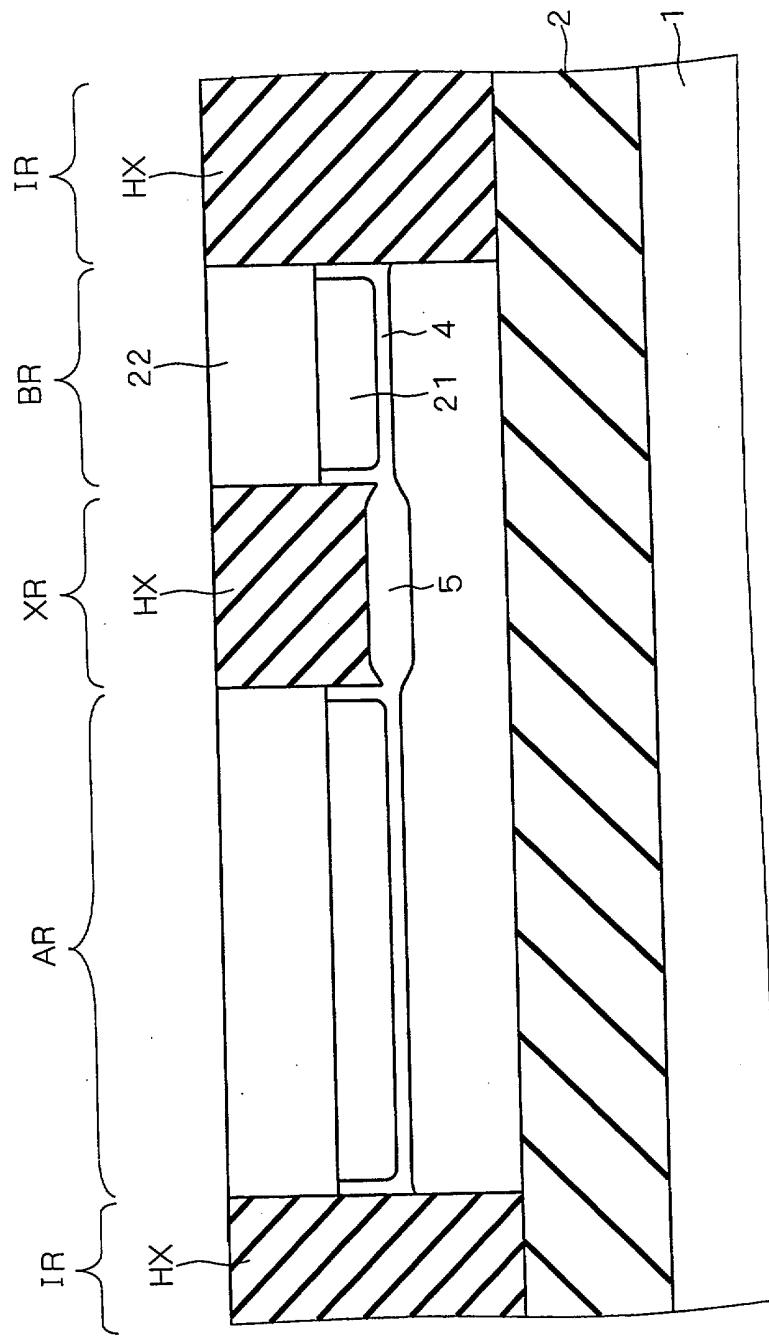

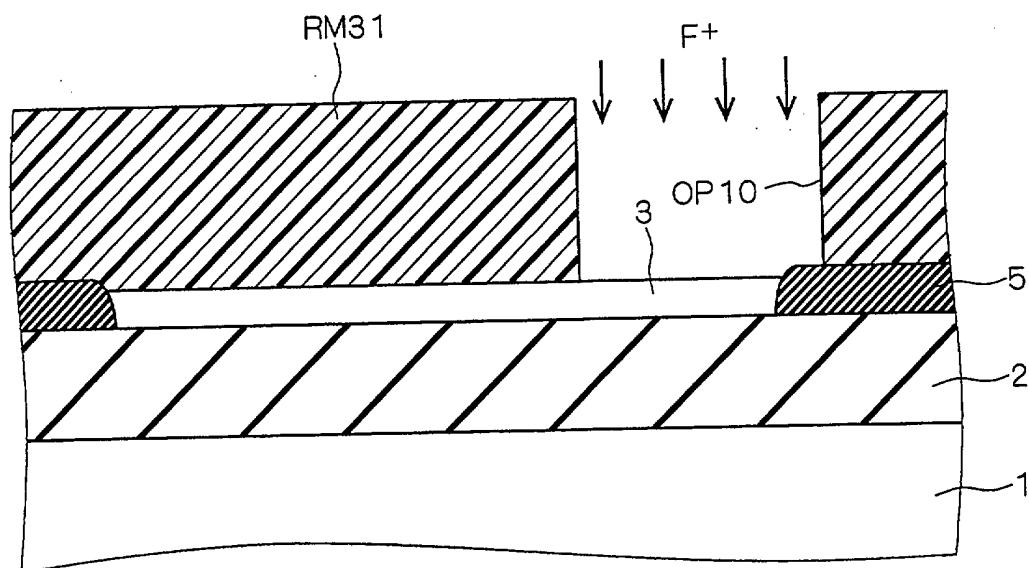

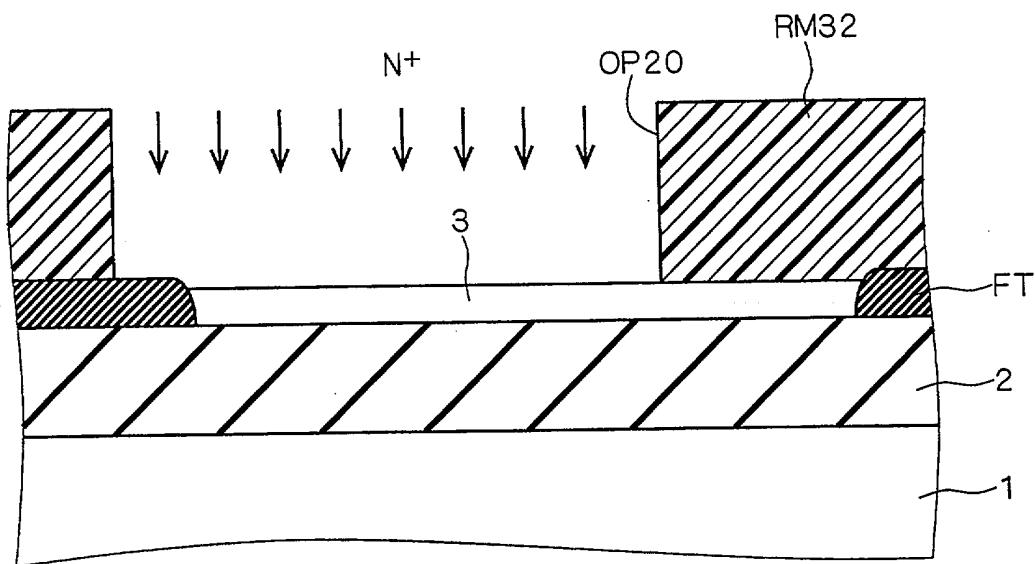

10 On décrira ci-dessous en référence aux figures 13 à 19 un procédé de fabrication conforme à un quatrième mode de réalisation.

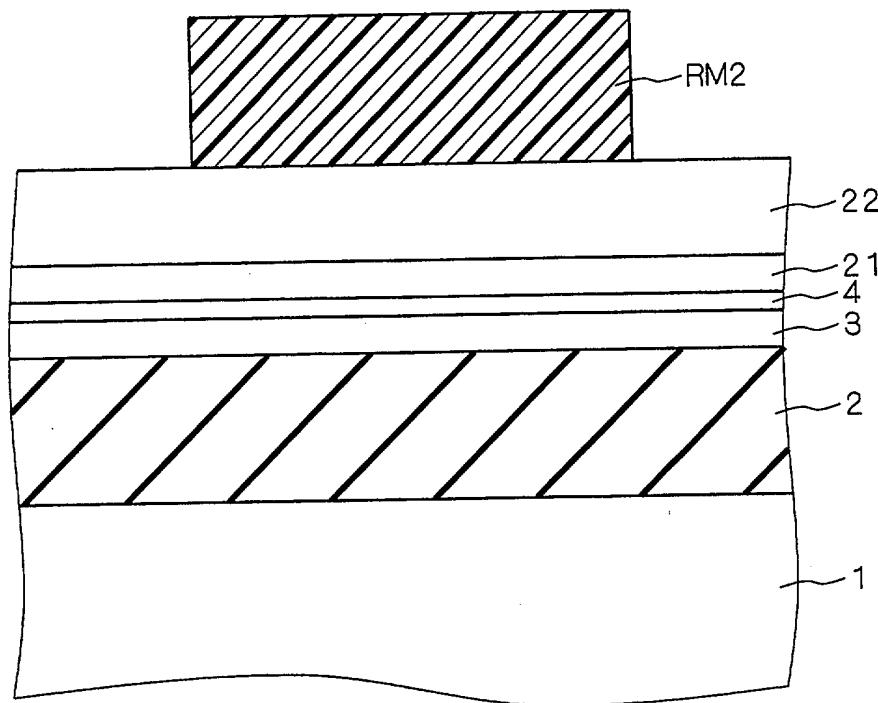

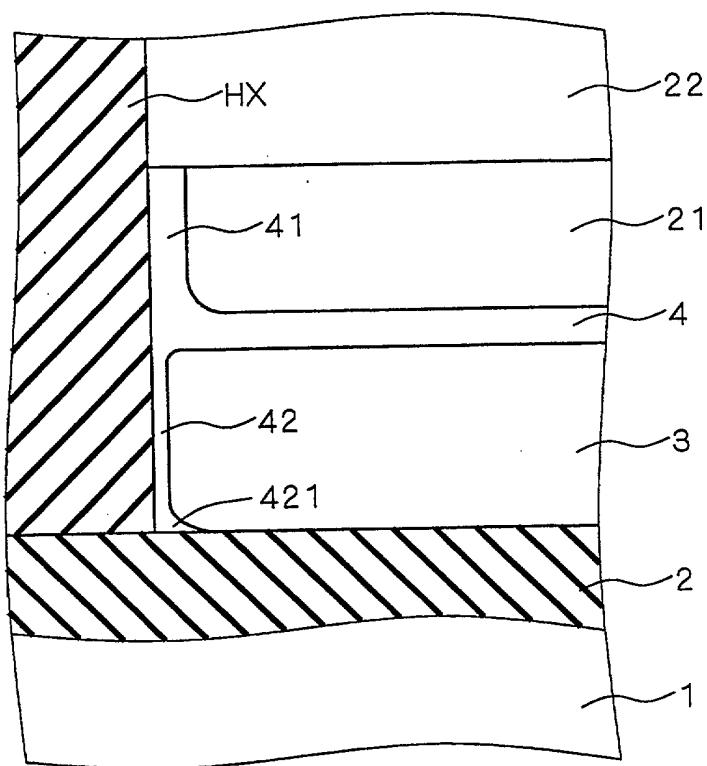

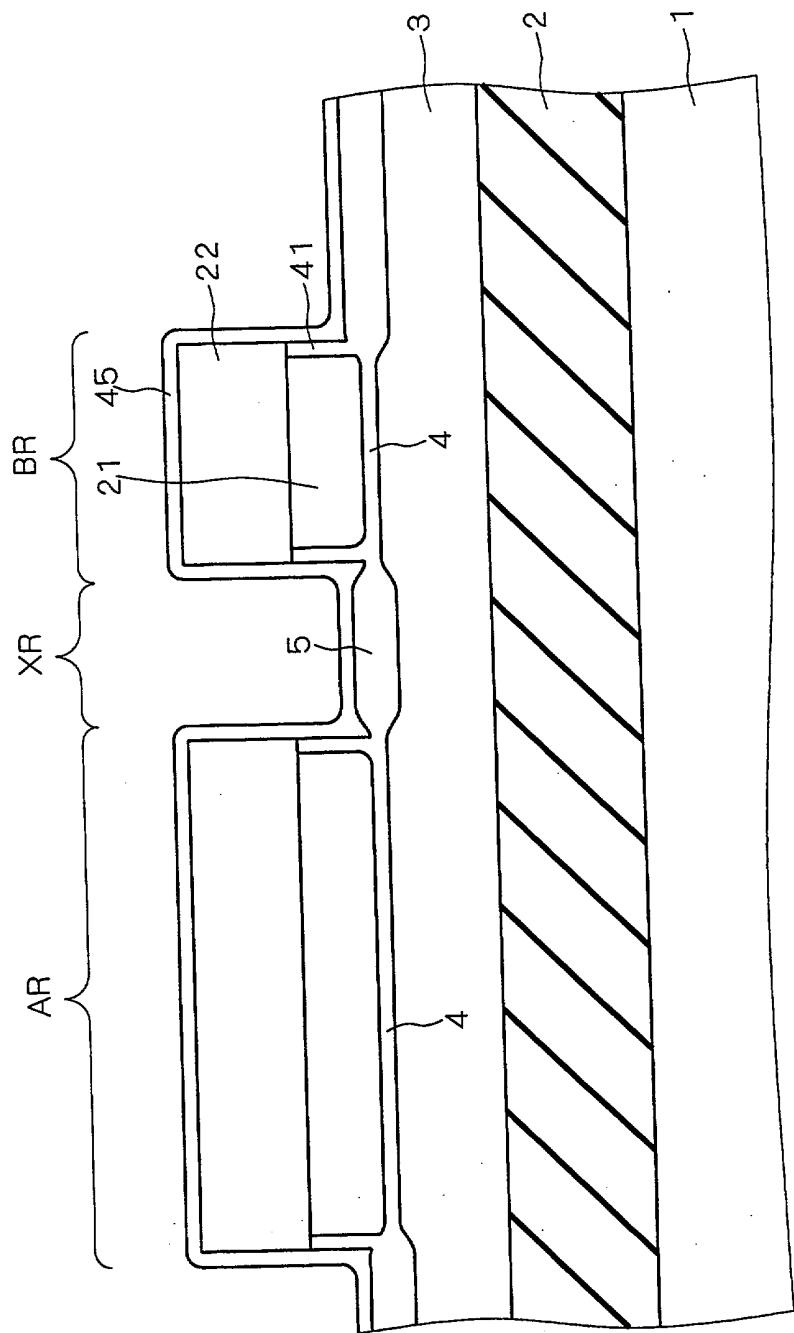

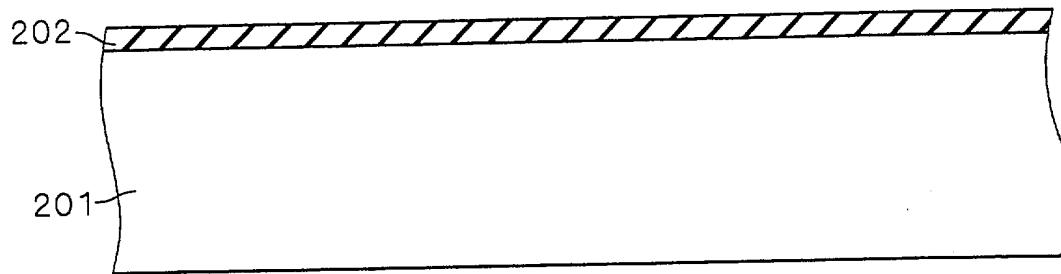

15 Comme représenté sur la figure 13, en premier lieu, on prépare un substrat SOI et on forme une pellicule d'oxyde 4 sur une couche SOI 3 du substrat SOI. La pellicule d'oxyde 4 est ce qu'on appelle une pellicule d'oxyde sous-jacente (une pellicule d'oxyde de plage) et son épaisseur est adaptée à une épaisseur de la pellicule isolante de grille épaisse qui sera formée ultérieurement.

20 Ensuite, on forme une pellicule de silicium polycristallin 21 sur la pellicule d'oxyde 4 par un procédé CVD et on forme une pellicule de nitrure 22 sur la pellicule de silicium polycristallin 21 par le procédé CVD. Du fait que la pellicule d'oxyde 4, la pellicule de silicium polycristallin 21 et la pellicule de nitrure 22 remplissent la fonction d'auxiliaires pour former une pellicule d'oxyde d'isolation, on les appelle également dans certains cas des pellicules auxiliaires. La pellicule de silicium polycristallin 21 n'est pas toujours exigée.

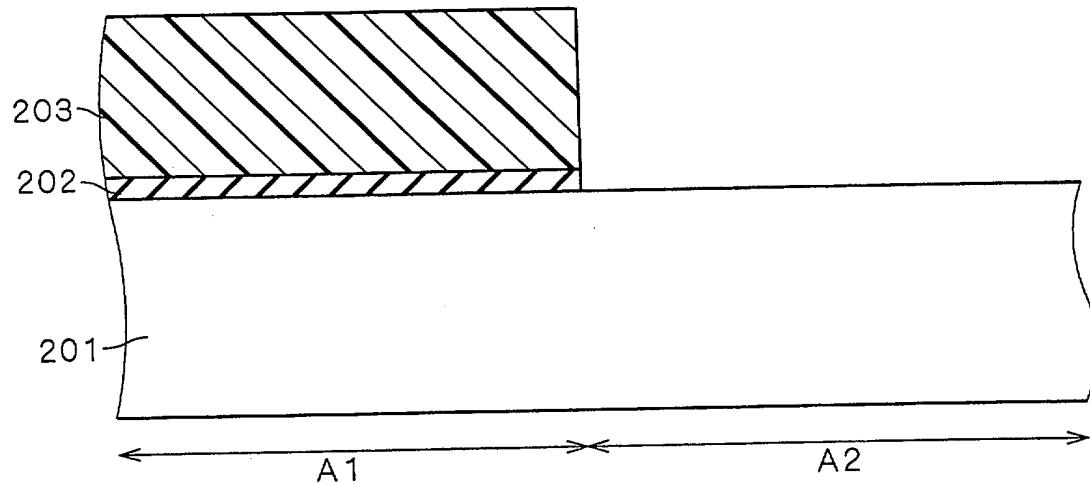

25 Ensuite, on recouvre par un masque de matière de réserve RM2 une région située sur la pellicule de nitrure 22 qui correspond à une région de formation de transistor MOS.

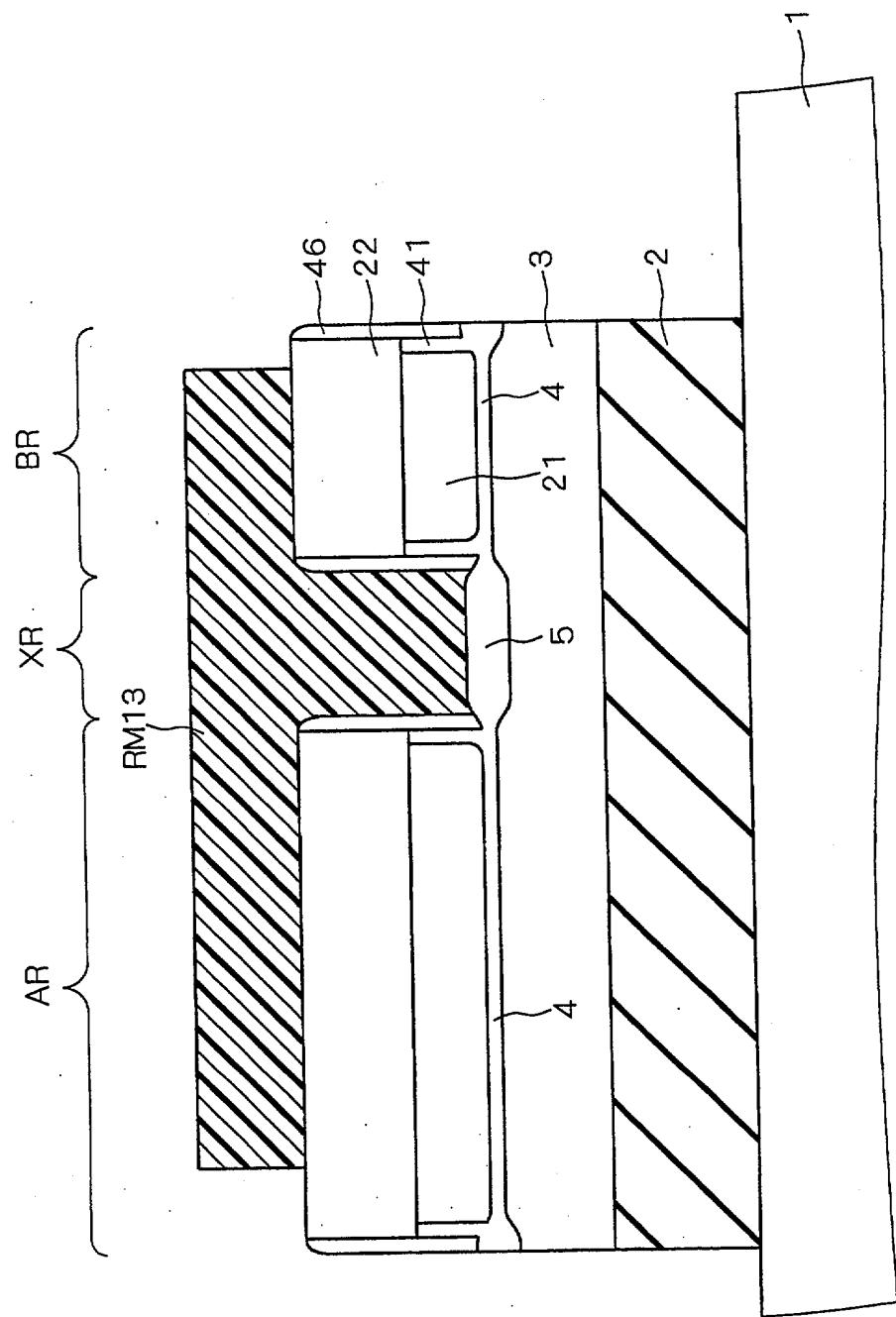

30 Ensuite, à une étape représentée sur la figure 14, on enlève sélectivement la pellicule de nitrure 22 et la pellicule de silicium polycristallin 21, par gravure par voie sèche ou gravure par voie humide, en utilisant le masque de matière de réserve RM2 à titre de masque de gravure.

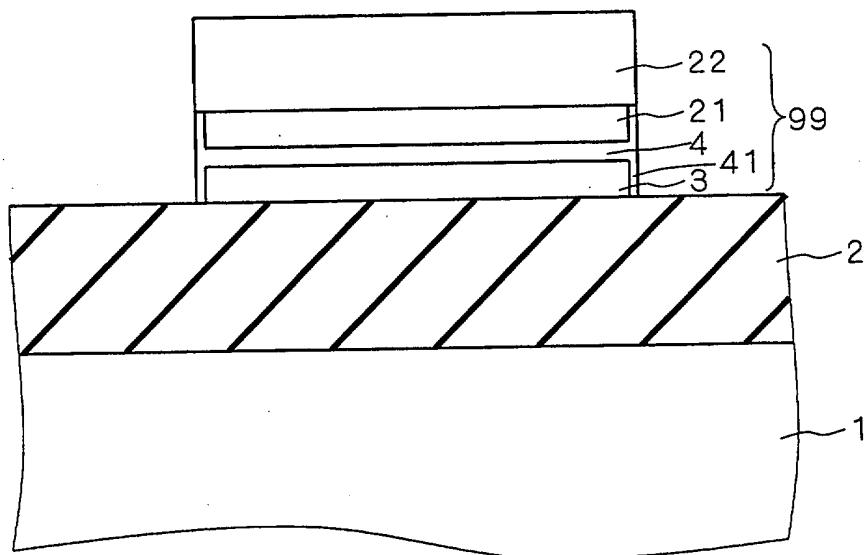

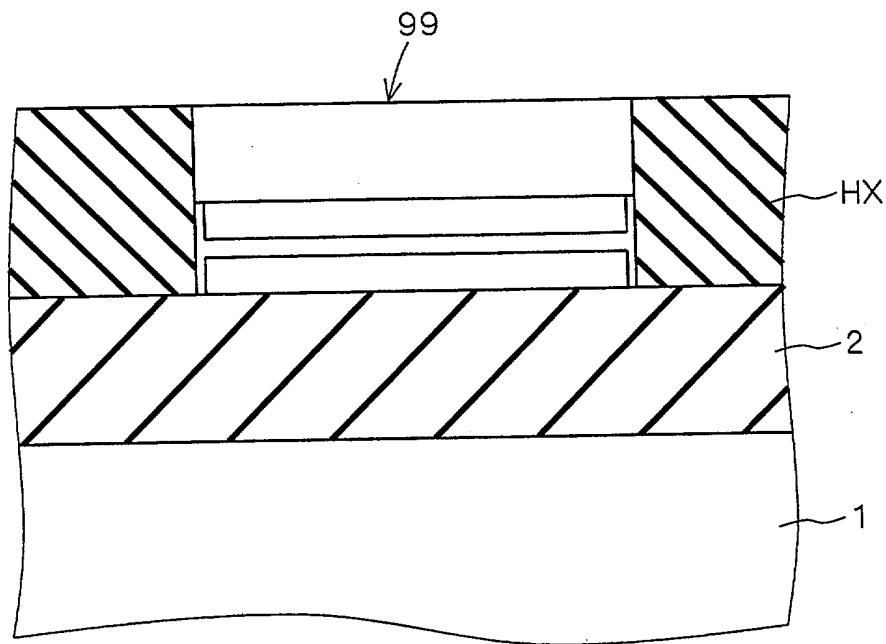

En outre, en utilisant en tant que masque de gravure la pellicule de nitrure 22 dans laquelle on a défini un motif, on enlève la pellicule d'oxyde 4 et la couche SOI 3 qui ne sont pas recouvertes par la pellicule de nitrure 22. Ainsi, une pellicule multicoche 99 5 comprenant la pellicule de nitrure 22, la pellicule de silicium polycristallin 21, la pellicule d'oxyde 4 et la couche SOI 3 est laissée seulement dans la région de formation de transistor MOS.

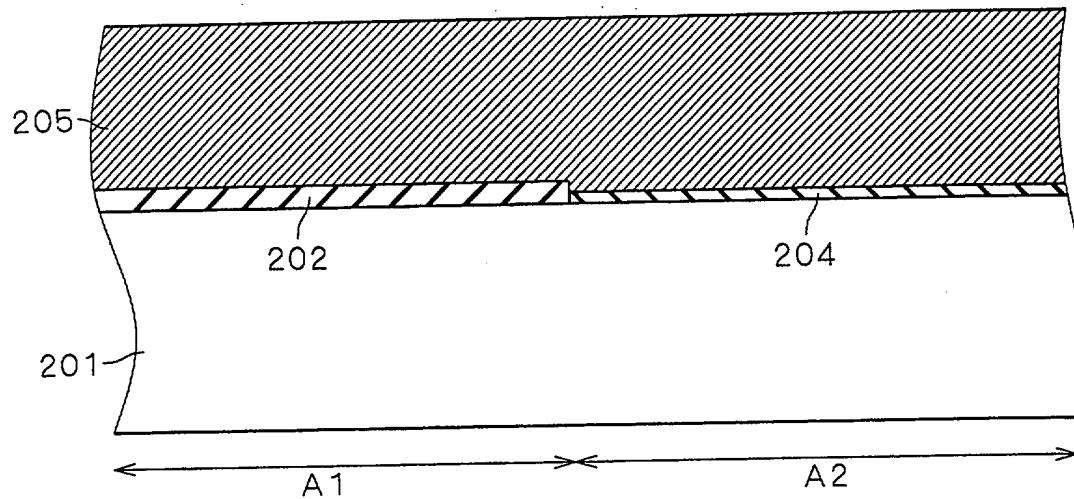

Ensuite, on forme par oxydation thermique une pellicule d'oxyde de paroi latérale 41 sur des surfaces latérales à nu de la 10 couche SOI 3 et de la couche de silicium polycristallin 21.

A une étape représentée sur la figure 15, on forme ensuite sur la totalité de la surface du substrat une pellicule d'oxyde ( $\text{SiO}_2$ ) HX par un procédé utilisant un plasma à haute densité et le dépôt chimique en phase vapeur, ou HDP (High Densité Plasma) - CVD, 15 pour couvrir ainsi la pellicule multicoche 99. Ensuite, on aplanit la pellicule d'oxyde HX par un traitement de polissage mécano-chimique ou CMP (Chemical Mechanical Polishing), pour mettre à nu une surface supérieure de la pellicule de nitrure 22.

Le procédé HDP-CVD utilise un plasma ayant une densité 20 supérieure d'un ou de deux ordres de grandeur à celle d'un procédé de CVD par plasma général, et il forme une pellicule d'oxyde tout en effectuant en même temps une pulvérisation cathodique et un dépôt. Il est donc possible d'obtenir une pellicule d'oxyde ayant une qualité de pellicule élevée.

25 Ensuite, à une étape représentée sur la figure 16, on réduit une épaisseur de la pellicule d'oxyde HX par la gravure par voie humide, et on enlève la pellicule de nitrure 22 avec de l'acide phosphorique à chaud, et en outre on enlève la pellicule de silicium polycristallin 21. Par conséquent, il est possible d'obtenir une structure dans 30 laquelle la pellicule d'oxyde 4 est laissée sur la couche SOI 3 définie par une pellicule d'oxyde d'isolation par tranchée parfaite FT.

La pellicule de silicium polycristallin 21 peut être enlevée 35 par gravure par voie humide en utilisant une solution mélangée comprenant une solution alcaline, par exemple une solution de KOH (hydroxyde de potassium) ou de l'ammoniaque et du peroxyde d'hydro-

gène aqueux, ou par une gravure par voie sèche ayant une sélectivité vis-à-vis d'une pellicule d'oxyde.

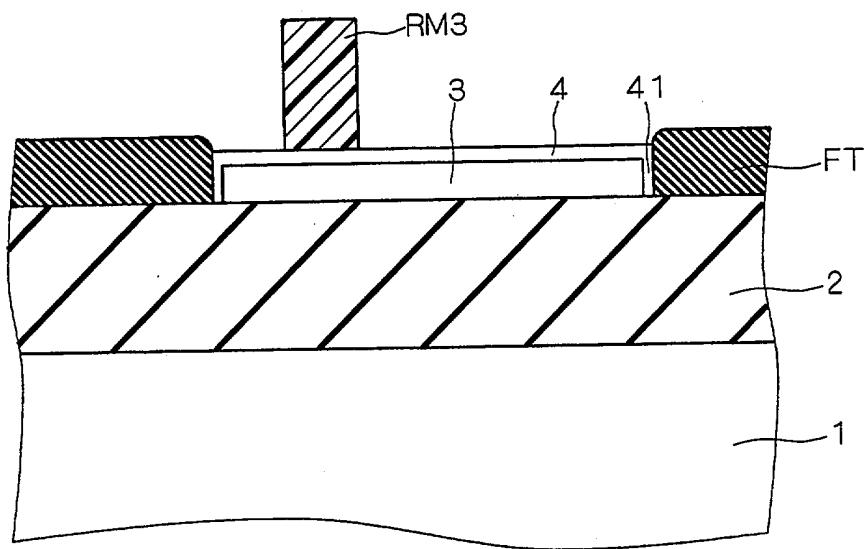

Ensuite, on définit un motif dans un masque de matière de réserve RM 3 pour couvrir une région prédéterminée de la pellicule d'oxyde 4. La région couverte par le masque de matière de réserve RM 3 remplit la fonction d'une région pour une pellicule isolante de grille épaisse.

Ensuite à une étape représentée sur la figure 17, on enlève par la gravure par voie humide la pellicule d'oxyde 4 dans une région qui n'est pas couverte par le masque de matière de réserve RM 3.

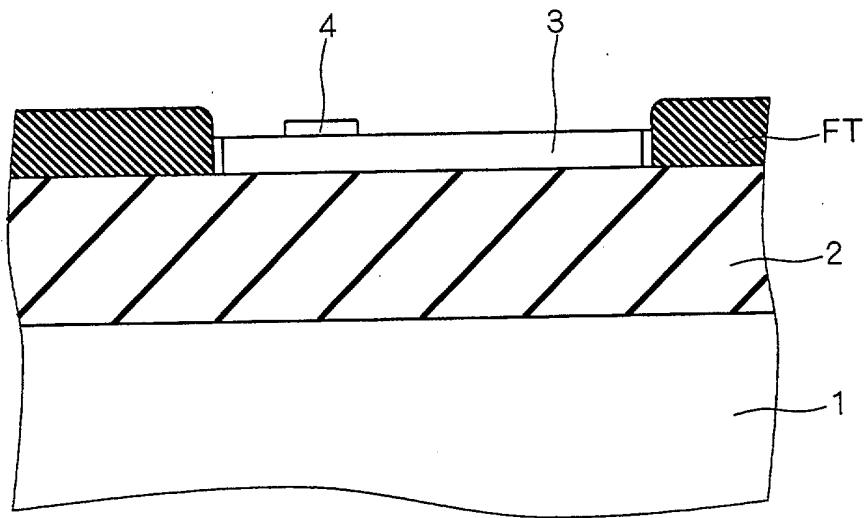

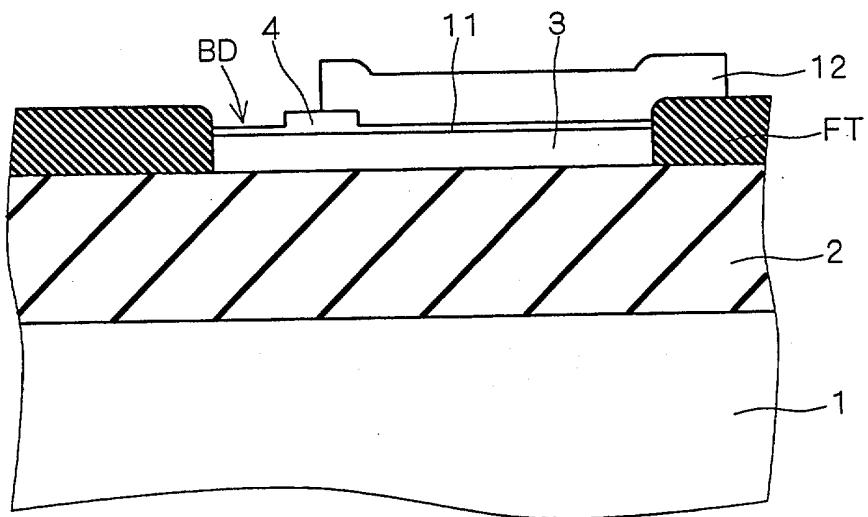

Ensuite, à une étape représentée sur la figure 18, on forme une pellicule isolante de grille mince 11 par oxydation de grille, et on définit ensuite un motif d'une électrode de grille 12. A ce moment, l'électrode de grille 12 est formée de façon que l'une des extrémités de l'électrode de grille 12 dans une direction d'une largeur de grille soit en contact avec la pellicule d'oxyde 4.

Par les étapes indiquées ci-dessus, il est possible d'obtenir une structure dans laquelle la pellicule isolante de grille 11 ayant une épaisseur relativement faible et la pellicule isolante de grille 4 ayant une épaisseur relativement grande sont formées en continuité dans la direction de la largeur de grille. Par conséquent, l'électrode de grille 12 est formée sur la couche SOI 3 avec les pellicules isolantes de grille 11 et 14 interposées entre elles.

En outre, une partie de contact de corps BD est formée dans une surface de la couche SOI 3 à l'extérieur de l'extrémité de l'électrode de grille 11 du côté où la pellicule isolante de grille 4 doit être formée.

Bien que la figure 18 montre une structure dans laquelle la pellicule isolante de grille mince 11 est formée sur la partie de contact de corps BD, il est également possible d'employer une structure dans laquelle la pellicule isolante de grille 4 est formée sur la partie de contact de corps BD comme représenté sur la figure 19. En changeant le motif du masque de matière de réserve RM 3 représenté sur la figure 16, il est possible de fixer de la manière désirée une région dans laquelle la pellicule isolante de grille 4 doit être laissée.

### D-2. Fonction et Effet

Conformément au procédé de fabrication du quatrième mode de réalisation décrit ci-dessus, la pellicule d'oxyde sous-jacente est également utilisée comme la pellicule isolante de grille épaisse. Par conséquent, il est possible d'omettre un processus pour former la pellicule isolante de grille épaisse, et le processus peut ainsi être simplifié, ce qui permet d'éviter une augmentation d'un coût de fabrication.

### D-3. Exemple Appliqué

Par l'application du procédé de fabrication conforme au quatrième mode de réalisation, il est possible de former, sur un substrat SOI commun et dans un processus de fabrication simplifié, quatre sortes de transistors MOS incluant deux sortes de transistors MOS ayant des pellicules isolantes de grille qui ont des épaisseurs différentes, et deux sortes de transistors MOS dans lesquels une pellicule isolante de grille ayant une relativement faible épaisseur et une pellicule isolante de grille ayant une relativement grande épaisseur sont formées en continuité dans la direction de la largeur de grille, et la fixation de potentiel de corps peut être effectuée. Il est donc possible d'éviter une augmentation d'un coût de fabrication.

On décrira ci-dessous le procédé en référence aux figures 20 à 26 qui sont des représentations en coupe montrant le processus de fabrication, dans l'ordre.

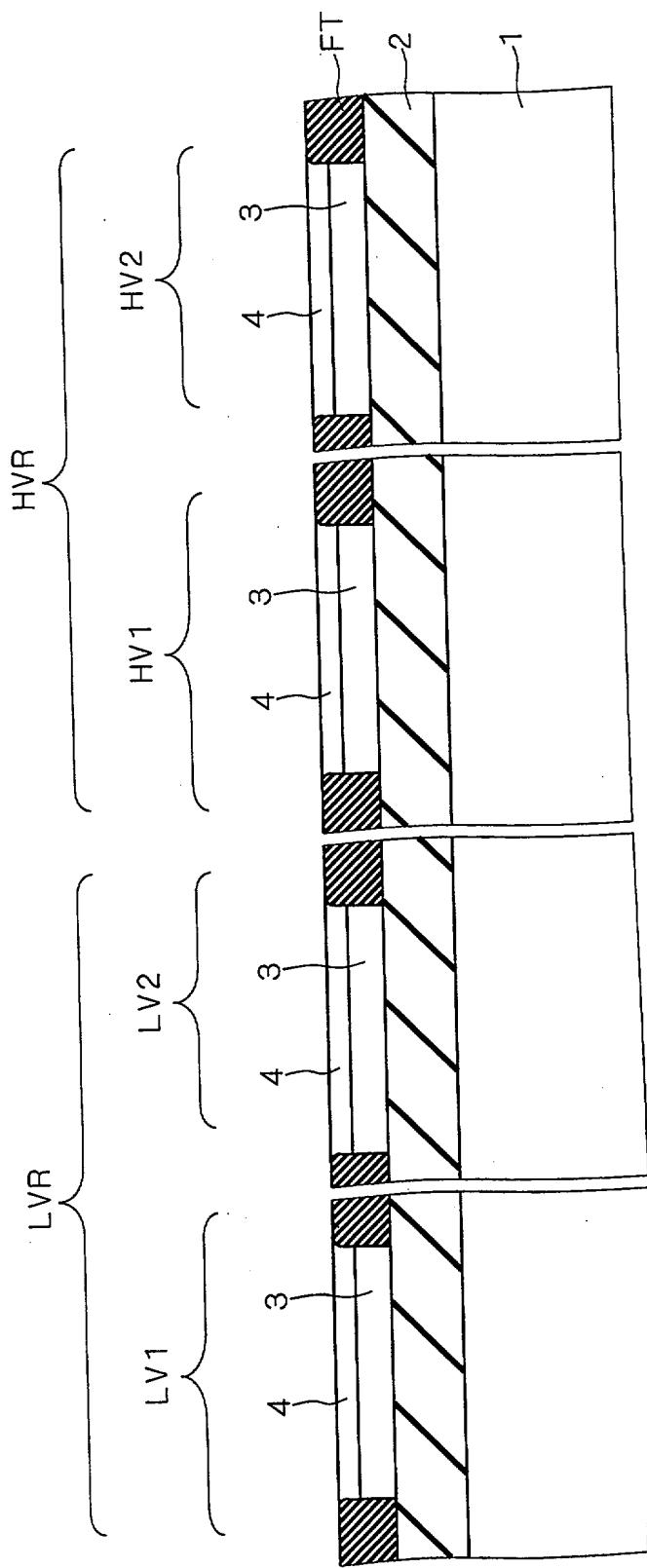

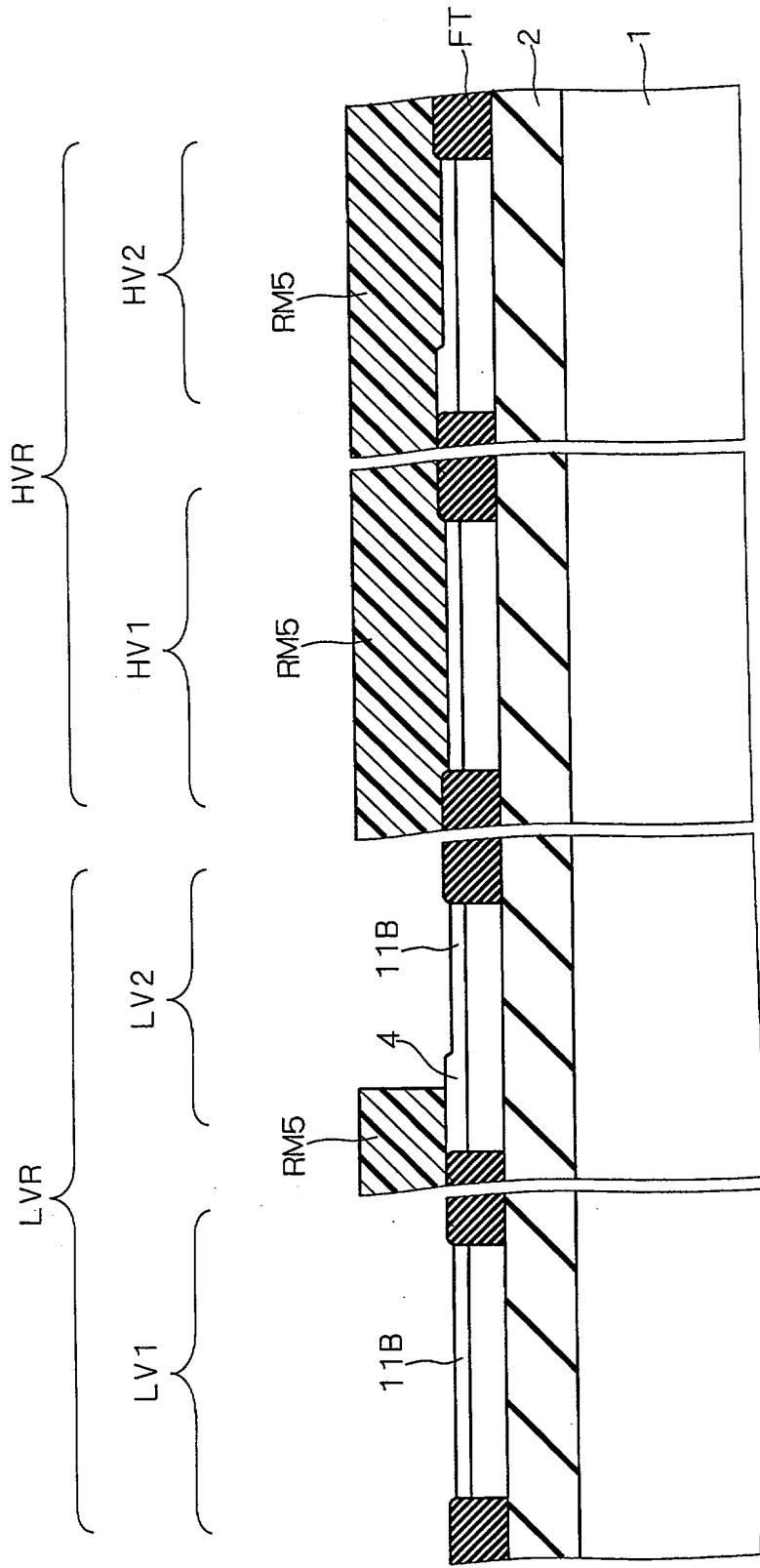

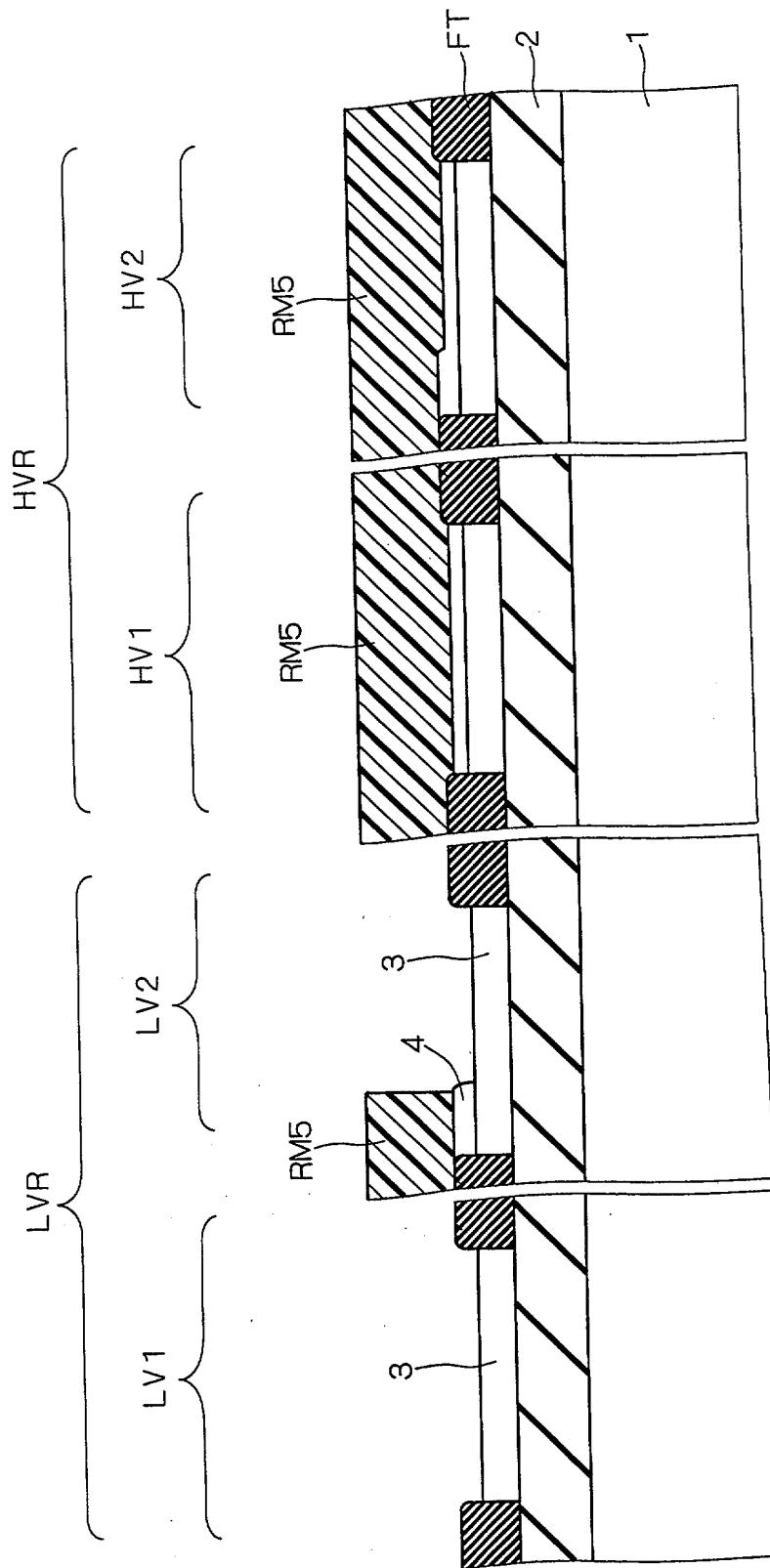

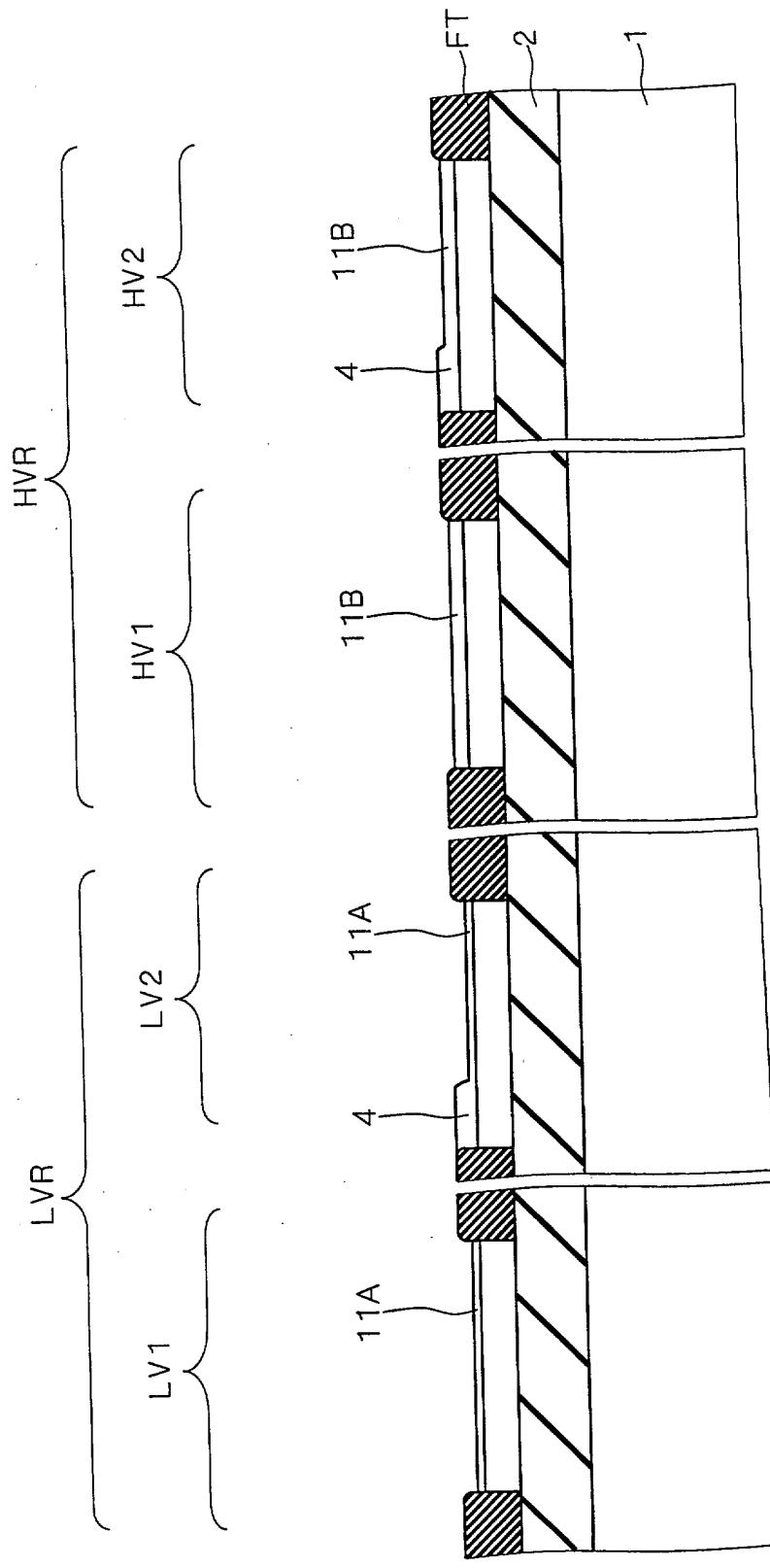

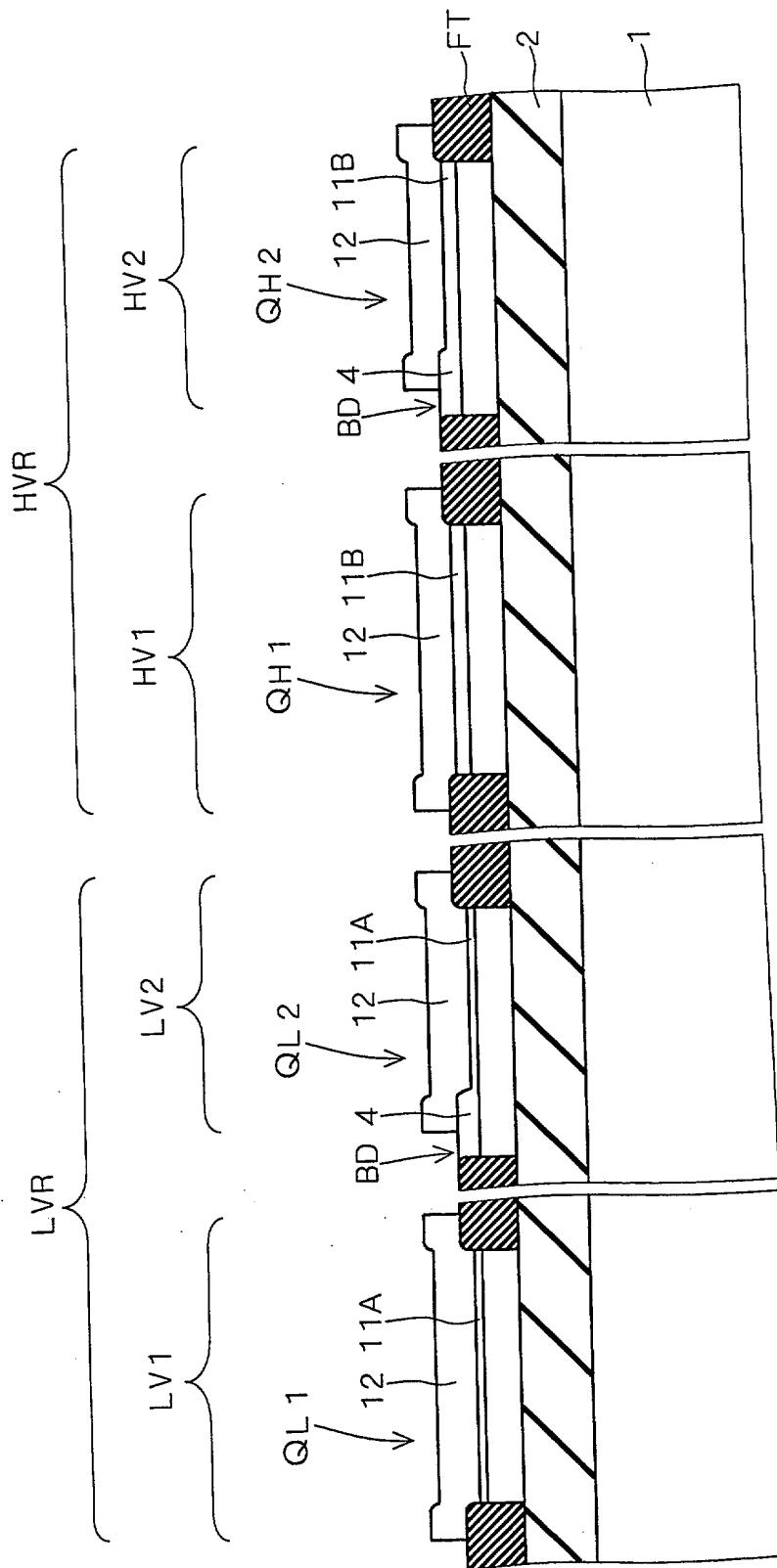

En premier lieu, les étapes décrites en référence aux figures 13 à 16 sont accomplies pour obtenir une structure dans laquelle une pellicule d'oxyde 4 est formée sur une multiplicité de régions d'une couche SOI 3 définies par une pellicule d'oxyde d'isolation par tranchée parfaite FT, comme représenté sur la figure 20. La pellicule d'oxyde 4 a une épaisseur de 7 à 30 nm.

Les régions de la couche SOI 3 sont classées en régions LV1, LV2, HV1 et HV2. Dans les régions LV1 et LV2, on doit former par exemple un transistor de tension basse ayant une tension de grille de 0,5 à 2,0 V. Les régions LV1 et LV2 sont formées dans une région de tension basse LVR.

En outre, dans les régions HV1 et HV2, on doit former par exemple un transistor de tension élevée ayant une tension de grille de 1,5 à 5,0 V. Les régions HV1 et HV2 sont formées dans une région de tension élevée HVR.

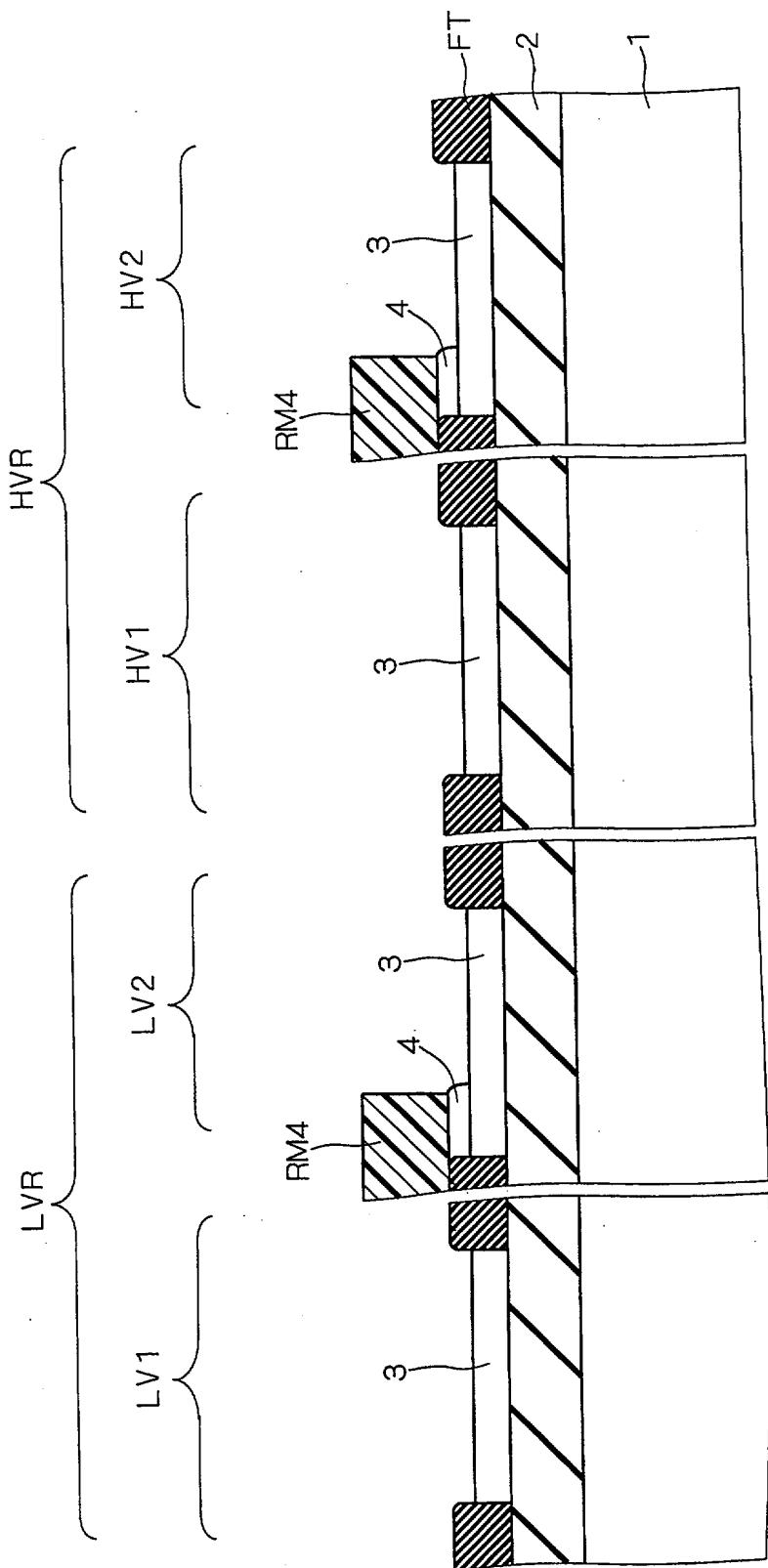

5       Ensuite, à une étape représentée sur la figure 21, on définit un motif d'un masque de matière de réserve RM4 pour couvrir une région prédéterminée sur la pellicule d'oxyde 4 dans les régions LV2 et HV2. La région couverte par le masque de matière de réserve RM4 remplit la fonction d'une pellicule isolante de grille épaisse.

10      Ensuite, on enlève la pellicule d'oxyde 4 dans une région qui n'est pas couverte par le masque de matière de réserve RM4, par gravure par voie humide en utilisant de l'acide fluorhydrique (HF) ou une substance similaire.

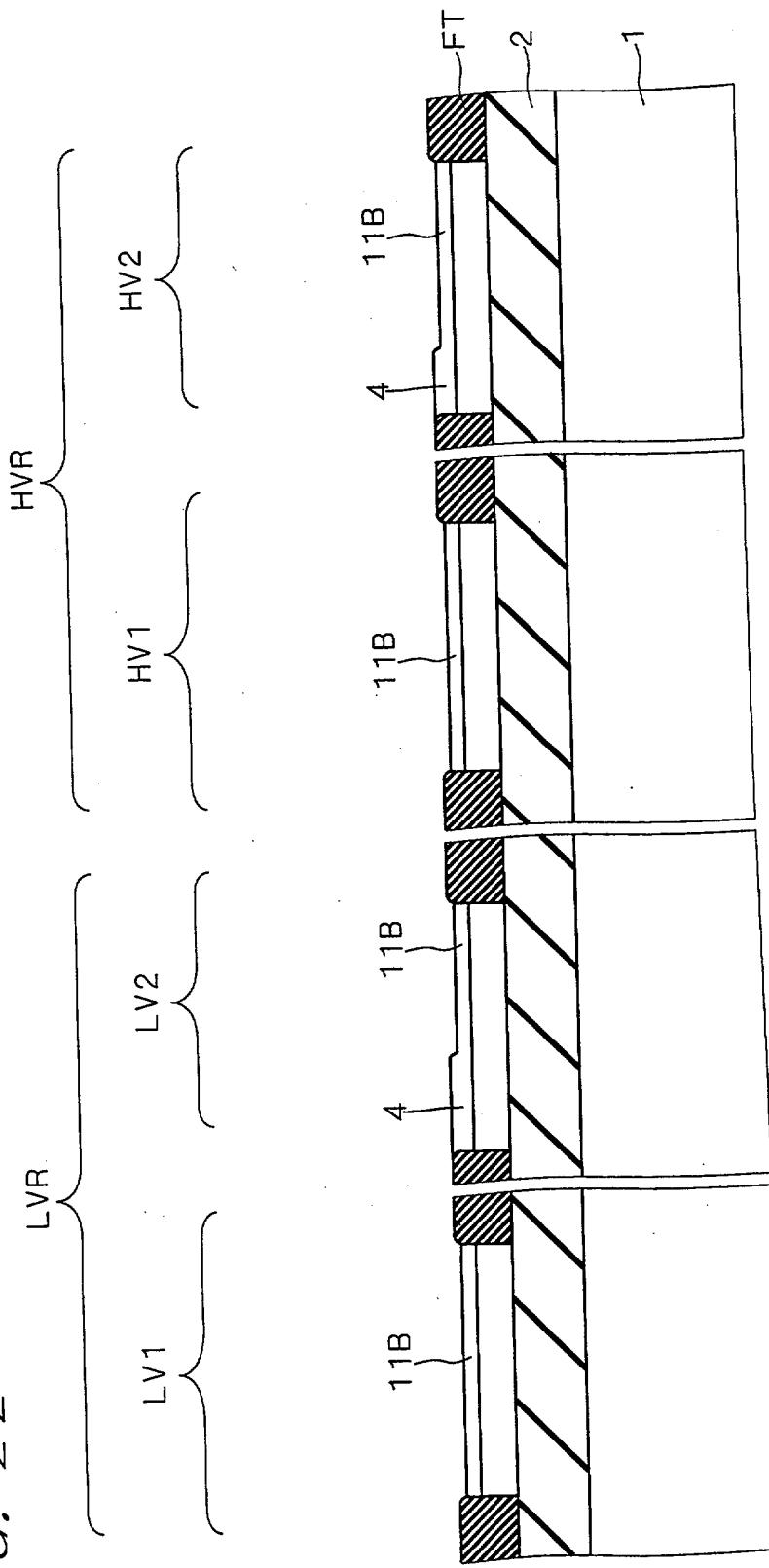

Ensuite, on enlève le masque de matière de réserve RM4 et 15 on forme ensuite une pellicule isolante de grille 11B sur la couche SOI 3 à nu, par oxydation de grille à une étape représentée sur la figure 22. La pellicule isolante de grille 11B a une épaisseur de 3 à 10 nm.

Ensuite, à une étape représentée sur la figure 23, on définit 20 un motif dans un masque de matière de réserve RM5 pour couvrir une région complète de la région de tension élevée HVR et une région prédéterminée sur la pellicule d'oxyde 4 dans la région LV2. Le masque de matière de réserve RM5 est également formé sur la pellicule d'oxyde 4 dans la région LV2 afin de laisser seulement la pellicule d'oxyde 4 dans une partie couverte par le masque de matière de réserve RM5. A l'étape représentée sur la figure 21, la pellicule d'oxyde 4 est laissée dans une région plus grande que la région qui sera finalement exigée. A l'étape représentée sur la figure 23, la pellicule d'oxyde 4 est réduite à la région qui sera finalement exigée. 25 Par une telle structure, on peut éviter qu'une étendue de la pellicule d'oxyde 4 qui sera exigée finalement dans la région LV2 soit réduite à cause d'un décalage de superposition du masque de matière de réserve RM5.

Ensuite, à une étape représentée sur la figure 24, la pellicule d'oxyde 4 dans la région qui n'est pas couverte par le masque 35

de matière de réserve RM5 est enlevée par la gravure par voie humide utilisant l'acide fluorhydrique (HF) ou une substance similaire.

Ensuite, le masque de matière de réserve RM5 est enlevé et une pellicule isolante de grille 11A est formée par la suite sur la 5 couche SOI 3 à nu, par oxydation de grille, à une étape représentée sur la figure 25. La pellicule isolante de grille 11A a une épaisseur de 1 à 5 nm.

A une étape représentée sur la figure 26, le motif d'une électrode de grille 12 est ensuite défini dans chacune des régions 10 LV1, LV2, HV1 et HV2. A ce moment, dans les régions LV2 et HV2, l'électrode de grille 12 est formée de façon que l'une des extrémités de l'électrode de grille 12 dans une direction d'une largeur de grille vienne en contact avec la pellicule d'oxyde 4.

Par les étapes mentionnées ci-dessus, des transistors flottants 15 QL1 et QH1 ayant des pellicules isolantes de grille 11A et 11B sont obtenus dans les régions LV1 et HV1, un transistor QL2 dans lequel la pellicule isolante de grille 11A ayant la plus petite épaisseur et la pellicule isolante de grille 4 ayant la plus grande épaisseur sont formées en continuité dans une direction d'une largeur de grille 20 et une fixation de potentiel de corps peut être effectuée, est obtenu dans la région LV2, et un transistor QH2 dans lequel la pellicule isolante de grille 11B ayant une épaisseur moyenne et la pellicule isolante de grille 4 ayant la plus grande épaisseur sont formées en continuité dans la direction de la largeur de grille, et la fixation de 25 potentiel de corps peut être effectuée, est obtenu dans la région HV2. Il est donc possible d'obtenir au total quatre sortes de transistors MOS par le processus de fabrication simplifié.

Une partie de contact de corps BD est formée dans une 30 surface de la couche SOI 3 à l'extérieur de l'extrémité de l'électrode de grille 12 du côté où la pellicule isolante de grille 4 des transistors QL2 et QH2 doit être formée.

Dans le cas où la pellicule d'oxyde 4 a une épaisseur de 35 7,2 nm, par exemple, et la pellicule isolante de grille 11B ayant une épaisseur de 3,5 nm est formée par oxydation de grille à l'étape représentée sur la figure 22, l'épaisseur de la pellicule d'oxyde 4 est

augmentée d'environ 0,3 nm par l'oxydation de grille et n'est pas fortement changée.

#### E. Cinquième Mode de Réalisation

Alors que la pellicule isolante de grille épaisse est formée 5 sur la totalité de la surface de la couche SOI dans la région active et la région dans laquelle la pellicule isolante de grille épaisse doit être laissée est ensuite définie par le motif de masque dans le premier mode de réalisation décrit en référence aux figures 1 et 2, et le second mode de réalisation décrit en référence aux figures 8 à 11, une 10 pellicule isolante de grille épaisse peut également être obtenue par un procédé de fabrication qu'on décrira ci-dessous à titre de cinquième mode de réalisation.

##### E-1. Procédé de Fabrication

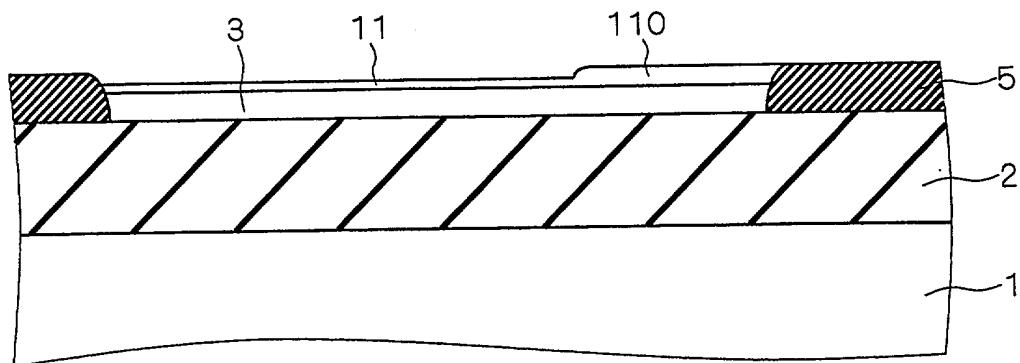

On décrira le procédé de fabrication conforme au cinquième 15 mode de réalisation en se référant aux figures 27 à 33 qui sont des coupes montrant un processus de fabrication, dans l'ordre.

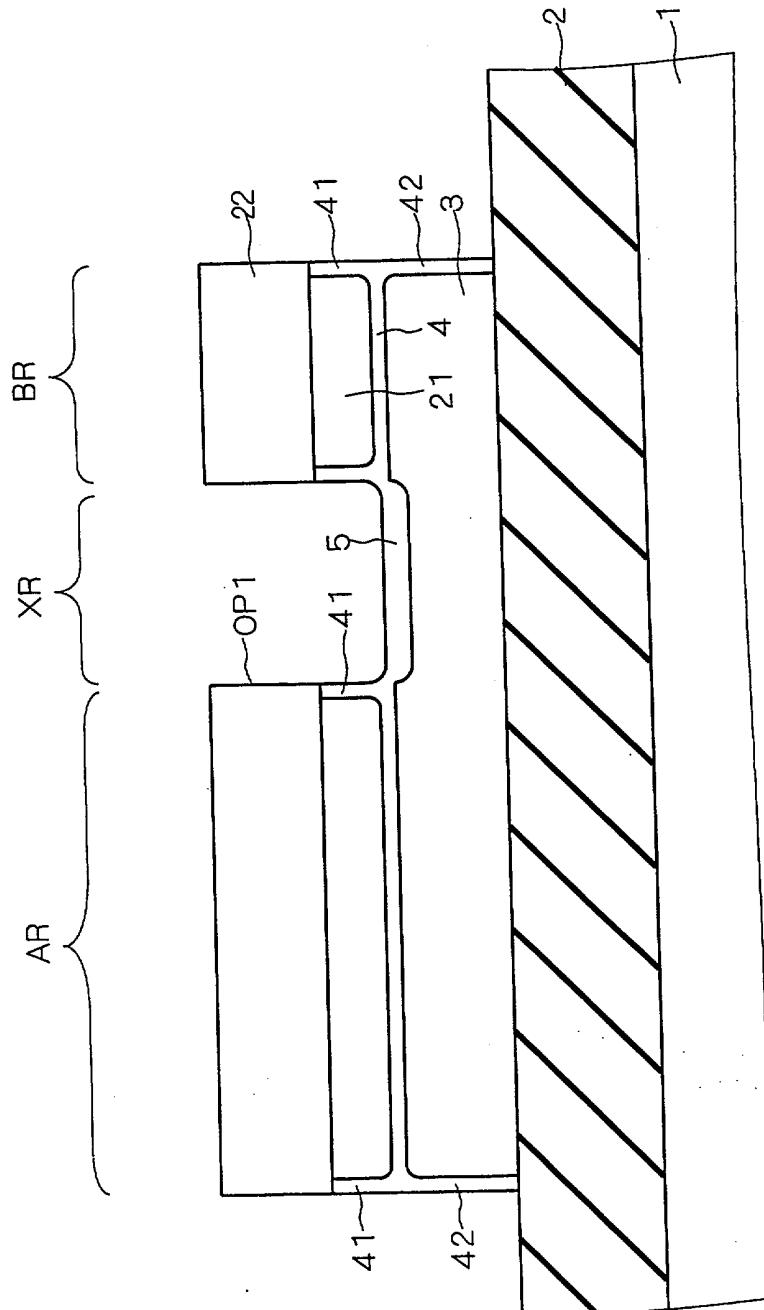

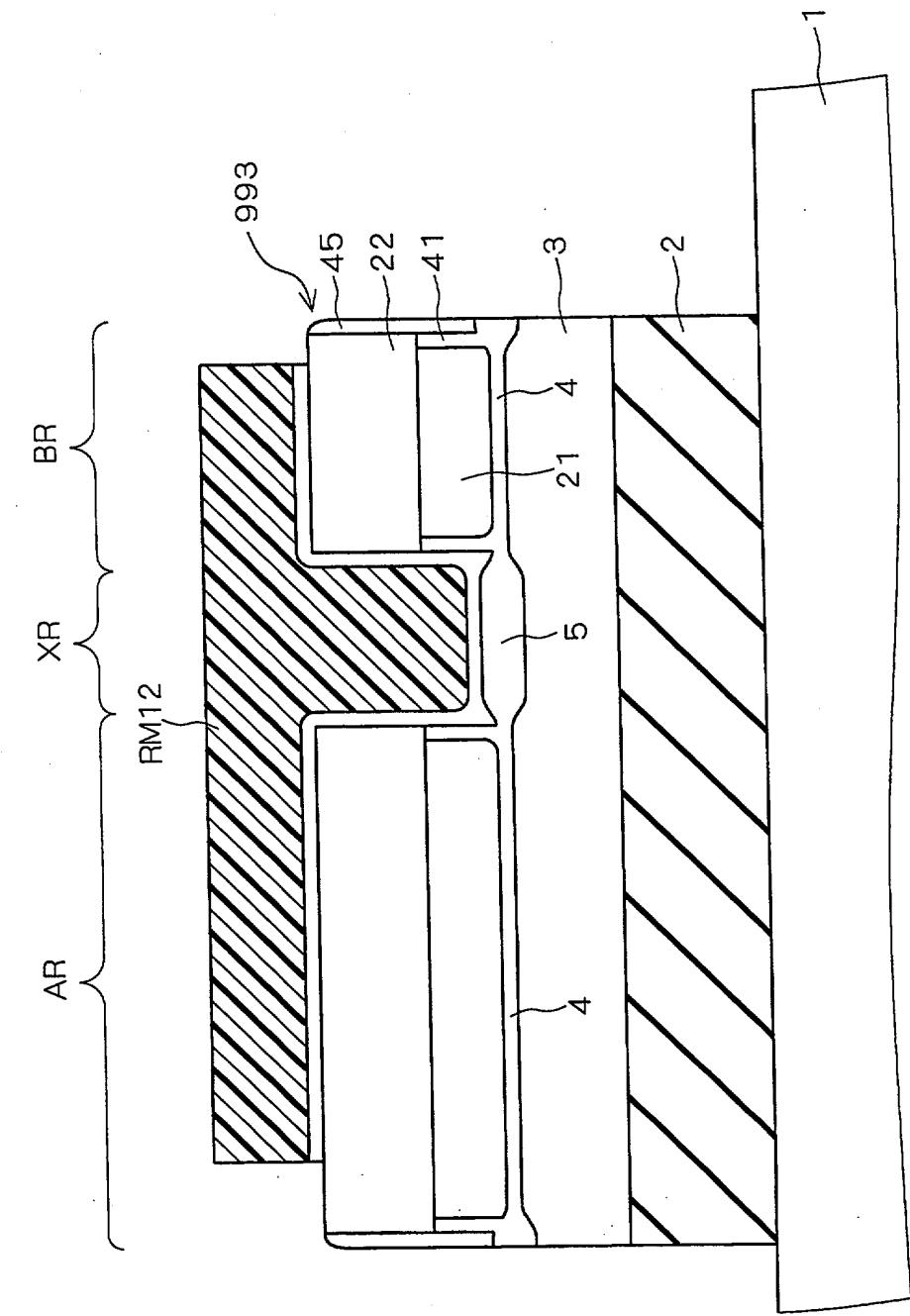

Comme représenté sur la figure 27, en premier lieu, on prépare un substrat SOI et on forme une pellicule d'oxyde 4 sur une couche SOI 3 du substrat SOI. La pellicule d'oxyde 4 est ce qu'on 20 appelle une pellicule d'oxyde sous-jacente (une pellicule d'oxyde de plage).

Ensuite, on forme une pellicule de silicium polycristallin 21 sur la pellicule d'oxyde 4 par un procédé CVD, et on forme une pellicule de nitre 22 sur la pellicule de silicium polycristallin 21 par le 25 procédé CVD. Du fait que la pellicule d'oxyde 4, la pellicule de silicium polycristallin 21 et la pellicule de nitre 22 remplissent des fonctions auxiliaires pour former une pellicule d'oxyde isolante, on les appelle également dans certains cas des pellicules auxiliaires. La pellicule de silicium polycristallin 21 n'est pas toujours exigée.

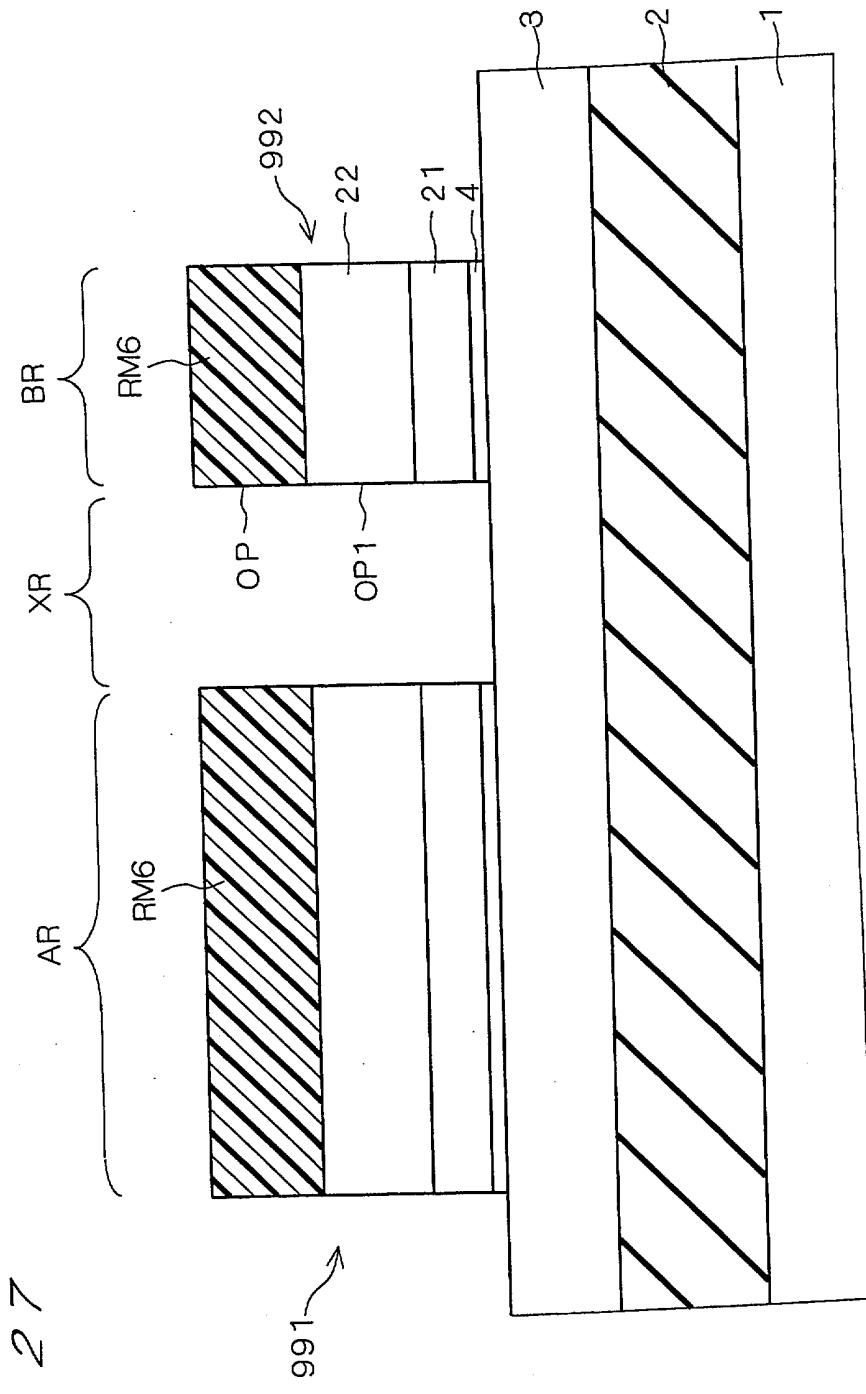

Ensuite, on recouvre par un masque de matière de réserve RM6 une région active AR d'un transistor MOS et une région sur la pellicule de nitre 22 correspondant à une région BR dans laquelle une partie de contact de corps doit être formée.

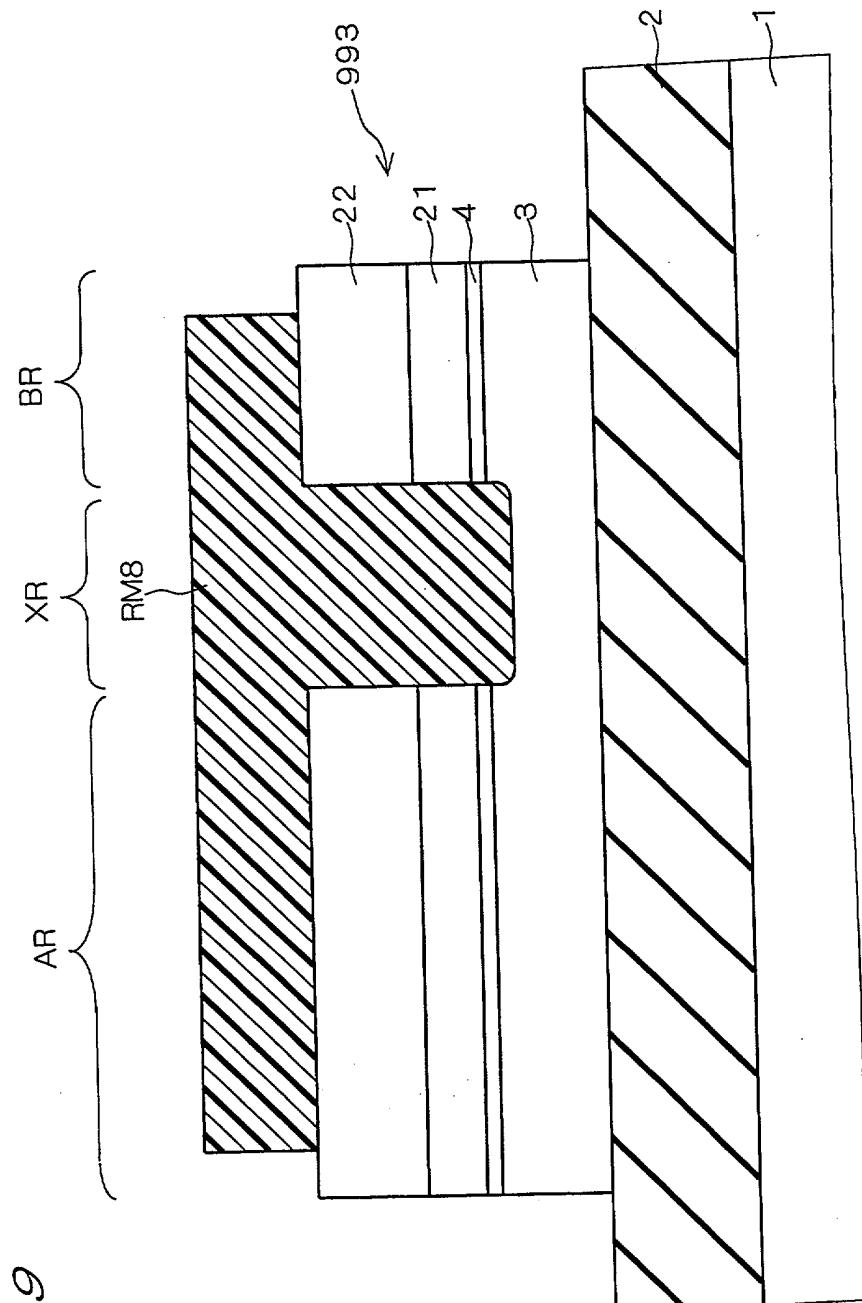

A ce moment, on définit un motif dans le masque de ma-

tière de réserve RM6 de façon qu'une région XR dans laquelle une pellicule isolante de grille épaisse doit être formée remplit la fonction d'une partie d'ouverture OP.

Ensuite, on enlève sélectivement la pellicule de nitrure 22 5 et la pellicule de silicium polycristallin 21 par gravure par voie sèche ou gravure par voie humide, en utilisant le masque de matière de réserve RM6 à titre de masque de gravure.

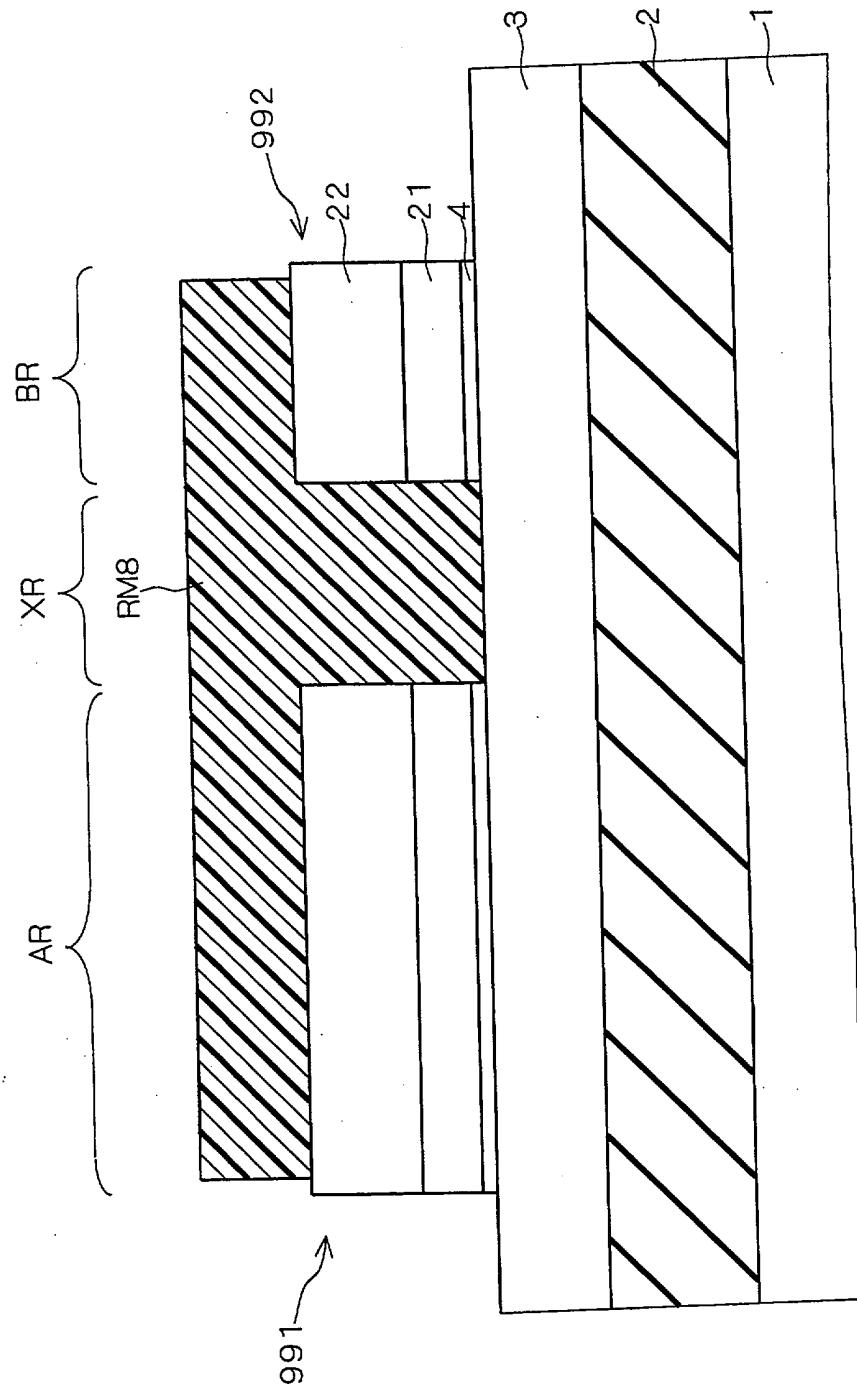

En outre, on enlève la pellicule d'oxyde 4 et la couche SOI 10 3 qui ne sont pas couvertes par la pellicule de nitrure 22, en utilisant à titre de masque de gravure la pellicule de nitrure 22 dans laquelle on a défini un motif, ce qui laisse des pellicules multicoches 991 et 992 comprenant la pellicule de nitrure 22, la pellicule de silicium polycristallin 21 et la pellicule d'oxyde 4, seulement dans la région active AR du transistor MOS et dans la région de formation de partie 15 de contact de corps BR. La région XR remplit la fonction d'une partie d'ouverture inférieure OP1 et la couche SOI 3 est à nu dans une partie de fond de celle-ci.

Une largeur W de la pellicule multicoche 991 correspond à 20 une largeur de grille du transistor MOS qui sera formé ultérieurement.

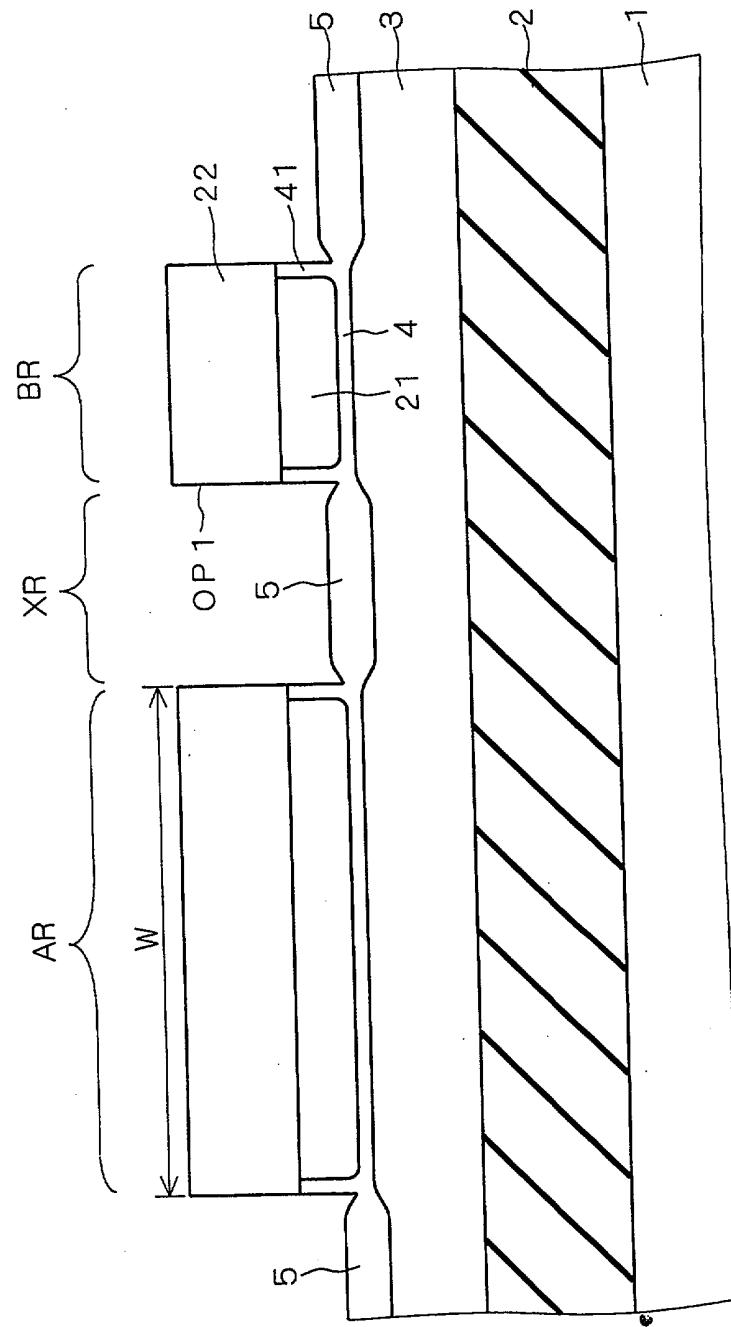

Ensuite, on enlève le masque de matière de réserve RM6 après quoi on effectue une oxydation thermique pour former une pellicule d'oxyde 5 ayant une épaisseur de 10 à 40 nm sur une surface de la couche SOI 3, incluant une surface de fond de la partie d'ouverture OP1, à une étape représentée sur la figure 28. A ce moment, 25 une pellicule d'oxyde 41 est également formée sur une paroi latérale à nu de la pellicule de silicium polycristallin 21 (oxydation de paroi latérale).

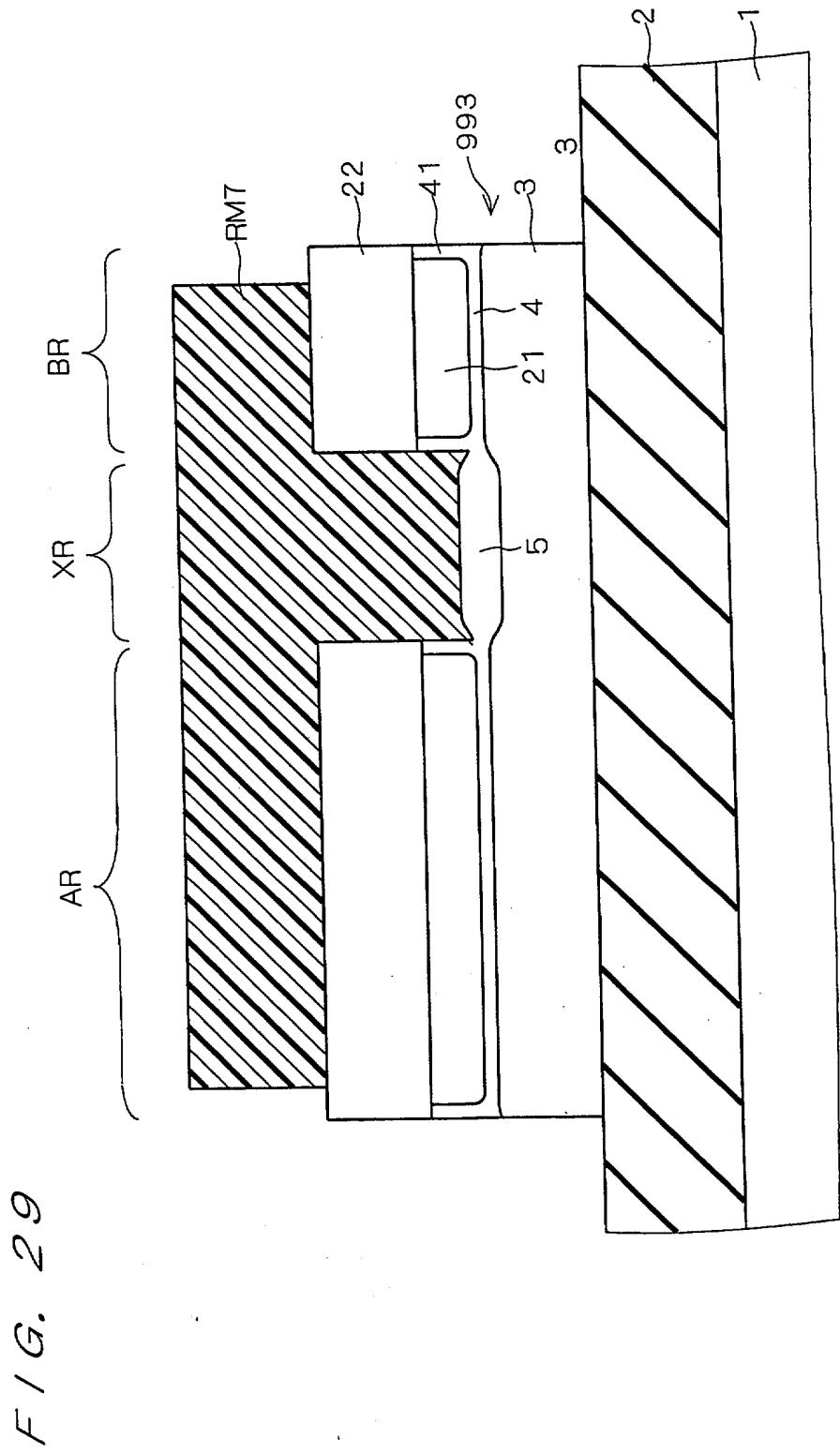

Ensuite, à une étape représentée sur la figure 29, on forme 30 un masque de matière de réserve RM7 de façon à couvrir seulement la région active AR du transistor MOS, la région de formation de partie de contact de corps BR et la région XR dans laquelle la pellicule isolante de grille épaisse doit être formée. Le masque de matière de réserve RM7 a un motif d'ouverture pour définir une région dans laquelle une pellicule d'oxyde d'isolation par tranchée parfaite doit 35

être formée ultérieurement, et la pellicule d'oxyde d'isolation par tranchée parfaite est formée dans une région qui n'est pas couverte par le masque de matière de réserve RM7.

En utilisant le masque de matière de réserve RM7 à titre de masque de gravure, on enlève la pellicule d'oxyde 5 et la couche SOI 3 dans la région qui n'est pas couverte par le masque de matière de réserve RM7. Par conséquent, une pellicule multicouche 993 comportant la pellicule de nitre 22, la pellicule de silicium polycristallin 21, la pellicule d'oxyde 4 et la couche SOI 3 est formée.

Sur la figure 29, le masque de matière de réserve RM7 ne couvre pas complètement la pellicule de nitre 22, en considération du fait que le masque de matière de réserve RM7 occasionne un décalage de superposition dans un processus réel. Même si le masque de matière de réserve RM7 occasionne ainsi le décalage de superposition, il remplit la fonction du masque de gravure du fait que la pellicule de nitre 22 est présente. Une largeur de grille du transistor MOS est déterminée par une largeur de la pellicule de nitre 22 dans la région BR, ce qui fait que le masque de matière de réserve RM7 n'est pas influencé par le décalage de superposition.

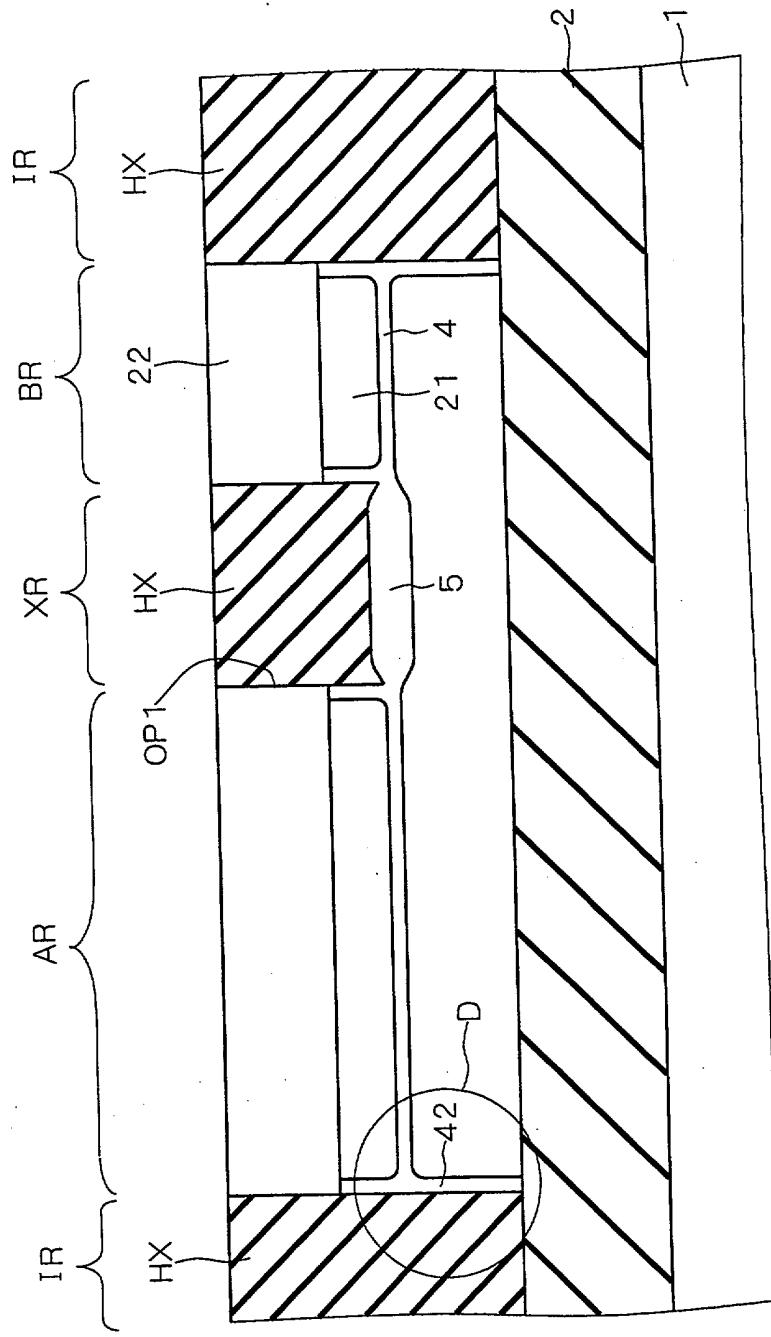

Ensuite, on enlève le masque de matière de réserve RM7 après quoi on effectue une oxydation thermique à une étape représentée sur la figure 30, pour former ainsi une pellicule d'oxyde 42 ayant une épaisseur de 3 à 30 nm sur une paroi latérale à nu de la couche SOI 3 (oxydation de paroi latérale). Ensuite, on forme une pellicule d'oxyde ( $\text{SiO}_2$ ) HX sur la totalité de la surface du substrat par un procédé HDP-CVD, pour recouvrir la pellicule multicouche 993, et on aplani ensuite la pellicule d'oxyde HX par un traitement de polissage mécano-chimique (CMP) pour mettre à nu une surface supérieure de la pellicule de nitre 22. Par conséquent, la pellicule d'oxyde HX remplit une région IR dans laquelle une pellicule d'oxyde d'isolation par tranchée parfaite doit être formée ultérieurement, et la partie d'ouverture OP1 de la région XR.

Ensuite, à une étape représentée sur la figure 31, on réduit une épaisseur de la pellicule d'oxyde HX par la gravure par voie humide, et on enlève la pellicule de nitre 22 avec de l'acide phospho-

rique chaud, et en outre, on enlève la pellicule de silicium polycristallin 21. Par conséquent, il est possible d'obtenir une structure dans laquelle les pellicules d'oxyde 4 et 5 sont laissées sur la couche SOI 3 définie par une pellicule d'oxyde d'isolation par tranchée parfaite FT.

On peut enlever la pellicule de silicium polycristallin 21 par gravure par voie humide en utilisant une solution mélangée constituée d'une solution alcaline, par exemple une solution de KOH (hydroxyde de potassium) ou de l'ammoniaque, et de peroxyde d'hydrogène aqueux, ou par gravure par voie sèche ayant une sélectivité vis-à-vis d'une pellicule d'oxyde.

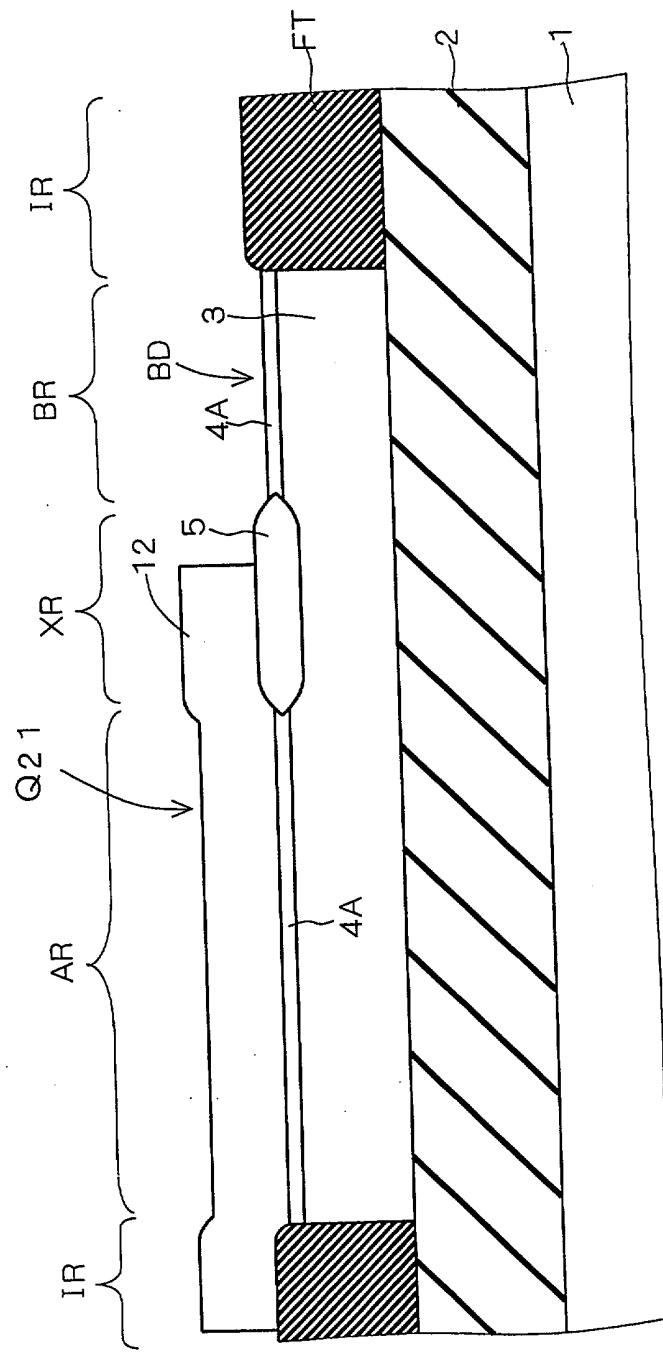

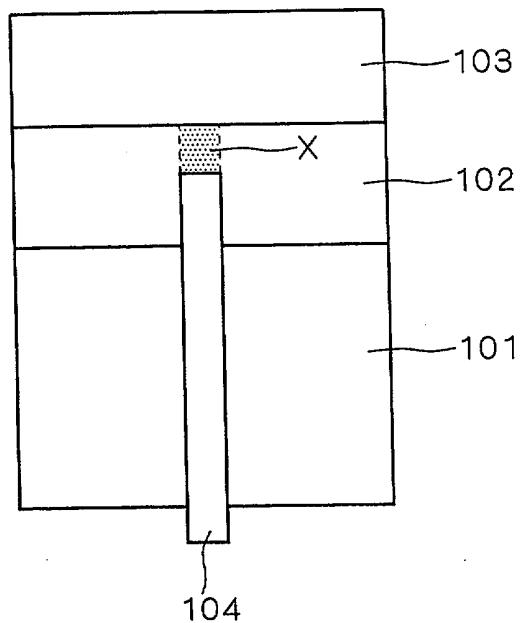

Ensuite à une étape représentée sur la figure 32, on enlève une pellicule d'oxyde 4 sous-jacente et on forme ensuite une pellicule d'oxyde 4A dans la région active AR du transistor MOS et dans la région de formation de partie de contact de corps BR. La pellicule d'oxyde 4A remplit la fonction d'une pellicule isolante de grille et son épaisseur est de préférence sélectionnée dans une plage de 1 à 10 nm, par exemple. Ensuite, on définit un motif d'une électrode de grille 12 sur la pellicule d'oxyde 4A dans la région active AR. A ce moment, on définit le motif de l'électrode de grille 12 de façon que l'une des extrémités dans une direction de la largeur de grille vienne en contact avec la pellicule d'oxyde 5, et que l'autre extrémité vienne en contact avec la pellicule d'oxyde d'isolation par tranchée parfaite FT, et qu'une partie devant être formée sur la pellicule d'oxyde 4A dans la région BR remplisse pratiquement la fonction d'une grille. On peut également appeler la pellicule d'oxyde 5 une pellicule isolante de grille, et les pellicules d'oxyde 4A et 5 constituent une pellicule isolante de grille continue. Ensuite, on forme une région de source-drain par une implantation d'une impureté de source-drain, et en outre, on forme la partie de contact de corps BD par une implantation d'impureté dans une surface de la couche SOI 3 à l'extérieur de l'extrémité de l'électrode de grille 12, du côté où la pellicule isolante de grille 5 doit être formée. On peut donc obtenir un transistor MOS Q21.

Bien qu'on ait décrit ci-dessus en référence à la figure 30

l'exemple dans lequel la pellicule d'oxyde 42 est formée sur la paroi latérale de la couche SOI 3, la figure 33 montre une structure détaillée d'une région D de la figure 30.

Comme représenté sur la figure 33, dans certains cas dans 5 lesquels la pellicule d'oxyde 42 est formée sur la paroi latérale de la couche SOI 3, comme représenté sur la figure 33, il se forme une pellicule d'oxyde 421 qui pénètre entre une surface inférieure de la couche SOI 3 et une pellicule d'oxyde enterrée 2. Lorsque la pellicule d'oxyde 421 est formée, une contrainte mécanique est appliquée à la couche SOI 3, ce qui occasionne un courant de fuite. 10

Après l'étape représentée sur la figure 29, on enlève le masque de matière de réserve RM7 et on n'effectue pas l'oxydation thermique, et la pellicule d'oxyde ( $\text{SiO}_2$ ) HX est alors formée au-dessus de la surface entière du substrat par le procédé HDP-CVD, 15 de façon à recouvrir la pellicule multicouche 993. Il est donc possible d'obtenir une structure dans laquelle la paroi latérale de la couche SOI 3 n'est pas oxydée, comme représenté sur la figure 34.

Dans certains cas dans lesquels la paroi latérale de la couche SOI 3 est endommagée par la gravure pour former la pellicule 20 d'oxyde d'isolation par tranchée parfaite représentée sur la figure 29, ceci crée la fuite de courant.

Dans ces cas, il est souhaitable que l'oxydation de paroi latérale soit effectuée pour éviter la fuite de courant.

Ainsi, il est le plus souhaitable de déterminer si l'oxydation 25 de paroi latérale de la couche SOI 3 doit être effectuée ou non, en considérant une relation de compromis entre la fuite de courant occasionnée par la pellicule d'oxyde 42 formée sur la paroi latérale de la couche SOI 3, et la fuite de courant occasionnée par l'endommagement de la paroi latérale de la couche SOI 3 par la gravure.

### 30 E-1-1. Première Variante

A la place des étapes représentées sur les figures 28 et 29, il est également possible d'employer les étapes représentées sur les figures 35 à 37 qu'on décrira ci-dessous.

De façon plus spécifique, après l'accomplissement de 35 l'étape décrite en référence à la figure 27, on enlève le masque de

matière de réserve RM6. A la place, on forme un masque de matière de réserve RM8 de façon à couvrir seulement la région active AR du transistor MOS, la région de formation de partie de contact de corps BR et la région XR dans laquelle une pellicule isolante de grille épaisse doit être formée, comme représenté sur la figure 35.

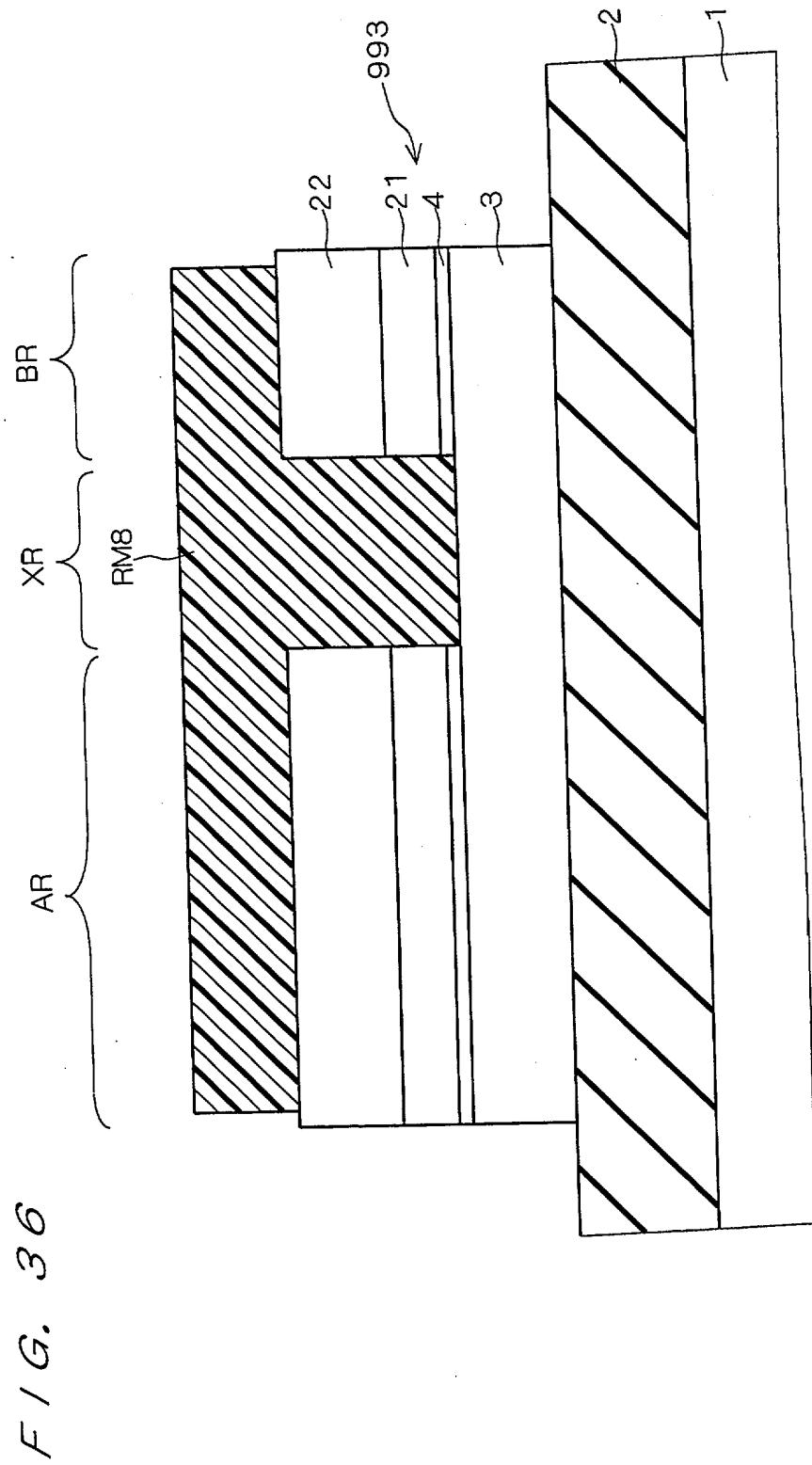

Ensuite à une étape représentée sur la figure 36, en utilisant en tant que masque de gravure le masque de matière de réserve RM8, on enlève la pellicule d'oxyde 4 et la couche SOI 3 dans la région qui n'est pas couverte par le masque de matière de réserve RM8. Par conséquent, une pellicule multicouche 993 comportant la pellicule de nitre 22, la pellicule de silicium polycristallin 21, la pellicule d'oxyde 4 et la couche SOI 3, est formée.

Ensuite, on enlève le masque de matière de réserve RM8 et on effectue ensuite une oxydation thermique à une étape représentée sur la figure 37, pour former ainsi une pellicule d'oxyde 5 ayant une épaisseur de 10 à 40 nm sur une surface de la couche SOI 3, et des pellicules d'oxyde 41 et 42 sont formées sur les parois latérales à nu de la couche de silicium polycristallin 21 et de la couche SOI 3 (oxydation de paroi latérale).

Si on emploie le procédé mentionné ci-dessus, on peut effectuer l'oxydation de paroi latérale de la couche SOI 3 simultanément à la formation de la pellicule d'oxyde 5. Par conséquent, il est possible d'obtenir un avantage consistant en ce que le processus de fabrication peut être simplifié. D'autre part, il est impossible de choisir de ne pas effectuer l'oxydation de paroi latérale de la couche SOI 3. Par conséquent, en considération de la relation de compromis avec la fuite de courant, il est souhaitable de déterminer si le procédé mentionné ci-dessus doit être employé ou non.

#### E-1-2. Seconde Variante

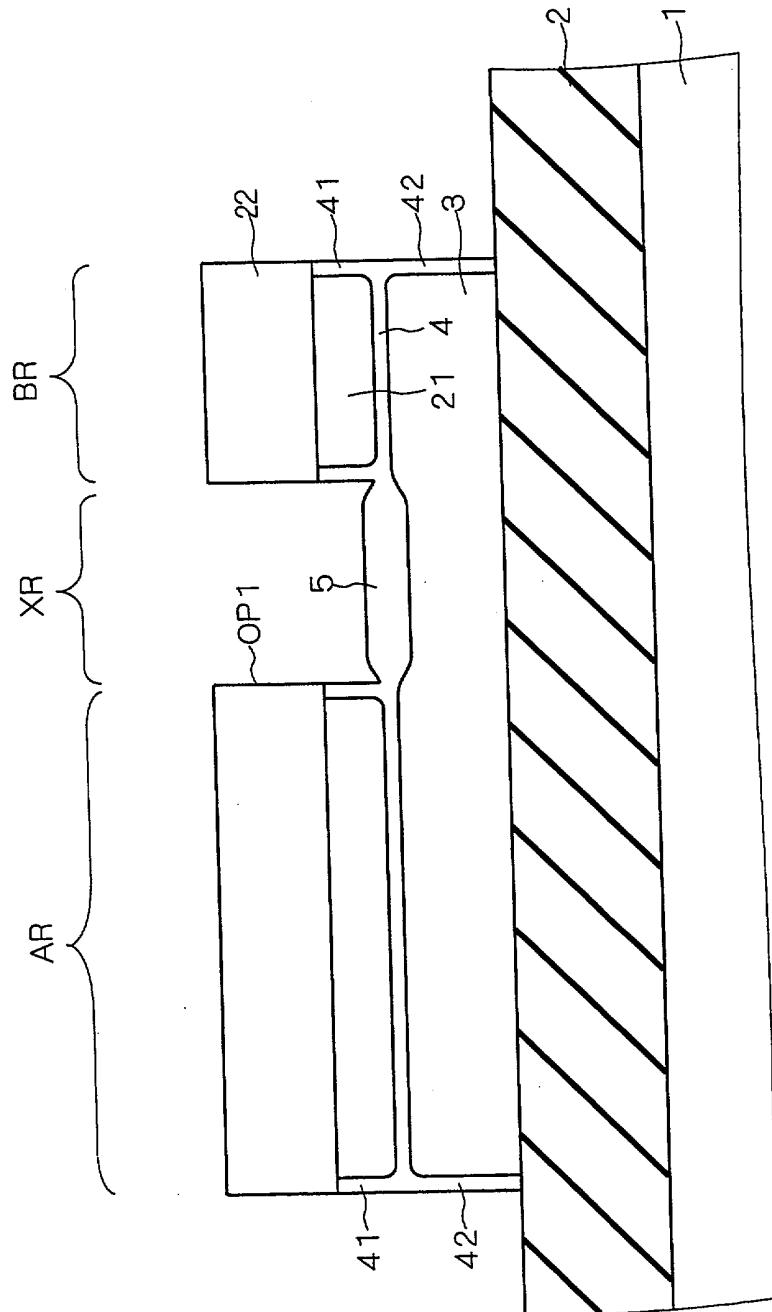

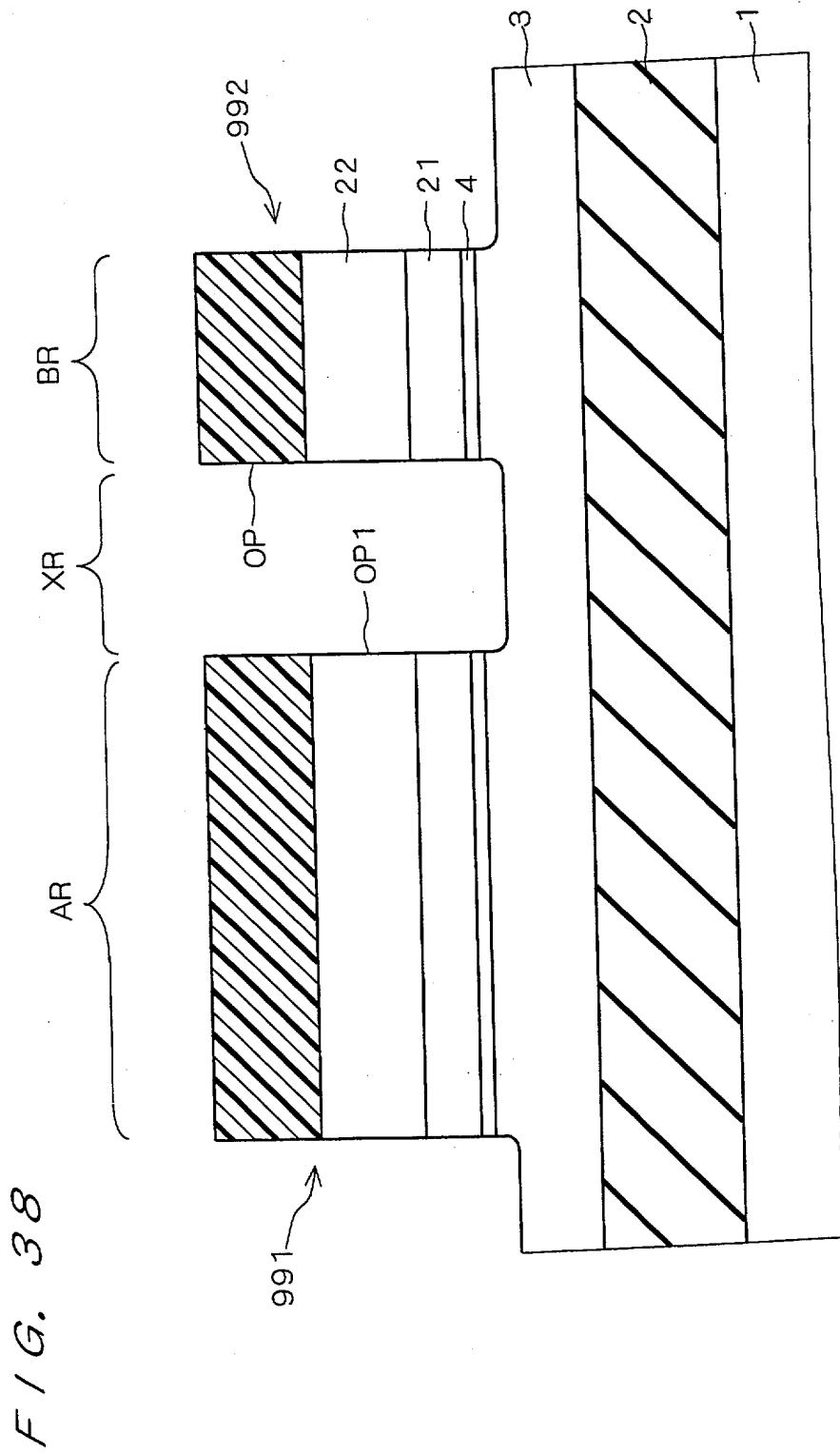

A la place des étapes représentées sur les figures 27 à 29, il est également possible d'employer des étapes représentées sur les figures 38 à 40 qu'on décrira ci-dessous.

Comme représenté sur la figure 38, on forme une pellicule multicouche comprenant une pellicule de nitre 22, une pellicule de silicium polycristallin 21 et une pellicule d'oxyde 4, sur un substrat

SOI, et on recouvre par un masque de matière de réserve RM6 une région sur la pellicule de nitre 22 qui correspond à une région de formation de transistor MOS.

A ce moment, on définit le motif du masque de matière de réserve RM6 de façon qu'une région XR dans laquelle une pellicule isolante de grille épaisse doit être formée, remplisse la fonction d'une partie d'ouverture OP.

Ensuite, en utilisant le masque de matière de réserve RM6 à titre de masque de gravure, on enlève sélectivement la pellicule de nitre 22 et la pellicule de silicium polycristallin 21, par attaque par voie sèche ou attaque par voie humide.

En outre, en utilisant en tant que masque de gravure la pellicule de nitre 22 dans laquelle on a défini un motif, on enlève la pellicule d'oxyde 4 et la couche SOI 3 qui ne sont pas couvertes par la pellicule de nitre 22, ce qui laisse des pellicules multicouches 991 et 992 comprenant la pellicule de nitre 22, la pellicule de silicium polycristallin 21 et la pellicule d'oxyde 4, seulement dans une région active AR du transistor MOS et dans une région de formation de partie de contact de corps BR. La région XR remplit la fonction d'une ouverture inférieure OP1 et la couche SOI 3 est à nu dans une partie de fond de celle-ci. A ce moment, la couche SOI 3 est légèrement enlevée par surgravure. L'enlèvement est effectué sur une épaisseur maximale d'environ 50 nm. En outre, la pellicule de nitre 22, la pellicule de silicium polycristallin 21 et la pellicule d'oxyde 4 sont gravées séquentiellement, une par une. Par conséquent, une valeur de surgravure de la couche SOI 3 varie peu, à la différence de la formation d'une structure PTI.

Ensuite, on enlève le masque de matière de réserve RM6 et on forme ensuite un masque de matière de réserve RM8 pour couvrir seulement la région active AR du transistor MOS, la région de formation de partie de contact de corps BR et la région XR dans laquelle une pellicule isolante de grille épaisse doit être formée, et en utilisant le masque de matière de réserve RM8 en tant que masque de gravure, on enlève la pellicule d'oxyde 4 et la couche SOI 3 dans une région qui n'est pas couverte par le masque de matière de ré-

serve RM8, ce qui forme une pellicule multicouche 993 comportant la pellicule de nitrure 22, la pellicule de silicium polycristallin 21, la pellicule d'oxyde 4 et la couche SOI 3, à une étape représentée sur la figure 39.

5       Ensuite, on enlève le masque de matière de réserve RM8, après quoi on effectue une oxydation thermique pour former une pellicule d'oxyde 5 ayant une épaisseur de 10 à 40 nm sur une surface de la couche SOI 3, incluant une surface de fond de la partie d'ouverture OP1, et pour former des pellicules d'oxyde 41 et 42 sur des

10 parois latérales à nu de la couche de silicium polycristallin 21 et de la couche SOI 3, à une étape représentée sur la figure 40 (oxydation de paroi latérale).

Du fait que la pellicule d'oxyde 5 est formée dans la partie surgravée de la couche SOI 3, son épaisseur peut aisément être

15 augmentée.

Après l'accomplissement de l'étape représentée sur la figure 38, on peut oxyder l'intérieur de la partie d'ouverture OP1 pour former la pellicule d'oxyde 5.

En outre, aux étapes représentées sur les figures 27 et 38,

20 on enlève sélectivement la pellicule de nitrure 22 et la pellicule de silicium polycristallin 21 par gravure par voie sèche ou gravure par voie humide et, de plus, on enlève la pellicule d'oxyde 4 et la couche SOI 3 en utilisant en tant que masque de gravure la pellicule de nitrure 22 dans laquelle on a défini un motif. Dans l'enlèvement de la pellicule d'oxyde 4 et de la couche SOI 3, aucun dommage de gravure n'est occasionné à la surface de la couche SOI 3 si on utilise une gravure ayant un faible endommagement de gravure, comme la gravure chimique par voie sèche (ou CDE pour "Chemical Dry Etching"). En outre, dans le cas où on doit effectuer la surgravure,

25 30 l'aptitude à la maîtrise d'une valeur de surgravure peut également être améliorée.

La CDE est une configuration de gravure par voie sèche qui est accomplie dans une atmosphère d'un gaz spécifique ou dans une enceinte à vide dans laquelle une pression est définie, et elle est

35 accomplie en utilisant en tant qu'agent de gravure un radical chim-

quement actif, et un dispositif pour séparer une partie dans laquelle un radical actif doit être formé, vis-à-vis d'une partie dans laquelle la gravure doit être effectuée.

5 Pour l'agent de gravure, il a été mentionné un exemple utilisant un radical consistant en fluor (F), obtenu à partir d'un plasma utilisant un gaz consistant en un mélange d'un gaz CF<sub>4</sub> et d'un gaz O<sub>2</sub> (voir Monthly Semiconductor World 1994, 1, pages 64 à 67 publié par Press Journal Co., Ltd.).

#### E-1-3. Troisième Variante

10 En outre, une pellicule multicoche comprenant une pellicule de nitrate 22, une pellicule de silicium polycristallin 21 et une pellicule d'oxyde 4 est formée sur un substrat SOI. Il est alors possible d'effectuer tout d'abord une gravure pour définir une région dans laquelle une pellicule d'oxyde d'isolation par tranchée parfaite 15 doit être formée.

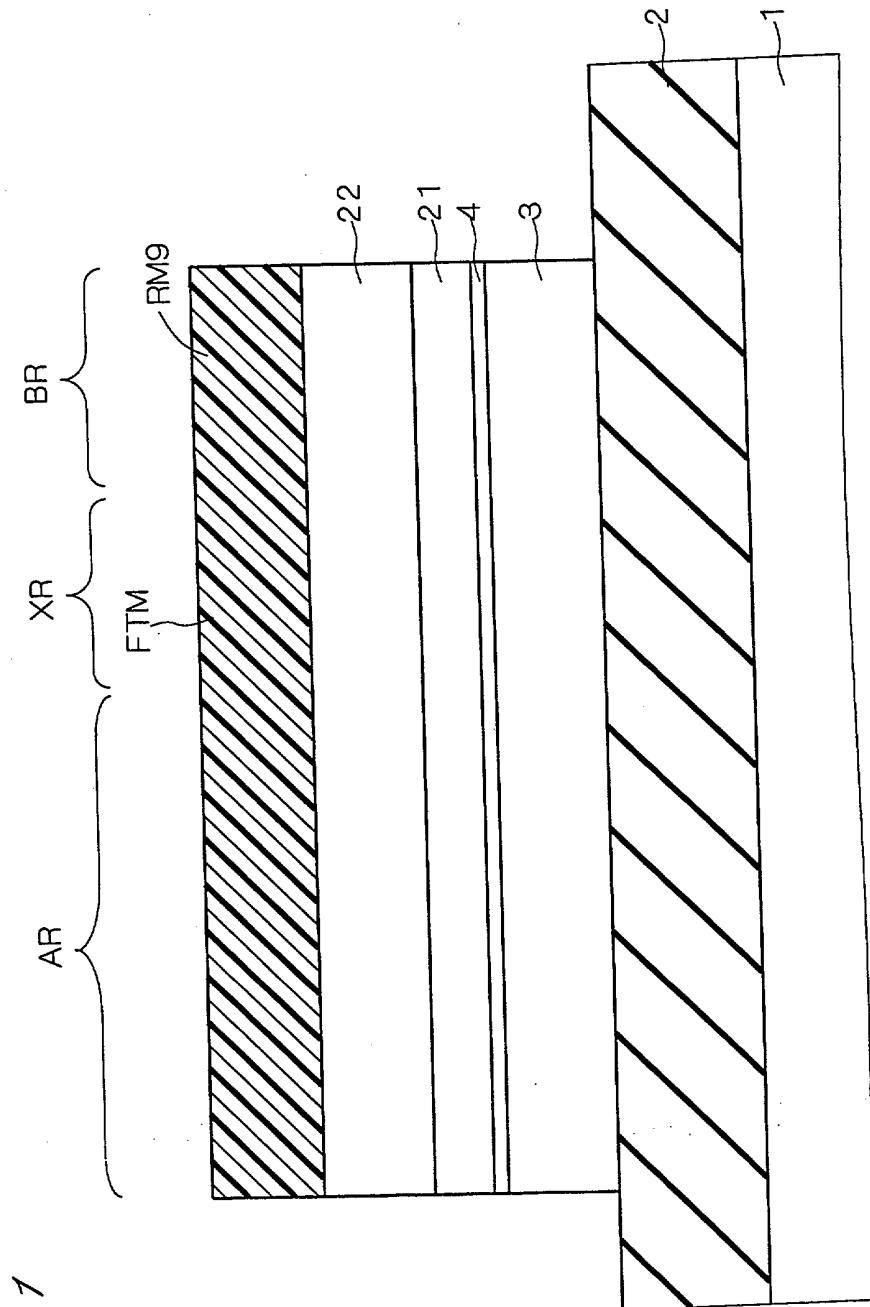

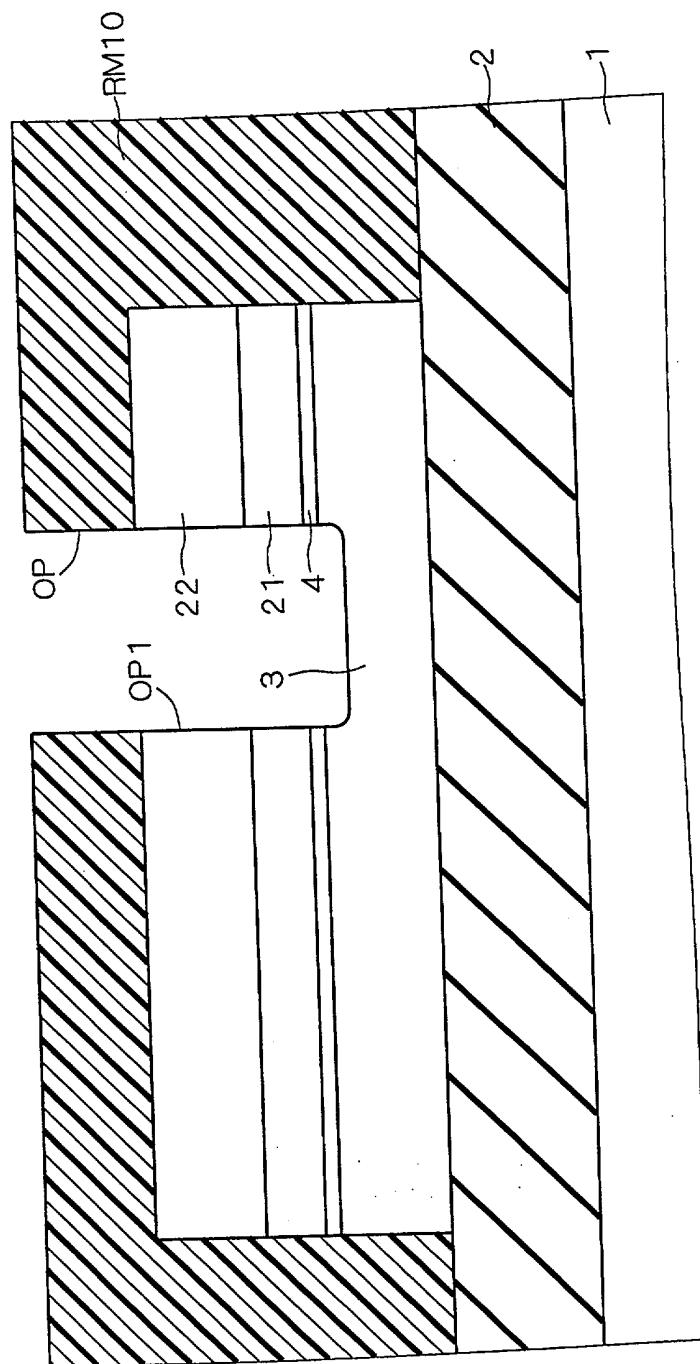

De façon plus spécifique, comme représenté sur la figure 41, on forme sur la pellicule multicoche comprenant la pellicule de nitrate 22, la pellicule de silicium polycristallin 21 et la pellicule d'oxyde 4 qui est formée sur le substrat SOI, un masque de matière 20 de réserve RM9 ayant un motif d'ouverture pour définir la région dans laquelle une pellicule d'oxyde d'isolation par tranchée parfaite doit être formée, et on enlève la pellicule de nitrate 22, la pellicule de silicium polycristallin 21, la pellicule d'oxyde 4 et la couche SOI 3 dans une région qui n'est pas couverte par le masque de matière de 25 réserve RM9.

Ensuite, à une étape représentée sur la figure 42, on forme un masque de matière de réserve RM10 sur une surface complète du substrat SOI. On définit un motif dans le masque de matière de réserve RM10 de façon que seule une région XR dans laquelle une pellicule isolante de grille épaisse doit être formée remplisse la fonction d'une partie d'ouverture OP. Ensuite, on enlève la pellicule de nitrate 22, la pellicule de silicium polycristallin 21 et la pellicule d'oxyde 4 pour former une partie d'ouverture OP1 en utilisant le masque de matière de réserve RM10 en tant que masque de gravure. 35

Ensuite, il est préférable d'employer l'étape décrite en référence à la figure 37 ou l'étape décrite en référence à la figure 40, pour une étape d'oxydation de l'intérieur de la partie d'ouverture OP1, pour former une pellicule d'oxyde 5.

5        E-2. Configuration en Plan

On décrira ci-dessous en référence aux figures 43 à 46 un exemple d'une configuration en plan à chacune des étapes décrites en référence aux figures 27 à 32.

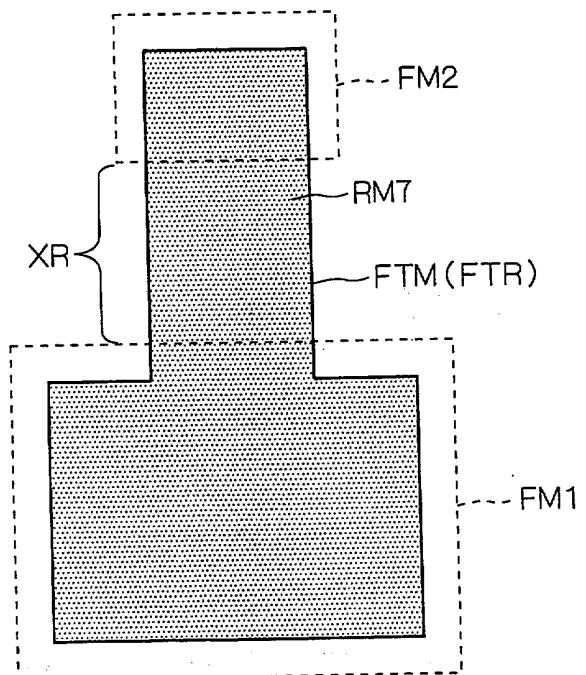

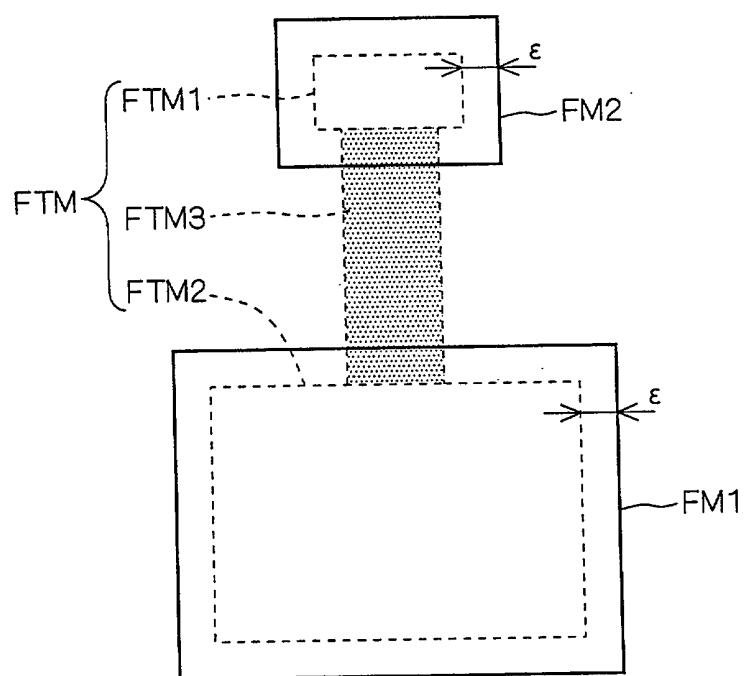

La figure 43 montre une configuration en plan du masque de matière de réserve RM6 devant être utilisé à l'étape représentée sur la figure 27, et des matières de réserve ayant des formes individuellement différentes sont placées dans des régions correspondant à la région active AR du transistor MOS et à la région de formation de partie de contact de corps BR et d'autres régions remplissant la fonction de parties d'ouverture. Une région dans laquelle la matière de réserve est placée remplit la fonction de ce qu'on appelle une région de champ. En outre, sur la figure 43, des données de masque pour définir la région de champ incluant la région active AR (non représentée) et des données de masque pour définir la région de champ incluant la région de formation de partie de contact de corps BR (non représentée) sont respectivement représentées de façon caractéristique par FM1 et FM2. Une partie située entre les données de masque FM1 et FM2 remplit la fonction d'une région dans laquelle une pellicule isolante de grille épaisse doit être formée, comme décrit en référence à la figure 27.

La figure 44 montre une configuration en plan du masque de matière de réserve RM7 devant être utilisé à l'étape représentée sur la figure 29, et une matière de réserve continue est placée dans des régions correspondant à la région active AR du transistor MOS, la région XR dans laquelle une pellicule isolante de grille épaisse doit être formée ultérieurement et la région de formation de partie de contact de corps BR, et d'autres régions remplissent la fonction de parties d'ouverture. La région dans laquelle la matière de réserve est placée et une région autre qu'une région entourée par une ligne en pointillés qui est définie par les données de masque FM1 et FM2,

remplissent la fonction de ce qu'on appelle une région de formation de pellicule d'oxyde d'isolation par tranchée parfaite. Sur la figure 44, des données de masque pour définir une région de non-formation de pellicule d'oxyde d'isolation par tranchée parfaite, FTR, 5 sont représentées de façon caractéristique par FTM.

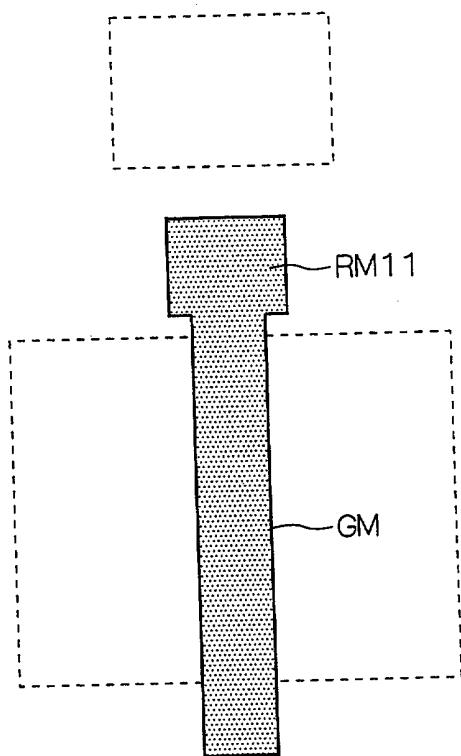

La figure 45 montre une configuration en plan d'un masque de matière de réserve RM11 (qui n'est pas représenté sur la figure 32) pour former l'électrode de grille 12 à l'étape représentée sur la 10 figure 32. Une matière de réserve est placée seulement dans une partie dans laquelle l'électrode de grille 12 doit être formée.

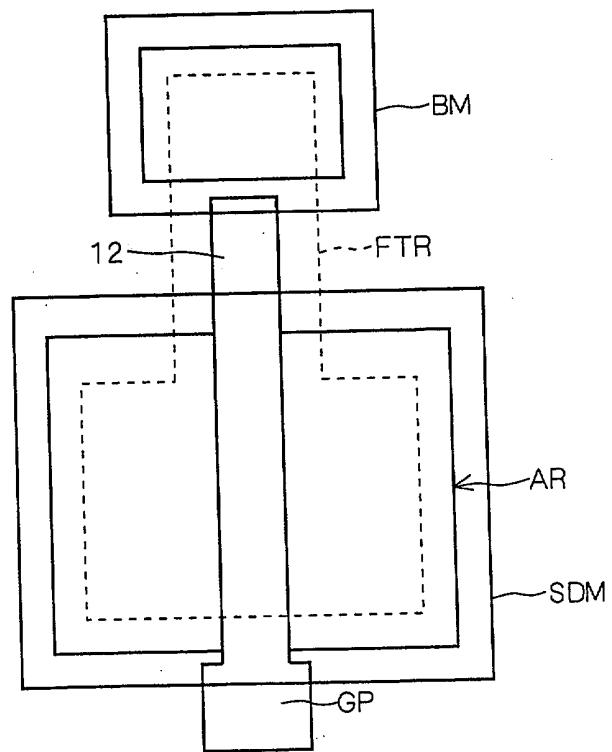

La figure 46 montre une configuration en plan d'un transistor MOS Q21 formé en utilisant les masques de matière de réserve RM6, RM7 et RM11 décrits ci-dessus.

La figure 46 montre le transistor MOS Q21 comprenant la 15 région active AR incluant une région de source/drain et l'électrode de grille 12 et la partie de contact de corps BD formée à l'extérieur dans une direction d'une largeur de grille du côté de la plage de contact de grille GP de l'électrode de grille 12.

La figure 47 est une représentation caractéristique qui est 20 superposée sur la figure 46, montrant des données de masque SDM et BM pour définir une région d'implantation d'une impureté de source-drain dans la région active AR, et une région d'implantation d'une impureté dans la partie de contact de corps BD.

Sur la figure 47, des régions rectangulaires indiquées 25 comme données de masque SDM et BM remplissent la fonction des parties d'ouverture de la matière de réserve. Il est souhaitable que les données de masque BM soient établies de façon qu'un bout de la plage de grille GP atteigne la région des données de masque BM. Si 30 le bout de la plage de grille GP n'atteint pas la région des données de masque BM, l'impureté de source-drain est introduite dans la couche SOI entre la partie de contact de corps BD et la région active AR. La raison est que l'introduction doit être évitée.

Dans le cas dans lequel un masque d'implantation doit être 35 formé, on peut employer deux procédés de formation en fonction d'une différence dans la nature de la matière de réserve.

De façon plus spécifique, il y a deux procédés incluant un procédé consistant à concevoir, par conception assistée par ordinateur (CAO) ou similaire, une région dans laquelle une impureté doit être implantée, puis à créer un masque négatif définissant une région autre que la région d'implantation d'impureté en tant que partie d'arrêt de lumière, et à exposer une matière de réserve positive en utilisant le masque négatif, pour former ainsi un masque de préférence d'ouverture, et un procédé consistant à concevoir, par la CAO ou similaire, une région dans laquelle une impureté doit être implantée, puis à créer un masque positif définissant la région d'implantation d'impureté comme étant une partie d'arrêt de lumière sur le masque tel quel et à exposer la matière de réserve négative en utilisant le masque positif, pour former ainsi un masque de préférence d'ouverture.

Bien que la figure 47 montre la structure dans laquelle la partie de contact de corps BD est formée à l'extérieur dans la direction de la largeur de grille du côté de la plage de grille GP de l'électrode de grille 12, il est également possible d'employer une configuration en plan dans laquelle l'électrode de grille 12 est renversée. La figure 48 montre la configuration en plan.

La figure 48 montre la configuration dans laquelle la partie de contact de corps BD est formée à l'extérieur dans la direction de la largeur de grille, du côté opposé à la plage de grille GP de l'électrode de grille 12.

### 25 E-3. Fonction et Effet

Conformément au procédé de fabrication du cinquième mode de réalisation décrit ci-dessus, dans le cas où on emploie le procédé de formation d'une pellicule d'oxyde d'isolation par tranchée parfaite en utilisant une pellicule auxiliaire, une épaisseur de la pellicule isolante de grille est changée dans la direction de la largeur de grille. La pellicule isolante de grille épaisse 5 peut être formée sous la plage de contact de grille GP établie sur une grande étendue sur la couche SOI 3. En réduisant une épaisseur de la pellicule isolante de grille 5 dans une région dans laquelle un courant circule avec une intensité élevée, il est possible de réduire une capacité pa-