(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2011-109081

(P2011-109081A)

(43) 公開日 平成23年6月2日(2011.6.2)

(51) Int.Cl.

H01L 29/786 (2006.01)

G02F 1/1368 (2006.01)

F 1

H01L 29/78

G02F 1/1368

テーマコード(参考)

2H092

5F110

審査請求 未請求 請求項の数 5 O L (全 30 頁)

(21) 出願番号 特願2010-235109 (P2010-235109)

(22) 出願日 平成22年10月20日 (2010.10.20)

(31) 優先権主張番号 特願2009-242787 (P2009-242787)

(32) 優先日 平成21年10月21日 (2009.10.21)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 荒澤 亮

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 宍戸 英明

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

最終頁に続く

(54) 【発明の名称】 液晶表示装置及び当該液晶表示装置を具備する電子機器

## (57) 【要約】

【課題】酸化物半導体を用いた薄膜トランジスタを具備する画素において、開口率の向上を図ることのできる液晶表示装置を提供する。

【解決手段】ゲート電極と、ゲート電極と重なるように設けられたゲート絶縁層及び酸化物半導体層と、酸化物半導体層の一部と重なるソース電極及びドレイン電極と、を有する薄膜トランジスタが、画素部に配設される信号線と画素電極との間に設けられており、薄膜トランジスタのオフ電流は、 $1 \times 10^{-13} A$ 以下であって、液晶素子に並列した容量素子を設けずに液晶容量のみで電位を保持することが可能となり、画素部には画素電極と接続される容量素子が形成されていない構成の液晶表示装置とする。

【選択図】図1

## 【特許請求の範囲】

## 【請求項 1】

ゲート電極と、

前記ゲート電極と重なる様に設けられたゲート絶縁層と、

前記ゲート絶縁層を介して前記ゲート電極と重なる様に設けられた酸化物半導体層と、

前記酸化物半導体層の一部と重なるソース電極及びドレイン電極と、

を有する薄膜トランジスタが、画素部に配設される信号線と画素電極との間に設けられており、前記画素電極と電気的に接続される補助容量が形成されていないことを特徴とする液晶表示装置。

## 【請求項 2】

ゲート電極と、

前記ゲート電極と重なる様に設けられたゲート絶縁層と、

前記ゲート絶縁層を介して前記ゲート電極と重なる様に設けられた酸化物半導体層と、

前記酸化物半導体層の一部と重なるソース電極及びドレイン電極と、

を有する薄膜トランジスタが、1画素内に設けられた複数の副画素のそれぞれに配設される信号線と画素電極との間に一つずつ設けられており、前記画素電極と電気的に接続される補助容量が形成されていないことを特徴とする液晶表示装置。

## 【請求項 3】

請求項 1 または 2 において、前記薄膜トランジスタのオフ電流は、 $1 \times 10^{-13} \text{ A}$  以下であることを特徴とする液晶表示装置。

## 【請求項 4】

請求項 1 乃至 3 のいずれか一項において、前記酸化物半導体層は、水素濃度が $5 \times 10^{-9} / \text{cm}^3$  以下であり、キャリア濃度が $5 \times 10^{14} / \text{cm}^3$  以下であることを特徴とする液晶表示装置。

## 【請求項 5】

請求項 1 乃至 4 のいずれか一項に記載の液晶表示装置を具備することを特徴とする電子機器。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明の一形態は、酸化物半導体を用いた電界効果型トランジスタにより構成される半導体装置に関する。

## 【0002】

なお、本明細書中において半導体装置とは、半導体特性を利用して機能しうる装置全般を指し、液晶表示装置などの電気光学装置、半導体回路及び電子機器は全て半導体装置である。

## 【背景技術】

## 【0003】

絶縁表面を有する基板上に形成された半導体薄膜を用いて薄膜トランジスタを構成する技術が注目されている。薄膜トランジスタは液晶テレビに代表されるような表示装置に用いられている。薄膜トランジスタに適用可能な半導体薄膜としてシリコン系半導体材料が公知であるが、その他の材料として酸化物半導体が注目されている。

## 【0004】

酸化物半導体の材料としては、酸化亜鉛または酸化亜鉛を成分とするものが知られている。そして、電子キャリア濃度が $10^{18} / \text{cm}^3$  未満である非晶質酸化物（酸化物半導体）なるもので形成された薄膜トランジスタが開示されている（特許文献 1 乃至 3）。

## 【先行技術文献】

## 【特許文献】

## 【0005】

## 【特許文献 1】特開 2006-165527 号公報

10

20

30

40

50

【特許文献2】特開2006-165528号公報

【特許文献3】特開2006-165529号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、酸化物半導体膜は、その形成工程において化学量論的組成からのずれが生じ、問題となることがある。例えば、膜中の酸素が過不足となった場合や、不純物として含まれる水素が電子供与体となる場合は、電気伝導度を変化させてしまう。

【0007】

電子キャリア濃度が $10^{18} / \text{cm}^3$ 未満としても、酸化物半導体においては実質的にはn型であり、上記特許文献に開示される薄膜トランジスタのオンオフ比は $10^3$ しか得られない。この様な薄膜トランジスタのオンオフ比が低い理由は、オフ電流が高いことによるものである。

【0008】

本発明の一形態は、安定した電気的特性（例えば、オフ電流がきわめて低減されている）を有する薄膜トランジスタを含んで構成される表示装置を提供することを目的とする。

【課題を解決するための手段】

【0009】

本発明の一形態は、酸化物半導体中で電子供与体（ドナー）となる不純物を除去することで、真性または実質的に真性な半導体であって、シリコン半導体よりもエネルギーギャップが大きい酸化物半導体でチャネル領域が形成される薄膜トランジスタを有する液晶表示装置を構成するものである。

【0010】

すなわち、本発明の一形態は、酸化物半導体に含まれる水素を $5 \times 10^{19} / \text{cm}^3$ 以下、好ましくは $5 \times 10^{18} / \text{cm}^3$ 以下、より好ましくは $5 \times 10^{17} / \text{cm}^3$ 以下となるように酸化物半導体に含まれる水素若しくはOH基を極めて少ない状態とし、キャリア濃度を $5 \times 10^{14} / \text{cm}^3$ 以下、好ましくは $5 \times 10^{12} / \text{cm}^3$ 以下とした酸化物半導体膜でチャネル領域が形成される薄膜トランジスタを有する液晶表示装置が構成されるものである。

【0011】

酸化物半導体のエネルギーギャップは2eV以上、好ましくは2.5eV以上、より好ましくは3eV以上として、ドナーを形成する水素等の不純物を極力低減し、キャリア濃度を $1 \times 10^{14} / \text{cm}^3$ 以下、好ましくは $1 \times 10^{12} / \text{cm}^3$ 以下となる様にする。

【0012】

この様に高純度化された酸化物半導体は、薄膜トランジスタのチャネル形成領域に用いることで、チャネル幅が10mmでドレイン電圧が10Vであっても、ゲート電圧が-5Vから-20Vの範囲において、そのドレイン電流は $1 \times 10^{-13} \text{ A}$ 以下となる様に作用する。

【0013】

本明細書で開示する本発明の一態様は、ゲート電極と、ゲート電極と重なる様に設けられたゲート絶縁層と、ゲート絶縁層を介してゲート電極と重なる様に設けられた酸化物半導体層と、酸化物半導体層の一部と重なるソース電極及びドレイン電極と、を有する薄膜トランジスタが、画素部に配設される信号線と画素電極との間に設けられており、前記画素電極と電気的に接続される補助容量が形成されていないことを特徴とする液晶表示装置である。

【0014】

また、本明細書で開示する本発明の他の一態様は、ゲート電極と、ゲート電極と重なる様に設けられたゲート絶縁層と、ゲート絶縁層を介してゲート電極と重なる様に設けられた酸化物半導体層と、酸化物半導体層の一部と重なるソース電極及びドレイン電極と、を有する薄膜トランジスタが、1画素内に設けられた複数の副画素のそれぞれに配設される信

10

20

30

40

50

号線と画素電極との間に一つずつ設けられており、前記画素電極と電気的に接続される補助容量が形成されていないことを特徴とする液晶表示装置である。

【0015】

なお、補助容量とは、意図的に設けた容量素子を意味するものであり、意図的に設けられたものではない寄生容量は形成されていても良い。

【発明の効果】

【0016】

本発明の一形態によれば、オフ電流が  $1 \times 10^{-13} A$  以下に低減されていることで、画素に印加した信号電圧を保持する容量を付加的に設ける必要がなくなる。すなわち、各画素に補助容量を設けなくて済むので、開口率を向上させることができる。また、本発明の一形態に係る薄膜トランジスタを用いた画素は、一定の状態（映像信号が書き込まれた状態）を保持することができる。静止画を表示する場合にも安定した動作をすることができる。

10

【図面の簡単な説明】

【0017】

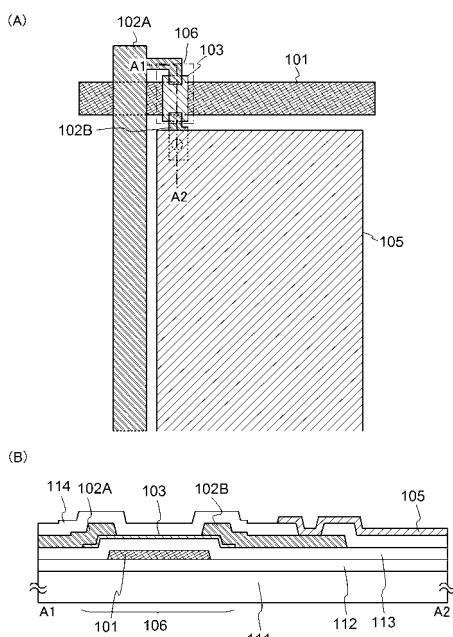

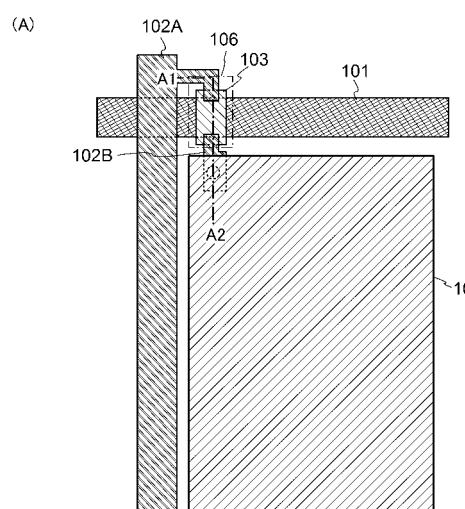

【図1】液晶表示装置について説明する上面図及び断面図。

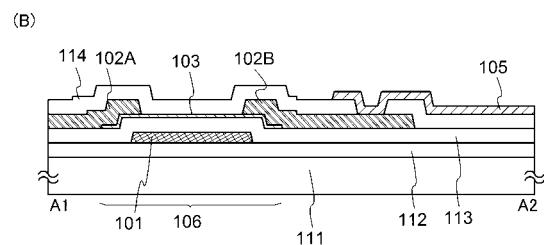

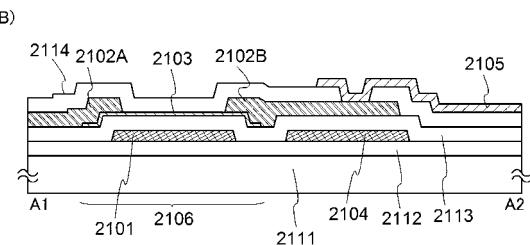

【図2】液晶表示装置について説明する上面図及び断面図。

【図3】液晶表示装置の作製方法について説明する断面図。

【図4】酸化物半導体を用いた薄膜トランジスタの  $V_g - I_d$  特性。

【図5】酸化物半導体を用いた薄膜トランジスタの写真。

20

【図6】酸化物半導体を用いた薄膜トランジスタの  $V_g - I_d$  特性（温度特性）。

【図7】液晶表示装置について説明する図。

【図8】酸化物半導体を用いた逆スタガ型の薄膜トランジスタの縦断面図。

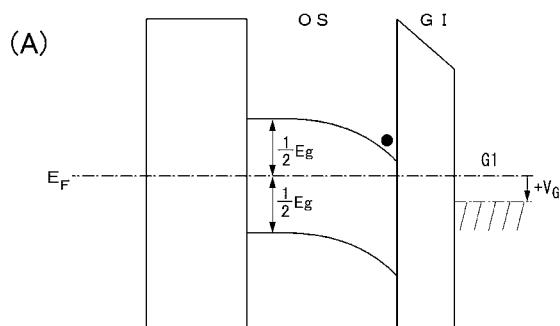

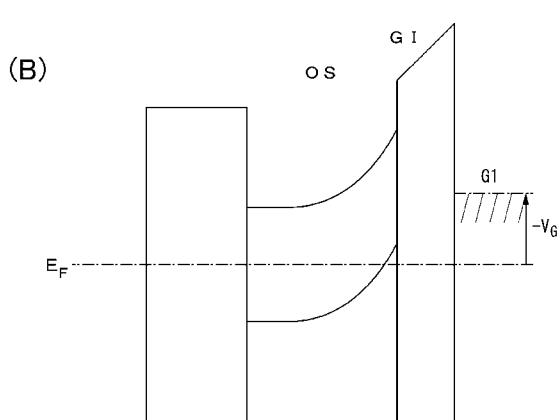

【図9】図8に示すA-A'断面におけるエネルギーバンド図（模式図）。

【図10】図8に示すB-B'断面におけるエネルギーバンド図（模式図）であって、（A）ゲート（G1）に正の電位（ $+V_g$ ）が印加された状態を示し、（B）ゲート（G1）に負の電位（ $-V_g$ ）が印加された状態を示す図。

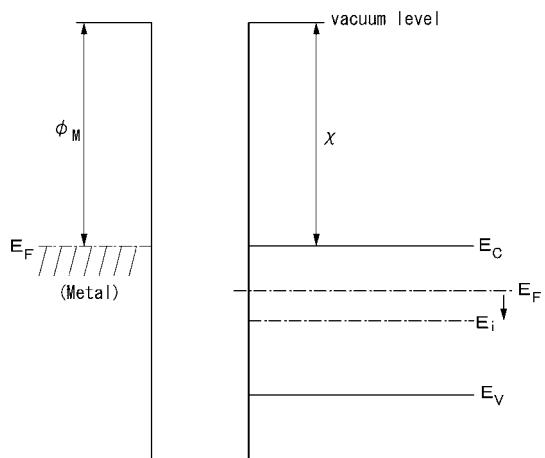

【図11】真空準位と金属の仕事関数（ $\phi_M$ ）、酸化物半導体の電子親和力（ $\phi$ ）の関係を示す図。

30

【図12】液晶表示装置について説明する図。

【図13】液晶表示装置について説明する図。

【図14】液晶表示装置について説明する図。

【図15】液晶表示装置について説明する図。

【図16】液晶表示装置について説明する図。

【図17】電子機器について説明する図。

【図18】電子機器について説明する図。

【図19】シリコンMOSトランジスタのソース-ドレイン間のバンド構造を示す図。

【発明を実施するための形態】

【0018】

本発明の実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同一部分または同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。

40

【0019】

なお、本明細書で説明する各図において、各構成の大きさ、層の厚さ、または領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。

【0020】

50

なお、本明細書にて用いる第1、第2、第3、等の用語は、構成要素の混同を避けるために付したものであり、数的に限定するものではない。そのため、例えば、「第1の」を「第2の」または「第3の」などと適宜置き換えて説明することができる。

【0021】

(実施の形態1)

本発明の一態様における薄膜トランジスタを用いて液晶表示装置の画素を構成する例を以下に説明する。本実施の形態では、一例として、液晶表示装置における画素が有する薄膜トランジスタ及び当該薄膜トランジスタに接続された電極(画素電極ともいう)について示し、説明する。なお、画素とは、表示装置の各画素に設けられた各素子、例えば薄膜トランジスタ、画素電極として機能する電極、及び電気的な信号を素子に供給する配線等を含むものである。なお、画素は、カラーフィルター等を含むものであっても良い。例えば、RGBの色要素からなるカラー表示装置の場合には、画像の最小単位は、Rの画素とGの画素とBの画素との三画素から構成されるものとなる。

10

【0022】

なお、AとBとが接続されている、と記載する場合は、AとBとが電気的に接続されている場合と、AとBとが直接接続されている場合とを含むものとする。ここで、A、Bは、対象物(例えば、装置、素子、回路、配線、電極、端子、導電膜、層、など)であるとする。

20

【0023】

また、保持容量とは液晶素子の容量と、別に設けられた容量素子の容量を合わせたものであり、前者を液晶容量、後者を補助容量と区別する。

20

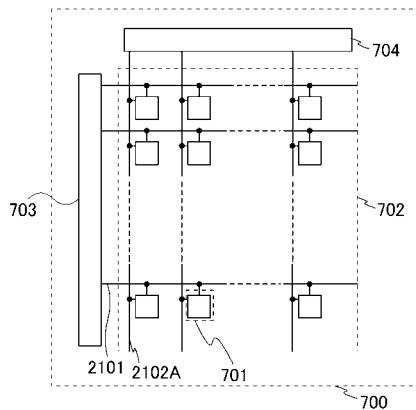

【0024】

まず、従来の液晶表示装置における画素部の一例として、上面図を図2(A)に示す。なお図2(A)に示す薄膜トランジスタの構造は、ボトムゲート型構造であり、ゲート電極と重なる酸化物半導体層上にソース電極及びドレイン電極となる配線層を有する、いわゆる逆スタガ型の構成について示している。

30

【0025】

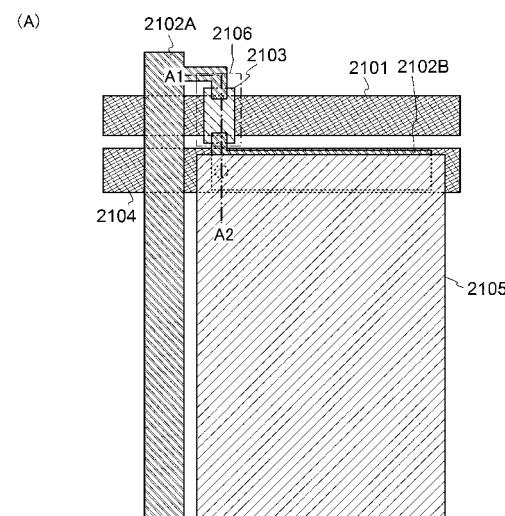

図2(A)に示す画素部は、走査線として機能する第1の配線2101、信号線として機能する第2の配線2102A、酸化物半導体層2103、容量線2104、画素電極2105を有する。また、酸化物半導体層2103と画素電極2105とを電気的に接続するための第3の配線2102Bを有する。

30

【0026】

第1の配線2101は、薄膜トランジスタ2106のゲート電極として機能する配線である。

40

【0027】

第2の配線2102Aは、ソース電極またはドレイン電極の一方及び容量素子の一方の電極として機能する配線である。

【0028】

第3の配線2102Bは、ソース電極またはドレイン電極の他方として機能する配線である。

40

【0029】

容量線2104は、容量素子の他方の電極として機能する配線である。なお、第1の配線2101と、容量線2104とが同層に設けられ、第2の配線2102Aと、第3の配線2102Bとが同層に設けられる。また、第3の配線2102Bと容量線2104とは、一部重畠して設けられており、液晶素子の補助容量(容量素子)を形成している。なお、薄膜トランジスタ2106が有する酸化物半導体層2103は、第1の配線2101上にゲート絶縁膜2113(図示せず)を介して設けられている。

【0030】

また、図2(B)には、図2(A)における一点鎖線A1-A2間の断面構造について示している。

50

## 【0031】

図2(B)に示す断面構造において、基板2111上には、下地膜2112を介して、ゲート電極である第1の配線2101、及び容量線2104が設けられている。また、第1の配線2101及び容量線2104を覆う様にゲート絶縁膜2113が設けられ、ゲート絶縁膜2113上には、酸化物半導体層2103が設けられている。更に酸化物半導体層2103上には、第2の配線2102A、第3の配線2102Bが設けられ、それらの上には、パッシベーション膜として機能する酸化物絶縁層2114が設けられている。酸化物絶縁層2114には開口部が形成されており、開口部において画素電極2105と第3の配線2102Bとの接続がなされる。また、第3の配線2102Bと容量線2104とは、ゲート絶縁膜2113を誘電体として容量素子を形成している。

10

## 【0032】

なお、図2(A)、(B)に示す画素は、図7に示す様に、基板700上に複数の画素701がマトリクス状に配置されるものである。図7では、基板700上に画素部702、走査線駆動回路703、及び信号線駆動回路704を有する構成について示している。画素701は、走査線駆動回路703に接続された第1の配線101によって供給される走査信号により、各行ごとに選択状態か、非選択状態かが決定される。また走査信号によって選択されている画素701は、信号線駆動回路704に接続された配線2102Aによって、ビデオ電圧(画像信号、ビデオ信号、またはビデオデータともいう)が供給される。

20

## 【0033】

図7では、走査線駆動回路703、信号線駆動回路704が基板700上に設けられる構成について示したが、走査線駆動回路703または信号線駆動回路704のいずれか一つが基板700上に設けられる構成としてもよい。また画素部702のみを基板700上に設ける構成としても良い。

30

## 【0034】

図7の画素部702には、複数の画素701がマトリクス状に配置(ストライプ配置)する例について示している。なお、画素701は、必ずしもマトリクス状に配置されている必要はなく、例えば、画素701をデルタ配置、またはベイヤー配置してもよい。また画素部702における表示方式はプログレッシブ方式、インターレース方式のいずれかを用いることができる。なお、カラー表示する際に画素で制御する色要素としては、RGB(Rは赤、Gは緑、Bは青)の三色に限定されず、例えば、RGBW(Wは白)、またはRGBに、イエロー、シアン、マゼンタなどを一色以上追加したものなどがある。なお、色要素のドット毎にその表示領域の大きさが異なっていてもよい。

30

## 【0035】

図7において、第1の配線2101及び第2の配線2102Aは、画素の行方向及び列方向の数に応じて形成される。なお、第1の配線2101及び第2の配線2102Aは、画素を構成するサブ画素(副画素、サブピクセルともいう)の数、または画素内のトランジスタの数に応じて、本数を増やす構成としてもよい。また画素間で第1の配線2101及び第2の配線2102Aを共有して画素701を駆動する構成としても良い。

40

## 【0036】

なお、図2(A)では第2の配線2102Aを矩形状であるものとして示しているが、第3の配線2102Bを囲む形状(具体的には、U字型またはC字型)とし、キャリアが移動する領域の面積を増加させ、流れる電流量を増やす構成としてもよい。

40

## 【0037】

なお、薄膜トランジスタは、ゲートと、ドレインと、ソースとを含む少なくとも三つの端子を有する素子であり、ドレイン領域とソース領域の間にチャネル領域を有しており、ドレイン領域とチャネル領域とソース領域とを介して電流を流すことが出来る。ここで、ソースとドレインとは、トランジスタの構造や動作条件等によって変わるために、いずれがソースまたはドレインであるかを限定することが困難である。そこで、ソース及びドレインとして機能する領域を、ソースもしくはドレインと呼ばない場合がある。その場合、一例

50

としては、それを第1端子、第2端子と表記する場合がある。あるいは、それを第1電極、第2電極と表記する場合がある。あるいは、第1領域、第2領域と表記する場合がある。

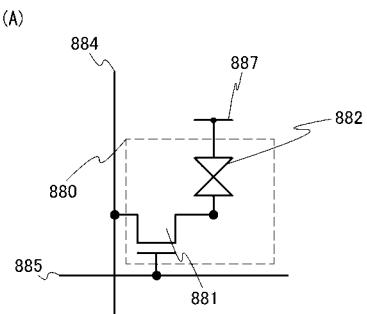

【0038】

次に、図1に本発明の一態様における画素部の構成例を示す。図1(A)は、図2(A)に示した従来例の画素部の構造から容量素子(補助容量)を省いたものである。それに伴って容量線が不要となり、第3の配線102Bは容量素子の電極を兼ねていたが、ソース電極またはドレイン電極として画素電極105のみと接続される配線となり、面積も縮小されている。従って、開口率を大幅に向上させることができる。

【0039】

なお、本発明の一態様として容量素子を省いた画素部の構成例においても、容量素子以外は前述した従来例と同じ構成を用いることができる。また、逆スタガ型のトランジスタを一例として説明したが、ボトムコンタクト型やトップゲート型など、他のトランジスタの構造を用いても良い。

【0040】

なお、上述した様に画素部から容量素子を省くには、充電された液晶素子のみによって画素の電位を一定期間保持する必要がある。このためには、薄膜トランジスタのオフ電流を十分に低くしなければならない。この特性を実現するための薄膜トランジスタの作製方法の一例を図3を用いて説明する。

【0041】

まず、透光性を有する基板111にはガラス基板を用いることができる。なお、基板111上に基板111からの不純物の拡散の防止、または基板111上に設ける各素子との密着性を向上するための下地膜112を設ける構成としている。なお、下地膜112は、必ずしも設ける必要はない。

【0042】

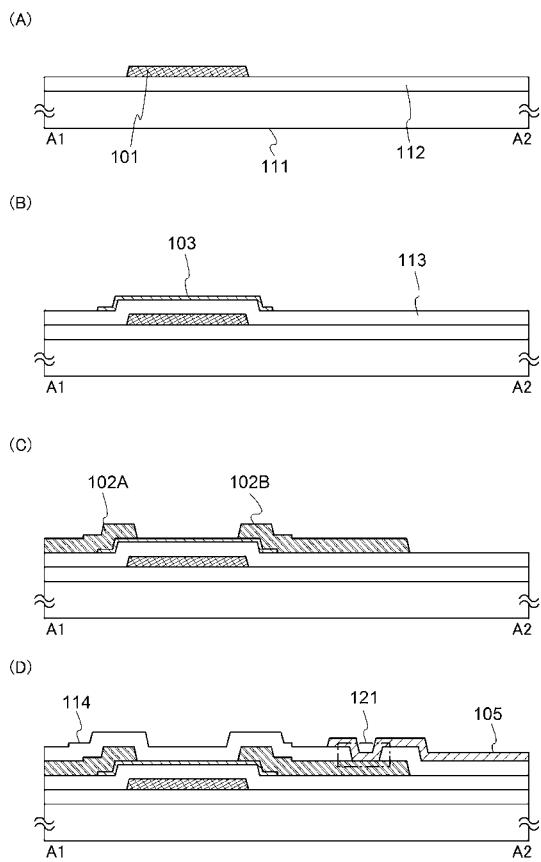

次いで、下地膜112上に導電層を形成した後、第1のフォトリソグラフィ工程を行い、レジストマスクを形成し、エッチングにより不要な部分を除去して第1の配線101を形成する。このとき、第1の配線101の端部がテーパー形状となる様にエッチングすることが好ましい。この段階での断面図を図3(A)に示す。

【0043】

第1の配線101は、アルミニウムや銅などの低抵抗導電性材料で形成することが望ましいが、アルミニウム単体では耐熱性が劣り、また腐蝕しやすい等の問題点があるので耐熱性導電性材料と組み合わせて形成すると良い。耐熱性導電性材料としては、チタン、タンタル、タンクスチル、モリブデン、クロム、ネオジム、スカンジウムから選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金、または上述した元素を成分とする窒化物で形成することができる。

【0044】

なお、インクジェット法や印刷法を用いて薄膜トランジスタを構成する配線等を形成することができる。これらはフォトマスクを用いなくても製造することができるため、トランジスタのレイアウトを容易に変更することができる。更に、レジストを用いる必要がないので、材料費が安くなり、工程数を削減できる。また、インクジェット法や印刷法を用いてレジストマスク等を形成することもできる。インクジェット法や印刷法は、レジストマスクを必要な部分にのみに形成することができるため、低コスト化が図れる。

【0045】

また、多階調マスクにより複数(代表的には二種類)の厚さの領域を有するレジストマスクを形成し、配線等の形成を行っても良い。

【0046】

次いで、第1の配線101上に絶縁膜(以下、ゲート絶縁膜113という)を成膜する。

【0047】

本実施の形態において、ゲート絶縁膜113の形成は、マイクロ波(2.45GHz)を

10

20

30

40

50

用いた高密度プラズマCVD装置により行う。ここで、高密度プラズマCVD装置とは、 $1 \times 10^{11} / \text{cm}^3$  以上のプラズマ密度を達成できる装置を指している。例えば、3 kW以上6 kW以下のマイクロ波電力を印加してプラズマを発生させて、絶縁膜の成膜を行う。

【0048】

チャンバーに材料ガスとしてモノシランガス( $\text{SiH}_4$ )と亜酸化窒素( $\text{N}_2\text{O}$ )と希ガスを導入し、10Pa以上30Pa以下の圧力で高密度プラズマを発生させて基板上に絶縁膜を形成する。その後、モノシランガスの供給を停止し、大気に曝すことなく亜酸化窒素( $\text{N}_2\text{O}$ )と希ガスとを導入して絶縁膜表面にプラズマ処理を行ってもよい。少なくとも亜酸化窒素( $\text{N}_2\text{O}$ )と希ガスとを導入して絶縁膜表面に行われるプラズマ処理は、絶縁膜の成膜より後に行う。上記プロセス順序を経た絶縁膜は、膜厚が薄く、例えば100nm未満であっても信頼性を確保することができる。

10

【0049】

ゲート絶縁膜113の形成の際、チャンバーに導入するモノシランガス( $\text{SiH}_4$ )と亜酸化窒素( $\text{N}_2\text{O}$ )との流量比は、1:10から1:200の範囲とする。また、チャンバーに導入する希ガスとしては、ヘリウム、アルゴン、クリプトン、キセノンなどを用いることができるが、中でも安価であるアルゴンを用いることが好ましい。

20

【0050】

また、高密度プラズマCVD装置により得られる絶縁膜は、段差被覆性に優れしており、膜厚も正確に制御することができる。

20

【0051】

上記プロセス順序を経た絶縁膜は、従来の平行平板型のPCVD装置で得られる絶縁膜とは大きく異なっており、同じエッチャントを用いてエッチング速度を比較した場合において、平行平板型のPCVD装置で得られる絶縁膜の10%以上または20%以上遅く、高密度プラズマCVD装置で得られる絶縁膜は緻密な膜と言える。

30

【0052】

本実施の形態では、ゲート絶縁膜113として高密度プラズマCVD装置による膜厚100nmの酸化窒化珪素膜( $\text{SiO}_x\text{N}_y$ とも呼ぶ、ただし、 $x > y > 0$ )を用いる。

【0053】

ゲート絶縁膜113を形成する他の手法として、スパッタ法を用いても良い。勿論、ゲート絶縁膜113は、この様な酸化シリコン膜に限定されるものでなく、酸化窒化シリコン膜、窒化シリコン膜、酸化アルミニウム膜、酸化タンタル膜などの他の絶縁膜を用い、これらの材料から成る単層または積層構造として形成しても良い。

30

【0054】

なお、酸化物半導体を成膜する前に、スパッタガスにアルゴンを用いて逆スパッタを行い、ゲート絶縁膜113の表面に付着しているゴミを除去することが好ましい。なお、スパッタガスをアルゴンに代えて窒素、ヘリウムなどを用いても良い。また、アルゴンに酸素、水素、 $\text{N}_2\text{O}$ 、 $\text{Cl}_2$ 、または $\text{CF}_4$ などを加えたスパッタガスを用いても良い。

【0055】

次に、ゲート絶縁膜113上に酸化物半導体膜を成膜する。酸化物半導体を半導体層に用いたトランジスタは、アモルファスシリコンを用いるものよりも電界効果移動度を高めることが出来る。なお、酸化物半導体としては、例えば、酸化亜鉛( $\text{ZnO}$ )、酸化スズ( $\text{SnO}_2$ )なども用いることができる。また、 $\text{ZnO}$ に $\text{In}$ や $\text{Ga}$ などを添加することもできる。

40

【0056】

酸化物半導体膜には、化学式 $\text{InMO}_3$ ( $\text{ZnO}$ ) $_m$ ( $m > 0$ )で表記される薄膜を用いることができる。ここで、Mは、 $\text{Ga}$ 、 $\text{Al}$ 、 $\text{Mn}$ 及び $\text{Co}$ から選ばれた一つまたは複数の金属元素を示す。具体的にMは、 $\text{Ga}$ 、 $\text{Ga}$ 及び $\text{Al}$ 、 $\text{Ga}$ 及び $\text{Mn}$ 、または $\text{Ga}$ 及び $\text{Co}$ 等とする。

【0057】

50

該酸化物半導体膜には、四元系金属酸化物である  $In - Sn - Ga - Zn - O$  系酸化物半導体や、三元系金属酸化物である  $In - Ga - Zn - O$  系酸化物半導体、  $In - Sn - Zn - O$  系酸化物半導体、  $In - Al - Zn - O$  系酸化物半導体、  $Sn - Ga - Zn - O$  系酸化物半導体、  $Al - Ga - Zn - O$  系酸化物半導体、  $Sn - Al - Zn - O$  系酸化物半導体や、二元系金属酸化物である  $In - Zn - O$  系酸化物半導体、  $Sn - Zn - O$  系酸化物半導体、  $Al - Zn - O$  系酸化物半導体、  $Zn - Mg - O$  系酸化物半導体、  $Sn - Mg - O$  系酸化物半導体、  $In - Mg - O$  系酸化物半導体や、  $In - Ga - O$  系酸化物半導体、  $In - O$  系酸化物半導体、  $Sn - O$  系酸化物半導体、  $Zn - O$  系酸化物半導体などを用いることができる。また、上記酸化物半導体に  $SiO_2$  を含んでもよい。ここで、  $In - Ga - Zn - O$  系酸化物半導体とは、インジウム ( $In$ )、ガリウム ( $Ga$ )、亜鉛 ( $Zn$ ) を有する酸化物という意味であり、その化学量論組成比は特に問わない。また、  $In$  と  $Ga$  と  $Zn$  以外の元素を含んでいてもよい。また、酸化物半導体のエネルギーギャップは 2 eV 以上、好ましくは 2.5 eV 以上、より好ましくは 3 eV 以上であることが好ましい。

10

#### 【0058】

ここでは、酸化物半導体として  $In - Ga - Zn - O$  系膜を用いる。ここでは、モル数比で  $In_2O_3 : Ga_2O_3 : ZnO = 1 : 1 : 1$  または、  $In_2O_3 : Ga_2O_3 : ZnO = 1 : 1 : 2$  としたターゲットを用いてスパッタ法にて成膜する。基板とターゲットの間との距離を 100 mm、圧力 0.6 Pa、直流 (DC) 電源 0.5 kW、酸素 (酸素流量比率 100 %) 霧囲気下で成膜する。なお、パルス直流 (DC) 電源を用いると、成膜時に発生する粉状物質 (パーティクル、ゴミともいう) が軽減でき、膜厚分布も均一となるために好ましい。

20

#### 【0059】

この場合において、処理室内の残留水分を除去しつつ酸化物半導体膜を成膜することが好ましい。酸化物半導体膜に水素、水酸基または水分が含まれない様にするためである。

#### 【0060】

処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボ分子ポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子や、水 ( $H_2O$ ) など水素原子を含む化合物等が排気されるため、当該成膜室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減できる。

30

#### 【0061】

次いで、第 2 のフォトリソグラフィ工程を行い、レジストマスクを形成し、エッチングにより不要な部分を除去して酸化物半導体層 103 を形成する。なお、次に行う酸化物半導体層への第 1 の加熱処理は、島状の酸化物半導体層に加工する前の酸化物半導体膜に行うことでもできる。この段階での断面図を図 3 (B) に示す。

#### 【0062】

次いで、酸化物半導体層の脱水化または脱水素化を行う。脱水化または脱水素化を行う第 1 の加熱処理の温度は、400 以上 750 以下、好ましくは 425 以上 750 以下とする。なお、425 以上であれば加熱処理時間は 1 時間以下でよいが、425 未満であれば加熱処理時間は、1 時間以上行うこととする。ここでは、加熱処理装置の一つである電気炉に基板を導入し、酸化物半導体層に対して窒素霧囲気下において加熱処理を行った後、大気に曝すことなく、同じ炉に高純度の酸素ガス、高純度の  $N_2O$  ガス、または超乾燥エア (露点が -40 以下、好ましくは -60 以下) を導入して冷却を行う。このとき、導入するガスに、水、水素などが含まれないことが好ましい。または、加熱処理装置に導入するガスの純度を、6N (99.9999 %) 以上、好ましくは 7N (99.99999 %) 以上、(即ちガス中の不純物濃度を 1 ppm 以下、好ましくは 0.1 ppm 以下) とする。

40

#### 【0063】

なお、本明細書では、窒素、または希ガス等の不活性気体雰囲気下での加熱処理を脱水化または脱水素化のための加熱処理と呼ぶ。本明細書では、この加熱処理によってH<sub>2</sub>として脱離させていることのみを脱水素化と呼んでいるわけではなく、H、OHなどを脱離することを含めて脱水化または脱水素化と便宜上呼ぶこととする。

【0064】

また、加熱処理装置は電気炉に限らず、例えば、G R T A (G a s R a p i d T h e r m a l A n n e a l) 装置、L R T A (L a m p R a p i d T h e r m a l A n n e a l) 装置等のRTA (R a p i d T h e r m a l A n n e a l) 装置を用いることができる。L R T A 装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、または高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。また、L R T A 装置は、ランプだけでなく、抵抗発熱体などの発熱体からの熱伝導または熱輻射によって、被処理物を加熱する装置を備えていてもよい。G R T A とは高温のガスを用いて加熱処理を行う方法である。ガスには、アルゴンなどの希ガスや窒素などの加熱処理によって被処理物と反応しない不活性気体が用いられる。この様なRTA法を用いて、600以上750以下の温度で数分間加熱処理を行ってもよい。

10

【0065】

また、脱水化または脱水素化を行う第1の加熱処理後に200以上400以下、好ましくは200以上300以下の温度で酸素ガスまたはN<sub>2</sub>Oガス雰囲気下での加熱処理を行ってもよい。

20

【0066】

酸化物半導体層を400以上750以下の温度で熱処理することで、酸化物半導体層の脱水化、脱水素化が図られ、その後の水(H<sub>2</sub>O)の再含浸を防ぐことができる。脱水化または脱水素化と同時にi型の酸化物半導体層は、酸素欠乏型となって低抵抗化、即ちn型化(n<sup>-</sup>、n<sup>+</sup>など)する。n型化した酸化物半導体層に接する酸化物絶縁膜を形成すると、酸化物半導体層は酸素過剰な状態となり、再びi型となって高抵抗化する。この様な酸化物半導体層を用いたトランジスタは、そのしきい値電圧値が正であり、所謂ノーマリーオフ特性を示す。表示装置等の半導体装置に用いるトランジスタは、ゲート電圧が0Vにできるだけ近い正のしきい値電圧であることが好ましい。アクティブマトリクス型の表示装置においては、回路を構成するトランジスタの電気特性が重要であり、この電気特性が表示装置の性能を左右する。特に、トランジスタのしきい値電圧は重要である。トランジスタのしきい値電圧値が負であると、ゲート電圧が0Vでもソース電極とドレイン電極の間に電流が流れる、所謂ノーマリーオン特性となり、該トランジスタで構成した回路を制御することが困難となる。また、しきい値電圧値が正であっても、その絶対値が高いトランジスタの場合には、駆動電圧が足りずにスイッチング動作そのものができないことがある。nチャネル型のトランジスタの場合は、ゲート電圧に正の電圧を印加してはじめてチャネルが形成されて、ドレイン電流が流れ出すトランジスタであることが望ましい。駆動電圧を高くしないとチャネルが形成されないトランジスタや、負の電圧状態でもチャネルが形成されてドレイン電流が流れるトランジスタは、回路に用いるトランジスタとしては不向きである。

30

【0067】

また、第1の加熱処理においては、窒素、またはヘリウム、ネオン、アルゴン等の希ガスに、水、水素などが含まれないことが好ましい。ここで、加熱処理装置に導入する窒素、またはヘリウム、ネオン、アルゴン等の希ガスの純度を、6N(99.9999%)以上、好ましくは7N(99.9999%)以上とすることが好ましい。

40

【0068】

ここで、水素等の不純物を除去することによりi型化または実質的にi型化された酸化物半導体(高純度化された酸化物半導体)は界面準位、界面電荷に対して極めて敏感であるため、ゲート絶縁膜との界面は重要である。そのため高純度化された酸化物半導体に接するゲート絶縁膜(G I)は、高品質化が要求される。

50

## 【0069】

例えば、先に説明したマイクロ波(2.45GHz)を用いた高密度プラズマCVD法は、緻密で絶縁耐圧の高い高品質な絶縁膜を形成することができる。高純度化された酸化物半導体と高品質ゲート絶縁膜が密接することにより、界面準位は低減して界面特性が良好となる。もちろん、ゲート絶縁膜として良質な絶縁膜を形成できるものであれば、スパッタリング法やプラズマCVD法など他の成膜方法を適用することができる。また、成膜後の熱処理によってゲート絶縁膜の膜質、酸化物半導体との界面特性が改質される絶縁膜であっても良い。いずれにしても、ゲート絶縁膜としての膜質が良好であることは勿論のこと、酸化物半導体との界面準位密度を低減し、良好な界面を形成できるものであれば良い。

10

## 【0070】

更に、85、 $2 \times 10^6$ V/cm、12時間のゲートバイアス・熱ストレス試験(BT試験)においては、不純物が酸化物半導体に多く含まれていると、不純物と酸化物半導体の主成分との結合が、強電界(B:バイアス)と高温(T:温度)により切断され、生成された未結合手がしきい値電圧(Vth)のドリフトを誘発することとなる。これに対して、本発明は、酸化物半導体の不純物、特に水素や水等を極力除去し、上記の様にゲート絶縁膜との界面特性を良好にすることにより、BT試験に対しても安定な薄膜トランジスタを得ることを可能としている。

## 【0071】

次に、酸化物半導体膜上に金属材料からなる導電膜をスパッタ法や真空蒸着法で形成する。導電膜の材料としては、アルミニウム、クロム、タンタル、チタン、モリブデン、タンゲステンから選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金等が挙げられる。また、200以上600以下の熱処理を行う場合には、この温度範囲の耐熱性を導電膜に持たせることができが好ましい。Al単体では耐熱性が劣り、また腐蝕しやすい等の問題点があるので耐熱性導電性材料と組み合わせて形成する。この様な耐熱性導電性材料としては、チタン、タンタル、タンゲステン、モリブデン、クロム、ネオジム、スカンジウムから選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金、または上述した元素を成分とする窒化物などがある。

20

## 【0072】

ここでは、導電膜としてチタン膜の単層構造を用いる。導電膜は2層構造としてもよく、アルミニウム膜上にチタン膜を積層してもよい。また、導電膜としてチタン膜上にネオジムを含むアルミニウム(Al-Nd)膜を積層し、更にその上にチタン膜を成膜する3層構造としてもよい。その他、導電膜にシリコンを含むアルミニウム膜の単層構造を用いても良い。

30

## 【0073】

次に、第3のフォトリソグラフィ工程を行い、レジストマスクを形成し、エッチングにより不要な部分を除去して導電膜でなる第2の配線102A及び第3の配線102Bを形成する。この際のエッチング方法としてウェットエッチングまたはドライエッチングを用いる。例えば、アンモニア過水(31重量%過酸化水素水:28重量%アンモニア水:水=5:2:2)を用いたウェットエッチングにより、チタン膜の導電膜をエッチングして第2の配線102A及び第3の配線102Bを選択的にエッチングして酸化物半導体層103を残存させることができる。この段階での断面図を図3(C)に示す。

40

## 【0074】

また、エッチング条件にもよるが第3のフォトリソグラフィ工程において酸化物半導体層の露出領域がエッチングされる場合がある。その場合、第2の配線102A及び第3の配線102Bに挟まれる領域の酸化物半導体層103は、第1の配線101上で第2の配線102A及び第3の配線102Bが重なる領域の酸化物半導体層に比べ、膜厚が薄くなる。

50

## 【0075】

次いで、ゲート絶縁膜 113、酸化物半導体層 103、第2の配線 102A、第3の配線 102B 上に酸化物絶縁層 114 を形成する。この段階で、酸化物半導体層 103 の一部は、酸化物絶縁層 114 と接する。

【0076】

酸化物絶縁層 114 は、少なくとも 1 nm 以上の膜厚とし、酸化物絶縁層に水、水素等の不純物を混入させない方法を適宜用いて形成することができる。本実施の形態では、酸化物絶縁層として酸化珪素膜をスパッタ法で成膜する。成膜時の基板温度は、室温以上 300 以下とすればよく、本実施の形態では 100 とする。酸化珪素膜のスパッタ法による成膜は、希ガス（代表的にはアルゴン）及び酸素の一方の雰囲気下、または両方が混合された雰囲気下において行うことができる。また、成膜用ターゲットとしては、酸化珪素ターゲットまたは珪素ターゲットを用いることができる。例えば、珪素ターゲットを用いて、酸素及び希ガス雰囲気下でスパッタリング法により酸化珪素膜を形成することができる。酸素欠乏状態となり低抵抗化している酸化物半導体層に接して形成する酸化物絶縁層としては、水分、水素イオン、OH<sup>-</sup>などの不純物を含まず、これらが外部から侵入することをブロックする無機絶縁膜を用い、代表的には酸化珪素膜、窒化酸化珪素膜、酸化アルミニウム膜、または酸化窒化アルミニウム膜などを用いる。なお、リン（P）や硼素（B）をドープした成膜用ターゲットを用い、リン（P）や硼素（B）が添加された酸化物絶縁層を形成することもできる。

10

【0077】

本実施の形態では、純度が 6N であり、柱状多結晶 B ドープの珪素ターゲット（抵抗値 0.01 cm）を用い、基板とターゲットとの間との距離（T-S 間距離）を 89 mm、圧力 0.4 Pa、直流（DC）電源 6 kW、酸素（酸素流量比率 100%）雰囲気下でパルス DC スパッタ法により酸化物絶縁層 114 を成膜する。膜厚は 300 nm とする。

20

【0078】

なお、酸化物絶縁層 114 は酸化物半導体層のチャネル形成領域となる領域上に接して設けられ、チャネル保護層としての機能も有する。

【0079】

この場合において、処理室内の残留水分を除去しつつ酸化物絶縁層 114 を成膜することが好ましい。酸化物半導体層 103 及び酸化物絶縁層 114 に水素、水酸基または水分が含まれない様にするためである。

30

【0080】

処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボ分子ポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子や、水（H<sub>2</sub>O）など水素原子を含む化合物等が排気されるため、当該成膜室で成膜した酸化物絶縁層 114 に含まれる不純物の濃度を低減できる。

【0081】

次いで、第2の加熱処理（好ましくは 200 以上 400 以下、例えば 250 以上 350 以下）を不活性ガス雰囲気下で行う。例えば、窒素雰囲気下で 250 、 1 時間の第2の加熱処理を行う。第2の加熱処理を行うと、酸化物半導体層 103 の一部が酸化物絶縁層 114 と接した状態で加熱される。

40

【0082】

第1の加熱処理で水素の離脱と同時に酸素欠乏状態となり低抵抗化された酸化物半導体層 103 が酸化物絶縁層 114 と接した状態で第2の加熱処理が施されると、酸化物絶縁層 114 が接した領域が酸素過剰な状態となる。その結果、酸化物半導体層 103 の酸化物絶縁層 114 が接する領域から、酸化物半導体層 103 の深さ方向に向けて、高抵抗化（i型化）が進む。

【0083】

また、大気中、100 以上 200 以下、1 時間以上 30 時間以下の加熱処理を行つ

50

てもよい。例えば、150で10時間加熱処理を行う。この加熱処理は一定の加熱温度を保持して加熱してもよいし、室温から、100以上200以下の加熱温度への昇温と、加熱温度から室温までの降温を複数回繰り返して行ってもよい。また、この加熱処理を、酸化物絶縁膜の形成前に、減圧下で行ってもよい。減圧下で加熱処理を行うと、加熱時間を短縮することができる。この加熱処理よって、酸化物半導体層から酸化物絶縁層中に水素がとりこまれ、ノーマリーオフとなる薄膜トランジスタを得ることができる。よって半導体装置の信頼性を向上できる。

#### 【0084】

次いで、第4のフォトリソグラフィ工程及びエッティング工程により、酸化物絶縁層114に開口部121を形成し、透光性を有する導電膜を成膜する。透光性を有する導電膜の材料としては、酸化インジウム( $In_2O_3$ )やインジウム錫酸化物( $In_2O_3-SnO_2$ 、以下ITOと略記する)などをスパッタ法や真空蒸着法などを用いて形成する。透光性を有する導電膜の他の材料として、窒素を含ませたAl-Zn-O系膜、即ちAl-Zn-O-N系膜や、窒素を含ませたZn-O系膜や、窒素を含ませたSn-Zn-O系膜を用いてもよい。なお、Al-Zn-O-N系膜の亜鉛の組成比(原子%)は、47原子%以下とし、膜中のアルミニウムの組成比(原子%)より大きく、膜中のアルミニウムの組成比(原子%)は、膜中の窒素の組成比(原子%)より大きい。このような材料のエッティング処理は塩酸系の溶液により行う。しかし、特にITOのエッティングは残渣が発生しやすいので、エッティング加工性を改善するためにインジウム亜鉛酸化物( $In_2O_3-ZnO$ )を用いても良い。

10

20

#### 【0085】

なお、透光性を有する導電膜の組成比の単位は原子%とし、電子線マイクロアナライザー(EPMA: Electron Probe X-ray Micro Analyzer)を用いた分析により評価するものとする。

#### 【0086】

次に、第5のフォトリソグラフィ工程を行い、レジストマスクを形成し、エッティングにより不要な部分を除去して画素電極105を形成する。この段階での断面図を図3(D)に示す。

30

#### 【0087】

こうして、オフ電流の低い薄膜トランジスタ106を有する画素を作製することができる。そして、該画素をマトリクス状に配置して画素部を構成することによりアクティブマトリクス型の液晶表示装置を作製するための一方の基板とすることができます。本明細書では便宜上この様な基板をアクティブマトリクス基板と呼ぶ。

40

#### 【0088】

なお、アクティブマトリクス型の液晶表示装置においては、マトリクス状に配置された画素電極を駆動することによって、画面上に表示パターンが形成される。詳しくは選択された画素電極と該画素電極に対応する対向電極との間に電圧が印加されることによって、画素電極と対向電極との間に配置された液晶層の光学変調が行われ、この光学変調が表示パターンとして観察者に認識される。液晶素子等の表示素子は画素電極105上に設けられる。

#### 【0089】

以上説明した様に、容量素子を省くという、本実施の形態で示す構成とすることにより、酸化物半導体を用いた薄膜トランジスタを具備する画素を作製する際に、開口率の向上を図ることができる。従って、高精細な表示部を有する液晶表示装置とすることができます。

#### 【0090】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

#### 【0091】

##### (実施の形態2)

本発明の一形態は、酸化物半導体中でキャリアの供与体(ドナーまたはアクセプタ)とな

50

り得る不純物を極めて少ないレベルにまで除去することで、真性または実質的に真性な半導体であって、当該酸化物半導体を薄膜トランジスタに適用するものである。本実施の形態では、評価用素子（TEGとも呼ぶ）でのオフ電流の測定値について以下に説明する。

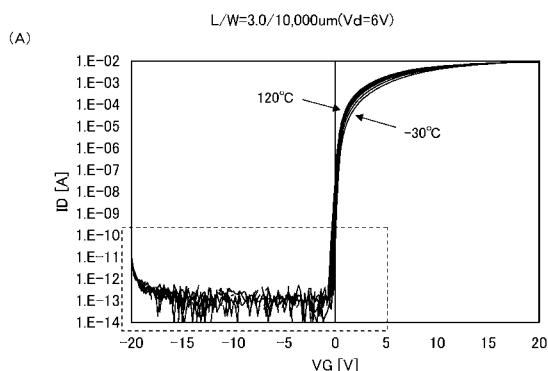

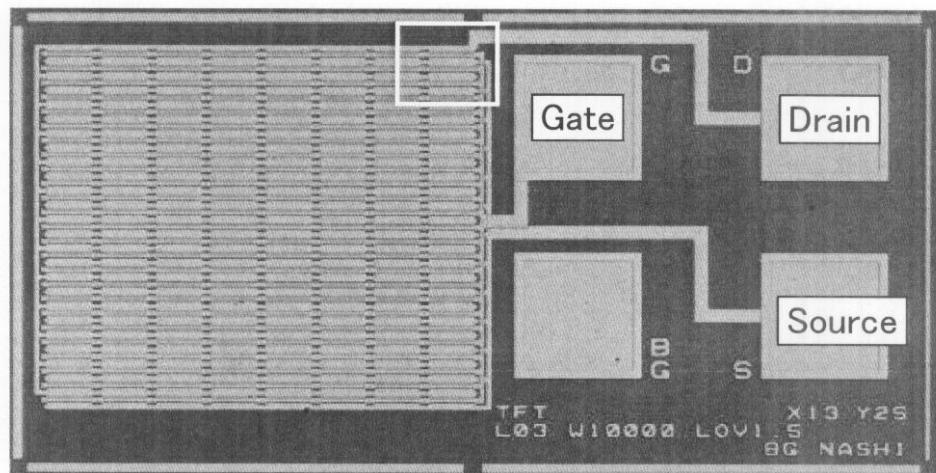

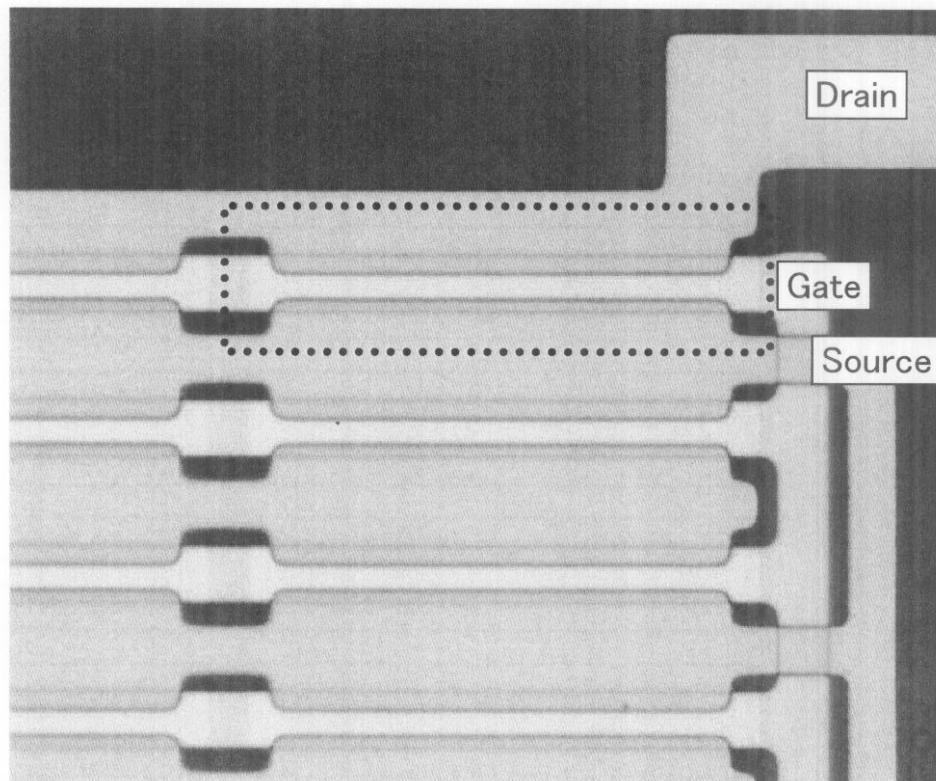

【0092】

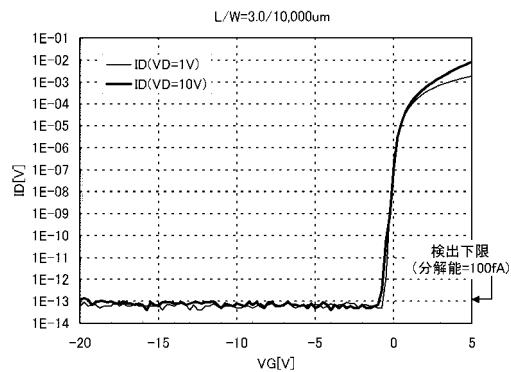

図4に $L/W = 3 \mu m / 50 \mu m$ の薄膜トランジスタを200個並列に接続し、 $L/W = 3 \mu m / 10000 \mu m$ とした薄膜トランジスタの初期特性を示す。また、上面図を図5(A)に示し、その一部を拡大した上面図を図5(B)に示す。図5(B)の点線で囲んだ領域が $L/W = 3 \mu m / 50 \mu m$ 、 $L_{ov} = 1.5 \mu m$ の1段分の薄膜トランジスタである。薄膜トランジスタの初期特性を測定するため、基板温度を室温とし、ソース-ドレイン間電圧（以下、ドレイン電圧または $V_d$ という）が10Vで、ソース-ゲート間電圧（以下、ゲート電圧または $V_g$ という）を-20V～+20Vまで変化させたときのソース-ドレイン電流（以下、ドレイン電流または $I_d$ という）の変化特性、すなわち $V_g - I_d$ 特性を測定した。なお、図4では、 $V_g$ を-20V～+5Vまでの範囲で示している。

10

【0093】

図4に示す様にチャネル幅 $W$ が10000 $\mu m$ の薄膜トランジスタは、 $V_d$ が1V及び10Vにおいてオフ電流は $1 \times 10^{-13} [A]$ 以下となっており、測定機（半導体パラメータ・アナライザ、Agilent 4156C；Agilent社製）の分解能（100fA）以下となっている。

20

【0094】

測定した薄膜トランジスタの作製方法について説明する。

【0095】

まず、ガラス基板上に下地層として、CVD法により窒化珪素膜を形成し、窒化珪素膜上に酸化窒化珪素膜を形成した。そして、酸化窒化珪素膜上にゲート電極層としてスパッタ法によりタンゲステン層を形成した。ここで、タンゲステン層を選択的にエッチングしてゲート電極層を形成した。

【0096】

次に、ゲート電極層上にゲート絶縁層としてCVD法により厚さ100nmの酸化窒化珪素膜を形成した。

30

【0097】

次に、ゲート絶縁層上に、スパッタ法によりIn-Ga-Zn-O系金属酸化物ターゲット（モル数比で、 $In_2O_3 : Ga_2O_3 : ZnO = 1 : 1 : 2$ ）を用いて、厚さ50nmの酸化物半導体膜を形成した。そして、酸化物半導体膜を選択的にエッチングし、島状の酸化物半導体層を形成した。

【0098】

次に、酸化物半導体層をクリーンオーブンにて窒素雰囲気下、450、1時間の第1の熱処理を行った。

【0099】

次に、酸化物半導体層上にソース電極層及びドレイン電極層となるチタン層（厚さ150nm）をスパッタ法により形成した。そして、チタン層を選択的にエッチングしてソース電極層及びドレイン電極層を形成し、チャネル長 $L$ が3 $\mu m$ 、チャネル幅 $W$ が50 $\mu m$ の薄膜トランジスタを200個を並列接続とすることで、 $L/W = 3 \mu m / 10000 \mu m$ となる様にした。

40

【0100】

次に、酸化物半導体層に接する様に保護絶縁層としてリアクティブスパッタ法により酸化珪素膜を膜厚300nmで形成した。そして、酸化珪素膜を選択的にエッチングし、ゲート電極層、ソース電極層及びドレイン電極層上に開口部を形成した。その後、窒素雰囲気下、250で1時間、第2の熱処理を行った。

【0101】

そして、 $V_g - I_d$ 特性を測定する前に150、10時間の加熱を行った。

50

## 【0102】

以上の工程により、ボトムゲート型の薄膜トランジスタを作製した。

## 【0103】

図4に示す様に薄膜トランジスタのオフ電流が、 $1 \times 10^{-13}$  [A] 程度であるのは、上記作製工程において酸化物半導体層中における水素濃度を十分に低減できたためである。酸化物半導体層中の水素濃度は、 $5 \times 10^{19}$  atoms/cm<sup>3</sup> 以下、好ましくは $5 \times 10^{18}$  atoms/cm<sup>3</sup> 以下、更に好ましくは $5 \times 10^{17}$  atoms/cm<sup>3</sup> 以下とする。なお、酸化物半導体層中の水素濃度測定は、二次イオン質量分析法 (SIMS: Secondary Ion Mass Spectrometry) で行う。

## 【0104】

また、In-Ga-Zn-O系酸化物半導体を用いる例を示したが、特に限定されず、他の酸化物半導体材料、例えば、四元系金属酸化物であるIn-Sn-Ga-Zn-O膜や、三元系金属酸化物であるIn-Ga-Zn-O膜、In-Sn-Zn-O膜、In-Al-Zn-O膜、Sn-Ga-Zn-O膜、Al-Ga-Zn-O膜、Sn-Al-Zn-O膜や、二元系金属酸化物であるIn-Zn-O膜、Sn-Zn-O膜、Al-Zn-O膜、Zn-Mg-O膜、Sn-Mg-O膜、In-Mg-O膜や、In-O膜、Sn-O膜、Zn-O膜などの酸化物半導体膜を用いることができる。また、酸化物半導体材料として、Al<sub>2</sub>O<sub>3</sub>を2.5~10wt%混入したIn-Al-Zn-O系や、SiO<sub>2</sub>を2.5~10wt%混入したIn-Zn-O系を用いることもできる。

## 【0105】

また、キャリア測定機で測定される酸化物半導体層のキャリア濃度は、シリコンの真性キャリア濃度 $1.45 \times 10^{10}$  / cm<sup>3</sup> と同等、もしくはそれ以下であることが好ましい。具体的には、 $5 \times 10^{14}$  / cm<sup>3</sup> 以下、好ましくは $5 \times 10^{12}$  / cm<sup>3</sup> 以下である。即ち、酸化物半導体層のキャリア濃度は、限りなくゼロに近くすることができる。

## 【0106】

また、薄膜トランジスタのチャネル長Lを10nm以上1000nm以下とすることも可能であり、回路の動作速度を高速化でき、オフ電流値が極めて小さいため、更に低消費電力化も図ることができる。

## 【0107】

また、薄膜トランジスタのオフ状態において、酸化物半導体層は絶縁体とみなして回路設計を行うことができる。

## 【0108】

続いて、本実施の形態で作製した薄膜トランジスタに対してオフ電流の温度特性を評価した。温度特性は、薄膜トランジスタが使われる最終製品の耐環境性や、性能の維持などを考慮する上で重要である。当然ながら、変化量が小さいほど好ましく、製品設計の自由度が増す。

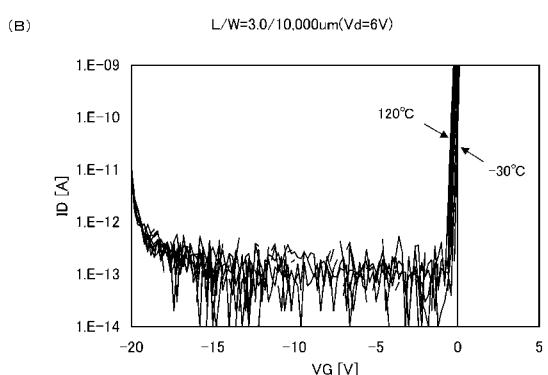

## 【0109】

温度特性は、恒温槽を用い、-30、0、25、40、60、80、100、及び120のそれぞれの温度で薄膜トランジスタを形成した基板を一定温度とし、ドレイン電圧を6V、ゲート電圧を-20V~+20Vまで変化させてVg-Id特性を取得した。

## 【0110】

図6(A)に示すのは、上記それぞれの温度で測定したVg-Id特性を重ね書きしたものであり、点線で囲むオフ電流の領域を拡大したものを図6(B)に示す。図中の矢印で示す右端の曲線が-30、左端が120で取得した曲線で、その他の温度で取得した曲線は、その間に位置する。オン電流の温度依存性はほとんど見られない。一方、オフ電流は拡大図の図6(B)においても明かである様に、ゲート電圧が20V近傍を除いて、全ての温度で測定機の分解能近傍の $1 \times 10^{-12}$  [A] 以下となっており、温度依存性も見えていない。すなわち、120の高温においても、オフ電流が $1 \times 10^{-12}$  [A] 以下を維持しており、チャネル幅Wが10000μmであることを考慮すると、オフ電

10

20

30

40

50

流が非常に小さいことがわかる。

【0111】

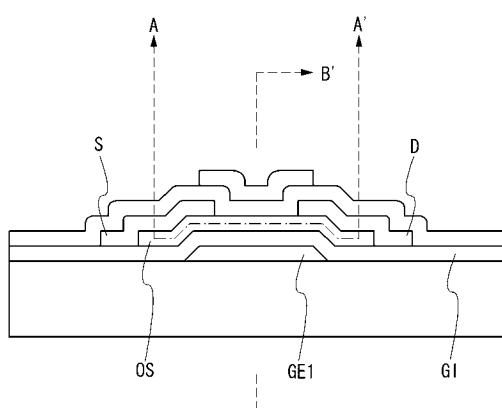

高純度化された酸化物半導体 (purified OS) を用いた薄膜トランジスタは、オフ電流の温度依存性がほとんど現れない。これは、図9(A)のエネルギー-band図で示す様に、酸化物半導体が高純度化されることによって、導電型が限りなく真性型に近づき、フェルミ準位が禁制帯の中央に位置するため、温度依存性を示さなくなると言える。また、これは、酸化物半導体のエネルギーギャップが3eV以上であり、熱励起キャリアが極めて少ないとても起因する。また、ソース領域及びドレイン領域は縮退した状態にあるのでやはり温度依存性が現れない要因となっている。薄膜トランジスタの動作は、縮退したソース領域から酸化物半導体に注入されたキャリアによるものがほとんどであり、キャリア密度の温度依存性がないことから上記特性（オフ電流の温度依存性無し）を説明することができる。また、この極めて低いオフ電流について、以下にエネルギー-band図を用いて説明する。

【0112】

図8は、酸化物半導体を用いた逆スタガ型の薄膜トランジスタの縦断面図である。ゲート電極 (G E 1) 上にゲート絶縁膜 (G I) を介して酸化物半導体層 (OS) が設けられ、その上にソース電極 (S) 及びドレイン電極 (D) が設けられている。

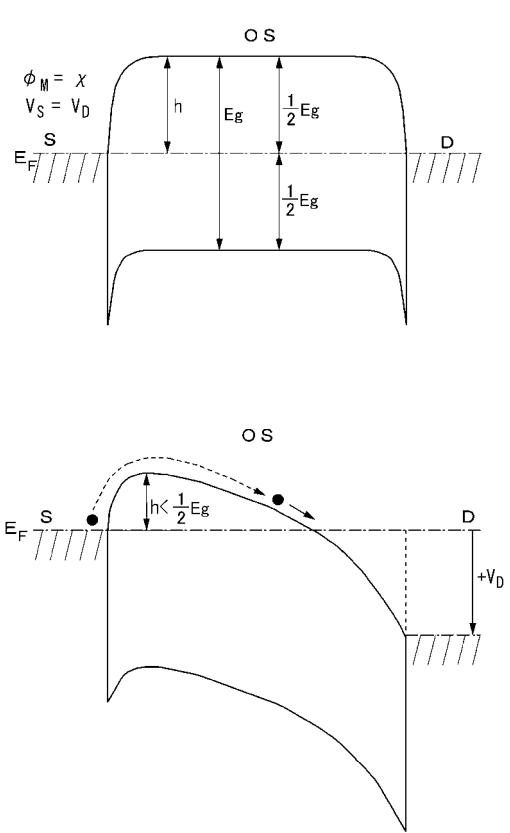

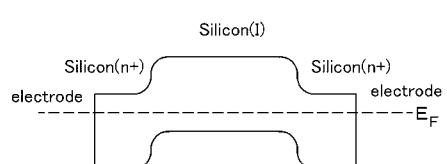

【0113】

図9は、図8に示すA-A'断面におけるエネルギー-band図（模式図）である。図9(A)はソースとドレインの間の電圧を等電位 ( $V_D = 0\text{V}$ ) とした場合を示し、図9(B)はソースに対しドレインに正の電位 ( $V_D > 0\text{V}$ ) を加えた場合を示す。

【0114】

図10は、図8におけるB-B'の断面におけるエネルギー-band図（模式図）である。図10(A)はゲート (G 1) に正の電位 ( $+V_G$ ) が印加された状態であり、ソースとドレイン間にキャリア（電子）が流れるオン状態を示している。また、図10(B)は、ゲート (G 1) に負の電位 ( $-V_G$ ) が印加された状態であり、オフ状態（少数キャリアは流れない）である場合を示す。

【0115】

図11は、真空準位と金属の仕事関数 ( $\phi_M$ ) 、酸化物半導体の電子親和力 ( $\phi$ ) の関係を示す。

【0116】

常温において金属中の電子は縮退しており、フェルミ準位は伝導帯内に位置する。一方、従来の酸化物半導体は一般にn型であり、その場合のフェルミ準位 ( $E_F$ ) は、バンドギャップ中央に位置する真性フェルミ準位 ( $E_i$ ) から離れて、伝導帯寄りに位置している。なお、酸化物半導体において含有される水素の一部はドナーとなり、n型化する一つの要因であることが知られている。

【0117】

これに対して本発明に係る酸化物半導体は、n型不純物である水素を酸化物半導体から除去し、酸化物半導体の主成分以外の不純物が極力含まれない様に高純度化することにより真性 (i型) とし、または真性型とせんとしたものである。すなわち、不純物を添加してi型化するのではなく、水素や水等の不純物を極力除去したことにより、高純度化されたi型（真性半導体）またはそれに近づけることを特徴としている。そうすることにより、フェルミ準位 ( $E_F$ ) は真性フェルミ準位 ( $E_i$ ) と同じレベルにまですることができる。

【0118】

酸化物半導体のバンドギャップ ( $E_g$ ) が3.15eVである場合、電子親和力 ( $\phi$ ) は4.3eVと言われている。ソース電極及びドレイン電極を構成するチタンの仕事関数は、酸化物半導体の電子親和力 ( $\phi$ ) とほぼ等しい。この場合、金属-酸化物半導体界面においては、電子に対してショットキー型の障壁は形成されない。

【0119】

すなわち、金属の仕事関数 ( $\phi_M$ ) と酸化物半導体の電子親和力 ( $\phi$ ) がほぼ等しい場合

10

20

30

40

50

、両者が接触すると図9(A)で示すようなエネルギー・バンド図(模式図)が示される。

【0120】

図9(B)において黒丸(●)は電子を示し、ドレインに正の電位が印加されると、電子はバリア(h)をこえて酸化物半導体に注入され、ドレインに向かって流れる。この場合、バリア(h)の高さは、ゲート電圧とドレイン電圧に依存して変化するが、正のドレイン電圧が印加された場合には、電圧印加のない図9(A)のバリアの高さすなわちバンドギャップ(Eg)の1/2よりもバリア(h)の高さは小さい値となる。

【0121】

このとき電子は、図9(A)で示す様にゲート絶縁膜と高純度化された酸化物半導体との界面における、酸化物半導体側のエネルギー的に安定な最低部を移動する。

10

【0122】

また、図9(B)において、ゲート(G1)に負の電位(逆バイアス)が印加されると、少数キャリアであるホールは実質的にゼロであるため、電流は限りなくゼロに近い値となる。

【0123】

例えば、薄膜トランジスタのチャネル幅Wが $1 \times 10^4 \mu\text{m}$ でチャネル長が $3 \mu\text{m}$ の素子であっても、オフ電流が $10^{-13} \text{ A}$ 以下であり、サブスレッショルドスイッチング値(S値)が $0.1 \text{ V} / \text{dec}$ 。(ゲート絶縁膜厚 $100 \text{ nm}$ )が得られる。

20

【0124】

なお、図19にシリコン半導体を用いた場合のトランジスタのバンド構造を示す。シリコン半導体の真性キャリア密度は $1.45 \times 10^{10} / \text{cm}^3$ (300K)であり、室温においてもキャリアが存在している。これは、室温においても、熱励起キャリアが存在していることを意味している。実用的にはリンまたはホウ素などの不純物が添加されたシリコンウェハーが使用されるので、実際には $1 \text{ cm}^3$ あたり $1 \times 10^{14}$ (個)以上のキャリアがシリコン半導体に存在し、これがソース-ドレイン間の伝導に寄与する。更に、シリコン半導体のバンドギャップは $1.12 \text{ eV}$ であるので、シリコン半導体を用いたトランジスタは温度に依存してオフ電流が大きく変動することとなる。

20

【0125】

従って、単にバンドギャップの広い酸化物半導体をトランジスタに適用するのではなく、酸化物半導体の主成分以外の不純物が極力含まれない様に高純度化することにより、キャリア濃度を $1 \times 10^{14} / \text{cm}^3$ 以下、好ましくは $1 \times 10^{12} / \text{cm}^3$ 以下となる様にすることで、実用的な動作温度で熱的に励起されるキャリアを排除して、ソース側から注入されるキャリアのみによってトランジスタを動作させることができる。それにより、オフ電流を $1 \times 10^{-13} \text{ A}$ 以下にまで下げると共に、温度変化によってオフ電流がほとんど変化しない極めて安定に動作するトランジスタを得ることができる。

30

【0126】

この様にオフ電流値が極めて小さい薄膜トランジスタを用いて、記憶回路(記憶素子)などを作製した場合、オフ電流値が小さくほとんどリークがないため、記憶データを保持する時間を長くすることができる。同様に液晶表示装置などでは、保持容量から薄膜トランジスタを通したリークが抑えられるため、補助容量を設けずに液晶容量のみで画素の電位を保持することが可能となる。

40

【0127】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

【0128】

(実施の形態3)

本実施の形態においては、液晶表示装置に適用できる画素の構成及び画素の動作について説明する。

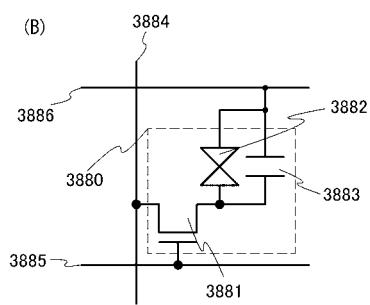

【0129】

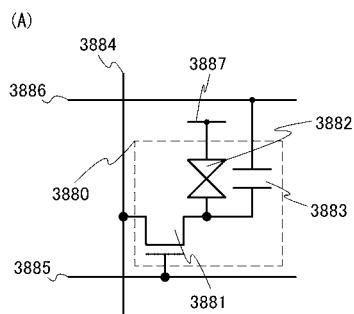

図12(A)は、液晶表示装置に適用できる画素構成の一例を示す図である。画素388

50

0は、トランジスタ3881、液晶素子3882及び容量素子3883を有している。トランジスタ3881のゲートは、配線3885と電気的に接続される。トランジスタ3881の第1端子は、配線3884と電気的に接続される。トランジスタ3881の第2端子は、液晶素子3882の第1端子と電気的に接続される。液晶素子3882の第2端子は、配線3887と電気的に接続される。容量素子3883の第1端子は、液晶素子3882の第1端子と電気的に接続される。容量素子3883の第2端子は、配線3886と電気的に接続される。

### 【0130】

配線3884は、信号線として機能させることができる。信号線は、画素の外部から入力された信号電圧を画素3880に伝達するための配線である。配線3885は、走査線として機能させることができる。走査線は、トランジスタ3881のオンオフを制御するための配線である。配線3886は、容量線として機能させることができる。容量線は、容量素子3883の第2端子に所定の電圧を加えるための配線である。トランジスタ3881は、スイッチとして機能させることができる。容量素子3883は、補助容量として機能させることができる。容量素子は、スイッチがオフの状態においても、信号電圧が液晶素子3882に加わり続ける様にするための補助容量である。配線3887は、対向電極として機能させることができる。対向電極は、液晶素子3882の第2端子に所定の電圧を加えるための配線である。なお、それぞれの配線が持つことのできる機能はこれに限定されず、様々な機能を有することができる。例えば、容量線に加える電圧を変化させることで、液晶素子に加えられる電圧を調整することもできる。

10

20

30

### 【0131】

図12(B)は、液晶表示装置に適用できる画素構成の他の一例を示す図である。図12(B)に示す画素構成例は、図12(A)に示す画素構成例と比較して、配線3887が省略され、かつ、液晶素子3882の第2端子と容量素子3883の第2端子とが電気的に接続されている点が異なっている以外は、図12(A)に示す画素構成例と同様な構成である。図12(B)に示す画素構成例は、液晶素子が横電界モード(IPSモード、FFSモードを含む)である場合に適用できる。なぜならば、液晶素子が横電界モードである場合、液晶素子3882の第2端子及び容量素子3883の第2端子を同一基板上に形成させることができるために、液晶素子3882の第2端子と容量素子3883の第2端子とを電気的に接続させることができるのである。図12(B)に示すような画素構成とすることで、配線3887を省略できるので、製造工程を簡略化することができ、製造コストを低減できる。

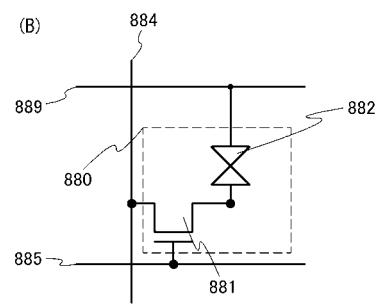

### 【0132】

ここで、図13に実施の形態1で説明した薄膜トランジスタを用いた画素部の構成を示す。図13(A)は図12(A)の構成から容量素子3883を省いた構成である。また、図13(B)は、図12(B)から容量素子3883を省いた構成であり、液晶素子の第2端子は、共通配線889に接続される。実施の形態2で説明した様に、オフ電流が十分に低い薄膜トランジスタを用いることで、液晶素子に並列した容量素子(補助容量)を設けずに液晶容量のみで電位を保持することができる。もちろん、前述した比較例と同様に容量素子を設けても良く、そのサイズを小さくすることもできる。また、液晶容量よりも小さな補助容量を設けることもできる。以降、本実施の形態では容量素子を省いた画素構成で説明を行う。

40

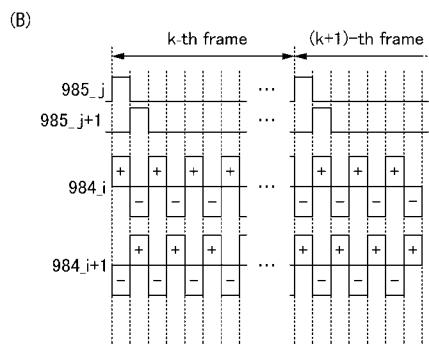

### 【0133】

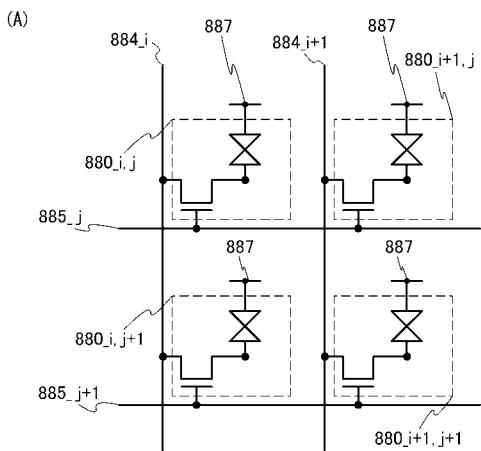

図14(A)は、図13(A)に示す画素構成がマトリクス状に複数配置されている場合の回路構成を示す図である。図14(A)に示す回路構成は、表示部が有する複数の画素のうち、4つの画素を抜き出して示す図である。そして、i列j行(i, jは自然数)に位置する画素を、画素880\_i, jと表記し、画素880\_i, jには、配線884\_i、配線885\_jが、それぞれ電気的に接続される。同様に、画素880\_i+1, jについては、配線884\_i+1、配線885\_jと電気的に接続される。同様に、画素880\_i, j+1については、配線884\_i、配線885\_j+1と電気的に接続さ

50

れる。同様に、画素  $880_{-}i+1, j+1$  については、配線  $884_{-}i+1$ 、配線  $885_{-}j+1$  と電気的に接続される。なお、各配線は、同じ列または行に属する複数の画素によって共有されることができる。なお、図 14 (A) に示す画素構成において配線  $887$  は対向電極であり、対向電極は全ての画素において共通であることから、配線  $887$  については自然数  $i$  または  $j$  による表記は行なわないこととする。なお、図 13 (B) に示す画素構成を用いることも可能であるため、配線  $887$  が記載されている構成であっても配線  $887$  は必須ではなく、他の配線と共有されること等によって省略されることがある。

#### 【0134】

図 14 (A) に示す画素構成は、様々な方法によって駆動されることがある。特に、交流駆動と呼ばれる方法によって駆動されることによって、液晶素子の劣化（焼き付き）を抑制することができる。図 14 (B) は、交流駆動の 1 つである、ドット反転駆動が行なわれる場合の、図 14 (A) に示す画素構成における各配線に加えられる電圧のタイミングチャートを表す図である。ドット反転駆動が行なわれることによって、交流駆動が行なわれる場合に視認されるフリッカ（ちらつき）を抑制することができる。なお、図 14 (B) には、配線  $885_{-}j$  に入力される信号  $985_{-}j$ 、配線  $885_{-}j+1$  に入力される信号  $985_{-}j+1$ 、配線  $884_{-}i$  に入力される信号  $984_{-}i$ 、配線  $884_{-}i+1$  に入力される信号  $984_{-}i+1$  を示す。

#### 【0135】

図 14 (A) に示す画素構成において、配線  $885_{-}j$  と電気的に接続されている画素におけるスイッチは、1 フレーム期間中の第  $j$  ゲート選択期間において選択状態（オン状態）となり、それ以外の期間では非選択状態（オフ状態）となる。そして、第  $j$  ゲート選択期間の後に、第  $j+1$  ゲート選択期間が設けられる。この様に順次走査が行なわれることで、1 フレーム期間内に全ての画素が順番に選択状態となる。図 14 (B) に示すタイミングチャートでは、電圧が高い状態（ハイレベル）となることで、当該画素におけるスイッチが選択状態となり、電圧が低い状態（ローレベル）となることで非選択状態となる。

#### 【0136】

図 14 (B) に示すタイミングチャートでは、第  $k$  フレーム（ $k$  は自然数）における第  $j$  ゲート選択期間において、信号線として用いる配線  $884_{-}i$  に正の信号電圧が加えられ、配線  $884_{-}i+1$  に負の信号電圧が加えられる。そして、第  $k$  フレームにおける第  $j+1$  ゲート選択期間において、配線  $884_{-}i$  に負の信号電圧が加えられ、配線  $884_{-}i+1$  に正の信号電圧が加えられる。その後も、それぞれの信号線は、ゲート選択期間ごとに極性が反転した信号が交互に加えられる。その結果、第  $k$  フレームにおいては、画素  $880_{-}i, j$  には正の信号電圧、画素  $880_{-}i+1, j$  には負の信号電圧、画素  $880_{-}i, j+1$  には負の信号電圧、画素  $880_{-}i+1, j+1$  には正の信号電圧が、それぞれ加えられることとなる。そして、第  $k+1$  フレームにおいては、それぞれの画素において、第  $k$  フレームにおいて書き込まれた信号電圧とは逆の極性の信号電圧が書き込まれる。その結果、第  $k+1$  フレームにおいては、画素  $880_{-}i, j$  には負の信号電圧、画素  $880_{-}i+1, j$  には正の信号電圧、画素  $880_{-}i, j+1$  には正の信号電圧、画素  $880_{-}i+1, j+1$  には負の信号電圧が、それぞれ加えられることとなる。この様に、同じフレームにおいては隣接する画素同士で異なる極性の信号電圧が加えられ、更に、それぞれの画素においては 1 フレームごとに信号電圧の極性が反転される駆動方法が、ドット反転駆動である。ドット反転駆動によって、液晶素子の劣化を抑制しつつ、表示される画像全体または一部が均一である場合に視認されるフリッカを低減することができる。なお、配線  $884$  のタイミングチャートにおける信号電圧の表記は極性のみとなっているが、実際は、表示された極性において様々な信号電圧の値をとり得る。なお、ここでは 1 ドット（1 画素）毎に極性を反転させる場合について述べたが、これに限定されず、複数の画素毎に極性を反転させることもできる。例えば、2 ゲート選択期間毎に書き込む信号電圧の極性を反転させることで、信号電圧の書き込みにかかる消費電力を低減させることができる。他にも、1 列毎に極性を反転させること（ソースライン反転）もできるし

10

20

30

40

50

、1行ごとに極性を反転させること（ゲートライン反転）もできる。

【0137】

また、このとき画素部にオーバードライブ電圧を加え、液晶素子の応答速度を高めて残像を抑える、所謂オーバードライブ駆動を用いてもよい。これにより動画を映したときにその動きを鮮明にすることができます。

【0138】

特に、本発明の一態様の様に液晶素子に並列した容量素子を設けない場合には、データの画素への書き込みが終わった後に液晶の状態変化と共に誘電率が変化し、液晶自身の容量が変化して画素で保持している電位を変えてしまう場合もあるため、オーバードライブ駆動は有効な駆動方法となる。

10

【0139】

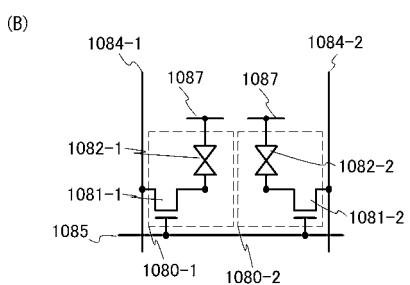

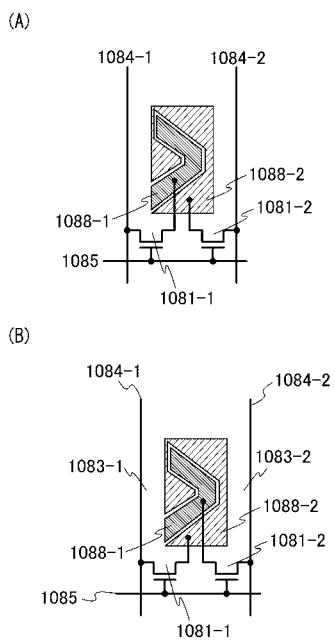

次に、液晶素子が、MVAモードまたはPVAモード等に代表される、垂直配向（VA）モードである場合に特に好ましい画素構成及びその駆動方法について述べる。VAモードは、製造時にラビング工程が不要、黒表示時の光漏れが少ない、駆動電圧が低い等の優れた特徴を有するが、画面を斜めから見たときに画質が劣化してしまう（視野角が狭い）という問題点も有する。VAモードの視野角を広くするには、図15（A）及び図15（B）に示す様に、1画素に複数の副画素（サブピクセル）を有する画素構成とすることが有効である。図15（A）及び図15（B）に示す画素構成は、画素が2つの副画素（第1の副画素1080-1、第2の副画素1080-2）を含む場合の一例を表すものである。なお、1つの画素における副画素の数は2つに限定されず、様々な数の副画素を用いることができる。副画素の数が大きいほど、より視野角を広くすることができます。複数の副画素は互いに同一の回路構成とすることができる、ここでは、全ての副画素が図13（A）に示す回路構成と同様であるとして説明する。なお、第1の副画素1080-1は、トランジスタ1081-1、液晶素子1082-1を有するものとし、それぞれの接続関係は図13（A）に示す回路構成に準じることとする。同様に、第2の副画素1080-2は、トランジスタ1081-2、液晶素子1082-2を有するものとし、それぞれの接続関係は図13（A）に示す回路構成に準じることとする。

20

【0140】

図15（A）に示す画素構成は、1画素を構成する2つの副画素に対し、走査線として用いる配線1085を2本（配線1085-1、配線1085-2）有し、信号線として用いる配線1084を1本有する構成を表すものである。この様に、信号線を2つの副画素で共用することにより、開口率を向上させることができ、更に、信号線駆動回路を簡単なものとすることができるので製造コストが低減でき、かつ、液晶パネルと駆動回路ICの接続点数を低減できるので、歩留まりを向上できる。図15（B）に示す画素構成は、1画素を構成する2つの副画素に対し、走査線として用いる配線1085を1本有し、信号線として用いる配線1084を2本（配線1084-1、配線1084-2）有する構成を表すものである。この様に、走査線を2つの副画素で共用することにより、開口率を向上させることができ、更に全体の走査線本数を低減できるので、高精細な液晶パネルにおいても1つあたりのゲート線選択期間を十分に長くすることができ、それぞれの画素に適切な信号電圧を書き込むことができる。

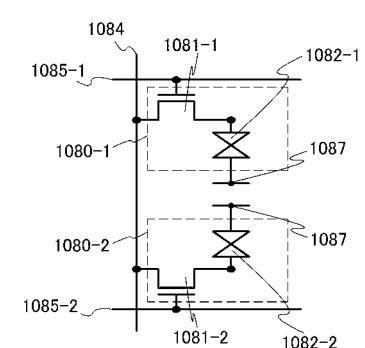

30

【0141】

図16（A）及び図16（B）は、図15（B）に示す画素構成において、液晶素子を画素電極の形状に置き換えた上で、各素子の電気的接続状態を模式的に表す例である。図16（A）において、第1画素電極1088-1は、図15（B）における液晶素子1082-1の第1端子に相当し、第2画素電極1088-2は、図15（B）における液晶素子1082-2の第1端子に相当する。すなわち、第1画素電極1088-1は、トランジスタ1081-1のソースまたはドレインの一方と電気的に接続され、第2画素電極1088-2は、トランジスタ1081-2のソースまたはドレインの一方と電気的に接続される。一方、図16（B）においては、画素電極とトランジスタの接続関係を逆にする。すなわち、第1画素電極1088-1は、トランジスタ1081-2のソースまたはド

40

50

レインの一方と電気的に接続され、第2画素電極1088-2は、トランジスタ1081-1のソースまたはドレンの一方と電気的に接続されるものとする。なお、図示はしていないが、それぞれの画素電極は、液晶を介して対向電極と接続され、液晶素子を形成する。

【0142】

次に、本発明の一態様における酸化物半導体層を用いた薄膜トランジスタにより、どの程度液晶表示装置の各画素での開口率が向上するかについて概算を見積もる。

【0143】

画素の開口率を見積もるためのパラメータとしては、酸化物半導体層を用いた薄膜トランジスタのリーク電流を $1 \times 10^{-13}$  (A)、パネルサイズを3.4インチ、表示する階調を256階調、入力する電圧を10V、1フレームを1/60秒で表示を行うものとする。また、ゲート絶縁膜の誘電率を3.7 (F/m)、膜厚を $1 \times 10^{-7}$  (m)として説明するものである。

10

【0144】

まず画素数 $540 \times RGB \times 960$ のパネル(第1のパネルという)に上記パラメータを適用した際の容量素子の面積、及び開口率について概算を見積もる。当該パネルにおいては、画素サイズが $26 (\mu m) \times 78 (\mu m)$ 、即ち $2.03 \times 10^{-9} (m^2)$ となる。このうち、配線及び薄膜トランジスタが占める領域を除いた面積は、 $1.43 \times 10^{-9} (m^2)$ となり、配線及び薄膜トランジスタが占める領域の面積は、 $6.00 \times 10^{-10} (m^2)$ となる。

20

【0145】

第1のパネルで必要最低限の容量値を有する補助容量は、酸化物半導体層を有する薄膜トランジスタを備えた画素で、 $4.25 \times 10^{-14} (F)$ となる。この場合、必要な容量面積が $1.30 \times 10^{-10} (m^2)$ となり、画素に占める容量素子の面積の割合が6.4(%)、開口率が64.0(%)となる。

【0146】

また、画素数 $480 \times RGB \times 640$ のパネル(第2のパネルという)に上記パラメータを適用した際の容量素子の面積、及び開口率について概算を見積もる。当該パネルにおいては、画素サイズが $36 (\mu m) \times 108 (\mu m)$ 、即ち $3.89 \times 10^{-9} (m^2)$ となる。このうち、配線及び薄膜トランジスタが占める領域を除いた面積は、 $3.29 \times 10^{-9} (m^2)$ となり、配線及び薄膜トランジスタが占める領域の面積は、 $6.00 \times 10^{-10} (m^2)$ となる。

30

【0147】

第2のパネルで必要最低限の容量値を有する補助容量は、酸化物半導体層を有する薄膜トランジスタを備えた画素で、 $4.25 \times 10^{-14} (F)$ となる。この場合、必要な容量面積が $1.30 \times 10^{-10} (m^2)$ となり、画素に占める容量素子の面積の割合が3.3(%)、開口率が81.2(%)となる。

【0148】

これら第1のパネル及び第2のパネルに対して、本発明の一態様における酸化物半導体層を有する薄膜トランジスタを用いることで、容量線が削減でき、画素電極105が占める領域を広げることができる。算出された開口率は、第1のパネルで70.4%、第2のパネルで84.5%であり、容量素子を省くことで大幅に開口率が向上することがわかる。

40

【0149】

本実施の形態の画素においても、上記実施の形態の構成と組み合わせることによって、酸化物半導体を用いた薄膜トランジスタを具備する画素を作製する際に、開口率の向上を図ることができる。

【0150】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

【0151】

50

## (実施の形態4)

本実施の形態においては、上記実施の形態で説明した液晶表示装置を具備する電子機器の例について説明する。

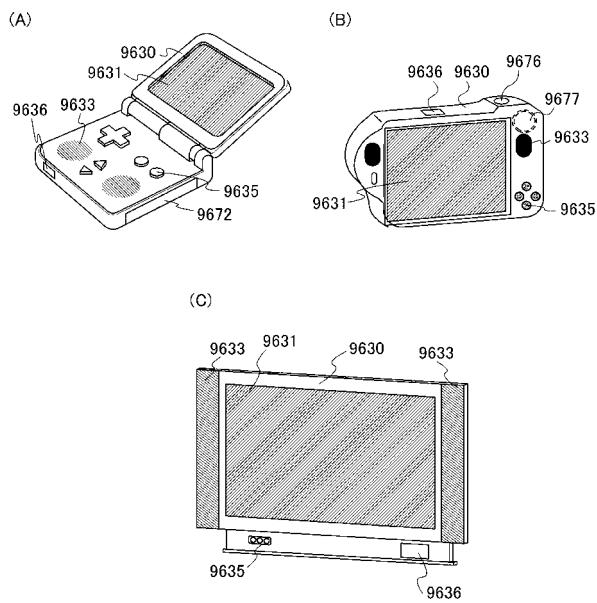

## 【0152】

図17(A)は携帯型遊技機であり、筐体9630、表示部9631、スピーカ9633、操作キー9635、接続端子9636、記録媒体読込部9672、等を有することができる。図17(A)に示す携帯型遊技機は、記録媒体に記録されているプログラムまたはデータを読み出して表示部に表示する機能、他の携帯型遊技機と無線通信を行って情報を共有する機能、等を有することができる。なお、図17(A)に示す携帯型遊技機が有する機能はこれに限定されず、様々な機能を有することができる。

10

## 【0153】

図17(B)はデジタルカメラであり、筐体9630、表示部9631、スピーカ9633、操作キー9635、接続端子9636、シャッターボタン9676、受像部9677、等を有することができる。図17(B)に示すテレビ受像機能付きデジタルカメラは、静止画を撮影する機能、動画を撮影する機能、撮影した画像を自動または手動で補正する機能、アンテナを介して様々な情報を取得する機能、撮影した画像、またはアンテナを介して取得した情報を保存する機能、撮影した画像、またはアンテナを介して取得した情報を表示部に表示する機能、等を有することができる。なお、図17(B)に示すテレビ受像機能付きデジタルカメラが有する機能はこれに限定されず、様々な機能を有することができる。

20

## 【0154】

図17(C)はテレビ受像機であり、筐体9630、表示部9631、スピーカ9633、操作キー9635、接続端子9636、等を有することができる。図17(C)に示すテレビ受像機は、テレビ用電波を処理して画像信号に変換する機能、画像信号を処理して表示に適した信号に変換する機能、画像信号のフレーム周波数を変換する機能、等を有することができる。なお、図17(C)に示すテレビ受像機が有する機能はこれに限定されず、様々な機能を有することができる。

30

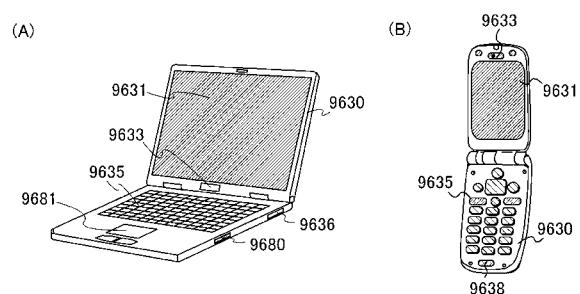

## 【0155】

図18(A)はコンピュータであり、筐体9630、表示部9631、スピーカ9633、操作キー9635、接続端子9636、ポインティングデバイス9681、外部接続ポート9680等を有することができる。図18(A)に示すコンピュータは、様々な情報(静止画、動画、テキスト画像など)を表示部に表示する機能、様々なソフトウェア(プログラム)によって処理を制御する機能、無線通信または有線通信などの通信機能、通信機能を用いて様々なコンピュータネットワークに接続する機能、通信機能を用いて様々なデータの送信または受信を行う機能、等を有することができる。なお、図18(A)に示すコンピュータが有する機能はこれに限定されず、様々な機能を有することができる。

40

## 【0156】

図18(B)は携帯電話であり、筐体9630、表示部9631、スピーカ9633、操作キー9635、マイクロフォン9638等を有することができる。図18(B)に示した携帯電話は、様々な情報(静止画、動画、テキスト画像など)を表示部に表示する機能、カレンダー、日付または時刻などを表示部に表示する機能、表示部に表示した情報を操作または編集する機能、様々なソフトウェア(プログラム)によって処理を制御する機能、等を有することができる。なお、図18(B)に示した携帯電話が有する機能はこれに限定されず、様々な機能を有することができる。

50

## 【0157】

図18(C)は電子ペーパー端末(E-bookともいう)であり、筐体9630、表示部9631、操作キー9635等を有することができる。図18(C)に示した電子ペーパーは、様々な情報(静止画、動画、テキスト画像など)を表示部に表示する機能、カレンダー、日付または時刻などを表示部に表示する機能、表示部に表示した情報を操作または編集する機能、様々なソフトウェア(プログラム)によって処理を制御する機能、等を

50

有することができる。なお、図18( C )に示した電子ペーパーが有する機能はこれに限定されず、様々な機能を有することができる。

## 【0158】

本実施の形態において述べた電子機器は、表示部を構成する複数の画素において、開口率の向上が図られた液晶表示装置を用いることができる。

## 【0159】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

## 【符号の説明】

## 【0160】

|        |          |    |

|--------|----------|----|

| 101    | 配線       | 10 |

| 102 A  | 配線       |    |

| 102 B  | 配線       |    |

| 103    | 酸化物半導体層  |    |

| 105    | 画素電極     |    |

| 106    | 薄膜トランジスタ |    |

| 111    | 基板       |    |

| 112    | 下地膜      |    |

| 113    | ゲート絶縁膜   |    |

| 114    | 酸化物絶縁層   | 20 |

| 121    | 開口部      |    |

| 700    | 基板       |    |

| 701    | 画素       |    |

| 702    | 画素部      |    |

| 703    | 走査線駆動回路  |    |

| 704    | 信号線駆動回路  |    |

| 880    | 画素       |    |

| 884    | 配線       |    |

| 885    | 配線       |    |

| 887    | 配線       | 30 |

| 889    | 共通配線     |    |

| 984    | 信号       |    |

| 985    | 信号       |    |

| 1080   | 副画素      |    |

| 1081   | トランジスタ   |    |

| 1082   | 液晶素子     |    |

| 1084   | 配線       |    |

| 1085   | 配線       |    |

| 1088   | 画素電極     |    |

| 2101   | 配線       | 40 |

| 2102 A | 配線       |    |

| 2102 B | 配線       |    |

| 2103   | 酸化物半導体層  |    |

| 2104   | 容量線      |    |

| 2105   | 画素電極     |    |

| 2106   | 薄膜トランジスタ |    |

| 2111   | 基板       |    |

| 2112   | 下地膜      |    |

| 2113   | ゲート絶縁膜   |    |

| 2114   | 酸化物絶縁層   | 50 |

|         |             |

|---------|-------------|

| 3 8 8 0 | 画素          |

| 3 8 8 1 | トランジスタ      |

| 3 8 8 2 | 液晶素子        |

| 3 8 8 3 | 容量素子        |

| 3 8 8 4 | 配線          |

| 3 8 8 5 | 配線          |

| 3 8 8 6 | 配線          |

| 3 8 8 7 | 配線          |

| 9 6 3 0 | 筐体          |

| 9 6 3 1 | 表示部         |

| 9 6 3 3 | スピーカ        |

| 9 6 3 5 | 操作キー        |

| 9 6 3 6 | 接続端子        |

| 9 6 3 8 | マイクロフォン     |

| 9 6 7 2 | 記録媒体読込部     |

| 9 6 7 6 | シャッターボタン    |

| 9 6 7 7 | 受像部         |

| 9 6 8 0 | 外部接続ポート     |

| 9 6 8 1 | ポインティングデバイス |

10

【図1】

【図2】

【図3】

【図4】

【図6】

【図7】

【図 8】

【図 9】

【図 10】

【図 11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図5】

(A)

(B)

---

フロントページの続き

F ターム(参考) 2H092 JA25 JA26 JA31 JA32 JA33 JA35 JA46 KA05 KA08 KA12

KA19 KA24 KB05 KB14 MA05 MA08 MA13 NA07 NA22

5F110 AA06 AA30 BB01 BB02 CC07 DD02 DD14 DD15 DD17 EE02

EE03 EE04 EE14 EE23 EE42 EE44 FF01 FF02 FF03 FF04

FF29 FF30 FF36 GG01 GG25 GG28 GG29 GG43 GG58 HK03

HK04 HK06 HK21 HK22 HK32 HK33 HL07 NN02 NN23 NN34

NN72 QQ02