(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2017년06월01일

(11) 등록번호 10-1742825

(24) 등록일자 2017년05월26일

(51) 국제특허분류(Int. Cl.)

H01L 21/768 (2006.01) H01L 21/02 (2006.01)

H01L 21/205 (2006.01) H01L 21/28 (2006.01)

H01L 21/324 (2017.01)

(21) 출원번호 10-2011-0004334

(22) 출원일자 2011년01월17일

심사청구일자 2016년01월15일

(65) 공개번호 10-2011-0084130

(43) 공개일자 2011년07월21일

(30) 우선권주장

12/688,154 2010년01월15일 미국(US)

12/689,803 2010년01월19일 미국(US)

(56) 선행기술조사문헌

US20050142833 A1

US20070145600 A1

JP2002164351 A

JP2001524754 A

(73) 특허권자

노벨러스 시스템즈, 인코포레이티드

미국, 94538 캘리포니아주, 프레몬트, 쿠싱 파크

웨이 4650

(72) 발명자

바너지, 아난다

미국, 오레곤 97068, 웨스트 린, 베닝تون 코트

19837

안토넬리, 조니 앤드류

미국, 오레곤 97202, 포틀랜드, 에스이 유마틸라

스트리트 1635

(뒷면에 계속)

(74) 대리인

특허법인인벤투스

전체 청구항 수 : 총 23 항

심사관 : 김종희

(54) 발명의 명칭 다마신 인터커넥트에서 전자이동 저항성 개선을 위한 계면층

**(57) 요약**

금속 배선과 절연막 확산 장벽(또는 에칭 저지) 층 사이의 계면에 존재하는 보호 캡을 이용하여 인터커넥트의 전자이동 성능을 개선할 수 있다. 보호 캡은 약 350°C의 기판 온도에서 플라스마의 부재 하에서 산화물-프리 구리 표면을 유기알루미늄 화합물로 처리하여, 노출된 구리 위에 알루미늄-함유 물질의 제 1 층을 중착함으로써 형성된다. 형성된 알루미늄-함유 층을 화학적으로 변화시켜 부분적으로 또는 전체적으로 패시베이션되어 상기 층에 Al-N, Al-O, 또는 Al-O와 Al-N 둘 모두의 결합을 형성한다. 일부 실시예에서, 노출된 제 1 층을 갖는 기판을 플라스마의 부재 하에서 산소-함유 반응물 및/또는 질소-함유 반응물과 접촉시킴으로써 패시베이션이 형성된다. 노출된 ULK를 포함하는 기판 위에 보호 캡이 형성될 수 있다. 통상적으로 절연막 부분에 존재하는 알루미늄-함유 층이 Al-O 결합을 갖는 비-전도성 층을 자발적으로 형성할 것이다.

**대표 도** - 도1e

(72) 발명자

오'리플린, 제니퍼

미국, 오레곤 97213, 포틀랜드, 엔이 47티에이치

애비뉴 1405

스리랍, 만디암

미국, 오레곤 97008, 비버튼, 에스더블유 모간 드

라이브 8455

반 슈라벤디즈크, 바트

미국, 캘리포니아 94087, 서니베일, 아일라 코트

741

바라다라잔, 세샤사이

미국, 오레곤 97035, 레이크 오스위고, 헌터 코트

17372

---

## 명세서

### 청구범위

#### 청구항 1

반도체 소자 구조물 형성 방법에 있어서, 상기 방법은,

- (a) 구리 또는 구리 합금의 층과 절연막 둘 모두의 위에 알루미늄을 포함한 제 1 층을 형성하도록 350°C 이상의 기판 온도에서, 산화물-프리(oxide-free) 구리 또는 구리 합금의 층의 노출 영역과 절연막의 노출 영역을 갖는 기판을 알루미늄을 포함한 화합물과 접촉시키는 단계;

- (b) 알루미늄을 포함한 패시베이션 층을 형성하도록 상기 제 1 층의 일부분 또는 전부를 화학적으로 변화시키는 단계; 및

- (c) 상기 패시베이션 층 위에 절연층을 증착하는 단계를 포함하는, 반도체 소자 구조물 형성 방법.

#### 청구항 2

제 1 항에 있어서,

구리 또는 구리 합금의 층의 표면으로부터 구리 산화물을 완전히 제거하도록 상기 (a) 단계 전에, 기판 표면을 세척하는, 반도체 소자 구조물 형성 방법.

#### 청구항 3

제 2 항에 있어서,

상기 세척은, N<sub>2</sub>, NH<sub>3</sub>, 및 H<sub>2</sub> 중 하나 이상을 포함하는 가스에서 직접 플라스마 처리, 원거리 플라스마 처리, UV 처리, 및 열 처리로 구성된 그룹으로부터 선택되는, 반도체 소자 구조물 형성 방법.

#### 청구항 4

제 1 항에 있어서,

상기 (a) 단계는, 플라스마의 부재 하에서 상기 기판을 유기알루미늄(organoaluminum) 화합물과 접촉시키는 단계를 포함하는, 반도체 소자 구조물 형성 방법.

#### 청구항 5

제 4 항에 있어서,

상기 (a) 단계는, 400°C 이상의 기판 온도에서 상기 기판을 유기알루미늄 화합물과 접촉시키는 단계를 포함하는, 반도체 소자 구조물 형성 방법.

#### 청구항 6

제 4 항에 있어서,

유기알루미늄 화합물이 트리메틸알루미늄(trimethylaluminum)인, 반도체 소자 구조물 형성 방법.

#### 청구항 7

제 1 항에 있어서,

상기 (b) 단계는, 알루미늄이 상기 구리의 층으로 확산되지 않고, 상기 구리 또는 구리 합금의 층 위에 존재하는 상기 제 1 층을 완전히 패시베이션하는 단계를 포함하는, 반도체 소자 구조물 형성 방법.

#### 청구항 8

제 1 항에 있어서,

상기 (b) 단계는, 알루미늄이 상기 구리의 층으로 부분적으로 확산되도록 하면서, 상기 구리 또는 구리 합금의 층 위에 존재하는 상기 제 1 층을 부분적으로 패시베이션하는 단계를 포함하는, 반도체 소자 구조물 형성 방법.

#### 청구항 9

제 1 항에 있어서,

상기 (b) 단계에서 상기 패시베이션 층을 형성하는 단계는, Al-N 결합들을 포함하는 부동성(immobile) 화합물을 형성하는 단계를 포함하는, 반도체 소자 구조물 형성 방법.

#### 청구항 10

제 9 항에 있어서,

상기 (b) 단계는, 질소-함유 제제를 이용해 상기 기판을 처리하는 단계를 포함하고, 여기서 상기 처리는 직접 플라스마 처리, 원거리 플라스마 처리, UV 처리, 및 열 처리로 구성된 그룹으로부터 선택되는, 반도체 소자 구조물 형성 방법.

#### 청구항 11

제 10 항에 있어서,

상기 (b) 단계는, 플라스마의 부재 하에서 질소-함유 제제를 이용해 상기 기판을 처리하는 단계를 포함하는, 반도체 소자 구조물 형성 방법.

#### 청구항 12

제 11 항에 있어서,

상기 절연막은 ULK 절연막인, 반도체 소자 구조물 형성 방법.

#### 청구항 13

제 1 항에 있어서,

상기 단계 (b)에서 상기 패시베이션 층을 형성하는 단계는, Al-O 결합들을 포함하는 부동성(immobile) 화합물을 형성하는 단계를 포함하는, 반도체 소자 구조물 형성 방법.

#### 청구항 14

제 13 항에 있어서,

상기 (b) 단계는, 산소-함유 제제를 이용해 상기 기판을 처리하는 단계를 포함하며, 여기서 상기 처리는 직접 플라스마 처리, 원거리 플라스마 처리, UV 처리, 및 열 처리로 구성된 그룹으로부터 선택되는, 반도체 소자 구조물 형성 방법.

#### 청구항 15

제 13 항에 있어서,

상기 (b) 단계는, 플라스마의 부재 하에서 상기 기판을 산소-함유 제제와 접촉시키는 단계를 포함하는, 반도체 소자 구조물 형성 방법.

#### 청구항 16

제 15 항에 있어서,

상기 절연막은 ULK 절연막인, 반도체 소자 구조물 형성 방법.

#### 청구항 17

제 13 항에 있어서,

상기 (b) 단계는, O<sub>2</sub>, N<sub>2</sub>O, CO<sub>2</sub>, 및 O<sub>3</sub>로 구성된 그룹으로부터 선택된 산소-함유 제제를 이용하여 상기 기판을 처리하는 단계를 포함하는, 반도체 소자 구조물 형성 방법.

### 청구항 18

제 1 항에 있어서,

상기 (a), (b), 및 (c) 단계는 화학적 기상 증착(CVD) 장치에서 수행되는, 반도체 소자 구조물 형성 방법.

### 청구항 19

제 1 항에 있어서,

상기 (c) 단계에서 증착된 상기 절연층은 에칭 저지 절연층인, 반도체 소자 구조물 형성 방법.

### 청구항 20

제 19 항에 있어서,

상기 에칭 저지 절연층은 실리콘 질화물 및 실리콘 탄화물로 구성된 그룹으로부터 선택된, 도핑되거나 도핑되지 않은 물질을 포함하는, 반도체 소자 구조물 형성 방법.

### 청구항 21

제 1 항에 있어서,

상기 (c) 단계에서 증착된 상기 절연층은, 상기 패시베이션 층 위에 바로 증착되는 층간 절연막(ILD)층인, 반도체 소자 구조물 형성 방법.

### 청구항 22

반도체 소자 구조물 형성 장치에 있어서, 상기 장치는,

- (a) 가스 또는 휘발성 금속-함유 반응물들의 주입을 위한 주입구를 갖는 공정 챔버;

- (b) 공정 챔버에서 웨이퍼 기판 위에 금속-함유 층을 증착하는 동안 상기 웨이퍼를 제 위치에 고정하기 위한 웨이퍼 지지부; 그리고

- (c) 컨트롤러를 포함하고,

상기 컨트롤러는,

(i) 노출된 구리 또는 구리 합금으로부터 산화막을 제거하도록, 노출된 구리 또는 구리 합금과 노출된 절연막을 갖는 기판을 처리하기 위한 프로그램 명령어;

(ii) 절연막과 상기 구리 또는 구리 합금 둘 모두의 위에 알루미늄을 포함하는 제 1 층을 형성하도록 350°C 이상의 기판 온도에서, 산화물-프리(oxide-free) 구리 또는 구리 합금의 노출 영역과 절연막의 노출 영역을 갖는 기판을 알루미늄-함유 반응물과 접촉시키기 위한 프로그램 명령어; 및

(iii) 알루미늄을 포함하는 패시베이션 층을 형성하도록 상기 제 1 층의 일부분 또는 전부를 화학적으로 변화시키기 위한 프로그램 명령어를 포함하는, 반도체 소자 구조물 형성 장치.

### 청구항 23

제 22 항에 있어서,

상기 컨트롤러 프로그램 명령어 (ii) 는, 플라스마의 부재 하에서 알루미늄-함유 반응물과 상기 기판을 접촉시키는 공정을 구현하는, 반도체 소자 구조물 형성 장치.

## 발명의 설명

### 기술 분야

[0001] 본 발명은 부분 제작된 집적 회로 위에 물질의 층을 형성하는 방법에 관한 것으로, 더욱 상세하게는, 다마신 인

터커넥트의 전자이동 속성을 개선하기 위하여 구리 배선 내에 보호 캡을 형성하는 방법에 관한 것이다.

## 배경기술

[0002] 다마신 공정은 집적 회로 상에 금속 배선을 형성하는 방법이다. 다마신 공정은 절연층(층간 절연막)에 형성된 트렌치와 비아 내에 상감 세공된 금속 배선을 형성하는 것과 관계된다. 다마신 공정은 종종, 그 밖의 다른 방법들보다 적은 처리 단계들을 필요로 하고 더 높은 수율(yield)을 제공하기 때문에 바람직한 방법으로 여겨진다. 다마신 공정은 플라스마 에칭에 의해 즉시 패턴화될 수 없는 구리와 같은 금속에서 특히 적합하다.

[0003] 통상적인 다마신 공정 흐름에서, 패턴화된 절연막 위에 금속이 증착되어, 절연층에 형성된 바이와 트렌치를 충전한다. 최종 금속배선(metallization) 층이 능동 소자를 지닌 층 위에 또는 더 낮게 놓인 금속배선 층 위에 통상적으로 바로 형성된다. 실리콘 탄화물 또는 실리콘 질화물과 같은 절연막 확산 장벽 물질의 얇은 층이 인접한 금속배선 층들 사이에 증착되어, 금속이 절연막의 벌크(bulk) 층으로 확산되는 것을 방지할 수 있다. 또한 일부 경우에는, 실리콘 탄화물 또는 실리콘 질화물 절연막 확산 장벽 층이 층간 절연막(inter layer dielectric, ILD)의 패터닝 동안 에칭 저지층의 역할도 한다.

[0004] 통상적인 집적 회로(IC)에서, 몇몇 금속배선 층들이 서로의 위에 증착되어 스택(stack)을 형성하며, 여기서 금속-충전된 비아와 트렌치가 IC 전도 경로(conducting path)의 역할을 한다. 하나의 금속배선 층의 전도 경로가, 일련의 다마신 인터커넥트에 의해, 밑에 놓이거나 위에 놓인 층의 전도 경로에 연결된다.

[0005] 이러한 인터커넥트들의 제작에서 몇 가지 문제점들이 제시되는데, 이러한 문제점들은 계속하여 축소되는 IC 소자 피쳐(feature)들의 치수에 있어서 점점 더 중요해지고 있다. 현재, 90nm 기술 노드에서, 그리고 좀 더 개선된 노드에서, 개선된 수명과 신뢰성을 갖는 인터커넥트를 제공할 수 있는 인터커넥트 제작 방법에 대한 요구가 강해지고 있다.

## 발명의 내용

[0006] IC 제작 동안 맞닥뜨리는 하나의 문제점은 전자이동(electromigration) 장애이다. 전자이동은 인터커넥트에 의해 경험되는 고전류 밀도가 전류를 가진 금속 원자의 이동을 초래하고, 그 결과 인터커넥트 내에 공동(void)이 형성될 때 발생한다. 궁극적으로, 공동의 형성으로 인해 소자의 장애를 초래할 수 있고 이것이 전자이동 장애로서 알려져 있다. 진행 중인 IC 소자의 소형화 동안, 인터커넥트 치수가 감소되고, 인터커넥트에 의해 더 큰 전류 밀도가 경험된다. 그 결과, 전자이동 장애의 가능성이 이러한 소자 소형화와 함께 증가하게 된다. 구리가 알루미늄보다 더 큰 전자이동 저항성을 가지지만, 구리 인터커넥트에서조차, 45nm 기술 노드에서 그리고 좀 더 개선된 노드에서 전자이동 장애가 상당한 신뢰성 문제가 되고 있다.

[0007] 금속 배선과 절연막 확산 장벽(또는 에칭 저지) 층 사이의 계면에 존재하는 보호 캡이 본원에서 제공되며, 상기 보호 캡은 인터커넥트들의 전자이동 성능을 개선할 수 있다. 이러한 보호 캡을 형성하는 방법 또한 기술된다. 유리하게, 본원에 기술된 보호 캡은, 인터커넥트 저항성을 유의하게 증가시키지 않고, 절연막 확산 장벽 층과의 계면에서 금속 배선의 상부에 존재하는 매우 얇은 층으로서 형성될 수 있다. 보호 캡핑 층(protective capping layer)은 예를 들어 고용체(solid solution), 합금, 또는 인터커넥트 금속(가령, 구리)과 도핑 원소(가령, 붕소, 알루미늄, 티타늄 등)의 화합물을 포함할 수 있다. 많은 실시예에서, 인터커넥트 금속과의 합금을 형성하거나 결정 경계(grain boundary)에 축적됨으로써 인터커넥트 금속 원자들의 이동을 감소시키는 도핑 원소를 선택하는 것이 유리하다.

[0008] 본원에 제공된 방법은 도편트-생성(dopant-generating) 물질(예를 들어, B, Al, Ti 등을 함유한 물질)의 소스 층을 노출된 금속 배선 위에 증착하고, 상기 소스 층의 상부를 패시베이션 층(가령, 질화물 또는 산화물)으로 변화시키고, 도편트-생성 소스 층의 변화되지 않은 부분을 인터커넥트 금속과 접촉 상태로 유지시키고, 뒤이어, 상기 소스 층의 변화되지 않은 부분이 인터커넥트 금속으로 확산되거나 인터커넥트 금속과 반응하도록 함으로써 보호 캡의 두께를 조절할 수 있다. 일 실시예에서, 인터커넥트 내로 삽입되는 도편트의 양은 인터커넥트와 접촉하여 존재하는 소스 층의 변화되지 않은 부분의 두께까지로 제한된다. 그 밖의 다른 실시예에서, 인터커넥트 내로 삽입되는 도편트의 양은 확산 및/또는 반응 동안의 온도를 조절함으로써 조절된다.

[0009] 도편트 또는 쉽게 확산되는 많은 양의 도편트(가령, Si 또는 Ge)가 인터커넥트 금속 위에 증착될 때 종종 인터커넥트의 저항성이 증가되는데, 유리하게, 이러한 조절 가능 방식으로 형성된 얇은 보호 캡은 인터커넥트의 저항성을 유의하게 증가시키지 않는다. 이에 더하여, 아래에 기술될 것이지만, 본원에 제공되는 방법은, 거의 또는 전혀 선택의 여지가 없이, 노출된 금속과 절연막 둘 모두의 위에 증착되는 도편트-생성 소스로부터 보호 캡

평 층을 형성하는 것에 적합하다. 이러한 방법은 또한, 도편트-함유 소스 층이 절연막 위에 유의하게 증착됨이 없이 금속 층에만 선택적으로 증착되는 경우에도 이용될 수 있다.

[0010] 본 발명의 일 형태를 따라, 반도체 소자 구조물을 형성하는 방법이 제공된다. 일 실시예에서, 상기 방법은 (a) 제 1 금속(가령, 구리 또는 구리 합금)의 노출 층과 절연막의 노출 층 갖는 기판을 봉소 또는 제 2 금속(가령, Al, Hf, Ti, Co, Ta, Mo, Ru, Sn, Sb 등)을 포함한 화합물과 접촉시켜서 봉소 또는 제 2 금속을 포함한 소스 층을 절연막과 상기 제 1 금속 둘 모두의 위에 증착시키는 단계; (b) 상기 제 1 금속의 영역 위의 소스 층의 상부 부분을 변화시켜 패시베이션 층을 형성하는 단계로서, 여기서, 변화되지 않은 소스 층의 부분은 제 1 금속의 층과 접촉 상태로 유지되는 특징의 단계와; (c) 상기 변화되지 않은 소스 층으로부터의 활성 성분(active component)이 제 1 금속으로 확산되거나 제 1 금속과 반응하도록 하여 제 1 금속의 층 내에 보호 캡을 형성하는 단계를 포함한다.

[0011] 일 실시예에서, 기판은 금속간 절연막의 층에 내장된 노출된 구리 배선을 갖는 다마신 구조이다. 소스 층의 증착에 앞서, 선택 사항으로서 상기 기판이, 구리 표면으로부터 오염물질(가령, 구리 산화물)을 제거하도록 사전에 세척될 수 있다. 예를 들어, 사전-세척은 기판을 플라스마의 환원 가스(가령, H<sub>2</sub> or NH<sub>3</sub>)에 노출시킴으로써 수행될 수 있다. 그 후, 특정 온도에서 기판을 휘발성 도편트 전구체(precursor)와 접촉시킴으로써, 도편트(활성 성분)의 소스를 함유한 소스 층이 증착될 수 있다. 통상적으로(필연적인 것은 아니지만) 소스 층의 증착은 플라스마 방전의 부재 하에서 열적으로(thermally) 수행된다. 사전-세척과 소스 층 증착은 예를 들어 동일한 공정 챔버에서 진공상태 해소(vacuum break) 없이 CVD 장치에서 수행될 수 있다.

[0012] 일 실시예에서, 플라스마 방전의 부재 하에서 약 200 내지 400°C 사이의 챔버 온도에서 기판을 B<sub>2</sub>H<sub>6</sub>(또는 그 밖의 다른 봉소-함유 전구체)를 함유한 가스 혼합물과 불활성 운반 가스(carrier gas)와 접촉시킴으로써 봉소-함유 소스 층이 증착된다. 증착 챔버 내의 압력이 약 0.5 내지 10 Torr의 범위로 유지되고, 가스 혼합물에서 B<sub>2</sub>H<sub>6</sub>의 농도가 약 0.5 내지 20 부피% 사이의 범위를 가진다. 이러한 조건 하에서, 봉소-함유 소스 층이 기판의 노출된 절연막과 금속 부분 둘 모두의 위에 증착된다. 상기 소스 층은 B-H 결합을 갖는 것으로 발견되었고, 따라서 BH<sub>x</sub> 층이라 언급될 것이다.

[0013] 많은 실시예에서, 금속 표면에서의 더 높은 전구체 분해율(decomposition rate)로 인해, 기판의 절연막 부분과 비교할 때 기판의 금속 부분 위에 더 많은 양의 도편트 소스 물질이 증착된다. 그 결과, 이러한 실시예들에서, 금속 부분 위에 증착된 소스 층의 두께가 절연막 위에 증착된 소스 층의 두께보다 더 두껍다. 그러나, 많은 봉소-함유 전구체와 금속-함유 전구체에 있어서 통상적으로 금속과 절연막 간의 완전한 증착 선택성은 달성되기 어렵다. 유리하게, 본원에 개시된 증착 방법이 소스 층의 증착에 있어서 절대적인 금속/절연막 선택성을 요구하지는 않는다.

[0014] 일부 실시예에서, 전구체 분해와 기판 위에 금속-함유 층의 증착을 야기하기에 적합한 온도와 압력 하에서 금속 할로겐화물, 금속 수소화물, 금속 카르보닐(metal carbonyl), 또는 휘발성 유기금속 화합물과 같은 휘발성 금속-함유 전구체와 기판을 접촉시킴으로써 금속-함유 소스 층이 증착된다. 많은 경우에서, BH<sub>x</sub> 층의 증착에 대해 위에서 나열된 것과 유사한 온도와 압력 범위가 사용된다. 해당업계 종사자라면 서로 다른 유형의 금속 전구체에 대하여 어떻게 증착 조건을 최적화할 수 있는지 이해할 것이다.

[0015] 다수의 금속이 보호 캡 형성을 위한 도편트로서 적합하다. 상기 금속에는, 고용체, 합금, 또는 인터커넥트 금속과의 금속간 상(intermetallic phase)을 형성하는 금속들과, 인터커넥트의 결정 경계에서 확산되거나 축적될 수 있는 금속들이 포함된다. 예를 들어 Al, Hf, Ti, Co, Ta, Mo, Ru, Sn, 및 Sb가 보호 캡의 성분으로서 사용될 수 있다. 이들 금속 서로간 또는 이들 금속과 그 밖의 다른 금속과의 합금 및 고용체가 이용될 수도 있다. 알루미늄-함유 소스 층을 위한 휘발성 전구체에는 트리메틸알루미늄, 디메틸알루미늄 수소화물, 트리에틸알루미늄, 트리이소부틸알루미늄, 및 트리스(디에틸아미노)알루미늄이 포함된다. 이에 한정되는 것은 아니다. 그 밖의 다른 금속들의 증착에 적합한 전구체에는 비스(시클로펜타디에닐)코발트, 코발트(Ⅱ) 아세틸아세톤염, 테트라카이스(디메틸아미노)하프늄, 테트라카이스(디에틸아미노)하프늄, 테트라카이스(디메틸아미노)몰리브덴, 테트라카이스(디메틸아미노)티타늄(TDMAT), 테트라카이스(디에틸아미노)티타늄(TDEAT), 테트라카이스(에틸메틸아미노)티타늄, 비스(디에틸아미노)비스(디이소프로필아미노)티타늄, 펜타카이스(디메틸아미노)티타늄, 터트(부틸이미도트리스)(디에틸아미노)탄탈(tert(butylimidotris)(diethylamido)tantalum)(TBTDET), 펜타카이스(디에틸아미노)탄탈(pentakis(diethylamido)tantalum), 비스(에틸시클로펜타디에닐)루테늄(bis(ethylcyclopentadienyl)ruthenium), 트리스(디메틸아미노)안티몬, 및 테트라메틸틴(tetramethyltin)이 포함된다.

함되나 이에 한정되는 것은 아니다.

[0016] 전술된 바와 같이, 봉소 또는 금속을 함유한 소스 층이 증착된 후, 그 상부 부분이 변화되어 패시베이션 층(가령, 질화물 또는 산화물을 함유한 층)을 형성하고, 그 바닥 부분은 변화되지 않고 인터커넥트 금속과 접촉 상태로 유지된다. 소스 층이 절연막 위에서보다 금속 위에 더 두꺼운 두께로 증착되는 많은 실시예에서, 이러한 변화 공정으로 인해 절연막 위에 존재하는 소스 층의 부분이 저 전도성을 가진 물질(가령,  $BN_x$ ,  $Al_xO_y$  등)을 함유한 패시베이션 층으로 완전히 변화된다. 이러한 변화는 인접한 인터커넥트들 간의 단락을 방지하기 위해 수행된다. 더욱이, 금속 배선 위에 존재하는 소스 층의 부분적 변화가 층 내에 존재하는 도편트의 양을 조절하는 기능을 하고, 보호 캡의 두께를 조절함으로써 인터커넥트 저항성을 조절할 수 있는 통로를 제공한다.

[0017] 패시베이션 층을 형성하기 위하여 다수의 공정들이 이용될 수 있다. 일 실시예에서, 플라스마 방전에서 질소-함유 반응물에 기판을 노출시킴으로써 소스 층이 변화된다. 예를 들어,  $NH_3$ ,  $N_2H_4$ , 아민,  $N_2$ , 및 이들의 혼합물이 사용될 수 있다. 구체적 예시에서, 기판을 플라스마에서  $N_2$  및  $NH_3$ 의 혼합물과 접촉시킴으로써  $BH_x$  소스 층이 변화되어  $BN_x$ 를 함유한 패시베이션 층을 형성할 수 있다. 그 밖의 다른 실시예에서, 플라스마 방전에서 산소-함유화합물(가령,  $O_2$ ,  $N_2O$ , 또는  $CO_2$ )에 기판을 노출시킴으로써 소스 층(가령, 금속-함유 소스 층)이 변화되어 산화물(가령, 알루미늄 산화물, 티타늄 산화물 등)을 함유한 패시베이션 층을 형성할 수 있다. 그 밖의 다른 실시예에서, 플라스마에서 반응물을 함유한 탄소를 이용해 소스 층을 변화시켜 탄화물 또는 탄화수소(가령,  $BC_x$ ,  $C_xH_y$  등)을 함유한 패시베이션 층을 형성할 수 있다.

[0018] 변화되는 층의 두께는 원하는 대로 맞춤화될 수 있다. 변화되는 층의 두께를 조절함으로써, 도편트 소스를 함유한, 변화되지 않고 남아 있는 층의 두께가 조절되고, 이로써 인터커넥트 내의 보호 캡의 두께가 조절되는 결과를 가져온다. 예를 들어, 패시베이션 층을 형성하기 위하여 금속 배선 위에 존재하는 소스 층 두께의 약 20 내지 60% 사이가 변화될 수 있고, 변화되지 않은 도편트-함유 부분은 금속 배선과 접촉 상태로 남긴다. 일 예시에서, 금속 배선 위에 존재하는 소스 층이 약 50 내지 500Å 사이의 두께를 가진다. 소스 층 두께의 약 20 내지 60% 두께가 패시베이션 층으로 변화된 후에, 약 20 내지 400Å 사이의 두께가 금속 배선과 접촉 상태로 남아 있다.

[0019] 그 다음, 변화된 층이 형성된 후, 변화되지 않은 소스 층으로부터의 활성 성분이 인터커넥트 금속으로 확산되거나 인터커넥트 금속과 반응할 수 있고, 인터커넥트 금속의 층 내에 보호 캡을 형성할 수 있다. 일부 실시예에서, 보호 캡을 형성하기 전에, 소스 층 내에 활성 성분이 첫 번째로 생성된다. 활성 성분의 성질에 따라, 다양한 조건들을 이용하여 활성 성분을 생성할 수 있고 상기 활성 성분이 인터커넥트 금속으로 확산되도록 촉진할 수 있다. 일부 실시예에서, 미리 정해진 시간 동안 기판을 고온에 노출시킴으로써 금속 인터커넥트 내에 보호 캡이 형성되는 것을 촉진할 수 있다. 그 밖의 다른 실시예에서, 보호 캡의 형성은 도편트 확산에 충분한 시간이 허용된 이후 실온에서 발생한다.

[0020] 일부 실시예에서, 패시베이션 층이 형성된 후에, 상기 패시베이션 층 위에 에칭 저지층 또는 절연막 확산 장벽 층(예를 들어, 도핑되었거나 도핑되지 않은 실리콘 탄화물 또는 실리콘 질화물을 포함한 층)이 증착된다. 그 밖의 다른 실시예에서, 패시베이션 층 자체가 에칭 저지층 또는 절연막 확산 장벽 층의 역할을 할 수 있고, 별도의 에칭 저지층이 요구되지 않는다. 후자의 실시예에서, 금속간 절연막이 패시베이션 층 위에 바로 증착된다.

[0021] 일부 실시예에서, 절연막 확산 장벽 층 또는 에칭 저지층이 증착된 후에, 도편트가 인터커넥트 금속으로 확산되거나 인터커넥트 금속과 반응하도록 함으로써 인터커넥트 금속의 도핑이 수행된다. 예를 들어, 에칭 저지층(가령, 실리콘 탄화물 층)이 증착된 후에 기판이 최소한 약 100°C까지 가열되어 보호 캡의 형성을 촉진할 수 있다.

[0022] 유리하게, 일부 실시예에서, 전체 캡-형성 공정과 확산 장벽(또는 에칭 저지) 증착 공정이 하나의 모듈에서 진공 상태 해소 없이 연속하여 수행된다. 하나의 챔버 내에 다수의 스테이션을 갖거나 다수의 챔버를 갖는 PECVD 모듈 장치가 이러한 증착에 적합한 장치이다. 주목할만하게, 금속-함유 층과 절연층 둘 모두가 진공 상태 해소 없이 하나의 PECVD 장치에서 연속하여 증착될 수 있다. 예를 들어, 일 실시예에서, 이러한 공정은 금속-함유 소스 층 증착 단계, 소스 층의 상부 부분을 패시베이션 층으로 변화시키는 단계, 활성 성분이 금속 인터커넥트 내에서 보호 캡을 형성하도록 하는 단계, 그리고 절연막 확산 장벽 층 또는 에칭 저지층 형성 단계와 관계되며, 여기서 모든 공정들이 진공 상태 해소 없이 하나의 장치에서 수행된다.

[0023] 이러한 방법을 이용하여 형성된 소자는 개선된 전자이동 속성을 가질 수 있고, 또한 금속/절연막 확산 계면에 더 큰 부착력을 나타낼 수 있다.

- [0024] 본 발명의 또 다른 양상을 따라, 반도체 소자가 제공된다. 반도체 소자는 절연 물질의 영역과, 상기 절연 물질에 내장된 구리 또는 구리 합금의 영역을 포함한다. 이러한 반도체 소자는 절연막의 층 위에 그리고 구리 또는 구리 합금의 영역 위에 증착되는 BN<sub>x</sub>를 포함한 층을 추가로 포함한다. 반도체 소자는 구리 또는 구리 합금 영역 내에 봉소-함유 캡을 추가로 포함한다.

- [0025] 본 발명의 또 다른 양상을 따라, 부분 제작된 반도체 소자의 금속 부분 위에 또는 금속 부분 내에 보호 캡을 형성하는 장치가 제공된다. 상기 장치는 (a) 반응물의 주입을 위한 주입구를 갖는 공정 챔버; (b) 보호 캡의 형성 동안 웨이퍼를 제 위치에 고정하기 위한 웨이퍼 지지부; 그리고 (c) 보호 캡 증착을 위한 프로그램 명령어를 포함하고 있는 컨트롤러를 포함한다. 상기 명령어는 (i) 웨이퍼 기판 상의 노출된 금속 부분과 노출된 절연막 부분 위에 봉소 또는 제 2 금속을 포함한 소스 층을 증착시키기 위한 명령어; (ii) 패시베이션 층을 형성하도록 활성 성분 층의 상부 부분을 변화시키기 위한 명령어; 및 (iii) 보호 캡을 형성하도록 소스 층 내의 활성 성분이 기판 위의 금속으로 확산되거나 금속과 반응하기 위한 명령어를 포함한다. 일부 실시예에서, 상기 장치는 PECVD 장치이다. 이러한 공정들은 멀티-스테이션 장치의 하나의 스테이션에서 연속하여 수행될 수 있다. 그 밖의 다른 실시예에서, 일부 공정들이 장치의 제 1 스테이션에서 수행될 수 있고 그 밖의 다른 공정들은 이와는 다른 스테이션에서 수행될 수 있다. 하나의 스테이션은 제 1 온도에서 수행되는 공정들을 위해 구성될 수 있고 또 다른 스테이션은 이와는 다른 온도에서 수행되는 공정들을 위해 구성될 수 있다. 예를 들어, 소스 층의 증착이 제 1 온도에서 멀티-스테이션의 하나의 스테이션에서 수행될 수 있고, 소스 층의 뒤이은 변화가 다른 스테이션에서 다른 온도로 수행될 수 있다. 진공 상태 해소 없이 스테이션들 사이로 기판이 운반될 수 있다. 그 밖의 다른 실시예에서, 기판을 대기 조건(ambient condition)에 노출시키지 않고 챔버들 사이로 기판이 운반될 수 있는 멀티-챔버 장치에서 공정이 유사하게 구현될 수 있다.

- [0026] 본 발명의 또 다른 양상에서, 산화물-프리(oxide-free) 구리 표면 위에 알루미늄-함유 보호 캡을 형성하는 방법이 제공된다. 상기 방법은 (a) 절연막과 구리 또는 구리 합금의 층 둘 모두의 위에 알루미늄을 포함한 제 1 층을 형성하도록 산화물-프리 구리 또는 구리 합금의 노출 층과 절연막의 노출 층을 갖는 기판을 알루미늄을 포함한 화합물과 접촉시키는 단계; (b) 알루미늄을 포함한 패시베이션 층을 형성하도록 상기 제 1 층의 일부분 또는 전부를 화학적으로 변화시키는 단계; 및 (c) 상기 패시베이션 층 위에 절연층을 증착하는 단계에 의해 특징지어 질 수 있다. 일부 실시예에서, (a), (b), 및 (c) 단계들 각각이 화학적 기상 증착(CVD) 장치에서 수행된다. 더욱이, 특정 실시예에서, (c)에서 증착된 절연층은 에칭 저지 절연층이다. 이러한 에칭 저지 절연층은 예를 들어 실리콘 질화물 또는 실리콘 탄화물과 같이 도핑되었거나 도핑되지 않은 물질일 수 있다. 또 다른 실시예에서, (c)에서 증착된 절연층은 패시베이션 층 위에 바로 증착되는 중간 절연막(ILD)층이다.

- [0027] 특정 실시예에서, 상기 방법은 (a) 단계 전에 추가 단계를 포함한다. 구체적으로, 구리 또는 구리 합금의 표면으로부터 구리 산화물을 완전히 제거하기 위하여 기판 표면이 세척된다. 세척 기법들의 예시에는 N<sub>2</sub>, NH<sub>3</sub> 및 H<sub>2</sub> 중 하나 이상을 포함한 가스에서 (1) 직접 플라스마 처리, (2) 원거리 플라스마 처리, (3) UV 처리, 그리고 (4) 열 처리가 포함된다.

- [0028] 전술된 실시예에서, (a) 단계는 플라스마의 부재 하에서 약 350°C 이상(가령, 약 400°C 이상)의 기판 온도에서 기판을 유기알루미늄(organoaluminum) 화합물과 접촉시키는 단계를 수반할 수 있다. 예로서, 유기알루미늄 화합물은 트리메틸알루미늄이다.

- [0029] 특정 실시예에서, (b) 단계는 알루미늄이 구리 층으로 실질적으로 확산되도록 하지 않고 구리 또는 구리 합금 위에 존재하는 제 1 층을 실질적으로 완전히 패시베이션하는 단계를 수반한다. 대안적으로, (b) 단계는 알루미늄이 구리 층으로 부분적으로 확산되도록 하면서 구리 또는 구리 합금 위에 존재하는 제 1 층을 부분적으로 패시베이션하는 단계를 수반한다.

- [0030] 특정 실시예에서, (b)에서 층을 패시베이션하는 단계는 Al-N 결합을 포함하는 실질적으로 부동성(immobile)인 화합물을 형성하는 단계를 포함한다. 구체적 실시예에서, 패시베이션 공정은 기판을 질소-함유 제제로 처리하는 단계를 수반하고, 상기 처리는 예를 들어 직접 플라스마 처리, 원거리 플라스마 처리, UV 처리, 또는 열 처리일 수 있다. 좀 더 구체적인 실시예에서, 상기 처리는 플라스마의 부재 하에 질소-함유 제제에 기판을 노출시키는 단계를 수반한다. 후자의 처리는, 예를 들어 절연막이 ULK 절연막인 경우 적절할 수 있다.

- [0031] 그 밖의 다른 실시예에서, (b)에서 층을 패시베이션하는 단계는 Al-O 결합을 포함하는 실질적으로 부동성인 화합물을 형성하는 단계를 포함한다. 이러한 공정은 기판을 산소-함유 제제로 처리하는 단계를 수반할 수 있고, 상기 처리는 예를 들어 직접 플라스마 처리, 원거리 플라스마 처리, UV 처리, 또는 열 처리 중 하나일 수 있다.

구체적인 실시예에서, 상기 처리는 플라스마의 부재 하에서 기판을 산소-함유 제제와 접촉시키는 단계를 수반한다. 이러한 처리는, 예를 들어, 절연막이 ULK 절연막일 때 적합할 수 있다 산소-함유 제제의 예에는 O<sub>2</sub>, N<sub>2</sub>O, CO<sub>2</sub>, 및 O<sub>3</sub>가 포함된다.

[0032] 본 발명의 또 다른 양상은 반도체 소자 구조물을 형성하는 장치에 관한 것으로, 상기 장치는 (a) 가스 형태의 금속-함유 반응물 또는 휘발성 금속-함유 반응물의 주입을 위한 주입구를 갖는 공정 챔버; (b) 공정 챔버에서 웨이퍼 기판 위에 금속-함유 층을 증착하는 동안 웨이퍼를 제 위치에 고정하기 위한 웨이퍼 지지부; 그리고 (c) 프로그램 명령어를 포함하는 컨트롤러를 포함한다. 상기 프로그램 명령어들은 (i) 산화물이 없는 구리 또는 구리 합금의 노출 층과 절연막의 노출 층을 갖는 기판을 알루미늄-함유 반응물과 접촉시켜 제 1 층을 증착시키기 위한 명령어; 및 (ii) 알루미늄을 포함한 패시베이션 층을 형성하도록 상기 제 1 층의 부분 또는 전부를 화학적으로 변화시키기 위한 명령어를 포함할 수도 있다.

[0033] 위와 같은 본 발명의 특징 및 그 밖의 다른 특징과 이점들이 첨부 도면을 참조하여 좀 더 자세히 기술될 것이다.

### 도면의 간단한 설명

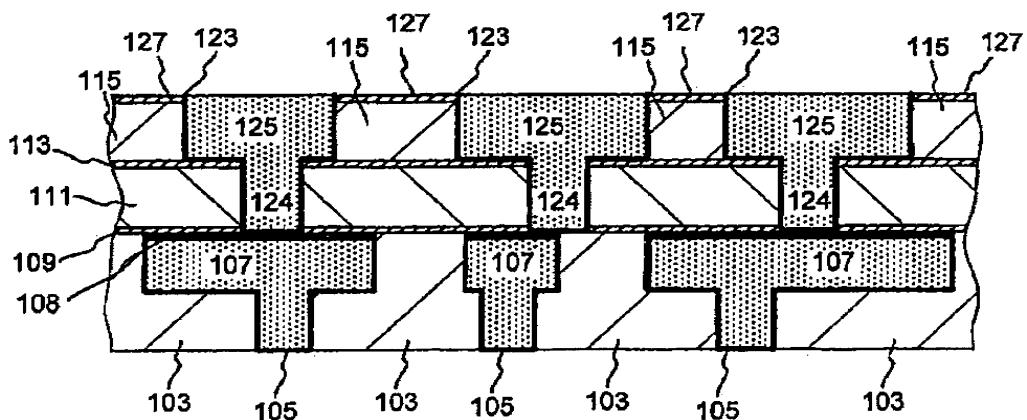

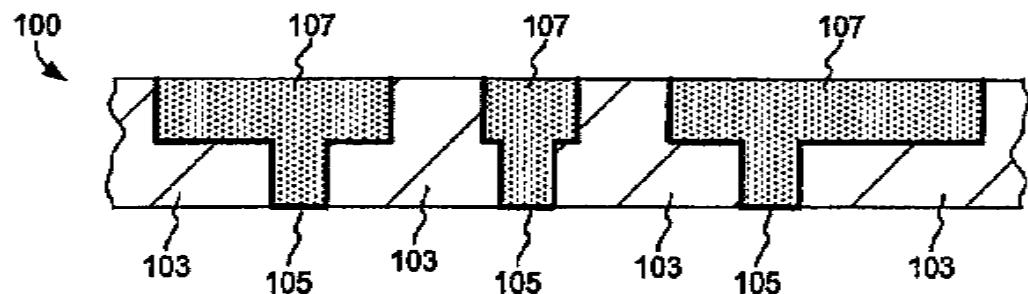

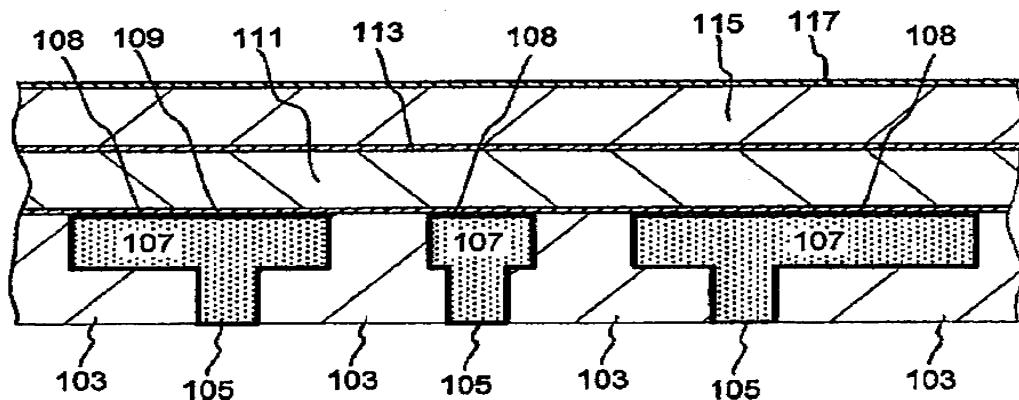

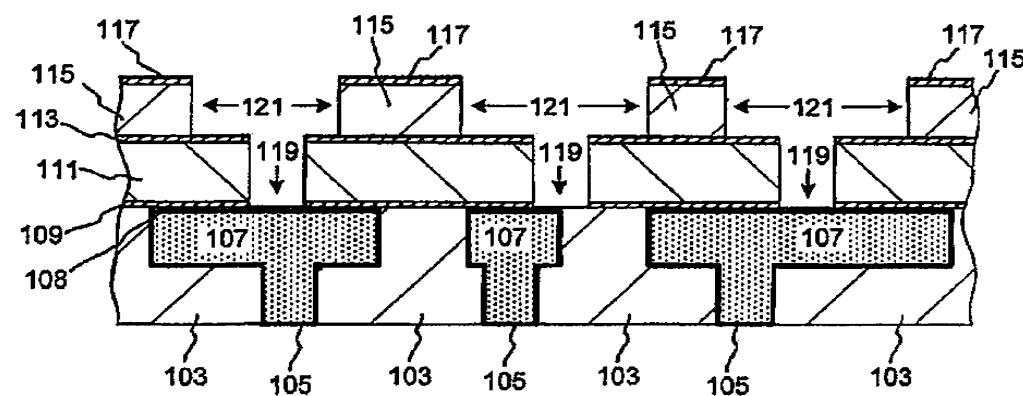

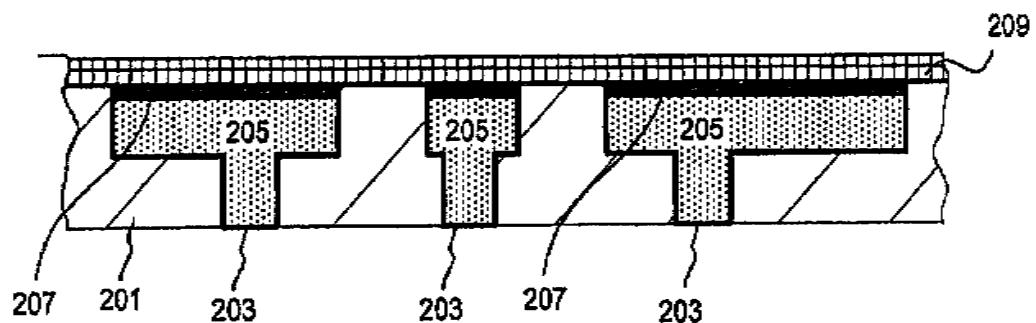

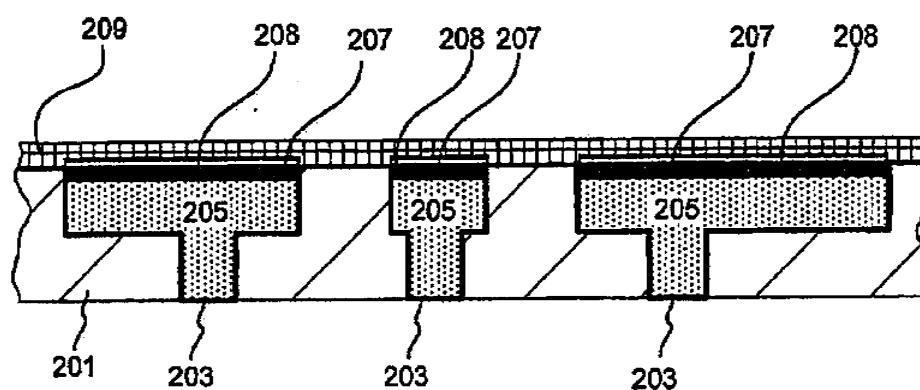

[0034] 도 1a 내지 도 1e는 구리 듀얼 다마신 제작 공정 동안 형성되는 소자 구조물의 횡단면도이다.

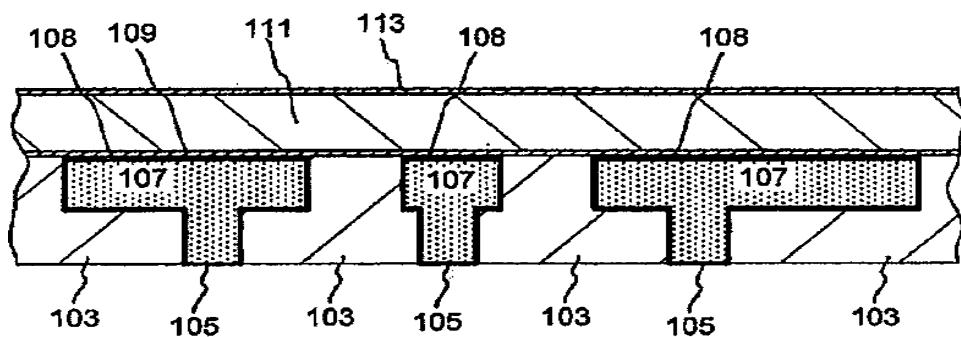

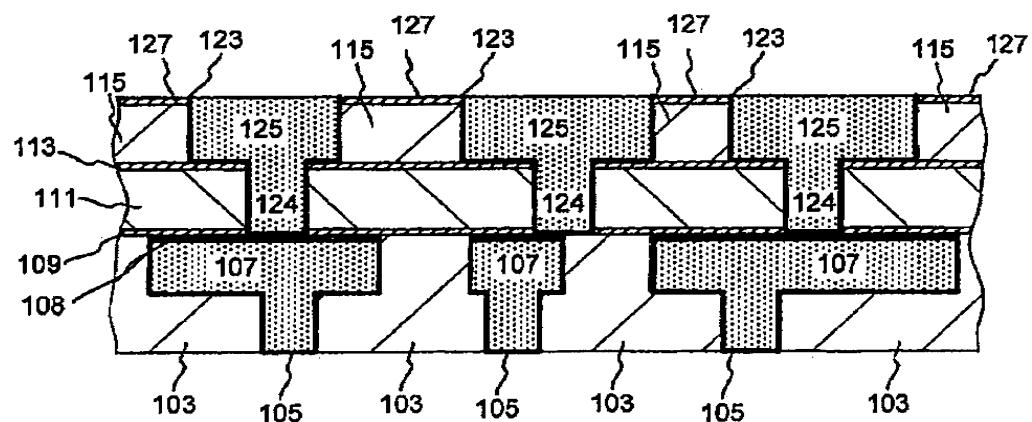

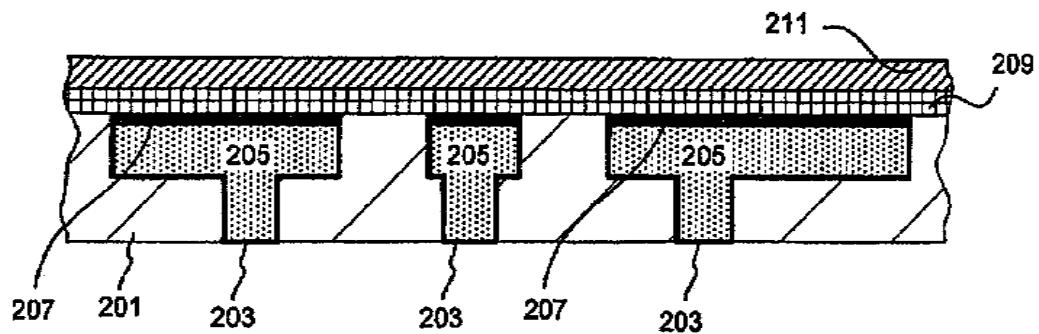

도 2a 내지 도 2c는 보호 캡을 도시하는 부분 제작된 소자 구조물의 횡단면도이다.

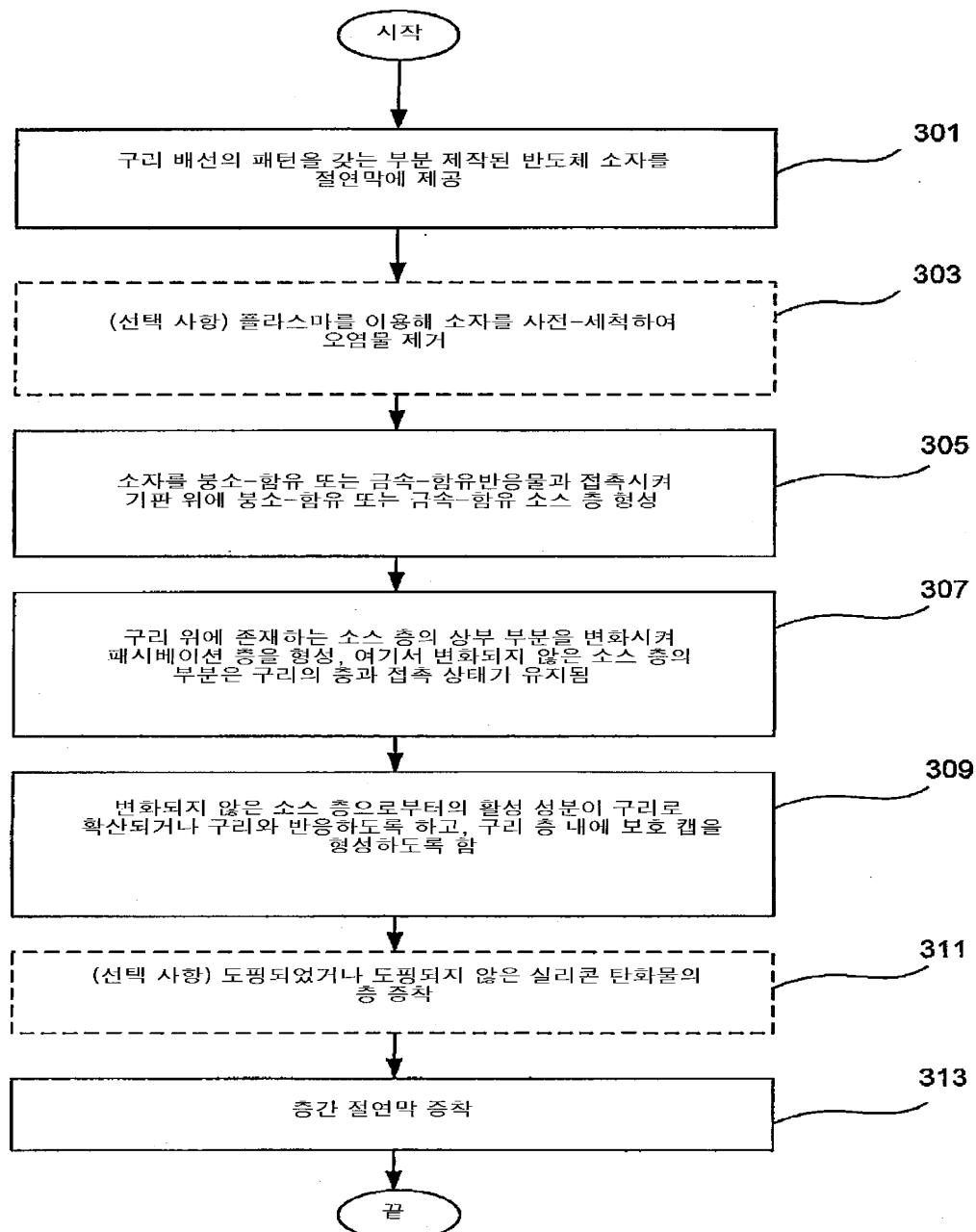

도 3a는 일부 실시예에 따른 캡-형성 공정의 예시적 공정 흐름도를 나타낸다.

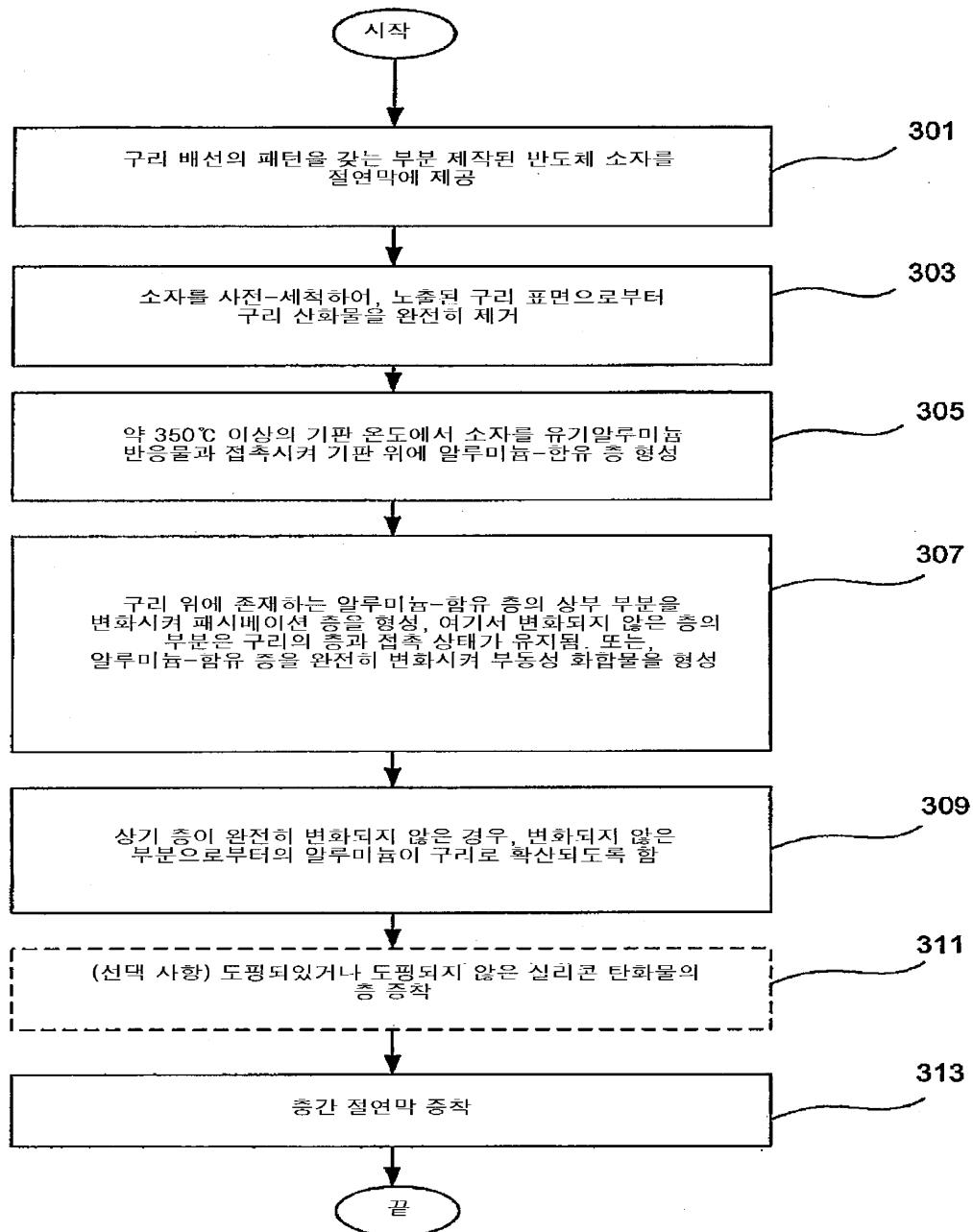

도 3b는 일부 실시예에 따른 캡-형성 공정의 또 다른 예시적 공정 흐름도를 나타낸다.

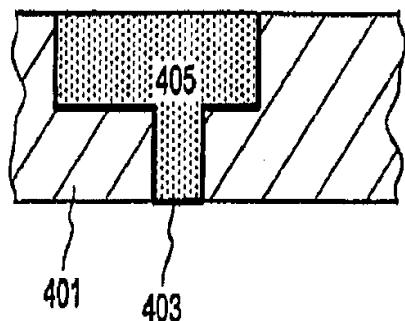

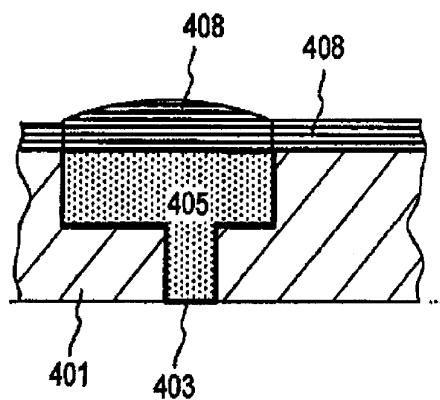

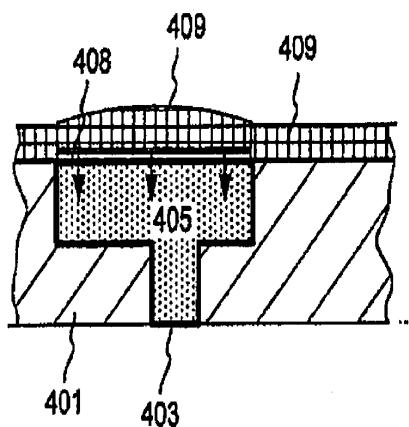

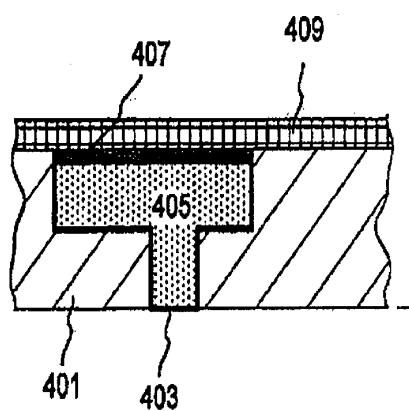

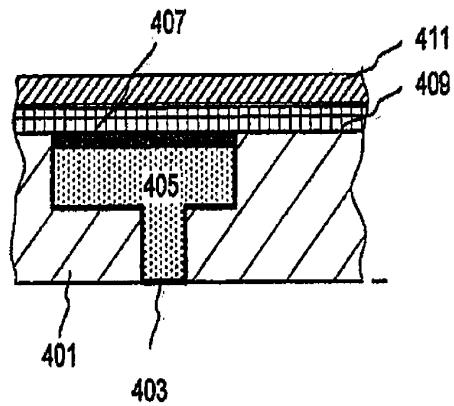

도 4a 내지 도 4e는 일부 실시예에 따라, 캡핑 층의 형성 동안 생성되는 소자 구조물의 횡단면도이다.

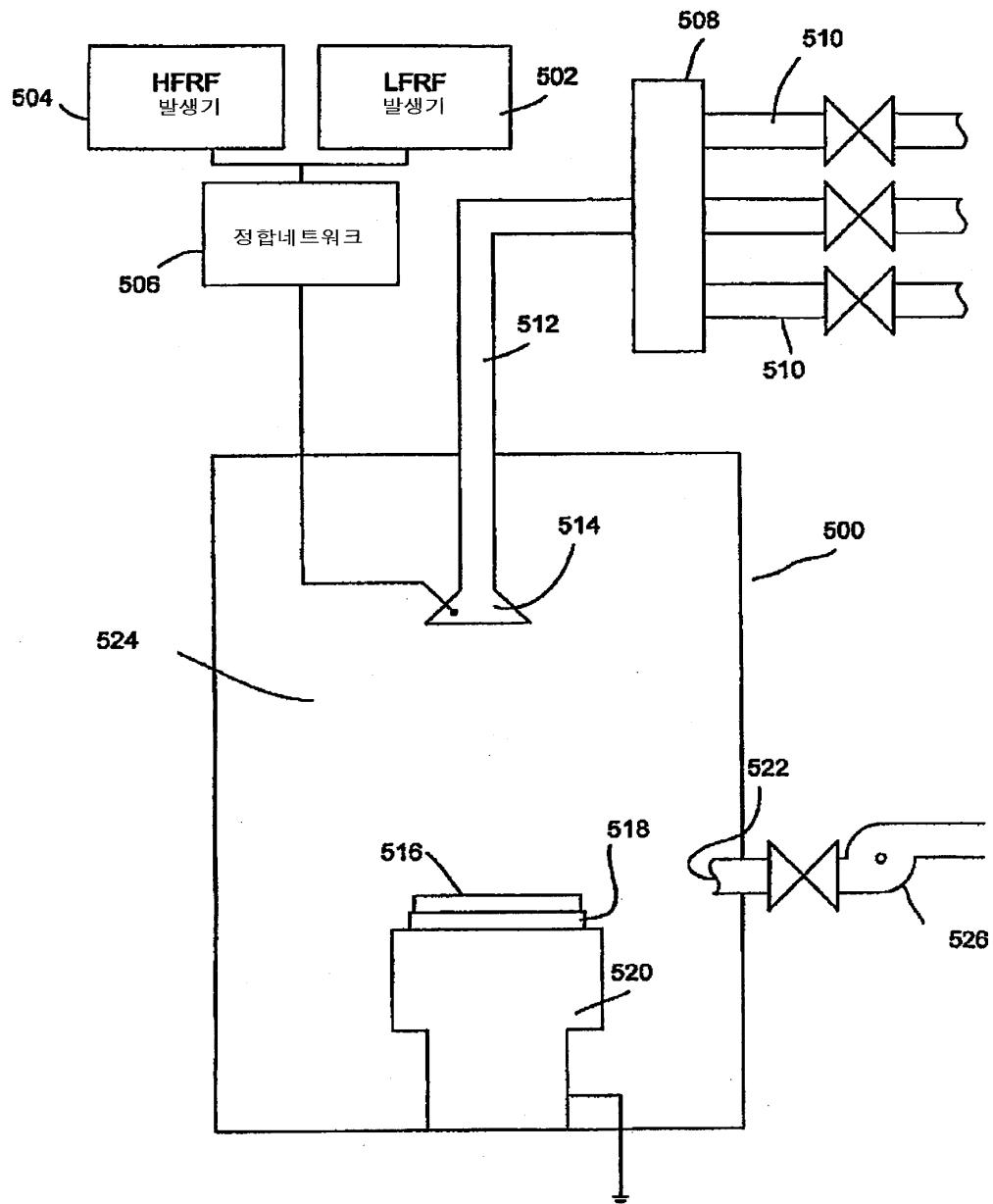

도 5는 본 발명의 일부 실시예를 따라 캡핑 층 형성에 이용될 수 있는 저주파(LF) 및 고주파(HF) 무선 주파수 플라스마 소스를 이용할 수 있는 PECVD 장치의 도식적 표현이다.

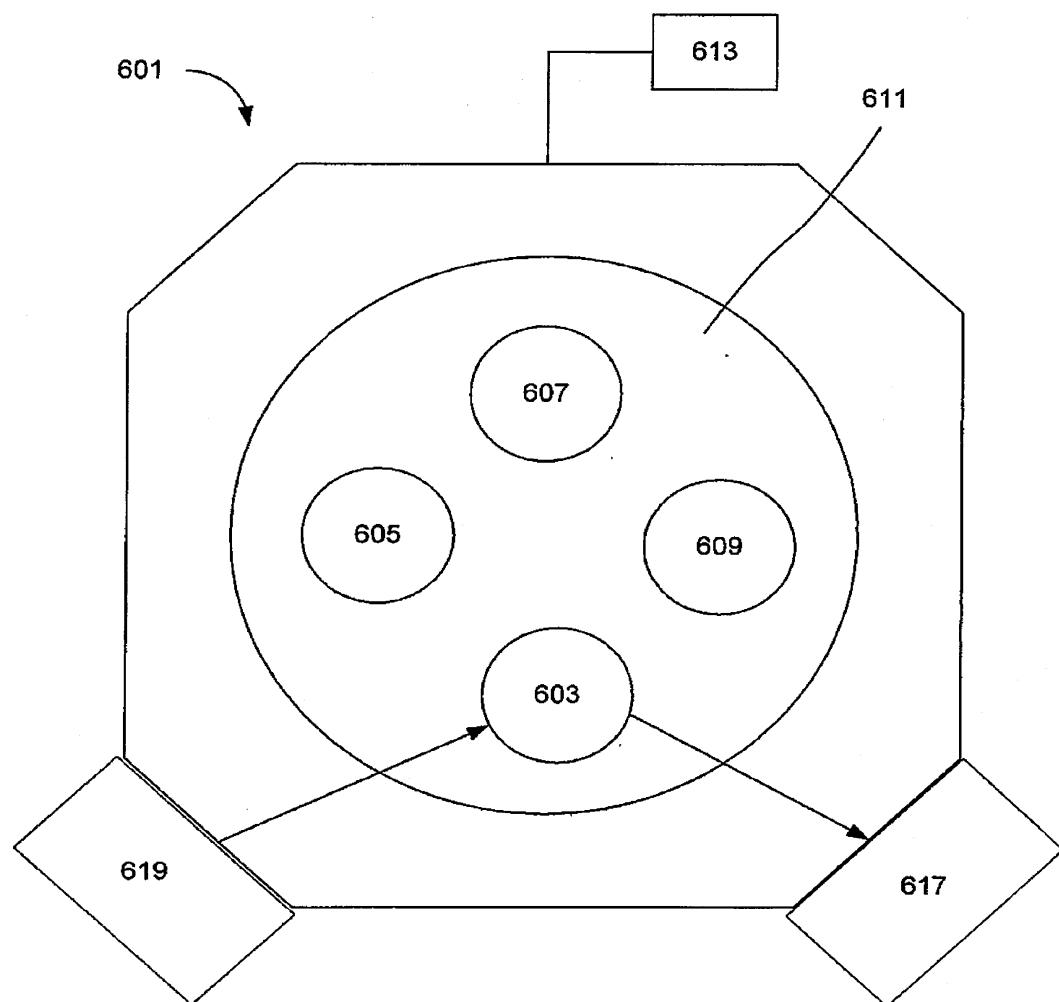

도 6은 본 발명의 일부 실시예를 따라 캡핑 층을 형성하기에 적합한 멀티-스테이션 장치의 일 예시의 도식적 표현이다.

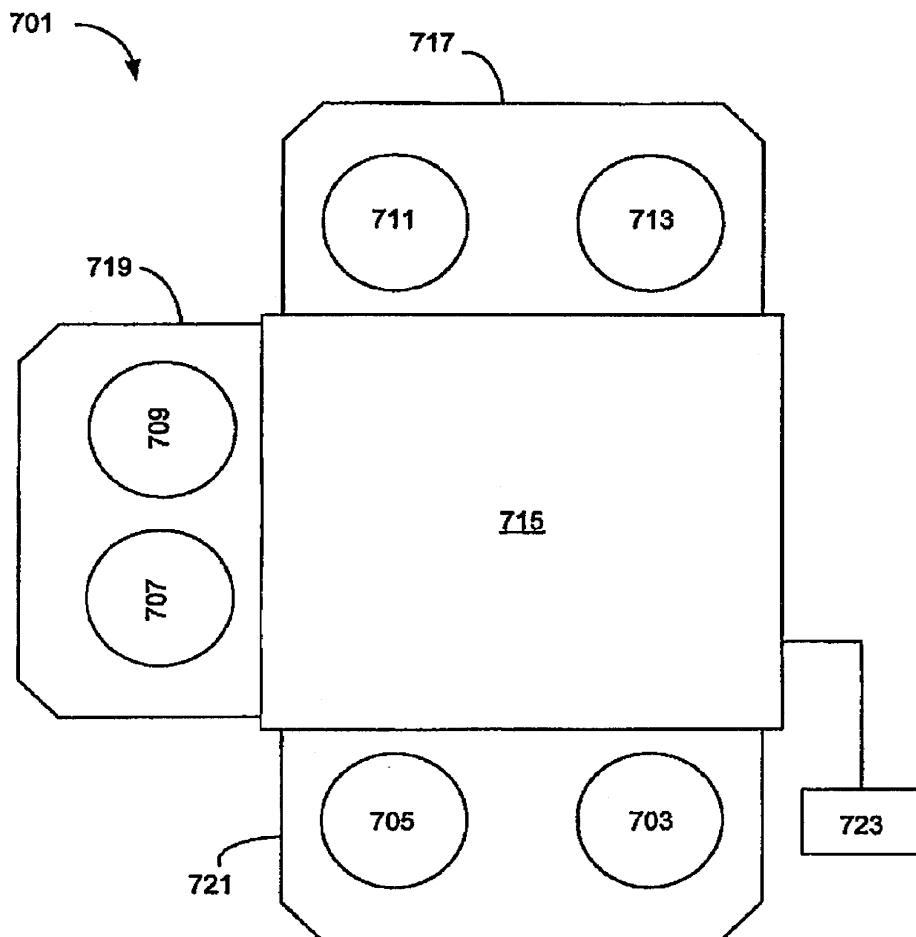

도 7은 본 발명의 일부 실시예에 따라 캡핑 층을 형성하기에 적합한 멀티-스테이션의 또 다른 예시의 도식적 표현이다.

### 발명을 실시하기 위한 구체적인 내용

#### 개요

[0035] 소자의 치수가 계속하여 감소하고 있고 인터커넥트에 의해 경험되는 전류 밀도가 증가하고 있기 때문에 IC 제작에 있어서 전자이동은 유의한 신뢰성 문제가 되고 있다. 전자이동은 전류를 가진 금속 원자의 이동과 인터커넥트 내의 공동(void)의 형성에서 그 자체가 증거로서 드러난다. 공동의 형성은 결과적으로 소자 장애를 초래할 수 있다. 금속 원자의 이동은 금속/확산 장벽 계면에서 그리고 결정 경계(grain boundary)를 따라 특히 두드러진다. 현재, 90nm 및 45nm 기술 노드에서, 전자이동 성능을 개선하기 위한 방법이 요구된다. 인터커넥트 내로 도편트 원소를 주입함으로써 전자이동 성능이 개선될 수 있지만, 이러한 도편트는 인터커넥트 금속(가령, Cu)보다 통상적으로 높은 저항성을 갖고, 인터커넥트 저항성을 유의하게 증가시킬 수 있다. 따라서, 조절되지 않는 인터커넥트 금속의 도핑은 허용될 수 없이 높은 저항성을 갖는 인터커넥트를 초래할 수 있다.

[0036] 조절 가능한 도편트 도입을 위한 방법이 본원에 제공된다. 상기 방법은 조절된 양의 도편트를 인터커넥트에 주입함으로써 금속 인터커넥트 내에 보호 캡을 형성하는 단계와 관련된다. 그 결과, 통상적으로, 금속과 절연막/확산 장벽(또는 애칭 저지) 층 사이의 계면에서 금속 배선의 상부 부분 내에 매우 얇은 보호 캡이 형성될 수 있다. 이러한 보호 캡은 고용체(solid solution), 합금, 또는 도편트와 인터커넥트 금속의 화합물을 포함하는 것이 바람직하다(단, 필연적인 것은 아니다). 예를 들어, 구리가 B, Al, Hf, Ti, Co, Ta, Mo, Ru, Sn, 또는 Sb로 도핑될 수 있다. 이러한 도편트는 또한, 서로가 함께 또는 그 밖의 다른 원소와 함께 이용될 수 있다. 일반적으로, 다양한 도편트가 이용될 수 있다. 고용체, 합금, 및 인터커넥트 금속과의 화합물을 형성할 수 있는 도편트와, 금속/확산 장벽 계면에 그리고 인터커넥트 내의 결정 경계에 축적될 수 있는 도편트가 특히 선호된다.

[0037] 본원에 기술된 보호 캡과 이러한 보호 캡의 형성 방법이 인터커넥트의 전자이동 성능 개선에 유리하지만, 기술

된 소자와 공정의 이용이 이러한 특정 응용예에만 한정되는 것은 아니다. 예를 들어, 보호 캡은 금속 배선과 절연막 확산 장벽층 또는 예칭 저지층 사이의 부착력을 개선시키는 역할을 할 수 있고, IC 소자 제작 동안 인터커넥트 금속이 산화되는 것을 방지하는 역할도 할 수 있다.

[0039] 인터커넥트에서의 보호 캡 형성이 구리 듀얼 다마신 공정의 맵락에서 예시될 것이다. 본원에 개시된 방법이 단일 다마신 공정을 포함한 그 밖의 다른 처리 방법에서도 이용될 수 있고 구리 이외의 다양한 인터커넥트 금속에도 적용될 수 있음이 이해된다. 예를 들어, 본원 발명은 알루미늄, 금, 및 은-함유 인터커넥트에도 적용될 수 있다.

[0040] 도 1a 내지 도 1d는 듀얼 다마신 제작 공정의 다양한 스테이지에서 반도체 기판 위에 형성되는 소자 구조물의 횡단면도를 도시한 것이다. 듀얼 다마신 공정에 의해 형성되는 완성 구조물의 횡단면도가 도 1e에 나타난다. 이번 응용예에서 사용된 "반도체 기판"은 IC 소자의 반도체 부분에 한정되지 않고 반도체-함유 기판으로서 광범위하게 정의된다. 도 1a를 참조하면, 듀얼 다마신 제작에서 이용되는 부분 제작된 IC 구조물(100)의 예시가 도시된다. 도 1a 내지 도 1d에 도시된 것과 같은 구조물(100)은 반도체 기판의 일부분이고, 일부 실시예에서는, 트랜지스터와 같은 능동 소자를 함유한 층 위에 바로 존재할 수 있다. 그 밖의 다른 실시예에서, 상기 구조물(100)은 전도성 물질(가령, 메모리 커패시터를 함유한 층)을 포함하는 금속배선(metallization) 층 또는 그 밖의 다른 층들 위에 바로 존재할 수 있다.

[0041] 도 1a에 도시된 층(103)은 실리콘 이산화물, 좀 더 일반적으로는 로우-k(low-k) 절연 물질일 수 있는 금속간 절연막의 층이다. 금속간 절연막 스택의 유전 상수를 최소화하기 위하여, 약 3.5보다 작은, 바람직하게는 약 3.0보다 작은, 그리고 종종 약 2.8보다 작은 k 값을 갖는 물질이 층간 절연막으로서 이용된다. 이러한 물질에는 해당업계 종사자에게 알려져 있는 불소 또는 탄소가 도핑된 실리콘 이산화물, 유기물이 함유된 로우-k 물질, 및 도핑된 다공성(porous) 실리콘 이산화물이 포함된다(이에 한정되는 것은 아님). 이러한 물질은 예를 들어 PECVD에 의해 또는 스핀-온(spin-on) 방식에 의해 증착될 수 있다. 층(103)에 배선 경로(트렌치 및 비아)가 증착되고, 이러한 배선 경로에, 부분적으로 전도성인 금속 확산 장벽(105)이 증착되고 뒤이어 구리 전도성 루트(107)가 상감된다. 구리 또는 그 밖의 다른 이동성(mobile) 전도성 물질이 반도체 기판, 밑에 놓인 실리콘 소자, 및 절연층의 전도성 경로를 금속 배선에 제공하여, 상기 금속 배선을 금속 이온(가령, Cu<sup>2+</sup>)으로부터 보호해야 하며, 상기 금속 이온은 전도성 경로가 없다면 실리콘 또는 층간 절연막으로 확산되거나 표류될 수 있고 이로써 실리콘이나 층간 절연막의 속성을 저하시키는 결과를 초래할 수 있다. IC 소자의 절연층을 보호하기 위하여 몇몇 유형의 금속 확산 장벽이 이용된다. 이를 유형은 부분적으로 전도성인 금속-함유 층(가령, 105)과 절연막 장벽 층으로 나누어질 수 있고, 이러한 금속-함유 층과 절연막 장벽 층은 도 1b와 관련해 좀 더 자세히 기술될 것이다. 부분적으로 전도성인 확산 장벽(105)에 적합한 물질에는 탄탈, 탄탈 질화물, 티타늄, 티타늄 질화물 등의 물질이 포함된다. 이를 물질은 비아와 트렌치를 갖는 절연층 위에 PVD 또는 ALD 법에 의해 통상적으로 증착된다.

[0042] PVD, 전해도금, 무전해 증착, CVD 등을 포함한 다수의 기법을 통해 구리 전도성 루트(107)가 형성될 수 있다. 일부 구현예에서, 구리 충전을 형성하는 바람직한 방법은 PVD에 의해 얇은 구리의 시드 층(seed layer)을 증착하는 단계와, 뒤이어 전해도금에 의해 벌크 구리 충전재(fill)를 증착하는 단계를 포함한다. 구리는 통상적으로 필드 부분에 존재하는 초과 부분을 갖도록 증착되기 때문에, 상기 초과 부분을 제거하여 평탄화된 구조물(100)을 얻기 위하여 화학 기계적 연마(CMP)가 필요하다.

[0043] 그 다음, 도 1b를 참조하면, 구조물(100)이 완성된 후, 기판(100)의 표면이 사전-세척되어 오염물과 금속 산화물을 제거할 수 있다. 사전-세척 후에, 활성 성분(붕소 또는 금속을 함유한 도편트-생성 성분)을 함유한 도편트 소스 층이 구리 배선(107)과 절연막(103) 둘 모두의 위에 증착된다. 그 다음, 예를 들어 상기 소스 층의 질화반응 또는 산화반응에 의해 상기 소스 층이 패시베이션 층으로 변화된다. 예를 들어, 패시베이션 층은 BN<sub>x</sub>, BO<sub>x</sub>, AlO<sub>x</sub>, TiO<sub>x</sub> 등을 함유할 수 있다. 소스 층이 절연막의 구역들 위에 비-전도성 패시베이션 층으로 완전히 변화되어 인접한 금속 배선들(107) 간의 단락을 방지할 수 있다. 구리 배선(107) 위에 바로 존재하는 소스 층의 부분이 오직 부분적으로만 패시베이션 층으로 변화되며, 이로써, 변화되지 않은 소스 층의 부분은 구리와 접촉 상태로 유지된다. 패시베이션되지 않은 소스 층의 부분으로부터의 도편트가 구리로 확산되거나 구리와 반응한 후, 금속 배선(107)의 상부 부분 내에 보호 캡(108)이 형성된다. 소스 층에 증착되는 물질의 양을 조절함으로써, 소스 층을 부분적으로 패시베이션하는 동안 변화 정도를 조절함으로써, 그리고 도편트와 구리의 확산 및/또는 반응 동안 이용되는 조건들을 조절함으로써 보호 캡의 두께가 조절될 수 있다. 보호 캡은, 예를 들어 B, Al, Ti 등과 구리의 합금 또는 고용체를 포함할 수 있다. 일부 실시예에서, 소스 층으로부터 도편트의

확산을 촉진하는데 이용되는 온도와 시간을 조절함으로써 합금 또는 고용체 내의 도편트의 양이 조절된다. 보호 캡의 조성 및 패시베이션 층의 조성이 다음의 섹션에서 자세히 기술될 것이다.

[0044] 일부 실시예에서, 패시베이션 층은 또한, 확산 장벽층의 역할도 한다. 그 밖의 다른 실시예에서, 별개의 확산 장벽(또는 에칭 저지) 층이 패시베이션 층의 상부에 증착된다. 통상적으로, 이러한 확산 장벽층은 도핑되었거나 도핑되지 않은 실리콘 탄화물 또는 실리콘 질화물을 포함한다.

[0045] 도 1b에 도시된 바와 같이, 필름(109)이 단일 패시베이션 층(가령, BN<sub>x</sub> 또는 AlO<sub>x</sub> 층)을 포함할 수도 있고, 또는 구리 배선(107)에 인접한 패시베이션 층과 상기 패시베이션 층 위에 존재하는 상부 절연막 확산 장벽층(가령, 도핑된 실리콘 탄화물 층)으로 구성된 이중층(bi-layer)일 수도 있다. 이러한 실시예들 모두가 도 2a 내지 도 2c를 참조해 뒤이은 섹션에서 자세히 기술될 것이다. 상기 필름(109)은 Cu/절연막 계면 필름이라고 언급될 수도 있고, 또는 단순히 "계면 필름"이라고 언급될 수도 있다.

[0046] 계면 필름이 별개의 절연막 확산 장벽층을 포함하는 실시예에서, 상기 절연막 확산 장벽층은 통상적으로 PECVD 법에 의해 패시베이션 층의 상부에 증착된다. 일 실시예에서, 패시베이션 층의 증착, 보호 캡(108)의 형성, 및 절연막 확산 장벽층의 증착이 진공 상태를 해소하지 않고 하나의 PECVD 장치에서 수행된다. 계면 필름(109)은 또한, 뒤이은 다마신 공정 동안 에칭 저지의 역할도 수행할 수 있다.

[0047] 도 1b를 다시 참조하면, 듀얼 다마신 절연막 구조의 제 1 절연층(111)이 필름(109) 위에 증착된다. 상기 증착에 뒤이어, 선택 사항으로서, PECVD 법에 의해 제 1 절연층(111) 위에 에칭 저지 필름(113)이 증착된다. 절연층(111)은 통상적으로 절연층(103)에 대해 나열된 것과 같은 로우-k 절연 물질로 구성된다. 층들(111 및 103)이 필연적으로 동일한 조성을 가질 필요가 있는 것은 아니다.

[0048] 도 1c에 도시된 바와 같이, 듀얼 다마신 절연막 구조물의 제 1 절연층(1115)이 상기 제 1 절연층(111)과 유사한 방식으로 에칭-저지 필름(113) 위에 증착되는 공정이 뒤따른다. 반사 방지층(도시되지 않은)과 CMP 저지 필름(117)의 증착이 뒤따른다. 제 2 절연층(115)은 층(103 및 111)에 대해 전술된 것과 같은 로우-k 절연 물질을 통상적으로 함유한다. CMP 저지 필름(117)은 뒤이은 CMP 공정 동안 금속간 절연막(IMD) 층(115)의 연약한 절연 물질을 보호하는 역할을 한다. 통상적으로, CMP 저지층은 확산 장벽 및 에칭 저지 필름(109 및 113)과 유사한 통합 요구사항(integration requirement)의 영향을 받고, 실리콘 탄화물 또는 실리콘 질화물에 기반을 둔 물질들을 포함할 수 있다.

[0049] 도 1d 및 도 1e에 도시된 바와 같이, 제 1 및 제 2 절연층 내의 비아(119)와 트렌치(121)의 에칭으로 듀얼 다마신 공정이 계속된다. 표준 리소그래피 기법을 사용하여 도 1d에 도시된 패턴을 에칭할 수 있다. 해당업계 종사자에게 잘 알려져 있는 트렌치-퍼스트(trench-first) 또는 비아-퍼스트(via-first) 법이 이용될 수 있다.

[0050] 그 다음, 도 1e에 도시된 바와 같이, 이렇게 새롭게 형성된 비아와 트렌치가 전술된 바와 같이 금속 확산 장벽(123)으로 코팅되고, 상기 금속 확산 장벽은 탄탈, 탄탈 질화물, 티타늄 질화물, 또는 구리 원자가 절연층으로 확산되는 것을 효과적으로 차단하는 그 밖의 다른 물질과 같은 장벽 물질을 함유할 수 있다.

[0051] 확산 장벽(123)이 증착된 후, 뒤이어구리 상감(inlay)을 이용해 피쳐를 전기-충전(electrofilling)할 수 있도록 (통상적으로 PVD 공정에 의해) 구리의 시드 층이 도포된다. 구리 층이 예를 들어 전기-충전에 의해 증착되고, CMP 저지 필름(117)에서 CMP를 저지하도록 수행되는 CMP 공정에서, 필드에 증착된 금속의 잉여 부분이 제거된다. 도 1e는 완료된 듀얼 다마신 공정을 보여주며, 여기서 구리 전도성 루트(124 및 125)가 장벽(123) 위의 비아와 트렌치 내에 상감된다(도시되지 않은 시드 층). 도 1e는 구리 배선이 조절 가능 방식으로 도핑된 세 개의 인터커넥트를 도시한다.

[0052] 추가적 처리가 요구되는 경우, 필름(109)과 유사한 계면 필름 및 캡(108)과 유사한 보호 캡이 도 2e에 도시된 구조물의 상부에 형성되고, 새로운 금속배선 층이 뒤따른다.

[0053] 보호 캡(108)과 계면 층(109)의 구조와 조성이 도 2a 내지 도 2c와 관련해 자세히 기술될 것이다.

#### 소자 구조

[0055] 도 2a를 참조하면, 부분적 IC 구조물의 예시적 획단면도가 도시된다. 이러한 소자에서, 층간 절연막(201)에 형성된 비아와 트렌치가 확산 장벽 물질(203)로 라이닝(lining)되고 구리 또는 구리 합금(205)으로 충전된다. 구리 배선(205)의 상부 부분이, 구리 배선(205)과 패시베이션 층(209) 사이의 계면에 존재하는 얇은 보호 캡(207)을 포함한다. 패시베이션 층(209)이 ILD 층(201)과 보호 캡(207) 둘 모두의 위에 존재하고, 이들 층 모두와

접촉하고 있다. 절연막 확산 장벽 또는 에칭 저지층(211)이 패시베이션 층(211)의 상부에 존재한다. 명확성을 위해 도시되지는 않았으나, 또 다른 ILD 층이 절연막 확산 장벽 또는 에칭 저지층(211)의 상부에 존재한다. 패시베이션 층(209)과 확산 장벽(또는 에칭 저지) 층(211)이 함께, 금속/ILD 경계에 존재하는 계면 필름(도 1b와 관련해 층(109)에 의해 도시된 것과 같은 계면 필름)을 구성한다.

[0056] 일 실시예에서, 층간 절연층(201)이 약 1,000 내지 10,000Å의 두께를 가진다. 층(210)은 해당업계 종사자에게 알려져 있는 로우-k 및 울트라 로우-k 절연막과 같은 다양한 ILD 물질을 포함할 수 있다. 예를 들어, 탄소가 도핑된 실리콘 산화물 또는 약 2.8보다 작은 k를 갖는 유기 절연 물질이 이용될 수 있다. 구리 배선(205)이 약 500 내지 10,000Å의 두께를 가질 수 있고, 층 두께에 의해 측정되는 바와 같이, 바람직하게는 상기 두께의 약 10% 이하, 좀 더 바람직하게는 약 2%이하를 보호 캡이 차지한다. 많은 실시예에서, 보호 캡이 단계적인 조성을 가질 것이고 패시베이션 층 계면에서 가장 큰 도편트 농도를 가질 것이라는 것이 이해된다. 보호 캡에 허용 가능한 두께는 도편트의 저항성에 따라 달라질 것이다. 일반적으로, 전술된 방법을 따라, 비아의 저항성 시프트(shift)가 약 10% 이하, 바람직하게는 약 5% 이하, 그리고 좀 더 바람직하게는 약 3% 이하가 되도록 보호 캡이 형성된다. 이러한 저항성 시프트는 캡이 없는 인터커넥트의 저항성 대비 평균 인터커넥트의 저항성의 차이로서 측정된다. 일부 실시예에서, 허용 가능한 저항성 시프트는 500Å을 초과하지 않는 두께, 바람직하게는 100Å을 초과하지 않는 두께를 갖도록 보호 캡을 형성함으로써 획득된다.

[0057] 서로 다른 도편트는 구리 인터커넥트로 서로 다르게 확산될 수 있고, 서로 다른 정도로 인터커넥트 저항성에 영향을 줄 수 있음이 이해된다. 따라서, 위에서 제공된 수치 값은 하나의 예시의 역할을 하는 것으로 언급된 두께 파라미터에 본 발명 구조가 한정되는 것으로 의도한 것은 아니다. 예를 들어, 특정 도편트가 구리 인터커넥트로 확산되어, 별개의 캡을 형성하지 않고 전체 구리 배선 위에 증착될 수 있고, 또는 결정 경계에서 축적될 수 있고 및/또는 그 밖의 다른 계면에서(가령, 확산 장벽(203)과 구리 층(205)의 계면에서) 축적될 수 있다. 유리하게, 제공된 발명은 이러한 도편트를 조절된 양으로 주입할 수 있도록 하여, 이러한 경우에서 층 두께가 정확하게 정의될 수 없다 하더라도 인터커넥트 저항성이 조절될 수 있도록 한다.

[0058] 다수의 도핑 원소가 보호 캡에 사용될 수 있다. 고용체, 합금, 또는 구리와의 화합물을 형성하는 도편트들과, 구리 결정 경계에서 그리고 구리와 그 밖의 다른 층들과의 계면에서 축적될 수 있는 도편트들에 우선순위가 정해진다. 상대적으로 낮은 저항성을 갖는 물질(가령, 금속)이 종종 선호된다. 더욱이, 저온에서(가령, 약 100°C 이하의 온도에서) 구리로 쉽게 확산되지 않는 물질이 종종 선호된다. 적합한 도편트의 예시에는 B, Al, Hf, Ti, Co, Ta, Mo, Ru, Sn, 및 Sb이 포함되나 이에 한정되는 것은 아니다. 일반적으로, 선택된 도편트가 휘발성 전구체를 가져서 CVD 법에 의해 증착이 수행될 수 있는 것이 바람직하다. 따라서, 휘발성 수소화물, 카르보닐, 할로겐화물, 및 유기금속 전구체를 갖는 금속 도편트가 통상적으로 선호된다. 최대 450°C의 온도에서 가스상(gas phase)으로 주입될 수 있는 화합물과 약 1 Torr 이상의 전구체가 적합한 전구체이다.

[0059] 구체적 실시예에서, 보호 캡(207)이 구리와 붕소, 또는 구리와 알루미늄, 또는 구리와 티타늄을 포함한다. 일부 실시예에서, 도편트들은 서로가 함께 사용된다. 예를 들어, 보호 캡(207)이 구리, 알루미늄, 및 티타늄, 또는 구리와 도편트들의 배합물을 포함할 수 있다. 일부 실시예에서, 전술된 도편트가 자체-정렬 보호 버퍼(protective self-aligned buffer, PSAB) 층을 형성하는데 사용되는 물질(가령, CuSi<sub>x</sub>, CuGe<sub>x</sub>, SiN<sub>x</sub>, 및 SiC<sub>x</sub> 등과 같은 물질)과 함께 사용된다. 이러한 층이, naming Yu 등이 발명자이고 2007년 3월 20일에 출원되어 공동 소유된 미국 특허 출원 제11/726,363호(발명의 명칭: Protective Self-aligned Buffer Layers for Damascene Interconnects), Chattopadhyay 등이 발명자이고 2007년 2월 20일에 출원된 미국 특허 출원 제11/709,293호(발명의 명칭: Protective Self-aligned Buffer Layers for Damascene Interconnects), 그리고 van Schravendijk 등이 발명자이고 2004년 11월 3일에 출원된 미국 특허 출원 제10/980,076호(발명의 명칭: Protection of Cu Damascene Interconnects by Formation of a Self-aligned Buffer Layer)에 자세히 기술되어 있으며, 위 미국 특허 출원은 본원에서 참조로서 포함된다.

[0060] 일 실시예에서, ILD 층(201)과 보호 캡(207) 둘 모두의 위에 존재하는 패시베이션 층(209)이 약 50 내지 500Å 사이의 두께를 가진다. 상기 패시베이션 층은 인접한 인터커넥트들 간의 단락을 방지하는 비-전도성 물질을 통상적으로 함유한다. 패시베이션 층은 변화된 도편트를 통상적으로 함유하는데, 예를 들어, 도편트(붕소 또는 금속)의 질화물, 산화물, 탄화물, 황화물, 셀렌화물, 인화물, 또는 비화물을 함유할 수 있다. 더욱이, 패시베이션 층은 탄화수소(C<sub>x</sub>H)를 함유할 수도 있다. 일 실시예에서, 패시베이션 층이 BN<sub>x</sub>를 함유한다. 일부 실시예에서, 그 밖의 다른 실시예에서, BN<sub>x</sub> 층은 또한, 수소를 포함할 수 있다. 또 다른 예시에서, 패시베이션 층이 AlO<sub>x</sub>, HfO<sub>x</sub>,

$TiO_x$ ,  $CoO_x$ ,  $TaO_x$ ,  $MoO_x$ ,  $RuO_x$ ,  $SnO_x$ , 및  $SbO_x$ 와 같은 금속 산화물을 함유한다.

[0061] 도 2a에 도시된 바와 같이, 절연막 확산 장벽 또는 에칭 저지층(211)이 패시베이션 층의 상부에 존재하고 있다. 일 실시예에서, 층(211)이 약 50 내지 500Å 사이의 두께를 가진다. 전통적으로, 실리콘 질화물 및 질소-도핑된 실리콘 탄화물(NDC)이 이러한 응용예에서 이용되었다. 현재에는, 실리콘 질화물보다 낮은 유전 상수를 갖는 물질이 절연막 확산 장벽으로서 종종 이용된다. 이러한 물질에는, Yu 등이 발명자이고 2004년 6월 15일에 출원되어 공동 소유된 미국 특허 출원 제10/869,474호에 기술된 것과 같은 탄소가 풍부한 실리콘 탄화물; Yu 등이 발명자이고 2004년 8월 9일에 출원된 미국 특허 출원 제10/915,117호와 Yu 등이 발명자이고 2006년 3월 8월에 출원된 미국 특허 출원 제11/373,847호에 기술되어 있는 봉소-도핑된 실리콘 탄화물; 그리고 Tang 등이 발명자이고 2005년 2월 15일에 특허된 미국 특허 제6,855,645호에 기술된 것과 같은 산소-도핑된 실리콘 탄화물이 포함된다. 이러한 모든 미국 특허 출원과 미국 특허가 참조로서 본원에 포함된다. 일부 실시예에서, 층(211)은 몇몇 서브-층(예를 들어, 개선된 확산 장벽과 에칭 저지 속성을 위해 맞춤화된 서로 다른 조성을 갖는, 도핑되었거나 도핑되지 않은 실리콘 탄화물을 함유한 서브-층)을 가질 수 있다. 예를 들어, 장벽이, 도핑되지 않은 탄화물의 서브-층, 질소-도핑된 탄화물의 서브-층, 및 산소-도핑된 탄화물의 서브-층의 임의의 조합을 포함할 수 있다. 장벽이 두 개의 서브-층, 세 개의 서브-층, 또는 그 이상의 서브-층을 가질 수도 있다. 조합 장벽 층의 예시가 2004년 6월 15일에 출원된 미국 특허 출원 제10/869,474호(2007년 10월 16일에 특허되어 현재 특허 번호 제 7,282,438호)에 제시되어 있으며, 위 미국 특허 출원은 본원에 참조로서 포함된다. 예를 들어, 절연막 확산 장벽층은 도핑되었거나 도핑되지 않은 실리콘 탄화물, 실리콘 질화물, 또는 실리콘 탄질화물(carbonitride)을 포함할 수 있다.

[0062] 도 2a에 도시된 실시예에서, 층들(209 및 211)이 함께 두 개의 ILD 층(가장 위에 있는 ILD 층은 도시되지 않음) 사이에 존재하는 계면 층을 형성한다.

[0063] 특정 실시예에서, 패시베이션 층(209)이 별개의 실리콘 탄화물 또는 실리콘 질화물 층(211)을 필요로 하지 않고 확산 장벽 또는 에칭 저지층의 역할을 할 수 있다. 도 2b에 도시된 이러한 실시예에서, 두 ILD 층 사이에 존재하는 계면 층이 오직 패시베이션 층(209)으로 구성된다. 예를 들어, 특정 금속 산화물과 금속 질화물이 에칭 저지층 또는 확산 장벽층의 역할을 할 수 있다.

[0064] 도 2c는 도편트 또는 도편트-생성 화합물(208)의 층이 보호 캡(207)과 패시베이션 층(209) 사이에 존재하고, 이러한 두 층들과 접촉하고 있는 실시예를 도시한다. 층(208)이 구리 배선(205) 위에 정렬되며, 절연막(201)의 층 위로 뻗어 있지 않다. 층(208)은 순수한 도편트 또는 도편트-생성 화합물을 포함할 수 있다. 예를 들어, 층(208)이  $BH_x$ , Al, Ti, Ta, Hf, Ru 등을 포함할 수 있다. 이러한 층 내의 금속은 H, C, N 등과 같은 그 밖의 다른 원소들을 갖지 않을 수도 있고, 이러한 그 밖의 다른 원소들과 결합될 수도 있다. 일부 실시예에서, 구리가 층(208)을 향해 위쪽으로 확산되어 층(208) 내의 도편트와 합금, 혼합물, 또는 고용체를 형성할 수 있다. 이러한 실시예에서, 이중층(207/208)이 보호 캡의 역할을 할 것이다. 일반적으로, 본원에 기술된 것과 같은 보호 캡은 주변 절연막(210)과 동일한 높이(level)로 구리 라인 내에 전체적으로 존재할 수 있고, 또는 주변 절연막(201)의 높이보다 위에 존재하는 부분을 포함할 수 있다.

[0065] 하나의 구체적 예시에서, 소자가, 봉소-도핑된 보호 캡(207)과  $BN_x$ 를 함유한 패시베이션 층(209)을 갖는, 도 2a에 도시된 것과 같은 구조를 가진다. 구리 배선(205)은 약 3,500Å의 두께를 갖는 ULK 절연막(약 2.5의 k)의 층에 존재한다. 보호 캡(207)은 구리와 봉소를 포함하고, 약 100Å의 두께를 가진다. 보호 캡은 패시베이션 층과의 계면에서 구리 층의 상부에 존재한다. 패시베이션 층은 약 150Å의 두께를 가지고  $BN_x$ 를 포함한다. 패시베이션 층은 또한, 수소를 포함할 수 있고,  $(BNH)_x$  층으로서 실험에 부분에서 언급될 것이다. 확산 장벽(211)의 층이 질소-도핑된 실리콘 탄화물, 산소-도핑된 실리콘 탄화물, 또는 도핑되지 않은 실리콘 탄화물을 포함할 수 있다. 층(211)은 100Å 내지 500Å의 두께를 가진다.

[0066] 또 다른 구체적 예시에서, 소자가, 도 2a에 도시된 것과 같은 구조를 갖고, 티타늄 보호 캡(207)과  $TiN_x$ 를 함유한 패시베이션 층(209)을 가진다. 약 3,500Å의 두께를 갖는 ULK 절연막(약 2.5의 k)의 층에 구리 배선(205)이 존재한다. 보호 캡(207)은 구리와 티타늄을 포함하고, 약 100Å의 두께를 가진다. 보호 캡은 패시베이션 층과의 계면에서 구리 배선의 상부에 존재한다. 패시베이션 층은 약 150Å의 두께를 가지고  $TiN_x$ 를 포함한다. 패시베이션 층은 또한, 수소를 포함할 수도 있다. 확산 장벽(211)의 층이 질소-도핑된 실리콘 탄화물, 산소-도핑된 실리콘 탄화물, 또는 도핑되지 않은 실리콘 탄화물을 포함할 수 있다. 층(211)이 100Å 내지 500Å의 두께를

가진다.

[0067] 또 다른 구체적 예시에서, 소자가, 도 2a에 도시된 것과 같은 구조를 갖고, 알루미늄-도핑된 보호 캡(207)을 가진다. 구리 배선(205)이 약 3,500Å의 두께를 갖는 ULK 절연막(약 2.5의 k)의 층에 존재한다. 보호 캡(207)은 구리와 알루미늄을 포함하고 약 100Å의 두께를 가진다. 보호 캡은 패시베이션 층과의 계면에서 구리 배선의 상부에 존재한다. 패시베이션 층은 약 100Å 이하의 두께를 갖고, 본질적으로 AlO<sub>x</sub>로 구성된다. 약 100Å 내지 500Å의 두께를 갖는 확산 장벽의 층(211)이 AlO<sub>x</sub>와 접촉하여 존재하고, 질소-도핑된 실리콘 탄화물, 산소-도핑된 실리콘 탄화물, 또는 도핑되지 않은 실리콘 탄화물을 포함할 수 있다.

#### 보호 캡핑 층 형성 방법

[0068] 보호 캡핑 층을 형성하는 예시적 방법이 도 3a에 도시된 공정 흐름도에 나타난다. 상기 공정의 다양한 스테이지에서 획득된 소자 구조의 획단면도가 도 4a 내지 도 4e에 도시된다. 본원에 기술된 방법이 여러 유형의 장치에서 실시될 수 있으나, 일부 실시예에서, 플라스마 화학적 기상 증착(PECVD) 장치가 선호된다. 일부 실시예에서, PECVD 장치는 고주파(HF)와 저주파(LF) 플라스마 생성 소스를 제공할 수 있다.

[0069] [0070] 도 3a를 참조하면, 공정(301)에 나타난 바와 같이, 구리 배선의 패턴을 갖는 부분 제작된 반도체 소자를 절연막에 제공함으로써 공정이 시작된다. 예를 들어, 도 4a에 도시된 것과 같은 소자가 이용될 수 있다. 상기 소자는 절연막의 층(401)에 내장된 구리 또는 구리 합금(405)의 층을 가진다. (예를 들어 Ta, TaN<sub>x</sub>, TiN<sub>x</sub>, Ru, W를 함유한) 얇은 확산 장벽 물질층이 구리와 절연막 사이의 계면에 존재하고 있다. 구리의 층과 절연막의 층이 기판 표면에 노출된다.

[0071] 선택 사항으로서, 공정(303)에서 기판이 사전-세척되어 기판의 표면으로부터 오염물을 제거할 수 있다. 예를 들어, 기판을 플라스마 내의 환원 가스(예를 들어, 플라스마 방전에서 H<sub>2</sub>, N<sub>2</sub>, NH<sub>3</sub> 및 이들의 혼합물로 구성된 그룹으로부터 선택된 가스)에 노출시킴으로써 기판이 사전-세척되어 구리 표면으로부터 구리 산화물을 제거할 수 있다. 일부 실시예에서, H<sub>2</sub> 플라스마를 이용한 사전-세척으로 인해 소자들이 특히 개선된 특성을 갖게 된다. 사전-세척 동안의 공정 가스에는 또한, N<sub>2</sub>, He, Ar과 같은 운반 가스(carrier gas)가 포함될 수 있다. 일부 실시예에서, 사전-세척은 약 200 내지 400°C의 온도에서, 약 1.5 내지 4 Torr에서, 그리고 약 4,000 내지 10,000 sccm의 H<sub>2</sub> 유량(flow rate)에서 PECVD 챔버에서 수행된다. HF와 LF 성분을 가질 수 있는 플라스마가 고도로 가열되고, 하나의 300mm 웨이퍼 당 200 내지 1000W의 총 전력이 지속된다. 일부 실시예에서, 사전-세척 공정 동안 0.1 내지 1.5 W/cm<sup>2</sup>의 HF 전력과 0 내지 0.8 W/cm<sup>2</sup>의 LF 전력을 이용하는 것이 바람직하다. 또 다른 예시에서, 환원 가스로서 H<sub>2</sub> 대신에 NH<sub>3</sub>가 이용되어, 약 6,000 내지 8,000 sccm 범위의 유량으로 공정 챔버 내로 흘러 들어간다. 약 2,000 내지 4,000 sccm의 유량으로 N<sub>2</sub> 운반 가스가 챔버 내로 흘러 들어간다. 사전-세척 처리가 몇 초간(예를 들어, 약 6 내지 20초 사이) 지속될 수 있다.

[0072] 일부 실시예에서, 직접 플라스마 노출보다 좀 더 마일드(mild)한 방법을 이용하여 사전-세척을 수행하는 것이 바람직하다. 이러한 마일드한 방법은, 직접 플라스마 노출에 의해 쉽게 손상을 입을 수 있는 연약한 ULK 절연막에 구리 배선이 내장되어 있을 때 특히 유리하다.

[0073] 일부 실시예에서, H<sub>2</sub>, N<sub>2</sub>, NH<sub>3</sub> 및 이들의 혼합물로 구성된 그룹으로부터 선택된 가스를 포함한 원거리 플라스마(remote plasma)를 이용함으로써 구리 산화물의 완전한 제거 또는 부분적 제거가 수행된다. 이러한 구현예에서, 이를 가스들 중 하나 이상(예를 들어, H<sub>2</sub>와 N<sub>2</sub>의 혼합물, 또는 NH<sub>3</sub>와 N<sub>2</sub>의 혼합물)을 이용하여 챔버 내에 플라스마를 형성할 수 있고, 상기 플라스마는 웨이퍼 기판을 지지하는 챔버와 물리적으로 이격되어 있다. 그 후, 형성된 플라스마가 전달 라인을 통해 이온 필터로 향하며, 상기 이온 필터는 라디칼(radical)을 남기면서 이온 플라스마를 감소시킨다. 결과로서 생성된 라디칼이 풍부한 공정 가스(일부 실시예에서, 이온 종을 거의 함유하지 않거나 이온 종을 실질적으로 함유하지 않음)가 기판 표면과 접촉하고, 원하는대로 부분적으로 또는 전체적으로 구리 산화물을 제거한다. 직접 플라스마에 함유된 고에너지 이온이 절연막 손상에 관계가 있었기 때문에, 이온이 부족한 원거리 플라스마의 이용으로 인해 마일드하고 효과적인 사전-세척 수행 방법을 제공할 수 있다. 적합한 원거리 플라스마 시스템의 예시는 캘리포니아, 산 호세의 노벨러스 시스템즈에 의해 제공되는 Gamma<sup>TM</sup> 제품 라인에서 찾을 수 있다.

- [0074] 그 밖의 다른 실시예에서, H<sub>2</sub>, N<sub>2</sub>, NH<sub>3</sub> 및 이들의 혼합물로 구성된 그룹으로부터 선택된 가스와 같은 환원 가스의 존재 하에서 자외선(UV) 방사선 처리를 이용함으로써 전체적인 또는 부분적인 구리 산화물 제거가 수행된다. 이러한 구현예에서, 기판에 UV가 조사되고 있는 동안 이들 가스 중 하나 이상(예를 들어, H<sub>2</sub>와 N<sub>2</sub>의 혼합물, 또는 NH<sub>3</sub>와 N<sub>2</sub>의 혼합물)이 기판과 접촉한다. 예를 들어, B. Varadarajan 등이 발명자이고 2009년 11월 12일에 출원되어 공동 소유된 가특허 출원 제61/260,789호(발명의 명칭: UV and Reducing Treatment for K Recovery and surface Clean in Semiconductor Processing)에 기술된 것과 같은 장치와 공정 조건이 이용되며, 상기 가특허 출원은, 본원에 기술된 실시예에서 이용되기에 적합한 UV 처리 장치 및 방법에 대한 세부 사항을 제공하기 위한 목적으로 본원에 참조로서 포함된다. 기술된 UV 처리를 이용하여 구리 산화물의 제거를 조절할 수 있고, 여기서, 제거된 산화물의 두께가 UV 노출의 지속 시간, 공정 가스 조성, 기판 온도, 및 그 밖의 다른 조건들에 의해 조절될 수 있다.

- [0075] 일부 실시예에서, 플라스마가 없는 환경에서 열 처리에 의해 사전-세척이 달성된다. 예를 들어, H<sub>2</sub>, N<sub>2</sub>, NH<sub>3</sub>, 또는 이들의 혼합물을 포함하는 대기에서 약 15 내지 60초 동안 약 200°C 이상의 온도까지 웨이퍼가 가열될 수 있다. 이러한 열 처리는 부분적인 구리 산화물 제거에 이용될 수 있고, 연약한 ULK 절연막을 함유한 기판 처리에 특히 유리하다.

- [0076] 사전-세척이 완료된 후, 공정(305)에서 도편트-함유 물질의 소스 층이 기판 표면 위에 증착된다. 유리하게, 도편트-함유 물질은 금속 표면 위에 선택적으로 증착될 필요가 없고, 절연막의 표면과 금속 둘 모두의 위에 증착될 수 있다. 도편트-함유(예를 들어, 봉소-함유 또는 금속-함유) 소스 층의 증착을 초래하는 조건 하에서, 부분 제작된 소자를 도편트-함유 반응물(가령, 봉소-함유 반응물 또는 금속-함유 반응물)과 접촉시킴으로써 소스 층이 증착된다.

- [0077] 일 실시예에서, 플라스마 방전 없이 도편트-함유 소스 층이 열적으로(thermally) 증착된다. 예를 들어, 휘발성 수소화물, 할로겐화물, 카르보닐, 또는 유기금속 화합물과 같은 휘발성 전구체가 고온에서 반응(예를 들어, 분해)하여 기판 표면 위에 도편트-함유 물질의 층을 증착할 수 있다. 해당업계 종사자에 의해 이해될 수 있는 바와 같이, 온도 범위, 기판 노출 시간, 및 그 밖의 다른 증착 조건들이 각각의 특정 전구체에 맞게 조정된다.

- [0078] 일 실시예에서, B<sub>2</sub>H<sub>6</sub>가 전구체로서 이용되어 B-도핑된 보호 캡을 형성할 수 있다. 하나의 예시적 공정에서, N<sub>2</sub>, O<sub>2</sub>, CO<sub>2</sub>, He, NH<sub>3</sub>, Ar 등과 같은 하나 이상의 추가적 운반 가스와 함께 B<sub>2</sub>H<sub>6</sub>가 공정 챔버 내로 주입된다. 이번 예시에서, B<sub>2</sub>H<sub>6</sub> 농도는 약 0.5 내지 20%의 범위이고, 압력은 약 0.5Torr 내지 약 10Torr 범위이다. B<sub>2</sub>H<sub>6</sub>는 플라스마 방전의 부재 하에서 약 200 내지 400°C 사이의 챔버 온도에서 기판과 접촉하여, 기판 위에 봉소-함유 층이 증착된다. 상기 층이 B-H 결합을 갖는 것으로 판단되었으므로 BH<sub>x</sub> 층이라고 언급될 것이다. BH<sub>x</sub> 층은 구리 배선으로 확산되어 보호 캡을 형성하는 B 도편트 소스의 역할을 한다.

- [0079] 또 다른 예시에서, 휘발성 금속-함유 전구체가 챔버 내로 주입된다. 유기금속 화합물, 금속 수소화물, 금속 할로겐화물, 및 금속 카르보닐이 적합한 전구체의 역할을 할 수 있다. 예를 들어, 알킬-치환된 금속 유도체와 시클로펜타디에닐-치환된 금속 유도체가 이용될 수 있다. 이러한 전구체가 고온에서 반응하여 기판 위에 금속-함유 소스 층을 형성할 수 있다. 일부 실시예에서, B-함유 캡의 증착에서 이용된 것과 유사한 압력과 온도 범위가 이용될 수 있다. 일반적으로, 전구체의 성질에 따라, 최적의 품질을 갖는 금속-함유 소스 층을 증착하기 위하여 증착 조건이 최적화된다. 예를 들어, 온도 범위는 전구체에 대한 특정 분해 과정에 알맞도록 최적화될 수 있고, 따라서 원하는 바에 따라 금속-함유 소스 층의 조성을 조정할 수 있다. 해당업계 종사자라면 증착 조건을 어떻게 최적화하는지, 최적화된 조성을 이용해 어떻게 금속-함유 소스 층을 얻는지 이해할 것이다.

- [0080] 언급된 바와 같이, 다양한 금속이 도편트의 역할을 할 수 있다. 예를 들어, 예시적 구리 배선이 Al, Hf, Ti, Co, Ta, Mo, Ru, Sn, 및 Sb로 도핑될 수 있다. 휘발성 전구체에 대해 잘 알려진 그 밖의 다른 금속들이 이용될 수도 있다. 알루미늄-함유 소스 층 증착에 적합한 전구체의 예시에는 트리메틸알루미늄, 디메틸알루미늄 수소화물, 트리에틸알루미늄, 트리이소부틸알루미늄, 및 트리스(디에틸아미노)알루미늄이 포함되나 이에 한정되는 것은 아니다. 그 밖의 다른 금속을 함유한 소스 층 증착에 이용될 수 있는 전구체의 예시에는 비스(시클로펜타디에닐)코발트, 코발트(Ⅱ) 아세틸아세톤염(acetylacetone), 테트라카이스(디메틸아미노)하프늄(tetrakis(dimethylamido)hafnium), 테트라카이스(디에틸아미노)하프늄(tetrakis(diethylamido)hafnium), 테트라카이스(디메틸아미노)몰리브덴(tetrakis(dimethylamido)molybdenum), 테트라카이스(디메틸아미노)티타늄(TDMAT), 테트라카이스(디에틸아미노)티타늄(TDEAT), 테트라카이스(에틸메틸아미노)티타늄

(tetrakis(ethylmethylamido)titanium), 비스(디에틸아미노)비스(디이소프로필아미노)티타늄, 펜타키스(디메틸아미노)탄탈, 터트(부틸이미도트리스)(디에틸아미도)탄탈

(tert(butylimidotris)(diethylamido)tantalum)(TBTDET), 펜타키스(디에틸아미노)탄탈

(pentakis(diethylamido)tantalum), 비스(에틸시클로펜타디에닐)루테늄, 트리스(디메틸아미도)안티몬

(tris(dimethylamido)antimony), 및 테트라메틸린(tetramethyltin)이 포함되나 이에 한정되는 것은 아니다.

[0081] 소스 층이 순수한 원소로 이루어진 도편트를 필연적으로 함유할 필요는 없고, 그 밖의 다른 원소(가령, H, C, N 등)와 도편트의 화합물을 포함할 수 있다. 그러나, 도편트가 이러한 층으로부터 용이하게 생성될 수 있고, 일단 생성되면, 도편트가 구리로 확산되거나 구리와 반응할 수 있다. 그러나, 그 밖의 다른 실시예에서, 소스 층이 실질적으로 순수한 금속 또는 봉소를 함유할 수 있다.

[0082] 소스 층이 오로지 구리 배선의 상부에만 선택적으로 증착될 필요는 없고, 절연층의 상부와 구리의 상부 둘 모두에 증착될 수 있다. 그러나, 많은 실시예에서, 구리와 절연막 간 일정한 정도의 선택성이 달성되고, ( $BH_x$  층 또는 금속-함유 층일 수 있는) 소스 층(408)이 절연막(401)의 층 위에서보다 구리 배선(408) 위에서 더 큰 두께를 갖는 도 4b에 도시된 바와 같이, 구리 배선 위에 더 두꺼운 소스 층이 형성된다. 특정 전구체와 증착 조건에 따라, 구리 배선 위에 소스 층이 완전히 선택적으로 증착하는 공정에서부터, 소스 층이 구리와 절연막 둘 모두의 위에서 동일한 두께로 증착되는 완전히 비-선택적인 공정까지의 범위를 갖는 광범위한 선택성이 달성될 수 있다. 본원에 기술된 방법들이 선택적으로 그리고 비-선택적으로 증착된 소스 층들로부터 도편트의 조절-가능한 주입에 이용될 수 있지만, 상기 방법들은 예시로서 부분적 선택성을 가지고 증착된 층들을 이용하여 본원에서 설명된다. 절연막 위에 증착된 소스 층의 두께와 비교할 때 구리 배선 위에 증착된 더 두꺼운 소스 층 두께로 특징지어지는 부분적 선택성이 봉소-함유 및 많은 금속-함유 소스 층들에 있어서 판측될 수 있다. 일부 실시예에서, 구리 위에 존재하는 소스 층의 두께가 절연막 위에 존재하는 소스 층의 두께보다 약 10 내지 500% 더 두껍다.

[0083] 도 3a에 도시된 공정 흐름도를 다시 참조하면, 공정(305)에서 소스 층이 형성된 이후, 뒤이은 공정(307)에서, 구리 위에 존재하는 소스 층의 상부 부분이 변화되어 패시베이션 층을 형성하고, 변화되지 않은 소스 층의 부분은 구리의 층과 접촉 상태로 유지된다. 이것이 도 4c에 도시된 구조물에 의해 나타나며, 여기서, 소스 층(408)의 적은 부분만이 변화되지 않고 구리 배선(405)과 접촉 상태로 있고, 구리 위에 존재하는 소스 층의 상부 부분은 변화되어 패시베이션 층(409)을 형성한다. 절연막 위에 존재하는 소스 층의 부분이 패시베이션 물질로 완전히 변화된다. 패시베이션 공정(309)은 두 가지 목적을 가진다. 첫째, 소스 층의 부분적 패시베이션이 이용 가능한 도편트의 양을 제한하기 때문에, 인터커넥트 저항성 조절에 도움을 준다. 바람직하게, 패시베이션 층은 패시베이션 물질로부터 구리 배선으로 쉽게 확산되지 않을 수 있는 물질을 함유한다. 예를 들어, 봉소가 봉소 질화물로 변화되고, 알루미늄이 알루미늄 산화물로 변화된다. 유리된 봉소와 알루미늄이 구리 배선으로 확산될 수 있지만, 질화물과 산화물로 변화된 때, 이러한 물질은 패시베이션 층 내에 트랩되고, 구리 배선으로 주입되어 구리 배선의 저항성을 증가시킬 수 없다. 소스 층의 상부 부분이 패시베이션 층으로 변화되기 때문에, 구리 배선으로 주입되는 도편트의 양은 구리 배선과 접촉 상태로 남아 있는 소스 층의 변화되지 않은 부분의 두께에 의해 판단된다. 배선으로 주입될 필요가 있는 도편트의 양에 따라, 더 많거나 더 적은 양의 소스 층이 패시베이션 층으로 변화될 수 있다. 예를 들어, 처음에 증착된 소스 층의 두께가 약 50 내지 500Å 사이의 범위일 수 있고, 이러한 두께 중 약 20 내지 60%가 패시베이션 층으로 변화될 수 있다.

[0084] 소스 층이, 구리와 절연막 둘 모두의 위에 증착되는 전도성 물질을 함유하는 실시예에서도 패시베이션이 요구된다. 이러한 실시예에서, 패시베이션이 전도성 물질(가령, 금속)을 거의 전도성이 없거나 전혀 없는 물질로 변화시킴으로써 인접한 구리 배선들 간 단락을 방지할 수 있다. 예를 들어, 절연막 위에 존재하는 부분적으로 전도성인  $BH_x$  소스 층이, 절연막 위에서, 본질적으로 비-전도성인  $BN_x$ 를 함유한 패시베이션 층으로 완전히 변화될 수 있다. 이와 유사하게, 알루미늄을 함유한 소스 층이 비-전도성인 알루미늄 산화물로 변화될 수 있다.

[0085] 질화물, 산화물, 황화물, 셀렌화물, 텔루르화물(telluride), 인화물, 및 탄화물과 같은 다수의 화합물이 패시베이션 층에 적합한 물질이다. 물론, 질화물과 산화물이 많은 실시예에서 선호된다.

[0086] 도편트-함유 소스 층을 적절한 시약과 접촉시킴으로써 패시베이션 층이 형성될 수 있는데, 상기 적절한 시약은 소스 층 물질을 패시베이션 물질로 변화시킬 수 있다. 변화가 (플라스마를 이용하지 않고) 열적으로 수행될 수 있는 일부 실시예에서, 플라스마 방전에서 소스 층을 변화시키는 것이 종종 선호된다. 예를 들어, 기판을 플라스마에서 질소-함유 반응물(가령,  $N_2$ ,  $NH_3$ ,  $N_2H_4$ , 아민 등)과 접촉시킴으로써 질화 반응이 이루어질 수 있다. 이

와 유사하게, 플라스마에서 산소-함유 반응물(가령, O<sub>2</sub>, CO<sub>2</sub>, N<sub>2</sub>O 등)과 접촉함으로써 산화물이 형성될 수 있다. 이와 유사하게, 기판을 원하는 원소를 함유한 반응물에 노출시킴으로써 황화물, 셀렌화물, 텔루르화물, 인화물, 및 탄화물(예를 들어, H<sub>2</sub>S, H<sub>2</sub>Se, H<sub>2</sub>Te, PH<sub>3</sub>, C<sub>x</sub>H<sub>y</sub> 각각)이 형성될 수 있다.

[0087] 일부 실시예에서, 후-처리(post-treatment)가 직접 플라스마 처리를 수반한다. 예를 들어, 노출된 소스 층을 갖는 기판이, H<sub>2</sub>, N<sub>2</sub>, NH<sub>3</sub> 및 이들의 혼합물로 구성된 그룹으로부터 선택된 공정 가스에 형성된 플라스마를 이용해 처리될 수 있다. 일부 실시예에서, 소스 층을 갖는 기판이 플라스마에서 H<sub>2</sub>를 이용해 처리된다. 수소 플라스마 처리는 전구체 층으로부터 잔여 유기 그룹을 제거하는 역할을 할 수 있고, 말단 금속-H 결합을 형성할 수 있다. 그 밖의 다른 예시에서, 기판이 플라스마에서 H<sub>2</sub> 및 N<sub>2</sub>의 혼합물을 이용해 후-처리되거나 플라스마 내에서 NH<sub>3</sub>를 이용해 후-처리되고, 이로써 유기 그룹이 제거되고 금속-N 결합이 형성된다. 그 밖의 다른 질화 제제(가령, N<sub>2</sub>H 및 아민)가 일부 실시예에서 이용될 수 있다.

[0088] 사전-처리를 이용하는 경우라도, 때때로 직접 플라스마 처리보다 더 마일드한 처리 방법을 이용하는 것이 바람직하다. 예를 들어, 일부 실시예에서, H<sub>2</sub>, N<sub>2</sub>, NH<sub>3</sub> 및 이들의 혼합물로 구성된 그룹으로부터 선택된 가스에서 형성된 원거리 플라스마를 이용하여 기판이 처리될 수 있다. 이전에 기술된 바와 같이, 기판을 하우징하고 있는 챔버와 물리적으로 이격된 챔버에서 원거리 플라스마가 생성되고, 이러한 원거리 플라스마가 기판으로 전달되기 전에 이온 종이 제거되어, 절연막 손상의 가능성이 더 적어지게 된다. 이는, 원거리 플라스마에 함유된 라디칼이 고에너지 이온보다 통상적으로 더 적게 손상시키기 때문이다. 금속-H 및 금속-N 형성뿐만 아니라 층으로부터 유기 그룹의 제거가 원거리 플라스마에 의해 달성될 수 있다.

[0089] 더욱이, 이전에 참조되었던 미국 특허 출원 제61/260,789호에 기술된 방법을 이용하여, H<sub>2</sub>, N<sub>2</sub>, NH<sub>3</sub> 및 이들의 혼합물로 구성된 그룹으로부터 선택된 공정 가스에서 UV 조사에 의해 마일드한 후-처리가 수행될 수 있다. 이러한 UV 처리를 이용하여 금속-H와 금속-N 결합을 형성할 수 있고, 또한 전구체 층으로부터 유기 치환기를 제거할 수 있다.

[0090] 일부 실시예에서, 플라스마가 없는 환경에서 열 처리에 의해 후-처리가 이루어진다. 예를 들어, H<sub>2</sub>, N<sub>2</sub>, NH<sub>3</sub>, 또는 이들의 혼합물을 포함한 대기에서 웨이퍼가 약 300 내지 350°C의 온도까지 가열될 수 있다. 이러한 열 처리는 연약한 ULK 절연막을 함유한 기판 처리에 특히 유리하다.

[0091] 일부 실시예에서, 플라스마가 없는 환경에서 실온에서 또는 상승된 온도에서 반응물을 이용해 소스 층을 처리함으로써 후-처리가 수행된다. 예를 들어, 플라스마가 없는 환경에서 산소-함유 반응물(가령, O<sub>2</sub>, H<sub>2</sub>O, N<sub>2</sub>O)을 이용해 기판을 처리함으로써 일부 실시예에서 금속-산소 결합을 갖는 패시베이션 층이 형성된다.

[0092] ULK 절연막, 특히 쉽게 손상되는 다공성 및 유기 절연막이 ILD 층에서 사용될 때 원거리 플라스마 후-처리, 열적 후-처리, 및 UV 후처리가 특히 유리하다.

[0093] 많은 실시예에서 질화 후-처리가 선호되나, 일부 실시예에서 그 밖의 다른 유형의 후-처리도 이용될 수도 있다.

[0094] 예를 들어, 산소-함유 가스(가령, O<sub>2</sub>, CO<sub>2</sub>, N<sub>2</sub>O 등)에 노출된 전구체 층을 갖는 기판을 플라스마와 접촉시키거나 플라스마와 접촉시키지 않음으로써 금속-O 결합을 형성하기 위한 후-처리가 구현될 수 있다. 그 밖의 다른 실시예에서, 예를 들어, 소스 층을 플라스마 내의 탄화수소로 처리함으로써 금속-C 결합이 후-처리 단계에서 형성된다. 플라스마가 존재할 때 또는 플라스마 없이, 원하는 원소를 함유한 반응물(가령, H<sub>2</sub>S, H<sub>2</sub>Se, H<sub>2</sub>Te, PH<sub>3</sub>) 각각에 기판을 노출시킴으로써 후-처리 단계에서 금속-S, 금속-Se, 금속-Te, 및 금속-P 결합이 형성될 수 있다. 이러한 유형의 후-처리를 위해 직접 플라스마와 원거리 플라스마 모두가 이용될 수 있다.

[0095] 도 4c를 다시 참조하면, (가령, BN<sub>x</sub>, AlO<sub>x</sub>, TiO<sub>x</sub> 등을 함유한) 패시베이션 층이 절연층(401)과 구리 층(405) 위에 존재하고 있음을 확인할 수 있다. 변화되지 않은 도편트 소스를 함유한 얇은 층(408)이 구리 배선과 패시베이션 층 물질층 사이에 존재한다.

[0096] 패시베이션 층이 형성된 후에, 공정(309)에서, 변화되지 않은 소스 층으로부터의 활성 성분(도편트)이 구리로 확산되거나 구리와 반응할 수 있고 구리 층 내에 보호 캡을 형성할 수 있다. 이것이 도 4c에 도시된 구조물에서 화살표에 의해 나타나 있다. 결과적 구조물이 도 4d에 도시되며, 여기서 보호 캡(407)이 구래 배선의 상부 내에 형성되어 있다. 이러한 예시에서, 소스 층(408)으로부터의 도편트가 온전히 구리 배선으로 이동(migration)되었

다. 그 밖의 다른 실시예에서, 도편트의 일부가 소스 층 내에 남아있을 수 있다. 그 밖의 다른 실시예에서, 변화되지 않은 소스 층으로 구리가 확산됨과 동시에 도편트가 구리 배선으로 확산될 수 있다. 후자의 두 경우에서, (도 2c에서 도시되었던 바와 같이) 처음에 제공된 구리 배선 내에 그리고 구리 배선 위에 보호 캡이 존재할 수 있다.

[0097] 보호 캡의 형성은 다양한 조건 하에서 발생할 수 있는데, 상기 조건은 변화되지 않은 소스 층에 존재하는 특정 도편트 소스에 의해 좌우될 수 있다. 일부 실시예에서, 소스 층 내에 존재하는 도편트-함유 물질이 구리로 즉시 확산되지 않거나 구리와 즉시 반응하지 않을 수 있다. 이러한 실시예에서, 예를 들어 기판을 고온에 노출시킴으로써 도편트가 먼저 생성될 수 있다. 그 밖의 다른 실시예에서, 기판을 가열함으로써 도편트의 확산 및/또는 도편트의 반응 또한 촉진된다. 일부 실시예에서, 기판을 고온에 노출시키는 시간과 노출 온도 자체를 조절함으로써 보호 캡의 두께가 조절될 수 있다. 일부 실시예에서, 미리 정해진 시간 기간 동안(가령, 약 0.25 내지 60분 동안) 약 100°C 이상의 온도까지 기판을 가열함으로써 보호 캡의 형성이 촉진된다.

[0098] 보호 캡 형성시, 공정(311)에서, 도핑되었거나 도핑되지 않은 실리콘 탄화물 층이 증착된다. 결과적 구조물이 도 4e에 도시된다. 구리 배선과 절연막 영역 위의 패시베이션 층(409)의 상부에 실리콘 탄화물 층(411)이 증착된다. 실리콘 탄화물 층이 에칭 저지층 또는 절연막 확산 장벽층의 역할을 하고, 통상적으로 약 100 내지 500Å의 두께로 증착된다. 예를 들어, 플라스마 방전에서 실리콘-함유 및 탄소-함유 전구체에 기판을 노출시킴으로써 CVD에 의해(바람직하게는 PECVD에 의해) 실리콘 탄화물 층이 증착된다. 예를 들어, 실란, 알킬실란, 및 탄화수소가 전구체로서 이용될 수 있다. 도핑된 실리콘 탄화물이 증착되는 때, 도편트-함유 전구체가 공정 챔버 내로 추가로 주입된다. 예를 들어, 산소-함유 실리콘 탄화물의 증착 동안 CO<sub>2</sub>, O<sub>2</sub> 또는 N<sub>2</sub>O가 첨가될 수 있고, B<sub>2</sub>H<sub>6</sub>가 첨가되어 봉소-도핑된 실리콘 탄화물을 증착할 수 있으며, NH<sub>3</sub> 및 N<sub>2</sub>가 첨가되어 질소-도핑된 실리콘 탄화물을 증착할 수 있다. 그 밖의 다른 실시예에서, 도핑되었거나 도핑되지 않은 실리콘 질화물이 패시베이션 층의 상부에 증착되어 에칭 저지층 또는 확산 장벽층의 역할을 할 수 있다. 일부 실시예에서, 절연막 확산 장벽층의 증착이 (소스 층과 패시베이션의 형성을 포함한) 캡핑 층의 형성에 이용되는 온도보다 높은 온도에서 수행된다. 예를 들어, 일부 실시예에서, 350°C 이하의 온도에서(예를 들어, 약 200 내지 350°C에서) 보호 캡의 형성이 구현되고, 약 350°C 이상의 온도에서(예를 들어, 375 내지 450°C에서) 확산 장벽 증착이 수행된다.

[0099] 일부 경우에서, 패시베이션 층 자체가 확산 장벽 또는 에칭 저지의 역할을 하기에 적합한 속성을 가질 수 있기 때문에, 절연막 확산 장벽 또는 에칭 저지층은 선택 사항이다. 예를 들어, 특정 금속 산화물을 함유한 패시베이션 층이 확산 장벽층의 역할을 할 수 있고, 이로 인해 별개의 실리콘 탄화물 층의 증착에 대한 필요를 제거할 수 있다.

[0100] 도 3에 도시된 공정이 후속 공정(313)으로 나아가며, 상기 공정(313)에서, 충간 절연막(가령, 실리콘 이산화물, 유기실리콘 유리, 다공성 유기 절연막 등)가 증착된다. 확산 장벽 또는 에칭 저지층 위에(가령, 실리콘 탄화물 층 위에) 절연막이 증착되고, 또는 패시베이션 물질이 확산 장벽의 역할을 하기에 적절한 속성을 가진 경우 패시베이션 층 위에 절연막이 바로 증착된다. 절연막은 PECVD에 의해 또는 스핀-온(spin-on) 법에 의해 증착될 수 있고, 통상적으로 약 3,000 내지 10,000Å 사이의 두께로 증착된다. 그 후, 도 1c 내지 도 1e에 도시된 바와 같이 다마신 공정이 추가로 뒤따를 수 있다.

[0101] 도 3에 도시된 흐름도에 의해 나타나는 공정은 오직 예시적인 것이고 상기 공정의 다양한 변형 형태가 구현될 수 있음이 이해된다. 예를 들어, 도 3에 도시된 다양한 공정들이 서로 다른 순서로 수행될 수 있다. 구체적으로, 구리 층으로의 활성 성분(도편트)의 주입이 공정 중 서로 다른 시간에 수행될 수 있다. 일부 실시예에서, 에칭 저지층 또는 확산 장벽층이 증착된 후에 도편트의 생성 및 확산이 시작될 수 있다. 일부 실시예에서, ILD 층이 형성된 이후, 후-처리에서 도편트의 확산이 촉진된다. 종종 이러한 공정은 약 100°C 이상의 온도로 기판을 가열시킴으로써 수행된다. 그 밖의 다른 실시예에서, 소스 층이 패시베이션되기 전에 활성 성분(도편트)이 구리로 확산되거나 구리와 반응할 수 있다. 이러한 실시예에서, 변화되지 않은 소스 층과 구리의 접촉 시간을 조절함으로써 및/또는 공정 온도를 조절함으로써, 주입된 도편트의 양이 조절될 수 있다.

[0102] 일부 실시예에서, 구리 배선 위에 존재하는 소스 층을 부분적으로 아니라 완전하게 패시베이션하여 구리 배선으로 도편트 원소가 확산되는 것을 실질적으로 방지함으로써, 도 3a에 도시된 공정이 수정된다. 이러한 수정 형태는, 개선된 전자이동 성능을 달성할 수 있으면서도 도편트 확산으로 인한 인터커넥트 저항성의 증가가 최소화될 수 있기 때문에 일부 경우에서 유리하다.

[0103] 공정의 또 다른 실시예가 도 3b에 도시된 공정 흐름도에 의해 도시된다. 상기 공정은 산화물이 없는 구리 표면

위에 알루미늄-함유 소스 층의 고온 증착을 이용한다. 상기 공정은, 구리 배선의 패턴을 갖는 부분 제작된 반도체 소자를 절연막에 제공함으로써 공정(301)에서 시작된다. 예를 들어, 기판(가령, 도 4a에 도시된 기판)이 사용될 수 있다. 일부 실시예에서, ULK 절연막(가령, 2.8 이하의 유전 상수를 갖는 다공성 및 유기 절연막)의 층에 구리 배선이 내장된다. 도 3b에 기술된 실시예에서, 산화물이 없는 구리 표면을 제공하여 구리 산화물과 유기알루미늄 전구체 사이의 반응을 방지하는 것이 매우 중요하다. 구리 산화물의 얇은 층이 알루미늄 증착 수단을 변경할 것이라 하더라도, 알루미늄 산화물이 형성될 수 있다. 도 3b에 도시된 실시예에서, 구리 표면 위에 이러한 즉각적인 알루미늄 산화물 형성은 요구되지 않는다.

[0104] 구리 산화물을 제거하기 위하여, 공정(303)에서 기판이 사전-세척된다. 이러한 사전-세척은 구리 산화물이 구리 표면으로부터 완전히 제거되는 방식으로 제어된다. 이러한 제어는 적절한 사전-세척 지속 시간과 공정 조건을 선택함으로써 달성될 수 있다. 이는 도 3a와 관련해 이전에 기술되었던 바와 같이, 직접 플라스마 처리, 원거리 플라스마 처리, UV 처리, 또는 열 처리에 의해 사전-세척이 수행될 수 있다. 연약한 ULK 절연막이 사용될 때, 일부 실시예에서 직접 플라스마의 부재 하에서 사전-처리가 이용된다.

[0105] 산화물-프리 구리 층이 획득된 이후, 공정(305)에 도시된 바와 같이, 부분 제작된 소자가 약 350°C 이상(가령, 약 400°C 이상)의 기판 온도에서 유기알루미늄 반응물과 접촉하여 알루미늄-함유 층을 형성할 수 있다. 유의하게, 더 낮은 온도에서는, 산화물-프리 구리 표면 위에 알루미늄-함유 층의 증착이 적절한 속도로 발생하지 않을 것이다. 다양한 유기알루미늄 반응물이 이용될 수 있는데, 일부 실시예에서는, 그 중에서도 트리알킬알루미늄, 그리고 특히 트리메틸알루미늄이 선호된다. 적합한 반응물의 예시에는 트리메틸알루미늄, 디메틸알루미늄 수소화물, 트리에틸알루미늄, 트리이소부틸알루미늄, 및 트리스(디에틸아미노)알루미늄(*tris(diethylamino)aluminum*)으로 구성된 그룹으로부터 선택된 전구체가 포함된다. 플라스마의 부재 하에서 CVD 챔버에서 반응물이 기판과 접촉하여, 노출된 절연막과 구리 표면 둘 모두의 위에 통상적으로 알루미늄-함유 층을 형성한다. 예를 들어, 반응물 유량(*flow rate*)과 기판 온도를 조절함으로써 층의 두께가 조절될 수 있다. 통상적으로 절연막 위에 증착된 층은 (절연막에 존재하는 산화 종(*oxidizing species*)으로 인해) 증착시 자발적으로 산화되어 Al-O 결합을 갖는 비-전도성 층을 형성할 수 있다. 알루미늄-함유 층이 절연막 위에서 완전히 산화되지 않은 경우에서, 절연막 위의 모든 전도성 물질을 비-전도성 형태로 변화시켜 인터커넥트 간 단락을 방지하는 후-처리 단계에서 상기 알루미늄-함유 층이 변화된다. 절연막 위에 증착된 알루미늄-함유 층이 증착시 즉시 자발적으로 산화되는지 여부와 무관하게, 구리 위에 존재하는 알루미늄-함유 층의 일부분 또는 전부를 부동성(*immobile*) 화합물(일부 실시예에서 비-전도성일 수 있는 화합물)로 변화시키기 위하여 후-처리 단계가 이용될 수 있다.

[0106] 공정(307)은 두 개의 후-처리 옵션을 제공한다. 제 1 실시예에서, 구리 위에 존재하는 알루미늄-함유 층의 상부 부분만이 변화되어 패시베이션 층을 형성하고, 여기서 변화되지 않은 층의 부분은 구리의 층과 접촉 상태로 남아 있으며, 공정(309)에서, 변화되지 않은 부분으로부터의 알루미늄이 구리로 확산된다. 대안적 실시예에서, 구리 위에 존재하는 알루미늄-함유 층 전부가 변화되어 부동성 화합물을 형성하고, 이로써 구리 배선으로의 알루미늄의 확산이 실질적으로 방지된다. 구리로 알루미늄의 과도한 확산으로 인해 인터커넥트 저항성이 원치 않게 증가되기 때문에, 그리고 구리 위에 얇은 부동성 캡(가령, Al-O 또는 Al-N 결합)의 형성이 절연막에 대한 부착력을 개선하기 때문에, 일부 실시예에서, 알루미늄 확산을 최소화하거나 완전히 회피하는 것이 바람직하다

[0107] 도 3a와 관련해 기술되었던 바와 같이, 직접 플라스마 처리, 원거리 플라스마 처리, UV 처리, 및 상승된 온도 또는 실온에서의 열(플라스마-프리) 처리를 포함한 다양한 후-처리가 이용될 수 있다.

[0108] 일 실시예에서, (실온 또는 상승된 온도에서) 플라스마-프리 산화 처리를 이용하여 구리 표면 위에 Al-O 결합을 갖는 층을 형성할 수 있다. 예를 들어, (유기알루미늄 반응물 처리 후에) 플라스마의 부재 하에서 알루미늄-함유 층을 갖는 기판이 산소-함유 반응물(가령, O<sub>2</sub>, O<sub>3</sub>, N<sub>2</sub>O, H<sub>2</sub>O 또는 CO<sub>2</sub>)과 접촉하여 부동성 Al-O 함유 물질을 형성할 수 있다.

[0109] 또 다른 실시예에서, (실온 또는 상승된 온도에서) 플라스마-프리 질화 처리를 이용하여 구리 표면 위에 Al-N 결합을 갖는 층을 형성할 수 있다. 예를 들어, (유기알루미늄 반응물 처리 후에) 플라스마의 부재 하에서 알루미늄-함유 층이 산소-함유 반응물(가령, 암모니아)과 접촉할 수 있다.

[0110] (UV 및 열 처리를 포함한) 플라스마-프리 후-처리는, 기판이 기계적으로 약한 ULK 절연막을 포함할 때 특히 선호되며, 이로 인해 절연막 손상을 최소화할 수 있다.

[0111] 후-처리 공정이 완료된 후, 공정(311 및 313)에서, 도 3a와 관련해 기술된 바와 같이 절연막 확산 장벽 층 증착

및 충간 절연막 증착이 수행된다.

[0112] 위에 기술된 방법들은, 인터커넥트에, 조절 가능한 저항성과 개선된 전자이동 특성을 제공할 수 있다. 이러한 방법들에 의해 형성된 보호 캡핑 층의 두께는 약 10Å 내지 10,000Å 범위를 가질 수 있다. 상기 방법들이 약 10 내지 100Å의 범위, 특히 10 내지 60Å 범위의 캡핑 층의 두께에 대한 조절 가능성을 제공하는 점이 특히 유리하다. 약 10 내지 60Å 두께 범위의 캡핑 필름은, 인터커넥트에, 1% 이하 및 3% 이하의 특히 작은 저항성 시프트를 제공하며, 이러한 작은 저항성 시프트가 현재 IC 산업에서 요구되는 것이다.

### [0113] 장치

[0114] 일반적으로, 임의의 유형의 장치에서 보호 캡 형성이 수행될 수 있는데, 이러한 임의의 유형의 장치는 휘발성 전구체의 주입을 가능하게 하고 반응 조건(가령, 챔버 온도, 전구체 유량, 노출 시간 등)에 대한 조절 가능성을 제공하도록 구성된다. 부주의에 의한 기판의 산화와 오염을 방지하기 위하여, 기판을 대기 환경에 노출시키지 않고 공정(301 내지 311)을 수행하는 것이 종종 선호된다. 일 실시예에서, 공정(301 내지 311)은 진공 상태를 해소하지 않고 하나의 모듈에서 연속하여 수행된다. 일부 실시예에서, 공정(301 내지 311)은 하나의 챔버 내에 다수의 스테이션을 갖거나 다수의 챔버를 갖는 하나의 CVD(바람직하게는 PECVD) 장치에서 수행된다. 캘리포니아, 산 호세의 노벨러스 시스템즈로부터 구입 가능한 VECTOR™ PECVD 장치가 적합한 장치의 예시이다.

[0115] 예시적 장치는 하나 이상의 웨이퍼를 하우징하고 웨이퍼 처리에 적합한 하나 이상의 챔버 또는 "반응기"를 포함할 것이다. 각각의 챔버가 처리를 위한 하나 이상의 웨이퍼를 하우징할 수 있다. 하나 이상의 챔버가 웨이퍼를 지정 위치에 유지시킨다(상기 위치에서 가령 회전, 진동, 또는 교반(agitation)과 같은 움직임이 있거나 없을 수 있다). 일 실시예에서, 소스 충과 에칭 저지층 증착을 겪는 웨이퍼가 공정 동안 반응기 내의 하나의 스테이션에서 또 다른 스테이션으로 운반된다. 공정 중에, 지지부, 웨이퍼 척, 및/또는 그 밖의 웨이퍼 고정 장치에 의해 각각의 웨이퍼가 제 위치에 고정된다. 웨이퍼가 가열되는 특정한 공정들에 있어서, 장치가 히팅 플레이트(heating plate)와 같은 히터를 포함할 수 있다. 본 발명의 바람직한 실시예에서, PECVD 시스템이 이용될 수 있다. 좀 더 바람직한 실시예에서, PECVD 시스템이 LF RF 전원을 포함한다.

[0116] 도 5는 본 발명을 구현하기 위해 배열된 다양한 반응기 컴포넌트를 도시하는 간단한 블록도이다. 도시된 바와 같이, 반응기(500)가 공정 챔버(524)를 포함하고, 상기 공정 챔버는, 반응기의 그 밖의 다른 컴포넌트들을 둘러싸고, 지면에 놓인 히터 블록(520)과 함께 작동하는 샤워헤드(514)를 포함하는 커페시터 유형 시스템에 의해 생성되는 플라스마를 보유하는 기능을 한다. 고주파 RF 발생기(502)와 저주파 RF 발생기(504)가 정합 네트워크(506)에 연결되고, 차례로 상기 정합 네트워크가 샤워헤드(514)에 연결된다.

[0117] 반응기 내에서, 웨이퍼 지지부(518)가 기판(516)을 지지한다. 상기 지지부는 통상적으로 척(chuck), 포크(fork), 또는 리프트 핀을 포함하여 증착 반응 동안 또는 증착 반응들 사이에서 기판을 고정 및 운반한다. 척은 정전 척(electrostatic chuck), 기계 척(mechanical chuck), 또는 산업 및/또는 연구에서 이용 가능한 그 밖의 다른 유형의 척일 수 있다.

[0118] 주입구(512)를 통해 공정 가스들이 주입된다. 다수의 소스 가스 라인(510)이 다기관(manifold)(508)에 연결된다. 가스들은 미리 혼합될 수도 있고 아닐 수도 있다. 사전-세척 동안, 소스 충의 형성 동안, 패시베이션 충의 형성 동안, 그리고 공정의 도핑 과정 동안 정확한 가스를 보장하기 위하여 적절한 밸브 및 유량 조절 수단이 이용된다. 화학 전구체가 액체 형태로 운송되는 경우에서, 액체 흐름 제어 수단이 이용된다. 그 후, 상기 액체는, 증착 챔버에 도달하기 전 상기 액체의 기화점 이상으로 가열된 다기관 안에서 액체의 운송 중 기화되고 그 밖의 다른 공정 가스들과 혼합된다.

[0119] 공정 가스들이 주입구(522)를 통해 챔버(500)를 빠져나간다. 진공 펌프(526)(가령, 하나 또는 두 개 스테이지의 기계적 건식 펌프 및/또는 터보분자 펌프(turbomolecular pump))가 통상적으로 공정 가스를 배기하고, 스로틀 밸브 또는 진자 밸브와 같은 흐름 제어 장치에 의해 조절되는 폐쇄 루프에 의해 반응기 내부를 적절하게 저압으로 유지시킨다.

[0120] 실시예들 중 하나에서, 멀티-스테이션 장치를 이용하여 캡핑 충과 확산 장벽을 형성할 수 있다. 멀티-스테이션 반응기는 하나의 챔버 환경에서 서로 다른 공정들을 동시에 구동할 수 있도록 함으로써 웨이퍼 처리의 효율성을 증가시킬 수 있다. 이러한 장치의 일 예시가 도 6에 도시된다. 평면도의 도식적 표현이 나타나 있다. 장치 챔버(601)가 네 개의 스테이션(603 내지 609)과 두 개의 로드락(loadlock), 입구 로드락(619)과 출구 로드락(617)을 포함한다. 그 밖의 다른 실시예에서, 웨이퍼의 입구와 출구 모두에 있어서 단일 로드락이 이용될 수 있다. 일반적으로, 멀티-스테이션 장치의 단일 챔버 내에 임의의 개수의 스테이션이 가능하다. 기판 웨이퍼를 로드 및

언로드하는데 스테이션(603)이 이용된다. 스테이션(603 내지 609)은 동일하거나 서로 다른 기능들을 가질 수 있다. 예를 들어, 스테이션들 중 일부가 캡핑 층의 형성에 전용으로 이용될 수 있고, 그 밖의 다른 스테이션들이 절연막 확산 장벽 필름을 증착하는데 이용될 수 있다. 더욱이, 일부 스테이션은 구리 산화물 환원에 전용으로 이용될 수 있다.

[0121] 실시예들 중 하나에서, 개개의 스테이션이 별개의 공정 조건 하에서 동작할 수 있고, 서로 실질적으로 고립될 수 있다. 예를 들어, 하나의 스테이션이 하나의 온도 체제 하에서 동작할 수 있고 또 다른 챔버가 이와는 다른 온도 체제 하에서 동작할 수 있다.

[0122] 일 실시예에서, 사전-세척 공정, 소스 층의 증착, 및 패시베이션 층의 형성이 하나의 바람직한 온도 체제에서 수행되고, 멀티-스테이션 장치의 하나의 스테이션에서 실행된다. 일부 실시예에서 절연막 확산 장벽의 증착은 서로 다른 온도 체제를 요구할 수 있고 서로 다른 스테이션에서 실행될 수 있다. 일부 실시예에서, 사전-처리, 소스 층의 형성, 패시베이션, 및 도펀트-함유 캡의 형성을 포함한 전체 캡핑 공정이 단일 스테이션 또는 멀티-스테이션 장치의 하나의 스테이션에서 수행된다. 일부 실시예에서, 절연막 확산 장벽의 증착, 캡핑 공정과 동일한 스테이션에서 수행될 수도 있다. 일부 경우에서, 입구 로드락(619)을 이용하여 웨이퍼를 사전-세척 또는 사전-처리할 수 있다. 이는, 예를 들어 화학적 환원에 의한 산화물 제거를 수반할 수 있다.

[0123] 일 예시에서, 스테이션(603)이 사전-세척과, (전구체 층과 패시베이션 층으로부터) 캡핑 층의 형성에 전용으로 이용될 수 있다. 스테이션(603)이 약 200 내지 400°C의 온도 범위에서 동작할 수 있고, 상기 온도 범위가 캡핑 공정과 사전-세척 공정 모두에 대한 일부 실시예에서 선호된다. 스테이션(605, 607 및 609)에서 실리콘 탄화물과 같은 절연막 확산 장벽 물질의 증착이 약 350 내지 400°C에서 수행될 수 있고, 이러한 온도 범위가 일부 실리콘 탄화물 증착 공정에 따른 바람직한 공정 온도이다.

[0124] 유리하게, 사전-세척, 소스 층의 증착, 패시베이션, 및 도펀트의 주입이 일부 실시예에서 유사한 조건을 필요로 할 수 있고, 하나의 스테이션(603)에서 수행될 수 있다.

[0125] 위에서 기술된 실시예에 따라, 스테이션(603)이 사전-세척 스테이션 및 보호 캡 형성 스테이션이다. 스테이션(605, 607 및 609) 모두가 절연막 확산 장벽 층의 증착을 위해 동작할 수 있다. 인덱스 판(611)을 이용하여 지지부로부터 기판을 들어올려 그 다음 처리 스테이션에서 상기 기판을 정확하게 위치시킬 수 있다. 웨이퍼 기판이 스테이션(603)에 로드되어 그곳에서 임의의 처리(가령, 전구체 층 증착과 패시베이션을 포함한 사전-세척 및 캡핑)를 받은 이후, 상기 웨이퍼 기판이 스테이션(605)으로 안내되어 (소스 층 증착과 패시베이션을 포함한) 캡핑 및/또는 절연막 증착이 수행된다. 그 후, 상기 웨이퍼가 스테이션(607)으로 운반되어 확산 장벽 절연막의 증착이 시작되거나 계속된다. 더 나아가 상기 기판이 스테이션(609)으로 안내되어 장벽 절연막의 추가 증착이 수행되고, 그 후 상기 기판이 스테이션(603)으로 안내되어, 상기 기판이 언로드되고 모듈이 새로운 웨이퍼로 변경된다. 정상 동작 동안, 별개의 기판이 각각의 스테이션을 차지하고, 공정이 반복되는 각각의 시간에 기판이 새로운 스테이션으로 운반된다. 따라서, 네 개의 스테이션(603, 605, 607, 및 609)을 갖는 장치가 네 개 웨이퍼의 동시 처리가 가능하게 하며, 여기서 하나 이상의 스테이션이 그 밖의 다른 스테이션에서 수행되는 공정들과 다른 공정을 수행한다. 대안적으로, 특정 스테이션을 특정한 층의 증착에 전용하여 이용하지 않고 네 개의 웨이퍼가 네 개 스테이션 모두에서 동일한 공정의 대상이 될 수 있다.

[0126] 스테이션-대-스테이션의 몇몇 구체적 예시가 지금부터 제공될 것이다. 제 1 예시에서, 입구 로드락이 사전-처리(가령, 구리 산화물의 환원)를 수행한다. 그 후, 장치의 제 1 스테이션(가령, 스테이션(603) 또는 연속하여 배열된 복수의 제 1 스테이션)이 (예를 들어, TMA와 같은 전구체에 노출시킴으로써) 캡핑 층을 형성한다. 그 후, 제 2 스테이션(가령, 도 6의 스테이션)이 패시베이션과 같은 후-처리(가령, 본원에 기술된 바와 같이 질소, 암모니아, 및/또는 수소에의 노출)를 수행한다. 그 후, 장치 내의 나머지 스테이션들(가령, 스테이션(607 및 609))에서 확산 장벽 형성을 수행한다.

[0127] 또 다른 예시에서, 제 1 스테이션(가령, 스테이션(603))이 사전 처리를 수행하고, 제 2 스테이션(가령, 스테이션(605) 또는 일련의 연속적 스테이션들)이 캡핑 층 형성과 후-처리(가령, 패시베이션) 둘 모두를 수행하며, 나머지 스테이션들이 절연막 확산 장벽 층 증착을 수행한다. 또 다른 예시에서, 제 1 스테이션이 사전-처리, 캡핑 층 증착, 및 후-처리를 수행한다. 나머지 스테이션들이 확산 장벽 형성을 수행한다.

[0128] 공정 조건과 공정 흐름 자체가 조절 유닛(613)에 의해 조절될 수 있고, 상기 조절 유닛은 특정 공정 변수(가령, HF 및 LF 전력, 가스 유량과 시간, 온도, 압력, 등)를 모니터링, 유지, 및/또는 조절하기 위한 프로그램 명령어들을 포함한다. 예를 들어, 소스 층 증착과 패시베이션을 위한 보란 및 암모니아의 유량을 특정하는 명령어들이

포함될 수 있다. 명령어는, 위에 기술된 방법들에 따라, 공정들을 수행하기 위한 파라미터들 전부를 특정할 수 있다. 예를 들어, 명령어가, 사전-세척, 소스 층 증착, 패시베이션 층의 형성, 구리 배선으로의 도편트 주입, 및 절연막 확산 장벽 증착을 위한 파라미터들을 포함할 수 있다. 컨트롤러가 서로 다른 장치 스테이션에 대하여 서로 다르거나 동일한 명령어를 포함할 수 있고, 이로 인해 상기 장치 스테이션이 독립적으로 또는 동기적으로 동작할 수 있다.

[0129] 멀티-스테이션 장치의 또 다른 예시가 도 7에 도시된다. 멀티-스테이션 장치(701)가, 세 개의 별개의 공정 챔버(717, 719, 및 721)에 존재하는 여섯 개의 스테이션(703, 705, 707, 709, 711, 및 713)과 각각의 챔버에 존재하는 두 개의 스테이션을 포함한다. 챔버(717, 719, 및 721)에 인접한 로봇-포함 챔버(715)가 웨이퍼를 스테이션에 로드 및 언로드하기 위한 수단을 제공한다. 컨트롤러(723)가 멀티-스테이션 장치(701)의 동작을 위한 명령어들을 제공한다. 하나의 챔버 내의 개개의 스테이션이 서로 고립되고, 동일하거나 서로 다른 공정들을 수행할 수 있다. 일 실시예에서, 두 개의 웨이퍼가 하나의 챔버(721)에 존재하는 스테이션(703 및 705)으로 동시에 운반되어, 사전-세척, 소스 층 증착, 패시베이션 층 형성, 및 구리 도핑을 포함한 동일한 공정들을 동시에 경험한다. 이러한 공정이 완료된 후, 상기 두 개의 웨이퍼가 챔버(721)에서 제거되고, 챔버(709)에 존재하는 스테이션(707 및 709)으로 동시에 삽입된다. 이러한 챔버에서, 확산 장벽 물질층이 동시에 증착된다. 그 후, 웨이퍼가 챔버(719)에서 제거되어, 챔버(717)에 존재하는 스테이션(711 및 713)으로 삽입되어 추가적 처리가 뒤 따른다. 일부 실시예에서, 보호 캡핑 층의 형성이 멀티-챔버 장치에서 수행될 수 있고, 서로 다른 서브-공정(가령, 소스 층 증착, 패시베이션, 도편트 확산)이 서로 다른 챔버에서 수행된다.

[0130] 도 6 및 도 7에 도시된 것과 같은 멀티-스테이션 도구에서 캡핑 공정이 구현될 수 있는 다수의 방법이 존재한다. 일반적으로, 기술된 공정은 실질적인 소스-소비 기판 처리를 필요로 하지 않는 다마신 흐름으로 쉽게 통합되고, 절연막 확산 장벽 증착과 동일한 장치에서 수행될 수 있다. 더욱이, 조절 가능한 도편트의 방출에 의한 저항성 조절이 특히 유리하다. 기술된 방법은 또한, 구리와 절연막 확산 장벽 사이의 개선된 부착력을 갖는 인터커넥트를 형성하는데에도 유용하다.

[0131] 기술된 방법들의 몇몇 실시예가 구체적 예시로서 지금부터 기술될 것이다.

## 실현예

[0133] 봉소-도핑된 보호 캡을 갖는 구리 인터커넥트와 봉소 및 질소를 함유한 패시베이션 층의 제작이 실험예와 관련해 예시될 것이다.

[0134] 기술된 예시에서, 플라스마 사전-세척 동작에 의해 공정이 시작된다. 울트라 로우-k 절연막( $k = 2.5; 5,000\text{\AA}$  두께)에서 구리 배선의 노출 패턴을 갖는 부분 제작된 반도체 소자가 CMP 공정 이후에 획득되었고, PECVD VECTOR<sup>TM</sup> 장치의 공정 챔버에 배치되었다. 전체 캡핑 공정이 네 개-스테이션 장치 중 하나의 스테이션에서 수행되었다. 첫째, 기판을  $350^\circ\text{C}$ 로 사전-가열하였고,  $4,000\text{sccm}$ 의 유량으로  $\text{H}_2$ 를 공정 챔버 내에 주입하였다.  $\text{H}_2$ 는  $4\text{Torr}$ 의 압력에서 0초 내지 30초의 공정 시간 동안 흘러들어갔다. 30초의 공정 시간에서, HF RF 플라스마에 고도로 열을 가했고 45초의 공정 시간까지  $1.23 \text{ W/cm}^2$ 의 전력으로 유지하였다. 기판을  $\text{H}_2$  플라스마를 이용해 사전-세척한 후,  $\text{H}_2$  흐름과 플라스마 전원을 끼고,  $\text{B}_2\text{H}_6$ 를 공정 챔버 내에 주입하여 아르곤과 혼합하였다. 혼합물에서  $\text{B}_2\text{H}_6$ 의 농도가 약 5 부피%였고,  $2400\text{sccm}$  유량으로 주입되는  $\text{N}_2$ 와 함께 상기 혼합물을 약  $3600\text{sccm}$ 의 유량으로 주입하였다. 이러한 가스들이 45초 내지 85초의 공정 시간 동안 흘러들어갔고, 상기 시간 동안  $\text{BH}_x$ 를 함유한 소스 층이 기판 위에 증착되었다. 약  $350^\circ\text{C}$ 의 온도 및 약  $2.3\text{Torr}$ 의 압력에서 증착을 수행했다. 구리의 상부에 증착되는 소스 층의 두께가 약  $215\text{\AA}$ 으로 추정되고, 절연막의 상부에 증착되는 소스 층의 두께가 약  $159\text{\AA}$ 으로 추정된다. 소스  $\text{BH}_x$  층이 증착된 후, 보란 흐름을 중지하였고, 상기 층이 패시베이션되어  $(\text{BNH})_x$ 를 형성하였다. 패시베이션은 85초와 90초의 공정 시간 사이에 수행되었고, 유량  $2800\text{sccm}$ 의  $\text{N}_2$ 와 함께 약  $7000\text{sccm}$  유량의  $\text{NH}_3$  주입이 수반되었다.  $0.80 \text{ W/cm}^2$ 의 전력 레벨의 HF 컴포넌트와  $0.37 \text{ W/cm}^2$ 의 전력 레벨의 LF 컴포넌트를 갖는 플라스마에 고도의 열을 가했고, 90초에서 96초까지 유지하였다. 약  $350^\circ\text{C}$ 의 온도와 약  $2.3\text{Torr}$ 의 압력에서 패시베이션을 수행하였다. 절연막 위에 존재하는  $\text{BH}_x$  층의 전체 두께가  $(\text{BNH})_x$ 로 변화되었고, 구리 위에 존재하는 소스 층 두께의 약 25%가  $(\text{BNH})_x$ 로 변화되었다.  $(\text{BNH})_x$  층은 나중에 FT IR 분광계를 이용해 분석하였다.  $3430 \text{ cm}^{-1}$

( $\nu_{N-H}$ ),  $2560\text{ cm}^{-1}$  ( $\nu_{B-H}$ ), and  $1375\text{ cm}^{-1}$  ( $\nu_{B-N}$ )에서의 피크가 IR 스펙트럼에서 관측되었다.

[0135] 붕소가 구리 배선으로 확산되어 붕소-도핑된 구리 층을 형성하였다. 붕소 확산은 소스 층의 상부 부분이 질화(페시베이션)되기 전에 그리고 후에 발생할 수 있다. 구리 배선 내에 존재하는 붕소-도핑된 캡의 두께가 약 25 nm(75Å)로 추정되었다.

[0136]  $350^{\circ}\text{C}$ 의 온도에서 전체 캡핑 공정이 단일 스테이션에서 수행되었다. 그 이후에, 플라스마 상태의 공정 가스로서 테트라메틸실란, 암모니아, 및 질소를 이용하여  $350^{\circ}\text{C}$ 에서 PECVD 장치의 세 개의 서로 다른 스테이션에서  $\text{Si}_x\text{C}_y\text{N}_z$  확산 장벽 층(약 500Å)이 기판 위에 증착되었다. 이러한 세 개의 스테이션 중 각각에서, 탄화물 층 두께의 3분의 1이 증착되었다.

[0137] 4점점 굽힘 부착력 시험법(four-point bending adhesion test)을 이용하여 붕소-함유 캡을 갖거나 갖지 않는  $\text{Cu}(5,000\text{Å})-\text{Si}_x\text{C}_y\text{N}_z(500\text{Å})$  샌드위치에 대한 부착 에너지를 측정하였다. B-도핑된 캡을 갖지 않는 종래의 샌드위치 구조에 대해 획득된 오직  $15.3\text{ J/m}^2$ 의 부착 에너지와 비교할 때,  $28.4\text{ J/m}^2$ 의 더 높은 부착 에너지가 전술된 방법에 의해 획득된 샌드위치 구조에서 관측되었다. 개선된 부착력이 통상적으로 개선된 전자이동 성능과 상관된다는 점이 알려져 있다.

[0138] B-도핑된 보호 캡과  $(\text{BNH})_x$  페시베이션 층을 가진 구조에 대하여 누설 전류와 포화된 커페시턴스가 측정되었다. 이러한 파라미터는 기술된 캡핑 절차에 의해 실질적으로 영향을 받지 않음이 관찰되었다.

[0139] 다양한 세부 사항이 명확성을 위해 생략되었으나, 다양한 설계상 대안예가 구현될 수 있다. 따라서, 본 예시들은 예시적인 것으로 고려되어야 하고 제한적인 것으로 고려되어서는 안되며, 본 발명은 본원에 제시된 세부 사항에 한정되지 않고 청구항의 범위 내에서 수정될 수 있다.

## 도면

### 도면 1a

### 도면 1b

도면1c

도면1d

도면1e

도면2a

도면2b

도면2c

## 도면3a

## 도면3b

## 도면4a

도면4b

도면4c

도면4d

도면4e

도면5

도면6

도면7