(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7340333号**

**(P7340333)**

(45)発行日 令和5年9月7日(2023.9.7)

(24)登録日 令和5年8月30日(2023.8.30)

(51)国際特許分類

F I

|         |                  |         |        |

|---------|------------------|---------|--------|

| H 0 4 N | 19/172 (2014.01) | H 0 4 N | 19/172 |

| H 0 4 N | 19/132 (2014.01) | H 0 4 N | 19/132 |

| H 0 4 N | 19/156 (2014.01) | H 0 4 N | 19/156 |

| H 0 4 N | 19/43 (2014.01)  | H 0 4 N | 19/43  |

| H 0 4 N | 19/46 (2014.01)  | H 0 4 N | 19/46  |

請求項の数 20 (全11頁)

|                   |                             |

|-------------------|-----------------------------|

| (21)出願番号          | 特願2018-528328(P2018-528328) |

| (86)(22)出願日       | 平成28年12月20日(2016.12.20)     |

| (65)公表番号          | 特表2019-505110(P2019-505110) |

|                   | A)                          |

| (43)公表日           | 平成31年2月21日(2019.2.21)       |

| (86)国際出願番号        | PCT/EP2016/081962           |

| (87)国際公開番号        | WO2017/108815               |

| (87)国際公開日         | 平成29年6月29日(2017.6.29)       |

| 審査請求日             | 令和1年12月11日(2019.12.11)      |

| 審判番号              | 不服2022-6100(P2022-6100/J1)  |

| 審判請求日             | 令和4年4月22日(2022.4.22)        |

| (31)優先権主張番号       | 15307088.3                  |

| (32)優先日           | 平成27年12月21日(2015.12.21)     |

| (33)優先権主張国・地域又は機関 | 歐州特許庁(EP)                   |

|          |                                                                                                               |

|----------|---------------------------------------------------------------------------------------------------------------|

| (73)特許権者 | 518338149<br>インターデジタル ヴイシー ホールディングス, インコーポレイテッド<br>アメリカ合衆国, デラウェア州 19809, ウィルミントン, ベルビュー パークウェイ 200, スイート 300 |

| (74)代理人  | 100079108<br>弁理士 稲葉 良幸                                                                                        |

| (74)代理人  | 100109346<br>弁理士 大貫 敏史                                                                                        |

| (74)代理人  | 100117189<br>弁理士 江口 昭彦                                                                                        |

| (74)代理人  | 100134120<br>弁理士 内藤 和彦                                                                                        |

| (74)代理人  | 100108213                                                                                                     |

最終頁に続く

(54)【発明の名称】 複合型の適応的解像度及び内部ビット深度増加コーディングのための方法及び機器

**(57)【特許請求の範囲】****【請求項1】**

適応的解像度コーディングの方法であって、

現在のブロックに対して動き補償を行うことと組み合わせて、参照ブロックをサイズ変更することと、

前記サイズ変更後のサイズを有する復号済みブロックのビット深度をサイズ変更前よりも高い精度に増加することであって、ビット深度の増加は解像度の変化がなくても領域ごとに行われる、増加することと、

前記ビット深度を増加した前記復号済みブロックを記憶することと、

元のビット深度精度を使用して他の復号済みピクチャからのブロックを記憶することと、を含む、方法。

**【請求項2】**

適応的解像度コーディングの機器であって、

現在のブロックに対して動き補償を行うことと組み合わせて、参照ブロックをサイズ変更するためのプロセッサと、

前記サイズ変更後のサイズを有する復号済みブロックのビット深度をサイズ変更前よりも優れた精度に増加するためのシフト回路であって、ビット深度の増加は解像度の変化がなくても領域ごとに行われる、シフト回路と、

前記ビット深度を増加した前記復号済みブロックを記憶するためのメモリと、

元のビット深度精度を使用して他の復号済みピクチャからのブロックを記憶するための

メモリと、を含む、機器。

**【請求項 3】**

エンコーダによって実装される、請求項 1 に記載の方法。

**【請求項 4】**

デコーダによって実装される、請求項 1 に記載の方法。

**【請求項 5】**

ビットストリーム内でビット深度情報がシグナリングされる、請求項 1 に記載の方法。

**【請求項 6】**

サイズ変更済み画像のビット深度の増加が低解像度の画像についてのみ行われる、請求項 1 に記載の方法。

10

**【請求項 7】**

ビット深度の増加がピクチャごとに行われる、請求項 1 に記載の方法。

**【請求項 8】**

参照画像のビット深度が前記参照画像内の領域ごとに異なる、請求項 1 に記載の方法。

**【請求項 9】**

サイズ変更済みピクチャのビット深度が等しいことを示し、前記ビット深度をコーディングするシーケンスヘッダ内のフラグをコーディングすることを更に含む請求項 1 に記載の方法。

**【請求項 10】**

前記サイズ変更することは、ダウンサンプリングである、請求項 1 に記載の方法。

20

**【請求項 11】**

エンコーダによって実装される、請求項 2 に記載の機器。

**【請求項 12】**

デコーダによって実装される、請求項 2 に記載の機器。

**【請求項 13】**

ビットストリーム内でビット深度情報がシグナリングされる、請求項 2 に記載の機器。

**【請求項 14】**

サイズ変更済み画像のビット深度の増加が低解像度の画像についてのみ行われる、請求項 2 に記載の機器。

**【請求項 15】**

ビット深度の増加がピクチャごとに行われる、請求項 2 に記載の機器。

30

**【請求項 16】**

参照画像のビット深度が前記参照画像内の領域ごとに異なる、請求項 2 に記載の機器。

**【請求項 17】**

サイズ変更済みピクチャのビット深度が等しいことを示し、前記ビット深度をコーディングするシーケンスヘッダ内のフラグをコーディングするプロセッサを更に含む請求項 2 に記載の機器。

**【請求項 18】**

前記サイズ変更することは、ダウンサンプリングである、請求項 2 に記載の機器。

**【請求項 19】**

現在のブロックに対して動き補償を行うことと組み合わせて、参照ブロックをサイズ変更すること、

40

前記サイズ変更後のサイズを有する復号済みブロックのビット深度をサイズ変更前よりも優れた精度に増加することであって、ビット深度の増加は解像度の変化がなくても領域ごとに行われる、増加することと、

前記ビット深度を増加した前記復号済みブロックを記憶することと、

元のビット深度精度を使用して他の復号済みピクチャからのブロックを記憶することと、

を実行する命令を含む、非一時的なコンピュータ可読媒体。

**【請求項 20】**

前記サイズ変更することは、ダウンサンプリングである、請求項 19 に記載の非一時的

50

なコンピュータ可読媒体。

【発明の詳細な説明】

【技術分野】

【0001】

本願は、ビデオ画像の適応的解像度コーディング（ARC : adaptive resolution coding）に関する。

【背景技術】

【0002】

最近の  $3840 \times 2048$  フォーマットの超高精細（UHD）ビデオコンテンツの展開、及びやがて来る  $100 / 120\text{Hz}$  における  $7680 \times 4320\text{p}$  の UHD-2 ビデオフォーマットは、そのような非常に高精細のピクチャを管理することができるビデオ圧縮ツール及びシステムに対する需要を引き起こした。

10

【0003】

加えて、ビデオオンデマンド（VOD）及びオーバザトップ（OTT）アプリケーションの登場、並びにビデオストリーミングアプリケーションによってやり取りされるビデオコンテンツの増加、適応的解像度は将来のビデオコーデックの新たな且つ困難な要件だと予見されている。

【0004】

高精細映像コーディング（HEVC）規格における適応的解像度コーディングは、瞬時デコーダリフレッシュ（ IDR ）フレームを挿入することなしに状況に応じて解像度を動的に適応させることを意味する。 IDR フレームを挿入することと比較し、 ARC を使用する場合ゲインが  $6.9\% \sim 7.4\%$  であることが示されている。一部の研究は、或る実験的な解像度スイッチ選択法（resolution switch selection method）を使用し、元のフレームのサイズ及び構成に応じて  $3\% \sim 30\%$  のゲインを報告している。

20

【0005】

実際の使用事例では、低ビットレートの応用において十分なコーディング効率を促進するために、下げられた解像度まで再サンプリングすることが使用されている。第1の従来の方法は、HEVC 参照ソフトウェアの修正バージョンと共に 4K 及び 8K ビデオコンテンツを使用し、平均約 10% (Y, U, V それぞれにおいて 15%, 27.1%, 及び 19.4% まで) の Blu-ray Disc (BD) レートの低下を報告した。

30

【0006】

適応的解像度コーディングをビデオコーデック内に実装する場合、2つの主な問題に直面する可能性がある。

【0007】

第1の問題は精度損失である。参照ピクチャの解像度を現在のピクチャサイズと整合させるためのサイズ変更の間に行われるアップサンプリング操作又はダウンサンプリング操作中に行われる計算内で精度が欠如することは幾らかの損失を生ぜしめる。アップサンプリングプロセス及びダウンサンプリングプロセスは、動き補償（MC）フィルタのフィルタリング及び丸め演算と共に蓄積する潜在的な情報損失を伴う追加の丸め演算を使用する。

40

【0008】

第2の問題はメモリ要件の増加である。デコーダピクチャバッファ（DPB）は、デコーダのメモリ要件を増加させ得るあり得る全ての解像度を含み得る。

【0009】

サイズ変更と動き補償とを共に組み合わせることによってこれらの制限の両方を減らせることを別の従来の手法が示している。しかし、このサイズ変更と動き補償との複合処理はタップ数が増加したフィルタを使用することによって得られ、かかるタップ数の増加は計算負荷を高め、この複合手法の利益を減らし得る。

【発明の概要】

【課題を解決するための手段】

【0010】

50

従来技術のこれらの及び他の欠点及び不利点が本原理によって対処され、本原理は適応的解像度コーディングと適応的内部ビット深度増加とを組み合わせる方法及び機器を対象とする。

#### 【0011】

本原理は、復号され再構築されるピクチャの正規のビット深度と無関係に、場合によつてはサイズ変更される参照ピクチャに関連する内部ビット深度増加（IBDI）を指定することを含む。サイズ変更されるIBDIのパラメータは、ピクチャごとに又は領域ごとに適応させることができる。これらの原理の利点は、適応的解像度コーディングが使用されるとき、サイズ変更済みピクチャの精度を高めることによってビデオコーディング効率を改善することである。

10

#### 【0012】

本原理の一態様によれば、適応的解像度コーディングの方法が提供される。この方法は、参照ピクチャとして使用する画像をサイズ変更すること、及びサイズ変更済み画像のビット深度をサイズ変更前よりも優れた精度に増加することを含む。この方法は、サイズ変更済みのビット深度増加画像を記憶すること、及び記憶したサイズ変更済み画像を参照として使用して現在の画像に対して動き補償を行うことを更に含む。

#### 【0013】

本原理の別の態様によれば、適応的解像度コーディングの機器が提供される。この機器は、参照として使用する画像をサイズ変更するためのプロセッサを含み、サイズ変更済み画像のビット深度をサイズ変更前よりも優れた精度に増加するためのシフト回路を更に含む。この機器は、サイズ変更済みのビット深度増加画像を記憶するためのメモリ、及び現在の画像に作用し、記憶されたサイズ変更済み画像を参照として使用する動き補償回路も含む。

20

#### 【0014】

或る有利な実施形態では、先に言及した方法及び機器をエンコーダによって実装する。

#### 【0015】

別の有利な実施形態では、先に言及した方法及び機器をデコーダによって実装する。

#### 【0016】

更に別の有利な実施形態では、先に言及した方法及び機器をビットストリーム内でシグナリングされるビット深度情報を使用して実装する。

30

#### 【0017】

更に別の有利な実施形態では、先に言及した方法及び機器を実装し、サイズ変更済み画像のビット深度の増加を特定の解像度の画像についてのみ行う。

#### 【0018】

更に別の有利な実施形態では、先に言及した方法及び機器を実装し、ビット深度の増加をピクチャごとに行う。

#### 【0019】

更に別の有利な実施形態では、先に言及した方法及び機器を実装し、参照画像のビット深度が参照画像内の領域ごとに異なる。

40

#### 【図面の簡単な説明】

#### 【0020】

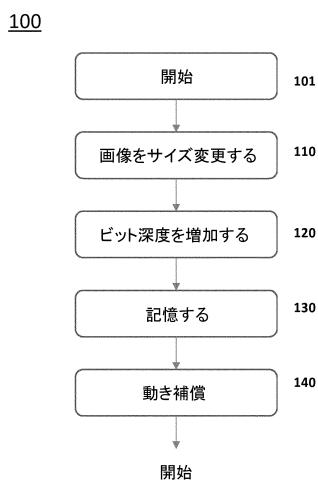

【図1】本原理を使用する方法の一実施形態を示す。

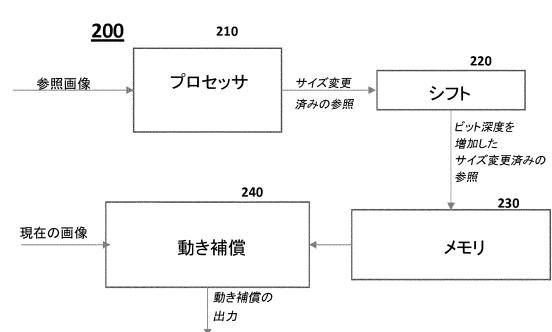

【図2】本原理を使用する機器の一実施形態を示す。

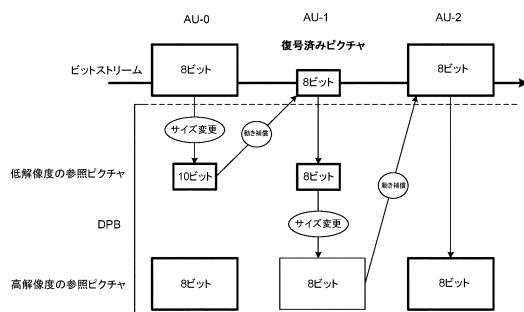

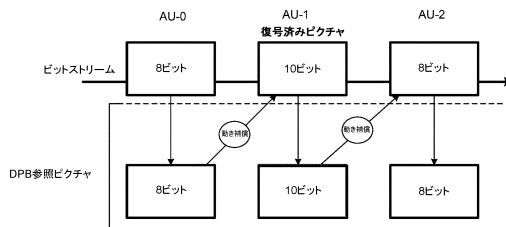

【図3】本原理を使用するARC及びIBDIの一実施形態例を示す。

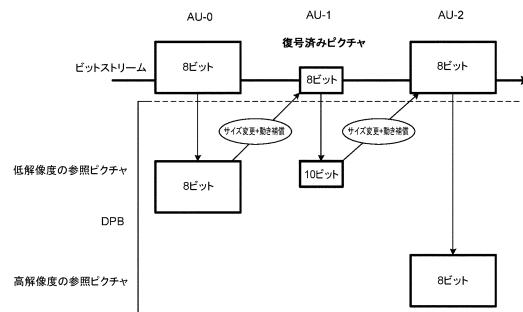

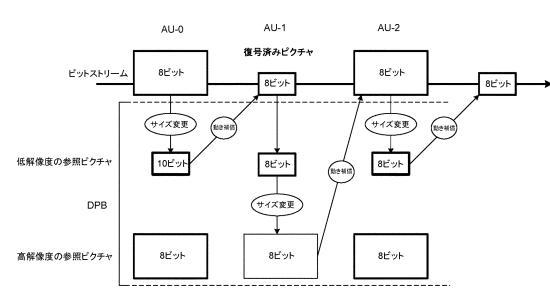

【図4】本原理を使用するARC単一解像度及びIBDIの組合せの一実施形態例を示す。

【図5】本原理を使用する、ピクチャごとに適応的なIBDIの一実施形態例を示す。

【図6】解像度の変化を伴うピクチャごとに適応的なIBDIの一実施形態例を示す。

#### 【発明を実施するための形態】

#### 【0021】

適応的解像度コーディング（ARC）は精度損失及びメモリの増加を引き起こし得る。

50

参照ピクチャを現在のピクチャサイズのフォーマットに合わせてサイズ変更する場合、数学演算の丸めがフィルタリング及び動き補償プロセスと共に蓄積する精度損失を引き起こし得る。

#### 【 0 0 2 2 】

本明細書に記載する実施形態は、内部ビット深度増加（ I B D I ）と呼ばれる内部データパスにおける増加したビット深度精度を使用できるようにし、より優れた予測、より小さい残差、及びより優れた全体的ビデオ画質をもたらす。サイズ変更是、例えば 8 ビットサンプルの線形結合に右シフトによって実施される最終的な丸めを加えたものによって実現することができる。所望の出力ビット深度を得るためにこの右シフトを調節することができる。参考フレームのための内部の 10 ビット精度を使用して 8 ビットのビデオコンテンツをコーディングする H E V C 参照ソフトウェアを使って行われた実験結果は、デコーダのメモリ要件を増加させたが著しい B D レートの改善を示した。10

#### 【 0 0 2 3 】

図 1 は、適応的解像度コーディングのための方法 100 の一実施形態を示す。この方法は開始ブロック 101 で始まり、画像をサイズ変更するためのブロック 110 に進む。次いで制御がブロック 110 から、サイズ変更済み画像のビット深度を増加させるためのブロック 120 に進む。ビット深度を増加させることは、画像をサイズ変更する数学プロセス内で使用されるより多くのビットを保つことによって実施され得る。制御はブロック 120 から、サイズ変更済みのビット深度増加画像を記憶するためのブロック 130 に進む。次いで制御がブロック 130 から、記憶したサイズ変更済みのビット深度増加画像を参照として使用して現在の画像に対して動き補償を行い、動き補償済み画像を作り出すためのブロック 140 に進む。20

#### 【 0 0 2 4 】

図 2 は、適応的解像度コーディングのための機器 200 の一実施形態を示す。この機器は、入力ポート上で参照画像を受信するプロセッサ 210 を含む。プロセッサ 210 は、自らの入力ポート上の画像をサイズ変更するために使用される。プロセッサ 210 の出力は、シフト回路 220 の入力と信号通信する。シフト回路 220 はサイズ変更済み画像を自らの入力上で受信し、その画像のビット深度を増加させる。シフト回路 220 の出力は、後で参照として使用されるサイズ変更済みのビット深度増加画像を記憶するメモリ 230 の入力と信号接続する。メモリ 230 の出力は、動き補償回路 240 の第 1 の入力と信号接続する。動き補償回路 240 は、第 2 の入力ポート上で現在の画像も受信する。動き補償回路 240 の第 1 の入力ポート上のサイズ変更済みのビット深度増加参照画像と共に現在の画像を処理して、動き補償回路 240 の出力ポート上に動き補償出力をもたらす。30

#### 【 0 0 2 5 】

提案する実施形態は、残りの参照ピクチャが正規のビット深度精度を使用しながら、サイズ変更済み解像度参照ピクチャを増加したビット深度精度で記憶することによって I B D I 及び A R C の利益を組み合わせる。この実施形態は精度損失の問題を軽減するのを助ける。

#### 【 0 0 2 6 】

提案する別の実施形態は、参照ピクチャのビット深度が動的に変わることを可能にする。低解像度の参照ピクチャしか I B D I と共に記憶されない場合、この手法は、デコーダのメモリ要件の増加によってゲインを消失させることなしに、A R C の効率を高めることによって I B D I の利点を活用する。より高精度でアップサンプリングしたサイズ変更済みピクチャを保つことは、メモリの帯域幅要件を著しく高める可能性があり、そのためダウンサンプリングした参照だけを有する I B D I を使用することによってトレードオフを検討することができる。例えば低解像度の参照をアップサンプリングするうちにより優れた精度が実現されるので A R C の効率は高まる。更に、全体的なデコーダのメモリ要件は変わらず、又は系統的に増加されない。40

#### 【 0 0 2 7 】

サイズ変更済み再構築参照ピクチャのビット深度が、例えばシーケンスパラメータセッ

10

20

30

40

50

ト( S P S )、ピクチャパラメータセット( P P S )、又はスライスヘッダを使用してビットストリーム内でシグナリングされる。より優れた精度を実現するために最終的な丸め及びシフト演算をしかるべき設定することにより、サイズ変更操作(アップサンプリング及びダウンサンプリングの両方)及び動き補償プロセスが記載の実施形態において適応される。

#### 【 0 0 2 8 】

サイズ変更済み参照ピクチャのビット深度が動的に変わる場合、ビット深度情報も動的に送信することができる。例えば、或るビット深度を特定の参照ピクチャに使用することができ、別のビット深度を第2の参照ピクチャに使用することができる。しかし、例えばサイズ変更済み(又は特定のサイズ変更比の)ピクチャ全てのビット深度が同じであることを示すシーケンスヘッダ内のフラグをコーディングし、その値をコーディングすることができる。予測としてこれらの参照ピクチャを使用する再構築ピクチャ内のドリフト誤差を避けるために、デコーダは参照ピクチャのビット深度を知る必要がある。

10

#### 【 0 0 2 9 】

本原理の一実施形態を図3に示し、図3は複合型のARC及びIBDIの一例を示す。アクセスユニットAU-0に対応するダウンサンプリングされたサイズ変更済み参照ピクチャが10ビット精度で出力される一方、正規のビット深度は8ビットである。AU-0に対応するより高精度のダウンサンプリングされた参照ピクチャが、より小さい8ビットサイズのピクチャAU-1への動き補償のためにデコーダピクチャバッファ(DPB)から入手できる。DPBは、低解像度の参照ピクチャ及び高解像度の参照ピクチャの両方を記憶する。

20

#### 【 0 0 3 0 】

本原理の別の実施形態を図4に示す。図4では、サイズ変更操作を動き補償処理と組み合わせる。精度を高めながら帯域幅メモリを減らす。

#### 【 0 0 3 1 】

別の実施形態では、メモリの帯域幅要件の増加を最小限に抑えるために、サイズ変更済みピクチャのビット深度の増加を低解像度のピクチャについてのみ行う。このシナリオの例が図3、図4、及び図6にある。但し、ビット深度の増加は図示のように低解像度のピクチャの全て又は単にその一部に関係し得る。低解像度のピクチャは、別の解像度で処理されている画像シーケンスのフォーマットと相対的なものであり得る。例えば $7680 \times 4320$ フォーマットの信号を処理する場合、低解像度は $1920 \times 1024$ フォーマットの参照であり得る。

30

#### 【 0 0 3 2 】

別の実施形態では、図5に示すように、解像度の変化がなくても、ビット深度の増加が図6に示すようにピクチャごとに行われる。この形態は、例えば重要な参照ピクチャ又は参照ピクチャとして頻繁に使用されるピクチャの精度を高めることを可能にする。

#### 【 0 0 3 3 】

別の実施形態では、参照ピクチャのビット深度が例えばスライスごと等、ピクチャ内の領域ごとに異なり得る。この実施形態は、より低いIBDIが使用される場合は帯域幅メモリを節約するために、又はより高いIBDIが使用される場合は精度を高めるために使用され得る。

40

#### 【 0 0 3 4 】

上記の実施形態は、セットトップボックス(STB)、モ뎀、ゲートウェイ、又はビデオのコーディング及び復号を行う他の装置によって実装することができる。

#### 【 0 0 3 5 】

図示の様々な要素の機能は、専用ハードウェア並びに適切なソフトウェアに関連してソフトウェアを実行可能なハードウェアを使用することによって提供することができる。プロセッサによって提供される場合、機能は単一の専用プロセッサによって、単一の共用プロセッサによって、又はその一部が共用されても良い複数の個々のプロセッサによって提供され得る。更に、「プロセッサ」又は「コントローラ」という用語の明示的使用は、ソ

50

ソフトウェアを実行可能なハードウェアを排他的に指すものだと解釈すべきではなく、デジタル信号プロセッサ（「DSP」）ハードウェア、ソフトウェアを記憶するための読み取り専用メモリ（「ROM」）、ランダムアクセスメモリ（「RAM」）、及び不揮発性記憶域を制限なしに暗に含み得る。

#### 【0036】

他の従来の及び／又は特注のハードウェアも含まれ得る。同様に、図示の何れのスイッチも概念上のものに過ぎない。それらの機能は、プログラムロジックの動作によって、専用ロジックによって、プログラム制御及び専用ロジックの相互作用によって、更には手動で実行することができ、文脈からより明確に理解されるように特定の技法が実装者によって選択可能である。

10

#### 【0037】

本明細書は本原理を例示する。従って本明細書で明確に説明され又は図示されていなくても、本原理を具体化し本原理の趣旨及び範囲に含まれる様々なアレンジを当業者なら考案できることが理解されよう。

#### 【0038】

本明細書で挙げた全ての例及び条件付き言語は、当技術分野を促進するために発明者がもたらす本原理及び概念を読者が理解するのを助けるための教示を目的とするものであり、具体的に挙げたかかる例及び条件に限定されないものと解釈されるべきである。

20

#### 【0039】

更に、本原理並びに本原理の具体例の原理、態様、及び実施形態を挙げる本明細書の全ての表現は、その構造上の等価物及び機能上の等価物の両方を包含することを意図する。加えて、かかる等価物は現在知られている等価物並びに将来開発される等価物、即ち構造に関係なく同じ機能を実行する開発される任意の要素の両方を含むことを意図する。

#### 【0040】

従って、例えば本明細書で示したブロック図は、本原理を具体化する例示的回路の概念図を示すことを当業者なら理解されよう。同様に、任意の工程図、流れ図、状態遷移図、疑似コード等は、コンピュータ可読媒体内で実質的に表わすことができ、そのためコンピュータ又はプロセッサによって、かかるコンピュータ又はプロセッサが明確に示されているがいまいが実行される様々なプロセスを表わすことが理解されよう。

30

#### 【0041】

本明細書の特許請求の範囲では、指定の機能を行うための手段として表わす如何なる要素も、例えばa) その機能を行う回路素子の組合せ、又はb) その機能を行うためにソフトウェアを実行するための適切な回路と組み合わせられる任意の形式の、従ってファームウェアやマイクロコード等を含むソフトウェアを含む、その機能を行う任意のやり方を包含することを意図する。かかる特許請求の範囲によって定める本原理は、列挙した様々な手段によって与えられる機能が、特許請求の範囲が必要とするやり方で組み合わせられ、まとめられるという事実にある。従って、それらの機能を提供可能な如何なる手段も本明細書に示した手段と等価と見なす。

#### 【0042】

本原理の「一実施形態」又は「或る実施形態」並びにそれらの他の変形形態に本明細書で言及することは、実施形態に関連して記載した特定の特徴、構造、特性等が本原理の少なくとも一実施形態に含まれることを意味する。従って、本明細書の全体を通して様々な場所に登場する「一実施形態では」又は「或る実施形態では」という語句並びに他の変形形態の登場は必ずしも全て同じ実施形態を指すものではない。

40

#### (付記1)

適応的解像度コーディングの方法であって、

参照ピクチャとして使用する画像をサイズ変更すること(110)と、

前記サイズ変更済み参照画像のピット深度をサイズ変更前よりも高い精度に増加すること(120)であって、ピット深度の増加は解像度の変化がなくてもピクチャごとに行われる、増加すること(120)と、

50

前記サイズ変更済みのビット深度増加画像を記憶すること(130)と、

前記記憶したサイズ変更済み画像を参照として使用して現在の画像に対して動き補償を行ふこと(140)と、

を含む、方法。

(付記2)

適応的解像度コーディングの機器であつて、

参照として使用する画像をサイズ変更するためのプロセッサ(210)と、

前記サイズ変更済み参照画像のビット深度をサイズ変更前よりも優れた精度に増加するためのシフト回路(220)であつて、ビット深度の増加は解像度の変化がなくてもピクチャごとに行われる、シフト回路(220)と、

前記サイズ変更済みのビット深度増加画像を記憶するためのメモリ(230)と、

現在の画像に作用し、前記記憶されたサイズ変更済み画像を参照として使用する動き補償回路(240)と、

を含む、機器。

(付記3)

エンコーダによって実装される、付記1に記載の方法又は付記2に記載の機器。

(付記4)

デコーダによって実装される、付記1に記載の方法又は付記2に記載の機器。

(付記5)

ビットストリーム内でビット深度情報がシグナリングされる、付記1に記載の方法又は付記2に記載の機器。

(付記6)

サイズ変更済み画像のビット深度の増加が特定の解像度の画像についてのみ行われる、付記1に記載の方法又は付記2に記載の機器。

(付記7)

ビット深度の増加がピクチャごとに行われる、付記1に記載の方法又は付記2に記載の機器。

(付記8)

参照画像のビット深度が前記参照画像内の領域ごとに異なる、付記1に記載の方法又は付記2に記載の機器。

(付記9)

サイズ変更済みピクチャのビット深度が等しいことを示し、前記ビット深度をコーディングするシーケンスヘッダ内のフラグを

コーディングすることを更に含む付記1に記載の方法、又はコーディングするプロセッサを更に含む付記2に記載の機器。

10

20

30

40

50

【図面】

【図 1】

【図 2】

【図 3】

【図 4】

30

40

50

【図5】

【図6】

10

20

30

40

50

---

フロントページの続き

弁理士 阿部 豊隆

(72)発明者 ポルデ , フィリップ

フランス国 , 3 5 5 7 6 セソン - セビニエ , アベニュー デ シャン ブラン , 9 7 5 , テクニカラ - アール・アンド・ディー フランス内

(72)発明者 ギャルピン , フランク

フランス国 , 3 5 5 7 6 セソン - セビニエ , アベニュー デ シャン ブラン , 9 7 5 , テクニカラ - アール・アンド・ディー フランス内

(72)発明者 アンドリヴィオン , ピエール

フランス国 , 3 5 5 7 6 セソン - セビニエ , アベニュー デ シャン ブラン , 9 7 5 , テクニカラ - アール・アンド・ディー フランス内

合議体

審判長 畑中 高行

審判官 板垣 有紀

審判官 國分 直樹

(56)参考文献 国際公開第2 0 0 7 / 1 1 4 3 6 8 (WO , A 1 )

Thomas Davies , "Resolution switching for coding efficiency and resilience" , Joint Collaborative Team on Video Coding (JCT-VC) , 2011 - 07 - 15 , [ J C T V C - F 1 5 8 ] (version 5)

(58)調査した分野 (Int.Cl. , DB名)

H04N19/00-19/98