(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5376414号

(P5376414)

(45) 発行日 平成25年12月25日(2013.12.25)

(24) 登録日 平成25年10月4日(2013.10.4)

(51) Int.Cl.

F 1

|                |           |              |         |

|----------------|-----------|--------------|---------|

| G 11 C 16/02   | (2006.01) | G 11 C 17/00 | 6 1 2 D |

| G 11 C 16/04   | (2006.01) | G 11 C 17/00 | 6 2 1 Z |

| H 01 L 21/8247 | (2006.01) | G 11 C 17/00 | 6 2 2 E |

| H 01 L 27/115  | (2006.01) | H 01 L 27/10 | 4 3 4   |

| H 01 L 21/336  | (2006.01) | H 01 L 29/78 | 3 7 1   |

請求項の数 11 外国語出願 (全 35 頁) 最終頁に続く

(21) 出願番号

特願2006-964 (P2006-964)

(22) 出願日

平成18年1月5日(2006.1.5)

(65) 公開番号

特開2006-216215 (P2006-216215A)

(43) 公開日

平成18年8月17日(2006.8.17)

審査請求日

平成18年9月25日(2006.9.25)

審判番号

不服2012-3644 (P2012-3644/J1)

審判請求日

平成24年2月24日(2012.2.24)

(31) 優先権主張番号

60/647012

(32) 優先日

平成17年1月27日(2005.1.27)

(33) 優先権主張国

米国(US)

(73) 特許権者 511043035

マクロニクス インターナショナル カンパニー リミテッド

台湾 シンチュ サイエンス パーク リーシン ロード ナンバー 16

(74) 代理人 100075638

弁理士 倉橋 咲

(72) 発明者 ハンーティン ルー

台湾 シンチュ チンーフワ ユニバーシティ 19 イースト ユアン

合議体

審判長 池淵 立

審判官 早川 朋一

審判官 西脇 博志

最終頁に続く

(54) 【発明の名称】メモリアレイの操作方法

## (57) 【特許請求の範囲】

## 【請求項 1】

ウェルを有する半導体基板上に配置された複数のメモリセルを有するメモリアレイの操作方法であり、前記メモリセルのそれぞれは、前記基板の表面より下に配置され且つチャネル領域によって分離されたソース領域及びドレイン領域と、前記チャネル領域より上に配置されたトンネル誘電体構造と、前記トンネル誘電体構造より上に配置された絶縁材料からなる電荷蓄積層と、前記電荷蓄積層より上に配置された絶縁層と、前記絶縁層より上に配置されたゲート電極と、を有し、前記トンネル誘電体構造は、あるホールトンネリング障壁高さを有する下端誘電体層と、前記下端誘電体層のものよりも小さいホールトンネリング障壁高さを有する中間誘電体層と、前記中間誘電体層のものよりも大きいホールトンネリング障壁高さを有する上端誘電体層と、を有し、前記下端誘電体層、中間誘電体層及び上端誘電体層のそれぞれは、約 3 nm 以下の厚さを有する前記方法であって、

リセット / 消去されるべき各メモリセルにおいて、一定の自己収束リセット / 消去電圧を、前記ウェル及び前記ゲート電極へ印加する工程と、

前記複数のメモリセルのうち少なくとも 1 つをプログラムする工程と、

前記複数のメモリセルのうち少なくとも 1 つの消去された状態のレベルとプログラムされた状態のレベルとの間の電圧を印加することによって前記複数のメモリセルのうち少なくとも 1 つを読み出す工程と、

を有することを特徴とする方法。

## 【請求項 2】

10

20

更に、前記少なくとも1つのプログラムされたメモリセルにおいて、一定の自己収束リセット／消去電圧を、前記ウェル及び前記ゲート電極に印加する工程を有することを特徴とする請求項1に記載の方法。

**【請求項3】**

前記一定の自己収束リセット／消去電圧を印加する工程は、負のゲート電圧 $V_g$ と、ウェル電圧 $V_s$ と、を印加することを含み、約-20Vから約-12Vの電位差 $V_g - V_s$ を有することを特徴とする請求項1に記載の方法。

**【請求項4】**

前記少なくとも1つのプログラムされたメモリセルに一定の自己収束リセット／消去電圧を印加する工程は、負のゲート電圧 $V_g$ と、ウェル電圧 $V_s$ と、を印加することを含み、約-20Vから約-12Vの電位差 $V_g - V_s$ を有することを特徴とする請求項2に記載の方法。10

**【請求項5】**

前記一定の自己収束リセット／消去電圧を印加する工程は、約-20Vから約-12Vのゲート電圧を印加すること及び前記ウェルを接地することを含むことを特徴とする請求項1に記載の方法。

**【請求項6】**

前記一定の自己収束リセット／消去電圧を印加する工程は、約-10Vから約-2Vのゲート電圧及び約+5Vから約+10Vのウェル電圧を印加することを含むことを特徴とする請求項1に記載の方法。20

**【請求項7】**

前記メモリアレイはNORアーキテクチャを有し、前記複数のメモリセルのうち少なくとも1つをプログラムする工程はチャネルホットエレクトロン注入を含むことを特徴とする請求項1に記載の方法。

**【請求項8】**

前記メモリアレイはNANDアーキテクチャを有し、前記複数のメモリセルのうち少なくとも1つをプログラムする工程はチャネル+FN注入を含むことを特徴とする請求項1に記載の方法。

**【請求項9】**

前記メモリアレイはNORアーキテクチャを有し、前記複数のメモリセルのうち少なくとも1つをプログラムする工程はチャネルイニシエイティッドセカンダリーエレクトロン注入を含むことを特徴とする請求項1に記載の方法。30

**【請求項10】**

前記複数のメモリセルのうち少なくとも1つをプログラムする工程は、約+16Vから約+20Vの電圧を少なくとも1つの選択されたワード線に印加すること及び前記ウェルを接地することを含むことを特徴とする請求項1に記載の方法。

**【請求項11】**

前記複数のメモリセルのうち少なくとも1つのメモリセルをプログラムする工程は更に、約+7Vの電圧を少なくとも1つの選択されていないビット線に印加することを含むことを特徴とする請求項1に記載の方法。40

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

**関連出願の相互参照**

本出願は、2005年1月3日出願の米国仮特許出願60/640,229号、2005年1月27日出願の米国仮特許出願60/647,012号、2005年6月10日出願の米国仮特許出願60/689,231号、及び2005年6月10日出願の米国仮特許出願60/689,314号に基づくものであり、又、米国法典35編119条(e)項により前記米国仮特許出願の優先権を主張する。前記各米国仮特許出願は、引用をもって、その全内容が本出願に内包されている。50

**【背景技術】****【0002】****発明の背景**

不揮発性メモリ (NVM: Non-volatile memory) は、NVMセルを有するデバイスであり、デバイスへの電力供給が除去された時でさえ情報を連続的に記憶することができる半導体メモリを指す。NVMには、マスクROM (Mask ROM: Mask Read-Only Memory)、プログラマブルROM (PROM: Programmable Read-Only Memory)、消去可能プログラマブルROM (EPROM: Erasable Programmable Read-Only Memory)、電気的消去可能プログラマブルROM (EEPROM: Electrically Erasable Programmable Read-Only Memory)、及びフラッシュメモリ (Flash Memory) などが含まれる。不揮発性メモリは半導体業界において広く使用されており、プログラム (書き込み) されたデータの損失を防止するために開発されたメモリとして分類される。通常、不揮発性メモリは、デバイスのエンドユース要件に基づいてプログラム、読み出し及び／又は消去が可能であり、プログラムされたデータを長期間に渡って記憶することができる。

**【0003】**

概して、不揮発性メモリデバイスは多様な設計を取り得る。NVMセル設計の1つの例が、所謂、SONOS (ケイ素 (silicon) - 酸化物 (oxide) - 窒化物 (nitride) - 酸化物 (oxide) - ケイ素 (silicon)) デバイスである。SONOSデバイスは、薄いトンネル酸化物層 (酸化被膜) を使用することができ、ホール (正孔) の直接トンネリング消去動作を行わせることができる。このような設計は、良好な消去速度を有し得るが、データ保持能力は一般に低い。これは、メモリデバイスの保持状態の期間に存在することのある低電界強度においてさえ直接トンネリングが起こり得ることが一因である。

**【0004】**

もう1つのNVM設計は、保持状態の期間における電荷の損失を防止するためにより厚いトンネル酸化物層を使用するNRDM (nitrided read-only memory: 窒化ROM) である。しかしながら、厚いトンネル酸化物層はチャネル消去速度に影響を与えることがある。結果として、ホールトラップを注入して電子を補うために、バンド間トンネリングホットホール (BTBTHH: band-to-band tunneling hot-hole) 消去方法を用いることができる。しかし、BTBTHH消去方法は、いくつかの信頼性の問題を引き起こすことがある。例えば、BTBTHH消去方法を採用したNRDMデバイスの特性は、多数のP/E (program/erase: プログラム／消去) サイクルの後で劣化することがある。

**【0005】**

従って、当該技術分野においては、向上されたデータ保持性能及び向上された動作速度をもって、多数回にわたり動作 (プログラム／消去／読み出し) させることのできる不揮発性メモリセル設計及びアレイが求められている。

**【発明の開示】****【0006】****発明の概要**

本発明は、不揮発性メモリデバイスに関するものであり、より詳しくは、自己収束消去動作を容易にすると共に保持状態の期間におけるメモリデバイスの電荷蓄積層内の電荷保持能力を保持してもいるトンネル誘電体構造を有する不揮発性メモリデバイスに関するものである。

**【0007】**

本発明の一実施形態は、半導体基板であって、該基板の表面より下に配置され且つチャネル領域によって分離されたソース領域及びドレイン領域を備えた半導体基板と；前記チャネル領域より上に配置されたトンネル誘電体構造であって、低いホールトンネリング障

10

20

30

40

50

壁高さを有する少なくとも 1 つの層を備えたトンネル誘電体構造と；前記トンネル誘電体構造より上に配置された電荷蓄積層と；前記電荷蓄積層より上に配置された絶縁層と；前記絶縁層より上に配置されたゲート電極と；を有するメモリセルを含む。

#### 【 0 0 0 8 】

本発明の他の実施形態は、半導体基板であって、該基板の表面より下に配置され且つチャネル領域で分離されたソース領域及びドレイン領域を備えた半導体基板と；前記チャネル領域より上に配置された多層トンネル誘電体構造であって、低いホールトンネリング障壁高さを有する少なくとも 1 つの層を備えた多層トンネル誘電体構造と；前記多層トンネル誘電体構造より上に配置された電荷蓄積層と；前記電荷蓄積層より上に配置された絶縁層と；前記絶縁層より上に配置されたゲート電極と；を有するメモリセルを含む。 10

#### 【 0 0 0 9 】

特定の好ましい実施形態においては、前記低いホールトンネリング障壁高さを提供する層は、窒化ケイ素 ( $\text{Si}_3\text{N}_4$ ) 又は酸化ハフニウム ( $\text{HfO}_2$ ) などの材料（物質）を含んでいてよい。本発明の特定の好ましい実施形態においては、メモリセルは、酸化ケイ素、窒化ケイ素及び酸化ケイ素の積み重ねられた誘電体 3 層構造 ( $\text{ONO}$ ) などの複数の層を備えたトンネル誘電体構造を有する。このようなトンネル誘電体構造は、 $\text{SONONOS}$  (ケイ素 - 酸化物 - 窒化物 - 酸化物 - 窒化物 - 酸化物 - ケイ素) 又は超格子  $\text{SONONOS}$  設計を提供する。

#### 【 0 0 1 0 】

本発明の特定の好ましい実施形態においては、前記トンネル誘電体構造は、それぞれが最大で約 4 nm まで（約 4 nm 以下）の厚さを有する少なくとも 2 つの誘電体層を有することができる。又、本発明の特定の好ましい実施形態においては、前記ゲート電極は、 $\text{N}^+$  ポリシリコンの仕事関数値よりも大きな仕事関数値を有する材料を含む。 20

#### 【 0 0 1 1 】

特定の好ましい実施形態においては、前記トンネル誘電体構造は、低いホールトンネリング障壁高さを有する材料を含む層を有することができ、その材料は、その材料の濃度がその層内のある深度位置で最大になるような濃度勾配にて、その層内に存在する。

#### 【 0 0 1 2 】

本発明はまた、本明細書に記載される 1 つ以上の実施形態に従う複数のメモリセル（即ち、アレイ）を有する不揮発性メモリデバイスを含む。本明細書にて用いられる「複数」とは、2 つ以上を意味する。本発明に従うメモリデバイスは、増大された消去速度、向上された電荷保持能力、及びより大きな動作ウインドウを含む、著しく改善された動作特性を示す。 30

#### 【 0 0 1 3 】

本発明はまた、不揮発性メモリセル及びアレイの操作方法を含む。本発明に従う操作方法は、メモリデバイス群の  $V_t$  分布をタイト化するように、自己収束方法を適用することによってメモリデバイス群をリセットする工程と；チャネル + FN 注入によって前記メモリデバイス群のうち少なくとも 1 つをプログラムする工程と；前記メモリデバイス群のうち少なくとも 1 つの消去された状態のレベルとプログラムされた状態のレベルとの間の電圧を印加することによって、前記メモリデバイス群のうち少なくとも 1 つを読み出す工程と；を有する。本明細書にて用いられる表現「タイト化 ( $tighten$ )」とは、1 つのアレイの多数のメモリセル間の閾（スレッショルド）電圧分布を狭めることを意味する。概して、閾電圧分布が「タイト化」されると、従来の設計よりもアレイの動作が改善されるように、複数のセルの閾電圧は互いに狭い範囲内にある。例えば、本発明の 1 つ以上の実施形態に従うメモリセルを有する NAND アレイなどの、いくつかの好ましい実施形態においては、「タイト化」された閾電圧分布とは、多様なメモリセルの閾電圧が互いに 0.5 V の範囲内にあることを示す。本発明に従うメモリセルを使用する他のアーキテクチャにおいては、「タイト化」された閾電圧分布は、上限（最大値）から下限（最小値）まで約 1.0 V の範囲を有することもある。 40

#### 【 0 0 1 4 】

50

本発明に従う操作方法の一実施形態は、次の各工程により本発明に従うアレイを操作することを含む。即ち、その操作は、自己収束リセット／消去電圧を、基板及びリセット／消去されるべき各メモリセルにおけるゲート電極に印加する工程と；複数のメモリセルのうち少なくとも1つをプログラムする工程と；メモリデバイス群のうち少なくとも1つの消去された状態のレベルとプログラムされた状態のレベルとの間の電圧を印加することによって、複数のメモリセルのうち少なくとも1つを読み出す工程と；を有する。

#### 【0015】

本発明はまた、半導体基板を提供する工程であって、該基板の表面より下の該基板内に形成され且つチャネル領域によって分離されたソース領域及びドレイン領域を備えた半導体基板を提供する工程と；前記チャネル領域より上にトンネル誘電体構造を形成する工程と；前記トンネル誘電体構造より上に電荷蓄積層を形成する工程と；前記電荷蓄積層より上に絶縁層を形成する工程と；前記絶縁層より上にゲート電極を形成する工程と；を有し、前記トンネル誘電体構造を形成する工程は、少なくとも2つの誘電体層を形成することを含み、該少なくとも2つの誘電体層のうち1つは、該少なくとも2つの誘電体層のうち他方よりも低いホールトンネリング障壁高さを有することを特徴とするメモリセルの形成方法を含む。

10

#### 【0016】

本明細書にて用いられる表現「低い（小さい）ホールトンネリング障壁高さ」とは、一般には、二酸化ケイ素のおおよそのホールトンネリング障壁高さ以下の値を意味する。特に、低いホールトンネリング障壁高さは、好ましくは、約4.5eV以下である。より好ましくは、低いホールトンネリング障壁高さは、約1.9eV以下である。

20

#### 【0017】

上述の発明の概要及び後述の発明の詳細な説明は、添付図面と合わせて読むことにより、より良く理解されるであろう。発明の説明を目的として、現在好ましい実施形態を添付図面に示した。しかし、本発明が図示された通りの配置及び機器に限定されるものではないことを理解されたい。

#### 【発明を実施するための最良の形態】

#### 【0018】

#### 発明の詳細な説明

以下、本発明及びその現在好ましい実施形態について詳細に説明する。それらの例は添付の図面に示した。可能な限り、同一又は類似の部分を参照するのには、図面及び説明文において同一又は類似の参照番号を使用した。グラフ以外の図面は、かなり単純化された形態にあり、縮尺も正確ではないことを理解されたい。本明細書の開示内容に関連して、上端（頂部）、下端（底部）、左、右、上方、下方、上、下、真下、後方及び前方などの方向を示す表現は、単なる簡明化のために添付図面に関して使用されている。図面についての以下の説明に関連して用いられているこのような方向を示す表現は、添付の特許請求の範囲に明示されていない如何なる形式においても本発明の範囲を限定するものと解釈すべきではない。本明細書の開示内容は、図示された特定の実施形態に言及しているが、これらの実施形態は例示のために提示したものであって、限定のために提示したものでないことを理解されたい。本明細書に記載される工程段階及び構造は、完全な集積回路の製造のための完全な工程フローをカバーしたものではないことを理解されたい。本発明は、当該技術分野において既知又は開発されるであろう各種の集積回路製造技術と共に実施することができる。

30

#### 【0019】

本発明に従うメモリセルは、SONOS及びNROMデバイスにおける信頼性の問題のいくつかを解決することができる。例えば、本発明に従うメモリセル構造は、良好な電荷保持特性を維持したまま、高速FNチャネル消去方法を可能にすることができます。又、本発明に従うメモリセルの各種の実施形態は、BTBTH消去方法への依存を低減することができ、それによって多数回のP/Eサイクルの後のデバイス劣化を防止することができる。

40

50

## 【0020】

一例では、極薄トンネル誘電体、即ち、極薄酸化物層を、低いホールトンネリング障壁高さの層（低ホールトンネリング障壁層）と共に、トンネル誘電体構造が多層構造である実施形態において採用することができる。これにより、より良好なストレス（応力）耐性を提供することができる。又、本発明に従う不揮発性メモリセルは、多数回のP/Eサイクルの後の劣化をほとんど示さない。

## 【0021】

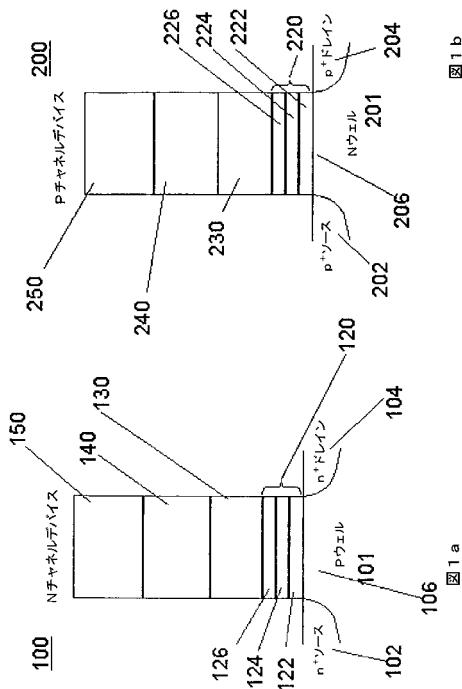

本発明に従うメモリセルは、図1a及び図1bに示されているような、nチャネル（n型）設計、pチャネル（p型）設計のいずれを採用することもできる。図1aは、本発明の一実施形態に従うnチャネルメモリセル100の断面図である。このメモリセルは、少なくとも2つのnドープ（添加）領域102、104を備えたp型基板101を有する。ドープ領域102、104はそれぞれ、印加される電圧に応じてソース又はドレインのいずれとしても機能することができる。参考として、図1aに示されるように、ドープ領域102はソースとして働くことができ、ドープ領域104はドレインとして働くことができる。基板101は更に、2つのnドープ領域の間にチャネル領域106を有する。チャネル領域106より上の、基板101の表面上には、トンネル誘電体構造120がある。特定の好ましい実施形態においては、トンネル誘電体構造120は、3層の薄いONO構造を有することができる。この構造においては、低いホールトンネリング障壁高さの窒化物層（窒化被膜）124が、薄い下側の酸化物層122と上側の薄い酸化物層126との間に挟まれている。メモリセル100は更に、好ましくは窒化物でありトンネル誘電体構造120より上に配置される電荷捕捉（即ち、電荷蓄積）層130と、好ましくはプロッキング酸化物を含み電荷捕捉層130より上に配置される絶縁層140とを有する。ゲート150は、絶縁層140の上に配置される。

## 【0022】

図1bは、本発明の一実施形態に従うpチャネルメモリセル200の断面図である。このメモリセルは、少なくとも2つのpドープ領域202、204を備えたn型基板201を有する。ドープ領域202、204はそれぞれ、ソース又はドレインのいずれとしても機能することができる。基板201は更に、2つのpドープ領域の間にチャネル領域206を有する。pチャネルメモリセル200も同様に、トンネル誘電体構造220、電荷捕捉（即ち、電荷蓄積）層230、絶縁層240、及びゲート250を有する。トンネル誘電体構造220は、低いホールトンネリング障壁高さの窒化物層224が、薄い下側の酸化物層222と上側の薄い酸化物層226との間に挟まれた、3層の薄いONO構造を有する。

## 【0023】

このように、例えば、図1a及び図1bに示すように、本発明に従うメモリセルは、第1の酸化ケイ素層O1、第1の窒化ケイ素層N1、及び第2の酸化ケイ素層O2を備える多層薄膜トンネル誘電体構造と；第2の窒化ケイ素層N2などの電荷蓄積層と；第3の酸化ケイ素層O3などの絶縁層と；を、半導体基板（例えば、シリコン基板）などの基板上に接触（on）して有するか又は基板の上方（over）（「above（上側）」）に有していてよい。トンネリング誘電体構造は、メモリデバイスの消去/リセット動作中に、基板から電荷蓄積層へのホールのトンネリングを生じさせることができる。本発明の不揮発性メモリセルにおけるトンネル誘電体構造は、メモリ動作中に、好ましくは無視できるほど小さい（極めて小さい）電荷捕捉効率を有し、より好ましくは電荷を全く捕捉しない。

## 【0024】

窒化ケイ素層、HfO<sub>2</sub>、及びAl<sub>2</sub>O<sub>3</sub>などの電荷蓄積材料を、トンネル誘電体構造における低いホールトンネリング障壁高さの層として使用することができる。本発明の特定の好ましい実施形態においては、窒化ケイ素などの電荷蓄積効率の高い材料を、メモリデバイスにおける電荷蓄積層として使用することができる。電荷の損失を防ぐプロッキング酸化物は、第3の酸化ケイ素層O3などの絶縁層として働くことができる。又、本発明に

10

20

30

40

50

従うメモリセルは、絶縁層より上に、ポリシリコンゲートなどのゲート又はゲート電極を有する。トンネル誘電体構造、電荷蓄積層、絶縁層、及びゲートは、基板より上であって、チャネル領域の少なくとも一部の上側に形成することができる。チャネル領域は、ソース領域とドレイン領域とによって画成され、且つ、それらの間に配置される。

#### 【0025】

本発明の各種実施形態に従うメモリセルは、負のゲート電圧 ( $V_g$ )、例えば約 - 10 Vから約 - 20 Vまでの  $V_g$  の下で、約 10 msec の高速の FN 消去速度を提供することができるトンネル誘電体構造を有する。一方、電荷保持能力も維持することができ、いくつかの例においては、電荷保持能力は多くの従来の SONOS デバイスよりも良好であり得る。本発明に従うメモリセルはまた、NROM デバイスで一般に用いられているバンド間ホットホール消去動作の使用を避けることが可能である。このようなバンド間ホットホール消去動作の回避は、ホットホールによるダメージを大幅に排除することができ、従ってこのような回避は望ましい。10

#### 【0026】

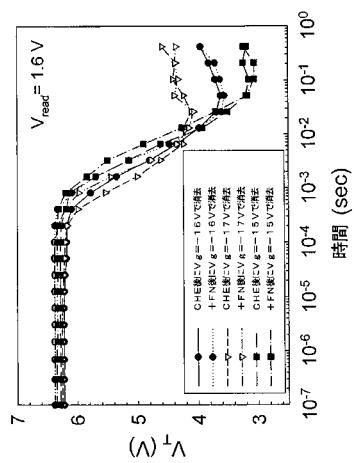

図 2 を参照すると、本発明の一実施形態に従うトンネル誘電体構造についての閾（スレッショルド）電圧の実測値は、連続するプログラミング（書き込み）パルスの下での変化しない閾電圧レベルによって証明されるように、極薄 O1 / N1 / O2 構造が無視できるほど小さい捕捉効率を有し得ることを示す。図 2 の試験例では、O1 / N1 / O2 層はそれぞれ、30、30、35 オングストローム ( ) の厚さを有する。図 2 に示すように、各種のプログラミング方法、即ち、- FN プログラミング、+ FN プログラミング、及び CHE (channel hot electron : チャネルホットエレクトロン) プログラミングを用いた数ショットのプログラムの間に、閾電圧  $V_t$  は約 1.9 ボルトで一定である。従って、このような極薄 O1 / N1 / O2 膜は、変調されたトンネル誘電体構造として働くことができる。CHE、+ FN 及び - FN を含む各種の電荷注入方法の下での結果は全て、無視できるほど小さい電荷捕捉を示唆している。製造工程又はデバイス構造は、界面トラップ（捕捉）を最小化するように設計することができ、従って O1 / N1 界面と N1 / O2 界面のいずれもアクティブにならない。20

#### 【0027】

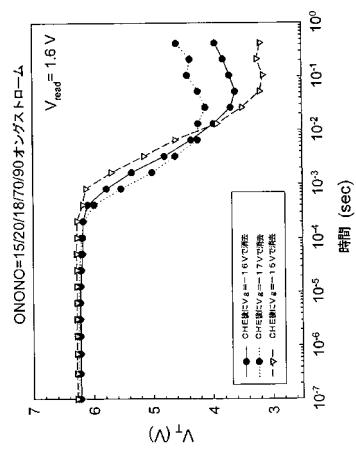

図 3 は、本発明の一実施形態に従う SONONOS 構造を有するメモリセルの消去特性を示す。図 3 に記載した実施形態におけるメモリセルは、それぞれ 15、20 及び 18 の厚さを有する ONO トンネル誘電体構造を備えた n-MOSFET 設計を有する。この実施形態のメモリセルは、約 70 の厚さを有する窒化ケイ素電荷蓄積層、約 90 の厚さを有する酸化ケイ素絶縁層、及び例えば n ドープ多結晶シリコンなどの任意の適切な導電材料を含むゲートを有する。図 3 を参照すると、10 msec 以内といった高速 FN 消去を達成することができ、又、優れた自己収束消去特性を得ることもできる。30

#### 【0028】

図 4 は、図 3 を参照して説明した本発明に従うメモリセルの一実施形態による SONONOS デバイスの電荷保持特性を示す。図示されているように、保持特性は従来の SONOS デバイスのそれよりも良好とすることが可能であり、数桁良くなり得る。40

#### 【0029】

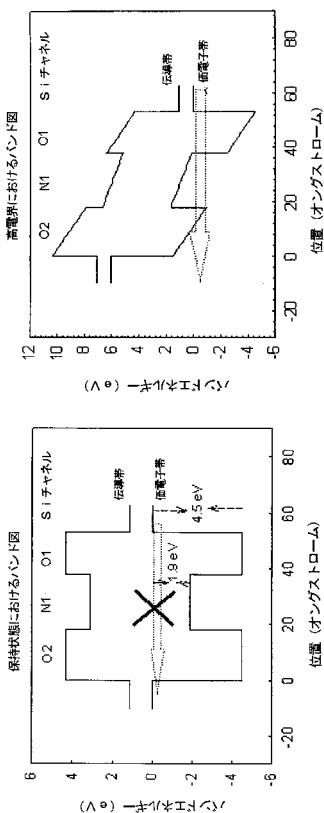

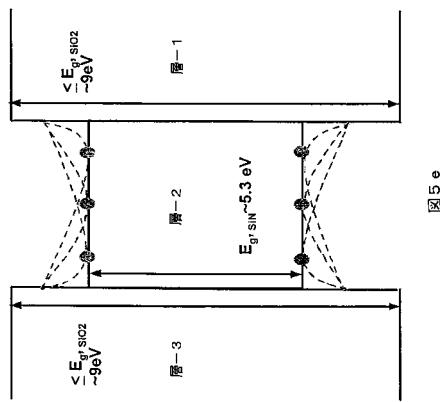

図 5 a 及び図 5 b は、低いホールトンネリング障壁高さを有する少なくとも 1 つの層を有するトンネル誘電体構造を用いることによって得られる効果を説明するバンド図である。図 5 a には、メモリデータ保持期間に存在し得る低電界下での、この例では O1 / N1 / O2 の 3 層であるトンネル誘電体構造のバンド図を示す。低電界下においては、点線の矢印で示した直接トンネリングを除去することができ、これによって保持状態の期間に良好な電荷保持能力を提供する。一方、図 5 b に示されているような高電界下におけるバンド図のオフセットは、N1 及び O2 の障壁効果を低減することができ、これにより O1 を通した直接トンネリングが起こり得る。少なくとも 1 つの低いホールトンネリング障壁高さの層を有するトンネル誘電体構造は、効率的な FN 消去動作を可能にすることができる。50

## 【0030】

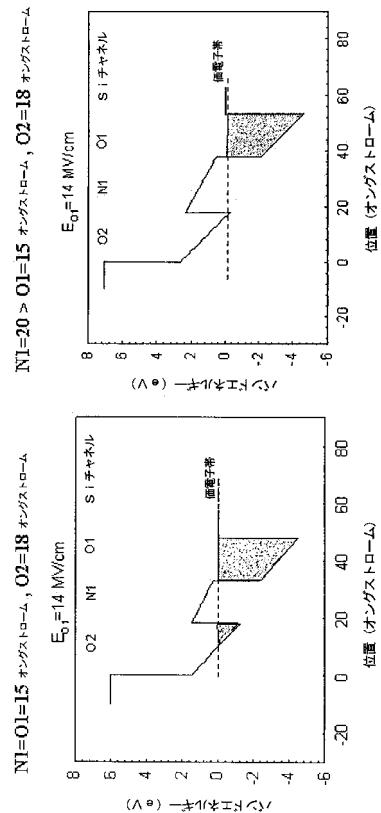

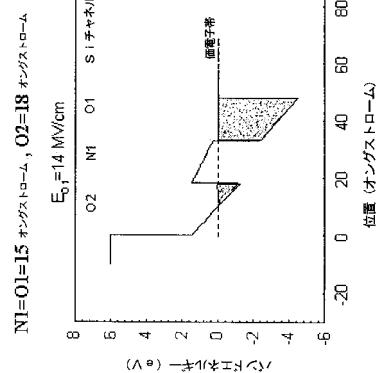

図5c及び図5dは、一例におけるもう一組みのバンド図を示す。一例におけるより良好なバンドオフセット状態のためには、N1の厚さをO1の厚さよりも厚くすることができる。同じ電界E<sub>01</sub>=14MV/cmにおける価電子帯のバンド図がプロットされている。WKB近似によるトンネリング確率は、シャドー領域と相関する。この例では、厚さがN1=O1の場合、バンドオフセットは、O2の障壁を完全には取り除かない。一方、N1>O1の場合、バンドオフセットは、より容易にO1を取り除くことができる。従って、同じO1内の電界の下では、厚さがN1>O1の場合に、ホールトンネリング電流をより大きくすることができる。

## 【0031】

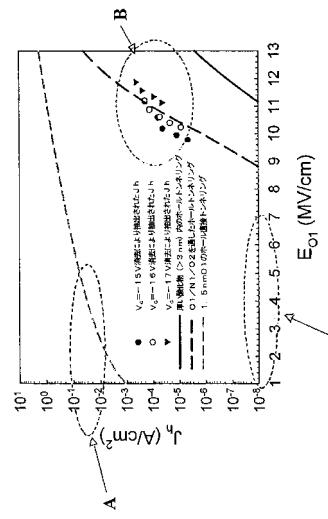

図6に示される、実測及びシミュレーションされたホールトンネリング電流の実験は、本発明の特定の実施形態に従うトンネル誘電体構造を通過するホールトンネリングを更に説明する。例えば、O1/N1/O2誘電体を通したホールトンネリング電流は、極薄酸化物についてのそれと、厚い酸化物についてのそれとの間の値になり得る。一例では、高電界下において、そのホールトンネリング電流は、極薄酸化物についてのそれとほぼ等しいことがある。しかし、低電界下においては、直接トンネリングを抑制することができる。図6に示されるように、たった1MV/cmの低電界強度においてさえ、薄い酸化物層を通したホールトンネリング電流は検出される。比較的高い電界強度、例えば11~13mV/cmにおいてさえ、厚い酸化物を通したホールトンネリング電流は無視できるほど小さい。しかし、高電界強度の存在時に、ONONトンネル誘電体構造を通したホールトンネリング電流は、薄い酸化物層についてのそれに近付く。図6において、低電界下における極薄酸化物を通したホールトンネリングによる大きな電流リークは、グラフの領域Aに見ることができる。図6において、高電界強度におけるO1/N1/O2トンネル誘電体構造を通したホールトンネリング電流は、グラフの領域Bに見ることができる。図6において、低電界におけるO1/N1/O2トンネル誘電体構造及び厚い酸化物を通した事実上存在しないトンネリング電流は、グラフの領域Cに見ることができる。

## 【0032】

本発明に従うメモリセル設計は、これに限定されるものではないが、NOR及び/又はNAND型のフラッシュメモリを含む、各種のメモリタイプへ適用することができる。

## 【0033】

上述したように、トンネル誘電体層は、低いホールトンネリング障壁高さを提供するとのできる1つの層を含む、2つ以上の層を有していてよい。一例では、低いホールトンネリング障壁高さを提供する層は、窒化ケイ素を含んでいてよい。この層は2つの酸化ケイ素層の間に挟まれていてよく、これにより、窒化ケイ素が中間層として用いられる場合にはO/N/Oトンネル誘電体を形成することができる。本発明の特定の好ましい実施形態においては、トンネル誘電体構造内の各層の厚さは、最大で約4nmまで(約4nm以下)である。いくつかの好ましい実施形態においては、トンネル誘電体構造内の各層は、約1nmから3nmの厚さを有し得る。一つの典型的なデバイスにおいては、3層構造は、約10から30の酸化ケイ素層などの下端層、約10から30の窒化ケイ素層などの中間層、及び約10から30の別の酸化ケイ素層などの上端層を有していてよい。一つの特定の例においては、15の下端酸化ケイ素層、20の中間窒化ケイ素層、及び18の上端酸化ケイ素層を有するO/N/Oの3層構造を用いることができる。

## 【0034】

一例では、薄いO/N/Oの3層構造は、無視できるほど小さい電荷捕捉を示す。図5a、図5b及び図6を参照して説明したように、理論的なバンド図及びトンネリング電流の分析は、各層の厚さが3nm以下のO1/N1/O2構造などのトンネル誘電体構造が、保持期間における低電界下でのホールの直接トンネリングを抑制可能であることを示唆することができる。そうでありながら、高電界下においては、依然として効率的なホールトンネリングを可能とすることができます。これは、バンドオフセットにより、N1及びO2のトンネリング障壁を効果的に取り除くことができるためであると考えられる。従って

10

20

30

40

50

、本提案のデバイスは、高速ホールトンネリング消去を可能としながら、従来のSONOSデバイスの保持性能上の問題を回避することができる。実験による分析は、本発明の多様な実施形態に従うメモリセルの優れた耐久特性及び保持特性を示す。

#### 【0035】

特定の好ましい実施形態においては、トンネル誘電体構造は、少なくとも1つの中間層と、その中間層の両側面（対向する側面）上の2つの隣接層とを有する。中間層及び2つの隣接層の各層は、第1の材料及び第2の材料を含む。第2の材料は、第1の材料の価電子帯エネルギー準位よりも大きい価電子帯エネルギー準位を有し、又第2の材料は、第1の材料の伝導帯エネルギー準位よりも小さい伝導帯エネルギー準位を有する。又、第2の材料の濃度は、2つの隣接層におけるよりも中間層において高く、第1の材料の濃度は、中間層におけるよりも2つの隣接層において高い。本発明のこの実施形態に従うトンネル誘電体構造においては、好ましくは、第1の材料は酸素及び/又は酸素含有化合物を含み、第2の材料は窒素及び/又は窒素含有化合物を含む。例えば、第1の材料は、酸化ケイ素などの酸化物を含むことができ、第2の材料は、 $\text{Si}_3\text{N}_4$ 又は $\text{Si}_x\text{O}_y\text{N}_z$ などの窒化物を含むことができる。10

#### 【0036】

本発明のこの態様に従うトンネル誘電体は3つ以上の層から成っていてよく、最小のホールトンネリング障壁高さを有する材料の濃度が、2つの隣接層におけるよりも中間層内において高い限り、全ての層が類似の成分（例えば、Si、N及びO）を含んでいてよい。20

#### 【0037】

本発明の上述の実施形態に従う特定のトンネル誘電体構造においては、第2の材料は、中間層における第2の材料の濃度が一方の隣接層／中間層界面から中間層内のある深度位置での最大濃度まで増加し、又その最大濃度深度位置から他方の隣接層／中間層界面でのより低い濃度まで低下するような勾配の濃度にて中間層内に存在することができる。濃度の増減は漸進的であることが好ましい。

#### 【0038】

本発明の更に他の実施形態において、トンネル誘電体構造は、少なくとも1つの中間層と、その中間層の両側面（対向する側面）上の2つの隣接層とを有する。2つの隣接層は第1の材料を含み、中間層は第2の材料を含む。第2の材料は、第1の材料の価電子帯エネルギー準位よりも大きい価電子帯エネルギー準位を有し、又第2の材料は、第1の材料の伝導帯エネルギー準位よりも小さい伝導帯エネルギー準位を有する。又、第2の材料は、中間層における第2の材料の濃度が一方の隣接層／中間層界面から中間層内のある深度位置での最大濃度まで増加し、又その最大濃度深度位置から他方の隣接層／中間層界面でのより低い濃度まで低下するような勾配の濃度にて中間層内に存在する。濃度の増減は漸進的であることが好ましい。本発明のこの実施形態に従うトンネル誘電体構造においては、好ましくは、第1の材料は酸素及び/又は酸素含有化合物を含み、第2の材料は窒素及び/又は窒素含有化合物を含む。例えば、第1の材料は、酸化ケイ素などの酸化物を含むことができ、第2の材料は、 $\text{Si}_3\text{N}_4$ 又は $\text{Si}_x\text{O}_y\text{N}_z$ などの窒化物を含むことができる。30

#### 【0039】

例えば、トンネル誘電体層が3層ONO構造を有する本発明の実施形態においては、下端酸化物層及び上端酸化物層は二酸化ケイ素を含むことができ、中間の窒化物層は例えば酸窒化ケイ素（シリコンオキシナイトライド）及び窒化ケイ素から成っていてよく、同層内における窒化ケイ素（即ち、2つの材料のうち、より小さいホールトンネリング障壁高さを有する材料）の濃度は一定ではなく、むしろその層を挟んでいる酸化物層との2つの界面の間の層内のある深度位置における最大値に達する。

#### 【0040】

最小のホールトンネリング障壁高さを有する材料がその最大濃度に達する中間層内の正確な位置は臨界的なものではなく、それは、濃度勾配内に存在して、又中間層内のある位40

置でトンネル誘電体層内におけるその最大濃度に達しさえすればよい。

#### 【0041】

最小のホールトンネリング障壁高さを有する材料の濃度を傾斜させることは、不揮発性メモリデバイス、特にSONONOS、又はSONONOS類似の構造を有する不揮発性メモリデバイスの種々の特性を改善する上で有利に働き得る。例えば、保持状態における電荷損失を低減することができ、高電界下におけるホールトンネリングを改善することができ、又、それが起こり得る範囲内でトンネル誘電体における電荷捕捉を防止することができる。

#### 【0042】

トンネル誘電体層のバンド図は、本発明のこの態様に従って、中間層の価電子帯のエネルギー準位及び伝導帯のエネルギー準位が一定値を有さず、むしろ最小のホールトンネリング障壁高さを有する材料の濃度によって層の厚さ方向に沿って変化するように好適に変更することができる。図5eを参照すると、本発明のこの態様に従うONOの3層のトンネル誘電体の変更が、バンド図によって示されている。中間層(層-2)は窒化ケイ素から成る。外側の層(層-1及び層-3)は二酸化ケイ素から成る。層-2における窒化ケイ素の濃度は変化させられ、これにより、価電子帯のエネルギー準位、伝導帯のエネルギー準位は、窒化ケイ素の濃度が最大となる層-2内の深度で、それぞれ最大値、最小値に達する。考えられる3つの窒化ケイ素濃度勾配が図5eに示されている。図示された破線は、濃度勾配によって得られる、変化する価電子帯と伝導帯のエネルギー準位を表す。図5eに示されるように、破線上の円は層-2内の3つの別個の最大窒化ケイ素濃度を表しており、最低の価電子帯エネルギー準位と最高の伝導帯エネルギー準位は、窒化ケイ素の濃度最大値と合致している。

10

20

30

#### 【0043】

本発明のこのような実施形態に従う多層トンネル誘電体構造は、様々な方法で作製することができる。例えば、第1の二酸化ケイ素層又は酸窒化ケイ素層は、これに限定されるものではないが、化学蒸着(CVD)法、並びに、熱酸化、ラジカル(ISSG)酸化、及びプラズマ酸化/窒化を含む任意の数の従来の酸化手法を用いて形成することができる。次いで、SiNの傾斜濃度を有する中間層は、例えば、化学蒸着法、又は別法では、第1の層の頂部上に形成された余分な酸化物又は酸窒化物のプラズマ窒化によって形成することができる。次いで、第3の層である上側の酸化物層は、例えば、酸化又は化学蒸着によって形成することができる。

30

#### 【0044】

次いで、電荷蓄積層を、トンネル誘電体構造の上方に形成することができる。一例では、約5nmから10nmの電荷蓄積層を、トンネル誘電体構造の上方に形成することができる。一つの特定の例では、厚さが約7nm以上の窒化ケイ素層を使用することができる。電荷蓄積層より上の絶縁層は、厚さが約5nmから12nmであってよい。例えば、厚さが約9nm以上の酸化ケイ素層を使用することができる。又、この酸化ケイ素層は、酸化ケイ素層を形成するように窒化物層の少なくとも一部を熱処理変換することによって形成することができる。本明細書に記載される好適な材料の層を形成するためには、既知の又はこれから開発されるであろう任意の方法を用いることができ、それにより、トンネル誘電体層、電荷蓄積層及び/又は絶縁層を堆積又は形成することができる。好適な方法は、例えば、熱成長法及び化学蒸着法を含む。

40

#### 【0045】

一例では、加熱変換処理は、高密度又は濃度の界面トラップを提供することができ、これによりメモリデバイスの捕捉効率を向上させることができる。例えば、窒化物の加熱変換は、ゲート流量比をH<sub>2</sub>:O<sub>2</sub>=1000:4000scmとして、1000(Cにおいて実施することができる。

#### 【0046】

更に、窒化ケイ素は一般に非常に低いホール障壁(約1.9eV)を有するため、高電界下においてホールトンネリングに対して無抵抗(透過的)になり得る。一方、ONO構

50

造などのトンネル誘電体の全体の厚さは、低電界下における電子の直接トンネリングを防止することができる。一例では、この非均衡的挙動は、高速ホットトンネリング消去だけではなく、保持期間における電荷リークの低減又は除去をも提供するメモリデバイスを与えることができる。

#### 【0047】

典型的なデバイスは、 $0.12 \mu\text{m}$  N R O M / N B i t 技術によって製造することができる。表1は、一例におけるデバイス構造及びパラメータを示す。提示した極薄O/N/Oを有するトンネル誘電体は、ホールトンネリング電流を変更することができる。一例では、より厚い( $7 \text{ nm}$ )N2層は電荷捕捉層として働くことができ、又O3( $9 \text{ nm}$ )層はブロッキング層として働くことができる。N2及びO3は両方とも、N R O M / N B i t 技術を使用して製造することができる。10

#### 【0048】

【表1】

表1

| 層                          | 概略厚さ(オングストローム) |

|----------------------------|----------------|

| 下端の酸化物(O1)                 | 15             |

| 中間の窒化物(N1)                 | 20             |

| 中間の酸化物(O2)                 | 18             |

| 捕捉窒化物(N2)                  | 70             |

| ブロッキング酸化物(O3)              | 90             |

| ゲート: $\text{N}^+$ -ポリシリコン  |                |

| チャネル長さ: $0.22 \mu\text{m}$ |                |

| チャネル幅: $0.16 \mu\text{m}$  |                |

#### 【0049】

本発明の特定の実施形態においては、ゲートは、 $\text{N}^+$ -ポリシリコンの仕事関数よりも大きな仕事関数を有する材料を含むことができる。本発明の特定の好ましい実施形態においては、このような高仕事関数ゲート材料は、例えば、白金、イリジウム、タングステン、及びその他の貴金属などの金属を含むことができる。好ましくは、このような実施形態におけるゲート材料は、約 $4.5 \text{ eV}$ 以上の仕事関数を有する。特定の好ましい実施形態においては、ゲート材料は、例えば、白金又はイリジウムなどの高仕事関数金属を含む。更に、好ましい高仕事関数材料は、これに限定されるものではないが、 $\text{P}^+$ -ポリシリコン、及び、例えば窒化チタン及び窒化タンタルなどの金属窒化物を含む。本発明の特に好ましい実施形態においては、ゲート材料は白金を含む。30

#### 【0050】

高仕事関数ゲート材料を有する本発明の実施形態に従う典型的なデバイスもまた、 $0.12 \mu\text{m}$  N R O M / N B i t 技術によって製造することができる。表2は、一例におけるデバイス構造及びパラメータを示す。提示した極薄O/N/Oを有するトンネル誘電体は、ホールトンネリング電流を変更することができる。一例では、より厚い( $7 \text{ nm}$ )N2層は電荷捕捉層として働くことができ、又O3( $9 \text{ nm}$ )層はブロッキング層として働くことができる。N2及びO3は両方とも、N R O M / N B i t 技術を使用して製造することができる。40

#### 【0051】

【表2】

表2

| 層                      | 概略厚さ(オングストローム) |

|------------------------|----------------|

| 下端の酸化物                 | 15             |

| 中間の窒化物                 | 20             |

| 中間の酸化物                 | 18             |

| 捕捉窒化物(N <sub>2</sub> ) | 70             |

| ブロックキング酸化物             | 90             |

| ゲート：白金                 |                |

| チャネル長さ：0.22 μm         |                |

| チャネル幅：0.16 μm          |                |

10

## 【0052】

本発明の高仕事関数ゲート材料を使用した実施形態に従うメモリセルは、他の実施形態よりも更に改善された消去特性を示す。高仕事関数ゲート材料は、捕捉層内へのゲート電子注入を抑制する。メモリセルがN<sup>+</sup>ポリシリコンゲートを有する本発明の特定の実施形態においては、消去期間における電荷捕捉層内へのホールトンネリングは、ゲート電子注入と同時に発生する。この自己収束消去効果は、NAND用途においては望ましくないことがある、消去された状態におけるより高い閾電圧レベルを招く。本発明の高仕事関数ゲート材料を使用した実施形態に従うメモリセルは、例えば、NOR型及びNAND型のメモリを含む種々のタイプのメモリ用途において使用することができる。しかし、本発明の高仕事関数ゲート材料を使用した実施形態に従うメモリセルは、消去ノリセットされた状態における上昇された閾電圧が望ましくないことがあるNAND用途における使用に特に適している。本発明の高仕事関数ゲート材料を使用した実施形態に従うメモリセルは、ホールトンネリング方法によって、又好ましくは-FN消去動作によって、消去することができる。

20

## 【0053】

ONOトンネリング誘電体及びN<sup>+</sup>ポリシリコンゲートを有する典型的なデバイスは、従来のSONOS又はNROM方法によってプログラムすることができ、又チャネルFNホールトンネリングによって消去することができる。図7aは、一例においてONOトンネリング誘電体を有する典型的なSONONOSデバイスの消去特性を示す。図7aを参照して、より高いゲート電圧は、より速い消去速度をもたらす。又、ゲート注入もより強力であり、その結果生じる動的平衡点(ダイナミックバランスポイント)(これはV<sub>t</sub>を決定する)がより高いため、より高い飽和V<sub>t</sub>をも有する。これは、グラフの右側に示されており、閾電圧が、消去ゲート電圧に応じて約3ボルトから約5ボルトまでの電圧において最小値に達している。ホールトンネリング電流は、図7aにおける曲線の微分による過渡解析手法(非定常解析法)によって抽出することができる。図7aにおける測定値から抽出されたホール電流は、前述した図6に示されている。比較のために、WKB近似を用いてシミュレートされたホールトンネリング電流もプロットされている。実験結果は、我々の予測と妥当に一致している。O1/N1/O2積層体を通したトンネリング電流は、高電界下においては極薄O1についてのそれに近づき、一方低電界下においては消される。

30

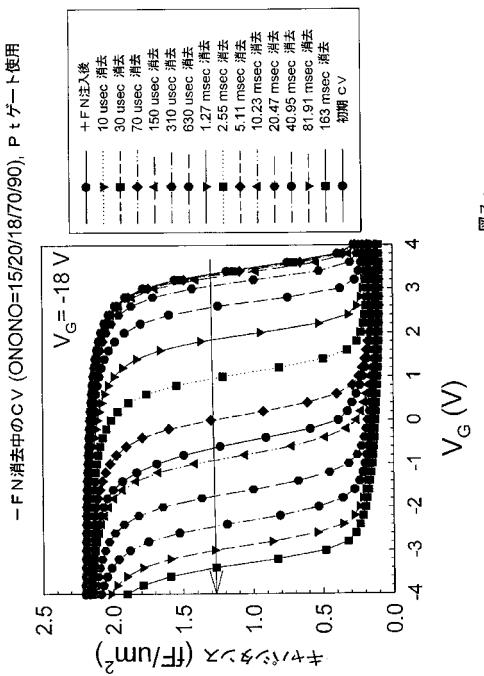

## 【0054】

高仕事関数ゲート材料を有する本発明のメモリセルの特定の実施形態においては、高仕事関数ゲートがゲート電子注入を抑制し、消去又はリセットされた状態におけるデバイスの閾電圧を非常に低くすることが可能であり、又消去時間に応じて負にすることさえもで

40

50

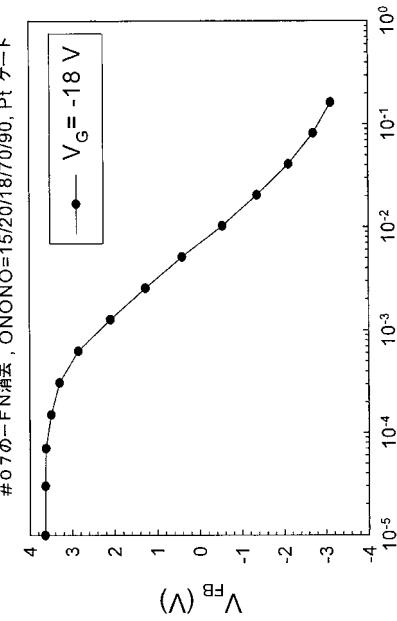

きる。図 7 b に、ゲートが白金から成り、トンネル誘電体層が 15 / 20 / 18 オングストロームの ONO 構造を有する本発明の一実施形態に従うメモリデバイスの閾電圧値を示す。図 7 b に示されるように、- FN 消去動作期間における同様のゲート電圧 (- 18 V) にて、デバイスの閾電圧を - 3 V 以下に設定することができる。このデバイスについて、対応するキャパシタンス (容量) とゲート電圧値との関係を図 7 c に示す。

#### 【 0 0 5 5 】

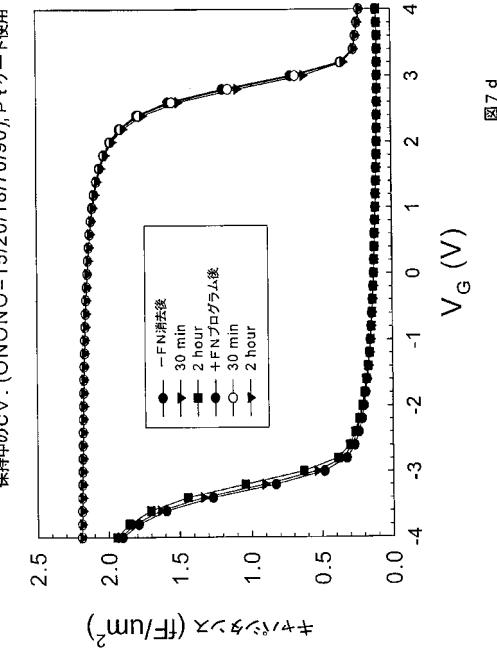

更に、本発明の高仕事関数ゲート材料を使用した実施形態に従うメモリデバイスの保持特性は改善される。白金ゲートを有するメモリデバイスの保持特性を、容量がゲート電圧の関数として、消去及びプログラム後、及びその各動作の 30 分後並びに各動作の 2 時間後についてグラフ化されている図 7 d に示す。極めて小さい偏差が観察される。

10

#### 【 0 0 5 6 】

本発明の種々の実施形態に従うメモリセルは、少なくとも 2 つの別個の方法 (スキーム) で動作させることができる。例えば、1 セル当たり 2 ビット (即ち、2 bits / cell 11) の動作を実行するために、逆読み出しを伴う CHE プログラミング (モード 1) を使用することができる。更に、1 セル当たり 2 ビットの動作のために、低電力 (低出力) + FN プログラミング (モード 2) を使用することもできる。いずれのモードも、同じホールトンネリング消去方法を使用することができる。モード 1 は、NOR 型フラッシュメモリのためのバーチャルグランドアレイアーキテクチャのために好適に使用することができる。モード 2 は、NAND 型フラッシュメモリのために好適に使用することができる。

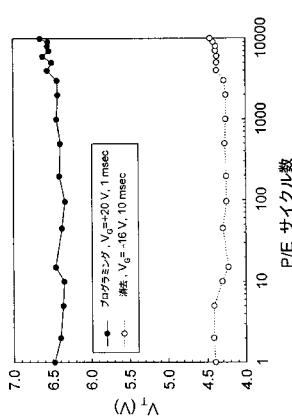

#### 【 0 0 5 7 】

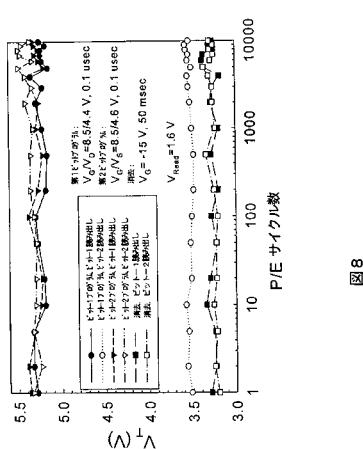

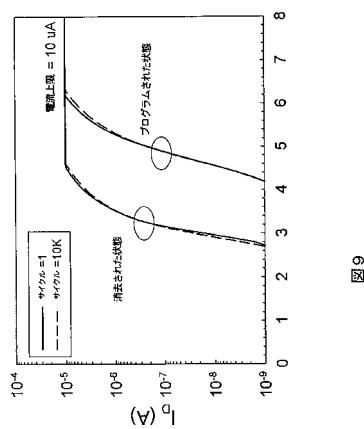

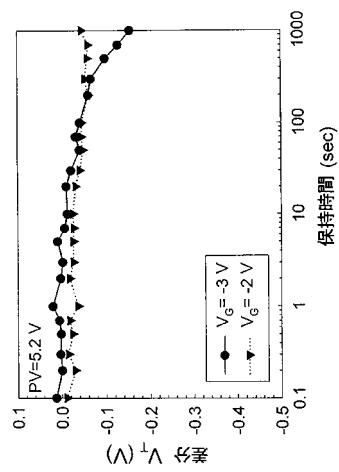

一例として、図 8 は、モード 1 動作における、本発明の一実施形態に従うバーチャルグランドアレイアーキテクチャ NOR 型フラッシュメモリの優れた耐久特性を示す。トンネル誘電体構造を有するこのようなメモリデバイスの消去の劣化は、ホールトンネリング消去 ( $V_g = - 15 V$ ) が均一チャネル消去方法であるので生じない。対応する I-V 曲線も図 9 に示す。同図は、多数の P/E サイクルの後にデバイスの劣化がほとんどないことを示唆する。一例では、これは、極薄酸化物 / 窒化物層が良好なストレス免除特性を有するためであると考えられる。更に、このメモリデバイスは、ホットホール起因のダメージが加えられることがない。図 10 には、モード 2 動作における、本発明の一実施形態に従う NAND 型フラッシュメモリの耐久特性が示されている。より速い収束消去時間のために、より大きなバイアス ( $V_g = - 16 V$ ) を使用することができる。この例においても、優れた耐久性が得られる。

20

#### 【 0 0 5 8 】

図 4 には、本発明の一実施形態に従う典型的な SONONOS デバイスの電荷保持性能が示されている。同図においては、100 時間後に、たった 60 mV の電荷損失が観察される。従来の SONOS デバイスよりも数桁規模良好な、保持特性の改善が得られる。VG 加速保持試験もまた、低電界下において直接トンネリングが抑制され得ることを示す。図 11 は、10K 回の P/E サイクルを行ったデバイスに関する VG 加速保持試験の一例を示す。1000 秒ストレス後の - VG ストレスにおいて電荷損失は小さく、低電界におけるホールの直接トンネリングが抑制され得ることを示す。

30

#### 【 0 0 5 9 】

従って、上述の例において特定される SONONOS 設計は、高速ホールトンネリング消去に、優れた耐久特性をもたらすことができる。前述のように、この設計は、NOR 及び NAND 型の窒化蓄積 (記憶) フラッシュメモリの両方において実現することできる。更に、本発明に従うメモリアレイは、類似又は異なる構成の多数のメモリデバイスを有していてよい。

40

#### 【 0 0 6 0 】

本発明に従うアレイの種々の実施形態においては、本発明に従うメモリセルは、バーチャルグランドアレイアーキテクチャにおいて、従来の ROM 又は SONOS デバイス代わりに用いることができる。ホットホール注入の代わりに FN ホールトンネリングを用いることにより、信頼性の問題及び消去の劣化を解決するか又は低減することができる。本

50

発明の範囲を後述の特定の構造に限定する意図はないが、以下、本発明のメモリアレイによる種々の動作方法を、典型的なNOR型バーチャルグランドアレイアーキテクチャについて説明する。

#### 【0061】

C H E 又は C H I S E L ( c h a n n e l i n i t i a t e d s e c o n d a r y e l e c t r o n ) : チャネルイニシエイティッドセカンダリーエレクトロン ( チャネル開始 2 次電子 ) ) プログラミング及び逆読み出しを、 1 セル当たり 2 ビットのメモリアレイのために用いることができる。又、消去方法は、均一チャネル FN ホールトンネリング消去であってよい。一例では、アレイアーキテクチャは、バーチャルグランドアレイ又は J T O X アレイであってよい。図 12 a ~ 図 20 を参照して、トンネル誘電体としては、ホールの直接トンネリングを提供するように各層が約 3 nm 以下の厚さを有する O1 / N1 / O2 の 3 層構造を用いることができる。図 12 a ~ 図 20 を参照して、 N2 は、高い捕捉効率を提供するように厚さが 5 nm より厚くてよい。絶縁層である O3 は、 O3 と N2 との間の界面における大きなトラップ密度を提供するように、湿式変換された上端酸化物 ( 酸化ケイ素 ) などの、湿式酸化によって形成された酸化ケイ素層であってよい。 O3 は、この酸化ケイ素層からの電荷損失を防止するように、厚さが約 6 nm 以上であってよい。

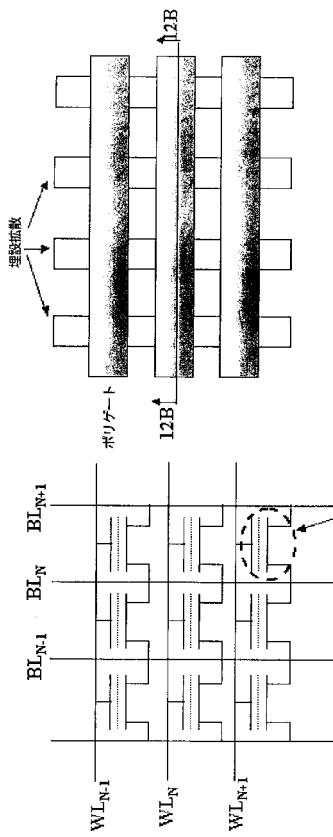

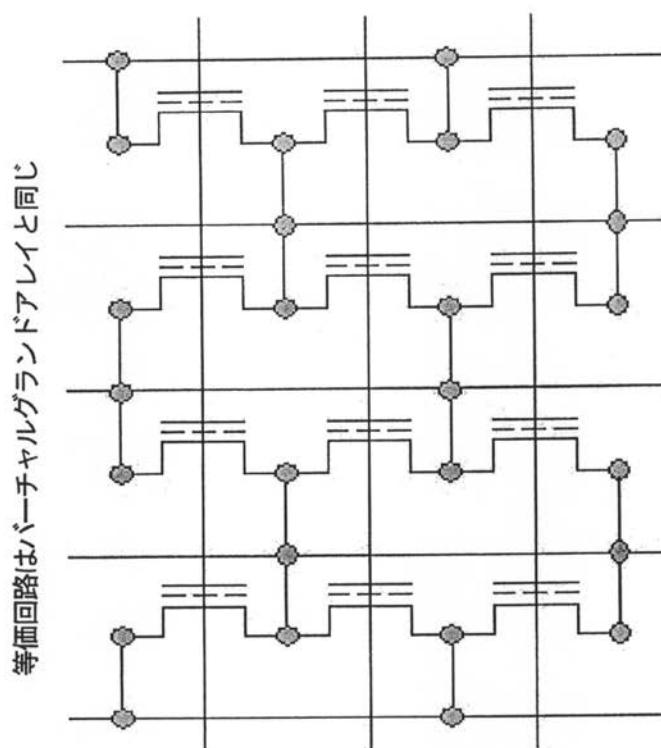

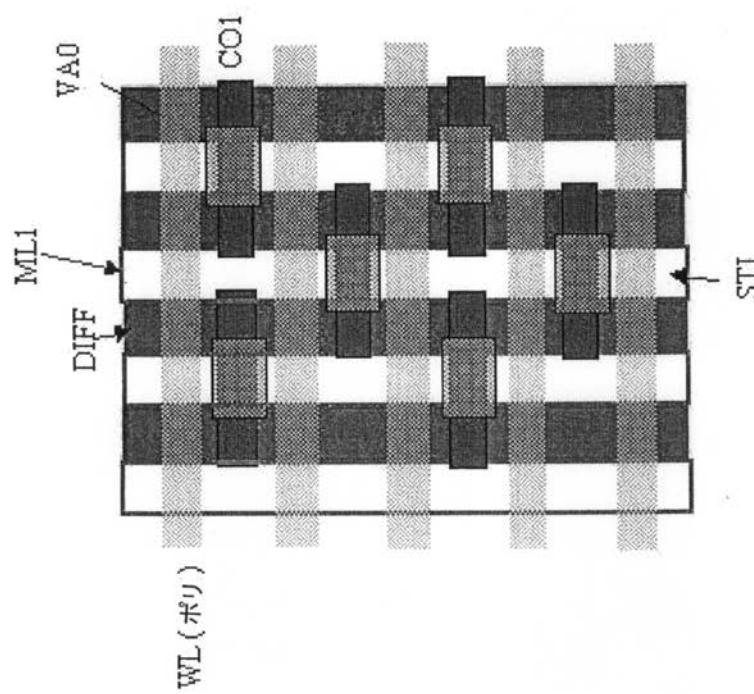

#### 【0062】

図 12 a 及び図 12 b は、 3 層 ONO トンネル誘電体を有するメモリセルなどの、上述したメモリセルを組み込んだバーチャルグランドアレイアーキテクチャの一例を示す。特に、図 12 a は、メモリアレイの一部分の等価回路を示し、図 12 b は、メモリアレイの一部分の典型的なレイアウトを示す。

#### 【0063】

更に、図 13 は、アレイ内に組み込まれた数個のメモリセルの概略断面図を示す。一例では、埋設拡散 ( B D : b u r i e d d i f f u s i o n ) 領域は、メモリセルのソース又はドレイン領域のための N<sup>+</sup> ドープジャンクション ( 接合 ) であってよい。基板は、 p 型基板であってよい。一例では、 - FN 消去期間に起こり得る B D O X 領域 ( B D より上の酸化物 ) の破壊 ( ブレークダウン , 絶縁破壊 ) を避けるために、厚い B D O X (> 50 nm) を用いることができる。

#### 【0064】

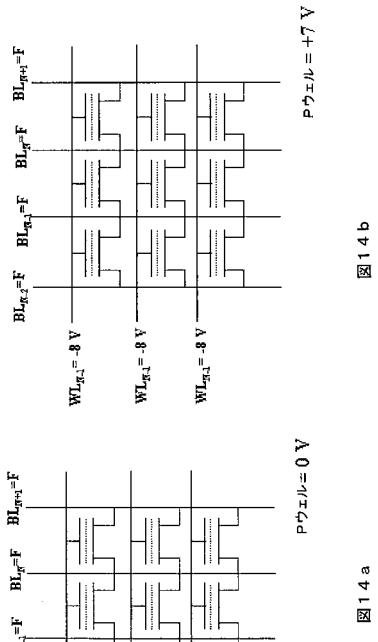

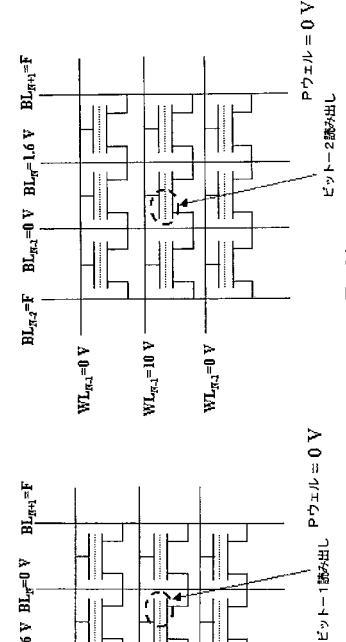

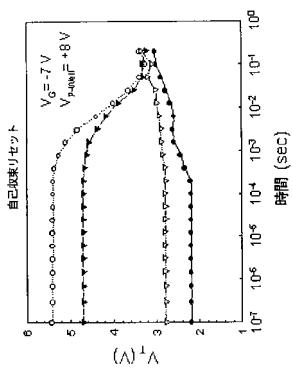

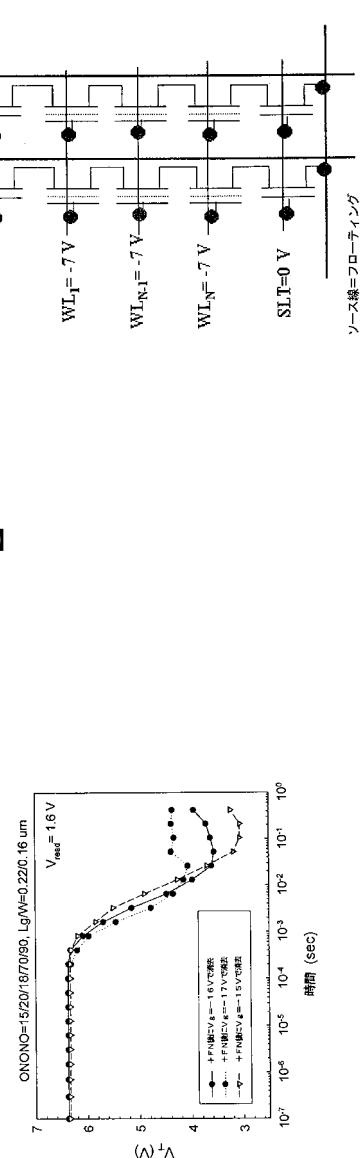

図 14 a 及び図 14 b は、上述したトンネル誘電体設計を有する 1 セル当たり 2 ビット ( 即ち、 2 bits / c e l l ) のメモリセルを組み込んだ典型的なバーチャルグランドアレイのための、考えられる電気的リセット方法 ( スキーム ) を示す。更なる P / E サイクルを実行する前に、全てのデバイスは先ず電気的な「リセット」を受けることができる。リセット処理は、同一アレイ内のメモリセル群における Vt の一様性を確保することができ、又デバイスの Vt を収束消去された状態へと上げることができる。例えば、図 14 a に示すような、 1 秒間の Vg = - 15 V の印加は、窒化ケイ素の電荷捕捉層内へいくらかの電荷を注入して、動的平衡状態に到達させる効果を有し得る。リセットにより、例えばそれらの製造工程期間におけるプラズマ帶電効果などにより不均一に帶電されたメモリセル群であっても、それらの Vt を収束させる ( 満える ) ことができる。自己収束バイアス条件を生成するための別の方法は、ゲート電圧及び基板電圧の両方に対してバイアスをかけることである。例えば、図 14 b を参照して、 Vg = - 8 V 、及び P ウェル ( P - w e l l : P 型ウェル ) = + 7 V を印加することができる。

#### 【0065】

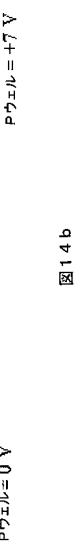

図 15 a 及び図 15 b は、上述したトンネル誘電体設計を有する 1 セル当たり 2 ビットのメモリセルを組み込んだ典型的なバーチャルグランドアレイのためのプログラミング方法 ( スキーム ) を示す。デバイスをプログラムするために、チャネルホットエレクトロン ( C H E ) プログラミングを用いることができる。図 15 a に示されるビット - 1 のプログラミングのためには、電子は、 BLN ( ビット線 N ) の上のジャンクションエッジ内へ局所的に注入される。図 15 b に示されるビット - 2 のプログラミングのためには、電子

10

20

30

40

50

は、B L N - 1 の上に蓄えられる。W L (ワード線) のための典型的なプログラミング電圧は、約 6 V から 12 V である。B L (ビット線) のための典型的なプログラミング電圧は約 3 V から 7 V であり、又 P ウェルは接地された状態にしておくことができる。

#### 【 0 0 6 6 】

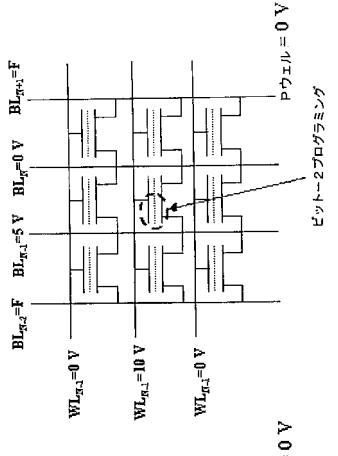

図 16 a 及び図 16 b は、上述したトンネル誘電体設計を有する 1 セル当たり 2 ビットのメモリセルを組み込んだ典型的なバーチャルグランドアレイのための読み出し方法(スキーム)を示す。一例では、デバイスを読み出して、1 セル当たり 2 ビットの動作を実行するために、逆読み出しが用いられる。図 16 a を参照して、ビット - 1 の読み出しのためには、1 . 6 V などの適当な読み出し電圧が B L N - 1 に印加される。図 16 b を参照して、ビット - 2 の読み出しのためには、1 . 6 V などの適当な読み出し電圧が B L N に印加される。一例では、読み出し電圧は、約 1 V から 2 V の範囲内にあってよい。ワード線及び P ウェルは、接地された状態にしておくことができる。しかし、V s を上げて逆に読み出す方法( raised - V s reverse read method )などの他の変更された読み出し方法(スキーム)を実行することもできる。例えば、V s を上げて逆に読み出す方法は、ビット - 2 の読み出しのためには  $V_d / V_s = 1 . 8 / 0 . 2 V$  、又ビット - 1 の読み出しのためには  $V_d / V_s = 0 . 2 / 1 . 8$  を用いることができる。

#### 【 0 0 6 7 】

図 14 a 及び図 14 b はまた、上述したトンネル誘電体設計を有する 1 セル当たり 2 ビットのメモリセルを組み込んだ典型的なバーチャルグランドアレイのためのセクタ消去方法(スキーム)を示す。一例では、メモリセル群を同時に消去するために、チャネルホールトンネリング消去によるセクタ消去を適用することができる。SONONOS 構造を有するメモリセル内のONOトンネル誘電体は、約 10 ~ 50 msec 及び自己収束チャネル消去速度にて起こり得る高速消去を提供することができる。一例では、セクタ消去動作条件は、リセット処理と同様とすることができる。例えば、図 14 a を参照して、W L 群に同時に  $V_G = \text{約} - 15 V$  を印加し、又 B L 群を全てフローティング状態にしておくことにより、セクタ消去を達成することができる。P ウェルは、接地された状態にしておくことができる。

#### 【 0 0 6 8 】

或いは、図 14 b を参照して、W L 群に約 - 8 V を印加し、又 P ウェルに約 + 7 V を印加することによっても、セクタ消去を達成することができる。いくつかの例においては、完全なセクタ消去動作を、如何なる過剰消去(over-erase)又は消去困難(hard-to-erase: 消去不足)のセルをも有することなく、100 msec 以内に実行することができる。上述のデバイス設計は、優れた自己収束特性をもたらすチャネル消去を容易にすることができる。

#### 【 0 0 6 9 】

図 17 は、SONONOS デバイスを用いる一例における消去特性を示す。SONONOS デバイスの一例は、O 1 / N 1 / O 2 / N 2 / O 3 の厚さがそれぞれ約 15 / 20 / 18 / 70 / 90 オンゲストロームであってよく、N<sup>+</sup>ポリシリコンゲート及び O 3 としての加熱変換された上端酸化物を有していてよい。種々のゲート電圧に対する消去速度が示されている。ゲート電圧がより高いと、消去速度がより高速になる。

#### 【 0 0 7 0 】

しかし、収束した V<sub>t</sub> もまた、より高い。これは、より高いゲート電圧の下では、ゲート注入がよりアクティブであるからである。ゲート注入を低減するためには、消去期間においてゲートから注入される電子を低減するように、ゲート材料として P<sup>+</sup>ポリシリコンゲート又は高仕事関数を有するその他の金属ゲートを代わりに使用することができる。

#### 【 0 0 7 1 】

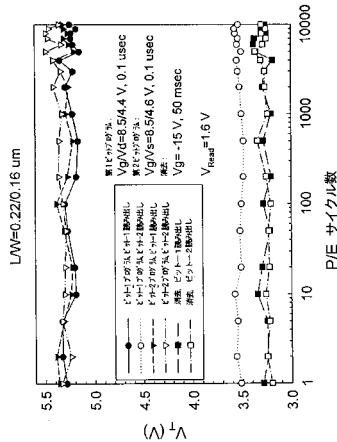

図 18 は、バーチャルグランドアレイアーキテクチャにおいて SONONOS デバイスを用いた場合の耐久特性を示す。いくつかの例における耐久特性は優れている。プログラミング条件は、ビット - 1 に対しては  $V_g / V_d = 8 . 5 / 4 . 4 V$  、  $0 . 1 \mu sec$  で

10

20

30

40

50

あり、ビット - 2 に対しては  $V_g / V_s = 8.5 / 4.6 \text{ V}$ 、 $0.1 \mu\text{sec}$  である。F N 消去は、約  $50 \text{ msec}$  間の  $V_g = -15 \text{ V}$  を使用することができ、2 ビットを同時に消去することができる。F N 消去は、自己収束均一チャネル消去であるため、消去不足又は過剰消去のセルは通常存在しない。いくつかの例においては、上述して提示したデバイスは、プログラム / 消去の確認（検証）又はステッピングアルゴリズムを用いなくても、優れた耐久特性を示す。

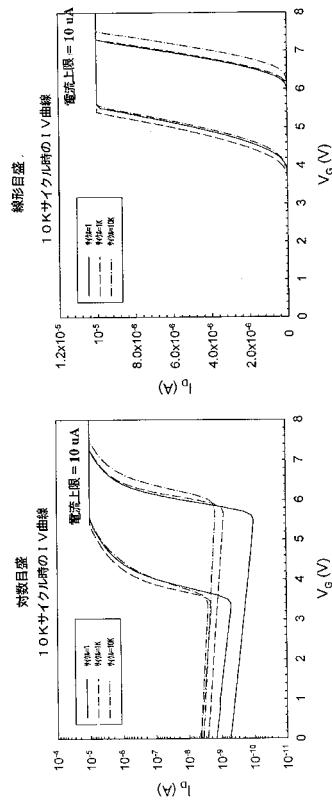

#### 【0072】

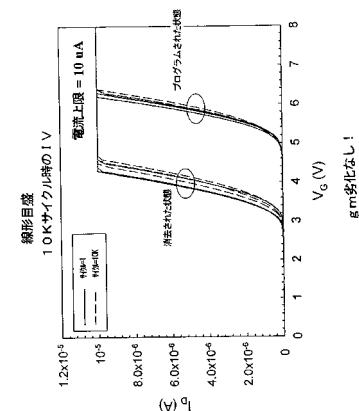

図 19 a 及び図 19 b は、一例における P / E サイクル中の I - V 特性を示す。対応する I - V 曲線が、対数目盛（図 19 a）及び線形目盛（図 19 b）の両方で示されている。一例では、SONONOS デバイスは、多数の P / E サイクルの後に劣化をほとんど有さない。そのため、サブスレショルドスイング（S . S .）及びトランスクンダクタンス（g m）の両方ともが、多数のサイクルの後でもほとんど同じである。この SONONOS デバイスは、N ROM デバイスよりも優れた耐久特性を有する。その要因の 1 つは、ホットホール注入が用いられないことであると考えられる。更に、前述したように、極薄酸化物は、厚いトンネル酸化物よりも良好なストレス耐性を有し得る。10

#### 【0073】

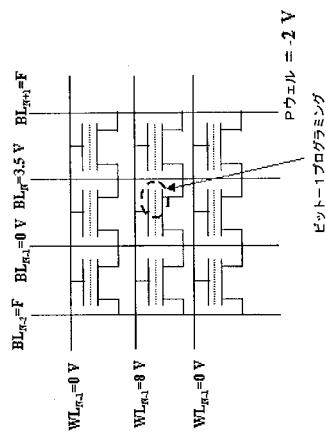

図 20 は、一例における CHISEL プログラミング方法（スキーム）を示す。デバイスをプログラムするための別の方法は、CHISEL プログラミング方法（スキーム）を使用することであり、これはホットキャリア効率を増大させるように負の基板バイアスを用いて衝撃イオン化（衝突電離）を促進する。又、ボディー効果（基板バイアスの効果）によって、プログラミング電流を低減することもできる。同図には典型的な条件が示されており、ここでは基板には負の電圧（-2 V）が印加され、又ジャンクション電圧が約 3.5 V に下げられている。従来の N ROM デバイス及び技術については、チャネルの中央領域付近により多くの電子を注入するため、CHISEL プログラミングを適用することはできない。又、ホットホール消去は、従来の N ROM デバイスにおけるチャネル中央領域付近の電子を除去するのには効果的でない。20

#### 【0074】

図 21 a 及び図 21 b は、一例における JTOX バーチャルグランドアレイ設計を示す。JTOX バーチャルグランドアレイは、メモリアレイ内の SONONOS メモリセルの使用を実現するもう 1 つの方法を提供する。一例において、JTOX 構造とバーチャルグランドアレイとの間で異なる点の一つは、JTOX 構造内のデバイス群が STI 处理（加工）によって分離されていることである。図 21 a には、典型的なレイアウト例が示されている。図 21 b は、対応する等価回路を示しており、これはバーチャルグランドアレイのそれと同じである。30

#### 【0075】

前述したように、本発明に従うメモリセル構造は、NOR 型及び NAND 型のフラッシュメモリの両方に適している。以下、メモリアレイ設計及びその動作方法の更なる例について説明する。本発明の範囲を後述の特定の構造に限定することを意図するものではないが、以下、本発明のメモリアレイによる種々の動作方法を、典型的な NAND アーキテクチャに関して説明する。40

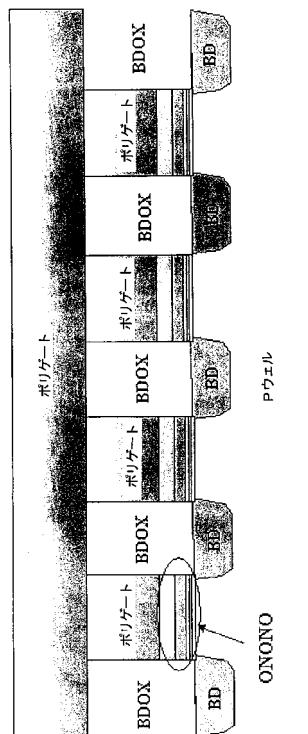

#### 【0076】

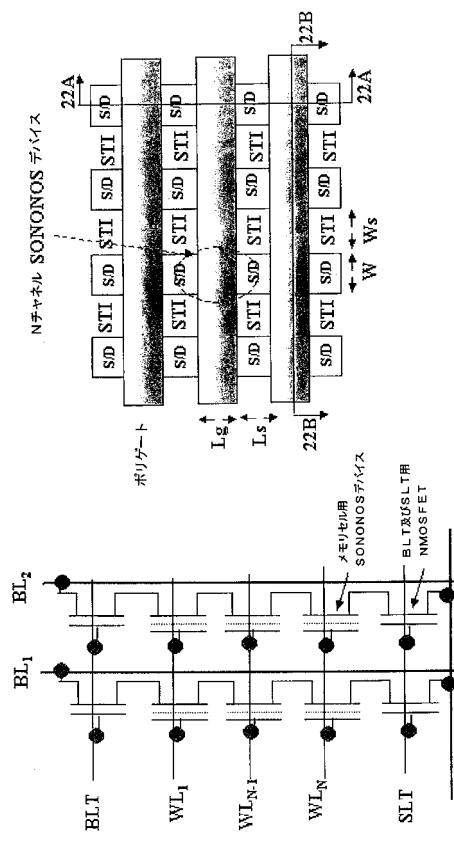

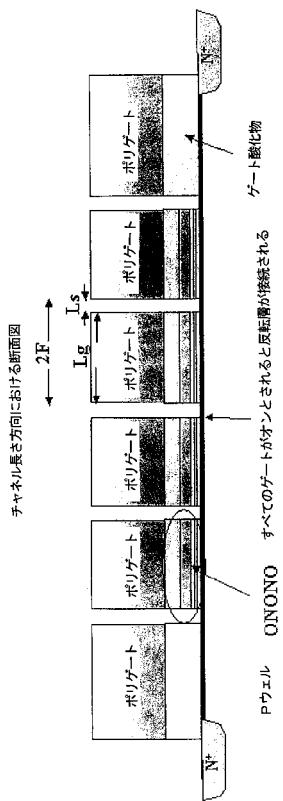

前述したように、ONO トンネリング誘電体を有する n チャネル SONONOS メモリデバイスを、メモリデバイスに利用することができる。図 22 a 及び図 22 b は、NAND アレイアーキテクチャの一例を示す。図 23 a 及び図 23 b は、典型的なメモリアレイ設計を 2 つの異なる方向から見た断面図である。いくつかの例においては、メモリアレイの動作方法は、+ FN プログラミング、自己収束リセット / 消去、及び読み出し方法を含んでいてよい。更に、いくつかの例においては、プログラムディスターブ（プログラム障害）を防止するために、回路動作方法が含まれていてよい。

#### 【0077】

シングルブロックゲート構造設計に加えて、ソース / ドrain 領域に隣接して配置され50

た 2 つ の ト ランジス タゲート間に位置付けられた SONONOS デバイスを用いる NAND アレイなどの、スプリットゲートアレイを用いてもよい。いくつかの例においては、スプリットゲート設計は、デバイス寸法を  $F = 30 \text{ nm}$  以下に縮小することができる。更に、良好な信頼性を得ること、フローティングゲート間の結合効果 (inter-float coupling - gate coupling effect) を低減又は除去すること、又はこれらの両方を達成することができるよう、デバイスを設計することができる。前述したように、SONONOS メモリデバイスは、優れた自己収束消去を提供することができ、これはセクタ消去動作及び  $V_t$  分布の制御に役立つ。更に、タイト化された消去状態分布は、多值用途 (MLC) を容易にすることができます。

## 【0078】

10

メモリアレイ構造のために特定の設計を用いることによって、有効チャネル長 ( $L_{eff}$ ) を大きくして、短チャネル効果 (short-channel effect) を低減又は除去することができる。いくつかの例は、拡散ジャンクションを使用しないで設計することができ、これによりメモリデバイスの製造工程におけるシャロージャンクション（浅い接合）の提供又はポケットインプランテーションの使用において生じる課題を回避することができる。

## 【0079】

図 1 は、SONONOS 設計を有するメモリデバイスの一例を示す。更に、前述の表 1 は、異なる層のために用いられる材料及びその厚さの一例を示す。いくつかの例においては、ゲート注入を低減することによって達成することのできる、より低い飽和リセット / 消去  $V_t$  を提供するように、 $P^+$  ポリシリコンゲートを用いることができる。

20

## 【0080】

図 22a 及び図 22b は、拡散ジャンクションを備え、表 1 に記載される実施形態に従うメモリセルを有する、SONONOS - NAND アレイなどのメモリアレイの一例を示す。一例では、個々のデバイスは、シャロートレンチアイソレーション (STI : shallow-trench isolation) 又はシリコンオンインシュレータ (SOI : silicon-on-insulator) (絶縁体上シリコン) の分離技術を用いるなどの、多様な分離技術によって互いに分離することができる。図 22a を参照して、メモリアレイは、BL1 及び BL2 などの多数のビット線と、WL1、WLN-1 及び WLN などの多数のワード線とを有していてよい。更に、アレイは、ソース線トランジスタ (群) (即ち、ソース線選択トランジスタ (群) 或いは SLT (群)) と、ビット線トランジスタ (群) (即ち、ビット線選択トランジスタ (群) 或いは BLT (群)) とを有していてよい。図示されているように、アレイ内のメモリセルは、SONONOS 設計を用いることができ、又 SLT 及び BLT は、n 型金属酸化膜半導体電界効果トランジスタ (NMOSFET : n-type metal-oxide-semiconductor field-effect transistor) を有していてよい。

30

## 【0081】

図 22b は、NAND アレイなどのメモリアレイのレイアウトの一例を示す。図 22b を参照して、 $L_g$  はメモリセルのチャネル長であり、 $L_s$  はメモリデバイスの個々の線 (ライン) 間の間隔である。更に、W はメモリセルのチャネル幅であり、 $W_s$  は個々のビット線間の分離領域又はソース / ドレイン領域の幅であり、これは一例では STI 幅であつてよい。

40

## 【0082】

図 22a 及び図 22b を再度参照して、メモリデバイスは、順次に接続して NAND アレイを形成することができる。例えば、1列のメモリデバイスは 16 又は 32 個のメモリデバイスを有していてよく、16 又は 32 の列数を提供することができる。BLT (群) 及び SLT (群) は、対応する NAND 列を制御するための選択トランジスタとして使用することができる。一例では、BLT 及び SLT のためのゲート誘電体は、窒化ケイ素捕獲層を含まない酸化ケイ素層であつてよい。このような構成は、全てのケースにおいて必

50

ずしも求められるものではないが、いくつかの例においては、メモリアレイの動作中に起きることのある B L T 及び S L T の V t シフトを防止することができる。別法として、B L T 及び S L T は、それらのゲート誘電体層として、O N O N O 層の組み合わせを用いることができる。

#### 【 0 0 8 3 】

いくつかの例においては、B L T 及び S L T に印加されるゲート電圧は、ゲートディスターブ（ゲート阻害）をほとんど引き起こすことがないと考えられる 10 V 未満とすることができます。B L T 及び S L T のゲート誘電体層が帯電されるか又は電荷捕捉されることがあるケースにおいては、追加の - V g 消去を B L T 又は S L T のゲートに印加して、それらのゲート誘電体層を放電させることができる。

10

#### 【 0 0 8 4 】

図 22 a を再度参照して、各 B L T は、ビット線 ( B L ) に接続されていてよい。一例では、B L は、S T I のピッチと同じか又はほぼ同じピッチを有する金属線であってよい。又、各 S L T は、ソース線 ( S L ) に接続される。ソース線は、W L に平行であり、又読み出し検知のためのセンスアンプに接続される。ソース線は、タンクステンなどの金属、又はポリシリコン線、又は拡散 N<sup>+</sup> ドープ線であってよい。

#### 【 0 0 8 5 】

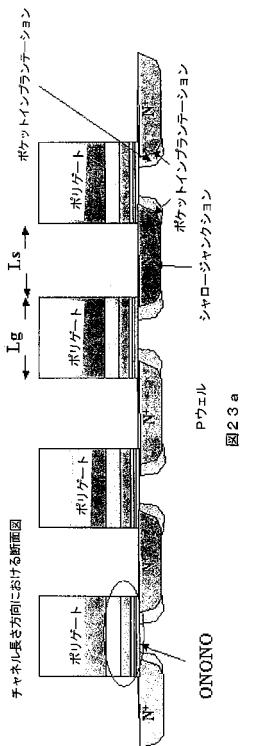

図 23 a は、S O N O N O S - N A N D メモリアレイなどの典型的なメモリアレイの、チャネル長方向に沿った断面図を示す。典型的には、L<sub>g</sub> 及び L<sub>s</sub> は、デバイス（又はノード）の限界寸法を一般的に表す F にほぼ等しい。限界寸法は、製造のために用いられる技術によって変わり得る。例えば、F = 50 nm は、50 nm のノードを使用することを意味する。図 23 b は、S O N O N O S - N A N D メモリアレイなどの典型的なメモリアレイの、チャネル幅方向に沿った断面図を示す。図 23 b を参照して、チャネル幅方向におけるピッチは、チャネル長方向におけるピッチにほぼ等しいか又はそれより少し大きい。従って、メモリセルのサイズは、ほぼ 1 セル当たり 4 F<sup>2</sup>（即ち、4 F<sup>2</sup> / c e l l ）である。

20

#### 【 0 0 8 6 】

上述のアレイなどのメモリアレイの製造についてのいくつかの例においては、製造工程は、2つだけの主要マスク（プライマリーマスク）又はリソグラフィー処理を使用することを含んでいてよく、例えば、1つはポリシリコン（ワード線）のためで、もう1つは S T I （ビット線）のためである。これに対して、N A N D 型フローティングゲートデバイスの製造は、少なくとも2つのポリ（poly）処理と、もう1つのインターポリ（inter-poly）ONO 処理とを必要とするだろう。従って、提示したデバイスの構造及び製造工程は、N A N D 型フローティングゲートメモリのそれよりも簡単であると考えられる。

30

#### 【 0 0 8 7 】

図 23 a を参照して、一例では、ワード線 ( W L ) 間の間隔 ( L<sub>s</sub> ) は、N<sup>+</sup> ドープ領域のシャロージャンクションなどのシャロージャンクションで形成することができ、これはメモリデバイスのソース又はドレイン領域として働くことができる。図 23 a に示されるように、傾斜ポケットインプランテーション（t i l t - a n g l e p o c k e t i m p l a n t a t i o n ）などの追加のインプランテーション及び / 又は拡散処理を実施することができ、これにより 1 つ以上のシャロージャンクション領域に隣接する、1 つ以上の「ポケット」領域、即ち、ジャンクションのポケット拡張部分を提供することができる。いくつかの例においては、このような構造は、より良好なデバイス特性を提供することができる。

40

#### 【 0 0 8 8 】

個々のメモリデバイスを分離するのに S T I が用いられるいくつかの例において、特に、用いられるジャンクションバイアスがより高く上げられる場合には、S T I 領域のトレチ（溝）深さは、P ウェル内の空乏幅より大きくすることができる。例えば、プログラム禁止（阻止）ビット線（群）（プログラミング中に非選択のビット線（群））について

50

は、ジャンクションバイアスは約 7 V 程度まで高くすることができる。一例では、S T I 領域の深さは、約 200 nm から 400 nm の範囲内にすることができる。

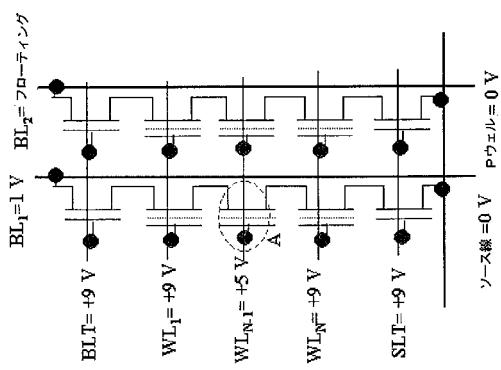

#### 【0089】

メモリアレイが製造された後に、V<sub>t</sub> 分布をタイト化する (V<sub>t</sub> のばらつきを抑える) ために、メモリアレイの他の動作の前に、先ず、リセット動作を実行することができる。図 24 a は、このような動作の一例を示す。一例では、他のオペレーションが開始する前に、先ず、V<sub>G</sub> = 約 -7 V 及び V<sub>P</sub> ウェル (V<sub>P</sub> - w e l l ) = +8 V を印加して、アレイをリセットすることができる (V<sub>G</sub> 及び V<sub>P</sub> - w e l l の電圧降下は、各 W L 及び P ウェル内のゲート電圧内に分配することができる。)。リセット中に、B L (群) は、フローティングにするか、又は P ウェルと同電圧に上げることができる。図 24 b に示されるように、リセット動作は、優れた自己収束特性を提供することができる。一例では、SONONOS デバイス群が当初多様な V<sub>t</sub> に帯電されていても、リセット動作は、それらをリセット / 消去状態へと「タイト化」することができる。一例では、リセット時間は約 100 msec である。この例において、メモリアレイは、L<sub>g</sub> / W = 0.22 / 0.16 μm の N<sup>+</sup> ポリシリコンゲートを有する、ONONO = 15 / 20 / 18 / 70 / 90 オンゲストロームの n チャネル SONONOS デバイスを使用することができる。

#### 【0090】

一般に、従来のフローティングゲートデバイスは、自己収束消去を提供することができない。これに対して、SONONOS デバイスは、収束性のリセット / 消去方法で動作させることができる。いくつかの例においては、この動作は不可欠なものとなり得る。なぜなら、処理の不均一性又はプラズマ帯電効果などのある種の処理上の問題によって、初期 V<sub>t</sub> の分布はしばしば広範囲に渡るからである。典型的な自己収束「リセット」は、メモリデバイス群の初期 V<sub>t</sub> の分布のタイト化、即ち、初期 V<sub>t</sub> の分布の範囲を狭めるのを助けることができる。

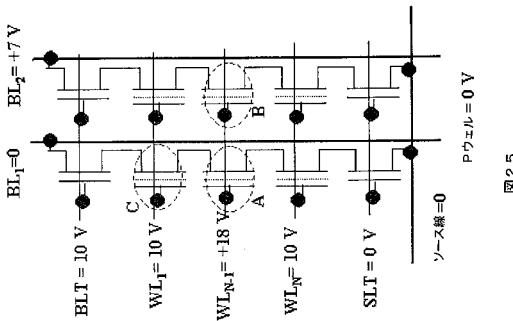

#### 【0091】

プログラミング動作の一例においては、選択された W L には、チャネル + F N 注入を生じさせるように、約 +16 V から +20 V の電圧などの高い電圧を印加することができる。他のパスゲート (P A S S g a t e) (他の非選択 W L (群)) は、N A N D 列における反転層を生じさせるように、オンとすることができます。いくつかの例においては、+ F N プログラミングは、低電力方法であってよい。一例では、並列の 4 K バイトのセルのページプログラミングなどの並列プログラミング方法は、プログラミングスループットを 10 MB / sec 以上に増大させることができるが、その場合でも全電流消費を 1 mA 以内に制御することができる。いくつかの例においては、他の B L におけるプログラムディスターブを防止するために、約 7 V の電圧などの高い電圧を、他の B L に印加することができる。これにより、反転層の電位がより高く上げられて、非選択 B L (図 25 中のセル B など) における電圧降下を抑制することができる。

#### 【0092】

読み出し動作のいくつかの例においては、選択された W L は、消去された状態のレベル (E V) とプログラムされた状態のレベル (P V) との間の電圧へ上げることができます。他の W L は、「パスゲート」として働くことができ、それによりそれらのゲート電圧は、P V よりも高い電圧に上げることができます。いくつかの例においては、消去動作は、上述のリセット動作と同様であってよく、これは同じか又は類似のリセット V<sub>t</sub> への自己収束を可能とすることができます。

#### 【0093】

図 25 は、メモリアレイの操作の一例を示す。プログラミングは、SONONOS 塗化物捕捉層内への電子のチャネル + F N 注入を含んでいてよい。いくつかの例は、V<sub>g</sub> = 約 +18 V を選択された W L N - 1 へ印加すること、及び V<sub>G</sub> = 約 +10 V を B L T 並びに他の W L へ印加することを含んでいてよい。セル B におけるチャネルホットエレクトロン注入を防止するために、S L T はオフとすることができます。この例では、N A N D 列内の全てのトランジスタがオンとされるため、反転層は列を通過する。更に、B L 1 が接地さ

れるため、B L 1 内の反転層はゼロ電位を有する。一方、他のB L は、約 + 7 V の電圧などの高い電位に上げられ、これにより他のB L の反転層の電位はより高くなる。

#### 【 0 0 9 4 】

特に、プログラミングのために選択されたセルであるセルAに関しては、電圧降下は約 + 18 V であり、これは + FN 注入を引き起こす。又、V t は、PVへと上げることができる。セルBに関しては、電圧降下は + 11 V であり、FN 注入は V g に対して敏感であるため、これはかなり少ない + FN 注入しか引き起こさない。セルCに関しては、+ 10 V しか印加されないので、+ FN 注入を引き起こさないか又は無視できるほど少ない + FN 注入しか引き起こさない。いくつかの例においては、プログラミング動作は、例示した技術に限定されるものではない。言い換えれば、他の適切なプログラム禁止技術を適用することもできる。10

#### 【 0 0 9 5 】

図24a、図26、及び図27は更に、アレイ動作のいくつかの例を示しており、又いくつかの例における耐久特性及び保持特性を示している。図示されているように、多数の動作サイクルの後のデバイスの劣化は、非常に小さいままであり得る。図24aは、典型的な消去動作を示しており、これはリセット動作と同様であってよい。一例では、消去は、セクタ単位又はブロック単位で行われる。前述したように、このメモリデバイスは、良好な自己収束消去特性を有し得る。いくつかの例においては、消去飽和 V t は、V g に依存し得る。例えば、より高い V g は、より高い飽和 V t を生じさせることができる。図26Bに示されるように、収束時間は、約 10 ~ 100 msec とすることができます。20

#### 【 0 0 9 6 】

図27は、典型的な読み出し動作を示す。一例では、読み出しは、消去された状態の V t (EV) とプログラムされた状態の V t (PV) との間のゲート電圧を印加することによって行うことができる。例えば、ゲート電圧は約 5 V であってよい。一方、他のWL と BL T 及び SL T には、約 + 9 V の電圧などのより高いゲート電圧が印加され、他のメモリセルの全てをオンとする。一例では、セルAの V t が 5 V より高い場合には、読み出し電流は非常に小さくてよい (< 0.1 μA)。セルAの V t が 5 V より低い場合には、読み出し電流はより高くてよい (> 0.1 μA)。その結果、メモリの状態、即ち、格納された情報を識別(決定)することができる。30

#### 【 0 0 9 7 】

いくつかの例においては、他のWL のためのバスゲート電圧は、高 V t 状態、即ち、プログラムされた状態の V t よりも高くすべきであるが、しかしゲートディスターブを引き起こすほど高くし過ぎるべきではない。一例では、バスゲート電圧は、約 7 ~ 10 V の範囲内にある。BL に印加される電圧は、約 1 V であってよい。より大きな読み出し電圧は、より大きな電流を生じさせることができるが、いくつかの例においては、リードディスターブ(読み出し阻害)がより顕著になることがある。いくつかの例においては、センシングアンプを、ソース線上(ソースセンシング)又はビット線上(ドレインセンシング)に配置することができる。30

#### 【 0 0 9 8 】

NAND列のいくつかの例は、1列当たり 8、16 又は 32 個のメモリデバイスを有し得る。より大きなNAND列は、オーバヘッドを低減する(より多く省く)ことができ、又アレイ効率を増大することができる。しかし、いくつかの例においては、読み出し電流がより小さくなることがあり、又ディスターブがより顕著になることがある。従って、適切なNAND列の数を、種々の設計、製造及び動作上のファクタに基づいて選択すべきである。40

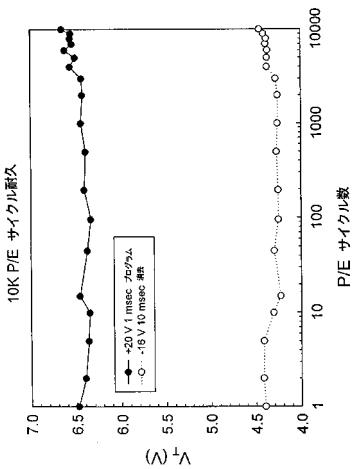

#### 【 0 0 9 9 】

図28は、特定の典型的なデバイスのサイクル耐久特性を示す。図28を参照すると、+ FN プログラム及び - FN 消去を用いた P / E サイクルを実行することができ、その結果は良好な耐久特性を示唆している。この例では、消去条件は、10 msec 間の V g = 約 - 16 V である。いくつかの例においては、单ショットのみの消去が必要とされ、又50

状態の確認は不要である。メモリのVtウインドウは、劣化がなく良好である。

#### 【0100】

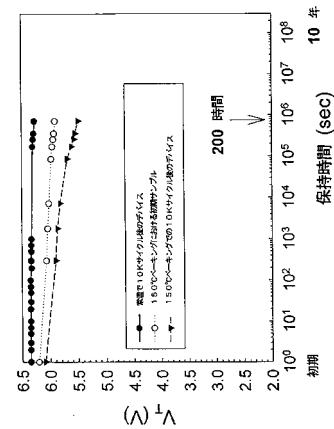

図29a及び図29bは、典型的なメモリデバイスのIV特性を、異なる目盛を使用して示している。特に、図29aはデバイスの少ないスイング劣化を示しており、又図29bはデバイスの少ないgm劣化を示している。図30は、典型的なSONONOSデバイスの保持特性を示す。図30を参照すると、良好な保持能力が得られており、10Kサイクル後に、室温（常温）で200時間放置した後に動作されたデバイスに関して、電荷損失は100mV未満である。図30はまた、高温における許容し得る電荷損失を示している。

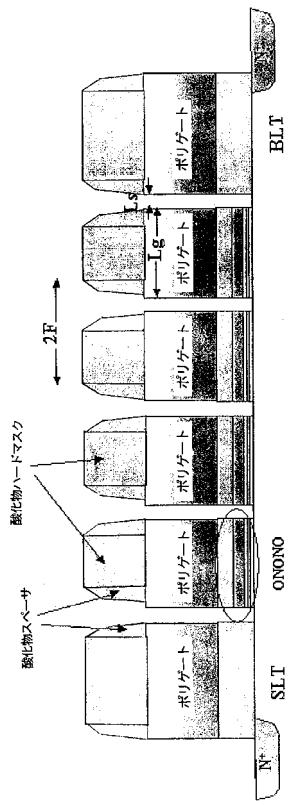

#### 【0101】

いくつかの例においては、スプリットゲートSONONOS-NAND設計などのスプリットゲート設計を、メモリアレイの更に積極的な縮小化を達成するために用いることができる。図31は、このような設計を用いる一例を示す。図31を参照して、各ワード線間、即ち、同じビット線を共用する2つの隣接するメモリデバイス間の間隔(Ls)は、低減することができる。一例では、Lsは、約30nm又は30nm未満に縮めることができる。図示されるように、同じビット線に沿った、スプリットゲート設計を用いたメモリデバイス群は、1つのソース領域及び1つのドレイン領域だけを共有する。言い換えると、スプリットゲートSONONOS-NANDアレイは、メモリデバイスのいくつかのために、拡散領域、即ち、N<sup>+</sup>ドープ領域などのジャンクションを使用しないことが可能である。一例では、この設計は、いくつかの例においてはより複雑な製造工程を含むことがあるシャロージャンクション及び隣接「ポケット」の必要性を、低減又は除去することができる。更に、いくつかの例においては、この設計は、短チャネル効果により受ける影響がより少ない。これは、一例では、チャネル長が、例えばLg = 2F - Lsへと増大されるなど、増大されたことによる。

10

20

30

#### 【0102】

図32は、スプリットゲート設計を用いたメモリアレイの典型的な製造工程を示す。この模式図は、単に説明のための一例であり、メモリアレイは種々の異なる方法において設計及び製造することができる。図32を参照して、メモリデバイスを提供するための材料による複数の層が形成された後、それらの層の上に形成されたハードマスクとしての酸化ケイ素構造を使用して、それらの層のパターニングを行うことができる。例えば、酸化ケイ素領域は、リソグラフィー及びエッチング処理によって画成することができる。一例では、最初の酸化ケイ素領域を画成するために用いられるパターンは、約Fの幅、及び約Fの酸化ケイ素領域間の間隔を有していてよく、結果として約2Fのピッチをもたらす。最初の酸化ケイ素領域がパターニングされた後に、次いで、各酸化ケイ素領域を拡大し又それらの間隔を狭めるために、上記パターニングされた領域の周囲に酸化ケイ素スペーサを形成することができる。

30

#### 【0103】

図32を再度参照して、酸化ケイ素領域が形成された後、それをハードマスクとして利用してその下にある層の画成、即ち、パターニングを行い、1つ以上のメモリデバイス、例えば多数のNAND列を提供することができる。更に、隣接するメモリデバイス間の、例えば図32に示されるLs間隔などの空間を満たすために、酸化ケイ素などの絶縁材料を使用することができる。

40

#### 【0104】

一例では、同一ビット線に沿った隣接するメモリデバイス間の間隔Lsは、約15nmから約30nmの範囲内とすることができます。前述したように、この例では、実効チャネル長は、2F - Lsに拡大することができる。一例では、Fが約30nmであり、又Lsが約15nmであれば、Leffは約45nmである。これらの典型的なメモリデバイスの操作に関しては、ゲート電圧は15V以下に低減することができる。更に、Ls間隔におけるスペーサのブレークダウンを避けるために、ワード線間におけるポリシリコン間電圧降下が7Vを越えないように設計することができる。一例では、これは、隣接するワード

50

ド線間の電界を  $5 \text{ MV} / \text{cm}$  未満とすることによって達成することができる。

#### 【0105】

従来の N A N D フローティングゲートデバイスにおける拡散ジャンクションを伴う L e f f は、そのゲート長の約半分である。これに対して、一例では、提示した設計（スプリットゲート N A N D）の場合、F が約  $50 \text{ nm}$  であり、又 L e f f が約  $30 \text{ nm}$  であれば、L e f f は約  $80 \text{ nm}$  である。より長い L e f f は、短チャネル効果の影響を低減又は除去することによって、より良好なデバイス特性を提供することができる。

#### 【0106】

前述したように、スプリットゲート N A N D 設計は、同一ビット線における隣接するメモリセル間の間隔 (L s) を更に縮小することができる。これに対して、従来の N A N D 型フローティングゲートデバイスは、フローティングゲート間の結合効果によってメモリウインドウが失われる（狭くなる）ことがあるため、小さい間隔を提供することができない。フローティングゲート間の結合は、隣接するフローティングゲート間の結合容量が大きいときの（隣接するフローティングゲート間の結合容量が非常に大きくなりリードディステーブルが起きるほど、フローティングゲート間の間隔が小さいときの）隣接するメモリセル間の干渉である。前述したように、この設計は、いくつかの拡散ジャンクションの作製を不要にでき、又全てのワード線がオンにされれば、反転層は直接連結することが可能である。従って、この設計は、メモリデバイスの製造工程を簡略化することができる。

#### 【0107】

以上説明したように、メモリデバイスの構造設計、アレイ設計及び動作を含む上述のいくつかの例は、望ましいアレイ寸法、良好な信頼性、良好な性能、又はこれらのうちいずれかの組み合わせを提供することができる。上述のいくつかの実施形態は、N A N D フラッシュメモリ及びデータアプリケーション用のフラッシュメモリなどの不揮発フラッシュメモリの寸法の縮小のために適用することができる。いくつかの実施形態は、一様で自己収束性のチャネルホットトンネリング消去が可能な S O N O N O S デバイスを提供することができる。又、いくつかの実施形態は、メモリデバイスの良好な耐久性を提供することができ、又、いくらかの消去不足又は過剰消去の問題を低減することができる。又、P / E サイクル後の劣化が小さく電荷保持能力が良好であるなどの、良好なデバイス特性を提供することができる。メモリアレイ内のデバイスの一様性は、異常ビット又はセルを生じることなく提供することができる。更に、いくつかの実施形態は、スプリットゲート N A N D 設計により、良好な短チャネルデバイス特性を提供することができ、これによりメモリデバイスの動作中に良好なセンスマージンを提供することができる。

#### 【0108】

本発明の好適な実施形態の上記開示は、例示と説明のためになされたものである。これは、包括的なものではなく、本発明を開示された通りの形式に限定するものではない。本発明の広範な発明概念を逸脱することなく上記の実施形態に変更を行え得ることは当業者には理解されよう。従って、当然のことながら、本発明は開示された特定の実施形態に限定されず、添付した請求の範囲で限定される本発明の精神と範囲内でなされる変更も包含する。

#### 【図面の簡単な説明】

#### 【0109】

【図1】図1a 及び図1b はそれぞれ、本発明の一実施形態に従う N チャネル (N型) メモリセルの概略断面図及び本発明の一実施形態に従う P チャネル (P型) メモリセルの概略断面図である。

【図2】図2は、各種のプログラミング方法の下での、本発明の一実施形態に従うトンネル誘電体構造の閾電圧（電荷捕捉能力）を示すグラフである。

【図3】図3は、消去期間における時間経過に対する、本発明の一実施形態に従う S O N O N O S メモリセルの閾電圧を示すグラフである。

【図4】図4は、保持期間における時間経過に対する、本発明の一実施形態に従う S O N

10

20

30

40

50

ONOSメモリセルの閾電圧を示すグラフである。

【図5-1】図5a及び5bは、本発明の各種の実施形態に従うONOトンネル誘電体構造のバンドエネルギー図である。

【図5-2】図5c及び5dは、本発明の各種の実施形態に従うONOトンネル誘電体構造のバンドエネルギー図である。

【図5-3】図5eは、本発明の各種の実施形態に従うONOトンネル誘電体構造のバンドエネルギー図である。

【図6】図6は、3つの異なるトンネル誘電体構造についてのホールトンネリング電流と電界強度との関係を示すグラフである。

【図7a】図7aは、各種のプログラミング後の消去期間における時間経過に対する本発明の一実施形態に従うメモリセルの閾電圧を示すグラフである。 10

【図7b】図7bは、消去期間における時間経過に対する本発明の一実施形態に従う白金ゲートを有するメモリセルの閾電圧を示すグラフである。

【図7c】図7cは、図7bで言及したメモリセルのキャパシタンスと電圧との関係を示すグラフである。

【図7d】図7dは、図7bで言及したメモリセルのキャパシタンスと電圧との関係を示すグラフである。

【図8】図8は、各種動作条件の下で多数のプログラム／消去サイクルを実行した場合の本発明の一実施形態に従うメモリセルの閾電圧を示すグラフである。

【図9】図9は、本発明の一実施形態に従うメモリセルについて、1サイクル後及び10<sup>3</sup>サイクル後の電流-電圧(I-V)関係を示すグラフである。 20

【図10】図10は、一組のプログラミング及び消去条件の下で多数のプログラム／消去サイクルを実行した場合の本発明の一実施形態に従うメモリセルの閾電圧を示すグラフである。

【図11】図11は、本発明の一実施形態に従うメモリセルについて、VG加速保持試験における閾電圧の経時変化を示すグラフである。

【図12】図12a及び図12bはそれぞれ、本発明の一実施形態に従うメモリセルによるバーチャルグランドアレイの等価回路図及びレイアウト図である。

【図13】図13は、図12bの線12B-12Bに沿った、本発明の一実施形態に従うメモリセルによるバーチャルグランドアレイの模式断面図である。 30

【図14】図14a及び図14bは、本発明の一実施形態に従うメモリセルを有するメモリアレイの等価回路図であり、本発明に従う動作の2つの実施形態に従った適当なリセット／消去電圧を示す図である。

【図15】図15a及び図15bは、本発明の一実施形態に従うメモリセルを有するメモリアレイの等価回路図であり、本発明に従う一つのプログラミング方法を示す図である。

【図16】図16a及び図16bは、本発明の一実施形態に従うメモリセルを有するメモリアレイの等価回路図であり、本発明に従う一つのビット読み出し方法を示す図である。

【図17】図17は、各種の消去条件の下での時間経過に対する本発明の一実施形態に従うメモリセルの閾電圧を示すグラフである。

【図18】図18は、多数のプログラム／消去サイクルを実行した場合の本発明の一実施形態に従うメモリセルの閾電圧を示すグラフである。 40

【図19】図19a及び図19bはそれぞれ、種々のゲート電圧の下での一実施形態に従うメモリセルのドレインにおける電流を、対数目盛り及び線形目盛りで表したグラフである。

【図20】図20は、本発明の一実施形態に従うメモリセルを有するアレイの等価回路図であり、本発明に従う一つのビットプログラミング方法を示す図である。

【図21】図21a及び図21bは、本発明の一実施形態に従うバーチャルグランドアレイのレイアウト図及び等価回路図である。

【図22】図22a及び図22bはそれぞれ、本発明の一実施形態に従うメモリセルによるNANDアレイの等価回路図及びレイアウト図である。 50

【図23】図23a及び図23bはそれぞれ、図22bの線22A-22A及び22B-22Bに沿った、本発明の一実施形態に従うメモリセルによるNANDアレイの模式断面図である。

【図24】図24aは、本発明の一実施形態に従うNANDの等価回路図であり、本発明に従う一つの動作方法を示す図である。図24bは、異なる初期閾電圧を有する2つのメモリセルについて、本発明の一実施形態に従うリセット動作中の時間経過に対する閾電圧示す図である。

【図25】図25は、本発明の一実施形態に従う一つの動作方法を示す等価回路図である。

【図26】図26は、各種の消去条件の下での時間経過に対する本発明の一実施形態に従うメモリセルの閾電圧を示すグラフである。 10

【図27】図27は、本発明の一実施形態に従う一つの動作方法を示す等価回路図である。

【図28】図28は、一組のプログラミング及び消去条件の下で多数のプログラム／消去サイクルを実行した場合の本発明の一実施形態に従うメモリセルの閾電圧を示すグラフである。

【図29】図29a及び図29bはそれぞれ、3つの異なるサイクル数での種々のゲート電圧の下での一実施形態に従うメモリセルのドレインにおける電流を、対数目盛り及び線形目盛りで表したグラフである。

【図30】図30は、3つの異なる温度及びサイクル条件での保持期間における時間経過に対する本発明の一実施形態に従うメモリセルの閾電圧を示すグラフである。 20

【図31】図31は、本発明の一実施形態に従うNANDアレイのワード線の模式断面図である。

【図32】図32は、本発明の一実施形態に従うNANDアレイのワード線形成技術を示す模式断面図である。

【図1】

【図2】

【図3】

【図4】

図3

図4

【図5-1】

図5 b

【図5-2】

図5 d

図5 a

図5 c

【図 5 - 3】

図 5 e

【図 6】

図 6

【図 7 a】

図 7 a

【図 7 b】

図 7 b

【図 7 c】

【図 7 d】

図 7 d

【図 8】

【図 9】

図 9

【図10】

図10

【 図 1 1 】

11

【図12】

図12b SONOS デバイス

モード SONOS デバイス

モード SONOS デバイス

図12-a バーチャルグランダレイの等価回路

【図13】

3

1

【図 1 4】

図 1 4 a

図 1 4 b

【図 1 5】

図 1 5 a

図 1 5 b

【図 1 6】

図 1 6 a

図 1 6 b

【図 1 7】

図 1 7

【図18】

88

【 図 1 9 】

196

【 図 2 0 】

82

【 図 2 2 】

四二

22 b

【図23】

【 図 25 】

【図24】

246

图 24 a

【図26】

26

【図 27】

【図 28】

図 28

【図 29】

図 29 b

【図 30】

図 30

【図31】

図31

【図32】

図32

【図21】

図21 b

図21 a

---

フロントページの続き

(51)Int.Cl. F I

H01L 29/788 (2006.01)

H01L 29/792 (2006.01)

(56)参考文献 特開平6 - 291332 (JP, A)

特開2004 - 363329 (JP, A)

特開平5 - 36991 (JP, A)

特開平9 - 92738 (JP, A)

特開昭64 - 55868 (JP, A)

特開平11 - 345496 (JP, A)

米国特許第6026026 (US, A)

(58)調査した分野(Int.Cl., DB名)

G11C16/00-16/34

H01L21/8247

H01L27/115

H01L29/788

H01L29/792