#### US00RE38049E

# (19) United States

## (12) Reissued Patent

Dennison et al.

### (10) Patent Number: US RE38,049 E

(45) Date of Reissued Patent: Mar. 25, 2003

#### (54) OPTIMIZED CONTAINER STACKED CAPACITOR DRAM CELL UTILIZING SACRIFICIAL OXIDE DEPOSITION AND CHEMICAL MECHANICAL POLISHING

(75) Inventors: Charles H. Dennison, Meridian, ID

(US); Michael A. Walker, Boise, ID

(US)

(73) Assignee: Micron Technology, Inc., Boise, ID

(US)

(21) Appl. No.: 08/759,058

(22) Filed: Oct. 7, 1996

#### Related U.S. Patent Documents

#### Reissue of:

(64) Patent No.: 5,270,241

Issued: Dec. 14, 1993

Appl. No.: 07/973,092

Filed: Nov. 6, 1992

#### U.S. Applications:

(63) Continuation of application No. 07/850,746, filed on Mar. 13, 1992, now Pat. No. 5,162,248.

| (51) | Int. Cl. <sup>7</sup> | ·          | H01L 21/20    |

|------|-----------------------|------------|---------------|

| (50) | TIO OI                | 120/207 12 | 0.050 400.000 |

(52) **U.S. Cl.** ...... **438/396**; 438/253; 438/238; 438/692; 438/633; 216/6

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 4,432,799 A | 2/1984    | Salazar                |

|-------------|-----------|------------------------|

| 4,671,851 A | * 6/1987  | Beyer et al 156/648    |

| 4,785,337 A | * 11/1988 | Kenney 365/149         |

| 4,877,750 A | * 10/1989 | Okumura 437/203        |

| 4,944,836 A | * 7/1990  | Beyer et al 156/656    |

| 5,045,899 A | * 9/1991  | Arimoto et al 357/23.6 |

| 5,150,276 A | * 9/1992  | Gonzalez et al 361/313 |

| 5,162,248 A | * 10/1992 | Dennison et al 437/919 |

| 5,185,282 A | * | 2/1993  | Lee et al  | 437/47    |

|-------------|---|---------|------------|-----------|

| 5,313,089 A | * | 5/1994  | Jones, Jr  | . 257/310 |

| 5.364.809 A | * | 11/1994 | Kwon et al | 438/396   |

#### FOREIGN PATENT DOCUMENTS

| JP | 0286270 | * | 12/1987 |

|----|---------|---|---------|

| JP | 0094554 | * | 4/1990  |

| JP | 0074752 | * | 7/1990  |

#### OTHER PUBLICATIONS

"Stacked Capacitor DRAM Cell with Vertical Fins", IBM TDB, Jul. 1990, pp. 245–247.\*

"Crown–Shaped Stacked–Capacitor Cell for 1.5–V Operation 64–Mb Dram's" by T. Kaga et al., IEEE Transactions on Electron Devices, vol. 38, No. 2, Feb. 1991, pp. 255–261.\*

"A Stacked Capacitor Cell with Ring Structure" by N. Shinmura et al., pp. 833–836. (Extended abstacts of the 22nd International Conference on Solid State Devices 1990).\*

\* cited by examiner

Primary Examiner—Tuan H. Nguyen (74) Attorney, Agent, or Firm—Traskbritt

#### (57) ABSTRACT

An existing stacked capacitor fabrication process is modified to construct a three-dimensional stacked container capacitor. The present invention develops the container capacitor by etching an opening (or contact opening) into a low etch rate oxide. The contact opening is used as a form for deposited polysilicon that conforms to the sides of the opening walls. Within the thin poly lining of the oxide container a high etch-rate oxide, such as ozone TEOS, is deposited over the entire structure thereby bridging across the top of the oxide container. The high etch-rate oxide is planarized back to the thin poly and the resulting exposed poly is then removed to separate neighboring containers. The two oxides, having different etch rates, are then etched thereby leaving a freestanding poly container cell with 100% (or all) of the higher etch rate oxide removed and a pre-determined oxide surrounding the container still intact.

#### 66 Claims, 4 Drawing Sheets

FIG. 1

FIG. 2

FIG. 3

FIG. 4

FIG. 7

#### OPTIMIZED CONTAINER STACKED CAPACITOR DRAM CELL UTILIZING SACRIFICIAL OXIDE DEPOSITION AND CHEMICAL MECHANICAL POLISHING

Matter enclosed in heavy brackets [ ] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue.

## CROSS-REFERENCE TO RELATED APPLICATION

This is a continuation to U.S. patent application Ser. No. 07/850,746, filed Mar. 13, 1992, now U.S. Pat. No. 5,162, 248.

#### FIELD OF THE INVENTION

This invention relates to semiconductor circuit memory storage devices and more particularly to a process for 20 fabricating three-dimensional stacked capacitor structures that may be used in such storage devices as high-density dynamic random access memories (DRAMs).

#### BACKGROUND OF THE INVENTION

In dynamic semiconductor memory storage devices it is essential that storage node capacitor cell plates be large enough to retain an adequate charge or capacitance in spite of parasitic capacitances and noise that may be present during circuit operation. As is the case for most semiconductor integrated circuitry, circuit density is continuing to increase at a fairly constant rate. The issue of maintaining storage node capacitance is particularly important as the density of DRAM arrays continues to increase for future generations of memory devices.

The ability to densely pack storage cells while maintaining required capacitance levels is a crucial requirement of semiconductor manufacturing technologies if future generations of expanded memory array devices are to be successfully manufactured.

One method of maintaining, as well as increasing, storage node size in densely packed memory devices is through the use of "stacked storage cell" design. With this technology, two or more layers of a conductive material such as polycrystalline silicon (polysilicon or poly) are deposited over an access device on a silicon wafer, with dielectric layers sandwiched between each poly layer. A cell constructed in this manner is known as a stacked capacitor cell (STC). Such a cell utilizes the space over the access device for capacitor plates, has a low soft error rate (SER) and may be used in conjunction with inter-plate insulative layers having a high dielectric constant.

However, it is difficult to obtain sufficient storage capacitance with a conventional STC capacitor as the storage 55 electrode area is confined within the limits of its own cell area. Also, maintaining good dielectric breakdown characteristics between poly layers in the STC capacitor becomes a major concern once insulator thickness is appropriately scaled.

A paper submitted by N. Shinmura, et al., entitled "A Stacked Capacitor Cell with Ring Structure," Extended Abstracts of the 22nd International Conference on Solid State Devices and Materials, 1990, pp. 833–836, discusses a 3-dimensional stacked capacitor incorporating a ring structure around the main electrode to effectively double the capacitance of a conventional stacked capacitor.

2

The ring structure and its development is shown in FIGS. 1(c) through 1(g), pp. 834 of the article mentioned above. FIG. 1(a), on the same page shows a bird's eye-view of storage electrodes. The storage node is formed by two polysilicon layers that form a core electrode encircled by a ring structure. Capacitor dielectric film surrounds the whole surface of the storage node electrode and then is covered with a third polysilicon layer to form the top capacitor electrode and completes the storage cell. This design can be fabricated using current methods and increases storage capacitance by as much as 200%.

Also, [in] a paper submitted by T. Kaga, et al., entitled "Crown-Shaped Stacked-Capacitor Cell for 1.5-V Operation 64-Mb DRAM's," IEEE Transactions on Electron Devices. VOL. 38, NO. 2, February 1991, pp. 255–261, discusses a self-aligned stacked-capacitor cell for 64-Mb DRAM's, called a CROWN cell. The CROWN cell and its development are shown in FIGS. 7(d) through 7(f), pp. 258 of this article. The crown shaped storage electrode is formed over word and bit lines and separated by [a] an oxide/nitride insulating layer with the top insulating layer being removed to form the crown shape. Capacitor dielectric film surrounds the whole surface of the storage node electrode and the top capacitor electrode is formed to complete the storage cell.

The present invention develops an existing stacked capacitor fabrication process to construct and optimize a three-dimensional container stacked capacitor cell. The capacitor's bottom plate (or storage node plate) is centered over a buried contact (or node contact) connected to an access transistor's diffusion area. The method presented herein provides fabrication uniformity and repeatability of the three-dimensional container cell.

#### SUMMARY OF THE INVENTION

The invention is directed to maximizing storage cell surface area in a high density/high volume DRAM (dynamic random access memory) fabrication process. An existing capacitor fabrication process is modified to construct a three-dimensional stacked container capacitor. The capacitor design of the present invention defines a stacked capacitor storage cell that is used in a DRAM process, however it will be evident to one skilled in the art to incorporate these steps into other processes requiring volatile memory cells, such as VRAMs or the like.

After a silicon wafer is prepared using conventional process steps, the present invention develops the container capacitor by etching a contact opening into a low etch rate oxide. The contact opening is used as a form for deposited polysilicon that conforms to the sides of the opening walls. Within the thin poly lining of the oxide container a high etch-rate oxide, such as ozone TEOS, is deposited over the entire structure thereby bridging across the top of the oxide container. The high etch-rate oxide is planarized back to the thin poly by using Chemical Mechanical Polishing (CMP). This CMP step is selective such that oxide is removed with sufficient overetch and stops on the thin poly. The resulting exposed poly is then removed to separate neighboring containers either through an isotropic wet poly etch or an additional CMP with the chemical aspect modified to now etch and selectively remove the poly and not the oxide. The two oxides, having different etch rates, are then etched by a single wet dilute BOE etch step, thereby leaving a freestanding poly container cell, with all the inside (high etch rate) oxide removed, that is equal in height to the depth of the original contact opening. In addition, a pre-determined amount of low etch rate oxide is removed, thereby leaving

oxide surrounding the [J]container, poly for both structural support and process integration for further processing which requires oxide to be left above the word lines.

The present invention uses a higher etch-rate oxide inside the container to block the container poly etch. This high etch 5 rate oxide is completely removed during oxide etch back. This protects the container during processing without adding photoresist and introducing extra processing steps or unwarranted contaminants. A standard CMP oxide etch is utilized that allows fabrication uniformity and repeatability across 10 the wafer which cannot be achieved by resist filled container processes.

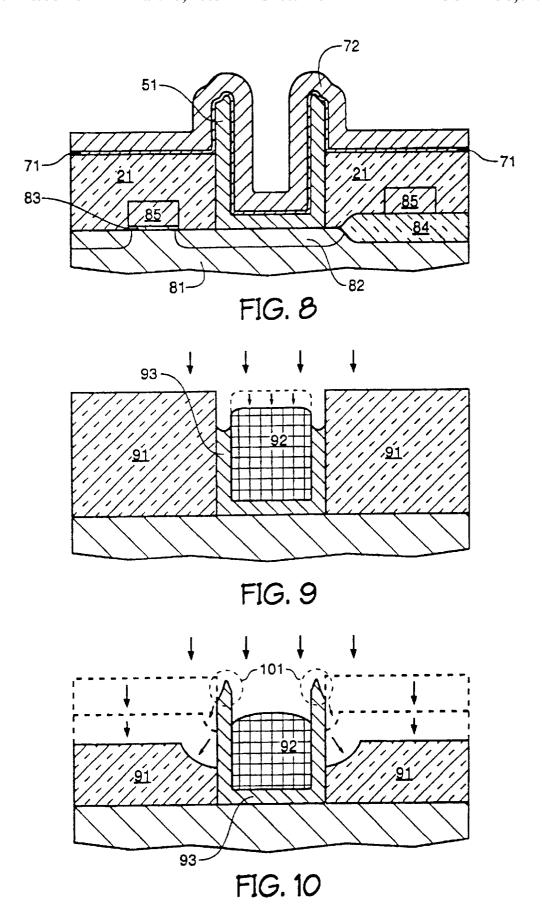

Another advantage of filling the container with high etch rate oxide is that the poly can be etched with a low cost, timed wet poly etch, while partially filled containers (as seen in FIG. 9), due to inherent recession of resist 92 height (to allow for sufficient process margin), will not allow a wet poly etch without loss in cell height 93, loss in uniformity and repeatability across the wafer's surface. Because this invention can be etched isotropically at poly etch, it avoids the recessing (overetch of the storage poly container 93 in FIG. 9) and splintering effects caused by a dry etch poly process.

As seen in FIG. 10, splintering effects 101 of storage node poly 93 result from a dry anisotropic etch (due to non-uniform etching of polycrystalline silicon 93) because the plasma etch reacts faster along heavily doped grain boundaries. Splinters 101 later tend to 'break off' in subsequent processing leading to contamination particulates. The trenching of the poly leads to the side-walls of the poly container to be exposed, thus making it impossible to wet etch the oxide around the cell without translating the trenched poly horizontal portion of the etch into surrounding oxide 91 thereby leaving a ring of thin oxide around [he] the container cell.

The present invention also protects the vertical sidewall of the oxide form by covering it with poly, thereby making a horizontal wet oxide etch back possible. In addition, all films which see etch processing, CMP or otherwise, are subsequently removed thereby acting as sacrificial films such that particles created during the CMP etch do not contaminate the inside of the poly containers.

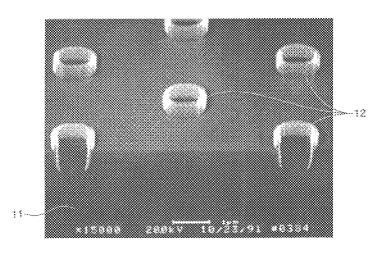

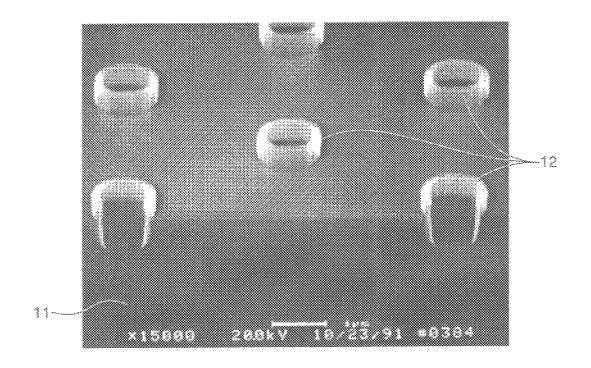

FIG. 1 shows a gray scale reproduction of a SEM photograph of an array of poly containers 12 which demonstrates the uniformity and repeatability of poly containers 12 across substrate 11 that results from utilizing the process steps of the present invention discussed hereinafter.

#### BRIEF DESCRIPTION OF THE DRAWINGS

- FIG. 1 is a gray-scale reproduction of a SEM (Scanning Electronic Microscope) photograph of a cross-sectional view of an array of container poly rings;

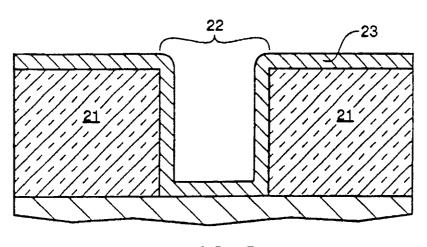

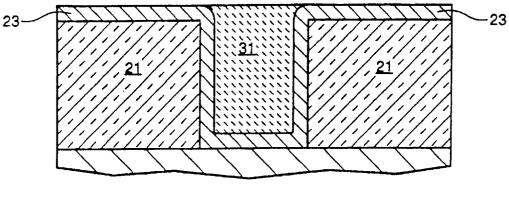

- FIG. 2 is a composite cross-sectional view of an in-process wafer portion depicting the beginning steps of the present invention, said steps comprising forming a planarized layer of low etch rate oxide, etching a buried contact and placing a thin layer of conformal poly;

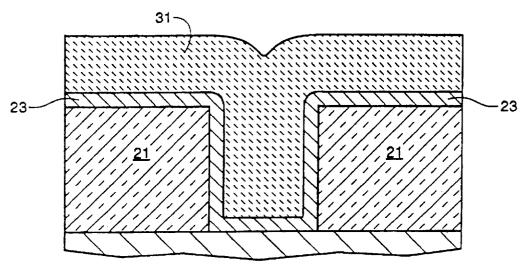

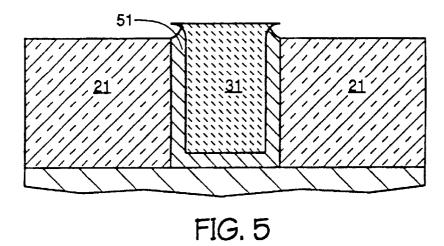

- FIG. 3 is a cross-sectional view of the in-process wafer portion of FIG. 2 after formation of a layer of high etch rate oxide:

- FIG. 4 is a cross-sectional view of the in-process wafer portion of FIG. 3 after planarization of the high etch rate oxide;

- FIG. 5 is a cross-sectional view of the in-process wafer 65 portion of FIG. 4 following a wet etch back of the exposed thin poly layer;

4

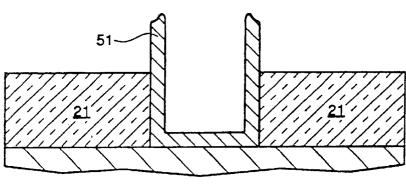

- FIG. 6 is a cross-sectional view of the in-process wafer portion of FIG. 5 following an etch of both low etch rate and high etch rate oxides;

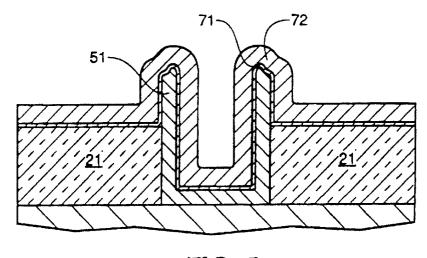

- FIG. 7 is a cross-sectional view of the in-process wafer portion of FIG. 6 following blanket formations of conformal cell dielectric and polysilicon, respectively;

- FIG. 8 is a cross-sectional view of a storage cell created by the present invention when integrated into a stacked capacitor fabrication process; [and]

- FIG. 9 is a composite cross-sectional view of an in-process wafer portion depicting a container cell filled with photoresist prior to patterning; and

- FIG. 10 is a composite cross-sectional view of the in-process wafer portion of FIG. 9 depicting splintering of storage node poly and formation of a thin ring of oxide surrounding the storage node poly following an anisotropic etching to pattern a container cell.

## DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENT

The invention is directed to maximizing storage cell surface area, as well as providing uniform and repeatable, defect free, storage cell structures across a given substrate, in a high density/high volume DRAM fabrication process, in a sequence shown in FIGS. 2–7.

A silicon wafer is prepared using conventional process steps up to the point of processing an array of storage cell capacitors. Capacitor cell fabrication will now follow.

The storage capacitor of each memory cell will make contact directly to an underlying diffusion area. Each underlying diffusion area will have two storage node connections isolated from a single digit line contact by access transistors formed by poly word lines crossing the active area. Normally each diffusion area within the array is isolated from one another by a thick field oxide. The diffusion areas can be arranged in interdigitated columns and non-interdigitated rows or simply parallel and in line to one another in both the vertical and horizontal directions. As previously mentioned, the diffusion areas are used to form active MOS transistors (serving as access transistors to each individual capacitor) that can be doped as NMOS or PMOS type FETs depending on the desired use.

Referring now to FIG. 2, a thick layer of low etch rate 45 oxide 21 is formed over an existing topography of a given substrate. Oxide 21 is then planarized, preferably by chemical-mechanical planarization (CMP) techniques down to a predetermined thickness. The thickness of planarized oxide 21 depends on the height that is desired for the poly container structure yet to be formed. The height of the resulting poly structure will determine the capacitor plate surface area that will be required to sufficiently hold a charge. It has been shown that a structure of approximately  $1.0-1.5\mu$  is sufficient to construct a reliable 64M DRAM cell using optimized cell dielectric (Container height depends on such factors as container diameter, dielectric constant and thickness of oxides used which are brought to light in the continuing discussion.). A contact opening 22 is then etched into oxide 21 thereby allowing access to the underlying topography (for DRAM-capacitor purposes this opening would normally expose a diffusion region conductively doped into a starting substrate). Contact opening 22 not only allows access to the underlying topography but also provides a form for a subsequent placed layer of thin poly. This thin poly is now formed, preferably by CVD, as a layer of conformal polysilicon 23 and is placed overlying planarized oxide 21, the patterned edges of oxide 21 and the exposed

underlying topography. Poly 23 may either have been deposited insitu doped or deposited insitu doped and rugged HSG poly for added cell capacitance or it may be subsequently doped.

Referring now to FIG. 3, a thick layer of oxide 31 having 5 a high etch rate is formed over poly 23. Oxide 31 is thick enough to completely fill the poly lined contact opening 22.

Referring now to FIG. 4, oxide layer 31 is removed down to poly 23, preferably by CMP which will selectively stop on the first exposed upper regions of poly 23.

Referring now to FIG. 5, the exposed upper portions of poly 23 are removed to separate neighboring poly structures, thereby forming individual containers 51 residing in contact openings 22 and exposing underlying oxide 21. The areas of poly 23 that are removed may be accomplished by performing a poly etch selective to oxide, which could be a timed wet etch or an optimized CMP poly etch. A very significant advantage of this process flow when a CMP etch step is utilized is that the inside of the future container 51 is protected from 'slurry' contamination that is inherent in the CMP step which proves difficult to remove in high aspect ratio storage containers  $(0.5\mu$  inside diameter by  $1.5\mu$  high).

Referring now to FIG. 6, both oxides 21 and 31, which have different etch rates, are now exposed. At this point, an oxide etch is performed such that oxide 31 is completely removed from inside container 51 while a portion of oxide 21 remains at the base of container 51 and thereby providing an insulating layer between the underlying topography and subsequent layers. [A] An etch rate ratio of 2:1 or greater between (a ratio of 4:1 is preferred) oxide 31 and oxide [22] 21 provides sufficient process margin to ensure all of high etch rate oxide 31 inside container 51 is removed during the single etch step, while a portion of oxide [22] 21 remains to provide adequate insulation from subsequently formed layers.

Referring now to FIG. 7, when using this structure to form a capacitor storage node plate container 51[and], the remaining portion of oxide 21 is coated with a capacitor cell dielectric 71. [And, finally] Finally a second conformal poly layer 72 is placed [to] onto blanket cell dielectric 71 and serves as a common capacitor cell plate to the entire array of containers 51. From this point on the wafer is completed using conventional fabrication process steps.

FIG. 8 depicts a cross-section of the present invention integrated into a stacked capacitor process on starting substrate 81. Container 51 connects to diffusion area 82 and thereby serves as a storage node container plate. Diffusion area 82 is accessed by word line 85 (separated by gate insulator 83) which in turn spans the channel's active area between diffusion areas 82. The poly of container 51 is doped to the same conductivity type as underlying diffusion region 82 to insure a good ohmic contact.

It is to be understood that although the present invention has been described with reference to a preferred embodiment, various modifications, known to those skilled 55 in the art, may be made to the structures and process steps presented herein without departing from the invention as recited in the several claims appended hereto.

We claim:

- 1. A process for fabricating a uniform and repeatable 60 conductive container structure on a starting substrate's existing topography, said process comprising the steps of:

- a) forming a blanketing first insulating layer, having a first etch rate, over said existing topography;

- b) patterning and etching an opening into said first insulating layer, said opening thereby forming a container form:

6

- c) forming a conformal first conductive layer superjacent said first insulating layer and said container form thereby lining said container form;

- d) forming a blanketing second insulating layer, having a second etch rate, superjacent said first conductive layer;

- e) removing said second insulating layer via chemical mechanical planarization until *an* upper portion of said first conductive layer is exposed;

- f) removing said exposed first conductive *layer* upper [layer] *portion* until underlying said first insulating layer is exposed, thereby [separating said first conductive layer into individual said] *forming a* conductive [containers] *container* having inner and outer walls;

- g) removing said first and said second insulating layers such that said second insulating layer is completely removed, thereby exposing the entire inner walls of said conductive container and said first insulating layer is partially removed, thereby exposing an upper portion of said outer walls of said conductive container, wherein the partially remaining first insulating layer provides insulation between [said] underlying substrate topography and subsequently formed layers;

- h) forming a third insulating layer superjacent and coextensive *with* said exposed *inner* walls and *an* inner bottom portion of said *conductive* container and said partially remaining first insulating layer; and

- i) forming a second conductive layer superjacent and coextensive with said third insulating layer.

- 2. A process as recited in claim 1, wherein said first insulating layer is planarized prior to said step of patterning and etching an opening into said first insulating layer.

- 3. A process as recited in claim 1, wherein said second insulating layer is a sacrificial layer conducive to said chemical mechanical planarization.

- **4**. A process as recited in claim **1**, wherein said first and said second insulating layers are oxides.

- 5. A process as recited in claim 1, wherein said first insulating layer etch rate is a lower etch rate than said second insulating layer etch rate.

- 6. A process as recited in claim 5, wherein the etch rate ratio between said second insulating layer etch rate and said first insulating layer etch rate is a ratio of 2:1 or greater.

- 7. A process as recited in claim 5, wherein the etch rate ratio between said second insulating layer etch rate and said first insulating layer etch rate is a ratio of 4:1.

- **8**. A process as recited in claim **1**, wherein said first and said second conductive layers are doped polysilicon.

- 9. A process as recited in claim  $\hat{\mathbf{8}}$ , wherein said doped polysilicon is formed by [insitu] in situ doped chemical vapor deposition.

- 10. A process as recited in claim 1, wherein said first, said second and said third insulating layers are formed by chemical vapor deposition.

- 11. A process for fabricating a uniform and repeatable conductive container structure on a starting substrate's existing topography, said process comprising the steps of:

- a) forming a blanketing first insulating layer, having a first etch rate, over said existing topography;

- b) patterning and etching an opening into said first insulating layer, said opening thereby forming a container form:

- c) forming a conformal first conductive layer superjacent said first insulating layer and said container forms thereby lining said container form;

- d) forming a blanketing second insulating layer, having a second etch rate, superjacent said first conductive layer;

- e) removing said second insulating layer until an upper portion of said first conductive layer is exposed;

- f) removing said exposed first conductive *layer* upper [layer] *portion* via chemical mechanical planarization until underlying said first insulating layer is exposed, thereby [separating said first conductive layer into individual said] *forming a* conductive [containers] *container* having inner and outer walls;

- g) removing said first and said second insulating layers such that said second insulating layer is completely removed, thereby exposing the entire inner walls of said conductive container and said first insulating layer is partially removed, thereby exposing an upper portion of said outer walls of said conductive container, wherein the partially remaining first insulating layer provides insulation between [said] underlying substrate topography and subsequently formed layers;

- h) forming a third insulating layer superjacent and coextensive *with* said exposed *inner* walls and *an* inner bottom portion of said *conductive* container and said partially remaining first insulating layer; and

- i) forming a second conductive layer superjacent and coextensive with said third insulating layer.

- 12. A process as recited in claim [1] 11, wherein said first insulating layer is planarized prior to said step of patterning and etching an opening into said first insulating layer.

- 13. A process as recited in claim [1] 11, wherein said second insulating layer is a sacrificial layer that is planarized by chemical mechanical planarization.

- 14. A process as recited in claim [1] 11, wherein said first <sup>30</sup> and said second insulating layers are oxides.

- 15. A process as recited in claim [1] 11, wherein said first insulating layer etch rate is a lower etch rate than said second insulating layer etch rate.

- 16. A process as recited in claim 15, wherein the etch rate ratio between said second insulating layer etch rate and said first insulating layer etch rate is a ratio of 2:1 or greater.

- 17. A process as recited in claim 15, wherein the etch rate ratio between said second insulating layer etch rate and said first insulating layer etch rate is a ratio of 4:1.

- **18**. A process as recited in claim 1, wherein said first and said second conductive layers are doped polysilicon.

- 19. A process as recited in claim 18, wherein said doped polysilicon is formed by [insitu] in situ doped chemical vapor deposition.

- 20. A process as recited in claim [1] 11, wherein said first, said second and said third insulating layers are formed by chemical vapor deposition.

- **21.** A process for fabricating a uniform and repeatable conductive container structure on a starting substrate's existing topography, said process comprising the steps of:

- a) forming a blanketing first insulating layer, having a first etch rate, over said existing topography;

- b) patterning and etching an opening into said first insulating layer, said opening thereby forming a container form;

- c) forming a conformal first conductive layer superjacent said first insulating layer and said container form, thereby lining said container form;

- d) forming a blanketing second insulating layer, having a second etch rate, superjacent said first conductive layer;

- e) removing said second insulating layer via chemical mechanical planarization until an upper portion of said first conductive layer is exposed;

- f) removing said exposed first conductive *layer* upper [layer] *portion* via chemical mechanical planarization

- until underlying said first insulating layer is exposed, thereby [separating said first conductive layer into individual said] forming a conductive [containers] container having inner and outer walls;

- g) removing said first and said second insulating layers such that said second insulating layer is completely removed, thereby exposing [the] entire inner walls of said conductive container and said first insulating layer is partially removed, thereby exposing an upper portion of said outer walls of said conductive container, wherein the partially remaining first insulating layer provides insulation between [said] underlying substrate topography and subsequently formed layers;

- h) forming a third insulating layer superjacent and coextensive *with* said exposed *inner* walls and *an* inner bottom portion of said *conductive* container and said partially remaining first insulating layer; and

- i) forming a second conductive layer superjacent and coextensive with said third insulating layer.

- 22. A process as recited in claim 21, wherein said first insulating layer is planarized prior to said step of patterning and etching an opening into said first insulating layer.

- 23. A process as recited in claim 21, wherein said second insulating layer is a sacrificial layer conducive to said chemical mechanical planarization.

- 24. A process as recited in claim 21, wherein said first and said second insulating layers are oxides.

- 25. A process as recited in claim 21, wherein said first insulating layer etch rate is a lower etch rate than said second insulating layer etch rate.

- 26. A process as recited in claim 25, wherein the etch rate ratio between said second insulating layer etch rate and said first insulating layer etch rate is a ratio of 2:1 or greater.

- 27. A process as recited in claim 25, wherein the etch rate ratio between said second insulating layer etch rate and said first insulating layer etch rate is a ratio [ob] of 4:1.

- **28**. A process as recited in claim **21**, wherein said first and said second conductive layers are doped polysilicon.

- 29. A process as recited in claim 28, wherein said doped polysilicon is formed by [insitu] in situ doped chemical vapor deposition.

- **30**. A process as recited in claim **21**, wherein said first, said second and said third insulating layers are formed by chemical vapor deposition.

- **31.** A process for fabricating a DRAM container storage capacitor on a silicon substrate having active areas, word lines and digit lines, said process comprising the following sequence of steps:

- a) forming a blanketing first insulating layer, having a first etch rate, over [said] existing topography;

- b) patterning and etching an opening into said first insulating layer, said opening thereby forming a container form;

- c) forming a conformal first conductive layer superjacent said first insulating layer and said container form, thereby lining said container form;

- d) forming a blanketing second insulating layer, having a second etch rate, superjacent said first conductive layer;

- e) removing said second insulating layer via chemical mechanical planarization until *an* upper portion of said first conductive layer is exposed;

- f) removing said exposed first conductive *layer* upper [layer] *portion* until underlying said first insulating layer is exposed, thereby [separating said first conductive layer into individual said] *forming a* container storage [capacitors] *capacitor* having inner and outer walls:

- g) removing said first and said second insulating layers such that said second insulating layer is completely removed, thereby exposing the entire inner walls of said container storage capacitor and said first insulating layer is partially removed, thereby exposing an upper 5 portion of said outer walls of said container storage capacitor, wherein the partially remaining first insulating layer provides insulation between [said] an underlying substrate topography and subsequently formed layers;

- h) forming a third insulating layer superjacent and coextensive with said exposed inner walls and an inner bottom portion of said storage capacitor and said partially remaining first insulating layer; and

- i) forming a second conductive layer superjacent and  $^{15}$ coextensive with said third insulating layer.

- 32. A process as recited in claim 31, wherein said first insulating layer is planarized prior to said step of patterning and etching an opening into said first insulating layer.

- 33. A process as recited in claim 31, wherein said second  $^{20}$ insulating layer is a sacrificial layer [conductive] conductive to said chemical mechanical planarization.

- 34. A process as recited in claim 31, wherein said first and said second insulating layers are oxides.

- 35. A process as recited in claim 31, wherein said first  $^{25}$ insulating layer etch rate is a lower etch rate than said second insulating layer etch rate.

- 36. A process as recited in claim 35, wherein the etch rate ratio between said second insulating layer etch rate and said first insulating layer etch rate is a ratio of 2:1 or greater.

- 37. A process as recited in claim 35, wherein the etch rate ratio between said second insulating layer etch rate and said first insulating layer etch rate is a ratio of 4:1.

- 38. A process as recited in claim 31, wherein said first and said second conductive layers are doped polysilicon.

- 39. A process as recited in claim 38, wherein said doped polysilicon is formed by [insitu] in situ doped chemical vapor deposition.

- 40. A process as recited in claim 31, wherein said first, said second and said third insulating layers are formed by chemical vapor deposition.

- 41. A process for fabricating a DRAM container storage capacitor on a silicon substrate having active areas, word lines and digit lines, said process comprising the following sequence of steps:

- a) forming a blanketing first insulating layer, having a first etch rate, over [said] existing topography;

- b) patterning and etching an opening into said first insulating layer, said opening thereby forming a container 50

- c) forming a conformal first conductive layer superjacent said first insulating layer and said container form, thereby lining said container form.

- d) forming a blanketing second insulating layer, having a  $_{55}$ second etch rate, superjacent said first conductive layer;

- e) removing said second insulating layer until an upper portion of said first conductive layer is exposed;

- f) removing said exposed first conductive laver upper [layer] portion via chemical mechanical planarization 60 until underlying said first insulating layer is exposed, thereby separating said first conductive layer into individual said] forming a container storage [capacitors capacitor having inner and outer walls;

- g) removing said first and said second insulating layers 65 such that said second insulating layer is completely removed, thereby exposing the entire inner walls of

10

- said container storage capacitor and said first insulating layer is partially removed, thereby exposing an upper portion of said outer walls of said container storage capacitor, wherein the partially remaining first insulating layer provides insulation between [said] an underlying substrate topography and subsequently formed layers;

- h) forming a third insulating layer superjacent and coextensive with said exposed inner walls and an inner bottom portion of said storage capacitor and said partially remaining first insulating layer; and

- i) forming a second conductive layer superjacent and coextensive with said third insulating layer.

- **42**. A process as recited in claim **41**, wherein said first insulating layer is planarized prior to said step of patterning and etching an opening into said first insulating layer.

- 43. A process as recited in claim 41, wherein said second insulating layer is a sacrificial layer that is planarized by chemical mechanical planarization.

- 44. A process as recited in claim 41, wherein said first and said second insulating layers are oxides.

- 45. A process as recited in claim 41, wherein said first insulating layer etch rate is a lower etch rate than said second insulating layer etch rate.

- 46. A process as recited in claim 45, wherein the etch rate ratio between said second insulating layer etch rate and said first insulating layer etch rate is a ratio of 2:1 or greater.

- 47. A process as recited in claim 45, wherein the etch rate ratio between said second insulating layer etch rate and said first insulating layer etch rate is a ratio of 4:1.

- 48. A process as recited in claim 41, wherein said first and said second conductive layers are doped polysilicon.

- 49. A process as recited in claim 48, wherein said doped polysilicon is formed by [insitu] in situ doped chemical vapor deposition.

- 50. A process as recited in claim 41, wherein said first, said second and said third insulating layers are formed by chemical vapor deposition.

- 51. A process for fabricating a DRAM container storage capacitor on a silicon substrate having active areas, word lines and digit lines, said process comprising the following sequence of steps:

- a) forming a blanketing first insulating layer, having a first etch rate, over [said] existing topography;

- b) patterning and etching an opening into said first insulating layer, said opening thereby forming a container form;

- c) forming a conformal first conductive layer superjacent said first insulating layer and said container form, thereby lining said container form;

- d) forming a blanketing second insulating layer, having a second etch rate, superjacent said first conductive layer;

- e) removing said second insulating layer via chemical mechanical planarization until an upper portion of said first conductive layer is exposed;

- f) removing said exposed first conductive layer upper [layer] portion via chemical mechanical planarization until underlying said first insulating layer is exposed, thereby [separating said first conductive layer into individual said forming a container storage [capacitors capacitor having inner and outer walls;

- g) removing said first and said second insulating layers such that said second insulating layer is completely removed, thereby exposing the entire inner walls of said container storage capacitor and said first insulating layer is partially removed, thereby exposing an upper

portion of said outer walls of said container storage capacitor, wherein the partially remaining first insulating layer provides insulation between [said] underlying substrate topography and subsequently formed layers;

- h) forming a third insulating layer superjacent and coextensive with said exposed inner walls and an inner bottom portion of said storage capacitor and said partially remaining first insulating layer; and

- i) forming a second conductive layer superjacent and coextensive with said third insulating layer.

- 52. A process as recited in claim 51, wherein said first insulating layer is planarized prior to said step of patterning and etching an opening into said first insulating layer.

- 53. A process as recited in claim 51, wherein said second insulating layer is a sacrificial layer conducive to said 15 of said third insulating layer. chemical mechanical planarization.

- 54. A process as recited in claim 51, wherein said first and said second insulating layers are oxides.

- 55. A process as recited in claim 51, wherein said first insulating layer etch rate is a lower etch rate than said second insulating layer etch rate.

- **56**. A process as recited in claim **55**, wherein the etch rate ratio between said second insulating layer etch rate and said first insulating layer etch rate is a ratio of 2:1 or greater.

- **57**. A process as recited in claim **55**, wherein the etch rate <sup>25</sup> ratio between said second insulating layer etch rate and said first insulating layer etch rate is a ratio of 4:1.

- 58. A process as recited in claim 51, wherein said first and said second conductive layers are doped polysilicon.

- **59**. A process as recited in claim **58**, wherein said doped  $^{30}$ polysilicon is formed by [insitu] in situ doped chemical vapor deposition.

- 60. A process as recited in claim 51, wherein said first, said second and said third insulating layers are formed by chemical vapor deposition.

- 61. A process for fabricating a capacitor on a substrate, said process comprising the steps of:

- providing a first insulating layer on said substrate, said insulating layer having an opening therein forming a  $_{40}$ container and being subject to a first etch rate;

- forming a generally conformal first conductive layer over said first insulating layer and in said container;

- forming a second insulating layer above said first conductive layer, wherein said second insulating layer is 45 an inner bottom portion of said conductive container. subject to a second etch rate;

- removing at least a portion of said second insulating layer through use of chemical mechanical planarization until an upper portion of said first conductive layer is exposed:

12

removing at least a portion of an upper portion of said first conductive layer until said first insulating layer is exposed; and

etching said first and second insulating layers such that said second insulating layer is completely removed thereby exposing the entire inner walls of said first conductive layer within said container, and such that said first insulating layer is partially removed.

62. The process of claim 61, further comprising the step of forming a third insulating layer over said inner walls of said first conductive layer within said container.

63. The process of claim 62, further comprising the step of forming a second conductive layer over at least a portion

64. A process for fabricating a DRAM containing storage capacitor on a silicon substrate having an existing topography including active areas, word lines and digit lines, said process comprising the steps of:

providing a first insulating layer having a first etch rate, over said existing topography;

forming an opening into said first insulating layer, said opening thereby forming a container;

forming a conformal first conductive layer over said first insulating layer and said container, thereby lining said container:

forming a second insulating layer having a second etch rate, over said first conductive layer;

removing said second insulating layer through use of chemical mechanical planarization until an upper portion of said first conductive layer is exposed;

removing at least a portion of an upper portion of said first conductive layer until said first insulating layer is exposed, thereby forming a conductive container having inner and outer walls; and

etching said first and second insulating layers such that said second insulating layer is completely removed, thereby exposing the entire inner walls of said first conductive layer within said container, and such that said first insulating layer is partially removed.

65. The process of claim 64, further comprising the step of forming a third insulating layer over said inner walls and

66. The process of claim 65, further comprising the step of forming a second conductive layer over at least a portion of said third insulating layer.

# UNITED STATES PATENT AND TRADEMARK OFFICE CERTIFICATE OF CORRECTION

PATENT NO. : RE 38,049 E Page 1 of 1

DATED : March 25, 2003

INVENTOR(S): Charles H. Dennison and Michael A. Walker

It is certified that error appears in the above-identified patent and that said Letters Patent is hereby corrected as shown below:

Title page,

Item [22], PCT Filed, change "Oct. 7, 1996" to -- Dec. 14, 1995 --

Signed and Sealed this

Third Day of May, 2005

JON W. DUDAS

Director of the United States Patent and Trademark Office