(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7598889号

(P7598889)

(45)発行日 令和6年12月12日(2024.12.12)

(24)登録日 令和6年12月4日(2024.12.4)

(51)国際特許分類

|         |                |     |         |      |       |

|---------|----------------|-----|---------|------|-------|

| G 0 2 F | 1/01 (2006.01) | F I | G 0 2 F | 1/01 | B     |

| G 0 2 B | 6/12 (2006.01) |     | G 0 2 B | 6/12 | 3 6 1 |

請求項の数 26 (全16頁)

|                   |                                  |          |                                                                                                                                      |

|-------------------|----------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------|

| (21)出願番号          | 特願2021-577094(P2021-577094)      | (73)特許権者 | 520447204<br>ライトマター インコーポレイテッド<br>L I G H T M A T T E R , I N C .<br>アメリカ合衆国 0 2 1 1 0 マサチューセッツ州 ボストン サマー ストリート<br>1 0 0 エイティーンス フロア |

| (86)(22)出願日       | 令和2年7月1日(2020.7.1)               | (74)代理人  | 100105957<br>弁理士 恩田 誠                                                                                                                |

| (65)公表番号          | 特表2022-539111(P2022-539111<br>A) | (74)代理人  | 100068755<br>弁理士 恩田 博宣                                                                                                               |

| (43)公表日           | 令和4年9月7日(2022.9.7)               | (74)代理人  | 100142907<br>弁理士 本田 淳                                                                                                                |

| (86)国際出願番号        | PCT/US2020/040428                | (72)発明者  | ドルタ - キニヨネス、カルロス<br>アメリカ合衆国 0 2 1 5 5 マサチューセッツ州 メドフォード ジェローム ス<br>最終頁に続く                                                             |

| (87)国際公開番号        | WO2021/003221                    |          |                                                                                                                                      |

| (87)国際公開日         | 令和3年1月7日(2021.1.7)               |          |                                                                                                                                      |

| 審査請求日             | 令和5年6月28日(2023.6.28)             |          |                                                                                                                                      |

| (31)優先権主張番号       | 62/869,690                       |          |                                                                                                                                      |

| (32)優先日           | 令和1年7月2日(2019.7.2)               |          |                                                                                                                                      |

| (33)優先権主張国・地域又は機関 | 米国(US)                           |          |                                                                                                                                      |

(54)【発明の名称】 フォトニクス安定化回路

## (57)【特許請求の範囲】

## 【請求項1】

フォトニクスベースの構成要素の光強度の測定値に基づいて第1の電気信号を出力するように構成されている光電気検出器であって、前記第1の電気信号は、前記フォトニクスベースの構成要素で伝送される電力を表す光電流を含み、前記光強度は、前記フォトニクスベースの構成要素の離調量に比例する前記光電気検出器と、

前記光電気検出器から出力されている前記第1の電気信号の前記光電流からオフセット値を減算することによって第2の電気信号を生成し、前記第2の電気信号に基づいてデジタル信号を出力するように構成されているアナログデジタル変換(ADC)回路と、

前記ADC回路から出力されているデジタル信号に少なくとも部分的に基づいて前記フォトニクスベースの構成要素を同調させるように構成されているフィードバック制御回路と、

前記ADC回路から出力されている前記デジタル信号を受信し、受信した前記デジタル信号に少なくとも部分的に基づいてデジタルパルス列を生成し、前記デジタルパルス列を前記フィードバック制御回路に供給するように構成されているデジタル制御器と、を含むデバイス。

## 【請求項2】

前記フォトニクスベースの構成要素は、リング共振器である、請求項1に記載のデバイス。

## 【請求項3】

前記フォトニクスベースの構成要素は、ビューポートを含み、前記光電気検出器は、前記ビューポートを介して光強度を検出するように構成されている光検出器を含む、請求項 1 又は 2 に記載のデバイス。

【請求項 4】

前記 A D C 回路は、デジタル信号の変換の前に前記光電気検出器から出力されている前記第 1 の電気信号の少なくとも一部を積分するように構成されている積分コンデンサを更に含む、請求項 1 ~ 3 のいずれか一項に記載のデバイス。

【請求項 5】

前記デジタル制御器は、前記積分コンデンサの積分時間を設定するように更に構成されている、請求項 4 に記載のデバイス。

10

【請求項 6】

前記 A D C 回路は、前記積分コンデンサによる積分の前に前記光電気検出器から出力されている前記第 1 の電気信号からオフセット値を引くように構成されている第 1 のアナログマルチプレクサを更に含む、請求項 4 又は 5 に記載のデバイス。

【請求項 7】

前記 A D C 回路は、前記第 1 のアナログマルチプレクサの出力と前記積分コンデンサとの間に配置されている第 2 のアナログマルチプレクサを更に含む、請求項 6 に記載のデバイス。

【請求項 8】

前記 A D C 回路は、前記積分コンデンサによって記憶されている電圧を増幅するように構成されている多段増幅回路を更に含む、請求項 4 ~ 7 のいずれか一項に記載のデバイス。

20

【請求項 9】

前記 A D C 回路は、デュアルスロープ積分 A D C を含む、請求項 1 ~ 8 のいずれか一項に記載のデバイス。

【請求項 10】

前記デジタル制御器は、カウンタを含む、請求項 1 ~ 9 のいずれか一項に記載のデバイス。

【請求項 11】

前記フィードバック制御回路は、デジタルアナログ変換器 ( D A C ) に結合されているパルス幅変調 ( P W M ) 回路を含む、請求項 1 ~ 10 のいずれか一項に記載のデバイス。

30

【請求項 12】

前記 D A C は、8 ビット以下の分解能を有する、請求項 11 に記載のデバイス。

【請求項 13】

前記 P W M 回路は、コードディザリングを実行するように構成されている、請求項 11 又は 12 に記載のデバイス。

【請求項 14】

前記デジタル制御器は、前記 P W M 回路によって実行されているコードディザリングの少なくとも 1 つのパラメータを制御するように構成されている、請求項 13 に記載のデバイス。

40

【請求項 15】

前記フィードバック制御回路は、前記フォトニクスベースの構成要素の温度を制御することによって、前記フォトニクスベースの構成要素を同調させるように構成されている、請求項 1 ~ 14 のいずれか一項に記載のデバイス。

【請求項 16】

前記フィードバック制御回路は、前記フォトニクスベースの構成要素の温度を制御するための熱を発生させることによって、前記フォトニクスベースの構成要素の温度を制御するように構成されている、請求項 15 に記載のデバイス。

【請求項 17】

前記フィードバック制御回路は、電気光学効果及びフォトニクスベースの構成要素の熱位相シフトのうち少なくとも 1 つを与える変調器を含む、請求項 15 又は 16 に記載のデ

50

バイス。

【請求項 18】

フォトニクスベースの構成要素を安定化させる方法であって、

前記フォトニクスベースの構成要素の離調量に比例する検出光強度に基づいて第1の電気信号を生成するステップであって、前記第1の電気信号は、前記フォトニクスベースの構成要素で伝送される電力を表す光電流を含むステップと、

前記第1の電気信号の前記光電流からオフセット値を引いて第2の電気信号を生成するステップと、

前記第2の電気信号を増幅するステップと、

増幅された前記第2の電気信号に基づいてデジタル信号を生成するステップと、

生成された前記デジタル信号に少なくとも部分的に基づいて前記フォトニクスベースの構成要素を同調させるステップと、を含む方法。

【請求項 19】

前記フォトニクスベースの構成要素は、リング共振器である、請求項18に記載の方法。

【請求項 20】

前記デジタル信号に少なくとも部分的に基づいてデジタルパルス列を生成するステップと、

生成された前記デジタルパルス列に少なくとも部分的に基づいて前記フォトニクスベースの構成要素を同調させるステップと、を更に含む、請求項18又は19に記載の方法。

【請求項 21】

前記デジタル信号を生成する前に前記第1の電気信号の少なくとも一部を積分するステップを更に含む、請求項18～20のいずれか一項に記載の方法。

【請求項 22】

前記第1の電気信号を積分するステップを実行する積分時間を動的に設定するステップを更に含む、請求項21に記載の方法。

【請求項 23】

前記第2の電気信号を増幅するステップは、多段増幅を実行するステップを含む、請求項18～22のいずれか一項に記載の方法。

【請求項 24】

生成された前記デジタル信号に基づいてコードディザリングを実行するステップを更に含む、請求項18～23のいずれか一項に記載の方法。

【請求項 25】

前記フォトニクスベースの構成要素を同調させるステップは、前記フォトニクスベースの構成要素の温度を制御するステップを含む、請求項18～24のいずれか一項に記載の方法。

【請求項 26】

前記フォトニクスベースの構成要素の温度を制御するステップは、前記フォトニクスベースの構成要素の温度を制御するための熱を発生させるステップを含む、請求項25に記載の方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、フォトニクス安定化回路に関する。

【背景技術】

【0002】

シリコンフォトニクスにおいて、リング/ディスク共振器は、様々な用途で使用される最も多目的な構成要素の1つである。リング/ディスク共振器の一般的な使用は、バス導波管からリング/ディスクへの光のエバネッセント結合を含む。この構成において、バス導波管の透過スペクトルは、リング共振でディップを示し、従って、高品質スペクトルフィルタ又はセンサとして使用可能である。例えば、p-n接合部又は熱抵抗器からの電気

10

20

30

40

50

入力と一緒に、リング／ディスク共振器は、高速電気光学変調器としても動作する。更に、共振に近い強い分散に起因する大きい群遅延のために、リング／ディスク共振器は、光遅延線の魅力的な選択肢である。

【発明の概要】

【0003】

本出願の態様は、フォトニクス構成要素の動作を安定化させる回路及び技法に関する。例えば、幾つかの実施形態において、温度の変動は、共振器の離調をもたらすリング／ディスク共振器の望ましくない位相シフトを引き起こす。ここに記載の回路及び技法は、望ましくない影響を補正するために、離調の高精度検出、及びフォトニクス構成要素の1つ又は複数の特性の高精度変調を行う。

10

【0004】

幾つかの実施形態は、フォトニクスベースの構成要素の光強度の測定値に基づいて電気信号を出力するように構成されている光電気検出器であって、光強度は、フォトニクスベースの構成要素の離調量に比例する光電気検出器と、光電気検出器から出力されている電気信号に基づいてデジタル信号を出力するように構成されているアナログデジタル変換（A D C）回路と、A D C回路から出力されているデジタル信号に少なくとも部分的に基づいてフォトニクスベースの構成要素を同調させるように構成されているフィードバック制御回路とを含むデバイスに関する。

【0005】

幾つかの態様において、フォトニクスベースの構成要素は、リング共振器である。

20

幾つかの態様において、フォトニクスベースの構成要素は、ビューポートを含み、光電気検出器は、ビューポートを介して光強度を検出するように構成されている光検出器を含む。

【0006】

幾つかの態様において、デバイスは、A D C回路から出力されているデジタル信号を受信し、受信した前記デジタル信号に少なくとも部分的に基づいてデジタルパルス列を生成し、デジタルパルス列をフィードバック制御回路に供給するように構成されているデジタル制御器を更に含む。

【0007】

幾つかの態様において、A D C回路は、デジタル信号の変換の前に光電気検出器から出力されている電気信号の少なくとも一部を積分するように構成されている積分コンデンサを更に含む。

30

【0008】

幾つかの態様において、デジタル制御器は、積分コンデンサの積分時間を設定するように更に構成されている。

幾つかの態様において、A D C回路は、積分コンデンサによる積分の前に光電気検出器から出力されている電気信号からオフセット値を引くように構成されている第1のアナログマルチプレクサを更に含む。

【0009】

幾つかの態様において、A D C回路は、第1のアナログマルチプレクサの出力と積分コンデンサとの間に配置されている第2のアナログマルチプレクサを更に含む。

40

幾つかの態様において、A D C回路は、積分コンデンサによって記憶されている電圧を増幅するように構成されている多段増幅回路を更に含む。

【0010】

幾つかの態様において、A D C回路は、デュアルスロープ積分A D Cを含む。

幾つかの態様において、デジタル制御器は、カウンタを含む。

幾つかの態様において、フィードバック制御回路は、デジタルアナログ変換器（D A C）に結合されているパルス幅変調（P W M）回路を含む。

【0011】

幾つかの態様において、D A Cは、8ビット以下の分解能を有する。

50

幾つかの態様において、P W M回路は、コードディザリングを実行するように構成されている。

【 0 0 1 2 】

幾つかの態様において、デジタル制御器は、P W M回路によって実行されているコードディザリングの少なくとも1つのパラメータを制御するように構成されている。

幾つかの態様において、フィードバック制御回路は、フォトニクスベースの構成要素の温度を制御することによって、フォトニクスベースの構成要素を同調させるように構成されている。

【 0 0 1 3 】

幾つかの態様において、フィードバック制御回路は、フォトニクスベースの構成要素の位相シフトを導入することによって、フォトニクスベースの構成要素の温度を制御するように構成されている。

10

【 0 0 1 4 】

幾つかの態様において、フィードバック制御回路は、電気光学効果及びフォトニクスベースの構成要素の熱位相シフトのうち少なくとも1つを与える変調器を含む。

幾つかの態様において、変調器は、抵抗器、p - n接合部、及びp - i - n接合部のうち少なくとも1つを含む。

【 0 0 1 5 】

幾つかの態様において、フィードバック制御回路は、フォトニクスベースの構成要素の温度を0 . 0 0 1 内に正確に制御するように構成されている。

20

幾つかの態様において、フィードバック制御回路は、印加電力において5 0 0 0 0 分の1の精度を有するように構成されている。

【 0 0 1 6 】

幾つかの態様において、フィードバック制御回路は、フィードバック制御回路によって生成されている時間平均電力に基づいてフォトニクスベースの構成要素を同調させるように構成されている。

【 0 0 1 7 】

幾つかの態様において、A D C回路は、ナノアンペアの範囲で電流感度を有するように構成されている。

幾つかの実施形態は、フォトニクスベースの構成要素を安定化させる方法に関する。方法は、フォトニクスベースの構成要素の離調量に比例する検出光強度に基づいて第1の電気信号を生成するステップと、第1の電気信号からオフセット値を引いて第2の電気信号を生成するステップと、第2の電気信号を增幅するステップと、増幅された第2の電気信号に基づいてデジタル信号を生成するステップと、生成されたデジタル信号に少なくとも部分的にに基づいてフォトニクスベースの構成要素を同調させるステップとを含む。

30

【 0 0 1 8 】

幾つかの態様において、フォトニクスベースの構成要素は、リング共振器である。

幾つかの態様において、方法は、デジタル信号に少なくとも部分的にに基づいてデジタルパルス列を生成するステップと、生成されたデジタルパルス列に少なくとも部分的にに基づいてフォトニクスベースの構成要素を同調させるステップとを更に含む。

40

【 0 0 1 9 】

幾つかの態様において、方法は、デジタル信号を生成する前に第1の電気信号の少なくとも一部を積分するステップを更に含む。

幾つかの態様において、方法は、第1の電気信号を積分するステップを実行する積分時間を動的に設定するステップを更に含む。

【 0 0 2 0 】

幾つかの態様において、第2の電気信号を増幅するステップは、多段増幅を実行するステップを含む。

幾つかの態様において、方法は、生成されたデジタル信号に基づいてコードディザリングを実行するステップを更に含む。

50

## 【0021】

幾つかの態様において、フォトニクスベースの構成要素を同調させるステップは、フォトニクスベースの構成要素の温度を制御するステップを含む。

幾つかの態様において、フォトニクスベースの構成要素の温度を制御するステップは、フォトニクスベースの構成要素の位相シフトを導入するステップを含む。

## 【0022】

幾つかの実施形態は、フォトニクスベースのリング共振器と、特定の期間にリング共振器の光強度を測定する光電気検出器と、リング共振器の温度変動を表す測定された光強度から精密信号を生成する精密回路と、リング共振器の温度を制御するフィードバック制御回路とを含むデバイスに関する。

10

## 【0023】

幾つかの態様において、フィードバック制御回路は、リング共振器の温度を0.001内に正確に制御する。

幾つかの態様において、精密回路は、デュアルスロープ積分アナログデジタル変換器（ADC）を含む。

## 【0024】

幾つかの態様において、フィードバック制御回路は、低精度デジタルアナログ変換器（DAC）及びコードディザリング回路を含む。

幾つかの態様において、フィードバック制御回路は、リング共振器に結合されている温度制御器を含む。幾つかの態様において、温度制御器は、リング共振器の位相シフトを導入する要素を含む。

20

## 【0025】

幾つかの態様において、温度制御器は、電気光学効果及びリング共振器の熱位相シフトのうち少なくとも1つを与える要素を含む。

幾つかの態様において、温度制御器は、抵抗器、p-n接合部、及びp-i-n接合部のうち少なくとも1つを含む。

## 【0026】

幾つかの実施形態は、周期的較正ベクトル中にフォトニクスベースのリング共振器によって出力される光の強度を測定するステップと、リング共振器の温度変動を表す測定された強度に基づいて電気信号を生成するステップと、フィードバックを介してリング共振器の温度を制御するステップとを含む方法を目的とする。

30

## 【0027】

幾つかの態様において、制御するステップは、リング共振器の温度を0.001内に制御するステップを含む。

幾つかの態様において、生成するステップは、デュアルスロープ積分アナログデジタル変換器（ADC）を使用するステップを含む。

## 【0028】

幾つかの態様において、生成するステップは、ナノアンペアの範囲で電流感度を有する高精度デジタル化信号を生成するステップを含む。

幾つかの態様において、生成するステップは、アナログベースライン減算を実行してデジタル化信号のダイナミックレンジを拡大するステップを含む。

40

## 【0029】

幾つかの態様において、制御するステップは、リング共振器に結合される温度制御器に制御信号を送るステップを含む。

幾つかの態様において、温度制御器は、リング共振器の位相シフトを導入する要素を含む。

## 【0030】

幾つかの態様において、温度制御を行うために使用される要素は、抵抗器、p-n接合部及びp-i-n接合部のうち少なくとも1つを含む。

幾つかの態様において、制御するステップは、低精度DACを用いてデジタルアナログ

50

変換 (D A C) を実行することによって制御信号を生成するステップを含む。

【0031】

幾つかの態様において、制御するステップは、コードディザリング方式を実行するステップを更に含む。

幾つかの態様において、制御するステップは、印加電力において 50000 分の 1 のオーダの精度を有する。

【0032】

幾つかの実施形態は、フォトニクスベースのリング共振器と、リング共振器の光強度を検出する光電気検出器と、リング共振器の温度変動を表す検出光に基づいて信号をデジタル化する低雑音高精度アナログデジタル変換器 (A D C) と、検出光に基づいて温度制御信号を供給するデジタルフィードバック回路と、制御信号に基づいてリング共振器の温度を制御する、リング共振器に結合されている温度制御器とを含むデバイスを目的とする。

10

【0033】

幾つかの態様において、A D C は、デュアルスロープ積分 A D C を含む。

幾つかの態様において、A D C は、ナノアンペアの範囲で電流感度を有する高精度デジタル化信号を生成する。

【0034】

幾つかの態様において、フィードバック回路は、低精度デジタルアナログ変換器 (D A C) を含む。

幾つかの態様において、フィードバック回路は、コードディザリング回路を更に含む。

20

【0035】

幾つかの態様において、温度制御器は、リング共振器の位相シフトを導入する要素を含む。

幾つかの態様において、温度制御器は、抵抗器、p - n 接合部及び p - i - n 接合部のうち少なくとも 1 つを含む。

30

【0036】

幾つかの態様において、検出器は、周期的較正期間中にリング共振器の光強度を検出する。

上述又はより詳細に後述の態様、特徴、及び動作の任意の適切な組み合わせを用いて、上述の装置及び方法の実施形態を実施してもよい。本教示のこれら及び他の態様、実施形態、及び特徴は、添付図面と併せて下記の説明からより十分に理解することができる。

【図面の簡単な説明】

【0037】

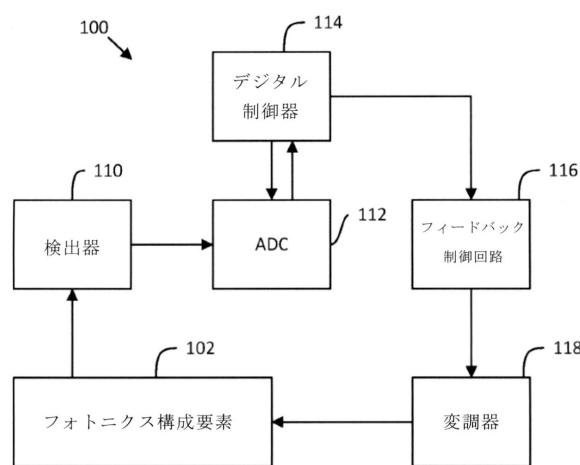

【図 1】幾つかの実施形態によるフォトニクス構成要素を安定化させるシステムのブロック図を例示する。

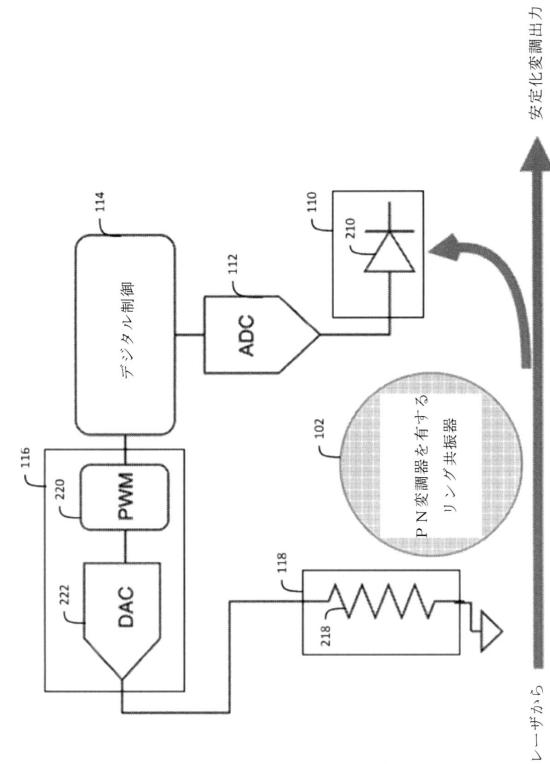

【図 2】幾つかの実施形態によるリング / ディスク共振器を安定化させるシステムの略図を例示する。

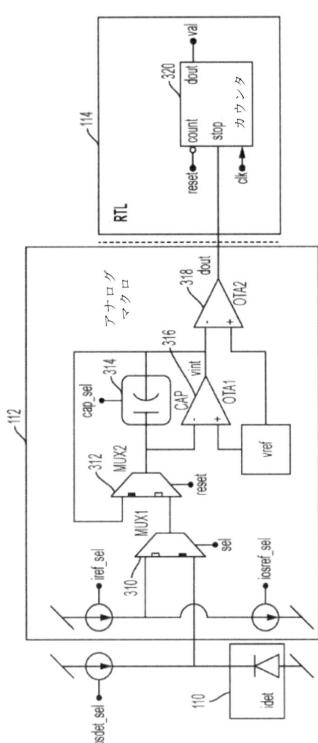

【図 3】幾つかの実施形態によって使用されるアナログデジタル変換回路を例示する。

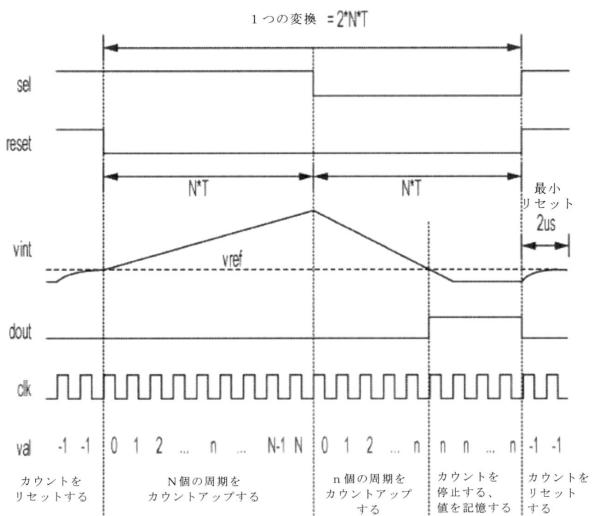

【図 4】幾つかの実施形態によるデジタル制御器によって生成される制御信号に対するタイミング図を例示する。

40

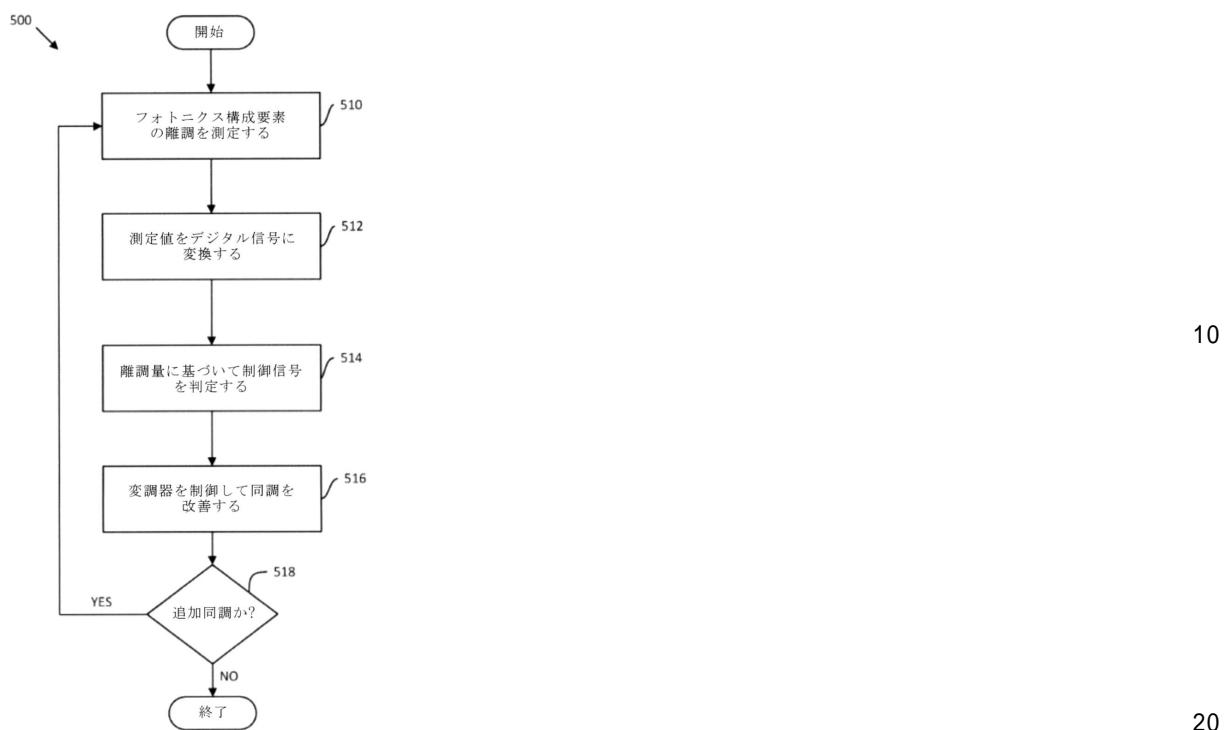

【図 5】幾つかの実施形態によるフォトニクス構成要素を安定化させる工程のフローチャートを例示する。

【発明を実施するための形態】

【0038】

リング / ディスク共振器などの多くのフォトニクス構成要素は、フォトニクス構成要素が準最適に実行するようにする変動 (例えば、温度変動) に敏感である。例えば、入力光信号の安定した変調を維持するために、リング / ディスク共振器の温度を、狭い範囲の温度内に維持すべきである。高精度の用途において、この温度は、0.001 未満内への制御を必要とすることがある。半導体デバイスに対する従来の熱監視は、熱ダイオードを使用する。しかし、これらのデバイスは、所望のレベルの精度まで正確に測定することが

50

できないことが多い。

【0039】

光学システムの性能の測定は、ナノアンペアの範囲における電流変動の検出を含んでもよい。しかし、これらのシステムの雑音レベルが典型的に、関心のある信号を雑音に覆い隠す変動のレベルを超える時に、これらの信号を電気フィードバック回路で直接使用することは実際的ではない。更に、従来の安定化リング共振器における增幅器設計は、高精度でリング/ディスク共振器を制御することができない。発明者は、高精度でリング/ディスク共振器などのフォトニクス構成要素を安定化させる従来の技法を改良することができる分かっている。このために、幾つかの実施形態は、フォトニクス構成要素の高感度検出及び高精度変調制御を行う回路及び技法を目的とする。

10

【0040】

図1は、フォトニクス構成要素102の1つ又は複数の態様（例えば、温度、位相）を安定化させるシステム100のブロック図を例示する。より詳細に後述のフォトニクス構成要素102の例は、リング/ディスク共振器である。しかし、フォトニック結晶空洞及びマッハツエンダー干渉計（但し、これらに限定されない）を含む、正確な温度制御又は位相安定化を要求する他のフォトニクス構成要素で、ここに記載の検出及びフィードバック制御回路を代わりに使用することができる分かることは、必ずある。更に、リング状のデバイスをフォトニクス構成要素102の1つの例として説明しているが、ここに記載の安定化回路で、リング以外の形状を有する空洞を有するフォトニクスデバイスを代わりに使用することができる分かることは、必ずある。

20

【0041】

システム100は、時間に応じて変化するフォトニクス構成要素102の関心のある特性を測定するように構成されている検出器110を含む。例えば、幾つかの実施形態において、検出器110は、リング/ディスク共振器で伝送される電力を表す光電流を検出するように構成されている。フォトニクス構成要素102の離調量（例えば、時間にわたるある特性の変動）に比例する信号を供給することができる任意の適切な検出器110を使用してもよい。

30

【0042】

更に、システム100は、検出器110によって生成されたアナログ信号を、フィードバック制御信号を設定するために使用可能なデジタル信号（例えば、デジタルビット列）に変換するアナログデジタル（ADC）回路112を含む。幾つかの実施形態において、ADC回路112の1つ又は複数の構成要素は、より詳細に後述のように、デジタル制御器114から受信される信号に基づいて構成可能である。アナログデジタル変換の実行に加えて、ADC回路112は、入力アナログ信号のオフセット成分を除去する、及び/又は所望のダイナミックレンジ内に信号を拡大することによって入力アナログ信号の信号対雑音比を改善する増幅を行う1つ又は複数の構成要素を含んでもよい。ADC112から出力されたデジタル信号を、デジタル制御器114に供給し、デジタル制御器114は、検出工程からのデジタル信号を使用して、フォトニクス構成要素102を同調するために1つ又は複数のフィードバック制御パラメータを設定する。

30

【0043】

更に、システム100は、制御信号をデジタル制御器114から受信し、高精度の制御出力を生成するように構成されているフィードバック制御回路116を含む。高精度制御出力を使用して、変調器118を制御し、フォトニクス構成要素102の関心のある特性（例えば、温度、位相）を安定化させる。

40

【0044】

図2は、安定化されるべきフォトニクス構成要素102がフォトニクスベースのリング/ディスク共振器であるシステム100の実装形態を概略的に例示する。図示のように、レーザから光を受信する入力導波管にリング/ディスク共振器を結合し、安定化変調出力を生成する。光電気要素210を用いて、検出器110を実施し、検出器110の例は、光検出器（例えば、フォトダイオード）である。共振器が完全に同調される場合、フォト

50

ダイオードによって光を検出しない。しかし、（例えば、温度変動又は製造変動のために）共振器が離調される場合、一部の電力は、共振器によって伝送され、フォトダイオードによって検出される。光電気要素 210 は、検出光に応じて時間にわたって電流又は電圧を積分する積分要素（例えば、コンデンサ）を含んでもよく、又は積分要素に関連付けられてもよい。次に、積分電流又は電圧を、より詳細に後述のように、ADC 回路 112 の構成要素によって更に処理してもよい。

#### 【0045】

システムへの入力として供給される周期的較正ベクトル中に受信される光の強度を測定するように、光電気要素 210 を構成してもよい。温度を調整して任意の大域温度変化に対応することができるように十分頻繁に較正ベクトルを送信してもよい。例えば、 $10 \mu s$ 、 $100 \mu s$ 、 $1 ms$  毎に、又は  $10 \mu s$  と  $1 ms$  との間の任意の他の適切な時間間隔で、較正ベクトルを送信してもよい。リング／ディスク共振器の観測窓を介して、光強度を光電気要素 210 によって取り込む。このようにして、この測定用の光学システムから少量の光を取り込む。光量が少ないので、関連電気信号も非常に小さく、典型的にマイクロアンペアのオーダである。

#### 【0046】

任意の適切な方法でリング／ディスク共振器から光を検出するように、光電気要素 210 を配置してもよい。例えば、図 2 に示すような入力導波管との結合点の近くに設置される代わりに、リング／ディスク共振器のある他の点で光を検出するように、光電気要素 210 を設置してもよい。

#### 【0047】

図 2 に示すシステムは、光電気要素 210 から電気信号を入力として受信し、入力電気信号をデジタル信号に変換するアナログデジタル変換（ADC）回路 112 を含む。

検出電気信号の小さい振幅のために、ADC 回路 112 は、より詳細に後述のように、入力信号を增幅する、及び／又はオフセット（例えば、ベースライン）成分の減算などの他の処理を実行する回路を含んでもよい。幾つかの実施形態において、ADC 回路 112 は、後述のアナログベースライン減算を用いた電流モードデュアルスロープ積分 ADC（IADC）を含み、この例を図 3 に一層詳細に示す。IADC は、ナノアンペアの範囲で電流感度を有する高精度デジタル化信号を出力するように構成されている。IADC アーキテクチャの電流モード機構は、フォトニクスシステムの他の構成要素を有する ADC 回路 112 の直接積分を容易にする。積分トポロジは、積分窓にわたって望ましくない高周波雑音を平均し、その結果、システムの検出感度が増加する。IADC 回路の得られるデュアルスロープアーキテクチャは、設計の感度を低くして積分器の変動を処理し、その結果、精度が増加する。

#### 【0048】

ADC 回路 112 の出力は、デジタル制御器 114 に入力として供給されるデジタルビット列である。デジタル制御器 114 は、デジタルビット列で動作して、制御信号を判定し、フィードバック制御回路 116 に送信する。幾つかの実施形態において、デジタル制御器 114 をカウンタとして実施し、この例を、図 3 及び図 4 に関連して説明する。

#### 【0049】

デジタル制御器から出力される制御信号は、デジタルパルス列であってもよく、フィードバック制御回路 116 に供給されて、変調器 118 に送出される時間平均電力を制御する。幾つかの実施形態において、デジタル制御器に入力されるデジタルビット列の大きさに少なくとも部分的に基づいて、デジタルパルス列のパルス幅及び／又はデューティサイクルを判定する。フィードバック制御回路 116 は、リング共振器 102 の特性を制御するために、変調器 118 に電圧をかけるように構成されている。図 2 の実装形態において、リング共振器の温度を制御する熱を発生する抵抗器として、変調器 118 を実施する。抵抗器によって発生される熱量は、上述のように、ADC 回路 112 によって取り込まれる測定値に基づいている。幾つかの実施形態において、p-n 接合部及び p-i-n 接合部（但し、これらに限定されない）を含む、抵抗器以外の 1 つ又は複数の構成要素を用い

10

20

30

40

50

て、変調器 118 を実施してもよい。

【0050】

リングの温度の厳しい制御を維持するために、幾つかの実施形態において、フィードバック制御回路 116 は、印加電力において 50000 分の 1 のオーダの精度を有する。発明者は、従来の高精度 DAC が、雑音に対する DAC の感度のためにこの性能要件を満たすことができないことが分かっている。更に、DAC の実装形態に必要な大きい領域、DAC の低動作速度、及び DAC を動作させるのに必要な大量の電力は、従来の高精度 DAC の望ましくない特性であり、その結果、高精度 DAC は、ここに記載のような高精度フィードバック制御システムで用いるのに適さない。

【0051】

変調器 116 を駆動するために高精度 DAC を使用する代わりに、幾つかの実施形態は、低精度回路及びデジタル符号化技法の組み合わせを使用して、高精度制御を実現する。図 2 に示すように、フィードバック制御回路 116 は、パルス幅変調 ( PWM ) 回路 220 及び低精度（例えば、8 ビット）デジタルアナログ変換器 ( DAC ) 222 を含む。 PWM 回路 220 の精度及び DAC 222 の精度の組み合わせに基づいて、制御方式の精度を判定し、これによって、低精度 DAC を使用することができ、高精度出力を実現する。 PWM 回路 220 は、デジタル制御器 114 からデジタルパルス列を入力として受信する。例えば、8 ビット PWM 周期で、256 ( $2^8$ ) 個の 2 値があり、2 値の各々は、入力デジタルパルス列で 0 又は 1 の値を含んでもよい。従って、 $2.560 \mu s$  の周期にわたって  $1/256$  の増分で、変調器を制御することができ、これによって、8 ビットの精度をフィードバック制御回路出力に追加する。8 ビット PWM 周期は、使用可能な PWM 周期の 1 つの例に過ぎず、システムの熱時定数が全 PWM 周期を超えるという条件で、より大きい（又はより小さい） PWM 周期を代わりに使用可能であることが分かるはずである。低精度（例えば、8 ビット）DAC 222 と組み合わせて使用した場合、フィードバック制御出力の全精度は、PWM 回路 220 及び DAC 222（例えば、16 ビット）によって与えられる精度の合計であり、リング / ディスク共振器に対する温度調節の微調整になる。

【0052】

幾つかの実施形態において、デジタル符号化方式を使用して、フィードバック制御回路 116 の高精度を更に増加する。このようなデジタル符号化方式の例は、コードディザリングである。コードディザリングを含む実施形態において、PWM 回路 220 は、高い周波数で出力隣接 DAC コードの間で交互する。例えば、各 PWM 周期で、PWM 回路 220 は、コード = N を駆動するかコード = N + 1 を駆動するかを判定するように構成されている。デジタル制御器 114 は、コード = N 対コード = N + 1 に費やされた時間の割合を制御するように構成されており、ディザ出力は、非常に低い精度の DAC を用いて非常に高い精度を実現する。制御されている電気及び熱システムは、システムに適用された得られる同調が、所望の精度要件（例えば、印加電力において 50000 分の 1 ）を満たすことができるよう、ディザコードを自動的に平均する低域通過フィルタを提供する。

【0053】

リング / ディスク共振器の温度を制御する熱を発生するために高精度で駆動される抵抗器として、変調器 116 を、図 2 の実装形態に示す。しかし、電子分散及びカーネル非線形性（但し、これらに限定されない）を含む異なる変調技法を提供するように設計されている他の構成要素を用いて、変調器 116 を実施することができるよう分かるはずである。

【0054】

図 3 は、ADC 回路 112 に含まれることができる例示的な IADC 回路を例示する。図示のように、ADC 回路 112 は、一定の時間にわたって光電気要素 210 から積分コンデンサ 314 に入力電流を導く 1 対のアナログマルチプレクサ ( MUX1 310, MUX2 312 ) を含む。例えば、積分コンデンサ 314 は、 $10 \sim 20 \mu F$  のオーダの値を有してもよく、積分時間を、 $1 \sim 10 \mu s$ （例えば、 $2 \mu s$ ）の範囲内に設定してもよい。

10

20

30

40

50

## 【0055】

更に、A D C回路112は、1対の演算相互コンダクタンス増幅器(OTA1 316、OTA2 318)を含む。例えば、OTA1及びOTA2は、高利得低電圧折り返しカスコードOTAであってもよく、OTA1及びコンデンサ314は、フィードバック積分器として構成されており、OTA2は、開ループ比較器(又はゼロ交差検出器)として構成されている。Vrefは、単一供給OTAで仮想接地としての機能を果たす低電圧バンドギャップ基準回路によって生成される直流基準電圧(例えば、500mV)である。

## 【0056】

図3の回路において、カウンタ320を用いてデジタル制御器114を実施する。図4は、図3に示すI A D C回路の1つのA D C変換周期に対するタイミング図を説明する。タイミング図は、幾つかの実施形態によるI A D C回路の構成要素を制御するカウンタ320によって生成される制御信号を含む。例えば、入力信号のタイミングは、積分コンデンサ314の異なる充電/放電時間を与えて、入力電流の正確な測定を可能にする。

10

## 【0057】

幾つかの実施形態において、図3に示すI A D C回路は、下記のように図4に示すタイミング図に従って動作するように構成されている。最初に、リセット信号(reset)をアサートして、積分器314の出力電圧及びカウンタ320の値の両方をゼロにそれぞれリセットする。A D C変換周期の開始に、まず、リセット信号をデアサートして、積分器314を使用可能にする。同様に、選択信号(sel)をアサートして、積分段階の開始を指示し、N=400の期間、5nsのクロック周期、又は2μsの同等の積分期間にわたって、正の直流入力光電流(idet)を積分器314に供給する。この時間中に、積分器314は、入力電流の割合に比例する正の傾斜を有する線形電圧アップランプをノードvintで生成する。積分段階の最後に、ノードvintにおける電圧は、vint = (idet/Cint) \* T(但し、Cintは、積分静電容量(例えば、16pF)である)によって与えられる。その後、信号selをデアサートして、非積分段階の開始を指示し、一定の負の基準電流(iref)を積分器314に供給する。この時間中に、積分器314が、一定の負の傾斜を有する線形電圧ダウンランプをノードvintで生成しながら、デジタルアップカウンタは、数え始める。ノードvintにおける電圧がゼロに達した場合、比較器318は、カウンタ320を停止するノードdoutでゼロ交差検出信号を生成する。この時に、既存のカウンタ値は、メモリに記憶される出力コードになる。出力コードは、D = ceil[N \* (idet / iref)](但し、0 < idet / iref < 1)によって与えられる。非積分段階の最後に、リセット信号(reset)をアサートして、積分器314及びカウンタ320をリセットし、変換周期の終了を指示する。

20

## 【0058】

発明者は、リング/ディスク共振器の温度変動を表す小さい検出電流を大きい直流ベースライン電流によって覆い隠すことが分かっている。幾つかの実施形態は、増幅の前にこの直流ベースライン電流を少なくとも部分的に除去する回路を含み、これによって、精度を向上させ、システムのダイナミックレンジを拡大する。高分解能システムで変換毎に望ましくないベースライン電流を解決する代わりに、変換の前に冗長ベースラインを除去して少数のビットを意図的に解決することによって、非常に低い精度のA D Cで、同様の高精度の結果を実現してもよい。幾つかの実施形態において、これは、下記のように望ましくない直流ベースラインを除去するプログラム可能な温度感度の低いバンドギャップ電流基準を生成することによって達成される。電流除去方式は、入力電流(idet)及び基準電流(iref)の両方から直流オフセット電流(iosdet及びiosref)をそれぞれ引くことによってダイナミックレンジを更に改善することができる。この場合、出力コードは、D = ceil[N \* (idet - iosdet) / (iref - iosref)](但し、0 < (idet - iosdet) / (iref - iosref) < 1)によって与えられる。オフセット電流の適切な選択は、項(idet - iosdet) / (iref - iosref)を最大化して、1に近くなり、次に、A D C出力コードを最

30

40

50

大化し、従って、システムのダイナミックレンジを改善する。直流ベースラインを引き、次いで残りの入力電流信号を増幅して、A D Cのダイナミックレンジを拡大する組み合わせは、低精度構成要素を用いた高精度検出回路を提供する。

#### 【 0 0 5 9 】

受動A D Cシステムではなく、幾つかの実施形態は、A D C回路112の動作方法の様々な態様を制御するためにデジタル制御器114から出力される制御信号を使用する。例えば、デジタル制御器114は、制御信号c a p \_ s e 1を用いて積分の傾斜又は速度を設定してもよい。更に、デジタル制御器114は、積分中に引く直流オフセット電流(i o s d e t)を選択するi o s d e t \_ s e 1信号、非積分中に引く直流オフセット電流(i o s r e f)を選択するi o s r e f \_ s e 1信号、積分段階と非積分段階との間で選択するM U X 3 1 0に供給されるs e 1信号、及び積分周期後に積分コンデンサ314上の電圧をリセットするM U X 3 1 2に供給されるr e s e t信号を含むA D C回路112に他の制御信号を供給してもよい。

#### 【 0 0 6 0 】

図5は、幾つかの実施形態によるフォトニクスベースの構成要素を安定化させるために変調器の高精度フィードバック制御を行う工程500を例示する。動作510で、フォトニクスベースの構成要素の離調を測定する。例えば、上述のシステムの例において、フォトダイオードを使用して、リング/ディスク共振器から抽出された少量の光を測定し、共振器の性能が、温度変動のために最適(共振)状態から変化しているかどうかを判定する。次に、工程500は、動作512に進み、動作512で、検出器によって生成されるアナログ電気信号(例えば、電流)を、デジタル制御器による処理用のデジタル信号に変換する。上述のように、幾つかの実施形態において、デジタル信号への変換の前に、(例えば、オフセット値を引くことによって、増幅を実行することによって、)入力電気信号を処理する。

#### 【 0 0 6 1 】

次に、工程500は、動作514に進み、動作514で、デジタル制御器は、A D C回路によって生成されるデジタル信号に符号化される離調量に少なくとも部分的に基づいて制御信号を生成する。例えば、上述の例において、デジタル制御器は、フィードバック制御回路への入力として供給されるデジタルパルス列を生成する。次に、工程500は、動作516に進み、動作516で、フィードバック制御回路を使用して、変調器を制御し、フォトニクス構成要素の同調を改善する。上述の例において、変調器は、抵抗器に印加される電流に応じて熱を発生するように構成されている抵抗器である。フィードバック制御回路は、抵抗器に供給される時間平均電力を制御して、検出器によって検出される温度変動を高精度で補償する。

#### 【 0 0 6 2 】

次に、工程500は、動作518に進み、動作518で、フォトニクス構成要素の追加同調を要求するかどうかを判定する。追加同調を要求しないと判定した場合、工程500は終了する。追加同調を要求すると判定した場合、工程500は、動作510に戻り、動作510で、フォトニクス構成要素の離調の新しい測定を行い、フォトニクス構成要素の同調をもはや要求しないと動作518で判定するまで、工程は繰り返す。

#### 【 0 0 6 3 】

この出願の技術の幾つかの態様及び実施形態をこのように説明しているが、様々な変更、修正及び改良は、当業者に容易に気付くことが分かるはずである。このような変更、修正及び改良は、この出願に記載の技術の範囲及び精神の範囲内にあるように意図されている。従って、上述の実施形態はほんの一例として提示されるものとし、添付の特許請求の範囲及び特許請求の範囲の均等物の範囲内で、明確に記載されたものと別の方法で発明の実施形態を実施することができるものとする。更に、ここに記載の2つ以上の特徴、システム、物、材料、及び/又は方法の任意の組み合わせは、このような特徴、システム、物、材料、及び/又は方法が相互に矛盾しない場合、本開示の範囲内に含まれる。

#### 【 0 0 6 4 】

10

20

30

40

50

更に、記載のように、幾つかの態様を、1つ又は複数の方法として具体化してもよい。任意の適切な方法で、方法の一部として実行される動作を順序付けしてもよい。従って、例示と異なる順序で動作を実行する実施形態を構成してもよく、例示の実施形態で連続動作として示されていても、幾つかの動作を同時に実行することを含んでもよい。

#### 【0065】

ここで定義及び使用されるような全定義は、辞書の定義、参照によって組み込まれた文書の定義、及び／又は定義用語の通常の意味にわたって管理するものとする。

明細書及び特許請求の範囲で使用されるような不定冠詞「1つ(a)」及び「1つ(a n)」は、明確に指示がない限り、「少なくとも1つ(at least one)」を意味するものとする。

10

#### 【0066】

明細書及び特許請求の範囲で使用されるような用語「及び／又は(and/or)」は、結合される要素、即ち、ある場合に接続的に存在し、他の場合の離接的に存在する要素の「一方又は両方(either or both)」を意味するものとする。

#### 【0067】

明細書及び特許請求の範囲で使用されるように、1つ又は複数の要素のリストに関する用語「少なくとも1つ(at least one)」は、要素のリストにおける要素のうち任意の1つ又は複数の要素から選択される少なくとも1つの要素を意味するものとし、要素のリスト内で具体的に列挙されたあらゆる要素のうち少なくとも1つの要素を必ずしも含む必要はなく、要素のリストにおける要素の任意の組み合わせを除外しない。更に、この定義により、具体的に識別された要素に関係があろうとなかろうと、用語「少なくとも1つ(at least one)」が参照する要素のリスト内で具体的に識別された要素以外に、要素は、任意選択的に存在することができる。

20

#### 【0068】

用語「約(approximately)」及び「約/about」は、幾つかの実施形態で目標値の±20%の範囲内、幾つかの実施形態で目標値の±10%の範囲内、幾つかの実施形態で目標値の±5%の範囲内、及び幾つかの実施形態で目標値の±2%の範囲内を意味するために使用されてもよい。用語「約(approximately)」及び「約/about」は、目標値を含んでもよい。

30

40

50

【図面】

【図 1】

【図 2】

10

20

30

40

【図 3】

【図 4】

50

【図 5】

10

20

30

40

50

## フロントページの続き

トリート 45

(72)発明者 レイミー、カール

アメリカ合衆国 01581 マサチューセッツ州 ウエストボロー アダムズ ストリート 39

(72)発明者 ユルドゥルム、オメル オズギュル

アメリカ合衆国 02482 マサチューセッツ州 ウェルズリー ベーコン ストリート 7

(72)発明者 ラヴィ、チシラ

アメリカ合衆国 02145 マサチューセッツ州 サマービル ローウェル ストリート 336 ユニット 2

(72)発明者 グプタ、シャシャンク

アメリカ合衆国 02458 マサチューセッツ州 ニュートン ホーソーン ストリート 44

(72)発明者 ハリス、ニコラス シー。

アメリカ合衆国 02130 マサチューセッツ州 ボストン シェリダン ストリート 38

審査官 奥村 政人

(56)参考文献 特開2008-065030 (JP, A)

特開2013-130738 (JP, A)

米国特許出願公開第2010/0200733 (US, A1)

米国特許出願公開第2015/0323818 (US, A1)

特開2010-175743 (JP, A)

特開2008-182688 (JP, A)

特開2010-224189 (JP, A)

韓国公開特許第10-2007-0098535 (KR, A)

特表2019-523932 (JP, A)

SUN et al. , A 45 nm CMOS-SOI Monolithic Photonics Platform With Bit-Statistics-Based Resonant Microring Thermal Tuning , IEEE Journal of Solid-State Circuits , 米国 , IEEE , 2016年03月04日 , Vol.51, No.4 , p.893-p.907

寺尾 麗、他 , S i リング光共振器の温度補償 , 第56回応用物理学関係連合講演会講演予稿集 , 日本 , 公益社団法人応用物理学会 , 2009年 , p.1233

(58)調査した分野 (Int.Cl. , DB名)

G 02 F 1 / 00 - 1 / 125

G 02 F 1 / 21 - 7 / 00

G 02 B 6 / 12 - 6 / 14

G 02 B 6 / 26 - 6 / 27

G 02 B 6 / 30 - 6 / 34

G 02 B 6 / 42 - 6 / 43

IEEE Explore