(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-32875

(P2004-32875A)

(43) 公開日 平成16年1月29日(2004.1.29)

(51) Int.CI.<sup>7</sup>

H02M 3/155

F 1

H02M 3/155

テーマコード(参考)

H 5 H 7 3 O

|           |                              | 審査請求 未請求 請求項の数 14 O L (全 19 頁)                     |

|-----------|------------------------------|----------------------------------------------------|

| (21) 出願番号 | 特願2002-184103 (P2002-184103) | (71) 出願人 000002185<br>ソニー株式会社<br>東京都品川区北品川6丁目7番35号 |

| (22) 出願日  | 平成14年6月25日 (2002. 6. 25)     | (74) 代理人 100094053<br>弁理士 佐藤 隆久                    |

|           |                              | (72) 発明者 関 肇裕<br>東京都品川区北品川6丁目7番35号 ソ<br>ニー株式会社内    |

|           |                              | (72) 発明者 中井 將勝<br>東京都品川区北品川6丁目7番35号 ソ<br>ニー株式会社内   |

|           |                              | (72) 発明者 目黒 哲正<br>東京都品川区北品川6丁目7番35号 ソ<br>ニー株式会社内   |

最終頁に続く

(54) 【発明の名称】電子装置

## (57) 【要約】

【課題】制御方式の切り替えに伴うオーバーヘッドを抑制でき、スイッチングレギュレータを広い負荷電流範囲で高効率に維持可能な電子装置を提供する。

【解決手段】アクティブモード時には、スイッチングレギュレータ41がPWM制御でかつ同期整流方式で動作するように指示する整流方式切替信号S45を出力し、スタンバイモード時には、スイッチングレギュレータ41がダイオード整流方式で動作するように指示する整流方式切替信号S45を出力する負荷回路44と、整流方式切替信号S45の指示に応じて同期整流方式で駆動するかダイオード整流方式で駆動するかを判断し、判断した整流方式に従って、制御信号CTL1, CTL2をドライバ回路420, 421に出力して、Pchスイッチングトランジスタ411とNchスイッチングトランジスタ412の駆動制御を行う制御回路419を含むスイッチングレギュレータ41とを設ける。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

動作電流に応じた整流方式切替信号を出力する負荷回路と、

入力電圧から規定の電圧を生成し、上記負荷回路に対して動作電流に対応した電流を供給

するスイッチングレギュレータと、

を有し、

上記スイッチングレギュレータは、第1の整流方式と第2の整流方式で動作可能で、負荷

電流が大きい場合には上記第1の整流方式で動作し、負荷電流が小さい場合には上記第2

の整流方式で動作し、上記第1の整流方式と第2の整流方式を上記負荷回路からの整流方

式切替信号に応じて切り替える

電子装置。

10

**【請求項 2】**

上記負荷回路は、第1の動作電流を消費する第1の動作モードと、上記第1の動作モード

よりも小さい第2の動作電流を消費する第2の動作モードとを有し、

上記負荷回路は、第1の動作モード時には、上記スイッチングレギュレータに対して上記

第1の整流方式を選択することを指示し、上記第2の動作モード時には、上記スイッчи

ングレギュレータに対して上記第2の整流方式を選択することを指示する上記整流方式切替信

号を出力する

請求項1記載の電子装置。

20

**【請求項 3】**

上記第1の整流方式は同期整流方式であり、上記第2の整流方式はダイオード整流方式で

ある

請求項1記載の電子装置。

**【請求項 4】**

上記第1の整流方式は同期整流方式であり、上記第2の整流方式はダイオード整流方式で

ある

請求項2記載の電子装置。

**【請求項 5】**

上記スイッチングレギュレータは、PWM方式とPFM方式の2つの制御方式で動作可能

で、上記第1の整流方式で動作している場合はPWM方式が選択され、上記第2の整流方

式で動作している場合は、負荷電流に応じてPDM方式とPFM方式を自動的に切り替えて

動作を行う

30

請求項4記載の電子装置。

**【請求項 6】**

上記スイッチングレギュレータと上記負荷回路を1つの半導体集積回路上に備えている

請求項5記載の電子装置。

**【請求項 7】**

上記負荷回路は、実行する処理内容に応じて動作周波数を変更する機能を有し、上記負荷

回路が規定の周波数よりも高い周波数で動作する場合は、上記スイッチングレギュレータ

に対して上記第1の整流方式を選択することを指示し、上記負荷回路が規定の周波数より

も低い周波数で動作する場合は、上記スイッチングレギュレータに対して上記第2の整流

方式を選択することを指示する上記整流方式切替信号を出力する

40

請求項1記載の電子装置。

**【請求項 8】**

上記第1の整流方式は同期整流方式であり、上記第2の整流方式はダイオード整流方式で

ある

請求項7記載の電子装置。

**【請求項 9】**

上記スイッチングレギュレータは、PWM方式とPFM方式の2つの制御方式で動作可能

で、上記第1の整流方式で動作している場合はPWM方式が選択され、上記第2の整流方

50

式で動作している場合は、負荷電流に応じて PWM 方式と PFM 方式を自動的に切り替えて動作を行う

請求項 8 記載の電子装置。

【請求項 10】

上記スイッチングレギュレータと上記負荷回路を 1 つの半導体集積回路上に備えている

請求項 9 記載の電子装置。

【請求項 11】

上記負荷回路は、実行する処理内容に応じて動作周波数と電源電圧を変更する機能を有し、

上記負荷回路が規定の周波数 / 電源電圧の組み合わせよりも大きい周波数 / 電源電圧で

動作する場合は、上記スイッチングレギュレータに対して上記第 1 の整流方式を選択する

ことを指示し、上記負荷回路が規定の周波数 / 電源電圧よりも低い周波数 / 電源電圧で動作する場合は、上記スイッチングレギュレータに対して上記第 2 の整流方式を選択することを指示する上記整流方式切替信号を出力する

請求項 1 記載の電子装置。

【請求項 12】

上記第 1 の整流方式は同期整流方式であり、上記第 2 の整流方式はダイオード整流方式である

請求項 11 記載の電子装置。

【請求項 13】

上記スイッチングレギュレータは、PWM 方式と PFM 方式の 2 つの制御方式で動作可能で、

上記第 1 の整流方式で動作している場合は PWM 方式が選択され、上記第 2 の整流方式で動作している場合は、負荷電流に応じて PWM 方式と PFM 方式を自動的に切り替えて動作を行う

請求項 12 記載の電子装置。

【請求項 14】

上記スイッチングレギュレータと上記負荷回路を 1 つの半導体集積回路上に備えている

請求項 13 記載の電子装置。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、入力電圧から規定の電圧を生成し、負荷回路に対してその動作電流に対応した電流を供給するスイッチングレギュレータを有する電子装置に係り、主にバッテリー駆動される携帯用電子装置の電源供給技術に利用して有効な技術に関するものである。

【0002】

【従来の技術】

近年、携帯機器に搭載される LSI は、動作クロック周波数や電源電圧を LSI の処理内容に応じて動的に変化させる技術が採用されてきている。

これは LSI の消費電力  $P_c$  が「 $P_c = C V^2 f$ 」（C は充放電される容量、V は電源電圧、f は動作クロック周波数）で表され、電源電圧 V と周波数 f を低減することにより、その消費電力を大きく低減できるためである。

【0003】

しかしながら、LSI に駆動電力を供給するスイッチングレギュレータから見ると、LSI のクロック周波数や電源電圧が動的に変化するということは、供給すべき負荷電流が大きく変動することを意味する。

一般的なスイッチングレギュレータの制御方式として PWM ( Pulse Width Modulation ) 方式がある。PWM 方式を採用したスイッチングレギュレータは、出力電流が比較的大きい領域では変換効率が高く、出力リップルが小さいという特徴をもっている。

【0004】

しかし、出力電流が小さい領域では、スイッチングトランジスタを駆動する際に発生する

10

20

30

40

50

スイッチング損失が、負荷で消費される電力と比較して大きくなり、変換効率が著しく低下する。

つまり、上述の負荷電流が大きく変動する L S I に駆動電力を供給する際には、L S I 側がクロック周波数や電源電圧の低減で消費電力を削減しても、スイッチングレギュレータの損失が大きくなり、L S I の低消費電力化の効果を相殺してしまう恐れがある。

#### 【 0 0 0 5 】

このような P W M 方式の軽負荷時の変換効率低下を抑制するための技術として、P F M ( Pulse Frequency Modulation ) 制御方式がある。

P F M 方式は、負荷電流に応じてスイッチング周波数を変更する方式であり、負荷電流が小さい領域ではスイッチング周波数が低くなる。したがって軽負荷時のスイッチング損失による変換効率の劣化を抑制することができる。10

#### 【 0 0 0 6 】

一般に、広い負荷電流範囲で高い変換効率を維持するためには、負荷電流が大きい領域では P W M 方式を使用し、負荷電流が小さい領域では P F M 方式に切り替える方式が用いられる。

#### 【 0 0 0 7 】

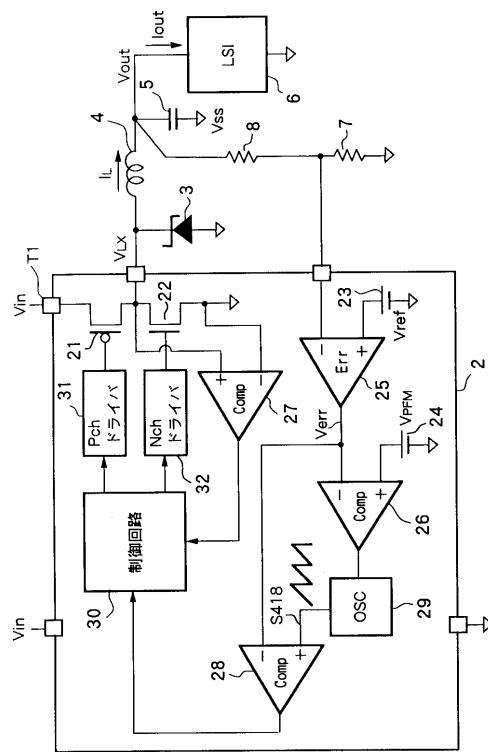

図 1 3 は、P W M / P F M 切り替え方式を採用した同期整流方式の降圧型スイッチングレギュレータを含む電子装置の構成例を示す図である。

#### 【 0 0 0 8 】

この電子装置 1 は、同期整流方式の降圧型スイッチングレギュレータ 2 、整流ダイオード 20 3 、平滑用インダクタ 4 、平滑用キャパシタ 5 、負荷回路 ( L S I ) 6 、および出力電圧をフィードバックするための分割抵抗 7 , 8 を有している。

そして、スイッチングレギュレータ 2 は、p チャネル ( P c h ) スイッチングトランジスタスイッチ 2 1 、n チャネル ( N c h ) スイッチングトランジスタ 2 2 、基準電圧源 2 3 、P F M 制御切替電圧源 2 4 、エラーアンプ 2 5 、コンパレータ 2 6 ~ 2 8 、発振器 2 9 、スイッチングレギュレータ制御回路 3 0 、P c h スイッチングトランジスタ駆動用のドライバ回路 3 1 、および N c h スイッチングトランジスタ駆動用のドライバ回路 3 2 を有し、これらの構成要素が一つのチップ集積化されている。

#### 【 0 0 0 9 】

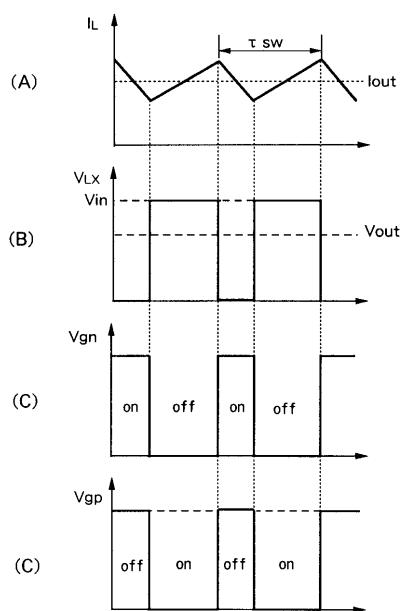

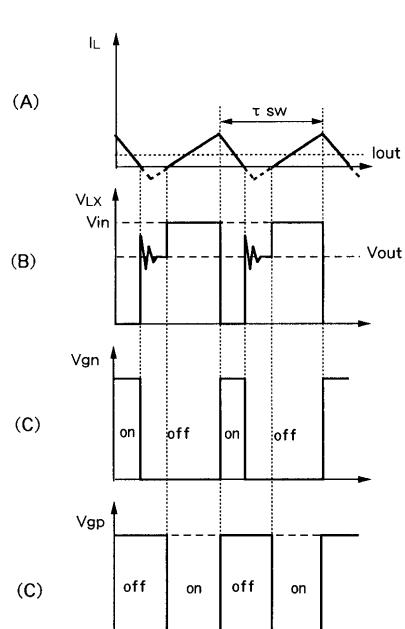

また、図 1 4 ( A ) は重負荷時のインダクタ電流 I L の電流波形、図 1 4 ( B ) はスイッチングトランジスタ出力 V L X の電圧波形、図 1 4 ( C ) は N c h スイッチングトランジスタ 2 2 のゲート駆動電圧波形、および図 1 4 ( D ) は P c h スイッチングトランジスタ 2 1 のゲート駆動電圧波形をそれぞれ示している。さらに、図 1 5 ( A ) は軽負荷時のインダクタ電流 I L の電流波形、図 1 5 ( B ) はスイッチングトランジスタ出力 V L X の電圧波形、図 1 5 ( C ) N c h スイッチングトランジスタ 2 2 のゲート駆動電圧波形、および図 1 5 ( D ) は P c h スイッチングトランジスタ 2 1 のゲート駆動電圧波形をそれぞれ示している。30

#### 【 0 0 1 0 】

このような構成を有する電子装置 1 において、図 1 4 ( A ) ~ ( D ) に示すように、重負荷時にはスイッチングレギュレータ 2 は電流連続モードで動作している。

これに対して、負荷電流が小さくなると、図 1 5 ( A ) , ( C ) に示すように、N c h スイッチングトランジスタ 2 2 のオン期間中にインダクタ 4 に流れるインダクタ電流 I L が負になり、インダクタ電流 I L の逆流が発生する。40

通常この逆流は、インダクタ電流 I L がゼロとなった時点で N c h スイッチングトランジスタ 2 2 をオフにすることにより防いでいる。このようなスイッチングサイクル中にインダクタ電流 I L がゼロとなる動作モードを電流不連続モードと呼ぶが、電流不連続モードでは負荷電流が減少していくと、出力電圧 V o u t が上昇する。

これにより、エラーアンプ 2 5 の出力電圧 ( エラー電圧 V e r r ) が低下し、エラー電圧 V e r r がしきい電圧 V P F M を越えた時点でスイッチングレギュレータ 2 の制御方式が P W M 方式から P F M 方式に変更される。つまり P F M 方式への移行には、電流不連続モ50

ードでの動作が必要となる。

【0011】

電流不連続モード動作を実現するためのゼロ電流検出方法としては、Nchスイッチングトランジスタ22にドレイン-ソース間電圧をモニタする方法や、出力ラインにセンス抵抗を挿入して、その電圧降下をモニタする方法が一般的に行われている。

【0012】

【発明が解決しようとする課題】

しかしながら、Nchスイッチングトランジスタ22のドレイン-ソース間電圧をモニタする方法は、負荷電流が非常に小さい領域では、ドレイン-ソース間電圧も非常に小さくなるために、これを検出するためには高感度のコンパレータ27が必要になる。

また、出力ラインにセンス抵抗を挿入して、その電圧をモニタする方法では、高感度のコンパレータが必要になる点に加え、センス抵抗での損失も発生する。

したがって、いずれの手法を選んでも、回路設計上の困難さや面積の増加、消費電力の増加といったオーバーヘッドが発生する。

【0013】

本発明は、かかる事情に鑑みてなされたものであり、その目的は、制御方式の切り替えに伴うオーバーヘッドを抑制でき、スイッチングレギュレータを広い負荷電流範囲で高効率に維持可能な電子装置を提供することにある。

【0014】

【課題を解決するための手段】

上記目的を達成するため、本発明の電子装置は、動作電流に応じた整流方式切替信号を出力する負荷回路と、入力電圧から規定の電圧を生成し、上記負荷回路に対して動作電流に対応した電流を供給するスイッチングレギュレータと、を有し、上記スイッチングレギュレータは、第1の整流方式と第2の整流方式で動作可能で、負荷電流が大きい場合には上記第1の整流方式で動作し、負荷電流が小さい場合には上記第2の整流方式で動作し、上記第1の整流方式と第2の整流方式を上記負荷回路からの整流方式切替信号に応じて切り替える。

【0015】

好適には、上記負荷回路は、第1の動作電流を消費する第1の動作モードと、上記第1の動作モードよりも小さい第2の動作電流を消費する第2の動作モードとを有し、上記負荷回路は、第1の動作モード時には、上記スイッチングレギュレータに対して上記第1の整流方式を選択することを指示し、上記第2の動作モード時には、上記スイッチングレギュレータに対して上記第2の整流方式を選択することを指示する上記整流方式切替信号を出力する。

【0016】

また、好適には、上記負荷回路は、実行する処理内容に応じて動作周波数を変更する機能を有し、上記負荷回路が規定の周波数よりも高い周波数で動作する場合は、上記スイッチングレギュレータに対して上記第1の整流方式を選択することを指示し、上記負荷回路が規定の周波数よりも低い周波数で動作する場合は、上記スイッチングレギュレータに対して上記第2の整流方式を選択することを指示する上記整流方式切替信号を出力する。

【0017】

また、好適には、上記負荷回路は、実行する処理内容に応じて動作周波数と電源電圧を変更する機能を有し、上記負荷回路が規定の周波数/電源電圧の組み合わせよりも大きい周波数/電源電圧で動作する場合は、上記スイッチングレギュレータに対して上記第1の整流方式を選択することを指示し、上記負荷回路が規定の周波数/電源電圧よりも低い周波数/電源電圧で動作する場合は、上記スイッチングレギュレータに対して上記第2の整流方式を選択することを指示する上記整流方式切替信号を出力する。

【0018】

また、上記第1の整流方式は同期整流方式であり、上記第2の整流方式はダイオード整流方式である。

10

20

30

40

50

## 【0019】

また、上記スイッチングレギュレータは、PWM方式とPFM方式の2つの制御方式で動作可能で、上記第1の整流方式で動作している場合はPWM方式が選択され、上記第2の整流方式で動作している場合は、負荷電流に応じてPWM方式とPFM方式を自動的に切り替えて動作を行う。

## 【0020】

また、上記スイッチングレギュレータと上記負荷回路を1つの半導体集積回路上に備えている。

## 【0021】

本発明によれば、たとえば負荷回路は、第1の動作モード時には、スイッチングレギュレータに対して第1の整流方式を選択することを指示する整流方式切替信号を出力する。10

この場合、スイッチングレギュレータは、第1の整流方式、たとえば同期整流方式で動作し、負荷回路の動作電流に対応した電流を負荷回路に供給する。

一方、第2の動作モード時には、スイッチングレギュレータに対して第2の整流方式を選択することを指示する整流方式切替信号を出力する。

この場合、スイッチングレギュレータは、第2の整流方式、たとえばダイオード整流方式で動作し、負荷回路の動作電流に対応した電流を負荷回路に供給する。

## 【0022】

## 【発明の実施の形態】

以下、本発明の実施形態を図面に関連付けて説明する。20

## 【0023】

第1実施形態

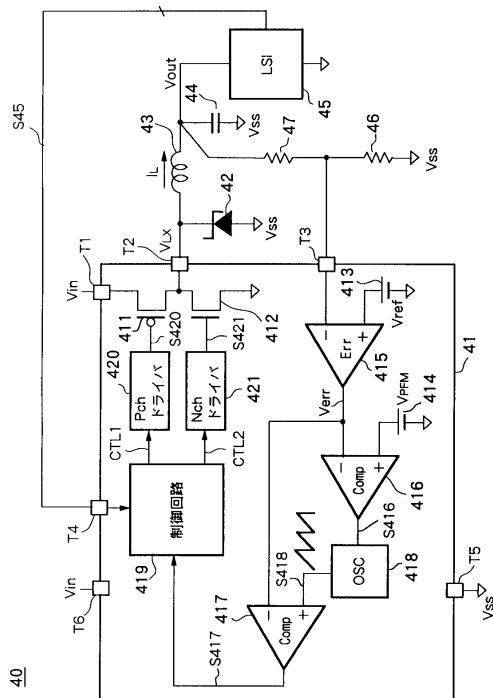

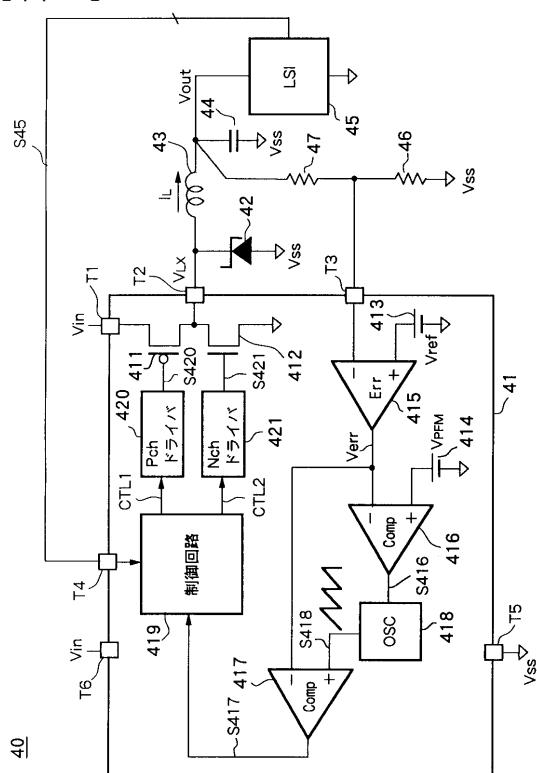

図1は、本発明に係る電子装置の第1の実施形態を示す回路図である。

## 【0024】

本電子装置40は、図1に示すように、スイッチングレギュレータ41、たとえばショットキーダイオードからなる整流ダイオード42、平滑用インダクタ43、平滑用キャパシタ45、負荷回路(LSI)46、および出力電圧をフィードバックするための分割抵抗47,48を有している。

## 【0025】

スイッチングレギュレータ41は、Pch(pチャネル)スイッチングトランジスタスイッチ411、Nch(nチャネル)スイッチングトランジスタ412、基準電圧源413、PFM制御切替電圧源414、エラーアンプ415、コンパレータ416,417、発振器418、スイッチングレギュレータ制御回路419、Pchスイッチングトランジスタ駆動用のドライバ回路420、およびNchスイッチングトランジスタ駆動用のドライバ回路421を有している。30

## 【0026】

スイッチングレギュレータ41は、各構成要素が一つのチップ集積化されており、外部の素子や回路等と接続するための端子T1~T6有する。

端子T1およびT6は図示しない電源、たとえば電源電圧Vin(たとえば3.6V~4.2V)のリチウムイオン電池に接続されている。40

端子T2は、整流ダイオード42のカソードおよび平滑用インダクタ43の一端に接続されている。

端子T3は、直列に接続された分割抵抗47と48の接続点に接続されている。

端子T4は、負荷回路45の整流方式切替信号S45の供給ラインに接続されている。

端子T5は、基準電位(接地電位)Vssに接続されている。

平滑用インダクタ43の他端が平滑用キャパシタ45の第1電極、負荷回路45の電源端子、および抵抗47の一端に接続されている。

そして、平滑用キャパシタ44の第2電極、抵抗46の一端が基準電位Vssに接続されている。

## 【0027】

スイッチングレギュレータ41において、Pchスイッチングトランジスタ411のソースが端子T1に接続され、ドレインが端子T2に接続され、ゲートがドライバ回路420の駆動信号S420の供給ラインに接続されている。

Nchスイッチングトランジスタ412のソースが基準電位Vssに接続され、ドレインが端子T2に接続され、ゲートがドライバ回路421の駆動信号S421の供給ラインに接続されている。

エラーアンプ415の反転入力(-)が端子T3に接続され、非反転入力(+)が基準電圧源413に接続され、出力がコンパレータ416の反転入力(-)およびコンパレータ417の反転入力(-)に接続されている。

コンパレータ416の非反転入力(+)がPFM制御切替電圧源414に接続され、出力が発振器418に供給される。 10

#### 【0028】

スイッチングレギュレータ41は、スタンバイモード時にコンパレータ416において、PFM制御切替電圧源414によるPFM制御切替電圧VPFMによりエラー電圧Veerrが低くなると、PWM方式からPFM方式に自動的に切り替え、PFM制御切替電圧VPFMによりエラー電圧Veerrが高くなると、PFM方式からPWM方式に自動的に切り替える。

#### 【0029】

発振器418はコンパレータ416の出力信号S416に応じて三角波である信号S418を出力する。 20

コンパレータ417の非反転入力(+)が発振器418の発振信号S418の供給ラインに接続されている。コンパレータ417は、発振信号S418とエラーアンプ415によるエラー電圧Veerrとを比較し、比較結果に応じた信号S417を制御回路419に出力する。

#### 【0030】

制御回路419は、端子T4を介して入力される負荷回路45による整流方式切替信号S45の指示に応じて第1の整流方式である同期整流方式で駆動する第2の整流方式であるダイオード整流方式で駆動するかを判断し、判断した整流方式に従って、制御信号CTL1, CTL2をドライバ回路420, 421に出力して、Pchスイッチングトランジスタ411とNchスイッチングトランジスタ412の駆動制御を行う。 30

#### 【0031】

具体的には、制御回路419は、同期整流方式で駆動すると判断した場合には、コンパレータ417の出力信号S417に応じてPchスイッチングトランジスタ411とNchスイッチングトランジスタ412のオンの期間とOFFの期間とのデューティを制御するPWM制御を行うように制御信号CTL1, CTL2をドライバ回路420, 421に出力する。

この場合、スイッチングレギュレータ41は電流連続モードでの動作となる。

#### 【0032】

一方、制御回路419は、ダイオード整流方式で駆動すると判断した場合には、Nchスイッチングトランジスタ412をオフ状態に保持するように、制御信号CTL2をドライバ回路421に出力し、Pchスイッチングトランジスタ411と外付けの整流ダイオード42により動作するように制御信号CTL1をドライバ回路420に出力する。 40

#### 【0033】

負荷回路45は、スイッチングレギュレータ41から出力された電圧VLXがインダクタ43、およびキャパシタ45により平滑化された、たとえば1.5V~3.3V程度の駆動電圧Voutが電源端子に供給される。

本第1の実施形態に係る負荷回路(LSI)46は、動作状態である第1の動作モードとしてのアクティブモードと、非動作状態である第2の動作モードとしてのスタンバイ(Standby)モードの2つの動作モードを有する。

#### 【0034】

10

20

30

40

50

アクティブモードにおいては、L S I が消費する電流が大きいため、スイッチングレギュレータ4 1 をP W M 制御でかつ同期整流方式で動作させる必要がある。負荷回路4 1 は、アクティブモード時には、スイッチングレギュレータ4 1 がP W M 制御でかつ同期整流方式で動作するように指示する整流方式切替信号S 4 5 をスイッチングレギュレータ4 1 の制御回路4 1 9 に出力する。

一方、負荷回路4 5 は、スタンバイモードにおいては、スイッチングレギュレータ4 1 がダイオード整流方式で動作するように指示する整流方式切替信号S 4 5 をスイッチングレギュレータ4 1 の制御回路4 1 9 に出力する。

#### 【0 0 3 5】

なお、負荷回路4 5 が出力する整流方式切替信号S 4 5 は、1 ビットのデータでも良いし、複数ビットのデータでも良い。複数ビットのデータの場合は、パラレルデータとしてスイッチングレギュレータ4 1 に送信しても良いし、信号線数を減らすためにシリアルデータに変換して送信しても良い。

#### 【0 0 3 6】

次に、上記構成による動作を図2 (A) ~ (D) および図3 (A) ~ (D) に関連付けて説明する。

#### 【0 0 3 7】

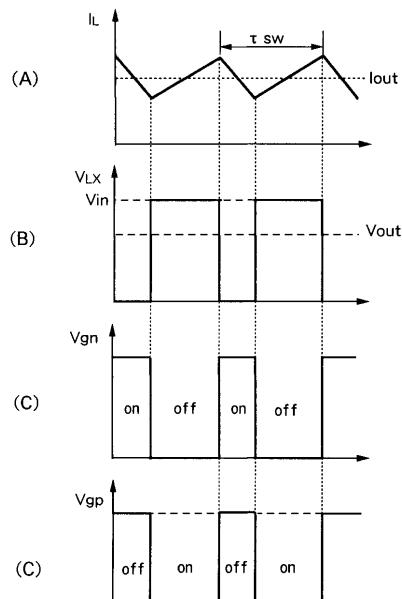

図2 (A) ~ (D) は、アクティブモード時の動作電流および動作電圧波形を示す図であって、図2 (A) はインダクタ電流I L の電流波形、図2 (B) はスイッチングトランジスタ出力V L X の電圧波形、図2 (C) はN c h スイッチングトランジスタ4 1 2 のゲート駆動電圧波形、および図2 (D) はP c h スイッチングトランジスタ4 1 1 のゲート駆動電圧波形をそれぞれ示している。

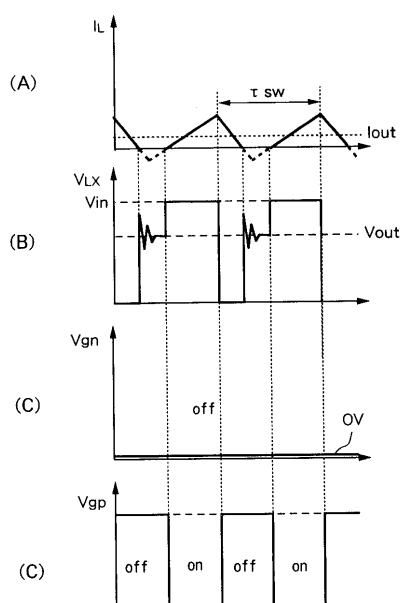

また、図3 (A) ~ (D) はスタンバイモード時の動作電流および動作電圧波形を示す図であって、図3 (A) はインダクタ電流I L の電流波形、図3 (B) はスイッチングトランジスタ出力V L X の電圧波形、図3 (C) N c h スイッチングトランジスタ4 1 2 のゲート駆動電圧波形、および図3 (D) はP c h スイッチングトランジスタ4 1 1 のゲート駆動電圧波形をそれぞれ示している。

#### 【0 0 3 8】

アクティブモードには、負荷回路4 5 は消費する電流が大きいため、スイッチングレギュレータ4 1 がP W M 制御でかつ同期整流方式で動作するように指示する整流方式切替信号S 4 5 が、負荷回路4 5 からスイッチングレギュレータ4 1 の制御回路4 1 9 に出力される。

#### 【0 0 3 9】

制御回路4 1 9 においては、端子T 4 を介して入力される負荷回路4 5 による整流方式切替信号S 4 5 の指示に応じて同期整流方式で駆動すべき旨が判断される。そして、コンパレータ4 1 7 の出力信号S 4 1 7 に応じてP c h スイッチングトランジスタ4 1 1 とN c h スイッチングトランジスタ4 1 2 のオンの期間とO F F の期間とのデューティを制御するP W M 制御を行うように制御信号C T L 1 , C T L 2 が制御回路4 1 9 からドライバ回路4 2 0 , 4 2 1 に出力される。

この場合、スイッチングレギュレータ4 1 は電流連続モードで動作する。

#### 【0 0 4 0】

たとえばインダクタ4 3 に流れるインダクタ電流I L がL S I 4 5 の動作状態の変化により増加すると、インダクタ4 3 およびキャパシタ4 4 により平滑化された電圧V o u t が減少する。

この電圧V o u t は分割抵抗4 6 , 4 7 により分圧されてスイッチングレギュレータ4 1 の端子T 3 を介してエラーアンプ4 1 5 に入力される。

エラーアンプ4 1 5 では、基準電圧より入力電圧が下がることから、出力エラー電圧V e r r は高くなり、コンパレータ4 1 6 および4 1 7 に供給される。

コンパレータ4 1 6 からはP F M 制御切り替え電圧V P F M と入力エラー電圧V e r r の比較結果に応じた信号S 4 1 6 が発振器4 1 8 に出力される。

10

20

30

40

50

発振器 418において、コンパレータ416の出力信号S416に応じて三角波である信号S418がコンパレータ417に出力される。

そして、コンパレータ417では、発振信号S418とエラーアンプ415によるエラー電圧Verrとが比較され、比較結果に応じたPWM信号S417が制御回路419に出力される。

このとき、制御回路419においては、PWM信号S417に基づいて、出力電圧を上げるよう、Pchスイッチングトランジスタ411のオン時間とNchスイッチングトランジスタ412のオン時間の比率を変更するように制御信号CTL1, CTL2が制御回路419からドライバ回路420, 421に出力される。

この制御状態は、スイッチングレギュレータ41のエラーアンプ415に供給される電圧Voutが分圧された電圧が基準電圧と等しくなるまで継続される。 10

#### 【0041】

これによりPchスイッチングトランジスタ411を通して端子T2には電荷が供給されることから、出力電圧VLX、ひいては電圧Voutが上昇する。

次に、たとえばインダクタ43に流れるインダクタ電流ILがLSI45の動作状態の変化により減少すると、インダクタ43およびキャパシタ44により平滑化された電圧Voutが増加する。すると、スイッチングレギュレータ41のエラーアンプ415に供給される電圧Voutが分圧された電圧が基準電圧Vrefより高くなる。

エラーアンプ415では、基準電圧より入力電圧が上がることから、出力エラー電圧Verは低くなり、コンパレータ416および417に供給される。 20

コンパレータ416からはPFM制御切り替え電圧VPFMと入力エラー電圧Verrの比較結果に応じた信号S416が発振器418に出力される。

発振器418において、コンパレータ416の出力信号S416に応じて三角波である信号S418がコンパレータ417に出力される。

そして、コンパレータ417では、発振信号S418とエラーアンプ415によるエラー電圧Verrとが比較され、比較結果に応じたPWM信号S417が制御回路419に出力される。

このとき、制御回路419においては、PWM信号S417に基づいて、出力電圧を下げるよう、Pchスイッチングトランジスタ411のオン時間とNchスイッチングトランジスタ412のオン時間の比率を変更するように制御信号CTL1, CTL2が制御回路419からドライバ回路420, 421に出力される。 30

この制御状態は、スイッチングレギュレータ41のエラーアンプ415に供給される電圧Voutが分圧された電圧が基準電圧と等しくなるまで継続される。

これによりPchスイッチングトランジスタ411を通して端子T2には電荷が供給されることから、出力電圧VLX、ひいては電圧Voutが下降する。

#### 【0042】

ここで、負荷回路45がアクティブモードからスタンバイモードに切り替わると、スイッチングレギュレータ41がダイオード整流方式で動作するように指示する整流方式切替信号S45が、負荷回路45からスイッチングレギュレータ41の制御回路419に出力される。 40

#### 【0043】

制御回路419においては、端子T4を介して入力される負荷回路45による整流方式切替信号S45の指示に応じて同期整流方式で駆動すべき旨が判断される。そして、Nchスイッチングトランジスタ412をオフ状態に保持するように、制御回路419から制御信号CTL2がドライバ回路421に出力され、Pchスイッチングトランジスタ411と外付けの整流ダイオード42により動作するように制御信号CTL1がドライバ回路420に出力される。

これにより、負荷回路45がスタンバイモードにある間は、図3(C)に示すように、Nchスイッチングトランジスタ412はオフ状態に保持される。

この状態ではスイッチングレギュレータ41は、図3(A), (B), (D)に示すよう 50

に、Pchスイッチングトランジスタ411とショットキーダイオード42によるダイオード整流で動作する。

#### 【0044】

スイッチングレギュレータ41においては、ダイオード整流時には負荷電流が低下するにしたがって出力電圧Voutが上昇し、その結果エラー電圧VERRが低下する。コンパレータ416において、PFM制御切替電圧源414によるPFM制御切替電圧VPFMによりエラー電圧VERRが低くなると、PWM方式からPFM方式に自動的に切り替えられる。PFM方式で動作中は、発振器418の発振周波数が信号S416にしたがって低下し、Pchスイッチングトランジスタ411の駆動回数が低減される。発振器418の発振周波数は、スイッチングレギュレータ41のエラーアンプ415に供給される電圧Voutが分圧された電圧が基準電圧と等しくなるまで低減される。10

一方、PFM制御切替電圧VPFMによりエラー電圧VERRが高くなると、PFM方式からPWM方式に自動的に切り替えられる。

#### 【0045】

ダイオード整流の場合、ダイオードの順方向電圧降下による損失が発生するため、負荷電流が大きい領域では効率が低下するが、スタンバイ状態にある負荷回路(LSI)45の消費電流は非常に小さいため、ダイオード順方向電圧降下による損失は無視できる範囲となる。

#### 【0046】

以上説明したように、本第1の実施形態によれば、動作状態であるアクティブモードと、非動作状態であるスタンバイモードの2つの動作モードを有し、アクティブモード時には、スイッチングレギュレータ41がPWM制御でかつ同期整流方式で動作するように指示する整流方式切替信号S45を出力し、スタンバイモード時には、スイッチングレギュレータ41がダイオード整流方式で動作するように指示する整流方式切替信号S45を出力する負荷回路44と、負荷回路45による整流方式切替信号S45の指示に応じて同期整流方式で駆動するかダイオード整流方式で駆動するかを判断し、判断した整流方式に従つて、制御信号CTL1, CTL2をドライバ回路420, 421に出力して、Pchスイッチングトランジスタ411とNchスイッチングトランジスタ412の駆動制御を行う制御回路419を含むスイッチングレギュレータ41とを設けたので、以下の効果を得ることができる。20

つまり、従来方式の同期整流で電流不連続モード動作となった場合に必要であったゼロ電流検出が不要となり、高精度のゼロ電流検出コンパレータが不要とできる。

これにより、スイッチングレギュレータ設計の難易度を緩和できる。

また、スイッチングレギュレータの自己消費電力を低減することもできる。軽負荷時の自己消費電力低減は、変換効率向上に大きく貢献する。

#### 【0047】

#### 第2実施形態

図4は、本発明に係る電子装置の第2の実施形態を示す回路図である。

#### 【0048】

本第2の実施形態が上述した第1の実施形態と異なる点は、負荷回路(LSI)45Aが処理内容に応じて動作周波数を変更する機能を有することにある。40

#### 【0049】

LSIの消費電力Pcは、前述した通り『 $P_c = C V_2 f$ 』で表されるため、周波数に比例してLSIの消費電力を低減できる。つまり負荷電流は動作周波数に比例して減少する。

#### 【0050】

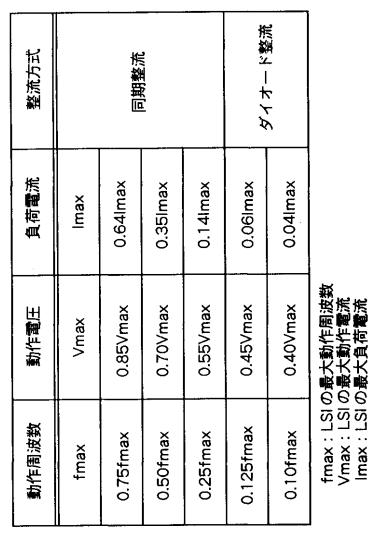

図5は、6段階の周波数設定が可能な場合の動作周波数と負荷電流の関係を示す図である。また、図6は、負荷電流の変化に対するインダクタ電流ILXの波形を示す図である。

#### 【0051】

本第2の実施形態では、最大動作周波数fmax時の負荷電流をImaxとし、インダク50

タ電流のリップル電流を  $0.4 \text{ I}_{\text{max}}$  と仮定している。つまり負荷電流が  $0.2 \text{ I}_{\text{max}}$  以下の場合に、スイッチングレギュレータは電流不連続モードで動作させる必要がある。

図 5 の対応表によれば、LSIの動作周波数が  $0.125 \text{ f}_{\text{max}}$  以下になった場合がこれに対応する。

よって LSI の動作周波数が  $0.125 \text{ f}_{\text{max}}$  以下になった場合に、スイッチングレギュレータ 41 に対して同期整流からダイオード整流に切り替える指示を出せば良いことになる。

実際にはバッテリー電圧である入力電圧  $V_{in}$  が変化するために、それに応じてリップル電流も変化する。よって、同期整流からダイオード整流に切り替えるポイントは、これらの条件も考慮して決定する必要がある。

10

#### 【0052】

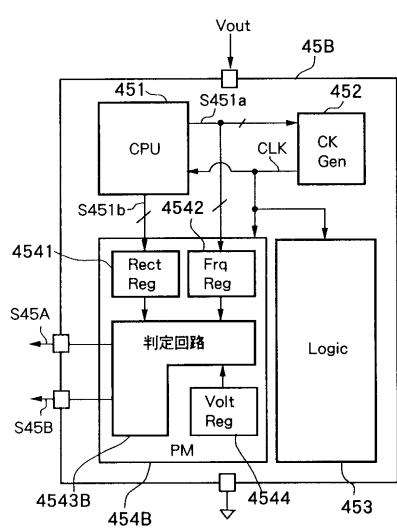

図 7 は、本第 2 の実施形態に係る負荷回路 (LSI) の具体的な構成例を示す図である。この負荷回路 45A は、周波数制御機構とスイッチングレギュレータの整流方式切り替え機構を備えている。

負荷回路 45A は、図 7 に示すように、CPU451、クロック発生ブロック 452、ロジックブロック 453、およびパワーマネージメント (PM) ブロック 454 を有する。そして、パワーマネージメントブロック 454 は、整流切替レジスタ (Rect Reg) 4541、周波数レジスタ (Freq Reg) 4542、および判定回路 4543 を有している。

20

#### 【0053】

このような構成を有する負荷回路 45Aにおいて、クロック発生ブロック 452 は CPU451 の指示により図 5 に示す 6 段階の周波数を切り替える機能を持つ。

CPU451 は処理内容に応じて、最適なクロック周波数をクロック周波数設定信号 S451a によりクロック発生回路 452 に指示する。

クロック発生ブロック 452 において、クロック周波数設定信号 S451a に従ってクロック信号 CLK が発生され、CPU451、ロジックブロック 453、およびパワーマネージメントブロック 454 に供給される。

CPU451 によるクロック周波数設定信号 S451a はパワーマネージメントブロック 454 にも供給される。

30

パワーマネージメント (PM) ブロック 454 においては、CPU451 から供給されたクロック周波数設定信号 S451a により指示された周波数が周波数レジスタ 4542 に設定される。

そして、周波数レジスタ 4542 に設定された値 F2 と CPU451 から供給された設定信号 S451b に応じた整流切替レジスタ 4541 の内容 F1 が判定回路 4543 で比較される。

ここで整流切替レジスタ 4541 の設定値 F1 は、スイッチングレギュレータ 41 の動作条件を基にあらかじめ決定されており、LSI のブート時にレジスタに設定する。本第 2 の実施形態に場合は  $0.2 \text{ f}_{\text{max}}$  となる。

#### 【0054】

判定回路 4543 は、周波数レジスタ 4542 の値 F2 と整流切替レジスタ 4541 の設定値 F1 を比較し、「 $F2 < F1$ 」の場合に、整流方式切替信号 S45A を活性化してスイッチングレギュレータ 41 に整流方式切り替えの指示を送る。

40

ここで整流方式切替信号 S45A は、1 ビットのデータでも良いし、複数ビットのデータでも良い。複数ビットのデータの場合は、パラレルデータとしてスイッチングレギュレータに送信しても良いし、信号線を減らすためにシリアルデータに変換して送信しても良い。

。

#### 【0055】

本第 2 の実施形態においては、スイッチングレギュレータ 41 は、整流方式切替信号 S45A が活性化している間はダイオード整流で動作する。

50

以降のスイッチングレギュレータの動作に関しては、上述した第1の実施形態と同じなので説明を省略する。

**【0056】**

本第2の実施形態によれば、上述した第1の実施形態の効果と同様の効果を得ることができる。

**【0057】**

**第3実施形態**

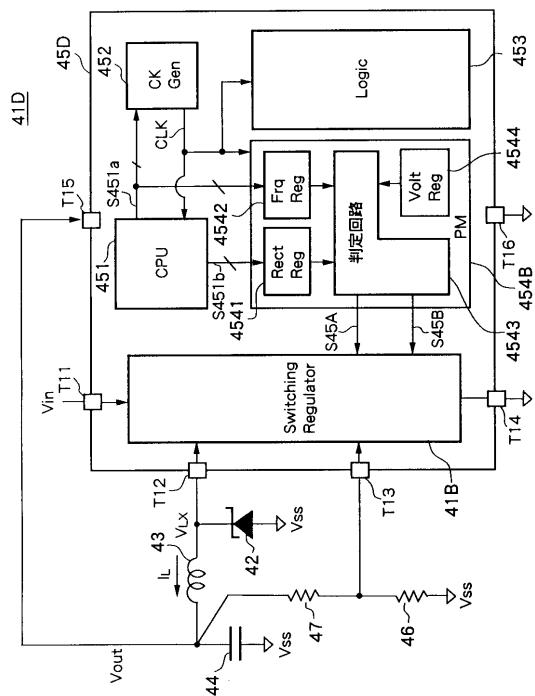

図8は、本発明に係る電子装置の第3の実施形態を示す回路図である。

**【0058】**

本第3の実施形態が上述した第2の実施形態と異なる点は、負荷回路(LSI)45Bが

10

処理内容に応じて動作周波数を変更する機能に加えて、電源電圧を変更する機能を備えていることにある。

**【0059】**

処理内容に応じて動作周波数を変更することでそのLSIが動作可能な電源電圧が変化する。したがって、動作周波数に見合った電源電圧を供給することによって、周波数のみを変更した場合に比較して、LSIの消費電力を大幅に低減できる。

**【0060】**

図8におけるスイッチングレギュレータ41Bは、基準電圧源の代わりのディジタル／アナログコンバータ(DAC)422を有している。

DAC422の入力が端子T7に接続され、端子T7が負荷回路(LSI)45Bの電源電圧設定信号S45Bの供給ラインに接続され、DAC422のアナログ出力がエラーアンプ415の非反転入力(+)に供給される。

20

**【0061】**

図9は、6段階の周波数／電源電圧の組み合わせ設定が可能な場合の動作周波数と負荷電流の関係を示す図である。

本第3の実施形態では、最大動作周波数 $f_{max}$ 時にLSIが動作可能な電源電圧を $V_{max}$ とし、また各動作周波数に対してLSIが動作可能な電源電圧値が規定されている。また最大負荷電流を $I_{max}$ 、最大リップル電流を $0.4I_{max}$ と仮定している。

**【0062】**

図9の対応表によれば、LSIの動作周波数が $0.25f_{max}$ 以下になった場合に、スイッチングレギュレータに対して同期整流からダイオード整流に切り替える指示を出せば良いことになる。

30

実際には本第3の実施形態の場合、入力電圧 $V_{in}$ と出力電圧 $V_{out}$ が共に変化するため、それに応じてリップル電流も変化し、同期整流からダイオード整流に切り替えるポイントも変化する。よって、同期整流からダイオード整流に切り替えるポイントは、これらの条件も考慮して決定する必要がある。

**【0063】**

図10は、本第3の実施形態に係る負荷回路(LSI)の具体的な構成例を示す図である。

。

この負荷回路45Bは、周波数／電源電圧制御機構とスイッチングレギュレータの整流方式切り替え機構を備えている。

40

図10の負荷回路45Bが図7の負荷回路45Aと異なる点は、パワーマネージメントブロック454Bにおいて、整流切替レジスタ(Recr Reg)4541、周波数レジスタ(Freq Reg)4542、および判定回路4543Bに加えて、電源電圧設定レジスタ(Volt Reg)4544を備えている点にある。

**【0064】**

このような構成を有する負荷回路45Bにおいて、クロック発生ブロック452はCPU451の指示により図5に示す6段階の周波数を切り替える機能を持つ。

CPU451は処理内容に応じて、最適なクロック周波数をクロック周波数設定信号S451aによりクロック発生回路452に指示する。

50

クロック発生ブロック 452において、クロック周波数設定信号 S451a に従ってクロック信号 CLK が発生され、CPU451、ロジックブロック 453、およびパワーマネージメントブロック 454B に供給される。

CPU451によるクロック周波数設定信号 S451a はパワーマネージメントブロック 454B にも供給される。

パワーマネージメント(PM)ブロック 454Bにおいては、CPU451から供給されたクロック周波数設定信号 S451a により指示された周波数が周波数レジスタ 4542 に設定される。

パワーマネージメントブロック 454Bにおいては、そのクロック周波数に対応した電源電圧が電源電圧設定レジスタ(Volt Reg)4544より判定回路 4543B に読み出され、電源電圧設定信号 S45B によりスイッチングレギュレータ 41B に対して供給すべき電源電圧が指示される。10

これと並行して、パワーマネージメントブロック 454Bにおいては、周波数レジスタ 4542 に設定された値 F2 と CPU451 から供給された設定信号 S451b に応じた整流切替レジスタ 4541 の内容 F1 が判定回路 4543B で比較される。

ここで整流切替レジスタ 4541 の設定値 F1 は、スイッチングレギュレータ 41 の動作条件を基にあらかじめ決定されており、LSIのブート時にレジスタに設定する。本第2の実施形態に場合は 0.2 fmax となる。

#### 【0065】

なお、ここでは整流切替レジスタ(Rect Reg)4541 と比較する対象として周波数レジスタ(Freq Reg)4542 を選択しているが、これに限定されるわけではなく、電圧設定レジスタ(Volt Reg)4544 でも良いし、周波数レジスタ(Freq Reg)4542 と電圧設定レジスタ(Volt Reg)4544 の両方でも良い。20

以降の動作は第1および第2の実施形態と同じなので、説明を省略する。

#### 【0066】

本第3の実施形態によれば、上述した第1および第2の実施形態の効果と同様の効果を得ることができる。

#### 【0067】

### 第4実施形態

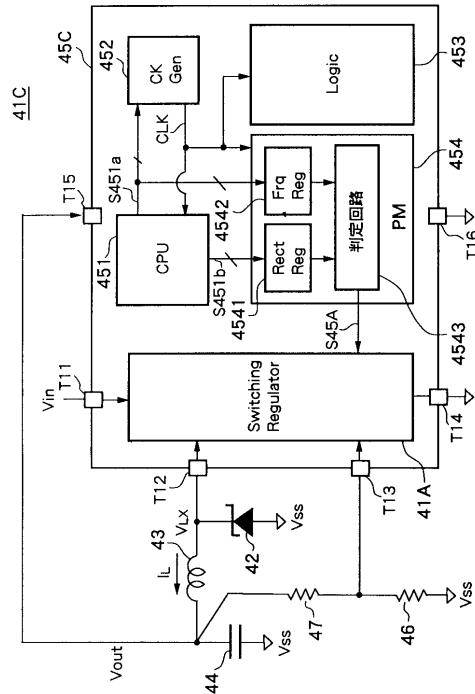

図11は、本発明に係る電子装置の第4の実施形態を示す回路図である。30

#### 【0068】

本第4の実施形態は、上述した第2の実施形態におけるスイッチングレギュレータ 41A を LSI(負荷回路)45C にオンチップ化した場合の形態である。本第4の実施形態によれば、スイッチングレギュレータ 41A を LSI 45C と混載することで、スイッチングレギュレータ 41A に係る実装面積を削減することができ、低コスト化が可能となる。

#### 【0069】

また、近年の LSI では、内部回路用電源電圧と入出力回路用電源電圧が異なる場合が多い。このような場合に、入力電圧 Vin として LSI の入出力回路用電源電圧を使用し、スイッチングレギュレータの出力電圧 Vout を内部回路用電源電圧として供給することで、単一電源の LSI として提供することができる。これによりシステム設計者の設計負担を軽減することができる。40

#### 【0070】

### 第5実施形態

図12は、本発明に係る電子装置の第5の実施形態を示す回路図である。

#### 【0071】

本第4の実施形態は、上述した第3の実施形態におけるスイッチングレギュレータ 41B を LSI(負荷回路)45D にオンチップ化した場合の形態である。本第4の実施形態によれば、スイッチングレギュレータ 41B を LSI 45D と混載することで、スイッチングレギュレータ 41B に係る実装面積を削減することができ、低コスト化が可能となる。50

**【0072】**

このように、本第5の実施形態によれば、上述した第4の実施形態の効果と同様の効果を得ることができる。

**【0073】****【発明の効果】**

本発明によれば、同期整流型スイッチングレギュレータの逆電流防止用検出回路を削除することができるため、スイッチングレギュレータ設計の難易度を緩和できる。

さらに、高感度なゼロ電流検出コンパレータが不要なるため、その消費電力を削減でき、スイッチングレギュレータの自己消費電力を低減できる。これにより軽負荷時の変換効率改善が期待できる。

10

**【0074】**

また、本発明によれば、スイッチングレギュレータを負荷となる負荷回路にオンチップ化することで、実装面積の低減による低コスト化が期待できる。

さらに、負荷回路とスイッチングレギュレータ間の通信に伴う消費電力を低減できる。

**【図面の簡単な説明】**

**【図1】**本発明に係る電子装置の第1の実施形態を示す回路図である。

**【図2】**(A)～(D)は、アクティブモード時の動作電流および動作電圧波形を示す図であって、(A)はインダクタ電流ILの電流波形、(B)はスイッチングトランジスタ出力VLXの電圧波形、(C)はNchスイッチングトランジスタのゲート駆動電圧波形、および(D)はPchスイッチングトランジスタのゲート駆動電圧波形をそれぞれ示す図である。

20

**【図3】**(A)～(D)はスタンバイモード時の動作電流および動作電圧波形を示す図であって、(A)はインダクタ電流ILの電流波形、(B)はスイッチングトランジスタ出力VLXの電圧波形、(C)Nchスイッチングトランジスタのゲート駆動電圧波形、および(D)はPchスイッチングトランジスタのゲート駆動電圧波形をそれぞれ示す図である。

**【図4】**本発明に係る電子装置の第2の実施形態を示す回路図である。

**【図5】**第2の実施形態におけるLSIの動作周波数と負荷電流およびそれに対応したスイッチングレギュレータの整流方式を示す図である。

30

**【図6】**第2の実施形態における負荷電流変動時のインダクタ電流波形を示す図である。

**【図7】**第2の実施形態に係る負荷回路(LSI)の具体的な構成例を示す図である。

**【図8】**本発明に係る電子装置の第3の実施形態を示す要部ブロック図である。

**【図9】**第3の実施形態におけるLSIの動作周波数と電源電圧、負荷電流およびそれに対応したスイッチングレギュレータの整流方式を示す図である。

**【図10】**第3の実施形態に係る負荷回路(LSI)の具体的な構成例を示す図である。

40

**【図11】**本発明に係る電子装置の第4の実施形態を示す要部ブロック図である。

**【図12】**本発明に係る電子装置の第5の実施形態を示す要部ブロック図である。

**【図13】**PWM/PFM制御切り替え機構を備えたスイッチングレギュレータの構成を示すブロック図である。

**【図14】**一般的なスイッチングレギュレータの重負荷時の動作電流および動作電圧波形を示す図であって、(A)はインダクタ電流ILの電流波形、(B)はスイッチングトランジスタ出力VLXの電圧波形、(C)はNchスイッチングトランジスタのゲート駆動電圧波形、および(D)はPchスイッチングトランジスタのゲート駆動電圧波形をそれぞれ示す図である。

**【図15】**一般的なスイッチングレギュレータの軽負荷時の動作電流および動作電圧波形を示す図であって、(A)はインダクタ電流ILの電流波形、(B)はスイッチングトランジスタ出力VLXの電圧波形、(C)Nchスイッチングトランジスタのゲート駆動電圧波形、および(D)はPchスイッチングトランジスタのゲート駆動電圧波形をそれぞれ示す図である。

**【符号の説明】**

50

40, 40A ~ 40D ... 電子装置、41, 41A, 41B ... スイッチングレギュレータ

41, 42 ... 整流ダイオード、43 ... 平滑用インダクタ、44 ... 平滑用キャパシタ、45 ...

負荷回路 (LSI)、46, 47 ... 分割抵抗 47, 48、411Pch (pチャネル) スイッチングトランジスタスイッチ、412 ... Nch (nチャネル) スイッチングトランジスタ、413 ... 基準電圧源、414 ... PFM制御切り替え電圧源、415 ... エラーアンプ、416, 417 ... コンパレータ 418 ... 発振器、419 ... スイッチング回路

制御回路、420 ... Pch スイッチングトランジスタ駆動用のドライバ回路、421 ... Nch

スイッチングトランジスタ駆動用のドライバ回路、422 ... ディジタル / アナログコンバータ (DAC)、451 ... CPU、452 ... クロック発生ブロック、453 ... ロジックブロック、454, 454B ... パワーマネージメント (PM) ブロック、4541 ... 整流切替レジスタ (Rect Reg)、4542 ... 周波数レジスタ (Freq Reg)、4543, 4543B ... 判定回路、4544 ... 電源電圧設定レジスタ (Volt Reg)。

。

10

【図1】

【図2】

【図3】

【 図 4 】

【図5】

| 動作周波数     | 負荷電流      | 整流方式    |

|-----------|-----------|---------|

| fmax      | lmax      | 同期整流    |

| 0.75fmax  | 0.75lmax  |         |

| 0.50fmax  | 0.50lmax  |         |

| 0.25fmax  | 0.25lmax  |         |

| 0.125fmax | 0.125lmax | ダイオード整流 |

| 0.10fmax  | 0.10lmax  |         |

fmax : LSI の最大動作周波数

Imax : LSI の最大負荷電流

【図6】

【 図 7 】

【図 8】

【図 9】

【図 10】

【図 11】

【図 1 2】

【図 1 3】

【図 1 4】

【図 1 5】

フロントページの続き

F ターム(参考) 5H730 AA14 AA15 AS01 AS05 BB03 BB13 DD04 EE07 FD03 FF02

FF05 FG05 FG07 FG22 ZZ01