(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5622355号

(P5622355)

(45) 発行日 平成26年11月12日(2014.11.12)

(24) 登録日 平成26年10月3日(2014.10.3)

(51) Int.Cl.

F 1

H01L 29/786 (2006.01)

H01L 29/78 612 D

H01L 21/336 (2006.01)

G02F 1/1368 (2006.01)

H01L 29/78 621

G02F 1/1368 (2006.01)

H01L 29/78 627 C

請求項の数 3 (全 25 頁)

(21) 出願番号

特願2008-269012 (P2008-269012)

(22) 出願日

平成20年10月17日 (2008.10.17)

(65) 公開番号

特開2009-124121 (P2009-124121A)

(43) 公開日

平成21年6月4日 (2009.6.4)

審査請求日

平成23年10月13日 (2011.10.13)

(31) 優先権主張番号

特願2007-275612 (P2007-275612)

(32) 優先日

平成19年10月23日 (2007.10.23)

(33) 優先権主張国

日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 細谷 邦雄

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 藤川 最史

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 綿引 隆

最終頁に続く

(54) 【発明の名称】 半導体装置およびその作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上に、第1の導電層、前記第1の導電層上の第1の絶縁層、前記第1の絶縁層上の第1の半導体層、及び前記第1の半導体層上の一導電型の不純物元素を含有する第2の半導体層を有する積層を形成し、

第1のレジストパターンをマスクとして、前記積層をエッチングして、第2の導電層、前記第2の導電層上の第2の絶縁層、前記第2の絶縁層上の第3の半導体層、及び前記第3の半導体層上の一導電型の不純物元素を含有する第4の半導体層を、それぞれ有する第1及び第2の島状の積層を形成し、

前記第1の島状の積層の側面に接する第1のサイドウォールと、前記第2の島状の積層の側面に接する第2のサイドウォールと、を形成し、

前記第1及び前記第2の島状の積層、前記第1及び前記第2のサイドウォール、並びに前記基板を覆うように、第3の導電層を形成し、

前記第3の導電層は、第1の透明導電層及び前記第1の透明導電層上の第1の金属層の積層であり、

第1の膜厚と前記第1の膜厚より厚い第2の膜厚とを有する第2のレジストパターンをマスクとして、前記第3の導電層をエッチングすることにより、前記第1の島状の積層及び前記第1のサイドウォールに接する第4の導電層と、前記第2の島状の積層及び前記第2のサイドウォールに接する第5の導電層とを形成し、

前記第4の導電層は、第2の透明導電層と前記第2の透明導電層上の第2の金属層の積

10

20

層であり、

前記第5の導電層は、第3の透明導電層と前記第3の透明導電層上の第3の金属層の積層であり、

前記第2の金属層の上面の面積は、前記第2の透明導電層の上面の面積より小さく、

前記第2の金属層は、前記第1の島状の積層の前記第4の半導体層と、前記第1のサイドウォールとに重なり、

前記第3の金属層の上面の面積は、前記第3の透明導電層の上面の面積より小さく、

前記第3の金属層は、前記第2の島状の積層の前記第4の半導体層のみと重なり、

前記第3の透明導電層は、前記第2の島状の積層の前記第4の半導体層上面及び前記第2のサイドウォールと接し、

前記第1の島状の積層及び前記第4の導電層は、トランジスタとして機能し、

前記第2の島状の積層及び前記第5の導電層は、容量素子として機能し、

前記第2の透明導電層のうち、前記第2の金属層と重ならず且つ前記基板上面に接する部分は、画素電極として機能することを特徴とする半導体装置の作製方法。

#### 【請求項2】

請求項1において、

前記第4の導電層及び前記第5の導電層を形成後、前記第1及び前記第2の島状の積層、前記第1及び前記第2のサイドウォール、前記第4及び前記第5の導電層、並びに前記基板を覆うように、第3の絶縁層を形成し、

前記第3の絶縁層上に第3のレジストパターンを形成し、

前記第3のレジストパターンにリフロー処理を行い、テーパー側面を有する第4のレジストパターンを形成し、

前記第4のレジストパターンをマスクとして、前記第3の絶縁層をパターニングすることを特徴とする半導体装置の作製方法。

#### 【請求項3】

基板上に、トランジスタと、容量素子と、前記トランジスタと電気的に接続する画素電極とを有し、

前記トランジスタは、

第1の導電層、前記第1の導電層上の第1の絶縁層、前記第1の絶縁層上の第1の半導体層、及び前記第1の半導体層上の一導電型の不純物元素を含有する第2の半導体層を有する第1の島状の積層と、

前記第1の島状の積層の側面に接する第1のサイドウォールと、

前記第2の半導体層上面及び前記第1のサイドウォール側面に接する第2の導電層とを有し、

前記第2の導電層は、第1の透明導電層及び前記第1の透明導電層上の第1の金属層の積層であり、

前記第1の金属層の上面の面積は、前記第1の透明導電層の上面の面積より小さく、

前記第1の金属層は、前記第1の透明導電層を介して前記第2の半導体層と重なり、かつ前記第1の透明導電層を介して前記第1のサイドウォール側面を覆い、

前記容量素子は、

第3の導電層、前記第3の導電層上の第2の絶縁層、前記第2の絶縁層上の第3の半導体層、及び前記第3の半導体層上の一導電型の不純物元素を含有する第4の半導体層を有する第2の島状の積層と、

前記第2の島状の積層の側面に接する第2のサイドウォールと、

前記第4の半導体層上面及び前記第2のサイドウォール側面に接する第4の導電層とを有し、

前記第4の導電層は、第2の透明導電層及び前記第2の透明導電層上の第2の金属層の積層であり、

前記第2の金属層の上面の面積は、前記第2の透明導電層の上面の面積より小さく、

前記第2の金属層は、前記第2の透明導電層を介して前記第2の半導体層のみと重なり

10

20

30

40

50

、前記第2の透明導電層は、前記第4の半導体層上面及び前記第2のサイドウォールと接し、

前記第1の導電層と前記第3の導電層とは、同一の導電層をエッティングする工程を経て形成されたものであり、

前記第1の絶縁層と前記第2の絶縁層とは、同一の絶縁層をエッティングする工程を経て形成されたものであり、

前記第1の半導体層と前記第3の半導体層とは、同一の半導体層をエッティングする工程を経て形成されたものであり、

前記第2の半導体層と前記第4の半導体層とは、一導電型の不純物元素を含有する同一の半導体層をエッティングする工程を経て形成されたものであり、

前記第1の透明導電層と前記第2の透明導電層とは、同一の透明導電層をエッティングする工程を経て形成されたものであり、

前記第1の金属層と前記第2の金属層とは、同一の金属層をエッティングする工程を経て形成されたものであり、

前記第1の金属層と重ならず且つ前記基板上面に接する前記第1の透明導電層の部分は、前記画素電極として機能することを特徴とする半導体装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、薄膜トランジスタ（以下、TFTという）で構成された回路を有する半導体装置及びその作製方法に関する。例えば、液晶や、自発光素子を用いた表示装置などに代表される電気光学装置及びこれらの電気光学装置を部品として搭載した電子機器に関する。

##### 【0002】

なお、本明細書において、半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、半導体回路及び電気機器は全て半導体装置である。

##### 【背景技術】

##### 【0003】

液晶テレビ、パーソナルコンピュータ、及び携帯電話のディスプレイなど広く普及している表示装置の多くは、シリコンを主構成元素とする非晶質半導体を用いたTFTをスイッチング素子として利用した液晶表示装置が用いられている。非晶質半導体を用いたTFT（以下、アモルファス半導体TFTという）は、従来5枚のフォトマスクを用い、フォトリソグラフィ工程によって積層構造を形成している。また近年、多階調フォトマスクを用いることで、フォトマスク数を4枚に削減したアモルファス半導体TFTの作製プロセスも開発されている。

##### 【発明の開示】

##### 【発明が解決しようとする課題】

##### 【0004】

本明細書においてフォトリソグラフィ工程とは、フォトレジストの形成処理、露光処理、現像処理、エッティング処理、レジスト剥離処理、洗浄処理、検査処理などの処理を含むものを言う。また、本明細書においてパターニングとは、基板上に形成した層の不要な部分を除去し、所望の形状に加工することをいう。例えば、基板上に形成した絶縁層、導電層、半導体層等の不要な部分を除去し、所望の形状に加工することをパターニングという。

##### 【0005】

従って、従来の5枚のフォトマスクを用いてアモルファス半導体TFTを作製する場合フォトリソグラフィ工程を5回繰り返すことになる。露光や現像など複数の工程を含むフォトリソグラフィ工程は、アモルファス半導体TFTの製造工程におけるスループットの低下や、製造コスト増大に大きな影響をおよぼす要因となっている。

10

20

30

40

50

**【 0 0 0 6 】**

このためフォトマスク数の削減によるフォトリソグラフィ工程の削減は、アモルファス半導体TFTの製造工程におけるスループットの改善や、製造コストの低減を意味する。このため、より安価なアモルファス半導体TFTを用いた半導体装置の生産を行うために、フォトマスク数の削減は大きな課題である。

**【 0 0 0 7 】**

近年、アモルファス半導体TFT作製プロセスの低減を目的として、アモルファス半導体層のパターニングと、ソース電極又はドレイン電極のパターニングを、一枚の多階調フォトマスク（グレートーンマスクまたはハーフトーンマスク）で行う方法が提案されているが、この方法を用いてもフォトマスクを4枚までにしか削減できていない。より、安価な液晶表示装置等の半導体装置が望まれるため、さらなるアモルファス半導体TFT作製プロセスの削減による、製造コスト低減は大きな課題である。10

**【 0 0 0 8 】**

さらに、従来のアモルファス半導体TFTの作製工程は、フォトリソグラフィ工程の数だけフォトマスクを必要としているため、フォトマスクの設計コストもアモルファス半導体TFTの製造コスト増大に大きな影響をおよぼす原因となっている。このためフォトマスク数削減による、フォトマスク設計コストを低減することも大きな課題である。

**【 0 0 0 9 】**

また、従来のアモルファス半導体TFTを用いた画素では、ソース電極又はドレイン電極と、画素電極の間に層間絶縁膜が存在する。このため画素内にソース電極又はドレイン電極と画素電極を電気的に接続するためのコンタクトホールを形成する必要があり、このコンタクトホール形成領域のスペースを確保する必要があった。このため画素内に形成されるコンタクトホール形成領域は、開口率低下の原因となっていた。特許文献1には、画素電極とソース電極又はドレイン電極の層間絶縁膜を省き、直接接続する構造としコンタクトホールを用いないソース電極又はドレイン電極と画素電極の接続構造を開示している。20

**【 0 0 1 0 】**

従来のアモルファス半導体TFTを用いた画素では、画素電極と絶縁層が積層された構造となっているため、画素における透過率の低下を招いていた。

**【 0 0 1 1 】**

本発明は上記問題を鑑みてなされたものであり、開口率と透過率が改善された画素を備えた半導体装置の提供、または製造コストを低減した半導体装置の作製方法を提供することを目的とする。30

**【特許文献1】特開2007-133371号公報****【課題を解決するための手段】****【 0 0 1 2 】**

本発明の特徴は、基板上に半導体素子を備えた半導体装置において、半導体素子は、基板上の第1の導電層、第1の導電層上の第1の絶縁層、第1の絶縁層上の第1の半導体層、及び第1の半導体層上の一導電型の不純物元素を含有する第2の半導体層を含む島状の積層と、島状の積層の側面に接するサイドウォールと、を有することである。40

**【 0 0 1 3 】**

本発明の特徴は、基板上にTFT及び容量素子を有する画素を備えた半導体装置において、容量素子は、基板上の第1の導電層、第1の導電層上の第1の絶縁層、第1の絶縁層上の第1の半導体層、及び第1の半導体層上の一導電型の不純物元素を含有する第2の半導体層を含む島状の積層と、島状の積層の側面に接するサイドウォールと、島状の積層及びサイドウォール上の第2の導電層と、を有することである。

**【 0 0 1 4 】**

本発明の特徴は、基板上にTFT及び容量素子を有する画素を備えた半導体装置において、TFTは、基板上の第1の導電層、第1の導電層上の第1の絶縁層、第1の絶縁層上の第1の半導体層、及び第1の半導体層上の一導電型の不純物元素を含有する第2の半導50

体層を含む島状の積層と、島状の積層の側面に接するサイドウォールと、島状の積層及びサイドウォール上の第2の導電層と、を有し、第2の導電層は、少なくとも透明導電層を含む積層構造であり、透明導電層の一部は、画素電極であり、画素電極は、基板に接していることである。

#### 【0015】

なお、第1の半導体層及び第2の半導体層として、非晶質半導体層または微結晶半導体層を適用することができる。また、第1の半導体層として、微結晶半導体層と非晶質半導体層の積層構造を適用することもできる。

#### 【0016】

本発明の特徴は、基板上に TFT 及び容量素子を有する画素、並びに接続端子を備えた半導体装置において、接続端子は、基板上の第1の導電層からなる島状の単層と、島状の単層の側面に接するサイドウォールと、島状の単層及びサイドウォール上の第2の導電層と、を有し、第2の導電層は、少なくとも透明導電層を含む積層構造であることである。10

#### 【0017】

以下に、上記記載の TFT、容量素子、および接続端子を同一基板上に有するアクティブマトリクス基板を作製する方法を簡略に説明する。

#### 【0018】

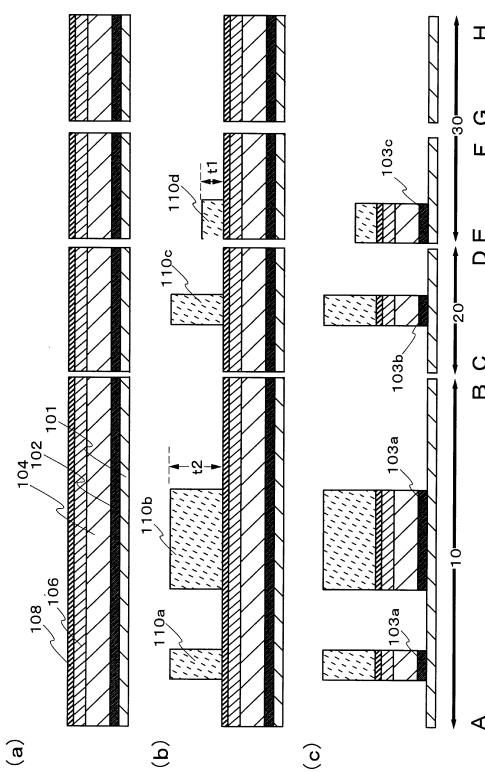

図4(a)において、基板101上に第1の導電層102を形成する。

#### 【0019】

次に、第1の導電層102上に、第1の絶縁層104、第1の絶縁層104上に第1の非晶質半導体層106、第1の非晶質半導体層106上に一導電型の不純物元素を含有する第2の非晶質半導体層108を形成する。20

#### 【0020】

次に、第1のフォトリソグラフィ工程により、第1の導電層102、第1の絶縁層104、第1の非晶質半導体層106、および一導電型の不純物元素を含有する第2の非晶質半導体層108をパターニングする。

#### 【0021】

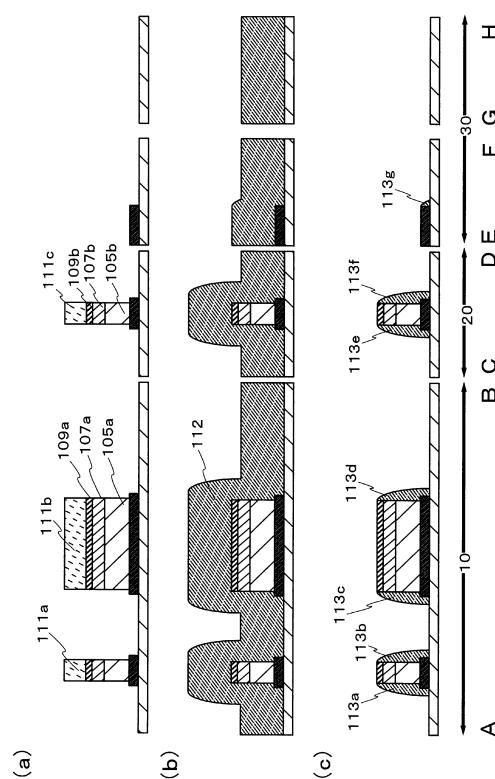

図4(b)において、一導電型の不純物元素を含有する第2の非晶質半導体層上にフォトレジストを形成し、第1のフォトマスクを用いて露光し、現像することにより第1のフォトレジストパターン110a～110dを形成する。ここで第1のフォトマスクは多階調フォトマスク(グレートーンマスクまたはハーフトーンマスク)を使用し、膜厚に差を有するフォトレジストパターンを形成する。第1の導電層102のみからなる島状の単層を形成する箇所は、フォトレジストパターンを第1の厚さ(t1)に設定し、第1の導電層102、第1の絶縁層104、第1の非晶質半導体層106及び一導電型の不純物元素を含有する第2の非晶質半導体層108からなる島状の積層を形成する箇所は、フォトレジストパターンを第2の厚さ(t2)に設定する。ここでフォトレジストパターンの第1の厚さは第2の厚さより薄い(t1 < t2)。30

#### 【0022】

図4(c)において、第1のフォトレジストパターン110a～110dをマスクとして第1の導電層102、第1の絶縁層104、第1の非晶質半導体層106、および一導電型の不純物元素を含有する第2の非晶質半導体層108のエッティングを行い、島状の単層および島状の積層を形成する。40

#### 【0023】

図5(a)において、第1のフォトレジストパターン110a～110dにアッシング処理を行い、変形された第1のフォトレジストパターン111a～111cの形成および第1のフォトレジストパターン110dの除去を行う。図5(a)のように、第1のフォトレジストパターン111a～111cは、第1のフォトレジストパターン110a～110cの第1の厚さ(t1)の部分が除去され、膜厚が減少している。加えて、第1のフォトレジストパターン110a～110dにアッシング処理を行う際、第1のフォトレジストパターン110a～110dの側面もアッシングされるため、第1のフォトレジスト50

パターン 111a ~ 111c の面積は、図 4 (b) の工程において第 2 の厚さ (t2) で形成されたフォトレジストパターンの面積よりも、若干小さくなり、図示されていないが、一導電型の不純物元素を含有する第 2 の非晶質半導体層の端部が表面に露出することになる。

#### 【0024】

変形された第 1 のフォトレジストパターン 111a ~ 111c をマスクとしたエッチングにより、第 1 の絶縁層 104 でなる島状のゲート絶縁層 105a 等と、第 1 の非晶質半導体層 106 でなる島状の第 1 の非晶質半導体層 107a 等と、一導電型の不純物元素を含有する第 2 の非晶質半導体層 108 でなる島状の一導電型の不純物元素を含有する第 2 の非晶質半導体層 109a 等とを形成する。その後、フォトレジストパターン 111a ~ 111c を剥離する。10

#### 【0025】

第 1 のフォトリソグラフィ工程において、多階調フォトマスクを第 1 のフォトマスクとして用いることにより、TFT 部 10 にはゲート配線 103a、ゲート絶縁層 105a、島状の第 1 の非晶質半導体層 107a、島状の一導電型の不純物元素を含有する第 2 の非晶質半導体層 109a が形成される。また、容量部 20 には、容量線 103b、絶縁層 105b、島状の第 1 の非晶質半導体層 107b、島状の一導電型の不純物元素を含有する第 2 の非晶質半導体層 109b が、端子部 30 には、電極 103c が形成される。(図 4 (b)、(c)、図 5 (a))

#### 【0026】

図 5 (b)において、基板全面に第 2 の絶縁層 112 を形成する。第 2 の絶縁層 112 は、第 1 のフォトリソグラフィ工程において、多階調フォトマスクを用いた露光技術により形成される第 1 の導電層が単層として存在するパターンと、第 1 の導電層、第 1 の絶縁層、第 1 の非晶質半導体層及び一導電型の不純物元素を含有する第 2 の非晶質半導体層が島状に積層された構造で残存するパターンの側面にサイドウォールを形成するためのものである。パターンの側面がテーパー形状になってしまふと、サイドウォールが形成されても第 1 の導電層と第 2 の導電層の不要なショートが起こりやすくなり、半導体素子の信頼性を損なう可能性があるため、第 2 の絶縁層 112 をサイドウォールとして用いる為には、被膜形成面の段差部の被覆性が良いことが重要である。20

#### 【0027】

図 5 (c)において、第 2 の絶縁層 112 をエッチングし、サイドウォール 113a ~ 113g を形成する。サイドウォール 113a ~ 113g を形成するためには、ドライエッティングなどにより異方性の高いエッチング処理を行う必要がある。また、第 2 の絶縁層 112 をエッチング処理する際、島状の一導電型の不純物元素を含有する第 2 の非晶質半導体層 109a、109bとの選択比を十分にとる必要があり、一導電型の不純物元素を含有する第 2 の非晶質半導体層 108 が、若干エッチングされる場合には、エッチングされることを考慮して厚めに形成しておく必要がある。30

#### 【0028】

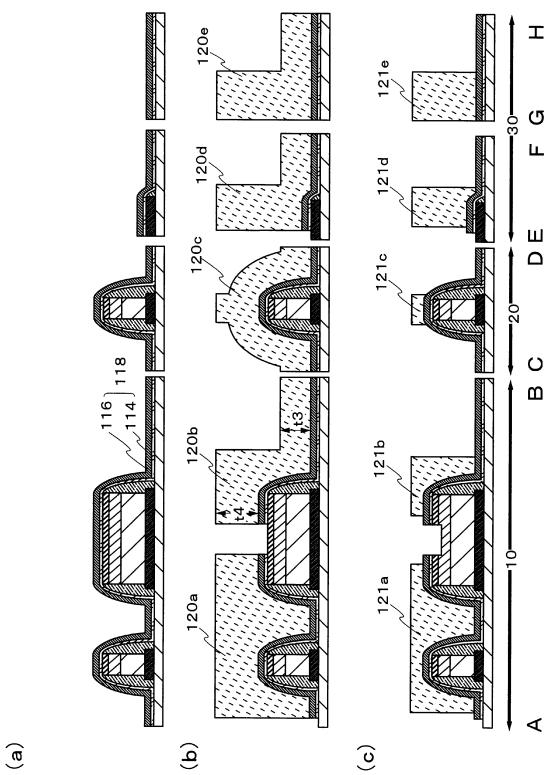

図 6 (a)において、基板全面に第 2 の導電層 118 を形成する。第 2 の導電層 118 は透明導電層 114、金属層 116 を順に積層した構造とする。40

#### 【0029】

次に、第 2 のフォトリソグラフィ工程により、透明導電層 114、金属層 116 からなる第 2 の導電層 118 をパターニングする。

#### 【0030】

図 6 (b)において、第 2 の導電層上にフォトレジストを形成し、第 2 のフォトマスクを用いて露光し、現像することにより第 2 のフォトレジストパターン 120a ~ 120e を形成する。ここで第 2 のフォトマスクとして、第 1 のフォトマスクと同様に多階調フォトマスクを使用することで、膜厚に差を有するフォトレジストパターンが形成される。透明導電層 114 および金属層 116 の積層構造である第 2 の導電層 118 を残存させる箇所は、フォトレジストパターンを第 4 の厚さ (t4) に、透明導電層 114 のみを残存さ50

せる箇所は、フォトレジストパターンを第3の厚さ( $t_3$ )に設定する。第3の厚さ( $t_3$ )は第4の厚さ( $t_4$ )より薄い( $t_3 < t_4$ )。第2のフォトレジストパターン $120\text{a} \sim 120\text{e}$ をマスクに第2の導電層 $118$ をエッティングする。この際のエッティング方法としてウエットエッティングまたはドライエッティングを用いることが可能である。

#### 【0031】

図6(c)において、第2のフォトレジストパターン $120\text{a} \sim 120\text{e}$ をアッシング処理し、変形された第2のフォトレジストパターン $121\text{a} \sim 121\text{e}$ を形成する。図6(c)のように、第2のフォトレジストパターン $121\text{a} \sim 121\text{e}$ は、第2のフォトレジストパターン $120\text{a} \sim 120\text{e}$ の第3の厚さ( $t_3$ )の部分が除去され、膜厚が減少するとともに、第2のフォトレジストパターンのうち初期膜厚が第3の厚さ( $t_3$ )であった部分では、金属層 $116$ が露出することになる。加えて、アッシング処理を行う際、第2のフォトレジストパターン $120\text{a} \sim 120\text{e}$ の側面もアッシングされるため、変形された第2のフォトレジストパターン $121\text{a} \sim 121\text{e}$ の面積は、図6(b)の工程において第4の厚さ( $t_4$ )で形成されたフォトレジストパターンの面積よりも、若干小さくなる。

10

#### 【0032】

図7(a)において、変形された第2のフォトレジストパターン $121\text{a} \sim 121\text{e}$ をマスクとして、表面に露出した金属層 $116$ をエッティングにより除去し、透明導電層 $114$ を表面に露出させる。このときエッティングは金属層と透明導電層とで選択比のとれる手法により行う。露出した透明導電層 $114$ は、画素電極や基板端の接続端子として用いる。さらに、島状の一導電型の不純物元素を含有する第2の非晶質半導体層 $109\text{a}$ の中央部をエッティングし、ソース領域とドレイン領域に分離させる。このエッティングは異方性を持つドライエッティング法により行う。実際には、島状の第1の非晶質半導体層 $107\text{a}$ も多少エッティングされる。

20

#### 【0033】

第2のフォトリソグラフィ工程において、多階調フォトマスクを第2のフォトマスクとして用いることにより、TFT部 $10$ では透明導電層 $115\text{a}$ と金属層 $117\text{a}$ の積層でなるソース配線 $119\text{a}$ 及び、透明導電層 $115\text{b}$ と金属層 $117\text{b}$ の積層でなるソース電極又はドレイン電極 $119\text{b}$ が形成される。また、透明導電層 $115\text{b}$ の一部が画素電極 $115\text{f}$ となる。また、容量部 $20$ には透明導電層 $115\text{b}$ の一部であり容量線 $103\text{b}$ に対向する電極 $115\text{c}$ が形成され、端子部 $30$ には、電極 $115\text{d}$ 、 $115\text{e}$ が形成される。(図6(b)、(c)、図7(a))

30

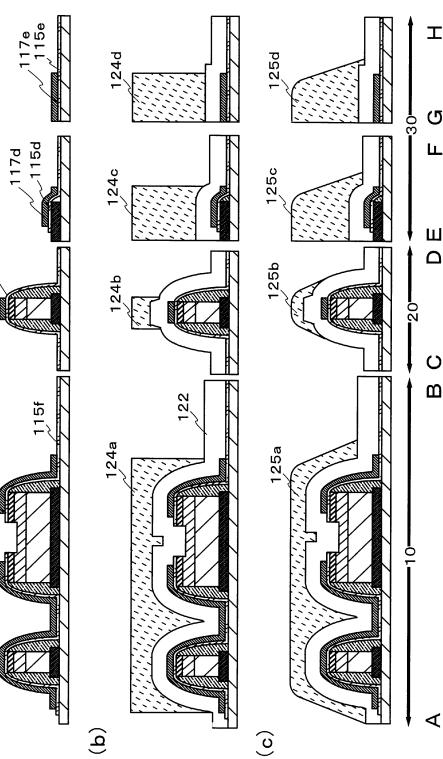

#### 【0034】

図7(b)において、基板全面に第3の絶縁層 $122$ を形成する。第3の絶縁層 $122$ は、TFTを不純物等から保護するための保護絶縁層(パッシベーション膜)として用いられる。

#### 【0035】

次に、第3のフォトリソグラフィ工程として、第3の絶縁層 $122$ 上にフォトレジストを形成し、基板 $101$ の裏面より露光を行う。このとき、第1のフォトリソグラフィ工程によりパターニングされた第1の導電層および第2のフォトリソグラフィ工程によりパターニングされた金属層をマスクとして利用し、第3のフォトレジストパターン $124\text{a} \sim 124\text{d}$ を形成する。第3のフォトレジストパターン形成に際し、基板 $101$ 上に形成されている第1の導電層 $102$ および第2の導電層 $118$ の上層である金属層 $116$ のパターンをマスクとして、裏面より露光を行うため、第3のフォトレジストパターン向けのフォトマスクが不要になり、フォトマスクと基板 $101$ との位置合わせも不要となる。

40

#### 【0036】

図7(c)において、図7(b)で形成された第3のフォトレジストパターン $124\text{a} \sim 124\text{d}$ にリフロー処理を行い、変形された第3のフォトレジストパターン $125\text{a} \sim 125\text{d}$ を形成する。リフロー処理をすることによりレジストパターンが第3の絶縁層 $122$ を被覆する面積が拡がり、変形された第3のフォトレジストパターン $125\text{a} \sim 12$

50

5 d の端部は、金属層 1 1 6 で形成されたパターンの端部を越える。

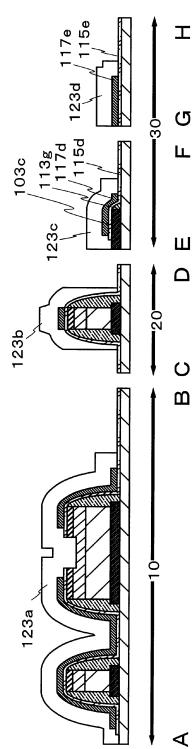

**【0037】**

図 8において、変形された第 3 のフォトレジストパターン 1 2 5 a ~ 1 2 5 d をマスクに、第 3 の絶縁層 1 2 2 をパターニングし、保護絶縁層 1 2 3 a ~ 1 2 3 d を形成する。

**【0038】**

第 3 のフォトリソグラフィ工程において、裏面露光（又は背面露光）技術を用いることにより、保護絶縁層 1 2 3 a ~ 1 2 3 d を形成する。（図 7（b）、（c）、図 8）

**【0039】**

このような構成とすることで、2枚のフォトマスクを使用し、3回のフォトリソグラフィ工程によってアクティブマトリクス基板を作製することができる。このため、従来4枚のフォトマスクを使用し、最低4回のフォトリソグラフィ工程によって製造されていたアモルファス半導体 TFT に比べて、大幅にフォトマスク数及びフォトリソグラフィ工程数を削減することができ、製造時間及び製造コストの削減が可能となる。10

**【発明の効果】**

**【0040】**

本発明により、2枚のフォトマスクを使用し、3回のフォトリソグラフィ工程によってアクティブマトリクス基板を作製することができる。このため、従来4枚のフォトマスクを使用し、最低4回のフォトリソグラフィ工程によって製造されていたアモルファス半導体 TFT に比べて、大幅にフォトマスク数及びフォトリソグラフィ工程数を削減することができ、製造時間及び製造コストの削減が可能となる。20

**【0041】**

本発明により、ソース電極又はドレイン電極・配線を透明導電層と金属層の積層構造である第2の導電層で形成することにより、従来画素領域に存在していた、ソース電極又はドレイン電極の一方と画素電極のコンタクトホールを形成する領域を必要としない為、開口率の向上が可能である。さらに、画素電極は基板と接し、絶縁膜と積層されない構造となるため画素における開口率、透過率が向上する。

**【発明を実施するための最良の形態】**

**【0042】**

以下、本発明の実施の形態について図面を参照しながら説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。30

**【0043】**

**（実施の形態 1）**

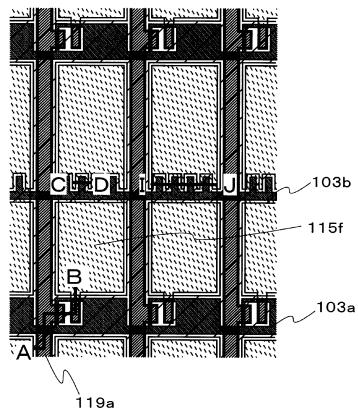

図 1 は本発明のアモルファス半導体 TFT を有するアクティブマトリクス基板の平面図の一例であり、ここでは簡略化のため、マトリックス上に配置された複数の画素のうち1つの画素の構成を示している。

**【0044】**

図 1 に示すように、アモルファス半導体 TFT を有するアクティブマトリクス基板は、互いに平行に配置された複数のゲート配線 1 0 3 a と、各ゲート配線 1 0 3 a と交差して互いに平行に配置されるソース配線 1 1 9 a を複数有している。40

**【0045】**

また、ゲート配線 1 0 3 a とソース配線 1 1 9 a とで囲まれた領域には画素電極 1 1 5 f が配置されている。この画素電極 1 1 5 f は、ソース電極又はドレイン電極 1 1 9 b の透明導電層 1 1 5 b と同じ材料で構成される。

**【0046】**

さらに、画素電極 1 1 5 f の下で隣り合う2本のゲート配線の間に、ゲート配線と平行に容量線 1 0 3 b が配置されている。この容量線 1 0 3 b は全画素に設けられており、画素電極 1 1 5 f との間に存在する絶縁層 1 0 5 b を誘電体として保持容量素子を形成している。50

**【 0 0 4 7 】**

また、ゲート配線 103a とソース配線 119a の交差部付近にはスイッチング素子としての TFT が設けられている。この TFT は、非晶質半導体層で形成されたチャネル形成領域を有する逆スダガ型（若しくは、ボトムゲート型）の TFT である。

**【 0 0 4 8 】**

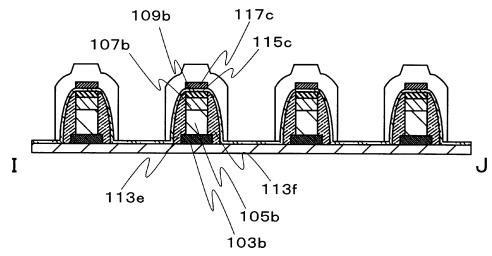

図 3 は、画素部における保持容量素子形成部の断面図であり、図 1 の I - J 部分を示したものである。保持容量素子は容量線 103b と画素電極 115f の一部を電極として用い、容量線 103b と画素電極 115f の間の絶縁層 105b 及び、サイドウォール（側壁）を誘電体膜として用いる。図 1 及び 3 では容量を効率的に形成するため、補助容量パターンを櫛状に形成している。

10

**【 0 0 4 9 】**

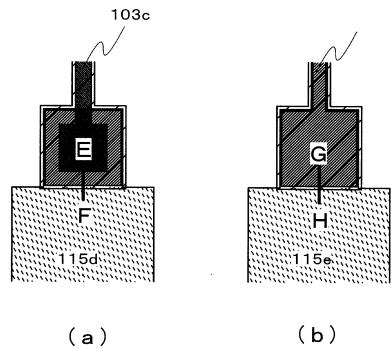

図 2 (a), (b) は本発明のアクティブマトリクス基板上に画素と同時に形成される外部回路への接続端子部の平面図の一例を示している。

**【 0 0 5 0 】**

図 2 (a)、(b) を例に取り、アクティブマトリクス基板端子部の構造を示す。図 2 (a) はアクティブマトリクス基板上における引き回しの配線を電極 103c で行う場合である。引き回された第 1 の導電層からなる電極 103c は透明導電層からなる電極 115d と接している。

**【 0 0 5 1 】**

また、電極 103c と電極 115d の接続部において電極 103c の端部には、第 2 の絶縁層 112 からなるサイドウォール 113g が設けられ、段差が緩和される。このため、電極 115d の断切れが防止される。また、電極 103c と電極 115d の接続部は完全に保護絶縁層 123c で覆われているため、汚染物等から保護され、信頼性を向上させることができる。

20

**【 0 0 5 2 】**

図 2 (b) は、引き回し配線が第 2 の導電層 118 で形成されている場合にもほぼ同様の構成をとる。

**【 0 0 5 3 】**

図 1、2、3 を例に取り、本発明を用いたチャネルエッチ型アモルファス半導体 TFT、保持容量素子部、及び、接続端子部の製造方法を図 4 乃至 8 に示す。図 4 乃至 8 では図 1 に示す画素部平面レイアウトの A - B の断面、C - D の断面、及び、図 2 (a) の E - F の断面、図 2 (b) の G - H の断面を用いて示す。尚、A - B の断面と C - D の断面の間、C - D の断面と E - F の断面の間、及び、E - F の断面と G - H の断面の間の空白は、省略を意味し、図示する TFT 部 10、容量部 20 及び端子部 30 は、同一基板上に形成される。

30

**【 0 0 5 4 】**

図 4 (a) において、基板 101 上に第 1 の導電層 102 を形成する。基板 101 には従来から使用されているアモルファス半導体 TFT の作製に使用されるガラス基板を用いれば良く、石英基板又は、透光性を有するプラスチック基板等を使用してもよい。また、第 1 の導電層 102 は、主として電極または配線となるものでアルミニウム (Al) 又は、銅 (Cu) などの低抵抗導電性材料が好ましい。

40

**【 0 0 5 5 】**

第 1 の導電層 102 は電極または配線として低抵抗であることと、アモルファス半導体 TFT の作製プロセス温度に対する耐熱性を有することが求められる。そのため耐熱性導電性材料、低抵抗導電性材料を積層した構造としても良い。積層構造は、下層を耐熱性導電性材料とし、中層を低抵抗導電性材料とし、上層を耐熱性導電性材料とすればよい。例えば第 1 の導電層 102 の構造を、下層をモリブデン (Mo)、中層をアルミニウム (Al)、上層をモリブデン (Mo) の積層構造とし、耐熱性導電性材料をバリア膜として使用しても良い。低抵抗導電性材料として Ag-Pd-Cu 合金を用いてもよい。耐熱性導電性材料としては、チタン (Ti)、タンタル (Ta)、タングステン (W)、モリブデン (Mo) の積層構造とする。

50

Mo)、クロム(Cr)、ネオジム(Nd)から選ばれた元素、または前記元素を成分とする合金か、前記元素を組み合わせた合金膜、または前記元素を成分とする窒化物で形成する。例えば、TiとCuの積層、窒化チタンとCuとの積層が挙げられる。また、Ti、Cr、Nd等の耐熱性導電性材料と組み合わせて形成した場合、平坦性が向上するため好ましい。また、このような耐熱性導電性材料のみ、例えばMoとWを組み合わせて形成しても良い。

#### 【0056】

液晶表示装置を実現するためには、ゲート配線は耐熱性導電性材料と低抵抗導電性材料とを組み合わせて形成することが望ましい。この時の適した組み合わせを説明する。

#### 【0057】

画面サイズが比較的小型(5型程度)であれば、耐熱性導電性材料の窒化物から成る導電層と耐熱性導電性材料から成る導電層とを積層した二層構造としてもよい。上層の導電層はAl、Cu、Ta、Ti、W、Nd、Crから選ばれた元素、または前記元素を成分とする合金か、前記元素を組み合わせた合金膜で形成すれば良く、窒化タンタル膜、窒化タンゲステン膜、窒化チタン膜などで形成する。例えば、上層の導電層としてCr、下層の導電層としてNdを含有するAlとを積層した二層構造とすることが好ましい。上層の導電層は10~100nm(好ましくは20~50nm)とし、下層の導電層は200~400nm(好ましくは250~350nm)とする。

#### 【0058】

一方、大画面に適用するには、下層として耐熱性導電性材料から成る導電層と、中層として低抵抗導電性材料から成る導電層と、上層として耐熱性導電性材料から成る導電層とを積層した三層構造とすることが好ましい。

#### 【0059】

低抵抗導電性材料から成る導電層は、アルミニウム(Al)を成分とする材料で形成し、純Alの他に、0.01~5atomic%のスカンジウム(Sc)、Ti、Nd、シリコン(Si)等を含有するAlを使用する。耐熱性導電性材料で構成された上層は、中層にAlを用いた場合にヒロックが発生するのを防ぐ効果がある。下層の耐熱性導電性材料から成る導電層は10~100nm(好ましくは20~50nm)とし、中層の低抵抗導電性材料から成る導電層は200~400nm(好ましくは250~350nm)とし、上層の耐熱性導電性材料から成る導電層は10~100nm(好ましくは20~50nm)とする。本実施の形態では、Tiをターゲットとしたスパッタ法により下層の耐熱性導電性材料から成る導電層をTi膜で50nmの厚さに成膜し、Alをターゲットとしたスパッタ法により中層の低抵抗導電性材料から成る導電層をAl膜で200nmの厚さに成膜し、Tiをターゲットとしたスパッタ法により上層の耐熱性導電性材料から成る導電層をTi膜で50nmの厚さに成膜する。

#### 【0060】

次に、プラズマCVD法、スパッタ法などの方法を用いて第1の導電層102上に、第1の絶縁層104を、第1の絶縁層104上に第1の非晶質半導体層106、第1の非晶質半導体層106上に一導電型の不純物元素を含有する第2の非晶質半導体層108を形成する。また、マルチチャンバー構造などのプラズマCVD若しくは、スパッタ法を用いて第1の絶縁層104と第1の非晶質半導体層106、第1の非晶質半導体層106と一導電型の不純物元素を含有する第2の非晶質半導体層108などの界面を大気に曝すことなく、連続で形成することが望ましい。

#### 【0061】

第1の絶縁層104は、窒化珪素膜、酸化窒化珪素膜、酸化珪素膜、などの絶縁膜であればよく单層若しくは積層構造とし、50~600nm(好ましくは300~500nm)の厚さに形成する。

#### 【0062】

第1の絶縁層104上に50~300nm(好ましくは100~200nm)の厚さで第1の非晶質半導体層106を形成する。第1の非晶質半導体層106としては、プラズ

10

20

30

40

50

マ C V D 法、シリコンのターゲットを用いたスパッタ法などの方法を用いて非晶質シリコン( a - S i )膜を形成する。その他、この第1の非晶質半導体層106には、微結晶半導体膜、非晶質シリコンゲルマニウム( S i <sub>x</sub> G e ( <sub>1 - x</sub> )、( 0 < X < 1 ) )膜、非晶質シリコンカーバイド( S i <sub>x</sub> C <sub>y</sub> )膜などの非晶質構造を有する化合物半導体膜を適用することも可能である。

#### 【 0 0 6 3 】

第1の非晶質半導体層106上に10~100nmの厚さで一導電型の不純物元素を含有する第2の非晶質半導体層108を形成する。一導電型の不純物元素を含有する第2の非晶質半導体層108としては、プラズマCVD法、シリコンのターゲットを用いたスパッタ法などの方法を用いてリン( P )、ヒ素( A s )、若しくは、ボロン( B )などに代表される不純物を添加した非晶質シリコン( a - S i )膜を形成する。その他、この一導電型の不純物元素を含有する第2の非晶質半導体層108には、リン( P )、ヒ素( A s )、若しくは、ボロン( B )などに代表される不純物を添加した微結晶半導体膜、非晶質シリコンゲルマニウム( S i <sub>x</sub> G e ( <sub>1 - x</sub> )、( 0 < X < 1 ) )膜、非晶質シリコンカーバイド( S i <sub>x</sub> C <sub>y</sub> )膜などの非晶質構造を有する化合物半導体膜を適用することも可能である。

10

#### 【 0 0 6 4 】

次に、第1のフォトリソグラフィ工程により、第1の導電層102、第1の絶縁層104、第1の非晶質半導体層106、および一導電型の不純物元素を含有する第2の非晶質半導体層108をパターニングする。

20

#### 【 0 0 6 5 】

図4( b )において、一導電型の不純物元素を含有する第2の非晶質半導体層上にフォトレジストを形成し、第1のフォトマスクを用いて露光し、現像することにより第1のフォトレジストパターン110a~110dを形成する。ここで第1のフォトマスクは多階調フォトマスク( グレートーンマスクまたはハーフトーンマスク )を使用し、膜厚に差を有するフォトレジストパターンを形成する。第1の導電層102のみからなる島状の単層のパターンを形成する箇所は、フォトレジストパターンを第1の厚さ( t1 )に設定し、第1の導電層102、第1の絶縁層104、第1の非晶質半導体層106及び一導電型の不純物元素を含有する第2の非晶質半導体層108からなる島状の積層のパターンを形成する箇所は、フォトレジストパターンを第2の厚さ( t2 )に設定する。ここでフォトレジストパターンの第1の厚さは第2の厚さより薄い( t1 < t2 )。

30

#### 【 0 0 6 6 】

図4( c )において、第1のフォトレジストパターン110a~110dをマスクとして第1の導電層102、第1の絶縁層104、第1の非晶質半導体層106、および一導電型の不純物元素を含有する第2の非晶質半導体層108のエッチングを行う。この際のエッチング方法としてウェットエッチングまたはドライエッチングを用いることが可能である。

#### 【 0 0 6 7 】

図5( a )において、第1のフォトレジストパターン110a~110dにアッシング処理を行い、変形された第1のフォトレジストパターン111a~111cの形成および第1のフォトレジストパターン110dの除去を行う。図5( a )のように、第1のフォトレジストパターン111a~111cは、第1のフォトレジストパターン110a~110cの第1の厚さ( t1 )の部分が除去され、膜厚が減少している。加えて、第1のフォトレジストパターン110a~110dにアッシング処理を行う際、第1のフォトレジストパターン110a~110dの側面もアッシングされるため、第1のフォトレジストパターン111a~111cの面積は、図4( b )の工程において第2の厚さ( t2 )で形成されたフォトレジストパターンの面積よりも、若干小さくなり、図示されていないが、一導電型の不純物元素を含有する第2の非晶質半導体層の端部が表面に露出することになる。

40

#### 【 0 0 6 8 】

50

変形された第1のフォトレジストパターン111a～111cを用いて、TFT部10では、第1の絶縁層104でなるゲート絶縁層105a等と、第1の非晶質半導体層106でなる島状の第1の非晶質半導体層107a等と、一導電型の不純物元素を含有する第2の非晶質半導体層108でなる島状の一導電型の不純物元素を含有する第2の非晶質半導体層109a等とを形成し、容量部20では、容量線103b、絶縁層105b、島状の第1の非晶質半導体層107b、島状の一導電型の不純物元素を含有する第2の非晶質半導体層109bを形成する。その後、フォトレジストパターン111a～111cを剥離する。

#### 【0069】

第1のフォトリソグラフィ工程において、多階調フォトマスクを第1のフォトマスクとして用いることにより、TFT部10にはゲート配線103a、ゲート絶縁層105a、島状の第1の非晶質半導体層107a、島状の一導電型の不純物元素を含有する第2の非晶質半導体層109aが形成される。また、容量部20には、容量線103b、絶縁層105b、島状の第1の非晶質半導体層107b、島状の一導電型の不純物元素を含有する第2の非晶質半導体層109bが形成される。端子部30には、電極103cが形成される。(図4(b)、(c)、図5(a))

#### 【0070】

図5(b)において、基板全面に第2の絶縁層112を形成する。第2の絶縁層112は、プラズマCVD法、スパッタ法などの方法を用いて形成し、窒化珪素膜、酸化窒化珪素膜、酸化珪素膜などの絶縁膜であればよく、単層若しくは積層構造としてもよい。第2の絶縁層112は、第1のフォトリソグラフィ工程において、多階調フォトマスクを用いた露光技術により形成される第1の導電層が単層として存在するパターンと、第1の導電層、第1の絶縁層、第1の非晶質半導体層及び一導電型の不純物元素を含有する第2の非晶質半導体層が島状に積層された構造で残存するパターンの側面にサイドウォールを形成するためのものである。第2の絶縁層112をサイドウォールとして用いる為には、被膜形成面の段差部の被覆性が良いことが重要である。また、パターンの側面がテーパー形状になってしまふと、サイドウォールが形成されても第1の導電層と第2の導電層の不要なショートが起こりやすくなり、半導体素子の信頼性を損なう可能性があるため、被覆性及び膜厚等の膜質を十分考慮して第2の絶縁層112を形成する必要がある。

#### 【0071】

図5(c)において、第2の絶縁層112をエッチングし、サイドウォール113a～113gを形成する。サイドウォール113a～113gを形成するためには、ドライエッチングなどにより異方性の高いエッチング処理を行う必要がある。また、第2の絶縁層112をエッチング処理する際、一導電型の不純物元素を含有する第2の非晶質半導体層108との選択比を十分にとる必要があり、島状の一導電型の不純物元素を含有する第2の非晶質半導体層109a、109bが、若干エッチングされる場合には、エッチングされる膜厚を考慮して厚めに形成しておく必要がある。

#### 【0072】

図6(a)において、基板全面に第2の導電層118を形成する。第2の導電層118は透明導電層114、金属層116を積層した構造とする。透明導電層114の材料として、例えばITO(インジウム-錫酸化物)やIZO(インジウム-亜鉛酸化物)等を用いる。また金属層116の材料として、Mo、W、Ti、Taなどの高融点金属あるいは低抵抗金属のAlやCuなどを用いることができる。但し、第2の導電層118として、例えばITOとAlなどの組合せのように、酸化還元反応により腐蝕が進行するものもあるため、間にバリア性のある金属を挟む構造とするなど考慮する必要がある。

#### 【0073】

次に、第2のフォトリソグラフィ工程により、第2の導電層118をパターニングする。

#### 【0074】

図6(b)において、第2の導電層上にフォトレジストを形成し、第2のフォトマスク

10

20

30

40

50

を用いて露光し、現像することにより第2のフォトレジストパターン120a～120eを形成する。ここで第2のフォトマスクとして、第1のフォトマスクと同様に多階調フォトマスクを使用することで、膜厚に差を有するフォトレジストパターンが形成される。透明導電層114および金属層116の積層構造である第2の導電層118を残存させる箇所は、フォトレジストパターンを第4の厚さ( $t_4$ )に、透明導電層114のみを残存させる箇所は、フォトレジストパターンを第3の厚さ( $t_3$ )に設定する。第3の厚さ( $t_3$ )は第4の厚さ( $t_4$ )より薄い( $t_3 < t_4$ )。第2のフォトレジストパターン120a～120eをマスクに第2の導電層118をエッティングする。この際のエッティング方法としてウェットエッティングまたはドライエッティングを用いることが可能である。

## 【0075】

10

図6(c)において、第2のフォトレジストパターン120a～120eをアッシング処理し、変形された第2のフォトレジストパターン121a～121eを形成する。図6(c)のように、変形された第2のフォトレジストパターン121a～121eは、第2のフォトレジストパターン120a～120eの第3の厚さ( $t_3$ )の部分が除去され、膜厚が減少するとともに、第2のフォトレジストパターンのうち初期膜厚が第3の厚さ( $t_3$ )であった部分では、金属層116が露出することになる。加えて、第2のフォトレジストパターン120a～120eにアッシング処理を行う際、第2のフォトレジストパターン120a～120eの側面もエッティングされるため、変形された第2のフォトレジストパターン121a～121eの面積は、図6(b)の工程において第4の厚さ( $t_4$ )で形成されたフォトレジストパターンの面積よりも、若干小さくなる。

20

## 【0076】

図7(a)において、変形された第2のフォトレジストパターン121a～121eをマスクとして、露出した金属層116をエッティングにより除去し、透明導電層114を露出する。このときエッティングは金属層と透明導電層とで選択比のとれる手法により行う。露出した透明導電層114は、画素電極や基板端の接続端子として用いる。さらに、島状の一導電型の不純物元素を含有する第2の非晶質半導体層109aの中央部をエッティングし、ソース領域とドレイン領域に分離させる。このエッティングは異方性を持つドライエッティング法により行う。実際には、島状の第1の非晶質半導体層107aも多少エッティングされる。

## 【0077】

30

第2のフォトリソグラフィ工程において、多階調フォトマスクを第2のフォトマスクとして用いることにより、TFT部10では透明導電層115aと金属層117aの積層でなるソース配線119a及び、透明導電層115bと金属層117bの積層でなるソース電極又はドレイン電極119bが形成される。また、透明導電層115bの一部が画素電極115fとなる。また、画素電極115fの一部であり容量部20には容量線103bに対向する電極115cが形成され、端子部30には、電極115d、115eが形成される。(図6(b)、(c)、図7(a))

## 【0078】

図7(b)において、基板全面に第3の絶縁層122を形成する。第3の絶縁層122は、プラズマCVD法、スパッタ法などの方法を用いて形成し、窒化珪素膜、酸化窒化珪素膜、酸化珪素膜などの絶縁膜であればよく、単層若しくは積層構造としてもよい。第3の絶縁層122は、TFTを不純物等から保護するための保護絶縁層として用いられる。

40

## 【0079】

次に、第3のフォトリソグラフィ工程として、第3の絶縁層122上にフォトレジストを形成し、基板101の裏面より露光を行う。このとき、第1のフォトリソグラフィ工程によりパターニングされた第1の導電層および第2のフォトリソグラフィ工程によりパターニングされた金属層をマスクとして利用し、第3のフォトレジストパターン124a～124dを形成する。第3のフォトレジストパターン形成に際し、基板101上に形成されている第1の導電層102および第2の導電層118の上層である金属層116のパターンをマスクとして、裏面より露光を行うため、第3のフォトレジストパターン用のフォ

50

トマスクが不要になるとともに、フォトマスクと基板 101との位置合わせも不要となる。

#### 【0080】

図 7 (c)において、図 7 (b)で形成された第3のフォトレジストパターン 124a ~ 124dにリフロー処理を行い、変形された第3のフォトレジストパターン 125a ~ 125dを形成する。リフロー処理をすることによりレジストパターンが第3の絶縁層 122を被覆する面積が拡がり、変形された第3のフォトレジストパターン 125a ~ 125dの端部は、金属層 116で形成されたパターンの端部を越える。フォトレジストのリフロー処理には、加熱処理や薬液溶解によるものなどあり、どの手法を用いてもよい。リフロー処理によって変形された第3のフォトレジストパターン 125a ~ 125dの拡がりは、フォトレジストの材質特性、膜厚および加熱条件、さらに下地である窒化珪素膜表面との物性によって決定される。従って、拡がりの制御はこれらの特性、条件によって適宜設計すれば良い。リフロー処理によって変形された第3のフォトレジストパターン 125a ~ 125dの拡がりは、金属層 116で形成されたパターンの端部を越える必要があるが、さらにマージンを確保する冗長設計が望ましい。10

#### 【0081】

図 8において、変形された第3のフォトレジストパターン 125a ~ 125dをマスクに、第3の絶縁層 122をパターニングし、保護絶縁層 123a ~ 123dを形成する。その後、変形された第3のフォトレジストパターンを除去する。この保護絶縁層は、ガラス基板または保護絶縁層上の配向膜、液晶からの汚染物がアモルファス半導体 TFTや金属配線へ侵入するのを抑制する。また透明導電層のパターンのみが存在する箇所では、裏面露光によるレジストが形成されないため、保護絶縁層が形成されずに透明導電層が露出した構造となる。20

#### 【0082】

第3のフォトリソグラフィ工程において、裏面露光技術を用いることにより、保護絶縁層 123a ~ 123dを形成する。(図 7 (b)、(c)、図 8)20

#### 【0083】

本実施の形態によって、2枚のフォトマスクを使用し、3回のフォトリソグラフィ工程によってアクティブマトリクス基板を作製することが出来る。このため、従来4枚のフォトマスクを使用し、最低4回のフォトリソグラフィ工程によって製造されていたアモルファス半導体 TFTに比べて、大幅にフォトマスク数及びフォトリソグラフィ工程数を削減することができ、製造時間及び製造コストの削減が可能となる。30

#### 【0084】

また、本実施の形態によって作製される半導体素子の側面にはサイドウォールが形成されるため、第1の導電層と第2の導電層が不要にショートすることを防止できること、および各パターンの端部においてステップカバレッジが向上し、配線、電極、絶縁層の被覆不良を低減することで、半導体装置の信頼性・歩留まりを向上させることが出来る。さらに、絶縁層の第1の導電層の端部を厳密にテーパー形状に作り込む必要がないことで、半導体装置作製工程の負担軽減が見込める。40

#### 【0085】

また、本実施の形態によって作製される TFTは、第1の導電層と、第1の導電層上の第1の絶縁層と、第1の絶縁層上の第1の非晶質半導体層と、第1の非晶質半導体層上の一導電型の不純物元素を含有する第2の非晶質半導体層を、多階調フォトマスクを用いてパターニングすることで、第1および第2の非晶質半導体層が第1の導電層の外側にのびてパターニングされることが無く、第1の導電層が、第1の非晶質半導体層と一導電型の不純物元素を含有する第2の非晶質半導体層を遮光する構造となることで、半導体層に光が入射して発生する光リーク電流を低減することが可能となる。40

#### 【0086】

また、本実施の形態によって作製される TFTは、ソース領域およびドレイン領域形成の際に、多階調フォトマスクを用いて第2の導電層と一導電型の不純物元素を含有する第50

2の非晶質半導体層と第1の非晶質半導体層の一部をエッティングする工程、および多階調マスクを変形させた後、第2の導電層の金属層をエッティングする工程によって、第1の非晶質半導体層と第2の導電層の透明導電層との間に第1の段差が、第2の導電層の透明導電膜と第2の金属層との間に第2の段差が生じる。これにより、下層の端部が上層の端部から露出することになり、第3の絶縁層のチャネル領域の被覆性を向上させることができるとなる。さらに、サイドウォールおよび第1の絶縁層によってTFTのチャネル形成部が覆われることで、基板や液晶層などTFT外部からチャネル形成部への不純物汚染による半導体素子の特性劣化を低減し、信頼性を向上させることができる。

#### 【0087】

また、本実施の形態によって作製される容量素子は、容量線と画素電極の一部を保持容量素子の対向する電極とし、その間の第1の絶縁層及びサイドウォールを誘電体とした保持容量素子の構造とすることで、容量線の側面にも容量を設けることが可能となる。第1の絶縁層を誘電体としている部分よりもサイドウォールの膜厚を薄く出来る為、容量線側面に容量を効率的に形成でき、容量線の上面だけではなく、側面も使用することで立体的に容量を形成することで、1画素に対する保持容量素子の形成面積を従来に比べて小さくすることが可能である。10

#### 【0088】

また、本実施の形態によって作製されるソース電極又はドレイン電極・配線は、透明導電層と金属層の積層構造である第2の導電層で形成される。これにより、従来画素領域に存在していた、ソース電極又はドレイン電極の一方と画素電極のコンタクトホールを形成する領域を必要としない為、開口率の向上が可能である。さらに、画素電極は基板と接し、絶縁膜と積層されない構造となるため画素における開口率、透過率が向上する。20

#### 【0089】

##### (実施の形態2)

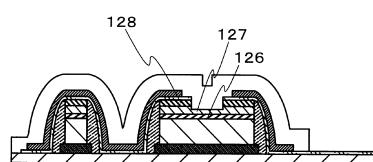

実施の形態1では、非晶質半導体層を用いたTFTを示したが、本実施の形態では、微結晶半導体層を用いたTFTの例を示す。微結晶半導体を用いるTFTの模式図を図9に示す。本実施の形態では、実施の形態1における第1の非晶質半導体層106を、第1の微結晶半導体層126と第1の非晶質半導体層127の積層とする。

#### 【0090】

第1の微結晶半導体層126は、チャネルとして機能する。第1の微結晶半導体層126は、周波数が数十MHz～数百MHzの高周波プラズマCVD法、または周波数が1GHz以上のマイクロ波プラズマCVD法により形成することができる。代表的には、SiH<sub>4</sub>、Si<sub>2</sub>H<sub>6</sub>などの水素化珪素を水素で希釈して形成することができる。また、水素化珪素及び水素に加え、ヘリウム、アルゴン、クリプトン、ネオンから選ばれた一種または複数種の希ガス元素で希釈して微結晶半導体膜を形成することができる。これらのときの水素化珪素に対して水素の流量比を5倍以上200倍以下、好ましくは50倍以上150倍以下、更に好ましくは100倍とする。なお、水素化珪素の代わりに、SiH<sub>2</sub>C<sub>1</sub><sub>2</sub>、SiHC<sub>1</sub><sub>3</sub>、SiC<sub>1</sub><sub>4</sub>、SiF<sub>4</sub>等を用いることができる。また、第1の非晶質半導体層127は、実施の形態1に示した第1の非晶質半導体層106を用いれば良く、TFTのオフ電流低減、第1の微結晶半導体層126の酸化防止、及び、ソース領域、ドレイン領域形成時のエッティングによって、第1の微結晶半導体層がエッティングされるのを防ぐなど、バッファ層として機能する。3040

#### 【0091】

また、実施の形態1における一導電型の不純物元素を含有する第2の非晶質半導体層108の代わりに一導電型の不純物元素を含有させた微結晶半導体層128を用いることも可能である。チャネルとソース電極又はドレイン電極間の寄生抵抗を低く抑えることが可能なため、オン電流の向上が実現出来る。

#### 【0092】

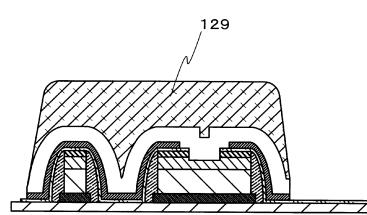

##### (実施の形態3)

本実施の形態では、実施の形態1における第3のフォトリソグラフィ工程において、第50

3のフォトレジストパターン124a～124dの代わりにポジ型の感光性樹脂を用いる例を示す。また、ポジ型感光性樹脂を用いるTFTの模式図を図10に示す。

#### 【0093】

実施の形態1における第3のフォトリソグラフィ工程において、ポジ型感光性材料を形成し、基板101の裏面より露光を行う。実施の形態1における第1のフォトリソグラフィ工程によりパターニングされた第1の導電層および第2のフォトリソグラフィ工程によりパターニングされた金属層の部分が遮光されることを利用して、ポジ型感光性材料パターン129を形成する。ポジ型感光性材料パターン129の形成に際し、基板101上に形成されている第1の導電層および金属層のパターンをマスクとして、裏面より露光を行うため、ポジ型感光性材料パターン形成用のフォトマスクが不要になるとともに、フォトマスクと基板101との位置合わせも不要となる。10

#### 【0094】

ポジ型感光性材料パターン129をマスクに、第3の絶縁層122をパターニングし、保護絶縁層123a～123dを形成する。この保護絶縁層は、ガラス基板または保護絶縁層上の配向膜、液晶からの汚染物がアモルファス半導体TFTや金属配線へ侵入するのを抑制する。また、透明導電層のパターンのみが存在する箇所では、裏面露光によるポジ型感光性材料パターンが形成されないため、保護絶縁層が形成されずに透明導電層が露出した構造となる。

#### 【0095】

ポジ型感光性材料としては、ポジ型のシロキサン、ポジ型のアクリル樹脂又はポリイミド樹脂などを用いることが可能である。さらにポジ型感光性ブラックマトリックス用樹脂を用いれば、ポジ型感光性材料パターンはブラックマトリックスとしても機能する。20

#### 【0096】

このように、実施の形態1で示した第3のフォトレジストパターン124a～124dの代わりにポジ型感光性材料パターン129を用いることで、第3のフォトリソグラフィ工程においてレジストを除去する工程を省略することができ、さらなる工程の簡略化を可能とする。

#### 【0097】

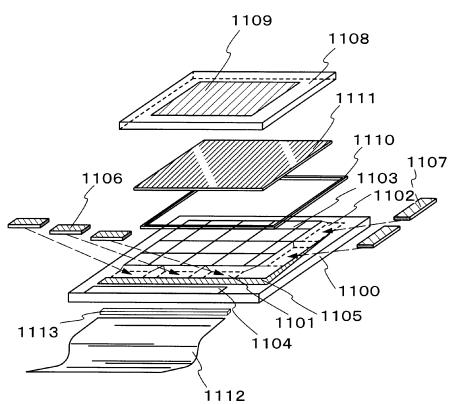

##### (実施の形態4)

図11はCOG(chip on glass)方式を用いて、電気光学装置の組み立てる様子を模式的に示す図である。第1の基板1100には画素領域1103、外部入出力端子1104、接続配線1105が形成されている。点線で囲まれた領域は、走査線側のICチップ貼り合わせ領域1101とデータ線側のICチップ貼り合わせ領域1102である。第2の基板1108には対向電極1109が形成され、シール材1110で第1の基板1100と貼り合わせる。シール材1110の内側には液晶が封入され液晶層1111を形成する。第1の基板1100と第2の基板1108とは所定の間隔を持って貼り合わせるが、ネマチック液晶の場合には3～8μm、スマートチック液晶の場合には1～4μmとする。30

#### 【0098】

ICチップ1106、1107は、データ線側と走査線側とで回路構成が異なる。ICチップは第1の基板1100に実装する。外部入出力端子1104には、外部から電源及び制御信号を入力するためのFPC1112(フレキシブルプリント配線板:Flexible Printed Circuit)を貼り付ける。FPC1112の接着強度を高めるために補強板1113を設けても良い。こうして電気光学装置を完成させることができる。ICチップは第1の基板1100に実装する前に電気検査を行えば電気光学装置の最終工程での歩留まりを向上させることができ、また、信頼性を高めることができる。40

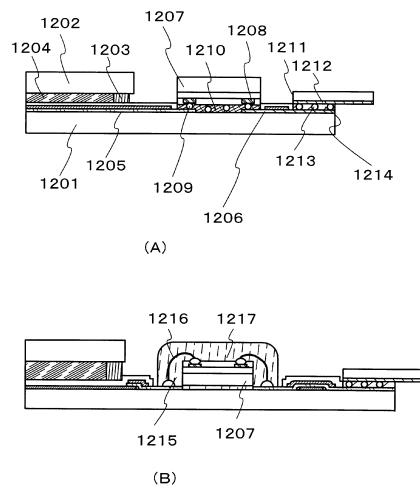

#### 【0099】

また、ICチップを第1の基板上に実装する方法は、異方性導電材を用いた接続方法やワイヤボンディング方式などを採用することができる。図12にその一例を示す。図12(A)は第1の基板1201にICチップ1207が異方性導電材を用いて実装される例50

を示している。第1の基板1201上には画素領域、画素領域に電気的に接続される引出線1205、接続配線及び入出力端子1206が設けられている。第2の基板1202はシール材1203で第1の基板1201と接着されており、その間に液晶層1204が設けられている。

#### 【0100】

また、接続配線及び入出力端子1206の一方の端にはFPC1211が異方性導電材で接着されている。異方性導電材は樹脂1214と表面にAuなどがメッキされた数十~数百μm径の導電性粒子1213から成り、導電性粒子1213により接続配線及び入出力端子1206とFPC1211に形成された配線1212とが電気的に接続されている。ICチップ1207も同様に異方性導電材で第1の基板に接着され、樹脂1210中に混入された導電性粒子1209により、ICチップ1207に設けられた入出力端子1208と引出線1205または接続配線及び入出力端子1206と電気的に接続されている。引出線1205、並びに接続配線及び入出力端子1206の構成としては、図8のG-Hの断面に示す構成を用いればよく、図12(A)では、引出線1205、並びに接続配線及び入出力端子1206に、透明導電層である電極115e及び金属層117eの積層を用いる例を示す。

#### 【0101】

また、図12(B)で示すように第1の基板にICチップを接着材1215で固定して、Auワイヤ1216によりICチップの入出力端子と引き出し線又は接続配線及び入出力端子とを接続しても良い。そして樹脂1217で封止する。図8のE-Fの断面に示す構成を用いればよく、図12(B)では、引出線1205及び接続配線及び入出力端子1206に、第1の導電層である電極103cと、電極103cに電気的に接続する透明導電層である電極115d及び金属層117dの積層を用いる例を示す。

#### 【0102】

ICチップの実装方法は図11及び図12を基にした方法に限定されるものではなく、ここで説明した以外にもCOG方法やワイヤボンディング方法、或いはTAB(Tape Automated Bonding)方法を用いることが可能である。

#### 【0103】

本実施の形態は実施の形態1、2、3のいずれか一と自由に組み合わせることが可能である。

#### 【0104】

##### (実施の形態5)

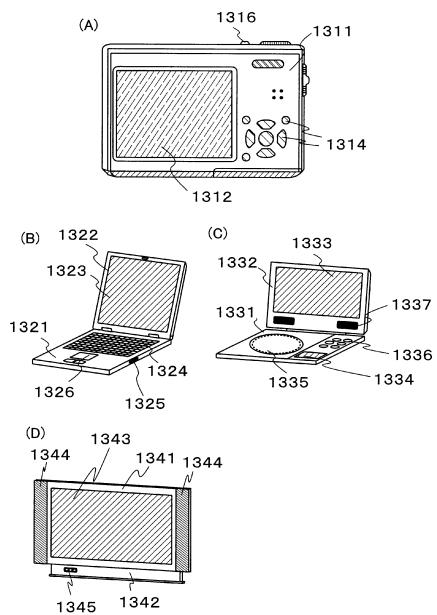

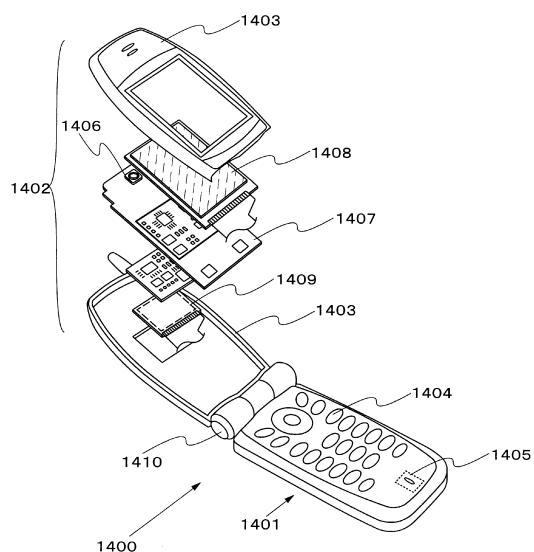

本発明の半導体装置、及び電子機器として、液晶TV、ビデオカメラ、デジタルカメラ等のカメラ、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置(カーオーディオ、オーディオコンポ等)、ノート型パーソナルコンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型ゲーム機又は電子書籍等)、記録媒体を備えた画像再生装置(具体的にはDigital Versatile Disc(DVD)等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置。例えば、ポータブルDVDプレイヤー。)などが挙げられる。それら電子機器のうち、一部の電子製品の具体例を図13および図14に示す。

#### 【0105】

図13(A)はデジタルカメラであり、本体1311、表示部1312、撮像部、操作キー1314、シャッターボタン1316等を含む。なお、図13(A)は表示部1312側からの図であり、撮像部は示していない。本発明により、より安価な表示部を有し、且つ、信頼性の高いデジタルカメラが実現できる。

#### 【0106】

図13(B)はノート型パーソナルコンピュータであり、本体1321、筐体1322、表示部1323、キーボード1324、外部接続ポート1325、ポインティングデバイス1326等を含む。本発明により、より安価な表示部を有し、且つ、信頼性の高いノート型パーソナルコンピュータを実現することができる。

10

20

30

40

50

**【0107】**

図13(C)は記録媒体を備えた携帯型の画像再生装置(具体的にはDVD再生装置)であり、本体1331、筐体1332、第1の表示部1333、第2の表示部1334、記録媒体(DVD等)読込部1335、操作キー1336、スピーカ部1337等を含む。第1の表示部1333は主として画像情報を表示し、第2の表示部1334は主として文字情報を表示する。なお、記録媒体を備えた画像再生装置には家庭用ゲーム機器なども含まれる。本発明により、安価な表示部を有し、且つ、信頼性の高い画像再生装置を実現することができる。

**【0108】**

また、図13(D)はテレビジョン(以下、テレビともいう)であり、筐体1341、支持台1342、表示部1343、スピーカ1344、ビデオ入力端子1345などを含む。このテレビジョンは、上述した実施の形態で示した作製方法により形成したTFTをその表示部1343および駆動回路に用いることにより作製される。なお、テレビジョンには液晶テレビ、有機ELテレビなどがある。本発明により、安価な表示部を有し、且つ、信頼性の高いテレビジョン、特に22インチ~50インチの大画面を有する大型のテレビジョンを実現することができる。

**【0109】**

また、図14で示す携帯電話機は、操作スイッチ類1404、マイクロフォン1405などが備えられた本体(A)1401と、表示パネル(A)1408、表示パネル(B)1409、スピーカ1406などが備えられた本体(B)1402とが、蝶番1410で開閉可能に連結している。表示パネル(A)1408と表示パネル(B)1409は、回路基板1407と共に本体(B)1402の筐体1403の中に収納される。表示パネル(A)1408及び表示パネル(B)1409の画素部は筐体1403に形成された開口窓から視認できるように配置される。

**【0110】**

表示パネル(A)1408と表示パネル(B)1409は、その携帯電話機1400の機能に応じて画素数などの仕様を適宜設定することができる。例えば、表示パネル(A)1408を主画面とし、表示パネル(B)1409を副画面として組み合わせることができる。

**【0111】**

本発明により、安価な表示部を有し、且つ、信頼性の高い携帯情報端末を実現することができる。

**【0112】**

本実施の形態に係る携帯電話機は、その機能や用途に応じてさまざまな態様に変容し得る。例えば、蝶番1410の部位に撮像素子を組み込んで、カメラ付きの携帯電話機としても良い。また、操作スイッチ類1404、表示パネル(A)1408、表示パネル(B)1409を一つの筐体内に納めた構成としても、上記した作用効果を奏することができる。また、表示部を複数個そなえた情報表示端末に本実施の形態の構成を適用しても、同様な効果を得ることができる。

**【0113】**

以上の様に、本発明を実施する、即ち実施の形態1乃至4のいずれか一の作製方法または構成を用いて、様々な電子機器を完成させることができる。

**【図面の簡単な説明】****【0114】**

【図1】本発明の画素の上面図を示す図。

【図2】本発明の端子部の上面図を示す図。

【図3】本発明の容量部の断面図を示す図。

【図4】本発明によるアクティブマトリクス基板の作製工程を示す断面図。

【図5】本発明によるアクティブマトリクス基板の作製工程を示す断面図。

【図6】本発明によるアクティブマトリクス基板の作製工程を示す断面図。

10

20

30

40

50

【図7】本発明によるアクティブマトリクス基板の作製工程を示す断面図。

【図8】本発明によるアクティブマトリクス基板の作製工程を示す断面図。

【図9】本発明によるアクティブマトリクス基板の断面図を示す図。

【図10】本発明によるアクティブマトリクス基板の断面図を示す図。

【図11】液晶表示装置の実装を示す図。

【図12】液晶表示装置の実装を示す図。

【図13】電子機器の一例を示す図。

【図14】電子機器の一例を示す図。

【符号の説明】

【0115】

10

10 TFT部

20 容量部

30 端子部

101 基板

102 第1の導電層

103a ゲート配線

103b 容量線

103c 電極

104 第1の絶縁層

105a ゲート絶縁層

20

105b 絶縁層

106 第1の非晶質半導体層

107a 島状の第1の非晶質半導体層

107b 島状の第1の非晶質半導体層

108 一導電型の不純物元素を含有する第2の非晶質半導体層

109a 島状の一導電型の不純物元素を含有する第2の非晶質半導体層

109b 島状の一導電型の不純物元素を含有する第2の非晶質半導体層

110a フォトレジストパターン

30

110b フォトレジストパターン

110c フォトレジストパターン

110d フォトレジストパターン

111a フォトレジストパターン

111b フォトレジストパターン

111c フォトレジストパターン

112 第2の絶縁層

113a サイドウォール

113b サイドウォール

113c サイドウォール

113d サイドウォール

113e サイドウォール

40

113f サイドウォール

113g サイドウォール

114 透明導電層

115a 透明導電層

115b 透明導電層

115c 電極

115d 電極

115e 電極

115f 画素電極

116 金属層

50

|         |                         |    |

|---------|-------------------------|----|

| 1 1 7 a | 金属層                     |    |

| 1 1 7 b | 金属層                     |    |

| 1 1 7 c | 金属層                     |    |

| 1 1 7 d | 金属層                     |    |

| 1 1 7 e | 金属層                     |    |

| 1 1 8   | 第2の導電層                  |    |

| 1 1 9 a | ソース配線                   |    |

| 1 1 9 b | ソース電極又はドレイン電極           |    |

| 1 2 0 a | フォトレジストパターン             | 10 |

| 1 2 0 b | フォトレジストパターン             |    |

| 1 2 0 c | フォトレジストパターン             |    |

| 1 2 0 d | フォトレジストパターン             |    |

| 1 2 0 e | フォトレジストパターン             |    |

| 1 2 1 a | フォトレジストパターン             |    |

| 1 2 1 b | フォトレジストパターン             |    |

| 1 2 1 c | フォトレジストパターン             |    |

| 1 2 1 d | フォトレジストパターン             |    |

| 1 2 1 e | フォトレジストパターン             |    |

| 1 2 2   | 第3の絶縁層                  |    |

| 1 2 3 a | 保護絶縁層                   | 20 |

| 1 2 3 b | 保護絶縁層                   |    |

| 1 2 3 c | 保護絶縁層                   |    |

| 1 2 3 d | 保護絶縁層                   |    |

| 1 2 4 a | フォトレジストパターン             |    |

| 1 2 4 b | フォトレジストパターン             |    |

| 1 2 4 c | フォトレジストパターン             |    |

| 1 2 4 d | フォトレジストパターン             |    |

| 1 2 5 a | フォトレジストパターン             |    |

| 1 2 5 b | フォトレジストパターン             |    |

| 1 2 5 c | フォトレジストパターン             | 30 |

| 1 2 5 d | フォトレジストパターン             |    |

| 1 2 6   | 第1の微結晶半導体層              |    |

| 1 2 7   | 第1の非晶質半導体層              |    |

| 1 2 8   | 一導電型の不純物元素を含有させた微結晶半導体層 |    |

| 1 2 9   | ポジ型感光性材料パターン            |    |

| 1 1 0 0 | 第1の基板                   |    |

| 1 1 0 1 | I Cチップ貼り合わせ領域           |    |

| 1 1 0 2 | I Cチップ貼り合わせ領域           |    |

| 1 1 0 3 | 画素領域                    |    |

| 1 1 0 4 | 外部入出力端子                 | 40 |

| 1 1 0 5 | 接続配線                    |    |

| 1 1 0 6 | I Cチップ                  |    |

| 1 1 0 7 | I Cチップ                  |    |

| 1 1 0 8 | 第2の基板                   |    |

| 1 1 0 9 | 対向電極                    |    |

| 1 1 1 0 | シール材                    |    |

| 1 1 1 1 | 液晶層                     |    |

| 1 1 1 2 | F P C                   |    |

| 1 1 1 3 | 補強板                     |    |

| 1 2 0 1 | 第1の基板                   | 50 |

|         |                      |    |

|---------|----------------------|----|

| 1 2 0 2 | 第 2 の基板              |    |

| 1 2 0 3 | シール材                 |    |

| 1 2 0 4 | 液晶層                  |    |

| 1 2 0 5 | 引出線                  |    |

| 1 2 0 6 | 接続配線及び入出力端子          |    |

| 1 2 0 7 | I C チップ              |    |

| 1 2 0 8 | 入出力端子                |    |

| 1 2 0 9 | 導電性粒子                |    |

| 1 2 1 0 | 樹脂                   | 10 |

| 1 2 1 1 | F P C                |    |

| 1 2 1 2 | 配線                   |    |

| 1 2 1 3 | 導電性粒子                |    |

| 1 2 1 4 | 樹脂                   |    |

| 1 2 1 5 | 接着材                  |    |

| 1 2 1 6 | A u ワイヤ              |    |

| 1 2 1 7 | 樹脂                   |    |

| 1 3 1 1 | 本体                   |    |

| 1 3 1 2 | 表示部                  |    |

| 1 3 1 4 | 操作キー                 |    |

| 1 3 1 6 | シャッター ボタン            | 20 |

| 1 3 2 1 | 本体                   |    |

| 1 3 2 2 | 筐体                   |    |

| 1 3 2 3 | 表示部                  |    |

| 1 3 2 4 | キー ボード               |    |

| 1 3 2 5 | 外部接続ポート              |    |

| 1 3 2 6 | ポインティングデバイス          |    |

| 1 3 3 1 | 本体                   |    |

| 1 3 3 2 | 筐体                   |    |

| 1 3 3 3 | 第 1 の表示部             |    |

| 1 3 3 4 | 第 2 の表示部             | 30 |

| 1 3 3 5 | 記録媒体 ( D V D 等 ) 読込部 |    |

| 1 3 3 6 | 操作キー                 |    |

| 1 3 3 7 | スピーカ部                |    |

| 1 3 4 1 | 筐体                   |    |

| 1 3 4 2 | 支持台                  |    |

| 1 3 4 3 | 表示部                  |    |

| 1 3 4 4 | スピーカ                 |    |

| 1 3 4 5 | ビデオ入力端子              |    |

| 1 4 0 0 | 携帯電話機                |    |

| 1 4 0 1 | 本体 ( A )             | 40 |

| 1 4 0 2 | 本体 ( B )             |    |

| 1 4 0 3 | 筐体                   |    |

| 1 4 0 4 | 操作スイッチ類              |    |

| 1 4 0 5 | マイクロフォン              |    |

| 1 4 0 6 | スピーカ                 |    |

| 1 4 0 7 | 回路基板                 |    |

| 1 4 0 8 | 表示パネル ( A )          |    |

| 1 4 0 9 | 表示パネル ( B )          |    |

| 1 4 1 0 | 蝶番                   |    |

【図1】

【図3】

【図2】

(a)

(b)

【図4】

【図5】

【図6】

【 四 7 】

【図8】

【図9】

【 10 】

【図11】

【図12】

【図13】

【図14】

---

フロントページの続き

(56)参考文献 特開2002-333845(JP,A)

特開平09-092838(JP,A)

特開2007-189120(JP,A)

特開2003-179069(JP,A)

(58)調査した分野(Int.Cl., DB名)

G02F 1/1368

H01L 21/336

H01L 29/786