(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5117791号

(P5117791)

(45) 発行日 平成25年1月16日(2013.1.16)

(24) 登録日 平成24年10月26日(2012.10.26)

|                          |                |

|--------------------------|----------------|

| (51) Int.Cl.             | F 1            |

| HO 1 L 21/3205 (2006.01) | HO 1 L 21/88 S |

| HO 1 L 21/768 (2006.01)  | HO 1 L 27/04 H |

| HO 1 L 23/522 (2006.01)  |                |

| HO 1 L 21/822 (2006.01)  |                |

| HO 1 L 27/04 (2006.01)   |                |

請求項の数 9 (全 27 頁)

|           |                              |

|-----------|------------------------------|

| (21) 出願番号 | 特願2007-216217 (P2007-216217) |

| (22) 出願日  | 平成19年8月22日 (2007.8.22)       |

| (65) 公開番号 | 特開2009-49313 (P2009-49313A)  |

| (43) 公開日  | 平成21年3月5日 (2009.3.5)         |

| 審査請求日     | 平成22年5月14日 (2010.5.14)       |

|           |                                                      |

|-----------|------------------------------------------------------|

| (73) 特許権者 | 302062931<br>ルネサスエレクトロニクス株式会社<br>神奈川県川崎市中原区下沼部1753番地 |

| (74) 代理人  | 100110928<br>弁理士 速水 進治                               |

| (72) 発明者  | 宇佐美 達矢<br>神奈川県川崎市中原区下沼部1753番地<br>NECエレクトロニクス株式会社内    |

審査官 崎間 伸洋

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

基板と、

前記基板上に形成され、ビアおよび配線が形成される素子形成領域と、

前記基板上に形成され、平面視において前記素子形成領域を囲むように当該素子形成領域の外周に形成されたシールリングと、

を含み、

前記シールリングは、平面視において前記素子形成領域を囲むように形成された貫通孔を有する第1のメタル層と、前記第1のメタル層上に当該第1のメタル層に接して形成された第2のメタル層と、を含み、

前記第1のメタル層の前記貫通孔の下部分には絶縁性材料が形成され、当該貫通孔の前記絶縁性材料が形成された箇所以外の上部分には前記第2のメタル層を構成するメタル材料がくい込んで形成され、

前記第1のメタル層の前記貫通孔は、平面視で複数の貫通孔が前記素子形成領域を囲むように分散配置されることにより構成され、前記複数の貫通孔の下部分にはそれぞれ前記絶縁性材料が形成され、当該複数の貫通孔の前記絶縁性材料が形成された箇所以外の上部分には、それぞれ前記第2のメタル層がくい込んで形成された半導体装置。

## 【請求項 2】

基板と、

前記基板上に形成され、ビアおよび配線が形成される素子形成領域と、

10

20

前記基板上に形成され、平面視において前記素子形成領域を囲むように当該素子形成領域の外周に形成されたシールリングと、

を含み、

前記シールリングは、平面視において前記素子形成領域を囲むように形成された貫通孔を有する第1のメタル層と、前記第1のメタル層上に当該第1のメタル層に接して形成された第2のメタル層と、を含み、

前記第1のメタル層の前記貫通孔の下部分には絶縁性材料が形成され、当該貫通孔の前記絶縁性材料が形成された箇所以外の上部分には前記第2のメタル層を構成するメタル材料がくい込んで形成され、

前記シールリングは前記第2のメタル層上に、当該第2のメタル層に接して形成された第3のメタル層をさらに含み、 10

前記第2のメタル層は、平面視において前記第1のメタル層の前記貫通孔とは重ならない位置において、前記素子形成領域を囲むように形成された貫通孔を有し、当該貫通孔の下部分には絶縁性材料が形成され、当該貫通孔の前記絶縁性材料が形成された箇所以外の上部分には前記第3のメタル層を構成するメタル材料がくい込んで形成され、

前記第2のメタル層の前記貫通孔は、平面視で複数の貫通孔が前記素子形成領域を囲むように分散配置されることにより構成され、前記複数の貫通孔の下部分にはそれぞれ前記絶縁性材料が形成され、当該複数の貫通孔の前記絶縁性材料が形成された箇所以外の上部分には、それぞれ前記第3のメタル層がくい込んで形成された半導体装置。

**【請求項3】**

20

基板と、

前記基板上に形成され、ピアおよび配線が形成される素子形成領域と、

前記基板上に形成され、平面視において前記素子形成領域を囲むように当該素子形成領域の外周に形成されたシールリングと、

を含み、

前記シールリングは、平面視において前記素子形成領域を囲むように形成された貫通孔を有する第1のメタル層と、前記第1のメタル層上に当該第1のメタル層に接して形成された第2のメタル層と、を含み、

前記第1のメタル層の前記貫通孔の下部分には絶縁性材料が形成され、当該貫通孔の前記絶縁性材料が形成された箇所以外の上部分には前記第2のメタル層を構成するメタル材料がくい込んで形成され、 30

前記シールリングは前記第2のメタル層上に、当該第2のメタル層に接して形成された第3のメタル層をさらに含み、

前記第2のメタル層は、平面視において前記第1のメタル層の前記貫通孔とは重ならない位置において、前記素子形成領域を囲むように形成された貫通孔を有し、当該貫通孔の下部分には絶縁性材料が形成され、当該貫通孔の前記絶縁性材料が形成された箇所以外の上部分には前記第3のメタル層を構成するメタル材料がくい込んで形成され、

前記シールリングは、前記第1のメタル層下に、当該第1のメタル層に接して形成された下層メタル層をさらに含み、

前記シールリングは、内周から外周に延在する直線で切断した断面において、前記下層メタル層、前記第1のメタル層、前記第2のメタル層、および前記第3のメタル層をそれぞれ構成するメタル材料中に前記絶縁性材料が島状に分散配置された構造を有する半導体装置。 40

**【請求項4】**

請求項2または3に記載の半導体装置において、

前記第1のメタル層の前記貫通孔は、平面視で複数の貫通孔が前記素子形成領域を囲むように分散配置されることにより構成され、前記複数の貫通孔の下部分にはそれぞれ前記絶縁性材料が形成され、当該複数の貫通孔の前記絶縁性材料が形成された箇所以外の上部分には、それぞれ前記第2のメタル層がくい込んで形成された半導体装置。

**【請求項5】**

50

請求項 1、請求項 2 に従属する請求項 4、請求項 3 に従属する請求項 4 いずれかに記載の半導体装置において、

前記第 1 のメタル層の前記複数の貫通孔は、平面視において格子状に配置された半導体装置。

【請求項 6】

請求項 1 または請求項 1 に従属する請求項 5 に記載の半導体装置において、

前記シールリングは前記第 2 のメタル層上に、当該第 2 のメタル層に接して形成された第 3 のメタル層をさらに含み、

前記第 2 のメタル層は、平面視において前記第 1 のメタル層の前記貫通孔とは重ならない位置において、前記素子形成領域を囲むように形成された貫通孔を有し、当該貫通孔の下部分には絶縁性材料が形成され、当該貫通孔の前記絶縁性材料が形成された箇所以外の上部分には前記第 3 のメタル層を構成するメタル材料がくい込んで形成された半導体装置。

10

【請求項 7】

請求項 2、請求項 2 に従属する請求項 4、請求項 2 に従属する請求項 4 に従属する請求項 5 いずれかに記載の半導体装置において、

前記第 2 のメタル層の前記複数の貫通孔は、平面視において格子状に配置された半導体装置。

【請求項 8】

請求項 2、7、請求項 2 に従属する請求項 4、請求項 2 に従属する請求項 4 に従属する請求項 5 いずれかに記載の半導体装置において、

20

前記シールリングは、前記第 1 のメタル層下に、当該第 1 のメタル層に接して形成された下層メタル層をさらに含み、

前記シールリングは、内周から外周に延在する直線で切断した断面において、前記下層メタル層、前記第 1 のメタル層、前記第 2 のメタル層、および前記第 3 のメタル層をそれぞれ構成するメタル材料中に前記絶縁性材料が島状に分散配置された構造を有する半導体装置。

【請求項 9】

請求項 2 から 4、6 から 8、請求項 2 に従属する請求項 4 に従属する請求項 5、請求項 3 に従属する請求項 4 に従属する請求項 5 いずれかに記載の半導体装置において、

30

前記シールリングは、内周から外周に延在する直線で切断した断面において、内周から外周の方向に、前記第 1 のメタル層の前記貫通孔が形成された列と前記第 2 のメタル層の前記貫通孔が形成された列とが交互に配置された半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置およびその製造方法に関する。

【背景技術】

【0002】

近年、半導体装置の高性能化が進むとともに、半導体装置製造プロセスにおいて、比誘電率が  $\text{SiO}_2$  より低い、いわゆる「low-k膜（低誘電率絶縁膜）」と呼ばれる絶縁膜形成技術が導入されるようになっている。この「low-k膜」には様々な種類があるが、一般的に密着性や機械強度が弱い。そのため、ウェハのダイシング工程で発生する膜剥離やクラックの伝播を防止できないという問題があった。

40

【0003】

図 26 は、従来のシールリング構造を示す図である。シールリングは、低誘電率膜への水分の侵入を防止するために半導体チップの周辺に沿って設けられる隔壁で、通常は配線層によって形成される。図 26 (a) は、半導体装置 10 の横断平面図、図 26 (b) は、半導体装置 10 の縦断正面図である。図 26 (b) は、図 26 (a) の H - H' 断面図に該当する。

50

## 【0004】

半導体装置10は、たとえばシリコン基板である基板12、たとえばSiO<sub>2</sub>膜である下層絶縁膜14、および低誘電率膜を含む層間絶縁膜16がこの順で積層された構造を有する。図中、破線の左側はチップ内部、破線の右側はシールリング部である。シールリング部のさらに外周に、ダイシングライン(不図示)が存在する。素子形成領域であるチップ内部において、層間絶縁膜16中には、配線層32およびビア層30がこの順で交互に形成される。また、シールリング部において、下層絶縁膜14中にはWシールリング34が、層間絶縁膜16中には、配線層24およびビア層22がこの順で交互に形成される。配線層24およびビア層22は、チップ内部の配線層32とビア層30とそれぞれ同層に形成される。また、配線およびビアは、バリアメタル膜18および銅含有メタル膜20により構成される。

## 【0005】

しかし、このような構成において、図中右側のダイシングライン側からクラックや膜剥離40が発生すると、このクラックや膜剥離40がビアと配線との間の部分で内部に伝播し、チップ内部のクラックや膜剥離に発展するという問題があった。

## 【0006】

特許文献1(特開2006-5011号公報)には、幅が広いシールリング配線内に複数の縞状の絶縁体が形成された構成が記載されている。これにより、配線形成時のCMP時に幅が広いシールリング配線内でディッキングおよびエロージョンが生じるのを防ぎ、配線間の短絡発生をなくすようにした構成が記載されている。

## 【0007】

特許文献2(特開2005-167198号公報)には、シールリングにおいて、デュアルダマシン配線を構成するビアおよび配線が設けられている層間絶縁膜につなぎ目のないシールビアが設けられた構成が記載されている。このシールリング部のつなぎ目の数を低減させた構造を用いることにより、つなぎ目が多いシールリング構造と比較して、つなぎ目からの不純物等の侵入を効果的に防ぐことができ、強固なシールリング構造を実現できるとされている。

【特許文献1】特開2006-5011号公報

【特許文献2】特開2005-167198号公報

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0008】

しかし、特許文献1に記載の技術では、シールリング部においても、素子形成層のビア層と配線層と同じ高さにビア層と配線層とが交互に形成されており、シールリングのつなぎ目がその周囲の絶縁膜の接面と同じ高さとなっている。そのため、外周からの剥離やクラックを内部に伝播してしまうという課題が解決できていない。

## 【0009】

また、特許文献2に記載の技術では、つなぎ目の数を低減しているが、シールリングのつなぎ目は、チップ領域の配線とビアとのつなぎ目と同じ高さに設けられており、さらにその周囲の絶縁膜の接面と同じ高さとなっている。そのため、膜剥離が生じた場合に、シールリングのつなぎ目に外周からの剥離やクラックが伝達するとともに内部にも伝播してしまうという課題が解決できない。

## 【課題を解決するための手段】

## 【0010】

本発明によれば、

基板と、

前記基板上に形成され、ビアおよび配線が形成される素子形成領域と、

前記基板上に形成され、平面視において前記素子形成領域を囲むように当該素子形成領域の外周に形成されたシールリングと、

を含み、

10

20

30

40

50

前記シールリングは、平面視において前記素子形成領域を囲むように形成された貫通孔を有する第1のメタル層と、前記第1のメタル層上に当該第1のメタル層に接して形成された第2のメタル層と、を含み、

前記第1のメタル層の前記貫通孔の下部分には絶縁性材料が形成され、当該貫通孔の前記絶縁性材料が形成された箇所以外の上部分には前記第2のメタル層を構成するメタル材料がくい込んで形成された半導体装置が提供される。

#### 【0011】

本発明によれば、

素子形成領域と、当該素子形成領域を囲むように当該素子形成領域の外周に形成されたシールリング部と、を含む半導体装置の製造方法であって、

10

基板上に形成された第1の絶縁膜に、前記素子形成領域においてビアまたは配線を形成するための第1の溝、および前記シールリング部において平面視で前記素子形成領域を取り囲むように第1のシールリング溝を形成する工程と、

前記第1の溝および前記第1のシールリング溝をメタル材料で埋め込み、次いで前記第1の溝および前記第1のシールリング溝外部に露出した前記メタル材料を除去することにより、前記第1の溝内にビアまたは配線を形成するとともに、前記第1のシールリング溝内に第1のメタル層を形成する工程と、

前記第1の絶縁膜上に第2の絶縁膜を形成する工程と、

前記第2の絶縁膜に、前記素子形成領域においてビアまたは配線を形成するための第2の溝、および前記シールリング部において前記第1のシールリング溝上に第2のシールリング溝を形成する工程と、

20

前記第2の溝および前記第2のシールリング溝をメタル材料で埋め込み、次いで前記第2の溝および前記第2のシールリング溝外部に露出した前記メタル材料を除去することにより、前記第2の溝内にビアまたは配線を形成するとともに、前記第2のシールリング溝内に、前記第1のメタル層に接する第2のメタル層を形成する工程と、

を含み、

前記第1のシールリング溝を形成する工程において、当該第1のシールリング溝は、当該第1のシールリング溝内に、前記第1の絶縁膜を残して形成され、

前記第1のシールリング溝内に第1のメタル層を形成する工程において、前記第1のシールリング溝に残して形成された前記第1の絶縁膜により、当該第1のメタル層には貫通孔が形成され、

30

前記第2のシールリング溝を形成する工程において、前記第2のシールリング溝底面に前記第1の絶縁膜が露出した後、当該露出した前記第1の絶縁膜の上部分を除去して、前記第1のメタル層の前記貫通孔の下部分に前記第1の絶縁膜を残し、

前記第2のメタル層を形成する工程において、前記第1のメタル層の前記貫通孔の上部分に、当該第2のメタル層をくい込ませる半導体装置の製造方法が提供される。

#### 【0012】

素子形成領域は、略四辺形を有する構成とすることができます、シールリングは、素子形成領域の四方を囲む構成とすることができる。さらに、シールリングの外周にダイシングラインが設けられる。

40

#### 【0013】

本発明の構成によれば、第2のメタル層が第1のメタル層に接して形成されるとともに、第2のメタル層を構成するメタル材料が第1のメタル層の貫通孔内にくい込んでいる。すなわち、シールリングは、貫通孔の下部分に絶縁性材料が形成されている以外はすべてメタル材料により構成されている。そのため、メタル層間の接触面積が大きくなり、メタル層間の密着性を高めることができ、ダイシング工程で発生する膜剥離やクラックがチップ内部の素子形成領域に伝搬するのを防ぐことができる。また、耐湿性を高めることができる。これにより、半導体装置の歩留まりを向上させることができる。

#### 【0014】

また、第2のメタル層を構成するメタル材料が第1のメタル層の貫通孔内にくい込むと

50

ともに、貫通孔の下部分には絶縁性材料が形成されている。すなわち、第2のメタル層の底面には、下方に突出する凸部が形成されており、その凸部が第1のメタル層に形成された貫通孔内に嵌め込まれた構成となっている。そのため、第2のメタル層の貫通孔内の底面は、第2のメタル層のそれ以外の領域の底面および第1のメタル層の貫通孔の底面とは異なる高さに位置することになり、メタル層間の接面に段差が生じている。このような構成によれば、ダイシング時の衝撃で生じる水平方向の応力がシールリングに伝搬されて、たとえば第1のメタル層と第2のメタル層との間にクラックが生じても、そのクラックは、第1のメタル層の貫通孔内に伝搬した後、当該貫通孔内で第1のメタル層の壁面で止められ、それ以上のクラックの進行を防ぐことができる。これにより、半導体装置の歩留まりを向上させることができる。

10

#### 【0015】

また、本発明のシールリングは、多層配線構造の配線およびビアをシングルダマシンプロセスまたはデュアルダマシンプロセスで作成するのと同時に、シールリング部において素子形成領域のパターンと異なるパターンを形成するようにするだけで、新たな工程を追加することなく製造することができる。さらに、シールリング部において、シールリング形成用の溝を形成する際に、当該溝内に絶縁膜が残されるので、メタル材料をCMPにより除去する際のディッキングを防ぐことができる。

#### 【発明の効果】

#### 【0016】

本発明によれば、ダイシング工程で発生する膜剥離やクラックがチップ内部に伝播するのを防ぐことにより、半導体装置の歩留まりを向上させることができる。

20

#### 【発明を実施するための最良の形態】

#### 【0017】

以下、本発明の実施の形態について、図面を用いて説明する。尚、すべての図面において、同様な構成要素には同様の符号を付し、適宜説明を省略する。

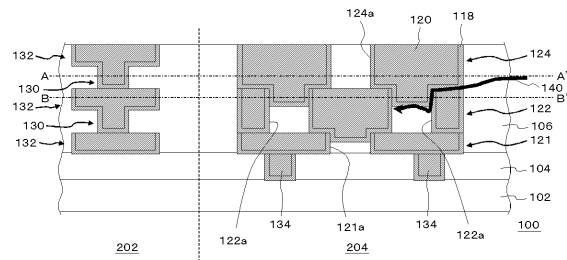

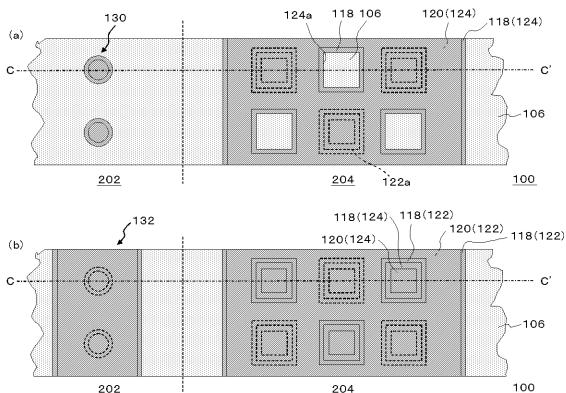

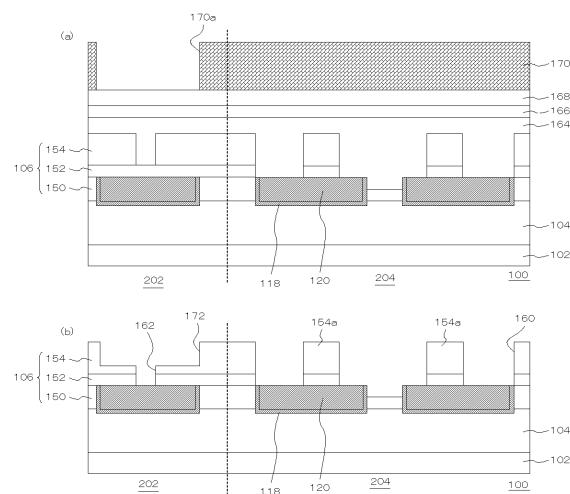

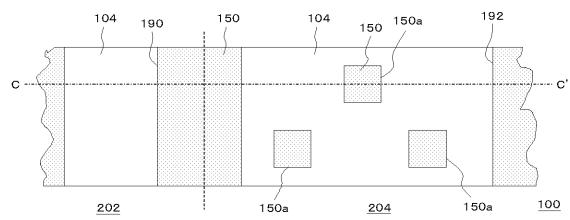

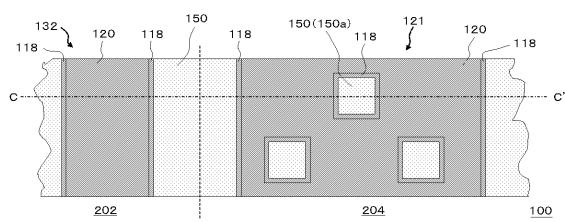

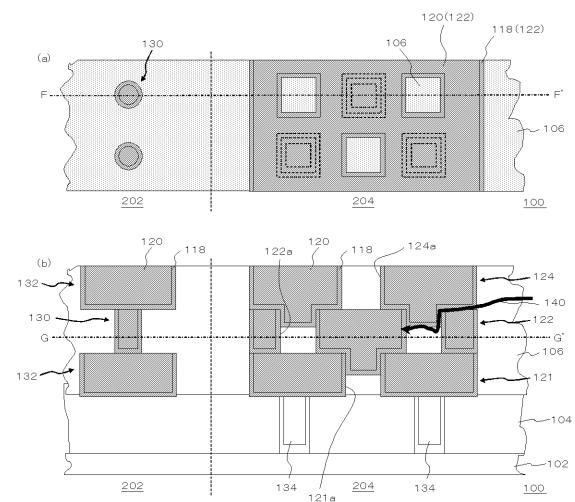

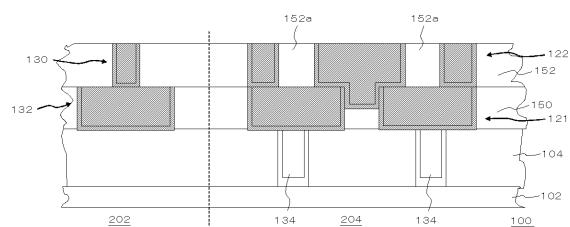

#### 【0018】

図1は、本実施の形態における半導体装置の構成を示す断面図である。図2は、図1に示した半導体装置100の横断平面図である。図2(a)は、図1のA-A'断面図、図2(b)は、図1のB-B'断面図に該当する。図1は、図2(a)および図2(b)のC-C'断面図に該当する。

30

#### 【0019】

半導体装置100は、たとえばシリコン基板の表面にトランジスタ等の素子(不図示)が形成されている基板102と、基板102上に形成された下層絶縁膜104と、下層絶縁膜104上に形成され、低誘電率膜を含む層間絶縁膜106とを含む。下層絶縁膜104は、たとえばSiO<sub>2</sub>膜により構成することができる。図中、破線の左側は素子形成領域であるチップ内部202、破線の右側はシールリング部204である。シールリング部204のさらに外周(図中右側)に、ダイシングラインが存在する。

#### 【0020】

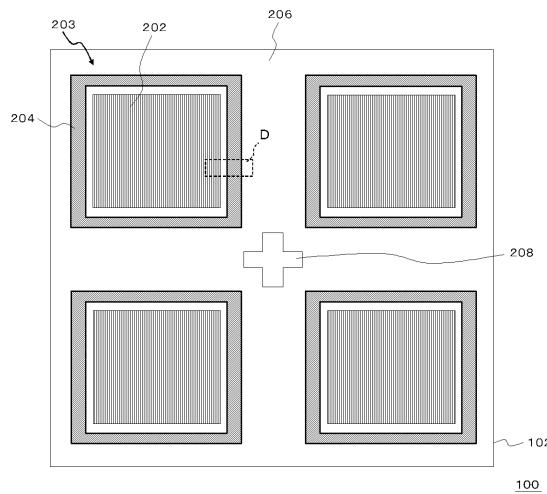

図3は、基板102上に複数のチップ203が形成された構成を示す平面図である。図3に示すように、各チップ203は略四辺形を有する。シールリング部204は、平面視においてチップ内部202を囲むようにチップ内部202の外周に形成される。また、ダイシングライン206は、平面視においてシールリング部204を囲むようにシールリング部204の外周に形成される。また、各チップ203の間には、アライメントマーク208が配置されている。図1および図2は、図3の破線Dで囲った部分を示す図である。

40

#### 【0021】

図1に戻り、チップ内部202において、層間絶縁膜106中には、配線層132およびビア層130がこの順で交互に形成される。ここでは、デュアルダマシン構造を有する配線を示している。

#### 【0022】

シールリング部204において、下層絶縁膜104には、W(タンゲステン)シールリ

50

ング134が形成される。さらに、シールリング部204において、層間絶縁膜106中には、下層メタル層121、第1のメタル層122、および第2のメタル層124がこの順で形成される。

【0023】

ここで、ピア層130、配線層132、下層メタル層121、第1のメタル層122、および第2のメタル層124は、それぞれバリアメタル膜118および銅含有メタル膜120により構成することができる。バリアメタル膜118は、高融点金属を含む構成とすることができる。バリアメタル膜118は、たとえば、Ta、Ta<sub>N</sub>、Ti、Ti<sub>N</sub>、W、WN等により構成することができる。銅含有メタル膜120は、銅を主成分として含むことができる。銅含有メタル膜120は、さらに、Ag、Al、Au、Pt、Cr、Mo、W、Mg、Be、Zn、Pd、Cd、Hg、Si、Zr、Ti、または、Snから選択される一又は二以上の異種元素を含む構成とすることもできる。銅含有メタル膜120は、たとえばめっき法により形成することができる。また、銅含有メタル膜120の表面は、たとえばシリサイド膜が形成された構成とすることもできる。

【0024】

本実施の形態において、下層メタル層121は、チップ内部202の層間絶縁膜106中の最下層の配線層132と同じ膜厚を有するように形成される。下層メタル層121は、平面視において島状に形成された複数の貫通孔121a（図1では1つのみ表示）を有する。第1のメタル層122は、下層メタル層121上に下層メタル層121に接して形成されるとともに、平面視において下層メタル層121の複数の貫通孔121aとは重ならない位置に島状に形成された複数の貫通孔122aを有する。ここで、下層メタル層121の複数の貫通孔121aの下部分にはそれぞれ層間絶縁膜106を構成する絶縁性材料が形成され、当該複数の貫通孔121aの絶縁性材料が形成された箇所以外の上部分にはそれぞれ第1のメタル層122を構成するメタル材料がくい込んで形成されている。すなわち、下層メタル層121の貫通孔121aは、下部分が絶縁性材料で埋め込まれ、上部分がメタル材料で埋め込まれている。本実施の形態において、第1のメタル層122は、下層メタル層121の貫通孔121aが形成された箇所では、チップ内部202のピア層130と配線層132との合計の膜厚と同じ膜厚を有する。

【0025】

第2のメタル層124は、第1のメタル層122上に第1のメタル層122に接して形成されるとともに、平面視において第1のメタル層122の複数の貫通孔122aとは重ならない位置に島状に形成された複数の貫通孔124a（図1では1つのみ表示）を有する。ここで、第1のメタル層122の複数の貫通孔122aの下部分にはそれぞれ層間絶縁膜106を構成する絶縁性材料が形成され、当該複数の貫通孔122aの絶縁性材料が形成された箇所以外の上部分にはそれぞれ第2のメタル層124を構成するメタル材料がくい込んで形成されている。すなわち、第1のメタル層122の貫通孔122aは、下部分が絶縁性材料で埋め込まれ、上部分がメタル材料で埋め込まれている。本実施の形態において、第2のメタル層124は、第1のメタル層122の貫通孔122aが形成された箇所では、チップ内部202のピア層130と配線層132との合計の膜厚と同じ膜厚を有する。

【0026】

なお、図示していないが、半導体装置100は、チップ内部202において、配線層132上にさらにピア層130および配線層132が順次交互に形成されるとともに、シールリング部204において、第2のメタル層124上にさらに第1のメタル層122および第2のメタル層124と同様の構成のメタル層（第3のメタル層）が順次交互に形成された構成とすることができる。シールリング部204において、このようなメタル層の積層構造により、シールリングが構成される。図1に示した例において、下層メタル層121の複数の貫通孔と、第2のメタル層124の複数の貫通孔とは、平面視において略等しい位置に形成されている。

【0027】

10

20

30

40

50

図2に示すように、第1のメタル層122の貫通孔122aおよび第2のメタル層124の貫通孔124aは、それぞれ、平面視において格子状に配置することができる。本実施の形態において、貫通孔122aおよび貫通孔124aは、それぞれ千鳥格子状に配置することができる。

【0028】

また、シールリング部204において、内周から外周に延在する直線(図2のC-C'直線)で切断した断面において、内周から外周の方向に、第1のメタル層122の貫通孔122aが形成された列と第2のメタル層124の貫通孔124aが形成された列とが交互に配置されている。また、図2の例では、シールリング部204の長軸方向(C-C'直線に垂直な方向)の断面においても、貫通孔122a(図2中破線で表示)が形成された列と貫通孔124aが形成された列とが交互に配置されている。 10

【0029】

さらに、シールリング部204では、内周から外周に延在する直線(図2のC-C'直線)で切断した断面(図1)において、層間絶縁膜106が分散配置された構造を有する。すなわち、本実施の形態において、シールリング部204では、図3で示した帯状のシールリング部204のほぼ全体がメタル材料により構成され、当該メタル材料中に絶縁性材料が水平方向および積層方向のいずれにおいても島状に分散配置された構造を有する。

【0030】

本実施の形態における半導体装置100の構成によれば、シールリングは、貫通孔の下部分に絶縁性材料が形成されている以外はすべてメタル材料により構成されている。そのため、メタル層間の接触面積が大きくなり、メタル層間の密着性を高めることができ、ダイシング工程で発生する膜剥離やクラックがチップ内部の素子形成領域に伝搬するのを防ぐことができる。また、耐湿性を高めることができる。これにより、半導体装置の歩留まりを向上させることができる。 20

【0031】

さらに、第2のメタル層124の底面には、下方に突出する凸部が形成されており、その凸部が第1のメタル層122に形成された貫通孔122a内に嵌め込まれた構成となっている。そのため、第2のメタル層124の底面に段差が生じ、第2のメタル層124が貫通孔122a内にくい込んだ部分の底面は、第1のメタル層122の貫通孔122aの底面とは異なる高さに位置することになる。このような構成によれば、図1に示したように、ダイシング時の衝撃で生じる水平方向の応力がシールリングに伝搬されて、たとえば第1のメタル層122と第2のメタル層124との間にクラックや膜剥離140が生じても、そのクラックや膜剥離140は、第1のメタル層122の貫通孔122a内に伝搬した後、貫通孔122a内において第2のメタル層124の壁面で止められ、それ以上のクラックや膜剥離140の進行を防ぐことができる。これにより、半導体装置100の歩留まりを向上させることができる。 30

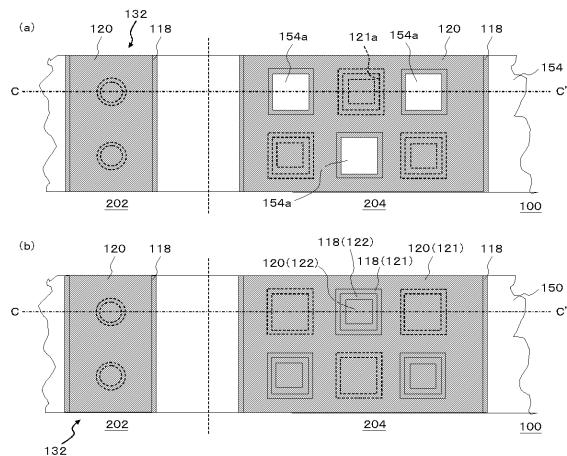

【0032】

なお、貫通孔122aおよび貫通孔124aは、種々の配置とすることができます。図25は、貫通孔122aおよび貫通孔124aの配置を模式的に示す平面図である。図1に示したように、貫通孔124aおよび貫通孔122aは、異なるメタル層に設けられているが、ここではわかりやすくするために貫通孔122aおよび貫通孔124aを同一平面上に示し、貫通孔122aを破線で示している。たとえば図25(a)に示したように、シールリング部204の長軸方向(図中縦方向)においては、列毎に貫通孔124aのみ、または貫通孔122aのみがそれぞれ配置されるようにすることもできる。 40

【0033】

さらに、図25(b)および図25(c)に示すように、平面視で同一列または同一行に配置される貫通孔は、厳密に一直線上に配置される必要はなく、貫通孔122aおよび貫通孔124aは、略格子状に配置されればよい。

【0034】

さらに、貫通孔122aおよび貫通孔124aは、必ずしも格子状に配置される必要は 50

なく、チップ内部 202 を囲むように配置されたシールリング部 204 において適宜分散配置されていればよい。すなわち、貫通孔 122a および貫通孔 124a は、第2のメタル層 124 の底面に分散配置して形成された複数の凸部が、貫通孔 122a 内に嵌め込まれ、さらに第2のメタル層 124 上に形成されるメタル層の底面に分散配置して形成された複数の凸部が貫通孔 124a に嵌め込まれる構成の繰り返し構造となつていれば、どのような配置となついてもよい。このような構成とすることにより、上述したのと同様、クラックや膜剥離がチップ内部 202 に伝搬するのを防ぐことができる。さらに、貫通孔 122a および貫通孔 124a は、略均等に分散配置されることが好ましい。これにより、後述する製造手順において、ディッキングを防ぐことができ、半導体装置の製造効率を高めることができる。なお、シールリング部 204 において、外部から伝搬されるクラックや膜剥離がチップ内部 202 に伝搬するのを防ぐためには、第1のメタル層 122 の貫通孔 122a および第2のメタル層 124 の貫通孔 124a は、それぞれ、チップ内部 202 の周囲全体を取り囲むように、チップ内部 202 の外周に略均等に設けられることが好ましい。10

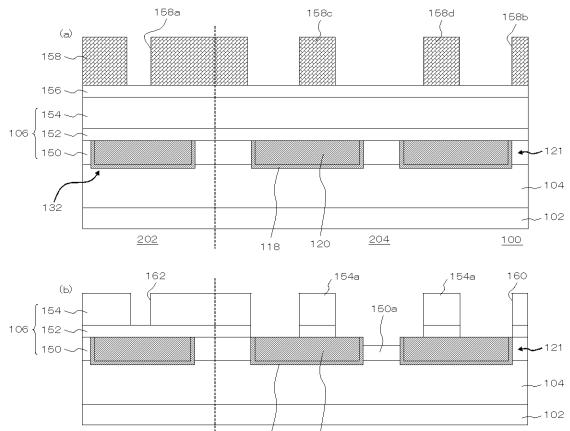

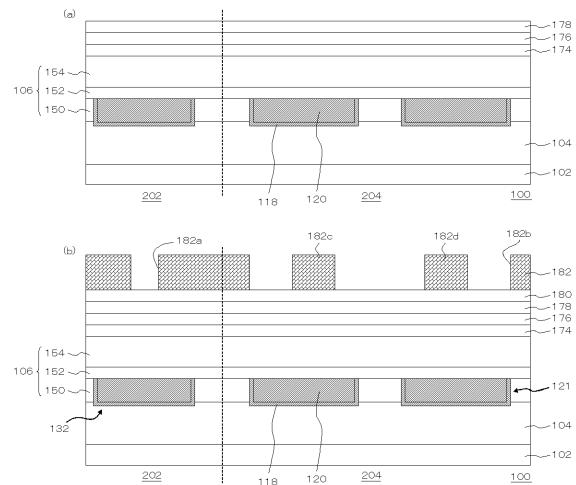

#### 【0035】

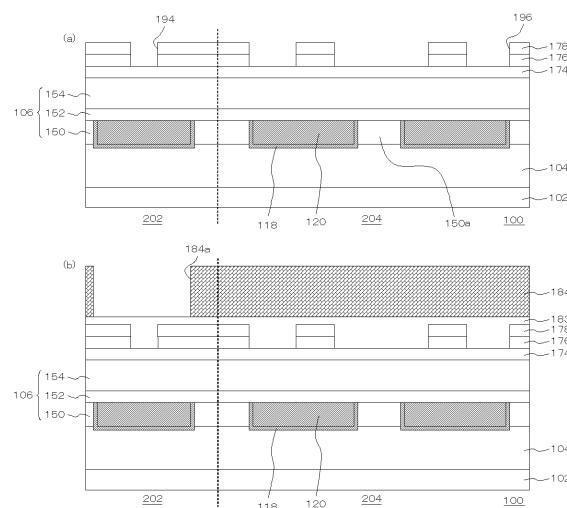

次に、図1および図2に示した半導体装置 100 の製造手順の一例を説明する。図4～図7は、半導体装置 100 の製造手順を示す工程断面図である。図8～図11は、半導体装置 100 の製造途中の構成を示す平面図である。ここでは、Wシールリング 134 の記載を省略しているが、半導体装置 100 の下層絶縁膜 104 中には、図1に示したように、Wシールリング 134 が形成された構成とすることができます。また、ここで、層間絶縁膜 106 は、第1の層間絶縁膜 150、第2の層間絶縁膜 152、および第3の層間絶縁膜 154 の積層構造により構成される。20

#### 【0036】

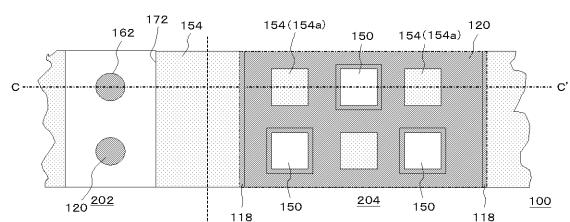

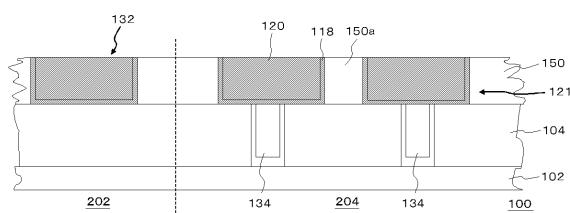

まず、図4(a)に示す構造の製造手順を説明する。下層絶縁膜 104 上に第1の層間絶縁膜 150 を形成する。次いで、第1の層間絶縁膜 150 上に反射防止膜および配線層 132 および下層メタル層 121 に対応するパターンを有するレジスト膜をこの順で形成し、レジスト膜および反射防止膜をマスクとして、第1の層間絶縁膜 150 をパターニングする。図8は、このときの第1の層間絶縁膜 150 の構成を示す平面図である。図中、白抜きの部分は、第1の層間絶縁膜 150 が除去され下層絶縁膜 104 が露出した箇所を示す。図中、ドットパターンの部分は、第1の層間絶縁膜 150 が除去されることなくそのまま残っている箇所を示す。チップ内部 202 においては、配線溝 190 が形成される。一方、シールリング部 204 においては、シールリング溝 192 が全体に形成され、その中に部分的に第1の層間絶縁膜 150 がエッチング除去されていない島状絶縁膜 150a が複数千鳥格子状に形成されている。30

#### 【0037】

つづいて、基板 102 上全面にバリアメタル膜 118 を形成する。これにより、配線溝 190 の内壁、シールリング溝 192 の内壁、および島状絶縁膜 150a の周囲にバリアメタル膜 118 が形成される。次いで、バリアメタル膜 118 上に銅含有メタル膜 120 を形成し、配線溝 190 およびシールリング溝 192 を銅含有メタル膜 120 により埋め込む。その後、CMPにより配線溝 190 およびシールリング溝 192 外に露出した銅含有メタル膜 120 およびバリアメタル膜 118 を除去する。このとき、CMP工程において、シールリング溝 192 中には島状絶縁膜 150a が形成されているため、ディッキングを防ぐことができる。これにより、配線層 132 および下層メタル層 121 が形成され、図9に示した構成となる。図4(a)は、図8および図9のC-C'断面部分に該当する。40

#### 【0038】

図4(a)に戻り、基板 102 上全面の第1の層間絶縁膜 150、配線層 132 および下層メタル層 121 上に、第2の層間絶縁膜 152 および第3の層間絶縁膜 154 をこの順で積層する。ここで、第1の層間絶縁膜 150 および第3の層間絶縁膜 154 は、SiOC 等の低誘電率膜により構成することができる。低誘電率絶縁膜は、たとえば比誘電率50

膜が3.3以下、好ましくは2.9以下の絶縁膜とすることができます。低誘電率膜としては、SiOCの他に、HSQ(ハイドロジエンシルセスキオキサン)、MSQ(メチルシルセスキオキサン)、またはMHSQ(メチル化ハイドロジエンシルセスキオキサン)等のポリハイドロジエンシロキサン、ポリアリールエーテル(PAE)、ジビニルシロキサンービスベンゾシクロブテン(BCB)、またはSilk(登録商標)等の芳香族含有有機材料、SOG、FOX(flowable oxide)、サイトップ、またはBCB(Benocyclobutene)等を用いることができる。また、低誘電率膜としては、これらのポーラス膜を用いることができる。第1の層間絶縁膜150および第3の層間絶縁膜154は、同じ材料により構成しても、異なる材料により構成してもいずれでもよい。

10

#### 【0039】

第2の層間絶縁膜152は、ビアホールや配線溝を形成する際のエッチング阻止膜として機能するとともに、銅含有メタル膜120中の銅の拡散を防止する機能を有する材料により構成することができる。第2の層間絶縁膜152は、たとえば、SiCN、SiN、SiC、SiOFまたはSiON等により構成することができる。

#### 【0040】

さらに、第3の層間絶縁膜154上に反射防止膜156および所定のパターンを有するレジスト膜158をこの順で積層する。これにより、図4(a)に示した構造となる。ここで、レジスト膜158は、チップ内部202ではビアホールに対応するパターン158aが開口したパターンを有する。レジスト膜158は、シールリング部204では、後述するシールリング溝160に対応するパターン158bが開口するとともに、シールリング溝160中で後述する島状絶縁膜154aが分散配置されるように島状絶縁膜154aをマスクする部分158cおよび158dを残したパターンを有する。

20

#### 【0041】

このように形成されたレジスト膜158および反射防止膜156をマスクとして、第3の層間絶縁膜154および第2の層間絶縁膜152をエッチングして、ビアホール162(第1の溝)およびシールリング溝160(第1のシールリング溝)を形成する。つづいて、レジスト膜158および反射防止膜156をアッシング等により除去する。このとき、シールリング溝160中には、島状絶縁膜154aが形成される(図4(b))。ここで、幅の狭いビアホール162においては、エッチングの進行も遅いため、第2の層間絶縁膜152が残っているが、幅が広いシールリング溝160においては、エッチングの進行が早く、第2の層間絶縁膜152もエッチングされる。このとき、第2の層間絶縁膜152の下に銅含有メタル膜120またはバリアメタル膜118が存在する場合は、これらのメタル膜がエッチング阻止膜として機能し、ここでエッチングが止まる。一方、第2の層間絶縁膜152の下に第1の層間絶縁膜150(島状絶縁膜150a)が存在する場合は、第2の層間絶縁膜152がエッチング除去された後、第1の層間絶縁膜150もエッチングされ、下層メタル層121の貫通孔中に凹部が形成される。

30

#### 【0042】

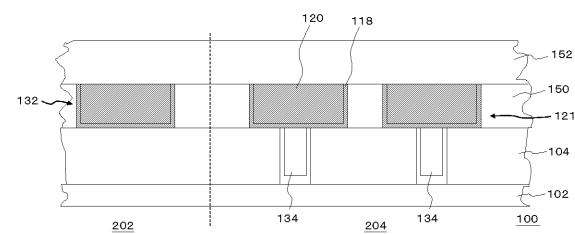

次いで、第3の層間絶縁膜154、第2の層間絶縁膜152、下層メタル層121、第1の層間絶縁膜150上の全面に、これらの間の段差がなくなるように下層レジスト膜164を形成する。さらに下層レジスト膜164上に、低温酸化膜(レジストが変質しない程度の低温、たとえば200で形成される酸化膜)166、反射防止膜168および所定パターンを有する上層レジスト膜170をこの順で積層する(図5(a))。ここで、上層レジスト膜170は、チップ内部202において配線溝に対応するパターン170aが開口したパターンを有する。このとき、上層レジスト膜170はシールリング部204には開口したパターンを有さない。そのため、以降のエッチング工程において、シールリング部204はエッチングされない。その後、上層レジスト膜170、反射防止膜168、低温酸化膜166および下層レジスト膜164をマスクとして、第3の層間絶縁膜154をエッチングして、配線溝172を形成する。これにより、チップ内部202にビアホール162および配線溝172により構成されたデュアルダマシン配線溝(第1の溝)が

40

50

形成される。つづいて、上層レジスト膜 170、反射防止膜 168、低温酸化膜 166、および下層レジスト膜 164 をアッシング等により除去する (図 5 (b))。

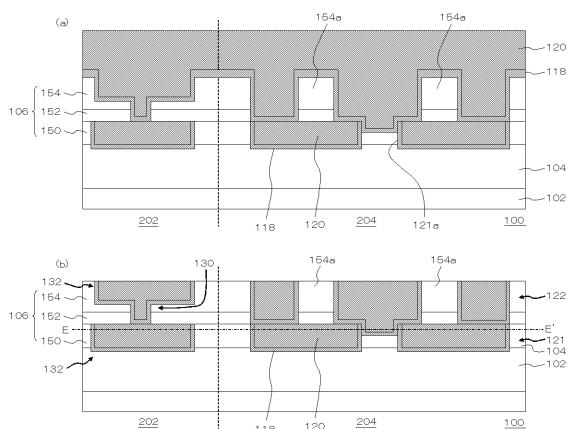

#### 【0043】

図 10 は、このときの半導体装置 100 の構成を示す平面図である。図 5 (b) は、図 10 の C - C' 断面図に該当する。図 10 において、図中、チップ内部 202 の白抜きの部分は、第 3 の層間絶縁膜 154 に配線溝 172 が形成された箇所を示す。図中、ドットパターンの部分は、第 3 の層間絶縁膜 154 が除去されることなくそのまま残っている箇所を示す。すなわち、チップ内部 202 において、ドットパターンで示した箇所も、白抜きで示した箇所も表面には第 3 の層間絶縁膜 154 が露出しているが、高さが異なっている。シールリング部 204 においては、シールリング溝 160 内では、バリアメタル膜 118 および銅含有メタル膜 120 が露出した箇所、および第 1 の層間絶縁膜 150 が露出した箇所が存在する。また、シールリング溝 160 中には、第 3 の層間絶縁膜 154 がエッティング除去されていない島状絶縁膜 154a が複数千鳥格子状に形成されている。10

#### 【0044】

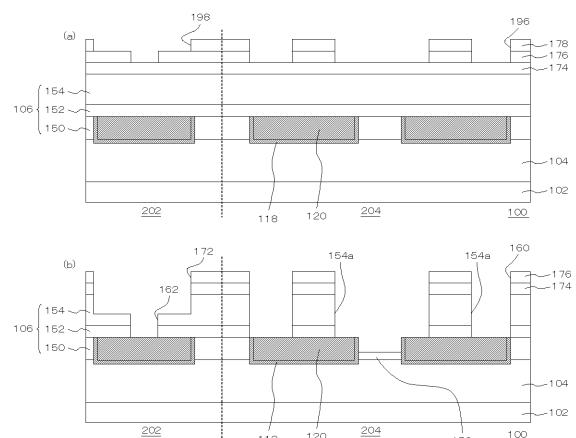

次いで、図 6 (a) に示すように、基板 102 上全面にバリアメタル膜 118 を形成する。これにより、配線溝 172 およびビアホール 162 の内壁、シールリング溝 160 の内壁、島状絶縁膜 154a の周囲および下層メタル層 121 の貫通孔の島状絶縁膜 150a が除去された上部分の内壁にバリアメタル膜 118 が形成される。次いで、バリアメタル膜 118 上に銅含有メタル膜 120 を形成し、配線溝 172 およびビアホール 162 ならびにシールリング溝 160 を銅含有メタル膜 120 により埋め込む。その後、CMP により配線溝 172 およびシールリング溝 160 外に露出した銅含有メタル膜 120 およびバリアメタル膜 118 を除去する。これにより、配線層 132 および第 1 のメタル層 122 が形成される (図 6 (b))。20 CMP 工程において、シールリング溝 160 内には島状絶縁膜 154a が形成されているため、ディッキングを防ぐことができる。

#### 【0045】

図 11 (a) は、図 6 (b) の状態を示す平面図、図 11 (b) は、図 6 (b) の E - E' 断面図である。図 6 (b) は、図 11 (a) および図 11 (b) の C - C' 断面図に該当する。

#### 【0046】

その後、基板 102 上全面に層間絶縁膜 152'、層間絶縁膜 154'、反射防止膜 156'、および所定のパターンを有するレジスト膜 158' を形成する。層間絶縁膜 152' および層間絶縁膜 154' は、それぞれ、上述した第 2 の層間絶縁膜 152 および第 3 の層間絶縁膜 154 と同様の材料により構成することができる。ここで、レジスト膜 158' は、チップ内部 202 ではビアホールに対応するパターン 158'a が開口したパターンを有する。レジスト膜 158' は、シールリング部 204 では、シールリング溝に対応するパターン 158'b が開口するとともに、シールリング溝中で、層間絶縁膜 154' が平面視で前述した島状絶縁膜 154a とは重ならない位置に島状に分散配置されるように層間絶縁膜 154' をマスクする部分 158'c を残したパターンを有する (図 7)。30 この後、レジスト膜 158' および反射防止膜 156' をマスクとして用いて、層間絶縁膜 154' および層間絶縁膜 152' をエッティングして、チップ内部 202 にビアホール (第 2 の溝)、シールリング部 204 にシールリング溝 (第 2 のシールリング溝) を形成する。次いで、第 1 のメタル層 122 を形成したのと同様の手順で、チップ内部 202 の層間絶縁膜 154' をエッティングして配線溝を形成し、デュアルダマシン配線溝 (第 2 の溝) を形成する。40 この後、溝をメタル材料で埋め込み、次いで溝外部に露出したメタル材料を除去することにより、チップ内部 202 にデュアルダマシン配線、シールリング部 204 に第 2 のメタル層 124 を形成する。以上により、図 1 に示した構造の半導体装置 100 が製造される。

#### 【0047】

以上のように、本実施の形態における半導体装置 100 の製造手順によれば、チップ内部 202 において多層配線構造の配線およびビアをデュアルダマシンプロセスで作成する50

のと同時に、シールリング部 204においてチップ内部202のパターンと異なるパターンを形成するようにするだけで、新たな工程を追加することなくシールリングを製造することができる。さらに、シールリング溝を形成する際に、当該溝内に絶縁膜が島状に残されるので、メタル材料をCMPにより除去する際のディッシングを防ぐことができる。

#### 【0048】

さらに、同様の処理を繰り返すことにより、配線層132上にさらにビア層130および配線層132が順次交互に形成されるとともに、シールリング部204において、第2のメタル層124上にさらに第1のメタル層122および第2のメタル層124と同様の構成のメタル層(第3のメタル層)が順次交互に形成された構成の半導体装置100を製造することができる。

10

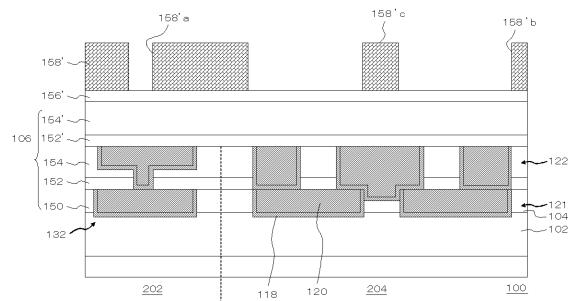

#### 【0049】

次に、図1および図2に示した半導体装置100の製造手順の他の例を説明する。図12～図15は、半導体装置100の製造手順を示す工程断面図である。ここでも、Wシールリング134の記載を省略しているが、半導体装置100の下層絶縁膜104中には、図1に示したように、Wシールリング134が形成された構成とすることができます。本例では、多層ハードマスクを用いてパターニングを行う点で、図4～図11を参照して説明した例と異なる。

#### 【0050】

まず、図4(a)を参照して説明したのと同様にして、第1の層間絶縁膜150中に配線層132および下層メタル層121を形成する。つづいて、第1の層間絶縁膜150、配線層132、および下層メタル層121上に第2の層間絶縁膜152および第3の層間絶縁膜154をこの順で積層する。次いで、第3の層間絶縁膜154上に第1のハードマスク174、第2のハードマスク176、および第3のハードマスク178を形成する(図12(a))。第1のハードマスク174、第2のハードマスク176、および第3のハードマスク178は、それぞれ、SiO<sub>2</sub>、SiN、SiCにより構成される。

20

#### 【0051】

その後、第3のハードマスク178上に反射防止膜180および所定のパターンを有するレジスト膜182をこの順で積層する(図12(b))。ここで、レジスト膜182は、チップ内部202ではビアホールに対応するパターン182aが開口したパターンを有する。レジスト膜182は、シールリング部204では、シールリング溝に対応するパターン182bが開口するとともに、シールリング溝中で後述する島状絶縁膜154aが分散配置されるように島状絶縁膜154aをマスクする部分182cおよび182dを残したパターンを有する。

30

#### 【0052】

このように形成されたレジスト膜182および反射防止膜180をマスクとして、第3のハードマスク178および第2のハードマスク176をエッチングして、ビアホールパターン194および開口部196を形成する。つづいて、レジスト膜182および反射防止膜180をアッシング等により除去する(図13(a))。

#### 【0053】

次いで、第1のハードマスク174、および第3のハードマスク178上の全面に、これらの間の段差をなくすように反射防止膜183を形成する。さらに反射防止膜183上に所定パターンを有するレジスト膜184を形成する(図13(b))。ここで、レジスト膜184は、チップ内部202において配線溝に対応するパターン184aが開口したパターンを有する。このとき、レジスト膜184はシールリング部204には開口したパターンを有さない。そのため、以降のエッチング工程において、シールリング部204はエッチングされない。その後、レジスト膜184および反射防止膜183をマスクとして、チップ内部202の第3のハードマスク178をエッチングして、配線溝パターン198を形成する(図14(a))。

40

#### 【0054】

次いで、まず第2のハードマスク176をマスクとして、下層をエッチングする。所定

50

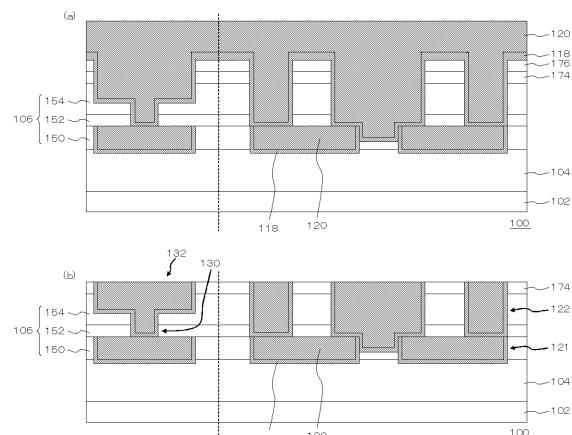

の深さエッティングされた後、第3のハードマスク178をマスクとして、下層をエッティングする。これにより、第2の層間絶縁膜152、および第3の層間絶縁膜154中に、チップ内部202においてはビアホール162および配線溝172により構成されたデュアルダマシン配線溝（第1の溝）が、シールリング部204においてはシールリング溝160（第1のシールリング溝）がそれぞれ形成される（図14（b））。このとき、第2の層間絶縁膜152の下に銅含有メタル膜120またはバリアメタル膜118が存在する場合は、これらのメタル膜がエッティング阻止膜として機能し、ここでエッティングが止まる。一方、第2の層間絶縁膜152の下に第1の層間絶縁膜150（島状絶縁膜150a）が存在する場合は、第2の層間絶縁膜152がエッティング除去された後、第1の層間絶縁膜150もエッティングされ、下層メタル層121の貫通孔中に凹部が形成される。また、シールリング溝160中には、第2のハードマスク176、第1のハードマスク174、第3の層間絶縁膜154および第2の層間絶縁膜152がエッティング除去されていない島状絶縁膜154aが複数千鳥状に形成されている。10

#### 【0055】

つづいて、基板102上全面にバリアメタル膜118を形成する。これにより、配線溝172およびビアホール162の内壁、シールリング溝160の内壁、島状絶縁膜154aの周囲および下層メタル層121の貫通孔の島状絶縁膜150aが除去された上部分の内壁にバリアメタル膜118が形成される。次いで、バリアメタル膜118上に銅含有メタル膜120を形成し、配線溝172およびビアホール162ならびにシールリング溝160を銅含有メタル膜120により埋め込む（図15（a））。その後、CMPにより配線溝172およびシールリング溝160外に露出した銅含有メタル膜120およびバリアメタル膜118、ならびに第2のハードマスク176を除去する（図15（b））。CMP工程において、シールリング溝160内には島状絶縁膜154aが形成されているため、ディッシングを防ぐことができる。20

#### 【0056】

この後、同様の手順を繰り返し、第1のメタル層122上に第2のメタル層124、さらにその上にメタル層を順次積層する。これにより、シールリング部204において、各メタル層の底面で下方に突出する凸部が下層のメタル層に形成された貫通孔内の上部分にくい込んだ構成のメタル層の積層構造を得ることができる。30

#### 【0057】

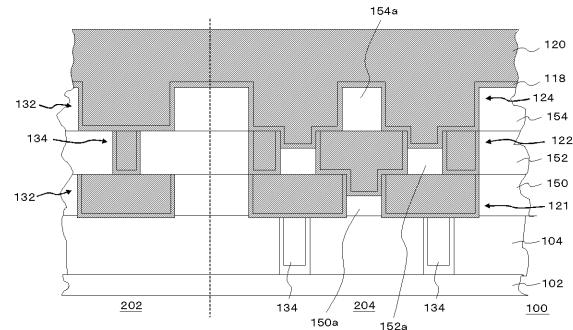

図16は、図1に示した半導体装置100の他の例を示す図である。図16（a）は、半導体装置100の横断平面図、図16（b）は、半導体装置100の縦断正面図である。図16（b）は、図16（a）のF-F'断面図に該当し、図16（a）は、図16（b）のG-G'断面図に該当する。30

#### 【0058】

本例では、チップ内部202のビア層130および配線層132がシングルダマシン構造を有する点で、図1に示した例と異なる。この例では、シールリング部204において、下層メタル層121、第1のメタル層122、および第2のメタル層124は、それぞれチップ内部202の配線層132、ビア層130、および配線層132と略等しい膜厚を有する。具体的には、下層メタル層121は、チップ内部202の配線層132と同じ膜厚を有する。第1のメタル層122は、下層メタル層121の貫通孔121aにくい込んだ箇所以外の箇所では、チップ内部202のビア層130と同じ膜厚を有する。同様に、第2のメタル層124は、第1のメタル層122の貫通孔122aにくい込んだ箇所以外の箇所では、チップ内部202の配線層132と同じ膜厚を有する。すなわち、チップ内部202におけるビア層130や配線層132の膜厚が図1に示した半導体装置100のビア層130や配線層132と等しい場合、図16に示した半導体装置100の下層メタル層121、第1のメタル層122、および第2のメタル層124は、図1に示した対応メタル層よりも膜厚が薄くなる。40

#### 【0059】

次に、図16に示した半導体装置100の製造手順の一例を説明する。図17～図24

50

は、半導体装置 100 の製造手順を示す工程断面図である。ここでも、層間絶縁膜 106 は、第 1 の層間絶縁膜 150、第 2 の層間絶縁膜 152、および第 3 の層間絶縁膜 154 の積層構造により構成される。

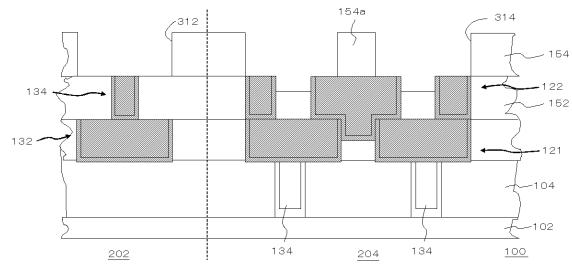

#### 【0060】

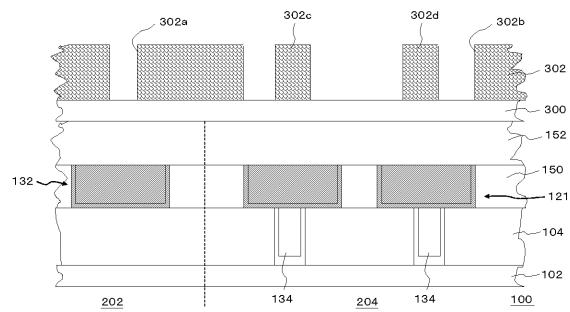

図 4 (a) を参照して説明したのと同様にして、第 1 の層間絶縁膜 150 中に配線層 132、および下層メタル層 121 を形成する (図 17)。つづいて、基板 102 上全面の第 1 の層間絶縁膜 150、配線層 132 および下層メタル層 121 上に、第 2 の層間絶縁膜 152 を形成する (図 18)。ここで、第 2 の層間絶縁膜 152 は、第 1 の層間絶縁膜 150 および後述する第 3 の層間絶縁膜 154 と同様の低誘電率膜とすることができます。さらに、第 2 の層間絶縁膜 152 上に反射防止膜 300 および所定のパターンを有するレジスト膜 302 をこの順で積層する (図 19)。ここで、レジスト膜 302 は、チップ内部 202 ではビアホールに対応するパターン 302a が開口したパターンを有する。レジスト膜 302 は、シールリング部 204 では、後述するシールリング溝 306 に対応するパターン 302b が開口するとともに、シールリング溝 306 中で後述する島状絶縁膜 152a が分散配置されるように島状絶縁膜 152a をマスクする部分 302c および 302d を残したパターンを有する。

#### 【0061】

このように形成されたレジスト膜 302 および反射防止膜 300 をマスクとして、第 2 の層間絶縁膜 152 をエッチングして、ビアホール 304 (第 1 の溝) およびシールリング溝 306 (第 1 のシールリング溝) を形成する。このとき、シールリング溝 306 中には、島状絶縁膜 152a が形成される。つづいて、レジスト膜 302 および反射防止膜 300 をアッシング等により除去する (図 20)。このとき、第 2 の層間絶縁膜 152 の下に銅含有メタル膜 120 またはバリアメタル膜 118 が存在する場合は、これらのメタル膜がエッチング阻止膜として機能し、ここでエッチングが止まる。一方、第 2 の層間絶縁膜 152 の下に第 1 の層間絶縁膜 150 が存在する場合は、第 2 の層間絶縁膜 152 がエッチング除去された後、貫通孔 121a 中の第 1 の層間絶縁膜 150 もエッチングされ、下層メタル層 121 の貫通孔 121a 中に凹部が形成される。

#### 【0062】

次いで、基板 102 上全面にバリアメタル膜 118 および銅含有メタル膜 120 をこの順で形成し、ビアホール 304 およびシールリング溝 306 をバリアメタル膜 118 および銅含有メタル膜 120 により埋め込む。その後、CMP によりビアホール 304 およびシールリング溝 306 外に露出した銅含有メタル膜 120 およびバリアメタル膜 118 を除去する。これにより、ビア層 130 および下層メタル層 121 が形成される (図 21)。CMP 工程において、シールリング溝 306 内には島状絶縁膜 152a が形成されているため、ディッシングを防ぐことができる。

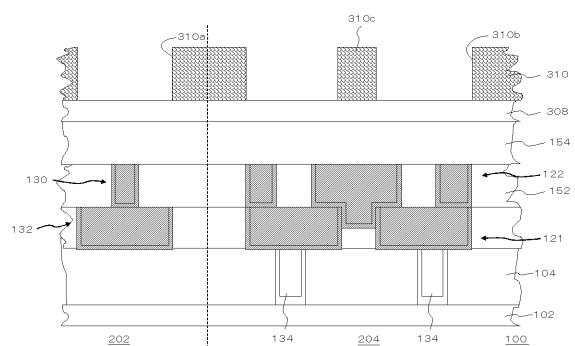

#### 【0063】

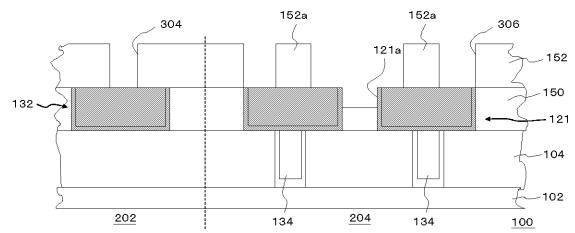

その後、基板 102 上全面の第 2 の層間絶縁膜 152、ビア層 130 および第 1 のメタル層 122 上に、第 3 の層間絶縁膜 154、反射防止膜 308 および所定のパターンを有するレジスト膜 310 をこの順で積層する (図 22)。ここで、レジスト膜 310 は、チップ内部 202 では配線溝に対応するパターン 310a が開口したパターンを有する。レジスト膜 310 は、シールリング部 204 では、後述するシールリング溝 314 に対応するパターン 310b が開口するとともに、シールリング溝 314 中で後述する島状絶縁膜 154a が分散配置されるように島状絶縁膜 154a をマスクする部分 310c を残したパターンを有する。

#### 【0064】

このように形成されたレジスト膜 310 および反射防止膜 308 をマスクとして、154 をエッチングして、配線溝 312 (第 2 の溝) およびシールリング溝 314 (第 2 のシールリング溝) を形成する。次いで、レジスト膜 310 および反射防止膜 308 をアッシング等により除去する (図 23)。このとき、第 3 の層間絶縁膜 154 の下に銅含有メタル膜 120 またはバリアメタル膜 118 が存在する場合は、これらのメタル膜がエッチ

10

20

30

40

50

グ阻止膜として機能し、ここでエッチングが止まる。ここで、シールリング溝314は、配線溝312よりも開口パターンが大きいため、シールリング溝314においては、エッチングの進行が早く、第3の層間絶縁膜154下に第2の層間絶縁膜152がある部分では、第3の層間絶縁膜154がエッチング除去された後、第2の層間絶縁膜152もエッチングされ、第1のメタル層122の貫通孔中に凹部が形成される。

【0065】

つづいて、基板102上全面にバリアメタル膜118および銅含有メタル膜120をこの順で形成し、配線溝312およびシールリング溝314をバリアメタル膜118および銅含有メタル膜120により埋め込む(図24)。その後、CMPにより配線溝312およびシールリング溝314外に露出した銅含有メタル膜120およびバリアメタル膜118を除去する。これにより、配線層132および第2のメタル層124が形成され、図16に示した構造の半導体装置100が製造される。CMP工程において、シールリング溝314内には島状絶縁膜154aが形成されているため、ディッシングを防ぐことができる。

10

【0066】

以上の処理を繰り返すことにより、配線層132上にさらにビア層130および配線層132が順次交互に形成されるとともに、シールリング部204において、第2のメタル層124上にさらに第1のメタル層122および第2のメタル層124と同様の構成のメタル層(第3のメタル層)が順次交互に形成された構成の半導体装置100を製造することができる。

20

【0067】

以上、図面を参照して本発明の実施形態について述べたが、これらは本発明の例示であり、上記以外の様々な構成を採用することもできる。

【0068】

以上の実施の形態において、層間絶縁膜106、第1の層間絶縁膜150、第2の層間絶縁膜152、および第3の層間絶縁膜154等を例示したが、これらは、低誘電率膜と、エッチング阻止膜や保護膜等との積層構造とすることができる。たとえば、低誘電率膜の上部には、CMP時に低誘電率膜を保護する保護膜が形成された構成とすることもできる。

【0069】

30

また、以上の実施の形態において、メタル層中に絶縁性材料が平面視において島状に分散配置される例を示したが、絶縁性材料が、シールリング部204の長軸方向に延在するスリット状に形成された構成とすることもできる。このような構成としても、実施の形態で説明した構成と同様、メタル層の底面に段差が生じ、下層のメタル層の貫通孔内でクラックや膜剥離の伝搬の進行を防ぐことができる。

【0070】

また、図2に示した例では、メタル層中に分散配置された島状絶縁膜が略正方形を有するが、島状絶縁膜は、たとえばシールリング部204の長軸方向に長辺を有する長方形や、円形等種々の形状とすることができる。

なお、本発明は、以下の構成を適用することも可能である。

40

(1)

基板と、

前記基板上に形成され、ビアおよび配線が形成される素子形成領域と、

前記基板上に形成され、平面視において前記素子形成領域を囲むように当該素子形成領域の外周に形成されたシールリングと、

を含み、

前記シールリングは、平面視において前記素子形成領域を囲むように形成された貫通孔を有する第1のメタル層と、前記第1のメタル層上に当該第1のメタル層に接して形成された第2のメタル層と、を含み、

前記第1のメタル層の前記貫通孔の下部分には絶縁性材料が形成され、当該貫通孔の前

50

記絶縁性材料が形成された箇所以外の上部分には前記第2のメタル層を構成するメタル材料がくい込んで形成された半導体装置。

(2)

(1)に記載の半導体装置において、

前記第1のメタル層の前記貫通孔は、平面視で複数の貫通孔が前記素子形成領域を囲むように分散配置されることにより構成され、前記複数の貫通孔の下部分にはそれぞれ前記絶縁性材料が形成され、当該複数の貫通孔の前記絶縁性材料が形成された箇所以外の上部分には、それぞれ前記第2のメタル層がくい込んで形成された半導体装置。

(3)

(2)に記載の半導体装置において、

前記第1のメタル層の前記複数の貫通孔は、平面視において格子状に配置された半導体装置。

(4)

(1)から(3)いずれかに記載の半導体装置において、

前記シールリングは前記第2のメタル層上に、当該第2のメタル層に接して形成された第3のメタル層をさらに含み、

前記第2のメタル層は、平面視において前記第1のメタル層の前記貫通孔とは重ならない位置において、前記素子形成領域を囲むように形成された貫通孔を有し、当該貫通孔の下部分には絶縁性材料が形成され、当該貫通孔の前記絶縁性材料が形成された箇所以外の上部分には前記第3のメタル層を構成するメタル材料がくい込んで形成された半導体装置。

。

(5)

(4)に記載の半導体装置において、

前記第2のメタル層の前記貫通孔は、平面視で複数の貫通孔が前記素子形成領域を囲むように分散配置されることにより構成され、前記複数の貫通孔の下部分にはそれぞれ前記絶縁性材料が形成され、当該複数の貫通孔の前記絶縁性材料が形成された箇所以外の上部分には、それぞれ前記第3のメタル層がくい込んで形成された半導体装置。

(6)

(5)に記載の半導体装置において、

前記第2のメタル層の前記複数の貫通孔は、平面視において格子状に配置された半導体装置。

(7)

(4)から(6)いずれかに記載の半導体装置において、

前記シールリングは、前記第1のメタル層下に、当該第1のメタル層に接して形成された下層メタル層をさらに含み、

前記シールリングは、内周から外周に延在する直線で切断した断面において、前記下層メタル層、前記第1のメタル層、前記第2のメタル層、および前記第3のメタル層をそれぞれ構成するメタル材料中に前記絶縁性材料が島状に分散配置された構造を有する半導体装置。

(8)

(4)から(7)いずれかに記載の半導体装置において、

前記シールリングは、内周から外周に延在する直線で切断した断面において、内周から外周の方向に、前記第1のメタル層の前記貫通孔が形成された列と前記第2のメタル層の前記貫通孔が形成された列とが交互に配置された半導体装置。

(9)

素子形成領域と、当該素子形成領域を囲むように当該素子形成領域の外周に形成されたシールリング部と、を含む半導体装置の製造方法であって、

基板上に形成された第1の絶縁膜に、前記素子形成領域においてピアまたは配線を形成するための第1の溝、および前記シールリング部において平面視で前記素子形成領域を取り囲むように第1のシールリング溝を形成する工程と、

10

20

30

40

50

前記第1の溝および前記第1のシールリング溝をメタル材料で埋め込み、次いで前記第1の溝および前記第1のシールリング溝外部に露出した前記メタル材料を除去することにより、前記第1の溝内にビアまたは配線を形成するとともに、前記第1のシールリング溝内に第1のメタル層を形成する工程と、

前記第1の絶縁膜上に第2の絶縁膜を形成する工程と、

前記第2の絶縁膜に、前記素子形成領域においてビアまたは配線を形成するための第2の溝、および前記シールリング部において前記第1のシールリング溝上に第2のシールリング溝を形成する工程と、

前記第2の溝および前記第2のシールリング溝をメタル材料で埋め込み、次いで前記第2の溝および前記第2のシールリング溝外部に露出した前記メタル材料を除去することにより、前記第2の溝内にビアまたは配線を形成するとともに、前記第2のシールリング溝内に、前記第1のメタル層に接する第2のメタル層を形成する工程と、

を含み、

前記第1のシールリング溝を形成する工程において、当該第1のシールリング溝は、当該第1のシールリング溝内に、前記第1の絶縁膜を残して形成され、

前記第1のシールリング溝内に第1のメタル層を形成する工程において、前記第1のシールリング溝に残して形成された前記第1の絶縁膜により、当該第1のメタル層には貫通孔が形成され、

前記第2のシールリング溝を形成する工程において、前記第2のシールリング溝底面に前記第1の絶縁膜が露出した後、当該露出した前記第1の絶縁膜の上部分を除去して、前記第1のメタル層の前記貫通孔の下部分に前記第1の絶縁膜を残し、

前記第2のメタル層を形成する工程において、前記第1のメタル層の前記貫通孔の上部分に、当該第2のメタル層をくい込ませる半導体装置の製造方法。

(10)

(9)に記載の半導体装置の製造方法において、

前記第1のシールリング溝を形成する工程において、当該第1のシールリング溝は、当該第1のシールリング溝内に、平面視で前記素子形成領域を取り囲むように前記第1の絶縁膜が島状に分散配置されるように当該第1の絶縁膜を残して形成され、

前記第1のシールリング溝内に第1のメタル層を形成する工程において、前記第1のシールリング溝に残して形成された前記第1の絶縁膜により、当該第1のメタル層には複数の貫通孔が形成される半導体装置の製造方法。

(11)

(9)または(10)に記載の半導体装置の製造方法において、

前記第2の絶縁膜上に第3の絶縁膜を形成する工程と、

前記第3の絶縁膜に、前記素子形成領域においてビアまたは配線を形成するための第3の溝、および前記シールリング部において前記第2のシールリング溝上に第3のシールリング溝を形成する工程と、

前記第3の溝および前記第3のシールリング溝をメタル材料で埋め込み、次いで前記第3の溝および前記第3のシールリング溝外部に露出した前記メタル材料を除去することにより、前記第3の溝内にビアまたは配線を形成するとともに、前記第3のシールリング溝内に、前記第2のメタル層に接する第3のメタル層を形成する工程と、

をさらに含み、

前記第2のシールリング溝を形成する工程において、当該第2のシールリング溝は、当該第2のシールリング溝内に、平面視で前記第1のメタル層の前記貫通孔とは重ならない位置において、前記素子形成領域を取り囲むように当該第2の絶縁膜を残して形成され、

前記第2のシールリング溝内に第2のメタル層を形成する工程において、前記第2のシールリング溝に残して形成された前記第2の絶縁膜により、当該第2のメタル層には貫通孔が形成され、

前記第3のシールリング溝を形成する工程において、前記第3のシールリング溝底面に前記第2の絶縁膜が露出した後、当該露出した前記第2の絶縁膜の上部分を除去して、前

10

20

30

40

50

記第2のメタル層の前記貫通孔の下部分に前記第2の絶縁膜を残し、

前記第3のメタル層を形成する工程において、前記第2のメタル層の前記貫通孔の上部分に、当該第3のメタル層をくい込ませる半導体装置の製造方法。

(12)

(11) に記載の半導体装置の製造方法において、

前記第2のシールリング溝を形成する工程において、当該第2のシールリング溝は、当該第2のシールリング溝内に、平面視で前記素子形成領域を取り囲むように前記第2の絶縁膜が島状に分散配置されるように当該第2の絶縁膜を残して形成され、

前記第2のシールリング溝内に第2のメタル層を形成する工程において、前記第2のシールリング溝に残して形成された前記第2の絶縁膜により、当該第2のメタル層には複数の貫通孔が形成される半導体装置の製造方法。

【図面の簡単な説明】

【0071】

【図1】本発明の実施の形態における半導体装置の構成を示す断面図である。

【図2】図1に示す半導体装置の横断平面図である。

【図3】基板上に複数のチップが形成された構成を示す平面図である。

【図4】図1に示す半導体装置の製造手順の一例を示す工程断面図である。

【図5】図1に示す半導体装置の製造手順の一例を示す工程断面図である。

【図6】図1に示す半導体装置の製造手順の一例を示す工程断面図である。

【図7】図1に示す半導体装置の製造手順の一例を示す工程断面図である。

【図8】図1に示す半導体装置の製造途中の構成を示す平面図である。

【図9】図1に示す半導体装置の製造途中の構成を示す平面図である。

【図10】図1に示す半導体装置の製造途中の構成を示す平面図である。

【図11】図1に示す半導体装置の製造途中の構成を示す平面図である。

【図12】図1に示す半導体装置の製造手順の他の例を示す工程断面図である。

【図13】図1に示す半導体装置の製造手順の他の例を示す工程断面図である。

【図14】図1に示す半導体装置の製造手順の他の例を示す工程断面図である。

【図15】図1に示す半導体装置の製造手順の他の例を示す工程断面図である。

【図16】本発明の実施の形態における半導体装置の他の例を示す図である。

【図17】図16に示す半導体装置の製造手順を示す工程断面図である。

【図18】図16に示す半導体装置の製造手順を示す工程断面図である。

【図19】図16に示す半導体装置の製造手順を示す工程断面図である。

【図20】図16に示す半導体装置の製造手順を示す工程断面図である。

【図21】図16に示す半導体装置の製造手順を示す工程断面図である。

【図22】図16に示す半導体装置の製造手順を示す工程断面図である。

【図23】図16に示す半導体装置の製造手順を示す工程断面図である。

【図24】図16に示す半導体装置の製造手順を示す工程断面図である。

【図25】第1のメタル層および第2のメタル層にそれぞれ形成される貫通孔の配置の他の例を示す平面図である。

【図26】従来の半導体装置の問題点を説明するための断面図である。

【符号の説明】

【0072】

100 半導体装置

102 基板

104 下層絶縁膜

106 層間絶縁膜

118 バリアメタル膜

120 銅含有メタル膜

121 下層メタル層

121a 貫通孔

10

20

30

40

50

|                   |    |

|-------------------|----|

| 1 2 2 第 1 のメタル層   |    |

| 1 2 2 a 貫通孔       |    |

| 1 2 4 第 2 のメタル層   |    |

| 1 2 4 a 貫通孔       |    |

| 1 3 0 ビア層         |    |

| 1 3 2 配線層         |    |

| 1 3 4 Wシールリング     |    |

| 1 4 0 クラックや膜剥離    |    |

| 1 5 0 第 1 の層間絶縁膜  | 10 |

| 1 5 0 a 島状絶縁膜     |    |

| 1 5 2 第 2 の層間絶縁膜  |    |

| 1 5 2 a 島状絶縁膜     |    |

| 1 5 2 ' 層間絶縁膜     |    |

| 1 5 4 第 3 の層間絶縁膜  |    |

| 1 5 4 a 島状絶縁膜     |    |

| 1 5 4 ' 層間絶縁膜     |    |

| 1 5 6 反射防止膜       |    |

| 1 5 6 ' 反射防止膜     |    |

| 1 5 8 レジスト膜       | 20 |

| 1 5 8 a パターン      |    |

| 1 5 8 b パターン      |    |

| 1 5 8 c 部分        |    |

| 1 5 8 d 部分        |    |

| 1 5 8 ' レジスト膜     |    |

| 1 5 8 ' a パターン    |    |

| 1 5 8 ' b パターン    |    |

| 1 5 8 ' c 部分      |    |

| 1 6 0 シールリング溝     |    |

| 1 6 2 ビアホール       |    |

| 1 6 4 下層レジスト膜     | 30 |

| 1 6 6 低温酸化膜       |    |

| 1 6 8 反射防止膜       |    |

| 1 7 0 上層レジスト膜     |    |

| 1 7 0 a パターン      |    |

| 1 7 2 配線溝         |    |

| 1 7 4 第 1 のハードマスク |    |

| 1 7 6 第 2 のハードマスク |    |

| 1 7 8 第 3 のハードマスク |    |

| 1 8 0 反射防止膜       |    |

| 1 8 2 レジスト膜       | 40 |

| 1 8 2 a パターン      |    |

| 1 8 2 b パターン      |    |

| 1 8 2 c 部分        |    |

| 1 8 2 d 部分        |    |

| 1 8 3 反射防止膜       |    |

| 1 8 4 レジスト膜       |    |

| 1 8 4 a パターン      |    |

| 1 9 0 配線溝         |    |

| 1 9 2 シールリング溝     |    |

| 1 9 4 ビアホールパターン   | 50 |

- 1 9 6 開口部

1 9 8 配線溝パターン

2 0 2 チップ内部

2 0 3 チップ

2 0 4 シールリング部

2 0 6 ダイシングライン

2 0 8 アライメントマーク

3 0 0 反射防止膜

3 0 2 レジスト膜

3 0 2 a パターン

3 0 2 b パターン

3 0 2 c 部分

3 0 2 d 部分

3 0 4 ピアホール

3 0 6 シールリング溝

3 0 8 反射防止膜

3 1 0 レジスト膜

3 1 0 a パターン

3 1 0 b パターン

3 1 0 c 部分

3 1 2 配線溝

3 1 4 シールリング溝

- 10

- 20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

---

フロントページの続き

(56)参考文献 特開2004-311930(JP,A)

特開2004-064046(JP,A)

特開2006-269519(JP,A)

特開平11-354637(JP,A)

特開2004-363376(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L21/3205

H01L21/3213

H01L21/768

H01L23/52 - H01L23/522