(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6178466号

(P6178466)

(45) 発行日 平成29年8月9日(2017.8.9)

(24) 登録日 平成29年7月21日(2017.7.21)

(51) Int.Cl.

F 1

|                     |                  |             |               |                |

|---------------------|------------------|-------------|---------------|----------------|

| <b>H01L 21/8234</b> | <b>(2006.01)</b> | <b>H01L</b> | <b>27/088</b> | <b>E</b>       |

| <b>H01L 27/088</b>  | <b>(2006.01)</b> | <b>H01L</b> | <b>27/105</b> | <b>4 4 1</b>   |

| <b>H01L 21/8239</b> | <b>(2006.01)</b> | <b>H03K</b> | <b>3/356</b>  | <b>B</b>       |

| <b>H01L 27/105</b>  | <b>(2006.01)</b> | <b>H01L</b> | <b>27/04</b>  | <b>D</b>       |

| <b>H03K 3/356</b>   | <b>(2006.01)</b> | <b>H01L</b> | <b>29/78</b>  | <b>6 1 8 B</b> |

請求項の数 6 (全 60 頁) 最終頁に続く

(21) 出願番号 特願2016-127447 (P2016-127447)

(22) 出願日 平成28年6月28日 (2016.6.28)

(62) 分割の表示 特願2015-84169 (P2015-84169)

分割

原出願日 平成23年8月22日 (2011.8.22)

(65) 公開番号 特開2016-201554 (P2016-201554A)

(43) 公開日 平成28年12月1日 (2016.12.1)

審査請求日 平成28年6月29日 (2016.6.29)

(31) 優先権主張番号 特願2010-189214 (P2010-189214)

(32) 優先日 平成22年8月26日 (2010.8.26)

(33) 優先権主張国 日本国 (JP)

(31) 優先権主張番号 特願2011-113178 (P2011-113178)

(32) 優先日 平成23年5月20日 (2011.5.20)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 小山 潤

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 市川 武宜

最終頁に続く

(54) 【発明の名称】 半導体装置及び半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

第1のトランジスタを含む論理素子と、第2のトランジスタと、容量素子と、を有し、前記論理素子が出力するデータを前記第2のトランジスタを介して前記容量素子に保持する機能と、

前記データを前記容量素子に保持した後に、前記第2のトランジスタをオフ状態にする機能と、

前記第2のトランジスタをオフ状態にした後に、前記論理素子への電源電圧の供給を停止する機能と、を有し、

前記第1のトランジスタは、半導体基板又はSOI基板に設けられ、

10

前記第1のトランジスタ上方に絶縁層を有し、

前記絶縁層の上面は、CMP処理によって平坦化されており、

前記第2のトランジスタ及び前記容量素子は前記絶縁層上方に設けられていることを特徴とする半導体装置。

## 【請求項 2】

請求項1において、

前記第2のトランジスタは、酸化物半導体層を有することを特徴とする半導体装置。

## 【請求項 3】

請求項2において、

前記酸化物半導体層は、第1の酸化物半導体層と、前記第1の酸化物半導体層上方の第

20

2の酸化物半導体層と、を有し、

前記第2の酸化物半導体層は、前記第1の酸化物半導体層よりも厚いことを特徴とする半導体装置。

**【請求項4】**

請求項2又は請求項3において、

前記酸化物半導体層は、In、Ga、及びZnを用いたものであり、

前記酸化物半導体層は、表面に対して垂直な方向に沿うようにc軸が配向した結晶を有することを特徴とする半導体装置。

**【請求項5】**

請求項2乃至請求項4のいずれか一項に記載の半導体装置の作製方法であって、

10

熱処理を経て前記酸化物半導体層を形成し、

前記熱処理の処理中に、不活性ガスを含む雰囲気から酸素を含む雰囲気に切り替えることを特徴とする半導体装置の作製方法。

**【請求項6】**

請求項1乃至請求項4のいずれか一項において、

前記第1のトランジスタのソース電極又はドレイン電極と前記容量素子の第1の電極とは、第1の導電層に設けられており、

前記第1のトランジスタのゲート電極と前記容量素子の第2の電極とは、同層であることを特徴とする半導体装置。

**【発明の詳細な説明】**

20

**【技術分野】**

**【0001】**

電源を切っても記憶している論理状態が消えない不揮発性の記憶装置、及びそれを用いた信号処理回路に関する。また、当該記憶装置及び当該信号処理回路の駆動方法に関する。更に当該信号処理回路を用いた電子機器に関する。

**【背景技術】**

**【0002】**

中央演算処理装置(CPU:Central Processing Unit)などの信号処理回路は、その用途によって多種多様な構成を有しているが、一般的に、データやプログラムを記憶するためのメインメモリの他に、レジスタ、キャッシュメモリなど、各種の記憶装置が設けられている。レジスタは、演算処理やプログラムの実行状態の保持などのために一時的にデータを保持する役割を担っている。また、キャッシュメモリは、演算回路とメインメモリの間に介在し、低速なメインメモリへのアクセスを減らして演算処理を高速化させることを目的として設けられている。

30

**【0003】**

レジスタやキャッシュメモリ等の記憶装置は、メインメモリよりも高速でデータの書き込みを行う必要がある。よって、通常は、レジスタとしてフリップフロップが、キャッシュメモリとしてSRAM(Static Random Access Memory)等が用いられる。つまり、これらのレジスタ、キャッシュメモリ等には、電源電圧の供給が途絶えるとデータを消失してしまう揮発性の記憶装置が用いられている。

40

**【0004】**

消費電力を抑えるため、データの入出力が行われない期間において信号処理回路への電源電圧の供給を一時的に停止するという方法が提案されている。その方法では、レジスタ、キャッシュメモリ等の揮発性の記憶装置の周辺に不揮発性の記憶装置を配置し、上記データをその不揮発性の記憶装置に一時的に記憶させる。こうして、信号処理回路において電源電圧の供給を停止する間も、レジスタ、キャッシュメモリ等はデータを保持する(例えば、特許文献1参照)。

**【0005】**

また、信号処理回路において長時間の電源電圧の供給停止を行う際には、電源電圧の供給停止の前に、揮発性の記憶装置内のデータをハードディスク、フラッシュメモリ等の外

50

部記憶装置に移すことで、データの消失を防ぐこともできる。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開平10-078836号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

信号処理回路において電源電圧の供給を停止する間、揮発性の記憶装置の周辺に配置した不揮発性の記憶装置へ揮発性の記憶装置のデータを記憶させる方法では、これらの不揮発性の記憶装置として主に磁気素子や強誘電体が用いられているため、信号処理回路の作製工程が複雑である。また、これらの不揮発性の記憶装置では、データの書き込みや消去を繰り返すことによる記憶素子の劣化のために、情報の書き換え回数が制限される。10

【0008】

また、信号処理回路において電源電圧の供給を停止する間、外部記憶装置に揮発性の記憶装置のデータを記憶させる方法では、外部記憶装置から揮発性の記憶装置にデータを戻すのには時間を要する。よって、外部記憶装置によるデータのバックアップは、消費電力の低減を目的とした短時間の電源停止には適さない。

【0009】

上述の課題に鑑み、本発明は、消費電力を抑えることができる信号処理回路、当該信号処理回路の駆動方法の提供を目的の一つとする。特に、短時間の電源停止により消費電力を抑えることができる信号処理回路、当該信号処理回路の駆動方法の提供を目的の一つとする。20

【課題を解決するための手段】

【0010】

入力された信号の位相を反転させて出力する論理素子（以下、位相反転素子と呼ぶ）を2つ（第1の位相反転素子及び第2の位相反転素子）と、第1の選択トランジスタと、第2の選択トランジスタと、を有する記憶素子であって、酸化物半導体層にチャネルが形成されるトランジスタと容量素子との組を2つ（第1のトランジスタと第1の容量素子との組、及び第2のトランジスタと第2の容量素子との組）有する。30

【0011】

酸化物半導層には、例えば、In-Ga-Zn-O系の酸化物半導体材料を用いることができる。

【0012】

第1の位相反転素子の出力端子の電位はオン状態となった第1のトランジスタを介して第2の位相反転素子の入力端子に与えられ、第2の位相反転素子の出力端子の電位はオン状態となった第2のトランジスタを介して第1の位相反転素子の入力端子に与えられる。第1のトランジスタと第2の位相反転素子の入力端子の間には、第1の容量素子の一対の電極のうちの一方の電極が電気的に接続されている。即ち、第1のトランジスタがオフ状態となっても、第2の位相反転素子の入力端子の電位を第1の容量素子は保持する。第2のトランジスタと第1の位相反転素子の入力端子の間には、第2の容量素子の一対の電極のうちの一方の電極が電気的に接続されている。即ち、第2のトランジスタがオフ状態となっても第1の位相反転素子の入力端子の電位を第2の容量素子は保持する。40

【0013】

なお、第1の容量素子の一対の電極のうちの他方の電極と、第2の容量素子の一対の電極のうちの他方の電極とには、一定の電位が与えられている。例えば、基準電位（GND）が与えられている。

【0014】

記憶素子への入力信号（データ）の電位は、オン状態となった第1の選択トランジスタ及び第2のトランジスタを介して第1の位相反転素子の入力端子に与えられる。また、第50

1の位相反転素子の出力端子の電位が、オン状態となった第2の選択トランジスタを介して記憶素子の出力信号として出力される。

#### 【0015】

ここで、第1のトランジスタと第2のトランジスタとは、一方がオン状態のとき他方もオン状態となるように制御される。例えば、第1のトランジスタと第2のトランジスタが同じ導電型のトランジスタである場合に、第1のトランジスタのゲートに入力される第1の制御信号と、第2のトランジスタのゲートに入力される第2の制御信号とは、同じ信号を用いることができる。

#### 【0016】

上記記憶素子において、電源電圧の供給の後、データの保持時における消費電力を削減するため電源電圧の供給を停止し、再び電源電圧を供給する場合の駆動方法は以下のようにすることができる。

10

#### 【0017】

はじめに、記憶素子に電源電圧が供給されている場合について説明する。つまり、第1の位相反転素子及び第2の位相反転素子に電源電圧が供給されている場合について説明する。第1のトランジスタ及び第2のトランジスタをオン状態とした状態で、第1の選択トランジスタをオン状態とする。こうして、第1の位相反転素子の入力端子に入力信号（データ）を入力する。その後、第1の選択トランジスタをオフ状態とすることによって第1の位相反転素子及び第2の位相反転素子でなる帰還ループによってそのデータが保持される。また、第2の位相反転素子の入力端子の電位は第1の容量素子に保持され、第1の位相反転素子の入力端子の電位は第2の容量素子に保持される。なお、データの入力及び保持の間、第2の選択トランジスタはオフ状態である。なお、データの保持が完了した後、第2の選択トランジスタをオン状態とすることによって、記憶素子からデータを読み出すことができる。

20

#### 【0018】

データの保持が完了した後、記憶素子への電源電圧の供給を停止する場合について説明する。つまり、第1の位相反転素子及び第2の位相反転素子への電源電圧の供給を停止する場合について説明する。電源電圧の供給を停止する前に、上記第1のトランジスタ及び第2のトランジスタをオフ状態にする。ここで、第2の位相反転素子の入力端子の電位は第1の容量素子に保持されており、第1の位相反転素子の入力端子の電位は第2の容量素子に保持されている。そのため、第1の位相反転素子及び第2の位相反転素子への電源電圧の供給を停止しても、記憶素子にデータを保持させ続けることが可能である。第1の位相反転素子及び第2の位相反転素子への電源電圧の供給を停止している間は、第1のトランジスタ及び第2のトランジスタはオフ状態である。第1の位相反転素子及び第2の位相反転素子への電源電圧の供給を停止している間は、記憶素子から出力信号を出力することはできず、また記憶素子に新たな入力信号（データ）を入力して保持することはできない。

30

#### 【0019】

次に再び記憶素子へ電源電圧を供給する場合について説明する。第1の位相反転素子及び第2の位相反転素子に電源電圧を供給した後、第1のトランジスタ及び第2のトランジスタをオン状態とする。こうして、記憶素子は出力信号を出力可能な状態となり、新たな入力信号（データ）を保持可能な状態となる。

40

#### 【0020】

以上が、上記記憶素子において、電源電圧の供給の後、データの保持時における消費電力を削減するために電源電圧の供給を停止し、再び電源電圧を供給する場合の駆動方法である。

#### 【0021】

なお、第1の位相反転素子や第2の位相反転素子としては、例えばインバータやクロックドインバータ等を用いることができる。

#### 【0022】

50

そして、信号処理回路が有する記憶装置に上記記憶素子を用いる。記憶装置は一または複数の記憶素子を用いて構成することができる。例えば、信号処理回路が有するレジスタ、キャッシュメモリ等の記憶装置に上記記憶素子を用いる。

#### 【0023】

さらに、信号処理回路は、上記記憶装置に加え、記憶装置とデータのやり取りを行う演算回路等の各種論理回路を有してもよい。そして、記憶装置へ電源電圧の供給を停止すると共に、当該記憶装置とデータのやり取りを行う演算回路への電源電圧の供給を停止するようにしてても良い。

#### 【0024】

そして、上記記憶装置は、記憶素子への電源電圧の供給を制御するスイッチング素子を有していても良い。また、演算回路への電源電圧の供給を停止する場合には、演算回路は、電源電圧の供給を制御するスイッチング素子を有していても良い。10

#### 【発明の効果】

#### 【0025】

酸化物半導体層にチャネルが形成されるトランジスタはオフ電流が極めて小さい。例えば、酸化物半導体層にチャネルが形成されるトランジスタのオフ電流は、結晶性を有するシリコンにチャネルが形成されるトランジスタのオフ電流に比べて著しく低い。そのため、当該トランジスタを第1のトランジスタ及び第2のトランジスタとして用いることによつて、記憶素子に電源電圧が供給されない間も第1の容量素子及び第2の容量素子に保持された電位は保たれる。こうして、記憶素子は電源電圧の供給が停止した間も記憶内容を保持することが可能である。20

#### 【0026】

記憶素子は電源電圧の供給が停止した間も、第1の容量素子に保持された電位によって第2の位相反転素子の入力端子の電位が保持され、第2の容量素子に保持された電位によつて第1の位相反転素子の入力端子の電位が保持されている。つまり、第1の位相反転素子の入力端子の電位と第2の位相反転素子の入力端子の電位の両方が保持されている。

#### 【0027】

一方、例えば、記憶素子が第1の容量素子と第1のトランジスタを有し、第2の容量素子と第2のトランジスタを有さない構成の場合を考える。つまり、第2の位相反転素子の出力端子が第1の位相反転素子の入力端子に直接接続されている場合を考える。この構成では、第1の容量素子に保持された電位によつて第2の位相反転素子の入力端子の電位は保持されるが、第1の位相反転素子の入力端子の電位は保持されない。そのため、記憶素子への電源電圧の供給が再開した後、第1のトランジスタをオン状態とすると、第1の位相反転素子の入力端子の電位が所定の電位（第2の位相反転素子の出力によつて定まる電位）となるように電荷の移動が生じる。この電荷の移動が完了するまで記憶素子はデータを出力することができない。そのため、記憶素子がデータを出力できるようになるまでの時間（以下、立ち上げ時間ともいう）が長くなる。つまり、電源供給停止前の状態に復帰するために時間がかかる。30

#### 【0028】

本発明では、記憶素子は電源電圧の供給が停止した間も、第1の位相反転素子の入力端子の電位と第2の位相反転素子の入力端子の電位の両方が保持されている。そのため、記憶素子への電源電圧の供給が再開された後、第1のトランジスタ及び第2のトランジスタをオン状態としても、第2の位相反転素子の入力端子や第1の位相反転素子の入力端子の電位が所定の電位となるように電荷が移動する必要がなく、立ち上げ時間を短くすることができます。40

#### 【0029】

このような記憶素子を、信号処理回路が有するレジスタやキャッシュメモリなどの記憶装置に用いることで、電源電圧の供給停止による記憶装置内のデータの消失を防ぐことができる。また、電源電圧の供給を再開した後、短時間で電源供給停止前の状態に復帰することができる。よつて、信号処理回路全体、もしくは信号処理回路を構成する一または複数の記憶素子を用いて構成することができる。50

数の論理回路において、短い時間でも電源停止を行うことができるため、消費電力を抑えることができる信号処理回路、消費電力を抑えることができる当該信号処理回路の駆動方法を提供することができる。

【図面の簡単な説明】

【0030】

【図1】記憶素子の回路図。

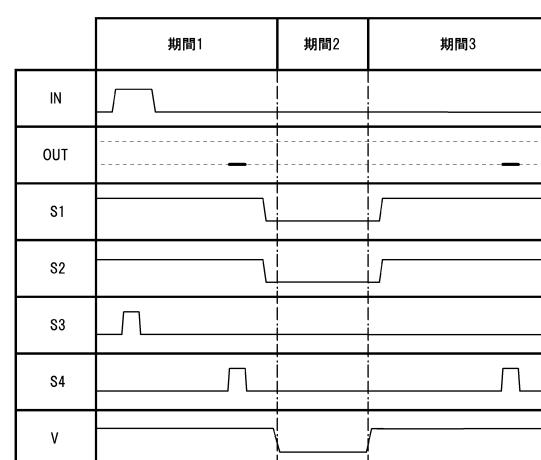

【図2】記憶素子の動作を示すタイミングチャート。

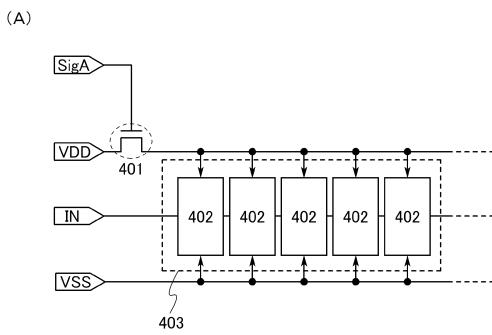

【図3】記憶装置の構成を示す図。

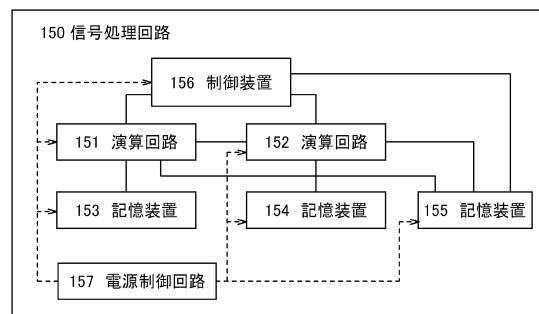

【図4】信号処理回路のブロック図。

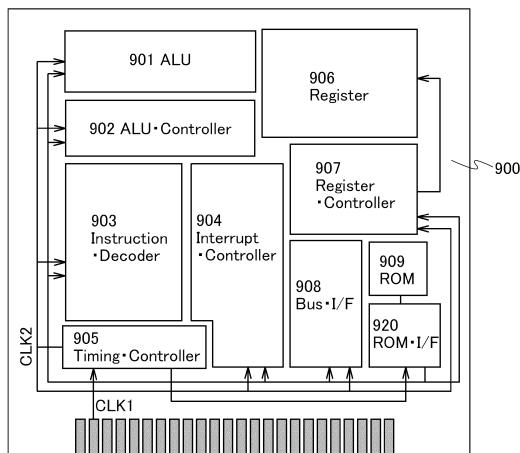

【図5】記憶装置を用いたCPUのブロック図。

10

【図6】記憶素子の構成を示す断面図。

【図7】記憶素子の構成を示す断面図。

【図8】記憶素子の構成を示す断面図。

【図9】記憶素子の構成を示す断面図。

【図10】記憶素子の作製方法を示す図。

【図11】記憶素子の作製方法を示す図。

【図12】記憶素子の作製方法を示す図。

【図13】記憶素子の作製方法を示す図。

【図14】記憶素子の作製方法を示す図。

【図15】記憶素子の作製方法を示す図。

20

【図16】記憶素子の作製方法を示す図。

【図17】トランジスタの構成を示す断面図。

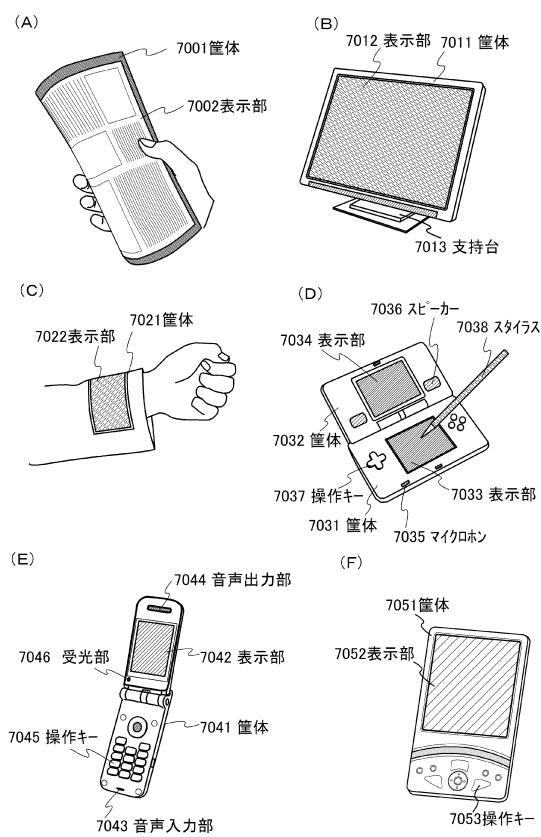

【図18】電子機器の構成を示す図。

【図19】酸化物材料の構造を説明する図。

【図20】酸化物材料の構造を説明する図。

【図21】酸化物材料の構造を説明する図。

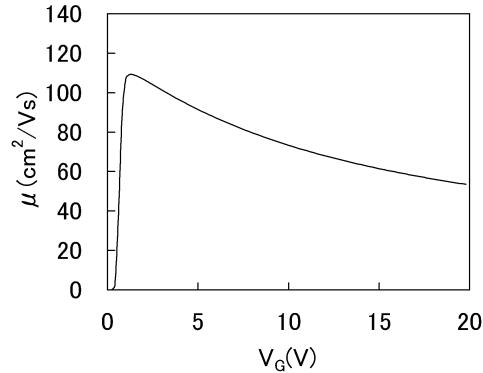

【図22】計算によって得られた移動度のゲート電圧依存性を説明する図。

【図23】計算によって得られたドレイン電流と移動度のゲート電圧依存性を説明する図。

。 【図24】計算によって得られたドレイン電流と移動度のゲート電圧依存性を説明する図 30

。 【図25】計算によって得られたドレイン電流と移動度のゲート電圧依存性を説明する図

。 【図26】計算に用いたトランジスタの断面構造を説明する図。

【図27】酸化物半導体膜を用いたトランジスタ特性のグラフ。

【図28】試料1のトランジスタのBT試験後の $V_g - I_d$ 特性を示す図。

【図29】試料2であるトランジスタのBT試験後の $V_g - I_d$ 特性を示す図。

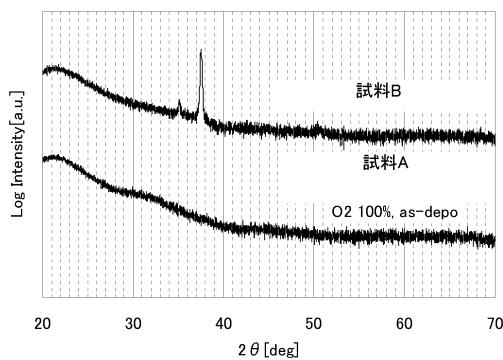

【図30】試料Aおよび試料BのXRDスペクトルを示す図。

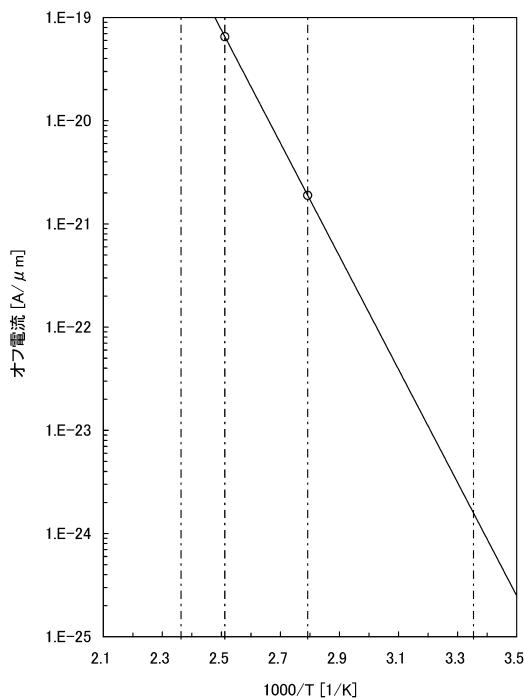

【図31】トランジスタのオフ電流と測定時基板温度との関係を示す図。

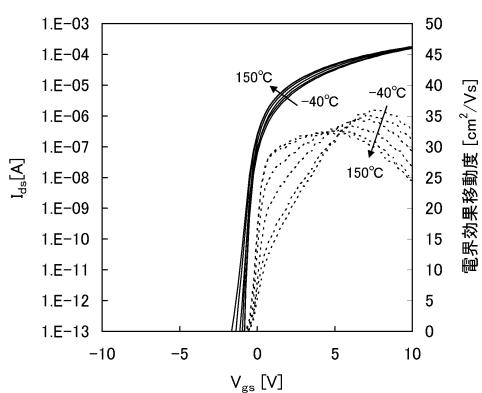

【図32】 $I_d$ および電界効果移動度の $V_g$ 依存性を示す図。

40

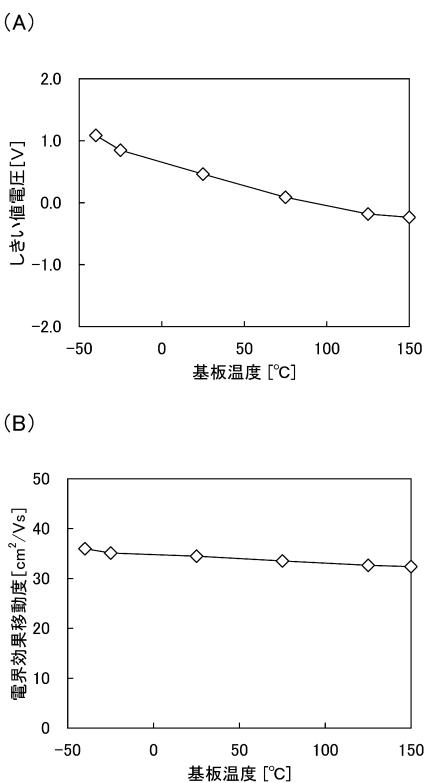

【図33】基板温度としきい値電圧の関係および基板温度と電界効果移動度の関係を示す図。

【図34】トランジスタの上面図及び断面図。

【図35】トランジスタの上面図及び断面図。

【発明を実施するための形態】

【0031】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明は、以下に示す実施の形態の記載内容に限定して解釈されるものではない。

50

**【0032】**

なお、「ソース」や「ドレイン」の機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れかわることがある。このため、本明細書においては、「ソース」や「ドレイン」の用語は、入れかえて用いることができるものとする。

**【0033】**

「電気的に接続」には、「何らかの電気的作用を有するもの」を介して接続されている場合が含まれる。ここで、「何らかの電気的作用を有するもの」は、接続対象間での電気信号の授受を可能とするものであれば、特に制限はない。例えば、「何らかの電気的作用を有するもの」には、電極や配線をはじめ、トランジスタなどのスイッチング素子、抵抗素子、インダクタ、キャパシタ、その他の各種機能を有する素子などが含まれる。10

**【0034】**

回路図上は独立している構成要素どうしが電気的に接続しているように図示されている場合であっても、実際には、例えば配線の一部が電極としても機能する場合など、一の導電膜が、複数の構成要素の機能を併せ持っている場合もある。本明細書において電気的に接続とは、このような、一の導電膜が、複数の構成要素の機能を併せ持っている場合も、その範疇に含める。

**【0035】**

「上」や「下」の用語は、構成要素の位置関係が「直上」または「直下」であることを限定するものではない。例えば、「ゲート絶縁層上のゲート電極」の表現であれば、ゲート絶縁層とゲート電極との間に他の構成要素を含むものを除外しない。20

**【0036】**

図面等において示す各構成の、位置、大きさ、範囲などは、理解の簡単のため、実際の位置、大きさ、範囲などを表していない場合がある。このため、開示する発明は、必ずしも、図面等に開示された位置、大きさ、範囲などに限定されない。

**【0037】**

「第1」、「第2」、「第3」などの序数詞は、構成要素の混同を避けるために付すものである。

**【0038】****(実施の形態1)**

信号処理回路は記憶装置を有し、記憶装置は1ビットのデータを記憶することができる記憶素子を、単数または複数有する。30

**【0039】**

なお、CPU、マイクロプロセッサ、画像処理回路、DSP(Digital Signal Processor)、FPGA(Field Programmable Gate Array)等のLSI(Large Scale Integrated Circuit)等が、本発明の信号処理回路の範疇に含まれる。

**【0040】**

図1(A)に、記憶素子の回路図の一例を示す。図1に示す記憶素子100は、入力された信号の位相を反転させて出力する位相反転素子101及び位相反転素子102と、選択トランジスタ103と、選択トランジスタ104と、トランジスタ111と、トランジスタ112と、容量素子121と、容量素子122とを有する。トランジスタ111とトランジスタ112は酸化物半導体層にチャネルが形成されるトランジスタである。なお、記憶素子100は、必要に応じて、ダイオード、抵抗素子、インダクタなどの他の回路素子をさらに有していても良い。図1(A)の回路図において、トランジスタ111とトランジスタ112は酸化物半導体層にチャネルが形成されるトランジスタであることを示すためにOSの符号を付す。40

**【0041】**

記憶素子100に入力されたデータを含む信号INは、オン状態となった選択トランジスタ103及びトランジスタ111を介して位相反転素子101の入力端子に与えられる50

。また、位相反転素子 101 の出力端子の電位が、オン状態となった選択トランジスタ 104 を介して記憶素子の出力信号 OUT として出力される。信号 OUT は、後段の記憶素子、或いは他の回路に出力される。

#### 【 0042 】

位相反転素子 101 の出力端子の電位はオン状態となったトランジスタ 112 を介して位相反転素子 102 の入力端子に与えられ、位相反転素子 102 の出力端子の電位はオン状態となったトランジスタ 111 を介して位相反転素子 101 の入力端子に与えられる。トランジスタ 112 と位相反転素子 102 の入力端子の間には、容量素子 122 の一対の電極のうちの一方の電極が電気的に接続されている。即ち、トランジスタ 112 がオフ状態となっても、位相反転素子 102 の入力端子の電位を容量素子 122 は保持する。トランジスタ 111 と位相反転素子 101 の入力端子の間には、容量素子 121 の一対の電極のうちの一方の電極が電気的に接続されている。即ち、トランジスタ 111 がオフ状態となっても位相反転素子 101 の入力端子の電位を容量素子 121 は保持する。10

#### 【 0043 】

なお、容量素子 121 の一対の電極のうちの他方の電極と、容量素子 122 の一対の電極のうちの他方の電極とには、一定の電位 VSS が与えられている。例えば、電位 VSS は基準電位 ( GND ) とすることができる。

#### 【 0044 】

また、トランジスタ 111 のゲートには制御信号 S1 が入力され、トランジスタ 112 のゲートには制御信号 S2 が入力され、選択トランジスタ 103 のゲートには制御信号 S3 が入力され、選択トランジスタ 104 のゲートには制御信号 S4 が入力されている。例えば、トランジスタ 111 とトランジスタ 112 が同じ導電型のトランジスタである場合に、制御信号 S1 と制御信号 S2 は同じ信号とすることができます。つまり、トランジスタ 111 とトランジスタ 112 は、一方がオン状態のとき他方もオン状態となるように制御される。20

#### 【 0045 】

なお、図 1 ( A ) では、位相反転素子 101 及び位相反転素子 102 として、インバータを用いる例を示している。しかしながら、位相反転素子 101 及び位相反転素子 102 は、入力された信号の位相を反転させて出力する素子であれば何でもよく、クロックドインバータ等を用いることもできる。30

#### 【 0046 】

図 1 ( A ) における位相反転素子 101 と位相反転素子 102 とを、n チャネル型トランジスタと p チャネル型トランジスタとでなるインバータとした例を図 1 ( B ) に示す。位相反転素子 101 は n チャネル型トランジスタ 131 と p チャネル型トランジスタ 132 を有し、位相反転素子 102 は n チャネル型トランジスタ 133 と p チャネル型トランジスタ 134 を有する。

#### 【 0047 】

n チャネル型トランジスタ 131 のソース及びドレインの一方には電位 V1 が与えられる、p チャネル型トランジスタ 132 のソース及びドレインの一方には電位 V2 が与えられる。n チャネル型トランジスタ 131 のソース及びドレインの他方と p チャネル型トランジスタ 132 のソース及びドレインの他方とは電気的に接続されている。n チャネル型トランジスタ 131 のゲートと p チャネル型トランジスタ 132 のゲートが位相反転素子 101 の入力端子となる。n チャネル型トランジスタ 131 のソース及びドレインの他方と p チャネル型トランジスタ 132 のソース及びドレインの他方が、位相反転素子 101 の出力端子となる。40

#### 【 0048 】

n チャネル型トランジスタ 133 のソース及びドレインの一方には電位 V1 が与えられる、p チャネル型トランジスタ 134 のソース及びドレインの一方には電位 V2 が与えられる。n チャネル型トランジスタ 133 のソース及びドレインの他方と p チャネル型トランジスタ 134 のソース及びドレインの他方とは電気的に接続されている。n チャネル型ト50

ランジスタ 133 のゲートと p チャネル型トランジスタ 134 のゲートが位相反転素子 102 の入力端子となる。n チャネル型トランジスタ 133 のソース及びドレインの他方と p チャネル型トランジスタ 134 のソース及びドレインの他方が、位相反転素子 102 の出力端子となる。

#### 【 0049 】

位相反転素子 101 及び位相反転素子 102 において電源電圧の供給がある場合は電位 V2 > 電位 V1 となる。電位 V1 と電位 V2 の差が位相反転素子 101 及び位相反転素子 102 の電源電圧である。例えば、位相反転素子 101 及び位相反転素子 102 において電源電圧の供給がある場合に、電位 V2 を電位 VDD とし、電位 V1 を電位 VSS とすることができる。また、電位 VSS は基準電位 (GND) とすることができる。一方、位相反転素子 101 及び位相反転素子 102 において電源電圧の供給が停止した場合は、例えば、電位 V1 と電位 V2 の一方または両方が供給されなくなった場合に対応する。また例えば、電位 V1 と電位 V2 が共に基準電位 (GND) となつた場合に対応する。10

#### 【 0050 】

また、本発明の一態様では、少なくとも、トランジスタ 111 とトランジスタ 112 が、酸化物半導体層にチャネルが形成されるトランジスタであればよい。よって、位相反転素子 101 及び位相反転素子 102 に用いられるトランジスタ、選択トランジスタ 103、選択トランジスタ 104 は、酸化物半導体以外の半導体でなる半導体層または半導体基板にチャネルが形成されるトランジスタを用いることができる。酸化物半導層には、例えば、In-Ga-Zn-O 系の酸化物半導体材料を用いることができる。また、酸化物半導体以外の半導体は、非晶質、微結晶、多結晶、または単結晶とすることができます、シリコンまたはゲルマニウムとすることができる。20

#### 【 0051 】

トランジスタ 111 とトランジスタ 112 に用いられているトランジスタは、高純度化された酸化物半導体層にチャネルが形成されるトランジスタとすることができます。当該トランジスタは、そのオフ電流密度を  $100 \text{ zA} / \mu\text{m}$  以下、好ましくは  $10 \text{ zA} / \mu\text{m}$  以下、更に好ましくは  $1 \text{ zA} / \mu\text{m}$  以下にすることができる。よって、このオフ電流が、結晶性を有するシリコンを用いたトランジスタのオフ電流に比べて著しく低い。その結果、トランジスタ 111 とトランジスタ 112 がオフ状態である時、容量素子 121 及び容量素子 122 に蓄積された電荷は殆ど放電しないため、記憶素子 100 のデータは保持される。30

#### 【 0052 】

なお、上記において、酸化物半導体材料の代わりに酸化物半導体材料と同等のオフ電流特性が実現できる材料、例えば、炭化シリコンをはじめとするワイドギャップ材料（より具体的には、例えば、エネルギーギャップ Eg が  $3 \text{ eV}$  より大きい半導体材料）などを適用しても良い。

#### 【 0053 】

次いで、図 1 (A) や図 1 (B) に示す記憶素子 100 の動作の一例について説明する。電源電圧の供給の後、データの保持時における消費電力を削減するために電源電圧の供給を停止し、再び電源電圧を供給する場合の記憶素子 100 の動作について、図 2 のタイミングチャートを参照して説明する。40

#### 【 0054 】

なお、タイミングチャートでは、選択トランジスタ 103、選択トランジスタ 104、トランジスタ 111、トランジスタ 112 が全て n チャネル型トランジスタの場合を例にし、ゲートにハイレベルの電位が入力されたときにトランジスタがオン状態となり、ゲートにローレベルの電位が入力されたときにトランジスタがオフ状態となる例を示しているがこれに限定されない。選択トランジスタ 103、選択トランジスタ 104、トランジスタ 111、トランジスタ 112 は n チャネル型トランジスタでも p チャネル型トランジスタでもよい。トランジスタの状態（オン状態であるかオフ状態であるか）が下記説明と同様になるよう、各信号の電位を定めればよい。50

**【0055】**

また、信号INがハイレベルの場合をデータ”1”に対応させ、ローレベルの場合をデータ”0”に対応させた例を示すがこれに限定されない。信号INがローレベルの場合をデータ”1”に対応させ、ハイレベルの場合をデータ”0”に対応させてもよい。

**【0056】**

はじめに、記憶素子100に電源電圧（図2中、Vで示す）が供給されている場合について説明する。つまり、位相反転素子101及び位相反転素子102に電源電圧が供給されている場合について説明する。この場合は図2中の期間1に対応する。制御信号S1及び制御信号S2をハイレベルとしてトランジスタ111及びトランジスタ112をオン状態とした状態で、制御信号S3をハイレベルにすることによって選択トランジスタ103をオン状態にする。こうして、位相反転素子101の入力端子に信号INを入力する。信号INは、選択トランジスタ103がオン状態の間（即ち、制御信号S3がハイレベルの間）は記憶するデータに対応した電位を有する。ここでは、例えば、データ”1”に対応するハイレベルの電位であるとする。このハイレベルの電位が位相反転素子101の入力端子に入力される。その後、制御信号S3をローレベルとして選択トランジスタ103をオフ状態とすることによって位相反転素子101及び位相反転素子102でなる帰還ループによって入力されたデータが保持される。また、位相反転素子102の入力端子の電位は容量素子122に保持され、位相反転素子101の入力端子の電位は容量素子121に保持される。なお、データの入力及び保持の間、制御信号S4はローレベルであり、選択トランジスタ104はオフ状態である。なお、データの保持が完了した後、制御信号S4をハイレベルとして選択トランジスタ104をオン状態とすることによって、信号OUTを出力する。信号OUTは、位相反転素子101及び位相反転素子102によって保持されているデータが反映される。よって、信号OUTの電位を読み取ることで記憶素子100からデータを読み出すことができる。図2のタイミングチャートの期間1では、位相反転素子101及び位相反転素子102によってデータ”1”が保持されたため、制御信号S4をハイレベルとして選択トランジスタ104をオン状態とした間は、信号OUTはローレベルとなる。

**【0057】**

次に、データの保持が完了した後、データの保持時における消費電力を削減するために記憶素子100への電源電圧の供給を停止する場合について説明する。つまり、位相反転素子101及び位相反転素子102への電源電圧の供給を停止する場合について説明する。この場合は図2中の期間2に対応する。電源電圧の供給を停止する前に、制御信号S1及び制御信号S2をローレベルとしてトランジスタ111及びトランジスタ112をオフ状態にする（図2中、期間2の開始間際を参照）。ここで、トランジスタ111及びトランジスタ112はオフ電流が非常に小さいため、位相反転素子102の入力端子の電位は容量素子122に保持されており、位相反転素子101の入力端子の電位は容量素子121に保持されている。こうして、位相反転素子101及び位相反転素子102への電源電圧の供給を停止しても、記憶素子100にデータを保持させ続けることが可能である。位相反転素子101及び位相反転素子102への電源電圧の供給を停止している間は、制御信号S1及び制御信号S2はローレベルであり、トランジスタ111及びトランジスタ112はオフ状態である。位相反転素子101及び位相反転素子102への電源電圧の供給を停止している間は、記憶素子100から信号OUTを出力することはできず、また記憶素子100に新たな信号INを入力して保持することはできない。

**【0058】**

なお、記憶素子100への電源電圧の供給を停止する場合には、記憶素子100への電源電圧の供給を停止する前に、トランジスタ111及びトランジスタ112をオフ状態にする必要がある。仮に、記憶素子100への電源電圧の供給を停止した後、トランジスタ111及びトランジスタ112をオフ状態にすると以下のようないくつかの問題が生じる。記憶素子100への電源電圧の供給停止によって、位相反転素子101及び位相反転素子102でなる帰還ループにおいてデータを保持することができなくなる。そのため、記憶素子100

10

20

30

40

50

0への電源電圧の供給停止後にトランジスタ111及びトランジスタ112をオフ状態にしても、容量素子121及び容量素子122にデータを保持することができない。よって、記憶素子100への電源電圧の供給を停止する場合には、記憶素子100への電源電圧の供給を停止する前に、トランジスタ111及びトランジスタ112をオフ状態にする必要がある。

#### 【0059】

なお、図2では、期間1において記憶素子100にデータを保持させ、当該データを読み出した後、期間2の動作を行う例を示したがこれに限定されない。期間1において記憶素子100にデータを保持させ、当該データを読み出すことなく期間2の動作を行っても良い。

10

#### 【0060】

次に再び記憶素子へ電源電圧を供給する場合について説明する。この場合は図2中の期間3に対応する。位相反転素子101及び位相反転素子102に電源電圧を供給した後、制御信号S1及び制御信号S2をハイレベルとしてトランジスタ111及びトランジスタ112をオン状態とする。位相反転素子102の入力端子の電位は容量素子122に保持されており、位相反転素子101の入力端子の電位は容量素子121に保持されているため、記憶素子への電源電圧の供給停止前の状態が再現される。ここで、制御信号S4をハイレベルにすると信号OUTはローレベルとなる。この様にして記憶素子への電源電圧の供給を停止しても、データを保持することが可能である。その後、上記期間1における動作と同様の動作によって、データを入力し、保持し、出力することができる。

20

#### 【0061】

なお、記憶素子100への電源電圧の供給を再開する場合には、記憶素子100への電源電圧の供給を再開した後に、トランジスタ111及びトランジスタ112をオン状態にする必要がある。仮に、記憶素子100への電源電圧の供給を再開する前に、トランジスタ111及びトランジスタ112をオン状態にすると以下のようないい問題が生じる。トランジスタ111及びトランジスタ112をオン状態しても、記憶素子100への電源電圧の供給再開がされていないため、位相反転素子101及び位相反転素子102でなる帰還ループにおいてデータを保持することができない。よって、記憶素子100への電源電圧の供給を再開する場合には、記憶素子100への電源電圧の供給を再開した後に、トランジスタ111及びトランジスタ112をオン状態にする必要がある。

30

#### 【0062】

以上が、記憶素子100において、電源電圧の供給の後、電源電圧の供給を停止し、再び電源電圧を供給する場合の駆動方法である。

#### 【0063】

酸化物半導体層にチャネルが形成されるトランジスタはオフ電流が極めて小さい。例えば、酸化物半導体層にチャネルが形成されるトランジスタのオフ電流は、結晶性を有するシリコンにチャネルが形成されるトランジスタのオフ電流に比べて著しく低い。そのため、当該トランジスタをトランジスタ111及びトランジスタ112として用いることによって、記憶素子100に電源電圧が供給されない間も容量素子121及び容量素子122に保持された電位は保たれる。こうして、記憶素子100は電源電圧の供給が停止した間も記憶内容を保持することが可能である。

40

#### 【0064】

記憶素子100は電源電圧の供給が停止した間も、容量素子122に保持された電位によって位相反転素子102の入力端子の電位が保持され、容量素子121に保持された電位によって位相反転素子101の入力端子の電位が保持されている。つまり、位相反転素子101の入力端子の電位と位相反転素子102の入力端子の電位の両方が保持されている。

#### 【0065】

一方、例えば、記憶素子100が容量素子122とトランジスタ112を有し、容量素子121とトランジスタ111を有さない構成の場合を考える。つまり、位相反転素子1

50

02の出力端子が位相反転素子101の入力端子に直接接続されている場合を考える。この構成では、容量素子122に保持された電位によって位相反転素子102の入力端子の電位は保持されるが、位相反転素子101の入力端子の電位は保持されない。そのため、記憶素子100への電源電圧の供給が再開した後、トランジスタ112をオン状態とすると、位相反転素子101の入力端子の電位が所定の電位（位相反転素子102の出力によって定まる電位）となるように電荷の移動が生じる。この電荷の移動が完了するまで記憶素子100はデータを出力することができない。そのため、記憶素子100がデータを出力できるようになるまでの時間（以下、立ち上げ時間ともいう）が長くなる。つまり、電源供給停止前の状態に復帰するために時間がかかる。

## 【0066】

10

図1に示した構成では、記憶素子100は電源電圧の供給が停止した間も、位相反転素子101の入力端子の電位と位相反転素子102の入力端子の電位の両方が保持されている。そのため、記憶素子100への電源電圧の供給が再開された後、トランジスタ111及びトランジスタ112をオン状態としても、位相反転素子102の入力端子や位相反転素子101の入力端子の電位が所定の電位となるように電荷が移動する必要がなく、立ち上げ時間を短くすることができる。

## 【0067】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

## 【0068】

20

## (実施の形態2)

本実施の形態では、実施の形態1で示した記憶素子を複数用いた記憶装置の構成について説明する。

## 【0069】

30

図3(A)に、本実施の形態における記憶装置の構成を一例として示す。図3(A)に示す記憶装置は、スイッチング素子401と、記憶素子402を複数有する記憶素子群403とを有している。具体的に、各記憶素子402には、実施の形態1に記載されている構成を有する記憶素子100を用いることができる。記憶素子群403が有する各記憶素子402には、スイッチング素子401を介して、ハイレベルの電源電位VDDが供給されている。さらに、記憶素子群403が有する各記憶素子402には、信号INの電位と、ローレベルの電源電位VSSの電位が与えられている。

## 【0070】

図3(A)では、スイッチング素子401として、トランジスタを用いており、該トランジスタは、そのゲート電極に与えられる制御信号SigAによりスイッチングが制御される。

## 【0071】

なお、図3(A)では、スイッチング素子401がトランジスタを一つだけ有する構成を示しているが、本発明はこの構成に限定されない。本発明の一態様では、スイッチング素子401が、トランジスタを複数有していても良い。スイッチング素子401が、スイッチング素子として機能するトランジスタを複数有している場合、上記複数のトランジスタは並列に電気的に接続されていても良いし、直列に電気的に接続されていても良いし、直列と並列が組み合わされて電気的に接続されていても良い。

40

## 【0072】

また、図3(A)では、スイッチング素子401により、記憶素子群403が有する各記憶素子402への、ハイレベルの電源電位VDDの供給が制御されているが、スイッチング素子401により、ローレベルの電源電位VSSの供給が制御されていても良い。図3(B)に、記憶素子群403が有する各記憶素子402に、スイッチング素子401を介して、ローレベルの電源電位VSSが供給されている記憶装置の一例を示す。スイッチング素子401により、記憶素子群403が有する各記憶素子402への、ローレベルの電源電位VSSの供給を制御することができる。

## 【0073】

50

本実施の形態は、上記実施の形態と適宜組み合わせて実施することが可能である。

**【0074】**

(実施の形態3)

本実施の形態では、実施の形態1で示した記憶素子や、実施の形態2で示した記憶装置を用いた信号処理回路の構成について説明する。

**【0075】**

図4に、本発明の一態様に係る信号処理回路の一例を示す。信号処理回路は、一または複数の演算回路と、一または複数の記憶装置とを少なくとも有する。具体的に、図4に示す信号処理回路150は、演算回路151、演算回路152、記憶装置153、記憶装置154、記憶装置155、制御装置156、電源制御回路157を有する。

10

**【0076】**

演算回路151、演算回路152は、単純な論理演算を行う論理回路をはじめ、加算器、乗算器、さらには各種演算回路などを含む。そして、記憶装置153は、演算回路151における演算処理の際に、データを一時的に保持するレジスタとして機能する。記憶装置154は、演算回路152における演算処理の際に、データを一時的に保持するレジスタとして機能する。

**【0077】**

また、記憶装置155はメインメモリとして用いることができ、制御装置156が実行するプログラムをデータとして記憶する、或いは演算回路151、演算回路152からのデータを記憶することができる。

20

**【0078】**

制御装置156は、信号処理回路150が有する演算回路151、演算回路152、記憶装置153、記憶装置154、記憶装置155の動作を統括的に制御する回路である。なお、図4では、制御装置156が信号処理回路150の一部である構成を示しているが、制御装置156は信号処理回路150の外部に設けられても良い。

**【0079】**

実施の形態1で示した記憶素子や、実施の形態2で示した記憶装置を記憶装置153、記憶装置154、記憶装置155に用いることで、記憶装置153、記憶装置154、記憶装置155への電源電圧の供給を停止しても、データを保持することができる。よって、信号処理回路150全体への電源電圧の供給を停止し、消費電力を抑えることができる。或いは、記憶装置153、記憶装置154、または記憶装置155のいずれか一つまたは複数への電源電圧の供給を停止し、信号処理回路150の消費電力を抑えることができる。また、電源電圧の供給を再開した後、短時間で電源供給停止前の状態に復帰することができる。

30

**【0080】**

また、記憶装置への電源電圧の供給が停止されるのに合わせて、当該記憶装置とデータのやり取りを行う演算回路または制御回路への、電源電圧の供給を停止するようにしても良い。例えば、演算回路151と記憶装置153において、動作が行われない場合、演算回路151及び記憶装置153への電源電圧の供給を停止するようにしても良い。

**【0081】**

40

また、電源制御回路157は、信号処理回路150が有する演算回路151、演算回路152、記憶装置153、記憶装置154、記憶装置155、制御装置156へ供給する電源電圧の大きさを制御する。そして、電源電圧の供給を停止する場合、電源電圧の供給を停止するためのスイッチング素子は、電源制御回路157に設けられていても良いし、演算回路151、演算回路152、記憶装置153、記憶装置154、記憶装置155、制御装置156のそれぞれに設けられていても良い。後者の場合、電源制御回路157は、必ずしも本発明の信号処理回路に設ける必要はない。

**【0082】**

なお、メインメモリである記憶装置155と、演算回路151、演算回路152、制御装置156の間に、キャッシュメモリとして機能する記憶装置を設けても良い。キャッシ

50

ユメモリを設けることで、低速なメインメモリへのアクセスを減らして演算処理などの信号処理を高速化させることができる。キャッシュメモリとして機能する記憶装置にも、上述した記憶素子を用いることで、信号処理回路150の消費電力を抑えることができる。また、電源電圧の供給を再開した後、短時間で電源供給停止前の状態に復帰することができる。

#### 【0083】

本実施の形態は、上記実施の形態と適宜組み合わせて実施することが可能である。

#### 【0084】

##### (実施の形態4)

本実施の形態では、本発明の一態様に係る信号処理回路の一つである、CPUの構成について説明する。 10

#### 【0085】

図5に、本実施の形態のCPUの構成を示す。図5に示すCPUは、基板900上に、ALU901、ALU・Controller902、Instruction・Decoder903、Interrupt・Controller904、Timing・Controller905、Register906、Register・Controller907、Bus・I/F908、書き換え可能なROM909、ROM・I/F920と、を主に有している。なお、ALUはArithmetic logic unitであり、Bus・I/Fはバスインターフェースであり、ROM・I/FはROMインターフェースである。ROM909及びROM・I/F920は、別チップに設けても良い。勿論、図5に示すCPUは、その構成を簡略化して示した一例にすぎず、実際のCPUはその用途によって多種多様な構成を有している。 20

#### 【0086】

Bus・I/F908を介してCPUに入力された命令は、Instruction・Decoder903に入力され、デコードされた後、ALU・Controller902、Interrupt・Controller904、Register・Controller907、Timing・Controller905に入力される。

#### 【0087】

ALU・Controller902、Interrupt・Controller904、Register・Controller907、Timing・Controller905は、デコードされた命令に基づき、各種制御を行なう。具体的にALU・Controller902は、ALU901の動作を制御するための信号を生成する。また、Interrupt・Controller904は、CPUのプログラム実行中に、外部の入出力装置や、周辺回路からの割り込み要求を、その優先度やマスク状態から判断し、処理する。Register・Controller907は、Register906のアドレスを生成し、CPUの状態に応じてRegister906の読み出しや書き込みを行なう。 30

#### 【0088】

またTiming・Controller905は、ALU901、ALU・Controller902、Instruction・Decoder903、Interrupt・Controller904、Register・Controller907の動作のタイミングを制御する信号を生成する。例えばTiming・Controller905は、基準クロック信号CLK1を元に、内部クロック信号CLK2を生成する内部クロック生成部を備えており、クロック信号CLK2を上記各種回路に供給する。 40

#### 【0089】

本実施の形態のCPUでは、Register906に、上記実施の形態で示した構成を有する記憶素子が設けられている。Register・Controller907は、ALU901からの指示に従い、Register906が有する記憶素子において、位相反転素子の帰還ループによるデータの保持（トランジスタ111及びトランジスタ112がオン状態の場合に対応）を行うか、容量素子によるデータの保持（トランジスタ1 50

11 及びトランジスタ 112 をオフ状態とする場合に対応)を行うかを選択する。位相反転素子の帰還ループによるデータの保持が選択されている場合、Register 906 内の記憶素子への電源電圧の供給が行われる。容量素子におけるデータの保持が選択されている場合、Register 906 内の記憶素子への電源電圧の供給を停止することができる。電源停止に関しては、図 3 に示すように、記憶素子群と、電源電位 VDD または電源電位 VSS の与えられているノード間に、スイッチング素子を設けることにより行うことができる。

#### 【0090】

この様にして、一時的に CPU の動作を停止し、電源電圧の供給を停止した場合においてもデータを保持することが可能であり、消費電力の低減を行うことができる。具体的には、例えば、パーソナルコンピュータのユーザーが、キーボードなどの入力装置への情報の入力を停止している間でも、CPU を停止することができ、それにより消費電力を低減することができる。

#### 【0091】

本実施の形態では、CPU を例に挙げて説明したが、本発明の信号処理回路は CPU に限定されず、マイクロプロセッサ、画像処理回路、DSP、FPGA 等の LSI にも応用可能である。

#### 【0092】

本実施の形態は、上記実施の形態と組み合わせて実施することが可能である。

#### 【0093】

##### (実施の形態 5)

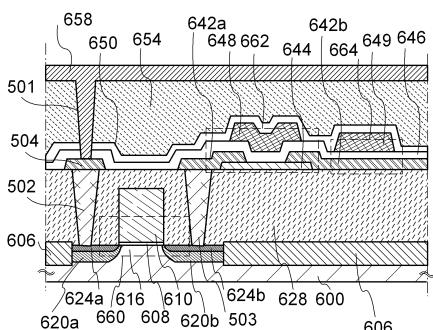

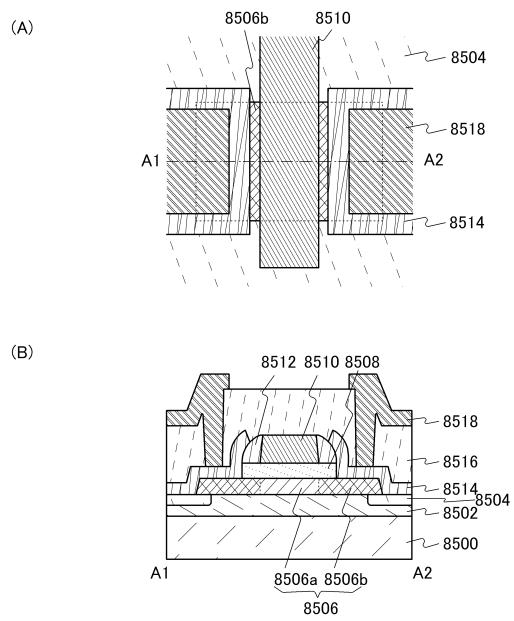

本実施の形態では、信号処理回路を構成するトランジスタ等の構成について、図 6 乃至図 9、図 17 を参照して説明する。

#### 【0094】

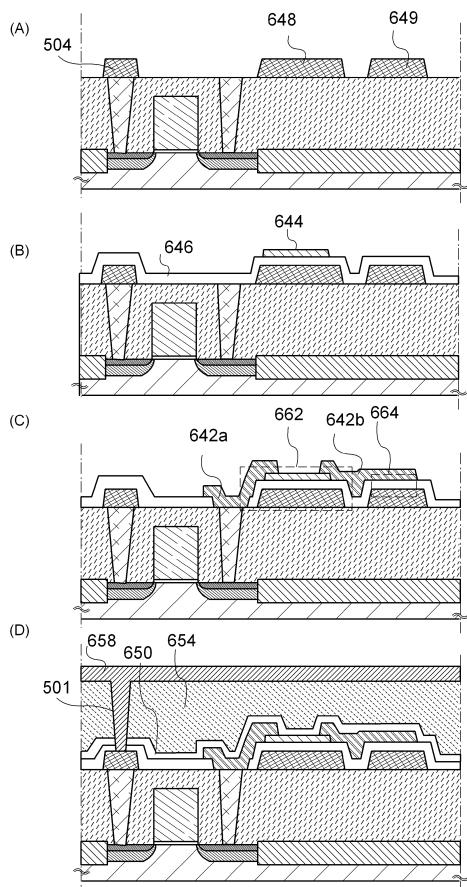

図 6 は、図 1 の回路図で示した記憶素子 100 の構成の一例である。図 6 では記憶素子 100 を構成する素子のうち、2 つのトランジスタ (トランジスタ 660 及びトランジスタ 662)、1 つの容量素子 664 の断面を示す。トランジスタ 662 は酸化物半導体層にチャネルが形成されるトランジスタである。トランジスタ 662 は図 1 におけるトランジスタ 111 やトランジスタ 112 とすることができます。トランジスタ 660 は酸化物半導体以外の半導体 (例えばシリコン等) にチャネルが形成されるトランジスタである。トランジスタ 660 は図 1 における選択トランジスタ 103、選択トランジスタ 104、位相反転素子を構成するトランジスタ (図 1 (B) における n チャネル型トランジスタ 131、p チャネル型トランジスタ 132、n チャネル型トランジスタ 133、p チャネル型トランジスタ 134) とすることができます。容量素子 664 は図 1 における容量素子 121、容量素子 122 とすることができます。

#### 【0095】

図 6 に示す構成では、トランジスタ 660 のソースとドレインの一方がトランジスタ 662 のソースとドレインの一方と接続され、トランジスタ 662 のソースとドレインの他方が容量素子 664 の一対の電極のうちの一方と接続されている例を示す。このような構成の一例として、トランジスタ 660 を図 1 における選択トランジスタ 103 とし、トランジスタ 662 を図 1 におけるトランジスタ 111 とし、容量素子 664 を図 1 における容量素子 121 とした場合について説明する。

#### 【0096】

なお、トランジスタ 660 及びトランジスタ 662 は、いずれも n チャネル型トランジスタであるものとして説明するが、p チャネル型トランジスタを用いることができるのいうまでもない。

#### 【0097】

図 6 におけるトランジスタ 660 は、半導体材料 (例えばシリコン等) を含む基板 600 に設けられたチャネル形成領域 616 と、チャネル形成領域 616 を挟むように設けられた不純物領域 620a 及び不純物領域 620b と、不純物領域 620a 及び不純物領域

10

20

30

40

50

620bに接する金属化合物領域624a及び金属化合物領域624bと、チャネル形成領域616上に設けられたゲート絶縁層608と、ゲート絶縁層608上に設けられたゲート電極610とを有する。また、基板600上には素子分離絶縁層606が設けられている。

#### 【0098】

なお、図において明示的にはソース電極やドレイン電極を有しない場合があるが、便宜上、このような状態を含めてトランジスタと呼ぶ場合がある。また、この場合、トランジスタの接続関係を説明するために、ソース領域やドレイン領域を含めてソース電極やドレイン電極と表現することがある。つまり、本明細書において、ソース電極との記載にはソース領域が、ドレイン電極との記載にはドレイン領域が、含まれうる。

10

#### 【0099】

なお、本明細書中において、不純物領域620a、不純物領域620bをまとめて、不純物領域620と記載する場合がある。本明細書中において、金属化合物領域624a、金属化合物領域624bをまとめて、金属化合物領域624と記載する場合がある。

#### 【0100】

トランジスタ660上に、絶縁層628が設けられている。なお、高集積化を実現するためには、図6に示すようにトランジスタ660がサイドウォール絶縁層を有しない構成とすることが望ましい。一方で、トランジスタ660の特性を重視する場合には、ゲート電極610の側面にサイドウォール絶縁層を設け、不純物濃度が互いに異なる複数の領域を含む不純物領域620を設けても良い。絶縁層628は、平坦性の良好な表面を有しているのが好ましく、例えば、絶縁層628の表面は、二乗平均平方根(RMS)粗さを1nm以下とすることが好ましい。このように、二乗平均平方根(RMS)粗さが1nm以下という極めて平坦な領域にトランジスタ662のチャネル形成領域(酸化物半導体層644)を設けることにより、トランジスタ662が微細化される状況においても、短チャネル効果などの不具合を防止し、良好な特性を有するトランジスタ662を提供することが可能である。

20

#### 【0101】

図6におけるトランジスタ662は、絶縁層628上に形成された酸化物半導体層644と、酸化物半導体層644と一部が接する電極642a及び電極642bと、酸化物半導体層644と電極642aと電極642bとを覆うゲート絶縁層646と、ゲート絶縁層646上に酸化物半導体層644と重畳するように設けられたゲート電極648とを有する。電極642aは、絶縁層628に設けられた開口部に形成された電極503によってトランジスタ660の金属化合物領域624bと接続されている。

30

#### 【0102】

なお、本明細書中において、電極642a、電極642bをまとめて、電極642と記載する場合がある。

#### 【0103】

ここで、酸化物半導体層644は水素などの不純物が十分に除去されることにより、または、十分な酸素が供給されることにより、高純度化されたものであることが望ましい。具体的には、例えば、酸化物半導体層644の水素濃度は $5 \times 10^{19}$ atoms/cm<sup>3</sup>以下、望ましくは $5 \times 10^{18}$ atoms/cm<sup>3</sup>以下、より望ましくは $5 \times 10^{17}$ atoms/cm<sup>3</sup>以下とする。また、酸化物半導体層644のアルカリ金属元素の濃度を低減させるとよい。例えば、Naの濃度は $5 \times 10^{16}$ atoms/cm<sup>3</sup>以下、好ましくは $1 \times 10^{16}$ atoms/cm<sup>3</sup>以下、さらに好ましくは $1 \times 10^{15}$ atoms/cm<sup>3</sup>以下とし、Liの濃度は $5 \times 10^{15}$ atoms/cm<sup>3</sup>以下、好ましくは $1 \times 10^{15}$ atoms/cm<sup>3</sup>以下とし、Kの濃度は $5 \times 10^{15}$ atoms/cm<sup>3</sup>以下、好ましくは $1 \times 10^{15}$ atoms/cm<sup>3</sup>以下とするとよい。

40

#### 【0104】

酸化物半導体は不純物に対して鈍感であり、膜中にはかなりの金属不純物が含まれていること、廉価なソーダ石灰ガラスも使えると指摘されている(神谷、野村、細野、「アモ

50

ルファス酸化物半導体の物性とデバイス開発の現状」、固体物理、2009年9月号、Vol. 44、pp. 621 - 633。)。しかし、このような指摘は適切でない。アルカリ金属、及びアルカリ土類金属は酸化物半導体層644にとっては悪性の不純物であり、少ないほうがよい。特にアルカリ金属のうち、Naは酸化物半導体層に接する絶縁膜が酸化物であった場合、その中に拡散し、 $\text{Na}^+$ となる。また、酸化物半導体層内において、金属と酸素の結合を分断し、あるいは結合中に割り込む。その結果、トランジスタ特性の劣化(例えば、ノーマリオン化(しきい値の負へのシフト)、移動度の低下等)をもたらす。加えて、トランジスタの特性のばらつきの原因ともなる。このような問題は、特に酸化物半導体層中の水素の濃度が十分に低い場合において顕著となる。したがって、酸化物半導体層中の水素の濃度が  $5 \times 10^{19}$  atoms/cm<sup>3</sup> 以下、特に  $5 \times 10^{18}$  atoms/cm<sup>3</sup> 以下である場合には、アルカリ金属元素の濃度を上記の値にすることが強く求められる。

10

#### 【0105】

なお、上述の酸化物半導体層644中の水素濃度、アルカリ金属元素の濃度は、二次イオン質量分析法(SIMS: Secondary Ion Mass Spectroscopy)で測定されるものである。このように、アルカリ金属元素濃度や水素濃度が十分に低減されて高純度化され、十分な酸素の供給により酸素欠乏に起因するエネルギーギャップ中の欠陥準位が低減された酸化物半導体層644では、アルカリ金属元素や水素等のドナーに起因するキャリア密度が  $1 \times 10^{12}$  / cm<sup>3</sup> 未満、望ましくは、 $1 \times 10^{11}$  / cm<sup>3</sup> 未満、より望ましくは  $1.45 \times 10^{10}$  / cm<sup>3</sup> 未満となる。また、例えば、室温(25)でのオフ電流(ここでは、単位チャネル幅(1 μm)あたりの値)は100 zA(1 zA(ゼプトアンペア)は  $1 \times 10^{-21}$  A)以下、望ましくは10 zA以下となる。このように、i型化(真性化)または実質的にi型化された酸化物半導体を用いることで、極めて優れたオフ電流特性のトランジスタ662を得ることができる。

20

#### 【0106】

図6における容量素子664は、絶縁層628上に形成された電極642bと、ゲート絶縁層646と、電極649とを有する。つまり、容量素子664は、電極642bを一方の電極とし、電極649を他方の電極とし、ゲート絶縁層646を誘電体層とする。

#### 【0107】

トランジスタ662の上には、絶縁層650が設けられており、絶縁層650上には絶縁層654が設けられている。そして、絶縁層654上には配線658が形成される。ここで、配線658は、図1に示す回路における信号INが入力される配線とことができる。

30

#### 【0108】

配線658は、絶縁層654、絶縁層650、ゲート絶縁層646に形成された開口部501において、電極504と接続されている。また、電極504は、絶縁層628に設けられた開口部に形成された電極502によって、トランジスタ660の金属化合物領域624aと接続されている。こうして、配線658は、トランジスタ660のソースまたはドレンの一方と電気的に接続されている。

40

#### 【0109】

なお、開示する発明に係る記憶素子の構成は、図6に示されるものに限定されない。図6に示される構成において電極の接続関係等の詳細については適宜変更することができる。

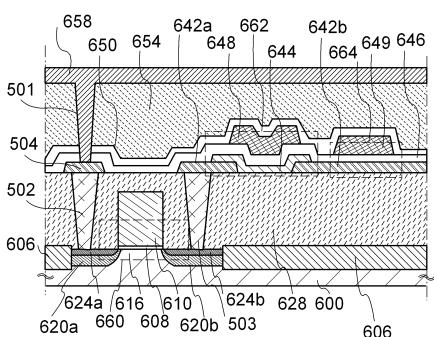

#### 【0110】

例えば、図6に示す構成では、酸化物半導体層644が電極642の下に配置される例を示した。しかしこれに限定されず、酸化物半導体層644を電極642の上に設けてよい。酸化物半導体層644を電極642の上に設けた例を図7に示す。なお、図7において図6と同じ部分は同じ符号を用いて示す。

#### 【0111】

図7に示した構成において、電極642a及び電極642bの端部は、テーパー形状で

50

あることが好ましい。電極 642a 及び電極 642b の端部をテーパー形状とすることにより、酸化物半導体層 644 の被覆性を向上し、段切れを防止することができるためである。ここで、テーパー角は、例えば、30°以上 60°以下とする。なお、テーパー角とは、テーパー形状を有する層（例えば、電極 642a）を、その断面（基板の表面と直交する面）に垂直な方向から観察した際に、当該層の側面と底面がなす傾斜角を示す。

#### 【0112】

なお、酸化物半導体層 644 の全体がゲート電極 648 や配線 658 と重なる（ゲート電極 648 や配線 658 で覆われる）構成とすることによって、上方からの光が酸化物半導体層 644 に入ることを抑制することもできる。こうして、酸化物半導体層 644 の光劣化を抑制することができる。

10

#### 【0113】

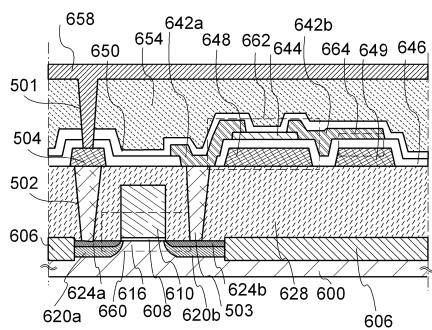

また、図 6 や図 7 に示す構成では、ゲート電極 648 が酸化物半導体層 644 の上に配置される例を示した。しかしこれに限定されず、ゲート電極 648 は酸化物半導体層 644 の下に設けてもよい。ゲート電極 648 を酸化物半導体層 644 の下に設けた例を図 8 に示す。なお、図 8 において図 6 や図 7 と同じ部分は同じ符号を用いて示す。

#### 【0114】

図 8 において、電極 642a はゲート絶縁層 646 に設けられた開口部において電極 503 と接続されている。

#### 【0115】

図 8 に示した構成において、ゲート電極 648 及び電極 649 の端部は、テーパー形状であることが好ましい。ゲート電極 648 及び電極 649 の端部をテーパー形状とすることにより、ゲート絶縁層 646 の被覆性を向上して、電極 642a とゲート電極 648 とのショートや、電極 642b とゲート電極 648 及び電極 649 とのショート等を防止することができる。ここで、テーパー角は、例えば、30°以上 60°以下とする。

20

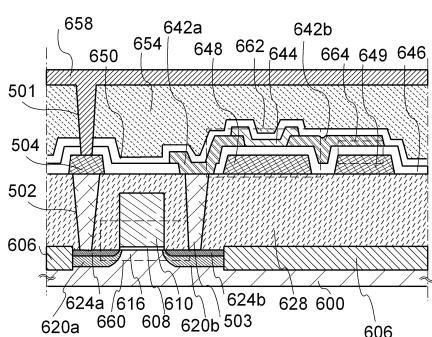

#### 【0116】

また、図 8 に示す構成において、酸化物半導体層 644 を電極 642 の上に設けてもよい。図 8 に示した構成において、酸化物半導体層 644 を電極 642 の上に設けた例を図 9 に示す。なお、図 9 において図 6 乃至図 8 と同じ部分は同じ符号を用いて示す。

#### 【0117】

図 8 及び図 9 では、ゲート電極 648 が酸化物半導体層 644 の下方に配置される構成を示した。この構成において、酸化物半導体層 644 の全体がゲート電極 648 と重なることによって、下方からの光が酸化物半導体層 644 に入ることを抑制することができる。こうして、酸化物半導体層 644 の光劣化を抑制することができる。更に、酸化物半導体層 644 の全体が配線 658 と重なる（配線 658 で覆われる）構成とすることによって、上方からの光が酸化物半導体層 644 に入ることを抑制することもできる。こうして、酸化物半導体層 644 の光劣化を更に抑制することができる。

30

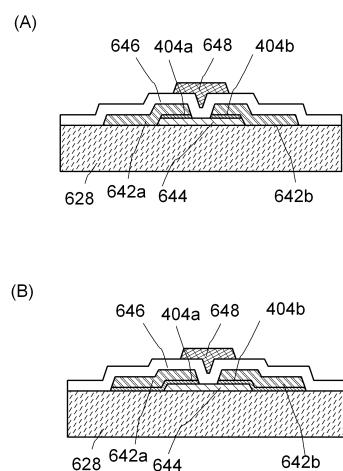

#### 【0118】

また、図 6 と図 8 に示した構成（酸化物半導体層 644 の上に電極 642a および電極 642b が配置される構成）において、酸化物半導体層 644 と電極 642a および電極 642b との間に、ソース領域及びドレイン領域となる酸化物導電層を設けることもできる。図 6 のトランジスタ 662 に酸化物導電層を設けたトランジスタを図 17 (A) 及び図 17 (B) に示す。なお、図 17 においてトランジスタ 662 以外の構成は記載を省略した。

40

#### 【0119】

図 17 (A) と図 17 (B) のトランジスタは、酸化物半導体層 644 と電極 642a 及び電極 642b との間に、ソース領域及びドレイン領域として機能する酸化物導電層 404a 及び酸化物導電層 404b が形成されている。図 17 (A) と図 17 (B) では作製工程により酸化物導電層 404a 及び酸化物導電層 404b の形状が異なる例である。

#### 【0120】

図 17 (A) のトランジスタでは、酸化物半導体膜と酸化物導電膜の積層を形成し、酸

50

化物半導体膜と酸化物導電膜との積層を同じフォトリソグラフィ工程によって加工して島状の酸化物半導体層 6 4 4 と酸化物導電膜を形成する。酸化物半導体層及び酸化物導電膜上に電極 6 4 2 a 及び電極 6 4 2 b を形成した後、電極 6 4 2 a 及び電極 6 4 2 b をマスクとして、島状の酸化物導電膜をエッティングし、ソース領域およびドレイン領域となる酸化物導電層 4 0 4 a、酸化物導電層 4 0 4 b を形成する。

#### 【0121】

図 17 (B) のトランジスタでは、島状の酸化物半導体層 6 4 4 を形成し、その上に酸化物導電膜を形成し、当該酸化物導電膜上に金属導電膜を形成し、酸化物導電膜および金属導電膜を同じフォトリソグラフィ工程によって加工して、ソース領域およびドレイン領域となる酸化物導電層 4 0 4 a、酸化物導電層 4 0 4 b、電極 6 4 2 a、及び電極 6 4 2 b を形成する。

10

#### 【0122】

なお、酸化物導電層 4 0 4 a 及び酸化物導電層 4 0 4 b を形成するためのエッティング処理の際、酸化物半導体層 6 4 4 が過剰にエッティングされないように、エッティング条件（エッティング材の種類、濃度、エッティング時間等）を適宜調整する。

#### 【0123】

酸化物導電層の材料としては、酸化亜鉛を成分として含むものが好ましく、酸化インジウムを含まないものであることが好ましい。そのような酸化物導電層して、酸化亜鉛、酸化亜鉛アルミニウム、酸窒化亜鉛アルミニウム、酸化亜鉛ガリウムなどを適用することができる。

20

#### 【0124】

金属電極（モリブデン、タンクスチレン等）と酸化物半導体層との接触に比べ、金属電極（モリブデン、タンクスチレン等）と酸化物導電層との接触は、接触抵抗を下げることができる。そのため、上記酸化物導電層を酸化物半導体層 6 4 4 と電極 6 4 2 a 及び電極 6 4 2 bとの間に設けることで、電極 6 4 2 a 及び電極 6 4 2 b と酸化物導電層との接触抵抗を低減できる。こうして、ソース及びドレインの低抵抗化図ることができ、トランジスタ 6 6 2 の高速動作を実現することができる。また、トランジスタ 6 6 2 の耐圧を向上させることもできる。

#### 【0125】

また、図 6 乃至図 9 に示した構成では、容量素子 6 6 4 の誘電体層としてトランジスタ 6 6 2 のゲート絶縁層 6 4 6 を用いる例を示したが、これに限定されない。容量素子 6 6 4 の誘電体層としてゲート絶縁層 6 4 6 とは異なる絶縁層を用いても良い。また、図 6 乃至図 9 に示した構成では、容量素子 6 6 4 の一対の電極のうちの一方として、トランジスタ 6 6 2 のソース電極またはドレイン電極として機能する電極 6 4 2 b を用いる例を示したが、これに限定されない。容量素子 6 6 4 の一対の電極のうちの一方として、電極 6 4 2 b とは異なる電極、例えば電極 6 4 2 b とは異なる層に形成された電極を用いても良い。また、図 6 乃至図 9 に示した構成では、容量素子 6 6 4 の一対の電極のうちの他方として、トランジスタ 6 6 2 のゲート電極 6 4 8 と同じ層に形成された電極 6 4 9 を用いる例を示したが、これに限定されない。容量素子 6 6 4 の一対の電極のうちの他方として、ゲート電極 6 4 8 とは異なる層に形成された電極を用いても良い。

30

#### 【0126】

図 6 乃至図 9 に示した構成では、トランジスタ 6 6 0 が半導体基板に形成される例を示した。しかしこれに限定されない。トランジスタ 6 6 0 は SOI 基板上に形成してもよい。なお、一般に「SOI 基板」は、絶縁表面上にシリコン半導体層が設けられた構成の基板をいうが、本明細書等においては、絶縁表面上にシリコン以外の材料からなる半導体層が設けられた構成の基板も含む概念として用いる。つまり、「SOI 基板」が有する半導体層は、シリコン半導体層に限定されない。また、トランジスタ 6 6 0 は、絶縁表面を有する基板上に形成されたシリコン等の半導体層を用いて形成してもよい。当該半導体層は、絶縁表面上に形成された非晶質半導体薄層を結晶化することによって形成されたものであってもよい。

40

50

**【 0 1 2 7 】**

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

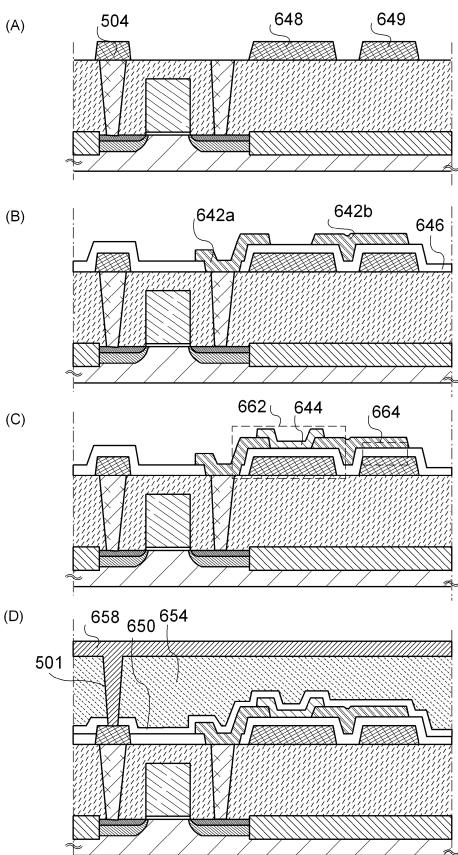

**【 0 1 2 8 】****( 実施の形態 6 )**

本実施の形態では、開示する発明の一態様に係る記憶素子の作製方法について、図 1 0 乃至図 1 5 を参照して説明する。

**【 0 1 2 9 】**

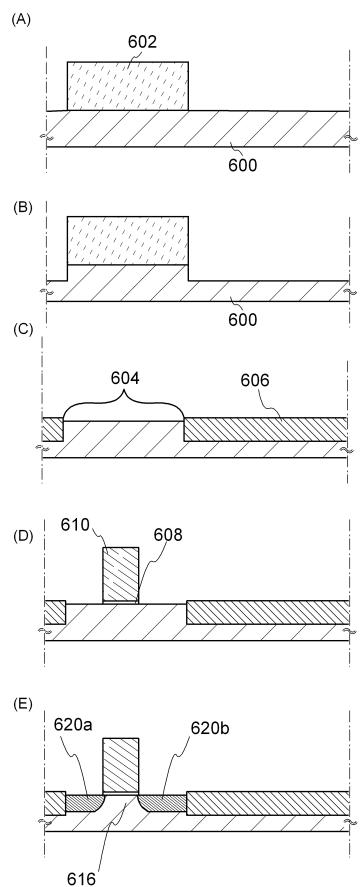

図 6 に示した記憶素子の作製方法の一例について説明する。以下では、はじめに下部のトランジスタ 6 6 0 の作製方法について図 1 0 及び図 1 1 を参照して説明し、その後、上部のトランジスタ 6 6 2 及び容量素子 6 6 4 の作製方法について図 1 2 乃至図 1 5 を参照して説明する。

10

**【 0 1 3 0 】****下部のトランジスタの作製方法**

まず、半導体材料を含む基板 6 0 0 を用意する（図 1 0 ( A ) 参照）。半導体材料を含む基板 6 0 0 としては、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコングルマニウムなどの化合物半導体基板、S O I 基板などを適用することができる。ここでは、半導体材料を含む基板 6 0 0 として、単結晶シリコン基板を用いる場合の一例について示すものとする。半導体材料を含む基板 6 0 0 として、特にシリコンなどの単結晶半導体基板を用いる場合には、記憶素子の読み出し動作を高速化することができるため好適である。

20

**【 0 1 3 1 】**

なお、トランジスタのしきい値電圧を制御するために、後にトランジスタ 6 6 0 のチャネル形成領域 6 1 6 となる領域に、導電型を付与する不純物元素を添加しても良い。ここでは、トランジスタ 6 6 0 のしきい値電圧が正となるように導電性を付与する不純物元素を添加する。半導体材料がシリコンの場合、当該導電性を付与する不純物として、例えば、硼素、アルミニウム、ガリウムなどを用いることができる。なお、導電型を付与する不純物元素の添加後には加熱処理を行い、不純物元素の活性化や不純物元素の添加時に基板 6 0 0 中に生じる欠陥の改善等を図るのが望ましい。

**【 0 1 3 2 】**

基板 6 0 0 上には、素子分離絶縁層を形成するためのマスクとなる保護層 6 0 2 を形成する（図 1 0 ( A ) 参照）。保護層 6 0 2 としては、例えば、酸化シリコンや窒化シリコン、酸窒化シリコンなどを材料とする絶縁層を用いることができる。

30

**【 0 1 3 3 】**

次に、保護層 6 0 2 をマスクとして基板 6 0 0 のエッティングを行い、基板 6 0 0 の保護層 6 0 2 に覆われていない領域（露出している領域）の一部を除去する。（図 1 0 ( B ) 参照）。当該エッティングには、ドライエッティングを用いるのが好適であるが、ウェットエッティングを用いても良い。エッティングガスやエッティング液については被エッティング材料に応じて適宜選択することができる。

**【 0 1 3 4 】**

次に、基板 6 0 0 を覆うように絶縁層を形成し、当該絶縁層を選択的に除去することで素子分離絶縁層 6 0 6 を形成する（図 1 0 ( C ) 参照）。当該絶縁層は、酸化シリコンや窒化シリコン、酸窒化シリコンなどを用いて形成される。絶縁層の除去方法としては、C M P ( 化学的機械的研磨 ) 処理などの研磨処理やエッティング処理などがあるが、そのいずれを用いても良い。これにより他の半導体領域と分離された半導体領域 6 0 4 が形成される。なお、保護層 6 0 2 をマスクとした基板 6 0 0 のエッティング後、または素子分離絶縁層 6 0 6 の形成後には、保護層 6 0 2 を除去する。

40

**【 0 1 3 5 】**

次に、半導体領域 6 0 4 の表面に絶縁層を形成し、当該絶縁層上に導電材料を含む層を形成する。

50

## 【0136】

絶縁層は後のゲート絶縁層となるものであり、例えば、半導体領域604表面の熱処理（熱酸化処理や熱窒化処理など）によって形成することができる。熱処理に代えて、高密度プラズマ処理を適用しても良い。高密度プラズマ処理は、例えば、He、Ar、Kr、Xeなどの希ガス、酸素、酸化窒素、アンモニア、窒素、水素などの混合ガスを用いて行うことができる。もちろん、CVD法やスパッタリング法等を用いて絶縁層を形成しても良い。当該絶縁層は、酸化シリコン、酸窒化シリコン、窒化シリコン、酸化ハフニウム、酸化アルミニウム、酸化タンタル、酸化イットリウム、ハフニウムシリケート(HfSi<sub>x</sub>O<sub>y</sub>(x>0, y>0))、窒素が添加されたハフニウムシリケート(HfSi<sub>x</sub>O<sub>y</sub>(x>0, y>0))、窒素が添加されたハフニウムアルミネート(HfAl<sub>x</sub>O<sub>y</sub>(x>0, y>0))等を含む単層構造または積層構造とすることが望ましい。また、絶縁層の厚さは、例えば、1nm以上100nm以下、好ましくは10nm以上50nm以下とすることができる。10

## 【0137】

導電材料を含む層は、アルミニウムや銅、チタン、タンタル、タングステン等の金属材料を用いて形成することができる。また、多結晶シリコンなどの半導体材料を用いて、導電材料を含む層を形成しても良い。導電材料を含む層の形成方法も特に限定されず、蒸着法、CVD法、スパッタリング法、スピンドル法などの各種成膜方法を用いることができる。なお、本実施の形態では、導電材料を含む層を金属材料を用いて形成する場合の一例について示すものとする。20

## 【0138】

その後、絶縁層及び導電材料を含む層を選択的にエッチングして、ゲート絶縁層608及びゲート電極610を形成する（図10（D）参照）。

## 【0139】

次に、半導体領域604にリン（P）やヒ素（As）などを添加して、チャネル形成領域616及び不純物領域620a、不純物領域620bを形成する（図10（E）参照）。なお、ここでは、トランジスタ660はnチャネル型トランジスタとし、nチャネル型トランジスタを形成するために半導体領域604にリンやヒ素などの導電型を付与する不純物元素を添加している。しかしながら、トランジスタ660をpチャネル型トランジスタとする場合には、半導体領域604に硼素（B）やアルミニウム（Al）などの導電型を付与する不純物元素を添加して、チャネル形成領域616及び不純物領域620a、不純物領域620bを形成すればよい。ここで、添加する導電型を付与する不純物元素の濃度は適宜設定することができるが、トランジスタ660が高度に微細化される場合には、その濃度を高くすることが望ましい。30

## 【0140】

なお、ゲート電極610の周囲にサイドウォール絶縁層を形成して、導電型を付与する不純物元素が異なる濃度で添加された複数の不純物領域（例えば、サイドウォール絶縁層と重ならない高濃度不純物領域と、サイドウォール絶縁層と重なる低濃度不純物領域）を半導体領域604に形成しても良い。

## 【0141】

次に、ゲート電極610、不純物領域620a及び不純物領域620bを覆うように金属層622を形成する（図11（A）参照）。金属層622は、真空蒸着法やスパッタリング法、スピンドル法などの各種成膜方法を用いて形成することができる。金属層622は、半導体領域604を構成する半導体材料と反応することによって低抵抗な金属化合物となる金属材料を用いて形成することが望ましい。このような金属材料としては、例えば、チタン、タンタル、タングステン、ニッケル、コバルト、白金等がある。40

## 【0142】

次に、熱処理を施して、金属層622と半導体領域604の表面の半導体材料とを反応させる。これにより、不純物領域620a及び不純物領域620bに接する金属化合物領域624a及び金属化合物領域624bが形成される（図11（A）参照）。なお、ゲー50

ト電極 610 として多結晶シリコンなどを用いる場合には、ゲート電極 610 の金属層 622 と接触する部分にも、金属化合物領域が形成されることになる。上記の金属化合物領域は十分に導電性が高められた領域である。当該金属化合物領域を形成することで、ソース及びドレイン等の電気抵抗を十分に低減し、トランジスタ 660 の素子特性を向上させることができる。

#### 【0143】

上記熱処理としては、例えば、フラッシュランプの照射による熱処理を用いることができる。もちろん、その他の熱処理方法を用いても良いが、金属化合物の形成に係る化学反応の制御性を向上させるためには、ごく短時間の熱処理を実現できる方法を用いることが望ましい。なお、金属化合物領域 624a 及び金属化合物領域 624b を形成した後には、金属層 622 は除去する。

10

#### 【0144】

こうして、半導体材料を含む基板 600 を用いたトランジスタ 660 が形成される（図 11（B）参照）。このようなトランジスタ 660 は高速動作が可能であるという特徴を有する。このため、トランジスタ 660 を用いることで、記憶素子は情報の読み出しを高速に行うことができる。

#### 【0145】

次に、上述の工程により形成されたトランジスタ 660 を覆うように、絶縁層 628 を形成する（図 11（C）参照）。絶縁層 628 は、酸化シリコン、酸窒化シリコン、窒化シリコン、酸化アルミニウム等の無機絶縁材料を含む材料を用いて形成することができる。特に、絶縁層 628 に誘電率の低い（low-k）材料を用いることで、各種電極や配線の重なりに起因する容量を十分に低減することが可能になるため好ましい。なお、絶縁層 628 には、これらの材料を用いた多孔質の絶縁層を適用しても良い。多孔質の絶縁層では、密度の高い絶縁層と比較して誘電率が低下するため、電極や配線に起因する容量をさらに低減することが可能である。また、絶縁層 628 は、ポリイミド、アクリル等の有機絶縁材料を用いて形成することも可能である。なお、ここでは、絶縁層 628 を単層構造としているが、開示する発明の一態様はこれに限定されない。絶縁層 628 を 2 層以上の積層構造としても良い。例えば、有機絶縁材料を用いた層と無機絶縁材料を用いた層との積層構造としても良い。

20

#### 【0146】

30

絶縁層 628 に金属化合物領域 624a 及び金属化合物領域 624b に達する開口部を形成し、導電層を用いて電極 502 及び電極 503 を形成する。導電層は、スパッタ法をはじめとする PVD 法や、プラズマ CVD 法などの CVD 法を用いて形成することができる。また、導電層の材料としては、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タンゲステンから選ばれた元素や、上述した元素を成分とする合金等を用いることができる。マンガン、マグネシウム、ジルコニウム、ベリリウム、ネオジム、スカンジウムのいずれか、またはこれらを複数組み合わせた材料を用いてもよい。導電層は、単層構造であっても良いし、2 層以上の積層構造としてもよい。例えば、チタン膜や窒化チタン膜の単層構造、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜が積層された 2 層構造、窒化チタン膜上にチタン膜が積層された 2 層構造、チタン膜とアルミニウム膜とチタン膜とが積層された 3 層構造などが挙げられる。

40

#### 【0147】

その後、トランジスタ 662 及び容量素子 664 の形成前の処理として、絶縁層 628 の表面に CMP 処理を施す（図 11（C）参照）。CMP 処理の他にエッチング処理などを適用することも可能である。なお、トランジスタ 662 の特性を向上させるために絶縁層 628 の表面、電極 502 の表面、及び電極 503 の表面は可能な限り平坦にしておくことが望ましく、例えば絶縁層 628 の表面は、二乗平均平方根（RMS）粗さを 1 nm 以下とすることが好ましい。

#### 【0148】

なお、図 10 及び図 11 を参照して説明した各工程の前後には、更に電極や配線、半導

50

体層、絶縁層などを形成する工程を含んでいても良い。例えば、配線の構造として、絶縁層及び導電層の積層構造でなる多層配線構造を採用して、高度に集積化した記憶素子を実現することも可能である。

#### 【0149】

##### 上部のトランジスタの作製方法

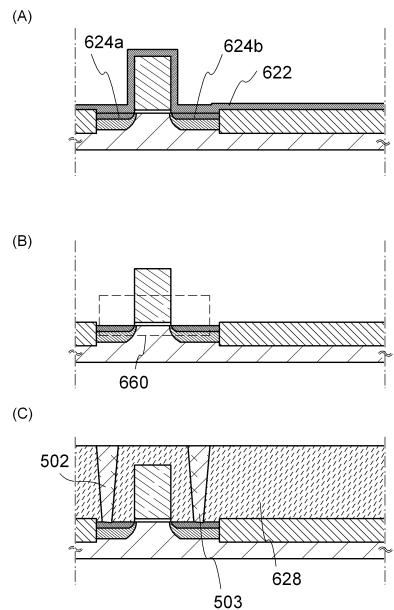

次に、上部トランジスタ 662 及び容量素子 664 の作製方法について説明する。図 6 に示した構成に対応する作製方法を図 12 を参照して説明する。図 7 に示した構成に対応する作製方法を図 13 を参照して説明する。図 8 に示した構成に対応する作製方法を図 14 を参照して説明する。図 9 に示した構成に対応する作製方法を図 15 を参照して説明する。

10

#### 【0150】

最初に、図 6 に示した構成に対応する作製方法を図 12 を参照して説明する。

#### 【0151】

絶縁層 628、電極 502 及び電極 503 上に酸化物半導体層を形成し、当該酸化物半導体層を選択的にエッティングして酸化物半導体層 644 を形成する（図 12（A）参照）。

#### 【0152】

酸化物半導体層 644 に用いる酸化物半導体としては、少なくともインジウム（In）あるいは亜鉛（Zn）を含むことが好ましい。特に In と Zn を含むことが好ましい。また、該酸化物半導体を用いたトランジスタの電気特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウム（Ga）を有することが好ましい。また、スタビライザーとしてスズ（Sn）を有することが好ましい。また、スタビライザーとしてハフニウム（Hf）を有することが好ましい。また、スタビライザーとしてアルミニウム（Al）を有することが好ましい。

20

#### 【0153】

また、他のスタビライザーとして、ランタノイドである、ラントン（La）、セリウム（Ce）、プラセオジム（Pr）、ネオジム（Nd）、サマリウム（Sm）、ユウロピウム（Eu）、ガドリニウム（Gd）、テルビウム（Tb）、ジスプロシウム（Dy）、ホルミウム（Ho）、エルビウム（Er）、ツリウム（Tm）、イッテルビウム（Yb）、ルテチウム（Lu）のいずれか一種あるいは複数種を有してもよい。

30

#### 【0154】

例えは、酸化物半導体として、酸化インジウム、酸化スズ、酸化亜鉛、二元系金属の酸化物である In-Zn 系酸化物、Sn-Zn 系酸化物、Al-Zn 系酸化物、Zn-Mg 系酸化物、Sn-Mg 系酸化物、In-Mg 系酸化物、In-Ga 系酸化物、三元系金属の酸化物である In-Ga-Zn 系酸化物（IGZO とも表記する）、In-Al-Zn 系酸化物、In-Sn-Zn 系酸化物、Sn-Ga-Zn 系酸化物、Al-Ga-Zn 系酸化物、Sn-Al-Zn 系酸化物、In-Hf-Zn 系酸化物、In-La-Zn 系酸化物、In-Ce-Zn 系酸化物、In-Pr-Zn 系酸化物、In-Nd-Zn 系酸化物、In-Sm-Zn 系酸化物、In-Sm-Zn 系酸化物、In-Eu-Zn 系酸化物、In-Gd-Zn 系酸化物、In-Tb-Zn 系酸化物、In-Dy-Zn 系酸化物、In-Ho-Zn 系酸化物、In-Er-Zn 系酸化物、In-Tm-Zn 系酸化物、In-Yb-Zn 系酸化物、In-Lu-Zn 系酸化物、四元系金属の酸化物である In-Sn-Ga-Zn 系酸化物、In-Hf-Ga-Zn 系酸化物、In-Al-Ga-Zn 系酸化物、In-Sn-Al-Zn 系酸化物、In-Sn-Hf-Zn 系酸化物、In-Hf-Al-Zn 系酸化物を用いることができる。

40

#### 【0155】

なお、ここで、例えは、In-Ga-Zn 系酸化物とは、In と Ga と Zn を有する酸化物という意味であり、In と Ga と Zn の比率は問わない。また、In と Ga と Zn 以外の金属元素が入っていてもよい。

#### 【0156】

50

例えば、 $In : Ga : Zn = 1 : 1 : 1 (= 1/3 : 1/3 : 1/3)$  あるいは  $In : Ga : Zn = 2 : 2 : 1 (= 2/5 : 2/5 : 1/5)$  の原子数比の  $In - Ga - Zn$  系酸化物やその組成の近傍の酸化物を用いることができる。あるいは、 $In : Sn : Zn = 1 : 1 : 1 (= 1/3 : 1/3 : 1/3)$ 、 $In : Sn : Zn = 2 : 1 : 3 (= 1/3 : 1/6 : 1/2)$  あるいは  $In : Sn : Zn = 2 : 1 : 5 (= 1/4 : 1/8 : 5/8)$  の原子数比の  $In - Sn - Zn$  系酸化物やその組成の近傍の酸化物を用いるとよい。

#### 【0157】

しかし、これらに限らず、必要とする半導体特性（移動度、しきい値、ばらつき等）に応じて適切な組成のものを用いればよい。また、必要とする半導体特性を得るために、キャリア濃度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間結合距離、密度等を適切なものとすることが好ましい。

10

#### 【0158】

例えば、 $In - Sn - Zn$  系酸化物では比較的容易に高い移動度が得られる。しかしながら、 $In - Ga - Zn$  系酸化物でも、バルク内欠陥密度を低減することにより移動度を上げることができる。

#### 【0159】

なお、例えば、 $In$ 、 $Ga$ 、 $Zn$  の原子数比が  $In : Ga : Zn = a : b : c (a + b + c = 1)$  である酸化物の組成が、原子数比が  $In : Ga : Zn = A : B : C (A + B + C = 1)$  の酸化物の組成の近傍であるとは、 $a$ 、 $b$ 、 $c$  が、

$$(a - A)^2 + (b - B)^2 + (c - C)^2 \leq r^2$$

20

を満たすことをいい、 $r$  は、例えば、 $0.05$  とすればよい。他の酸化物でも同様である。

#### 【0160】

酸化物半導体は単結晶でも、非単結晶でもよい。後者の場合、アモルファスでも、多結晶でもよい。また、アモルファス中に結晶性を有する部分を含む構造でも、非アモルファスでもよい。

#### 【0161】

アモルファス状態の酸化物半導体は、比較的容易に平坦な表面を得ることができるために、これを用いてトランジスタを作製した際の界面散乱を低減でき、比較的容易に、比較的高い移動度を得ることができる。

30

#### 【0162】

また、結晶性を有する酸化物半導体では、よりバルク内欠陥を低減することができ、表面の平坦性を高めればアモルファス状態の酸化物半導体以上の移動度を得ることができます。表面の平坦性を高めるためには、平坦な表面上に酸化物半導体を形成することが好ましく、具体的には、平均面粗さ ( $Ra$ ) が  $1\text{ nm}$  以下、好ましくは  $0.3\text{ nm}$  以下、より好ましくは  $0.1\text{ nm}$  以下の表面上に形成するとよい。

#### 【0163】

なお、 $Ra$  は、JIS B 0601 で定義されている中心線平均粗さを面に対して適用できるよう三次元に拡張したものであり、「基準面から指定面までの偏差の絶対値を平均した値」と表現でき、以下の式にて定義される。

40

#### 【0164】

##### 【数1】

$$Ra = \frac{1}{S_0} \int_{y_1}^{y_2} \int_{x_1}^{x_2} |f(x, y) - Z_0| dx dy$$

#### 【0165】

なお、上記において、 $S_0$  は、測定面（座標  $(x_1, y_1)$ 、 $(x_1, y_2)$ 、 $(x_2, y_1)$ 、 $(x_2, y_2)$ ）で表される 4 点によって囲まれる長方形の領域）の面積を指し、 $Z_0$  は測定面の平均高さを指す。 $Ra$  は原子間力顕微鏡 (AFM: Atomic Force Microscope) にて評価可能である。

50

## 【0166】

$In - Ga - Zn - O$  系の酸化物半導体材料の代表例としては、 $InGaO_3$  ( $ZnO$ )<sub>m</sub> ( $m > 0$ ) で表記されるものがある。また、 $Ga$  に代えて  $M$  の表記を用い、 $InMO_3$  ( $ZnO$ )<sub>m</sub> ( $m > 0$ ) のように表記される酸化物半導体材料がある。ここで、 $M$  は、ガリウム ( $Ga$ )、アルミニウム ( $Al$ )、鉄 ( $Fe$ )、ニッケル ( $Ni$ )、マンガン ( $Mn$ )、コバルト ( $Co$ ) などから選ばれた一の金属元素または複数の金属元素を示す。例えば、 $M$  としては、 $Ga$ 、 $Ga$  及び  $Al$ 、 $Ga$  及び  $Fe$ 、 $Ga$  及び  $Ni$ 、 $Ga$  及び  $Mn$ 、 $Ga$  及び  $Co$ などを適用することができる。なお、上述の組成は結晶構造から導き出されるものであり、あくまでも一例に過ぎないことを付記する。

## 【0167】

酸化物半導体層 644 をスパッタ法で作製するためのターゲットとしては、 $In : Ga : Zn = 1 : x : y$  ( $x$  は 0 以上、 $y$  は 0.5 以上 5 以下) の組成比で表されるものを用いるのが好適である。例えば、 $In : Ga : Zn = 1 : 1 : 1$  [atom 比] ( $x = 1$ 、 $y = 1$ )、(すなわち、 $In_2O_3 : Ga_2O_3 : ZnO = 1 : 1 : 2$  [mol 数比]) の組成比を有するターゲットなどを用いることができる。また、 $In : Ga : Zn = 1 : 1 : 0.5$  [atom 比] ( $x = 1$ 、 $y = 0.5$ ) の組成比を有するターゲットや、 $In : Ga : Zn = 1 : 1 : 2$  [atom 比] ( $x = 1$ 、 $y = 2$ ) の組成比を有するターゲットや、 $In : Ga : Zn = 1 : 0 : 1$  [atom 比] ( $x = 0$ 、 $y = 1$ ) の組成比を有するターゲットを用いることもできる。金属酸化物ターゲット中の金属酸化物の相対密度は 80% 以上、好ましくは 95% 以上、更に好ましくは 99.9% 以上である。相対密度の高い金属酸化物ターゲットを用いることにより、緻密な構造の酸化物半導体層 644 を形成することが可能である。

## 【0168】

また、 $In - Sn - Zn$  系酸化物を用いて酸化物半導体層 644 を形成することもできる。 $In - Sn - Zn$  系酸化物は、ITO と呼ぶことができ、用いるターゲットの組成比は、 $In : Sn : Zn$  が原子数比で、1 : 2 : 2、2 : 1 : 3、1 : 1 : 1、または 20 : 45 : 35 などとなる酸化物ターゲットを用いることができる。

## 【0169】

酸化物半導体層 644 の形成雰囲気は、希ガス (代表的にはアルゴン) 雰囲気、酸素雰囲気、または、希ガス (代表的にはアルゴン) と酸素との混合雰囲気とするのが好適である。具体的には、例えば、水素、水、水酸基、水素化物などの不純物が、濃度 1 ppm 以下 (望ましくは濃度 10 ppb 以下) にまで除去された高純度ガス雰囲気を用いるのが好適である。

## 【0170】

酸化物半導体層 644 の形成の際には、例えば、減圧状態に保たれた処理室内に被処理物を保持し、被処理物の温度が 100 以上 550 未満、好ましくは 200 以上、400 以下となるように被処理物を熱する。または、酸化物半導体層 644 の形成の際の被処理物の温度は、室温 ( $25 \pm 10$ ) としてもよい。そして、処理室内の水分を除去しつつ、水素や水などが除去されたスパッタガスを導入し、上記ターゲットを用いて酸化物半導体層 644 を形成する。被処理物を熱しながら酸化物半導体層 644 を形成することにより、酸化物半導体層 644 に含まれる不純物を低減することができる。また、スパッタによる酸化物半導体層 644 の損傷を軽減することができる。処理室内の水分を除去するためには吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプなどを用いることができる。また、ターボポンプにコールドトラップを加えたものを用いてもよい。クライオポンプなどを用いて排気することで、処理室から水素や水などを除去することができるため、酸化物半導体層 644 中の不純物濃度を低減できる。

## 【0171】

酸化物半導体層 644 の形成条件としては、例えば、被処理物とターゲットの間との距離が 170 mm、圧力が 0.4 Pa、直流 (DC) 電力が 0.5 kW、雰囲気が酸素 (酸

10

20

30

40

50

素 100% ) 雰囲気、またはアルゴン (アルゴン 100%) 雰囲気、または酸素とアルゴンの混合雰囲気、といった条件を適用することができる。なお、パルス直流 (D C) 電源を用いると、ごみ (成膜時に形成される粉状の物質など) を低減でき、酸化物半導体層 644 の膜厚分布も均一となるため好ましい。

#### 【0172】

なお、酸化物半導体層 644 をスパッタ法により形成する前には、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、形成表面 (例えば絶縁層 628 の表面) の付着物を除去しても良い。ここで、逆スパッタとは、通常のスパッタにおいては、スパッターゲットにイオンを衝突させるところを、逆に、処理表面にイオンを衝突させることによってその表面を改質する方法のことをいう。処理表面にイオンを衝突させる方法としては、アルゴン雰囲気下で処理表面側に高周波電圧を印加して、被処理物付近にプラズマを生成する方法などがある。なお、アルゴン雰囲気に代えて窒素、ヘリウム、酸素などによる雰囲気を適用してもよい。

10

#### 【0173】

本実施の形態では、酸化物半導体層 644 を In - Ga - Zn - O 系の金属酸化物ターゲットを用いるスパッタ法により形成することとする。また、酸化物半導体層 644 の膜厚は 1 nm 以上 50 nm 以下、好ましくは 2 nm 以上 20 nm 以下、より好ましくは 3 nm 以上 15 nm 以下とすることができます。ただし、酸化物半導体材料等により適切な膜厚は異なるから、酸化物半導体層 644 の膜厚は用いる材料等に応じて選択することができる。なお、上記のように絶縁層 628 の表面を可能な限り平坦にしておくことにより、厚みの小さい酸化物半導体層 644 であっても、酸化物半導体層 644 のチャネル形成領域に相当する部分の断面形状を平坦な形状とすることができます。酸化物半導体層 644 のチャネル形成領域に相当する部分の断面形状を平坦な形状とすることにより、酸化物半導体層 644 の断面形状が平坦でない場合と比較して、トランジスタ 662 のリーク電流を低減することができる。

20

#### 【0174】

酸化物半導体層 644 の形成後には、酸化物半導体層 644 に対して熱処理 (第 1 の熱処理) を行うことが望ましい。この第 1 の熱処理によって酸化物半導体層 644 中の、過剰な水素 (水や水酸基を含む) を除去することができる。第 1 の熱処理の温度は、例えば、300 以上 550 未満、好ましくは 400 以上 500 以下とする。

30

#### 【0175】

第 1 の熱処理は、例えば、抵抗発熱体などを用いた電気炉に被処理物を導入し、窒素雰囲気下、450 、1 時間の条件で行うことができる。この間、酸化物半導体層は大気に触れさせず、水や水素の混入が生じないようにする。

#### 【0176】

熱処理装置は電気炉に限られず、加熱されたガスなどの媒体からの熱伝導、または熱輻射によって、被処理物を加熱する装置を用いても良い。例えば、G R T A ( Gas Rapid Thermal Anneal ) 装置、L R T A ( Lamp Rapid Thermal Anneal ) 装置等の R T A ( Rapid Thermal Anneal ) 装置を用いることができる。L R T A 装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光 (電磁波) の輻射により、被処理物を加熱する装置である。G R T A 装置は、高温のガスを用いて熱処理を行う装置である。ガスとしては、アルゴンなどの希ガス、または窒素のような、熱処理によって被処理物と反応しない不活性ガスが用いられる。

40

#### 【0177】

例えば、第 1 の熱処理として、熱せられた不活性ガス雰囲気中に被処理物を投入し、数分間熱した後、当該不活性ガス雰囲気から被処理物を取り出す G R T A 処理を行ってもよい。G R T A 処理を用いると短時間での高温熱処理が可能となる。また、被処理物の耐熱温度を超える温度条件であっても適用が可能となる。

50

## 【0178】

なお、処理中に、不活性ガスを、酸素を含むガスに切り替えるても良い。酸素を含む雰囲気において第1の熱処理を行うことで、酸素欠損に起因するエネルギー・ギャップ中の欠陥準位を低減することができるためである。更に当該熱処理によって、酸化物半導体層644が酸素を過剰に含む状態とすることが望ましい。過剰に含まれる酸素は酸化物半導体層644の格子間に存在する。なお、不活性ガス雰囲気としては、窒素、または希ガス（ヘリウム、ネオン、アルゴン等）を主成分とする雰囲気であって、水、水素などが含まれない雰囲気を適用するのが望ましい。例えば、熱処理装置に導入する窒素や、ヘリウム、ネオン、アルゴン等の希ガスの純度を、6N(99.9999%)以上、好ましくは7N(99.99999%)以上（すなわち、不純物濃度が1ppm以下、好ましくは0.1ppm以下）とする。

## 【0179】

ところで、上述の熱処理（第1の熱処理）には水素や水などを除去する効果があるから、当該熱処理を、脱水化処理や、脱水素化処理などと呼ぶこともできる。このような熱処理は、酸化物半導体層の形成後や後に形成するゲート絶縁層646の形成後、ゲート電極648の形成後、などのタイミングにおいて行うことも可能である。また、このような熱処理は、一回に限らず複数回行っても良い。

## 【0180】

酸化物半導体層のエッティングは、上記熱処理の前、または上記熱処理の後のいずれにおいて行っても良い。また、素子の微細化という観点からはドライエッティングを用いるのが好適であるが、ウェットエッティングを用いても良い。エッティングガスやエッティング液については被エッティング材料に応じて適宜選択することができる。

20

## 【0181】

次いで、酸化物半導体層644上に導電層を形成し、当該導電層を選択的にエッティングして、電極642a、電極642b、電極504を形成する（図12（B）参照）。なお、電極642aは電極503と接続するように設けられる。電極504は電極502と接するように設けられる。

## 【0182】

導電層は、スパッタ法をはじめとするPVD法や、プラズマCVD法などのCVD法を用いて形成することができる。また、導電層の材料としては、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タンクステンから選ばれた元素や、上述した元素を成分とする合金等を用いることができる。マンガン、マグネシウム、ジルコニウム、ベリリウム、ネオジム、スカンジウムのいずれか、またはこれらを複数組み合わせた材料を用いてもよい。

30

## 【0183】

導電層は、単層構造であっても良いし、2層以上の積層構造としてもよい。例えば、チタン膜や窒化チタン膜の単層構造、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜が積層された2層構造、窒化チタン膜上にチタン膜が積層された2層構造、チタン膜とアルミニウム膜とチタン膜とが積層された3層構造などが挙げられる。なお、導電層を、チタン膜や窒化チタン膜の単層構造とする場合には、端部にテーパー形状を有する電極642a、電極642bへの加工が容易であるというメリットがある。

40

## 【0184】

また、導電層は、導電性の金属酸化物を用いて形成しても良い。導電性の金属酸化物としては酸化インジウム( $In_2O_3$ )、酸化スズ( $SnO_2$ )、酸化亜鉛( $ZnO$ )、酸化インジウム酸化スズ( $In_2O_3 - SnO_2$ 、ITOと略記する場合がある)、酸化インジウム酸化亜鉛( $In_2O_3 - ZnO$ )、または、これらの金属酸化物材料にシリコン若しくは酸化シリコンを含有させたものを用いることができる。

## 【0185】

なお、導電層のエッティングは、ドライエッティング、ウェットエッティングのいずれを用いて行っても良いが、微細化のためには、制御性の良いドライエッティングを用いるのが好適

50

である。また、形成される電極 642a、及び電極 642b の端部がテーパー形状となるように行っても良い。テーパー角は、例えば、30°以上60°以下とすることができる。

#### 【0186】

上部のトランジスタ 662 のチャネル長 (L) は、電極 642a、及び電極 642b の下端部の間隔によって決定される。なお、チャネル長 (L) が 25 nm 未満のトランジスタを形成する場合に用いるマスクを形成するための露光を行う際には、数 nm ~ 数 10 nm と波長の短い超紫外線 (Extreme Ultraviolet) を用いるのが望ましい。超紫外線による露光は解像度が高く焦点深度も大きい。従って、トランジスタ 662 のチャネル長 (L) を、2 μm 未満、好ましくは 10 nm 以上 350 nm (0.35 μm) 以下とすることも可能であり、回路の動作速度を高めることができる。10

#### 【0187】

また、電極 642b は容量素子 664 の一対の電極のうち一方の電極となる。

#### 【0188】

なお、絶縁層 628 の上には、トランジスタ 662 の下地として機能する絶縁層を設けても良い。当該絶縁層は、PVD 法や CVD 法などを用いて形成することができる。

#### 【0189】

次に、電極 642a、電極 642b、電極 504、酸化物半導体層 644 を覆うようにゲート絶縁層 646 を形成する（図 12 (C) 参照）。

#### 【0190】

ゲート絶縁層 646 は、CVD 法やスパッタ法等を用いて形成することができる。ゲート絶縁層 646 は、酸化物半導体層 644 に接することになるから、水素が十分に低減された方法によって形成するのが望ましい。また、ゲート絶縁層 646 は、酸化シリコン、窒化シリコン、酸窒化シリコン、酸化アルミニウム、酸化タンタル、酸化ハフニウム、酸化イットリウム、ハフニウムシリケート ( $HfSi_xO_y$  ( $x > 0$ ,  $y > 0$ ))、窒素が添加されたハフニウムシリケート ( $HfSi_xO_y$  ( $x > 0$ ,  $y > 0$ ))、窒素が添加されたハフニウムアルミネート ( $HfAl_xO_y$  ( $x > 0$ ,  $y > 0$ ))、などを含むように形成するのが好適である。ゲート絶縁層 646 は、単層構造としても良いし、積層構造としても良い。また、ゲート絶縁層 646 の厚さは特に限定されないが、記憶素子を微細化する場合にはゲート絶縁層 646 を薄くするのが望ましい。例えば、ゲート絶縁層 646 として酸化シリコンを用いる場合には、ゲート絶縁層 646 の厚さは 1 nm 以上 100 nm 以下、好ましくは 10 nm 以上 50 nm 以下とすることができます。2030

#### 【0191】

上述のように、ゲート絶縁層 646 を薄くすると、トンネル効果などに起因するトランジスタ 662 のゲートリークが問題となる。ゲートリークの問題を解消するには、ゲート絶縁層 646 に、酸化ハフニウム、酸化タンタル、酸化イットリウム、ハフニウムシリケート ( $HfSi_xO_y$  ( $x > 0$ ,  $y > 0$ ))、窒素が添加されたハフニウムシリケート ( $HfSi_xO_y$  ( $x > 0$ ,  $y > 0$ ))、窒素が添加されたハフニウムアルミネート ( $HfAl_xO_y$  ( $x > 0$ ,  $y > 0$ ))、などの高誘電率 (high-k) 材料を用いると良い。high-k 材料をゲート絶縁層 646 に用いることで、電気的特性を確保しつつ、ゲートリークを抑制するために膜厚を大きくすることが可能になる。例えば、酸化ハフニウムは比誘電率が 1.5 程度であり、酸化シリコンの比誘電率の 3 ~ 4 と比較して非常に大きな値を有している。このような材料を用いることにより、酸化シリコン換算で 15 nm 未満、好ましくは 2 nm 以上 10 nm 以下のゲート絶縁層 646 を実現することも容易になる。なお、high-k 材料を含む膜と、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウムなどのいずれかを含む膜との積層構造としてもよい。40

#### 【0192】

ゲート絶縁層 646 の形成後には、酸素雰囲気下で第 2 の熱処理を行うのが望ましい。熱処理の温度は、200 以上 450 以下、好ましくは 250 以上 350 以下である50

る。第2の熱処理を行うことによって、酸化物半導体層644に酸素を供給する。

【0193】

なお、本実施の形態では、ゲート絶縁層646の形成後に第2の熱処理を行っているが、第2の熱処理のタイミングはこれに限定されない。例えば、ゲート電極648の形成後に第2の熱処理を行っても良い。また、第1の熱処理に続けて第2の熱処理を行っても良いし、第1の熱処理に第2の熱処理を兼ねさせても良い。

【0194】

また、酸素雰囲気下で第2の熱処理を行う代わりに、酸化物半導体層644に隣接する絶縁層（例えば、ゲート絶縁層646）として酸素を含む層を形成した後、窒素雰囲気下等で熱処理を行うことによって、当該絶縁層から酸化物半導体層644に酸素を供給してもよい。10

【0195】

また、酸素雰囲気下で第2の熱処理を行う代わりに、ドーピングによって酸化物半導体層644に酸素を添加してもよい。

【0196】

以上のように、脱水化処理、脱水素化処理を行った後に、酸化物半導体層644に酸素を供給することによって、酸化物半導体層644中の酸素欠損に起因するエネルギー・ギャップ中の欠陥準位を低減することができる。なお、酸化物半導体層644が酸素を過剰に含む状態とすることが望ましい。過剰に含まれる酸素は酸化物半導体層644の格子間に存在する。20

【0197】

また、ゲート絶縁層646は容量素子664の誘電体層となる。

【0198】

なお、酸化物半導体層644に接する絶縁層（例えば図6及び図7に示した構成では、当該絶縁層は、ゲート絶縁層646と、絶縁層628であり、図8及び図9に示した構成では、ゲート絶縁層646と、絶縁層650である。）は、第13族元素及び酸素を含む絶縁材料を用いることが好ましい。酸化物半導体材料には第13族元素を含むものが多く、第13族元素を含む絶縁材料は酸化物半導体との相性が良く、これを酸化物半導体に接する絶縁層に用いることで、酸化物半導体との界面の状態を良好に保つことができる。30

【0199】

第13族元素を含む絶縁材料とは、絶縁材料に一または複数の第13族元素を含むことを意味する。第13族元素を含む絶縁材料としては、例えば、酸化ガリウム、酸化アルミニウム、酸化アルミニウムガリウム、酸化ガリウムアルミニウムなどがある。ここで、酸化アルミニウムガリウムとは、ガリウムの含有量（原子%）よりアルミニウムの含有量（原子%）が多いものを示し、酸化ガリウムアルミニウムとは、ガリウムの含有量（原子%）がアルミニウムの含有量（原子%）以上のものを示す。

【0200】

例えば、ガリウムを含有する酸化物半導体層644に接して絶縁層を形成する場合に、当該絶縁層に酸化ガリウムを含む材料を用いることで酸化物半導体層644と絶縁層の界面特性を良好に保つことができる。例えば、酸化物半導体層644と酸化ガリウムを含む絶縁層とを接して設けることにより、酸化物半導体層644と絶縁層の界面における水素のパイルアップを低減することができる。なお、絶縁層に酸化物半導体の成分元素と同じ族の元素を用いる場合には、同様の効果を得ることが可能である。例えば、酸化アルミニウムを含む材料を用いて絶縁層を形成することも有効である。なお、酸化アルミニウムは、水を透過させにくいという特性を有しているため、当該材料を用いることは、酸化物半導体層644への水の侵入防止という点においても好ましい。40

【0201】

また、酸化物半導体層644に接する絶縁層はその一部の領域または全領域を、酸素雰囲気下による熱処理や酸素ドープなどにより、絶縁層を構成する絶縁材料の化学量論的組成比より酸素が多い状態とすることが好ましい。酸素ドープとは、酸素をバルクに添加す50

ることをいう。なお、当該バルクの用語は、酸素を薄膜表面のみでなく薄膜内部に添加することを明確にする趣旨で用いている。また、酸素ドープには、プラズマ化した酸素をバルクに添加する酸素プラズマドープが含まれる。また、酸素ドープは、イオン注入法またはイオンドーピング法を用いて行ってもよい。

#### 【0202】

例えば、酸化物半導体層644に接する絶縁層として酸化ガリウムを用いた場合、酸素雰囲気下による熱処理や、酸素ドープを行うことにより、酸化ガリウムの組成を $Ga_2O_x$  ( $X = 3 + , 0 < X < 1$ ) とすることができる。

#### 【0203】

また、酸化物半導体層644に接する絶縁層として酸化アルミニウムを用いた場合、酸素雰囲気下による熱処理や、酸素ドープを行うことにより、酸化アルミニウムの組成を $Al_2O_x$  ( $X = 3 + , 0 < X < 1$ ) とすることができる。

#### 【0204】

また、酸化物半導体層644に接する絶縁層として酸化ガリウムアルミニウム(酸化アルミニウムガリウム)を用いた場合、酸素雰囲気下による熱処理や、酸素ドープを行うことにより、酸化ガリウムアルミニウム(酸化アルミニウムガリウム)の組成を $Ga_xAl_{2-x}O_{3+}$  ( $0 < X < 2 , 0 < X < 1$ ) とすることができる。

#### 【0205】

酸素ドープ処理を行うことにより、構成する絶縁材料の化学量論的組成比より酸素が多い領域を有する絶縁層を形成することができる。このような絶縁層と酸化物半導体層が接することにより、絶縁層中の過剰な酸素が酸化物半導体層に供給され、酸化物半導体層中、または酸化物半導体層と絶縁層の界面における酸素不足欠陥を低減し、酸化物半導体層をi型化またはi型に限りなく近い酸化物半導体とすることができます。

#### 【0206】

なお、構成する絶縁材料の化学量論的組成比より酸素が多い領域を有する絶縁層は、酸化物半導体層644に接する絶縁層のうち、上層に位置する絶縁層または下層に位置する絶縁層のうち、どちらか一方のみに用いても良いが、両方の絶縁層に用いる方が好ましい。構成する絶縁材料の化学量論的組成比より酸素が多い領域を有する絶縁層を、酸化物半導体層644に接する絶縁層のうち、上層及び下層に位置する絶縁層に用い、酸化物半導体層644を挟む構成とすることで、上記効果をより高めることができる。

#### 【0207】

また、酸化物半導体層644の上層または下層に用いる絶縁層は、上層と下層で同じ構成元素を有する絶縁層としても良いし、異なる構成元素を有する絶縁層としても良い。例えば、上層と下層とも、組成が $Ga_2O_x$  ( $X = 3 + , 0 < X < 1$ ) の酸化ガリウムとしても良いし、上層と下層の一方を組成が $Ga_2O_x$  ( $X = 3 + , 0 < X < 1$ ) の酸化ガリウムとし、他方を組成が $Al_2O_x$  ( $X = 3 + , 0 < X < 1$ ) の酸化アルミニウムとしても良い。

#### 【0208】

また、酸化物半導体層644に接する絶縁層は、構成する絶縁材料の化学量論的組成比より酸素が多い領域を有する絶縁層の積層としても良い。例えば、酸化物半導体層644の上層に組成が $Ga_2O_x$  ( $X = 3 + , 0 < X < 1$ ) の酸化ガリウムを形成し、その上に組成が $Ga_xAl_{2-x}O_{3+}$  ( $0 < X < 2 , 0 < X < 1$ ) の酸化ガリウムアルミニウム(酸化アルミニウムガリウム)を形成してもよい。なお、酸化物半導体層644の下層を、構成する絶縁材料の化学量論的組成比より酸素が多い領域を有する絶縁層の積層としても良いし、酸化物半導体層644の上層及び下層の両方を、構成する絶縁材料の化学量論的組成比より酸素が多い領域を有する絶縁層の積層としても良い。

#### 【0209】

次に、ゲート絶縁層646上にゲート電極648及び電極649を形成する(図12(C)参照)。

#### 【0210】

10

20

30

40

50

ゲート電極 648 及び電極 649 は、ゲート絶縁層 646 上に導電層を形成した後に、当該導電層を選択的にエッチングすることによって形成することができる。ゲート電極 648 及び電極 649 となる導電層は、スパッタ法をはじめとする PVD 法や、プラズマ CVD 法などの CVD 法を用いて形成することができる。材料等の詳細は、電極 642a または電極 642b などの場合と同様であり、これらの記載を参照できる。

#### 【0211】

また、電極 649 は容量素子 664 の一対の電極のうちの他方の電極となる。

#### 【0212】

以上により、高純度化された酸化物半導体層 644 を用いたトランジスタ 662 と、容量素子 664 とが完成する（図 12 (C) 参照）。上述した作製方法により、酸化物半導体層 644 は水素濃度が十分に低減されて高純度化され、十分な酸素の供給により酸素欠乏に起因するエネルギーギャップ中の欠陥準位が低減される。こうして作製された酸化物半導体層 644 は、i 型化（真性化）または実質的に i 型化されており、このような酸化物半導体層 644 をチャネル形成領域に用いることで、極めて優れたオフ電流特性のトランジスタ 662 を得ることができる。

10

#### 【0213】

次に、ゲート絶縁層 646、ゲート電極 648、及び電極 649 上に、絶縁層 650 及び絶縁層 654 を形成する（図 12 (D) 参照）。絶縁層 650 及び絶縁層 654 は、PVD 法や CVD 法などを用いて形成することができる。また、絶縁層 650 及び絶縁層 654 は、酸化シリコン、酸窒化シリコン、窒化シリコン、酸化ハフニウム、酸化アルミニウム等の無機絶縁材料を含む材料を用いて、単層または積層で形成することができる。

20

#### 【0214】

なお、絶縁層 654 には、誘電率の低い材料や、誘電率の低い構造（多孔質の構造など）を用いることが望ましい。絶縁層 654 の誘電率を低くすることにより、配線や電極などの間に生じる容量を低減し、動作の高速化を図ることができるためである。

#### 【0215】

なお、絶縁層 654 は、その表面が平坦になるように形成することが望ましい。表面が平坦になるように絶縁層 654 を形成することで、記憶素子を微細化した場合などにおいても、絶縁層 654 上に、電極や配線などを好適に形成することができるためである。なお、絶縁層 654 の平坦化は、CMP（化学的機械的研磨）などの方法を用いて行うことができる。

30

#### 【0216】

次に、絶縁層 650 及び絶縁層 654 に、電極 504 に達する開口部 501 を形成する。その後、配線 658 を形成する（図 12 (D) 参照）。配線 658 は、スパッタ法をはじめとする PVD 法や、プラズマ CVD 法などの CVD 法を用いて導電層を形成した後、当該導電層をエッチング加工することによって形成される。また、導電層の材料としては、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タンクステンから選ばれた元素や、上述した元素を成分とする合金等を用いることができる。マンガン、マグネシウム、ジルコニア、ベリリウム、ネオジム、スカンジウムのいずれか、またはこれらを複数組み合わせた材料を用いてもよい。詳細は、電極 642a、電極 642b などと同様である。なお、開口部 501 において電極を形成し、当該電極と接するように配線 658 を形成しても良い。

40

#### 【0217】

以上の工程より、図 6 に示すような構成の記憶素子を作製することができる。

#### 【0218】

次に、図 7 に示した構成に対応する作製方法を図 13 を参照して説明する。

#### 【0219】

図 12 に示した作製方法と図 13 に示した作製方法とでは、酸化物半導体層 644 と電極 642 の作製方法が異なる。図 13 に示した作製方法において、酸化物半導体層 644 と電極 642 の作製方法以外の作製方法は図 12 に示した作製方法と同様であるため説明

50

は省略する。

【0220】

電極 502、電極 503 及び絶縁層 628 上に導電層を形成し、当該導電層を選択的にエッティングして、電極 642a、電極 642b、電極 504 を形成する(図 13(A) 参照)。当該導電層は、図 12 に示した作製方法において、電極 642a、電極 642b、電極 504 を形成するために用いた導電層と同様の材料とし、同様の方法で作製することができる所以説明は省略する。

【0221】

次いで、電極 642a、電極 642b、電極 504 上に酸化物半導体層 644 を形成する(図 13(B) 参照)。酸化物半導体層 644 は、図 12 に示した作製方法において酸化物半導体層 644 を形成するために用いた酸化物半導体層と同様の材料とし、同様の方法で作製することができるので説明は省略する。

10

【0222】

次に、電極 642a、電極 642b、電極 504、酸化物半導体層 644 を覆うようにゲート絶縁層 646 を形成する(図 13(C) 参照)。これ以降の作製工程は図 12 で示した工程と同様であるため説明は省略する。

【0223】

以上の工程より、図 7 に示すような構成の記憶素子を作製することができる。

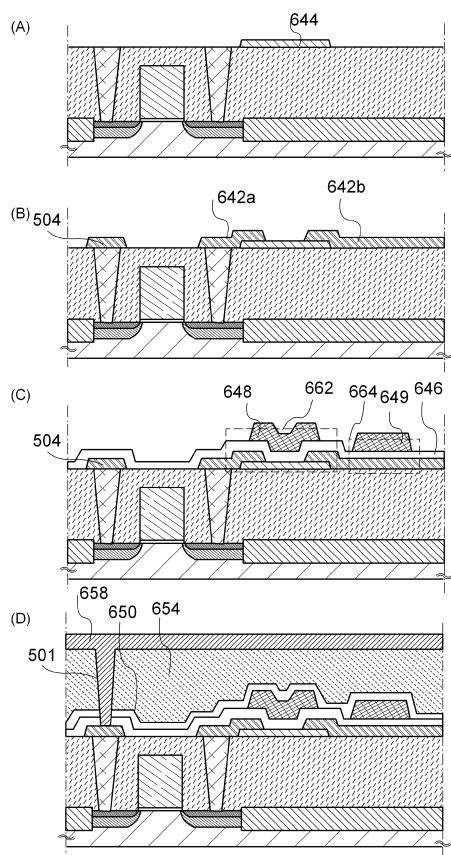

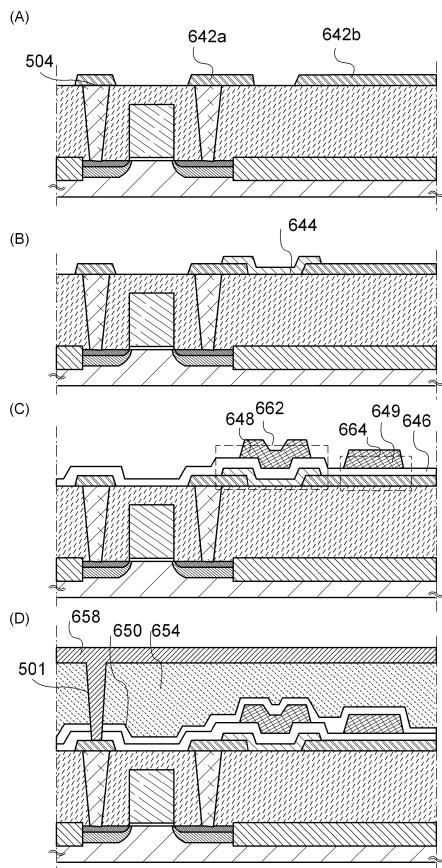

【0224】

次に、図 8 に示した構成に対応する作製方法を図 14 を参照して説明する。

20

【0225】

図 12 に示した作製方法と図 14 に示した作製方法とでは、ゲート電極 648、電極 649、電極 504、ゲート絶縁層 646 の作製方法が異なる。図 14 に示した作製方法において、それ以外の作製方法以外の作製方法は図 12 に示した作製方法と同様であるため説明は省略する。

【0226】

電極 502、電極 503 及び絶縁層 628 上に導電層を形成し、当該導電層を選択的にエッティングして、ゲート電極 648、電極 649、電極 504 を形成する(図 14(A) 参照)。当該導電層は、図 12 に示した作製方法において、ゲート電極 648、電極 649 を形成するために用いた導電層と同様の材料とし、同様の方法で作製することができるので説明は省略する。

30

【0227】

次いで、ゲート電極 648、電極 649、電極 504 を覆うようにゲート絶縁層 646 を形成する(図 14(B) 参照)。ゲート絶縁層 646 は図 12 に示した作製方法においてゲート絶縁層 646 を形成するために用いた材料と同様の材料を用いて、同様の方法で作製することができるので説明は省略する。

【0228】

次いで、ゲート絶縁層 646 上に、酸化物半導体層 644 を形成する(図 14(C) 参照)。酸化物半導体層 644 は、図 12 に示した作製方法において酸化物半導体層 644 を形成するために用いた酸化物半導体層と同様の材料とし、同様の方法で作製することができるので説明は省略する。

40

【0229】

次に、酸化物半導体層 644 上に導電層を形成し、当該導電層を選択的にエッティングして、電極 642a、電極 642b を形成する(図 14(D) 参照)。当該導電層は、図 12 に示した作製方法において、電極 642a、電極 642b を形成するために用いた導電層と同様の材料とし、同様の方法で作製することができるので説明は省略する。

【0230】

これ以降の作製工程は図 12 で示した工程と同様であるため説明は省略する。

【0231】

以上の工程より、図 8 に示すような構成の記憶素子を作製することができる。

50

**【0232】**

次に、図9に示した構成に対応する作製方法を図15を参照して説明する。

**【0233】**

図14に示した作製方法と図15に示した作製方法とでは、酸化物半導体層644と電極642の作製方法が異なる。図15に示した作製方法において、酸化物半導体層644と電極642の作製方法以外の作製方法は図14に示した作製方法と同様であるため説明は省略する。

**【0234】**

ゲート絶縁層646上に、導電層を形成し、当該導電層を選択的にエッチングして、電極642a、電極642bを形成する(図15(B)参照)。当該導電層は、図14に示した作製方法において、電極642a、電極642bを形成するために用いた導電層と同様の材料とし、同様の方法で作製することができるため説明は省略する。

10

**【0235】**

次いで、電極642a、電極642b上に酸化物半導体層644を形成する(図15(C)参照)。酸化物半導体層644は、図14に示した作製方法において酸化物半導体層644を形成するために用いた酸化物半導体層と同様の材料とし、同様の方法で作製することができるので説明は省略する。

**【0236】**

これ以降の作製工程は図14で示した工程と同様であるため説明は省略する。

**【0237】**

20

以上の工程より、図9に示すような構成の記憶素子を作製することができる。

**【0238】**

なお、図12乃至図15を参照して説明した各工程の前後には、更に電極や配線、半導体層、絶縁層などを形成する工程を含んでいても良い。例えば、配線の構造として、絶縁層及び導電層の積層構造でなる多層配線構造を採用して、高度に集積化した記憶素子を実現することも可能である。

**【0239】**

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

**【0240】**

30

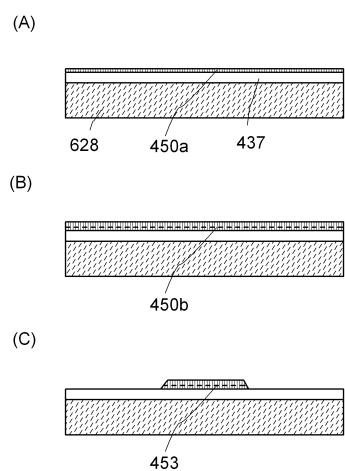

**(実施の形態7)**

トランジスタ662の酸化物半導体層644の一形態を、図16を用いて説明する。

**【0241】**

本実施の形態の酸化物半導体層は、第1の結晶性酸化物半導体層上に第2の結晶性酸化物半導体層よりも厚い第2の結晶性酸化物半導体層を有する積層構造である。

**【0242】**

絶縁層628上に絶縁層437を形成する。本実施の形態では、絶縁層437は、P C V D法またはスパッタリング法を用いて形成された50nm以上600nm以下の膜厚の酸化物絶縁層とする。当該酸化物絶縁層としては、酸化シリコン膜、酸化ガリウム膜、酸化アルミニウム膜、酸化窒化シリコン膜、酸化窒化アルミニウム膜、または窒化酸化シリコン膜から選ばれた一層またはこれらの積層を用いることができる。

40

**【0243】**

次に、絶縁層437上に膜厚1nm以上10nm以下の第1の酸化物半導体膜を形成する。第1の酸化物半導体膜の形成は、スパッタリング法を用い、そのスパッタリング法による成膜時における基板温度は200以上400以下とする。

**【0244】**

本実施の形態では、酸化物半導体用ターゲット(I n - G a - Z n - O系酸化物半導体用ターゲット(I n<sub>2</sub>O<sub>3</sub> : G a<sub>2</sub>O<sub>3</sub> : Z nO = 1 : 1 : 2 [モル数比])を用いて、基板とターゲットの間との距離を170mm、基板温度250、圧力0.4Pa、直流(DC)電源0.5kW、酸素のみ、アルゴンのみ、又はアルゴン及び酸素雰囲気下で

50

膜厚 5 nm の第 1 の酸化物半導体膜を成膜する。

【 0 2 4 5 】

次いで、基板を配置するチャンバー雰囲気を窒素、または乾燥空気とし、第 1 の加熱処理を行う。第 1 の加熱処理の温度は、400 以上 750 以下とする。第 1 の加熱処理によって第 1 の結晶性酸化物半導体層 450a を形成する（図 16（A）参照）。

【 0 2 4 6 】

成膜時の基板温度や第 1 の加熱処理の温度にもよるが、第 1 の加熱処理によって、膜表面から結晶化が起こり、膜の表面から内部に向かって結晶成長し、C 軸配向した結晶が得られる。第 1 の加熱処理によって、亜鉛と酸素が膜表面に多く集まり、上平面が六角形をなす亜鉛と酸素からなるグラフェンタイプの二次元結晶が最表面に 1 層または複数層形成され、これが膜厚方向に成長して重なり積層となる。加熱処理の温度を上げると表面から内部、そして内部から底部と結晶成長が進行する。10

【 0 2 4 7 】

第 1 の加熱処理によって、酸化物絶縁層である絶縁層 437 中の酸素を第 1 の結晶性酸化物半導体層 450a との界面またはその近傍（界面からプラスマイナス 5 nm）に拡散させて、第 1 の結晶性酸化物半導体層の酸素欠損を低減する。

【 0 2 4 8 】

次いで、第 1 の結晶性酸化物半導体層 450a 上に 10 nm よりも厚い第 2 の酸化物半導体膜を形成する。第 2 の酸化物半導体膜の形成は、スパッタリング法を用い、その成膜時における基板温度は 200 以上 400 以下とする。成膜時における基板温度を 200 以上 400 以下とすることにより、第 1 の結晶性酸化物半導体層の表面上に接して成膜する第 2 の酸化物半導体膜にプリカーサの整列が起きる。20

【 0 2 4 9 】

本実施の形態では、酸化物半導体用ターゲット（In - Ga - Zn - O 系酸化物半導体用ターゲット（ $In_2O_3 : Ga_2O_3 : ZnO = 1 : 1 : 2$  [mol 数比]）を用いて、基板とターゲットの間との距離を 170 mm、基板温度 400 、圧力 0.4 Pa、直流（DC）電源 0.5 kW、酸素のみ、アルゴンのみ、又はアルゴン及び酸素雰囲気下で膜厚 25 nm の第 2 の酸化物半導体膜を成膜する。

【 0 2 5 0 】

次いで、基板を配置するチャンバー雰囲気を窒素、または乾燥空気とし、第 2 の加熱処理を行う。第 2 の加熱処理の温度は、400 以上 750 以下とする。第 2 の加熱処理によって第 2 の結晶性酸化物半導体層 450b を形成する（図 16（B）参照）。第 2 の加熱処理は、窒素雰囲気下、酸素雰囲気下、或いは窒素と酸素の混合雰囲気下で行うことができる。第 2 の加熱処理によって、第 1 の結晶性酸化物半導体層 450a を核として膜厚方向、即ち底部から内部に結晶成長が進行して第 2 の結晶性酸化物半導体層 450b が形成される。30

【 0 2 5 1 】

また、絶縁層 437 の形成から第 2 の加熱処理までの工程を大気に触れることなく連続的に行なうことが好ましい。絶縁層 437 の形成から第 2 の加熱処理までの工程は、水素及び水分をほとんど含まない雰囲気（不活性雰囲気、減圧雰囲気、乾燥空気雰囲気など）下に制御することが好ましく、例えば、露点 -40 以下、好ましくは露点 -50 以下の乾燥窒素雰囲気とする。40

【 0 2 5 2 】

次いで、第 1 の結晶性酸化物半導体層 450a と第 2 の結晶性酸化物半導体層 450b からなる酸化物半導体積層を加工して島状の酸化物半導体積層からなる酸化物半導体層 453 を形成する（図 16（C）参照）。図では、第 1 の結晶性酸化物半導体層 450a と第 2 の結晶性酸化物半導体層 450b の界面を点線で示し、酸化物半導体積層と説明しているが、明確な界面が存在しているのではなく、あくまで分かりやすく説明するために図示している。

【 0 2 5 3 】

10

20

30

40

50

酸化物半導体積層の加工は、所望の形状のマスクを酸化物半導体積層上に形成した後、当該酸化物半導体積層をエッティングすることによって行うことができる。上述のマスクは、フォトリソグラフィなどの方法を用いて形成することができる。または、インクジェット法などの方法を用いてマスクを形成しても良い。

【0254】

なお、酸化物半導体積層のエッティングは、ドライエッティングでもウェットエッティングでもよい。もちろん、これらを組み合わせて用いてもよい。

【0255】

また、上記作製方法により、得られる第1の結晶性酸化物半導体層及び第2の結晶性酸化物半導体層は、C軸配向を有していることを特徴の一つとしている。ただし、第1の結晶性酸化物半導体層及び第2の結晶性酸化物半導体層は、単結晶構造ではなく、非晶質構造でもない構造であり、C軸配向を有した結晶(C Axis Aligned Crystal; CAACとも呼ぶ)を含む酸化物を有する。なお、第1の結晶性酸化物半導体層及び第2の結晶性酸化物半導体層は、一部に結晶粒界を有している。

10

【0256】

なお、第1及び第2の結晶性酸化物半導体層は、上述の実施の形態において示した酸化物半導体によって形成することができる。

【0257】

また、第1の結晶性酸化物半導体層上に第2の結晶性酸化物半導体層を形成する2層構造に限定されず、第2の結晶性酸化物半導体層の形成後に第3の結晶性酸化物半導体層を形成するための成膜と加熱処理のプロセスを繰り返し行って、3層以上の積層構造としてもよい。

20

【0258】

上記作製方法で形成された酸化物半導体積層からなる酸化物半導体層453を、図6乃至図9に示した酸化物半導体層644として用いることができる。

【0259】

また、酸化物半導体層644として本実施の形態の酸化物半導体積層を用いたトランジスタにおいては、電流は、主として酸化物半導体積層の界面を流れるトランジスタ構造であるため、トランジスタに光照射が行われ、またはBTストレスが与えられても、トランジスタ特性の劣化は抑制される、または低減される。

30

【0260】

酸化物半導体層453のような第1の結晶性酸化物半導体層と第2の結晶性酸化物半導体層の積層をトランジスタに用いることで、安定した電気的特性を有し、且つ、信頼性の高いトランジスタを実現できる。

【0261】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

【0262】

(実施の形態8)

本実施の形態では、c軸配向し、かつab面、表面または界面の方向から見て三角形状または六角形状の原子配列を有し、c軸においては金属原子が層状または金属原子と酸素原子とが層状に配列しており、ab面においてはa軸またはb軸の向きが異なる(c軸を中心に回転した)結晶(CAAC:C Axis Aligned Crystalともいう。)を含む酸化物について説明する。

40

【0263】

CAACを含む酸化物とは、広義に、非単結晶であって、そのab面に垂直な方向から見て、三角形、六角形、正三角形または正六角形の原子配列を有し、かつc軸方向に垂直な方向から見て、金属原子が層状、または金属原子と酸素原子が層状に配列した相を含む酸化物をいう。

【0264】

50

C A A C は単結晶ではないが、非晶質のみから形成されているものでもない。また、C A A C は結晶化した部分（結晶部分）を含むが、1つの結晶部分と他の結晶部分の境界を明確に判別できないこともある。

#### 【 0 2 6 5 】

C A A C に酸素が含まれている場合、酸素の一部は窒素で置換されてもよい。また、C A A C を構成する個々の結晶部分の c 軸は一定の方向（例えば、C A A C を支持する基板面、C A A C の表面などに垂直な方向）に揃っていてもよい。または、C A A C を構成する個々の結晶部分の a b 面の法線は一定の方向（例えば、C A A C を支持する基板面、C A A C の表面などに垂直な方向）を向いていてもよい。

#### 【 0 2 6 6 】

C A A C は、その組成などに応じて、導体であったり、半導体であったり、絶縁体であったりする。また、その組成などに応じて、可視光に対して透明であったり不透明であったりする。

#### 【 0 2 6 7 】

このようなC A A C の例として、膜状に形成され、膜表面または支持する基板面に垂直な方向から観察すると三角形または六角形の原子配列が認められ、かつその膜断面を観察すると金属原子または金属原子および酸素原子（または窒素原子）の層状配列が認められる結晶を挙げることもできる。

#### 【 0 2 6 8 】

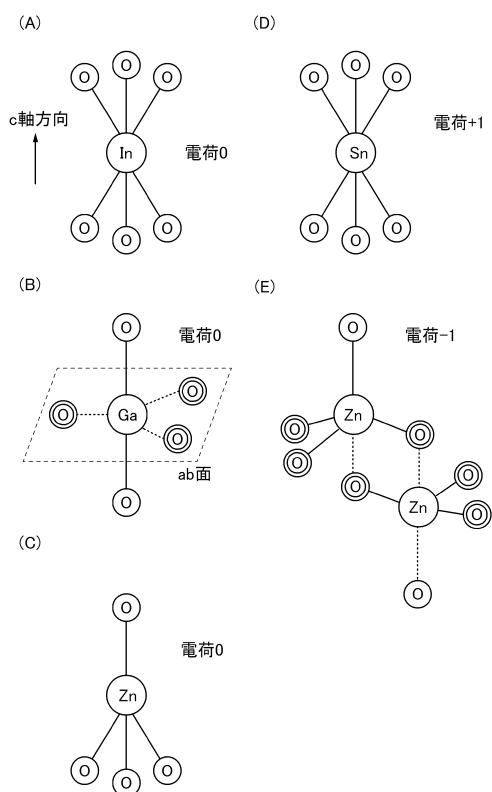

C A A C に含まれる結晶構造の一例について図19乃至図21を用いて詳細に説明する。なお、特に断りがない限り、図19乃至図21は上方向をc軸方向とし、c軸方向と直交する面をa b面とする。なお、単に上半分、下半分という場合、a b面を境にした場合の上半分、下半分をいう。また、図19において、丸で囲まれたOは4配位のOを示し、二重丸で囲まれたOは3配位のOを示す。

#### 【 0 2 6 9 】

図19(A)に、1個の6配位のInと、Inに近接の6個の4配位の酸素原子（以下4配位のO）と、を有する構造を示す。ここでは、金属原子が1個に対して、近接の酸素原子のみ示した構造を小グループと呼ぶ。図19(A)の構造は、八面体構造をとるが、簡単のため平面構造で示している。なお、図19(A)の上半分および下半分にはそれぞれ3個ずつ4配位のOがある。図19(A)に示す小グループは電荷が0である。

#### 【 0 2 7 0 】

図19(B)に、1個の5配位のGaと、Gaに近接の3個の3配位の酸素原子（以下3配位のO）と、近接の2個の4配位のOと、を有する構造を示す。3配位のOは、いずれもa b面に存在する。図19(B)の上半分および下半分にはそれぞれ1個ずつ4配位のOがある。また、Inも5配位をとるため、図19(B)に示す構造をとりうる。図19(B)に示す小グループは電荷が0である。

#### 【 0 2 7 1 】

図19(C)に、1個の4配位のZnと、Znに近接の4個の4配位のOと、を有する構造を示す。図19(C)の上半分には1個の4配位のOがあり、下半分には3個の4配位のOがある。または、図19(C)の上半分に3個の4配位のOがあり、下半分に1個の4配位のOがあつてもよい。図19(C)に示す小グループは電荷が0である。

#### 【 0 2 7 2 】

図19(D)に、1個の6配位のSnと、Snに近接の6個の4配位のOと、を有する構造を示す。図19(D)の上半分には3個の4配位のOがあり、下半分には3個の4配位のOがある。図19(D)に示す小グループは電荷が+1となる。

#### 【 0 2 7 3 】

図19(E)に、2個のZnを含む小グループを示す。図19(E)の上半分には1個の4配位のOがあり、下半分には1個の4配位のOがある。図19(E)に示す小グループは電荷が-1となる。

#### 【 0 2 7 4 】

10

20

30

40

50

ここでは、複数の小グループの集合体を中グループと呼び、複数の中グループの集合体を大グループ（ユニットセルともいう。）と呼ぶ。

#### 【0275】

ここで、これらの小グループ同士が結合する規則について説明する。図19(A)に示す6配位のInの上半分の3個のOは下方向にそれぞれ3個の近接Inを有し、下半分の3個のOは上方向にそれぞれ3個の近接Inを有する。5配位のGaの上半分の1個のOは下方向に1個の近接Gaを有し、下半分の1個のOは上方向に1個の近接Gaを有する。4配位のZnの上半分の1個のOは下方向に1個の近接Znを有し、下半分の3個のOは上方向にそれぞれ3個の近接Znを有する。この様に、金属原子の上方向の4配位のOの数と、そのOの下方向にある近接金属原子の数は等しく、同様に金属原子の下方向の4配位のOの数と、そのOの上方向にある近接金属原子の数は等しい。Oは4配位なので、下方向にある近接金属原子の数と、上方向にある近接金属原子の数の和は4になる。従つて、金属原子の上方向にある4配位のOの数と、別の金属原子の下方向にある4配位のOの数との和が4個のとき、金属原子を有する二種の小グループ同士は結合することができる。例えば、6配位の金属原子（InまたはSn）が上半分の4配位のOを介して結合する場合、4配位のOが3個であるため、5配位の金属原子（GaまたはIn）、または4配位の金属原子（Zn）いずれかと結合することになる。

10

#### 【0276】

これらの配位数を有する金属原子は、c軸方向において、4配位のOを介して結合する。また、このほかにも、層構造の合計の電荷が0となるように複数の小グループが結合して中グループを構成する。

20

#### 【0277】

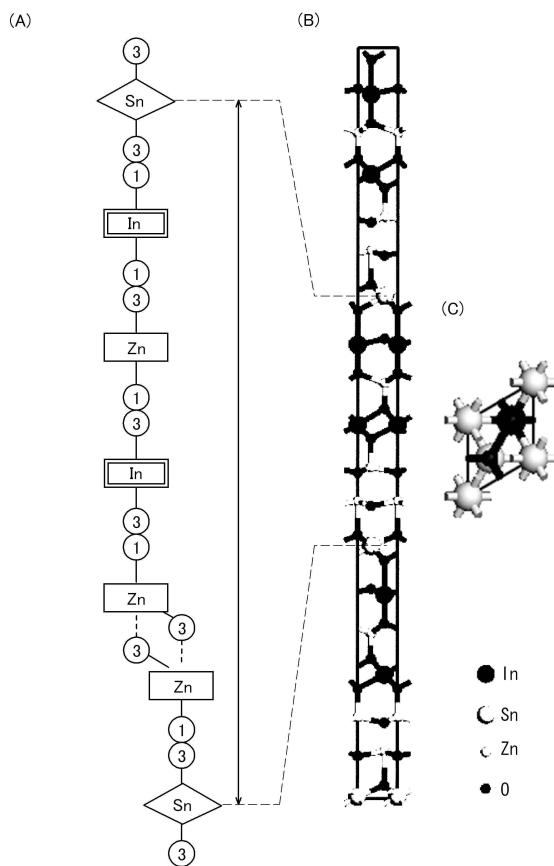

図20(A)に、In-Sn-Zn-O系の層構造を構成する中グループのモデル図を示す。図20(B)に、3つの中グループで構成される大グループを示す。なお、図20(C)は、図20(B)の層構造をc軸方向から観察した場合の原子配列を示す。

#### 【0278】

図20(A)においては、簡単のため、3配位のOは省略し、4配位のOは個数のみ示し、例えば、Snの上半分および下半分にはそれぞれ3個ずつ4配位のOがあることを丸枠の3として示している。同様に、図20(A)において、Inの上半分および下半分にはそれぞれ1個ずつ4配位のOがあり、丸枠の1として示している。また、同様に、図20(A)において、下半分には1個の4配位のOがあり、上半分には3個の4配位のOがあるZnと、上半分には1個の4配位のOがあり、下半分には3個の4配位のOがあるZnとを示している。

30

#### 【0279】

図20(A)において、In-Sn-Zn-O系の層構造を構成する中グループは、上から順に4配位のOが3個ずつ上半分および下半分にあるSnが、4配位のOが1個ずつ上半分および下半分にあるInと結合し、そのInが、上半分に3個の4配位のOがあるZnと結合し、そのZnの下半分の1個の4配位のOを介して4配位のOが3個ずつ上半分および下半分にあるInと結合し、そのInが、上半分に1個の4配位のOがあるZn2個からなる小グループと結合し、この小グループの下半分の1個の4配位のOを介して4配位のOが3個ずつ上半分および下半分にあるSnと結合している構成である。この中グループが複数結合して大グループを構成する。

40

#### 【0280】

ここで、3配位のOおよび4配位のOの場合、結合1本当たりの電荷はそれぞれ-0.667、-0.5と考えることができる。例えば、In(6配位または5配位)、Zn(4配位)、Sn(5配位または6配位)の電荷は、それぞれ+3、+2、+4である。従つて、Snを含む小グループは電荷が+1となる。そのため、Snを含む層構造を形成するためには、電荷+1を打ち消す電荷-1が必要となる。電荷-1をとる構造として、図19(E)に示すように、2個のZnを含む小グループが挙げられる。例えば、Snを含む小グループが1個に対し、2個のZnを含む小グループが1個あれば、電荷が打ち消さ

50

れるため、層構造の合計の電荷を 0 とすることができます。

【0281】

具体的には、図 20 (B) に示した大グループが繰り返されることで、 $In - Sn - Zn - O$  系の結晶 ( $In_2SnZn_3O_8$ ) を得ることができる。なお、得られる  $In - Sn - Zn - O$  系の層構造は、 $In_2SnZn_2O_7$  ( $ZnO$ )<sub>m</sub> (m は 0 または自然数。) とする組成式で表すことができる。

【0282】

また、このほかにも、四元系金属の酸化物である  $In - Sn - Ga - Zn$  系酸化物や、三元系金属の酸化物である  $In - Ga - Zn$  系酸化物 (IGZOとも表記する。)、 $In - Al - Zn$  系酸化物、 $Sn - Ga - Zn$  系酸化物、 $Al - Ga - Zn$  系酸化物、 $Sn - Al - Zn$  系酸化物や、 $In - Hf - Zn$  系酸化物、 $In - La - Zn$  系酸化物、 $In - Ce - Zn$  系酸化物、 $In - Pr - Zn$  系酸化物、 $In - Nd - Zn$  系酸化物、 $In - Pm - Zn$  系酸化物、 $In - Sm - Zn$  系酸化物、 $In - Eu - Zn$  系酸化物、 $In - Gd - Zn$  系酸化物、 $In - Tb - Zn$  系酸化物、 $In - Dy - Zn$  系酸化物、 $In - Ho - Zn$  系酸化物、 $In - Er - Zn$  系酸化物、 $In - Tm - Zn$  系酸化物、 $In - Yb - Zn$  系酸化物、 $In - Lu - Zn$  系酸化物や、二元系金属の酸化物である  $In - Zn$  系酸化物、 $Sn - Zn$  系酸化物、 $Al - Zn$  系酸化物、 $Zn - Mg$  系酸化物、 $Sn - Mg$  系酸化物、 $In - Mg$  系酸化物や、 $In - Ga$  系酸化物などを用いた場合も同様である。

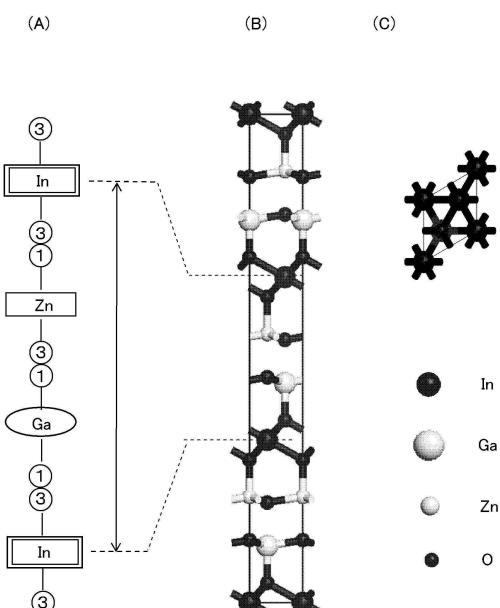

【0283】

例えば、図 21 (A) に、 $In - Ga - Zn - O$  系の層構造を構成する中グループのモ 20 デル図を示す。

【0284】

図 21 (A) において、 $In - Ga - Zn - O$  系の層構造を構成する中グループは、上から順に 4 配位の O が 3 個ずつ上半分および下半分にある In が、4 配位の O が 1 個上半分にある Zn と結合し、その Zn の下半分の 3 個の 4 配位の O を介して、4 配位の O が 1 個ずつ上半分および下半分にある Ga と結合し、その Ga の下半分の 1 個の 4 配位の O を介して、4 配位の O が 3 個ずつ上半分および下半分にある In と結合している構成である。この中グループが複数結合して大グループを構成する。

【0285】

図 21 (B) に 3 つの中グループで構成される大グループを示す。なお、図 21 (C) 30 は、図 21 (B) の層構造を c 軸方向から観察した場合の原子配列を示している。

【0286】

ここで、In (6 配位または 5 配位)、Zn (4 配位)、Ga (5 配位) の電荷は、それぞれ +3、+2、+3 であるため、In、Zn および Ga のいずれかを含む小グループは、電荷が 0 となる。そのため、これらの小グループの組み合わせであれば中グループの合計の電荷は常に 0 となる。

【0287】

また、 $In - Ga - Zn - O$  系の層構造を構成する中グループは、図 21 (A) に示した中グループに限定されず、In、Ga、Zn の配列が異なる中グループを組み合わせた大グループも取りうる。

【0288】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

【0289】

(実施の形態 9)

酸化物半導体に限らず、実際に測定される絶縁ゲート型トランジスタの電界効果移動度は、さまざまな理由によって本来の移動度よりも低くなる。移動度を低下させる要因としては半導体内部の欠陥や半導体と絶縁膜との界面の欠陥があるが、Levinson モデルを用いると、半導体内部に欠陥がないと仮定した場合の電界効果移動度を理論的に導き出せる。

10

20

30

40

50

## 【0290】

半導体本来の移動度を  $\mu_0$  、測定される電界効果移動度を  $\mu$  とし、半導体中に何らかのポテンシャル障壁（粒界等）が存在すると仮定すると、以下の式で表現できる。

## 【0291】

## 【数2】

$$\mu = \mu_0 \exp\left(-\frac{E}{kT}\right)$$

## 【0292】

ここで、  $E$  はポテンシャル障壁の高さであり、  $k$  がボルツマン定数、  $T$  は絶対温度である。また、ポテンシャル障壁が欠陥に由来すると仮定すると、 Levinson モデルでは、以下の式で表される。 10

## 【0293】

## 【数3】

$$E = \frac{e^2 N^2}{8\epsilon n} = \frac{e^3 N^2 t}{8\epsilon C_{ox} V_g}$$

## 【0294】

ここで、  $e$  は電気素量、  $N$  はチャネル内の単位面積当たりの平均欠陥密度、  $\epsilon$  は半導体の誘電率、  $n$  は単位面積当たりのチャネルに含まれるキャリア数、  $C_{ox}$  は単位面積当たりの容量、  $V_g$  はゲート電圧、  $t$  はチャネルの厚さである。なお、厚さ 30 nm 以下の半導体層であれば、チャネルの厚さは半導体層の厚さと同一として差し支えない。 20

線形領域におけるドレイン電流  $I_d$  は、以下の式となる。

## 【0295】

## 【数4】

$$I_d = \frac{W \mu V_g V_d C_{ox}}{L} \exp\left(-\frac{E}{kT}\right)$$

## 【0296】

ここで、  $L$  はチャネル長、  $W$  はチャネル幅であり、ここでは、  $L = W = 10 \mu m$  である。また、  $V_d$  はドレイン電圧である。 30

上式の両辺を  $V_g$  で割り、更に両辺の対数を取ると、以下のようになる。

## 【0297】

## 【数5】

$$\ln\left(\frac{I_d}{V_g}\right) = \ln\left(\frac{W \mu V_d C_{ox}}{L}\right) - \frac{E}{kT} = \ln\left(\frac{W \mu V_d C_{ox}}{L}\right) - \frac{e^3 N^2 t}{8kT \epsilon C_{ox} V_g}$$

## 【0298】

数5の右辺は  $V_g$  の関数である。この式からわかるように、縦軸を  $\ln(I_d / V_g)$  、横軸を  $1 / V_g$  として実測値をプロットして得られるグラフの直線の傾きから欠陥密度  $N$  が求められる。すなわち、トランジスタの  $I_d$  -  $V_g$  特性から、欠陥密度を評価できる。酸化物半導体としては、インジウム ( $In$ )、スズ ( $Sn$ )、亜鉛 ( $Zn$ ) の比率が、  $In : Sn : Zn = 1 : 1 : 1$  のものでは欠陥密度  $N$  は  $1 \times 10^{12} / cm^2$  程度である。 40

## 【0299】

このようにして求めた欠陥密度等をもとに数2および数3より  $\mu_0 = 120 \text{ cm}^2 / \text{Vs}$  が導出される。欠陥のある  $In-Sn-Zn$  酸化物で測定される移動度は  $35 \text{ cm}^2 / \text{Vs}$  程度である。しかし、半導体内部および半導体と絶縁膜との界面の欠陥が無い酸化物半導体の移動度  $\mu_0$  は  $120 \text{ cm}^2 / \text{Vs}$  となると予想できる。

## 【0300】

ただし、半導体内部に欠陥がなくても、チャネルとゲート絶縁層との界面での散乱によってトランジスタの輸送特性は影響を受ける。すなわち、ゲート絶縁層界面から  $x$  だけ離れた場所における移動度  $\mu_1$  は、以下の式で表される。

### 【0301】

#### 【数6】

$$\frac{1}{\mu_1} = \frac{1}{\mu_0} + \frac{D}{B} \exp(-\frac{x}{G})$$

### 【0302】

ここで、Dはゲート方向の電界、B、Gは定数である。BおよびGは、実際の測定結果より求めることができ、上記の測定結果からは、 $B = 4.75 \times 10^7 \text{ cm/s}$ 、 $G = 10 \text{ nm}$ （界面散乱が及ぶ深さ）である。Dが増加する（すなわち、ゲート電圧が高くなる）と数6の第2項が増加するため、移動度  $\mu_1$  は低下することがわかる。

10

### 【0303】

半導体内部の欠陥が無い理想的な酸化物半導体をチャネルに用いたトランジスタの移動度  $\mu_2$  を計算した結果を図22に示す。なお、計算にはシノプシス社製デバイスシミュレーションソフト、Sentaurus Deviceを使用し、酸化物半導体のバンドギャップ、電子親和力、比誘電率、厚さをそれぞれ、2.8電子ボルト、4.7電子ボルト、15、15nmとした。これらの値は、スパッタリング法により形成された薄膜を測定して得られたものである。

20

### 【0304】

さらに、ゲート、ソース、ドレインの仕事関数をそれぞれ、5.5電子ボルト、4.6電子ボルト、4.6電子ボルトとした。また、ゲート絶縁層の厚さは100nm、比誘電率は4.1とした。チャネル長およびチャネル幅はともに10μm、ドレイン電圧  $V_d$  は0.1Vである。

### 【0305】

図22で示されるように、ゲート電圧1V強で移動度  $100 \text{ cm}^2/\text{Vs}$  以上のピークをつけるが、ゲート電圧がさらに高くなると、界面散乱が大きくなり、移動度が低下する。なお、界面散乱を低減するためには、半導体層表面を原子レベルで平坦にすること（Atomic Layer Flatness）が望ましい。

30

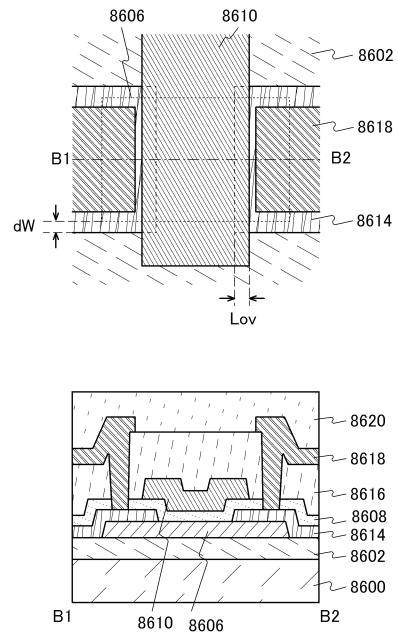

### 【0306】

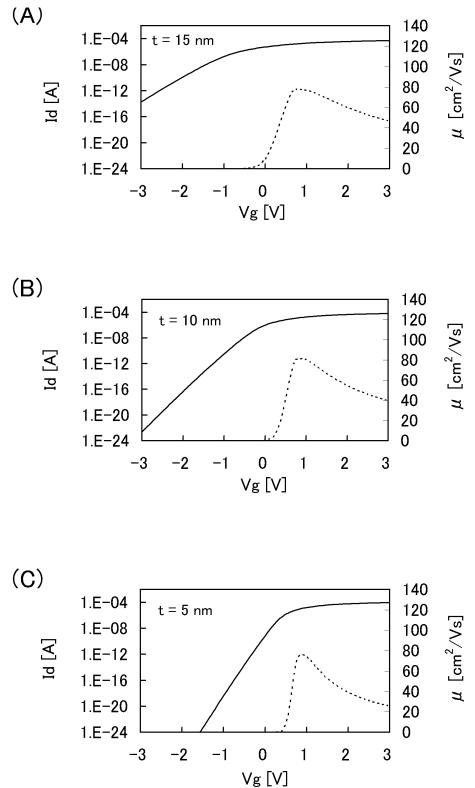

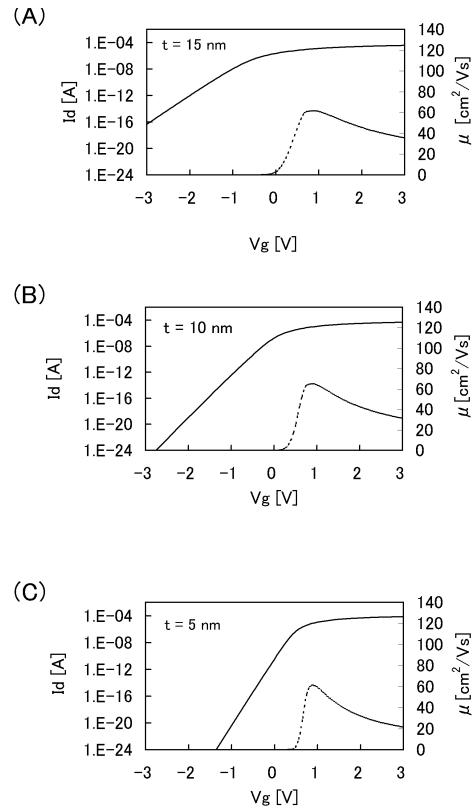

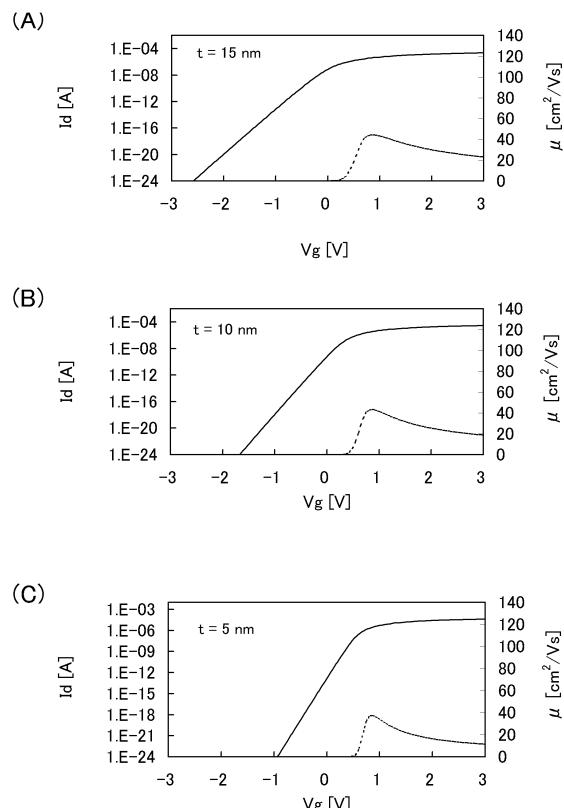

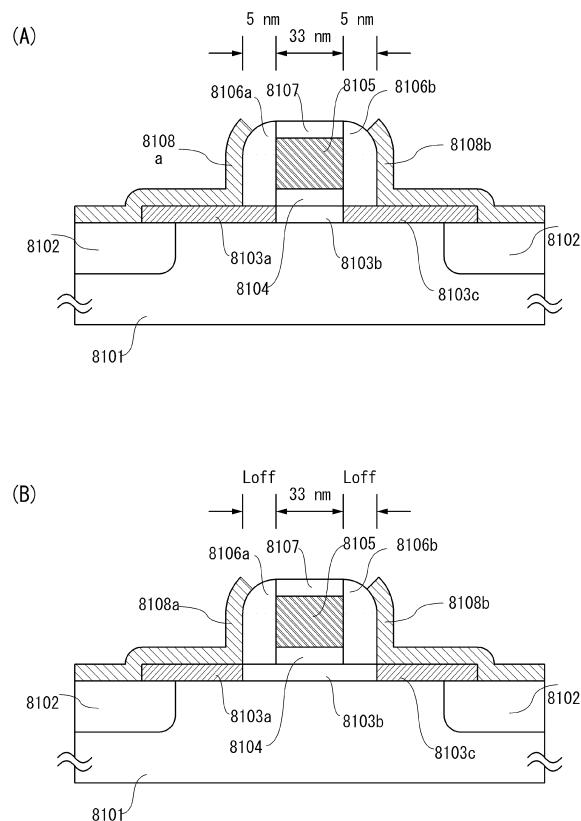

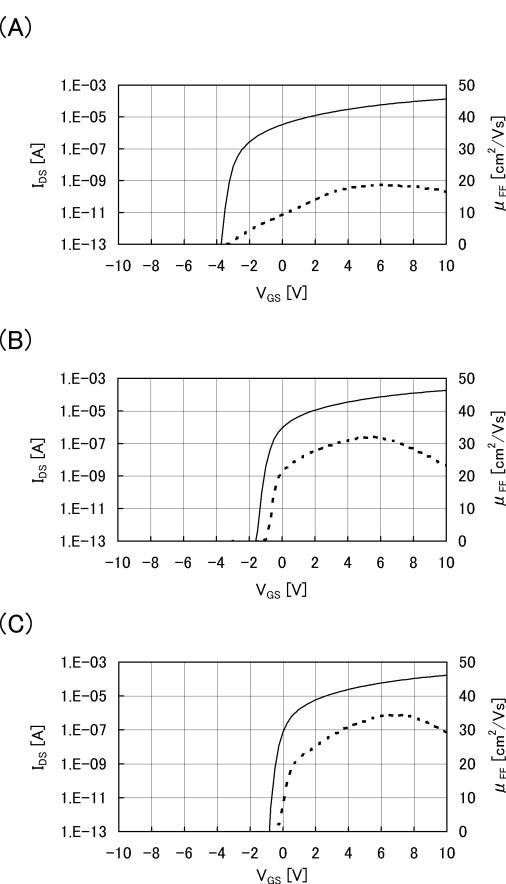

このような移動度を有する酸化物半導体を用いて微細なトランジスタを作製した場合の特性を計算した結果を図23乃至図25に示す。なお、計算に用いたトランジスタの断面構造を図26に示す。図26に示すトランジスタは酸化物半導体層に  $n^+$  の導電型を呈する半導体領域8103aおよび半導体領域8103cを有する。半導体領域8103aおよび半導体領域8103cの抵抗率は  $2 \times 10^{-3} \text{ cm}$  とする。

### 【0307】

図26(A)に示すトランジスタは、下地絶縁層8101と、下地絶縁層8101に埋め込まれるように形成された酸化アルミニウムによる埋め込み絶縁物8102の上に形成される。トランジスタは半導体領域8103a、半導体領域8103cと、それらに挟まれ、チャネル形成領域となる真性の半導体領域8103bと、ゲート電極8105を有する。ゲート電極8105の幅を33nmとする。

40

### 【0308】

ゲート電極8105と半導体領域8103bの間には、ゲート絶縁層8104を有し、また、ゲート電極8105の両側面には側壁絶縁物8106aおよび側壁絶縁物8106b、ゲート電極8105の上部には、ゲート電極8105と他の配線との短絡を防止するための絶縁物8107を有する。側壁絶縁物の幅は5nmとする。また、半導体領域8103aおよび半導体領域8103cに接して、ソース8108aおよびドレイン8108bを有する。なお、このトランジスタにおけるチャネル幅を40nmとする。

### 【0309】

50

図26(B)に示すトランジスタは、下地絶縁層8101と、酸化アルミニウムよりなる埋め込み絶縁物8102の上に形成され、半導体領域8103a、半導体領域8103cと、それらに挟まれた真性の半導体領域8103bと、幅33nmのゲート電極8105とゲート絶縁層8104と側壁絶縁物8106aおよび側壁絶縁物8106bと絶縁物8107とソース8108aおよびドレイン8108bを有する点で図26(A)に示すトランジスタと同じである。

#### 【0310】

図26(A)に示すトランジスタと図26(B)に示すトランジスタの相違点は、側壁絶縁物8106aおよび側壁絶縁物8106bの下の半導体領域の導電型である。図26(A)に示すトランジスタでは、側壁絶縁物8106aおよび側壁絶縁物8106bの下の半導体領域は $n^+$ の導電型を呈する半導体領域8103aおよび半導体領域8103cであるが、図26(B)に示すトランジスタでは、真性の半導体領域8103bである。すなわち、図26(B)に示す半導体層において、半導体領域8103a(半導体領域8103c)とゲート電極8105がLooffだけ重ならない領域ができている。この領域をオフセット領域といい、その幅Looffをオフセット長という。図から明らかなように、オフセット長は、側壁絶縁物8106a(側壁絶縁物8106b)の幅と同じである。

#### 【0311】

その他の計算に使用するパラメータは上述の通りである。計算にはシノプシス社製デバイスシミュレーションソフト、Sentaurus Deviceを使用した。図23は、図26(A)に示される構造のトランジスタのドレイン電流( $I_d$ 、実線)および移動度( $\mu$ 、点線)のゲート電圧( $V_g$ 、ゲートとソースの電位差)依存性を示す。ドレイン電流 $I_d$ は、ドレイン電圧(ドレインとソースの電位差)を+1Vとし、移動度 $\mu$ はドレイン電圧を+0.1Vとして計算したものである。

#### 【0312】

図23(A)はゲート絶縁層の厚さを15nmとしたものであり、図23(B)は10nmとしたものであり、図23(C)は5nmとしたものである。ゲート絶縁層が薄くなるほど、特にオフ状態でのドレイン電流 $I_d$ (オフ電流)が顕著に低下する。一方、移動度 $\mu$ のピーク値やオン状態でのドレイン電流 $I_d$ (オン電流)には目立った変化がない。ゲート電圧1V前後で、ドレイン電流は記憶素子等で必要とされる10μAを超えることが示された。

#### 【0313】

図24は、図26(B)に示される構造のトランジスタで、オフセット長Looffを5nmとしたもののドレイン電流 $I_d$ (実線)および移動度 $\mu$ (点線)のゲート電圧 $V_g$ 依存性を示す。ドレイン電流 $I_d$ は、ドレイン電圧を+1Vとし、移動度 $\mu$ はドレイン電圧を+0.1Vとして計算したものである。図24(A)はゲート絶縁層の厚さを15nmとしたものであり、図24(B)は10nmとしたものであり、図24(C)は5nmとしたものである。

#### 【0314】

また、図25は、図26(B)に示される構造のトランジスタで、オフセット長Looffを15nmとしたもののドレイン電流 $I_d$ (実線)および移動度 $\mu$ (点線)のゲート電圧依存性を示す。ドレイン電流 $I_d$ は、ドレイン電圧を+1Vとし、移動度 $\mu$ はドレイン電圧を+0.1Vとして計算したものである。図25(A)はゲート絶縁層の厚さを15nmとしたものであり、図25(B)は10nmとしたものであり、図25(C)は5nmとしたものである。

#### 【0315】

いずれもゲート絶縁層が薄くなるほど、オフ電流が顕著に低下する一方、移動度 $\mu$ のピーク値やオン電流には目立った変化がない。

#### 【0316】

なお、移動度 $\mu$ のピークは、図23では $80\text{ cm}^2/\text{Vs}$ 程度であるが、図24では $60\text{ cm}^2/\text{Vs}$ 程度、図25では $40\text{ cm}^2/\text{Vs}$ 程度と、オフセット長Looffが増加

10

20

30

40

50

するほど低下する。また、オフ電流も同様な傾向がある。一方、オン電流もオフセット長  $L_{off}$  の増加にともなって減少するが、オフ電流の低下に比べるとはるかに緩やかである。また、いずれもゲート電圧 1 V 前後で、ドレイン電流は記憶素子等で必要とされる 10  $\mu A$  を超えることが示された。

#### 【0317】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

#### 【0318】

##### (実施の形態 10)

本実施の形態は、酸化物半導体層にチャネルが形成されるトランジスタの一例として、

In、Sn、Znを主成分とする酸化物半導体をチャネル形成領域とするトランジスタについて、より詳細に説明する。In、Sn、Znを主成分とする酸化物半導体層にチャネルが形成されるトランジスタは、該酸化物半導体層となる酸化物半導体膜を形成する際に基板を加熱して成膜すること、或いは酸化物半導体膜を形成した後に熱処理を行うことで良好な特性を得ることができる。なお、主成分とは組成比で 5 atomic % 以上含まれる元素をいう。

#### 【0319】

In、Sn、Znを主成分とする酸化物半導体膜の成膜後に基板を意図的に加熱することで、トランジスタの電界効果移動度を向上させることができるとなる。また、トランジスタのしきい値電圧をプラスシフトさせ、ノーマリ・オフ化させることができるとなる。

#### 【0320】

例えば、図 27 (A) ~ (C) は、In、Sn、Znを主成分とし、チャネル長  $L$  が 3  $\mu m$ 、チャネル幅  $W$  が 10  $\mu m$  である酸化物半導体膜と、厚さ 100 nm のゲート絶縁層を用いたトランジスタの特性である。なお、 $V_d$  は 10 V とした。

#### 【0321】

図 27 (A) は基板を意図的に加熱せずにスパッタリング法で In、Sn、Znを主成分とする酸化物半導体膜を形成したときのトランジスタ特性である。このとき電界効果移動度は  $18.8 \text{ cm}^2 / \text{V sec}$  が得られている。一方、基板を意図的に加熱して In、Sn、Znを主成分とする酸化物半導体膜を形成すると電界効果移動度を向上させることができるとなる。図 27 (B) は基板を 200 °C に加熱して In、Sn、Znを主成分とする酸化物半導体膜を形成したときのトランジスタ特性を示すが、電界効果移動度は  $32.2 \text{ cm}^2 / \text{V sec}$  が得られている。

#### 【0322】

電界効果移動度は、In、Sn、Znを主成分とする酸化物半導体膜を形成した後に熱処理をすることによって、さらに高めることができる。図 27 (C) は、In、Sn、Znを主成分とする酸化物半導体膜を 200 °C でスパッタリング成膜した後、650 °C で熱処理をしたときのトランジスタ特性を示す。このとき電界効果移動度は  $34.5 \text{ cm}^2 / \text{V sec}$  が得られている。

#### 【0323】

基板を意図的に加熱することでスパッタリング成膜中の水分が酸化物半導体膜中に取り込まれるのを低減する効果が期待できる。また、成膜後に熱処理をすることによっても、酸化物半導体膜から水素や水酸基若しくは水分を放出させ除去することができ、上記のように電界効果移動度を向上させることができる。このような電界効果移動度の向上は、脱水化・脱水素化による不純物の除去のみならず、高密度化により原子間距離が短くなるためとも推定される。また、酸化物半導体から不純物を除去して高純度化することで結晶化を図ることができる。このように高純度化された非単結晶酸化物半導体は、理想的には 100  $\text{cm}^2 / \text{V sec}$  を超える電界効果移動度を実現することも可能になると推定される。

#### 【0324】

In、Sn、Znを主成分とする酸化物半導体に酸素イオンを注入し、熱処理により該

10

20

30

40

50

酸化物半導体に含まれる水素や水酸基若しくは水分を放出させ、その熱処理と同時に又はその後の熱処理により酸化物半導体を結晶化させてても良い。このような結晶化若しくは再結晶化の処理により結晶性の良い非単結晶酸化物半導体を得ることができる。

#### 【0325】

基板を意図的に加熱して成膜すること及び／又は成膜後に熱処理することの効果は、電界効果移動度の向上のみならず、トランジスタのノーマリ・オフ化を図ることにも寄与している。基板を意図的に加熱しないで形成されたIn、Sn、Znを主成分とする酸化物半導体膜をチャネル形成領域としたトランジスタは、しきい値電圧がマイナスシフトしてしまう傾向がある。しかし、基板を意図的に加熱して形成された酸化物半導体膜を用いた場合、このしきい値電圧のマイナスシフト化は解消される。つまり、しきい値電圧はトランジスタがノーマリ・オフとなる方向に動き、このような傾向は図27(A)と図27(B)の対比からも確認することができる。10

#### 【0326】

なお、しきい値電圧はIn、Sn及びZnの比率を変えることによっても制御することが可能であり、組成比としてIn : Sn : Zn = 2 : 1 : 3とすることでトランジスタのノーマリ・オフ化を期待することができる。また、ターゲットの組成比をIn : Sn : Zn = 2 : 1 : 3とすることで結晶性の高い酸化物半導体膜を得ることができる。

#### 【0327】

意図的な基板加熱温度若しくは熱処理温度は、150以上、好ましくは200以上、より好ましくは400以上であり、より高温で成膜し或いは熱処理することでトランジスタのノーマリ・オフ化を図ることが可能となる。20

#### 【0328】

また、意図的に基板を加熱した成膜及び／又は成膜後に熱処理をすることで、ゲートバイアス・ストレスに対する安定性を高めることができる。例えば、2MV/cm、150、1時間印加の条件において、ドリフトがそれぞれ±1.5V未満、好ましくは1.0V未満を得ることができる。

#### 【0329】

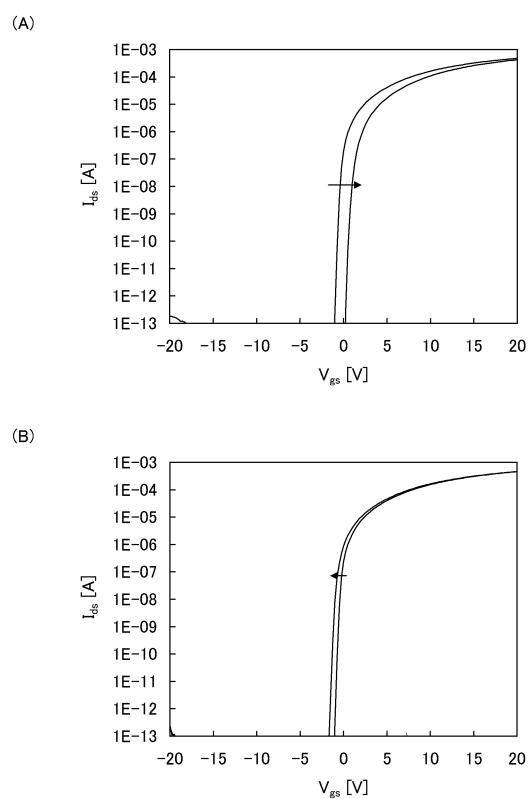

実際に、酸化物半導体膜成膜後に加熱処理を行っていない試料1と、650の加熱処理を行った試料2のトランジスタに対してBT試験を行った。

#### 【0330】

まず基板温度を25とし、 $V_{ds}$ を10Vとし、トランジスタの $V_g - I_d$ 特性の測定を行った。なお、 $V_{ds}$ はドレイン電圧(ドレインとソースの電位差)を示す。次に、基板温度を150とし、 $V_{ds}$ を0.1Vとした。次に、ゲート絶縁層に印加される電界強度が2MV/cmとなるように $V_g$ に20Vを印加し、そのまま1時間保持した。次に、 $V_g$ を0Vとした。次に、基板温度25とし、 $V_{ds}$ を10Vとし、トランジスタの $V_g - I_d$ 測定を行った。これをプラスBT試験と呼ぶ。30

#### 【0331】

同様に、まず基板温度を25とし、 $V_{ds}$ を10Vとし、トランジスタの $V_g - I_d$ 特性の測定を行った。次に、基板温度を150とし、 $V_{ds}$ を0.1Vとした。次に、ゲート絶縁層に印加される電界強度が-2MV/cmとなるように $V_g$ に-20Vを印加し、そのまま1時間保持した。次に、 $V_g$ を0Vとした。次に、基板温度25とし、 $V_{ds}$ を10Vとし、トランジスタの $V_g - I_d$ 測定を行った。これをマイナスBT試験と呼ぶ。40

#### 【0332】

試料1のプラスBT試験の結果を図28(A)に、マイナスBT試験の結果を図28(B)に示す。また、試料2のプラスBT試験の結果を図29(A)に、マイナスBT試験の結果を図29(B)に示す。

#### 【0333】

試料1のプラスBT試験およびマイナスBT試験によるしきい値電圧の変動は、それぞれ1.80Vおよび-0.42Vであった。また、試料2のプラスBT試験およびマイナ50

SBT試験によるしきい値電圧の変動は、それぞれ0.79Vおよび0.76Vであった。試料1および試料2のいずれも、BT試験前後におけるしきい値電圧の変動が小さく、信頼性が高いことがわかる。

#### 【0334】

熱処理は酸素雰囲気中で行うことができるが、まず窒素若しくは不活性ガス、または減圧下で熱処理を行ってから酸素を含む雰囲気中で熱処理を行っても良い。最初に脱水化・脱水素化を行ってから酸素を酸化物半導体に加えることで、熱処理の効果をより高めることができる。また、後から酸素を加えるには、酸素イオンを電界で加速して酸化物半導体膜に注入する方法を適用しても良い。

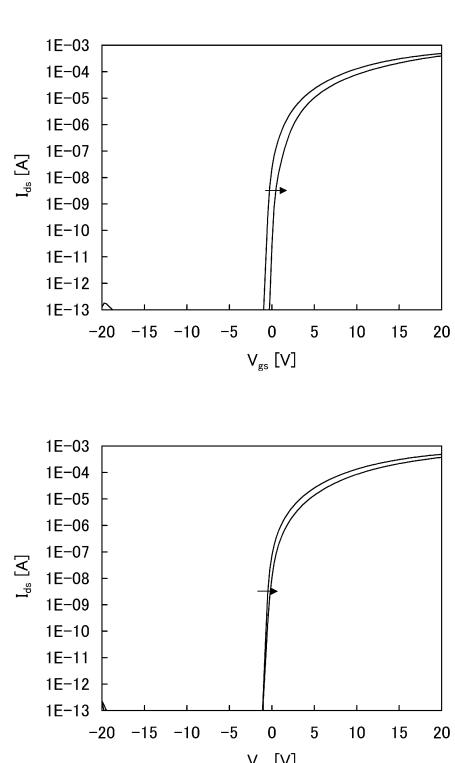

#### 【0335】