(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4877868号

(P4877868)

(45) 発行日 平成24年2月15日(2012.2.15)

(24) 登録日 平成23年12月9日(2011.12.9)

|                         |                      |

|-------------------------|----------------------|

| (51) Int.Cl.            | F 1                  |

| HO 1 L 21/336 (2006.01) | HO 1 L 29/78 6 1 2 D |

| HO 1 L 29/786 (2006.01) | HO 1 L 21/288 Z      |

| HO 1 L 21/288 (2006.01) | HO 1 L 29/78 6 1 2 C |

| HO 1 L 51/50 (2006.01)  | HO 1 L 29/78 6 1 7 J |

|                         | HO 5 B 33/14 A       |

請求項の数 12 (全 56 頁)

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2004-348260 (P2004-348260)  |

| (22) 出願日     | 平成16年12月1日 (2004.12.1)        |

| (65) 公開番号    | 特開2005-191555 (P2005-191555A) |

| (43) 公開日     | 平成17年7月14日 (2005.7.14)        |

| 審査請求日        | 平成19年11月13日 (2007.11.13)      |

| (31) 優先権主張番号 | 特願2003-403849 (P2003-403849)  |

| (32) 優先日     | 平成15年12月2日 (2003.12.2)        |

| (33) 優先権主張国  | 日本国 (JP)                      |

| (31) 優先権主張番号 | 特願2003-403850 (P2003-403850)  |

| (32) 優先日     | 平成15年12月2日 (2003.12.2)        |

| (33) 優先権主張国  | 日本国 (JP)                      |

|           |                                                |

|-----------|------------------------------------------------|

| (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (72) 発明者  | 山崎 舜平<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 桑原 秀明<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 前川 慎志<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 藤井 厳<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内    |

最終頁に続く

(54) 【発明の名称】表示装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

開口部を有する第1の絶縁層を形成し、

前記開口部に第1の導電層を形成し、

導電性材料を含む液滴を噴出することにより、前記第1の絶縁層及び前記第1の導電層に接して第2の導電層を形成し、

前記第2の導電層上に、ゲート絶縁膜を介して半導体層を形成し、

前記半導体層上に、導電性材料を含む液滴を噴出することにより第3の導電層を形成し、

前記第3の導電層上に、第2の絶縁層及び第4の導電層を形成し、

前記第1の導電層は、前記第2の導電層より、幅が広くかつ厚く、

前記第4の導電層は、前記第3の導電層より、幅が広くかつ厚く、

前記第1の絶縁層は、スピンドルコート法又はディップ法により全面に形成した絶縁層を工

ッチングすることによって形成することを特徴とする表示装置の作製方法。

## 【請求項 2】

開口部を有する第1の絶縁層を形成し、

前記開口部に第1の導電層を形成し、

導電性材料を含む液滴を噴出することにより、前記第1の絶縁層及び前記第1の導電層に接して第2の導電層を形成し、

前記第2の導電層上に、ゲート絶縁膜を介して半導体層を形成し、

10

20

前記半導体層上に、導電性材料を含む液滴を噴出することにより第3の導電層を形成し、

前記第3の導電層上に、第1の電極を形成し、

前記第1の電極上に、電界発光層を形成し、

前記電界発光層上に、第2の電極を形成し、

前記第1の導電層は、前記第2の導電層より、幅が広くかつ厚く、

前記第1の絶縁層は、スピンドルコート法又はディップ法により全面に形成した絶縁層を工

ッチングすることによって形成することを特徴とする表示装置の作製方法。

## 【請求項3】

開口部を有する第1の絶縁層を形成し、

前記開口部に第1の導電層を形成し、

導電性材料を含む液滴を噴出することにより、前記第1の絶縁層及び前記第1の導電層

に接して第2の導電層を形成し、

前記第2の導電層上に、ゲート絶縁膜を介して半導体層を形成し、

前記半導体層上に、導電性材料を含む液滴を噴出することにより一対の第3の導電層を

形成し、

一対の前記第3の導電層の一方の上に、第1の電極を形成し、

一対の前記第3の導電層の他方の上に、第2の絶縁層及び第4の導電層を形成し、

前記第1の電極上に、電界発光層を形成し、

前記電界発光層上に、第2の電極を形成し、

前記第1の導電層は、前記第2の導電層より、幅が広くかつ厚く、

前記第1の絶縁層は、スピンドルコート法又はディップ法により全面に形成した絶縁層を工

ッチングすることによって形成することを特徴とする表示装置の作製方法。

## 【請求項4】

開口部を有する第1の絶縁層を形成し、

前記開口部に第1の導電層を形成し、

導電性材料を含む液滴を噴出することにより、前記第1の絶縁層及び前記第1の導電層

に接して第2の導電層を形成し、

前記第2の導電層上に、ゲート絶縁膜を介して半導体層を形成し、

前記半導体層上に、導電性材料を含む液滴を噴出することにより第3の導電層を形成し、

前記第3の導電層上に、第2の絶縁層及び第4の導電層を形成し、

前記第1の導電層は、前記第2の導電層より、幅が広くかつ厚く、

前記第4の導電層は、前記第3の導電層より、幅が広くかつ厚く、

前記第1の絶縁層は、絶縁性材料を含む液滴を噴出することにより形成することを特徴

とする表示装置の作製方法。

## 【請求項5】

開口部を有する第1の絶縁層を形成し、

前記開口部に第1の導電層を形成し、

導電性材料を含む液滴を噴出することにより、前記第1の絶縁層及び前記第1の導電層

に接して第2の導電層を形成し、

前記第2の導電層上に、ゲート絶縁膜を介して半導体層を形成し、

前記半導体層上に、導電性材料を含む液滴を噴出することにより第3の導電層を形成し、

前記第3の導電層上に、第1の電極を形成し、

前記第1の電極上に、電界発光層を形成し、

前記電界発光層上に、第2の電極を形成し、

前記第1の導電層は、前記第2の導電層より、幅が広くかつ厚く、

前記第1の絶縁層は、絶縁性材料を含む液滴を噴出することにより形成することを特徴

とする表示装置の作製方法。

10

20

30

40

50

## 【請求項 6】

開口部を有する第 1 の絶縁層を形成し、

前記開口部に第 1 の導電層を形成し、

導電性材料を含む液滴を噴出することにより、前記第 1 の絶縁層及び前記第 1 の導電層に接して第 2 の導電層を形成し、

前記第 2 の導電層上に、ゲート絶縁膜を介して半導体層を形成し、

前記半導体層上に、導電性材料を含む液滴を噴出することにより一対の第 3 の導電層を形成し、

一対の前記第 3 の導電層の一方の上に、第 1 の電極を形成し、

一対の前記第 3 の導電層の他方の上に、第 2 の絶縁層及び第 4 の導電層を形成し、 10

前記第 1 の電極上に、電界発光層を形成し、

前記電界発光層上に、第 2 の電極を形成し、

前記第 1 の導電層は、前記第 2 の導電層より、幅が広くかつ厚く、

前記第 1 の絶縁層は、絶縁性材料を含む液滴を噴出することにより形成することを特徴とする表示装置の作製方法。

## 【請求項 7】

請求項 1 乃至 請求項 6 のいずれか一項において、

前記第 1 の導電層の下に、酸化チタン膜を形成することを特徴とする表示装置の作製方法。

## 【請求項 8】

請求項 1 乃至 請求項 7 のいずれか一項において、

前記第 1 の導電層の下に、W (タンゲステン)、A l (アルミニウム)、T a (タンタル)、Z r (ジルコニウム)、H f (ハフニウム)、I r (イリジウム)、N b (ニオブ)、P d (鉛)、P t (白金)、M o (モリブデン)、R h (ロジウム)、S c (スカンジウム)、T i (チタン)、V (バナジウム)、C r (クロム)、M n (マンガン)、F e (鉄)、C o (コバルト)、N i (ニッケル)、C u (銅) 又は Z n (亜鉛) の元素を有する膜、もしくは、前記元素の酸化物、前記元素の窒化物又は前記元素の酸窒化物を有する膜を形成することを特徴とする表示装置の作製方法。

## 【請求項 9】

請求項 1 乃至 請求項 8 のいずれか一項において、

前記導電性材料は、銀、金、銅、又はインジウム錫酸化物を有することを特徴とする表示装置の作製方法。

## 【請求項 10】

請求項 1 乃至 請求項 9 のいずれか一項において、

前記半導体層は、水素又はハロゲン元素を含むガスを用いて形成された非単結晶半導体を有することを特徴とする表示装置の作製方法。

## 【請求項 11】

請求項 1 乃至 請求項 9 のいずれか一項において、

前記半導体層は、水素又はハロゲン元素を含むガスを用いて形成されたセミアモルファス半導体を有することを特徴とする表示装置の作製方法。 40

## 【請求項 12】

請求項 1 乃至 請求項 9 のいずれか一項において、

前記半導体層は、水素とハロゲン元素を含むガスを用いて形成された多結晶半導体を有することを特徴とする表示装置の作製方法。

## 【発明の詳細な説明】

## 【技術分野】

## 【0 0 0 1】

本発明は、液滴吐出法を用いた表示装置及びその作製方法、並びにテレビジョン装置に関する。

## 【背景技術】

**【0002】**

薄膜トランジスタ（以下、「TFT」という。）及びそれを用いた電子回路は、半導体、絶縁体及び導電体などの各種薄膜を基板上に積層し、適宜フォトリソグラフィ技術により所定のパターンを形成して製造されている。フォトリソグラフィ技術とは、フォトマスクと呼ばれる透明な平板面上に光を通さない材料で形成した回路等のパターンを、光を利用して目的とする基板上に転写する技術であり、半導体集積回路等の製造工程において広く用いられている。

**【0003】**

従来のフォトリソグラフィ技術を用いた製造工程では、フォトレジストと呼ばれる感光性の有機樹脂材料を用いて形成されるマスクパターンの取り扱いだけでも、露光、現像、焼成、剥離といった多段階の工程が必要になる。従って、フォトリソグラフィ工程の回数が増える程、製造コストは必然的に上がってしまうことになる。このような問題点を改善するために、フォトリソグラフィ工程を削減してTFTを製造することが試みられている（例えば、特許文献1参照。）。

10

**【0004】**

しかし、上記特許文献1に記載された技術は、TFTの製造工程で複数回行われるフォトリソグラフィ工程の一部を印刷法で置き替えただけのものであり、抜本的に工程数の削減に寄与できるものではない。また、フォトリソグラフィ技術においてマスクマスクパターンを転写するために用いる露光装置は、等倍投影露光若しくは縮小投影露光により、数ミクロンから1ミクロン以下のパターンを転写するものであり、原理的にみて、一辺が1メートルを越えるような大面積基板を一括で露光することは技術的に困難である。

20

**【特許文献1】特開平11-251259号公報****【発明の開示】****【発明が解決しようとする課題】****【0005】**

本発明は、TFT及びそれを用いる電子回路並びにTFTによって形成される表示装置の製造工程においてフォトリソグラフィ工程の回数を削減し、或いはその工程自体を無くすることで製造工程を簡略化し、一辺が1メートルを越えるような大面積の基板にも、低いコストで歩留まり良く製造することができる技術を提供することを目的とする。

30

**【課題を解決するための手段】****【0006】**

上述した従来技術の課題を解決するために、本発明においては以下の手段を講じる。

**【0007】**

本発明は、配線層若しくは電極を形成する導電層や、所定のパターンを形成するためのマスク層など表示パネルを作製するために必要なパターンのうち、少なくとも一つ若しくはそれ以上を、選択的にパターンを形成可能な方法により形成して、表示装置を作製することを特徴とするものである。選択的にパターンを形成可能な方法として、導電層や絶縁層など形成し、特定の目的に調合された組成物の液滴を選択的に吐出して所定のパターンを形成することができる、液滴吐出法（その方式によっては、インクジェット法とも呼ばれる。）を用いる。また、パターンが転写、または描写できる方法、例えば印刷法（スクリーン印刷やオフセット印刷などパターンが形成される方法）なども用いることができる。

40

**【0008】**

本発明は、エレクトロルミネンス（以下「EL」ともいう。）と呼ばれる発光を発現する有機物、若しくは有機物と無機物の混合物を含む媒体を、電極間に介在させた発光素子、又は液晶材料を有する液晶素子を表示素子とTFTとが接続された表示装置（発光表示装置、液晶表示装置）であって、このような表示装置を液滴吐出法を用いて作製する。

**【0009】**

また、本発明は、液滴吐出法によりパターンを形成するに際し、その形成する領域に密

50

着性を向上させる手段（下地前処理）を行い、表示装置の信頼性を向上させる。

【0010】

本発明は、密着性を高める効果を有する物質を利用して、配線、その他半導体膜、絶縁膜、マスク等表示装置を構成することを特徴とする。工程において、所定の組成物を含む液滴を細孔から吐出して所定のパターンを形成する際、その密着性を高めるために下地前処理として高融点金属からなる物質を形成する。具体的には、高融点金属からなる導電層上又はその両端に、塗布法等により、溶媒に混入された配線材料（配線材料（導電性材料）を溶媒に溶解又は分散させたものを含む）を形成し、配線を形成することを特徴とする。例えば、高融点金属や、3d遷移元素からなる導電層上に、液滴吐出法により、溶媒に混入された導電体を吐出する。液滴吐出法以外に、スピンドルティング法、ディップ法、他の塗布法、印刷法（スクリーン印刷やオフセット印刷などパターンが形成される方法）により、前記高融点金属からなる導電層上に、溶媒に混入された導電体を形成してもよい。

【0011】

下地前処理として用いられる物質は、酸化チタン（ $TiO_x$ ）、チタン酸ストロンチウム（ $SrTiO_3$ ）、セレン化カドミウム（ $CdSe$ ）、タンタル酸カリウム（ $KTaO_3$ ）、硫化カドミウム（ $CdS$ ）、酸化ジルコニア（ $ZrO_2$ ）、酸化ニオブ（ $Nb_2O_5$ ）、酸化亜鉛（ $ZnO$ ）、酸化鉄（ $Fe_2O_3$ ）、酸化タンクス滕（ $WO_3$ ）等を用いることができる。

【0012】

ゾルゲル法のディップコーティング法、スピンドルティング法、液滴吐出法、イオンプレーティング法、イオンビーム法、CVD法、スパッタリング法、RFマグネットロンスパッタリング法、プラズマ溶射法、プラズマスプレー法、又は陽極酸化法により形成することができる。また物質は、その形成方法により膜としての連続性を有さなくても良い。

【0013】

前記高融点金属、または3d遷移元素として、 $Ti$ （チタン）、 $W$ （タンクス滕）、 $Cr$ （クロム）、 $Al$ （アルミニウム）、 $Ta$ （タンタル）、 $Ni$ （ニッケル）、 $Zr$ （ジルコニア）、 $Hf$ （ハフニウム）、 $V$ （バナジウム）、 $Ir$ （イリジウム）、 $Nb$ （ニオブ）、 $Pd$ （鉛）、 $Pt$ （白金）、 $Mo$ （モリブデン）、 $Co$ （コバルト）、 $Rh$ （ロジウム）、 $Sc$ （スカンジウム）、 $Mn$ （マンガン）、 $Fe$ （鉄）、 $Cu$ （銅）又は $Zn$ （亜鉛）の材料、またそれらの酸化物、窒化物、酸化窒化物などを用いることができる。前記導電層は、スパッタリング法、蒸着法、イオン注入法、CVD法、ディップ法、スピンドルティング法等の公知の方法で形成することを特徴とし、好適には、スパッタリング法、ディップ法又はスピンドルティング法で形成することを特徴とする。また、後に導電層を絶縁化する場合には、導電層を0.01~10nmの厚さで形成し、自然酸化で絶縁化すると簡便であり好ましい。

【0014】

また、他の方法として、形成領域（被形成面）に対してプラズマ処理を行う方法がある。プラズマ処理の条件は、空気、酸素又は窒素を処理ガスとして用い、圧力を数十Torr~1000Torr（133000Pa）、好ましくは100（13300Pa）~1000Torr（133000Pa）、より好ましくは700Torr（93100Pa）~800Torr（106400Pa）、つまり大気圧又は大気圧近傍の圧力となる状態で、パルス電圧を印加する。このとき、プラズマ密度は、 $1 \times 10^{10} \sim 1 \times 10^{14} m^{-3}$ 、所謂コロナ放電やグロー放電の状態となるようにする。空気、酸素又は窒素の処理ガスを用いプラズマ処理を用いることにより、材質依存性なく、表面改質を行うことができる。その結果、あらゆる材料に対して表面改質を行うことができる。

【0015】

また、他の方法として、液滴吐出法によるパターンのその形成領域との密着性を上げるために、接着材として機能するような有機材料系の物質を形成してもよい。材料としては、感光性または非感光性の有機材料（有機樹脂材料）（ポリイミド、アクリル、ポリアミ

10

20

30

40

50

ド、ポリイミドアミド、レジスト、ベンゾシクロブテンなど)、低誘電率であるLow-k材料などの一種、もしくは複数種からなる膜、またはこれらの膜の積層などを用いることができる。また、シリコン(Si)と酸素(O)との結合で骨格構造が構成され、置換基に少なくとも水素を含む材料、もしくは置換基にフッ素、アルキル基、または芳香族炭化水素のうち少なくとも1種を有する材料を用いてもよい。作製法としては、液滴吐出法や、印刷法(スクリーン印刷やオフセット印刷などパターンが形成される方法)を用いることもできる。塗布法で得られるT OF膜やSOG膜なども用いることができる。

#### 【0016】

上記、液滴吐出法を用いて形成される導電体の領域に、下地前処理として密着性向上や、表面改質のために行われる工程は、液滴吐出法を用いて形成したパターンの上に、さらに導電体を形成する場合行っても良い。また、その場合の下地前処理として、液滴吐出法によって第1の導電層を形成した後、紫外線の照射をする紫外線照射処理を行い、処理領域に第2の導電層を液滴吐出法により形成しても良い。例えば、径の大きな吐出口を用いて、幅広のパターンを形成した後、径の小さな吐出口を用いて幅広のパターンに部分的に重なるように細いパターンを形成し、微細なパターンを形成することも出来る。

10

#### 【0017】

導電体(導電層)を形成するため、液滴吐出法により吐出口から吐出する組成物は、導電性材料を溶媒に溶解又は分散させたものを用いる。導電性材料とは、Ag、Au、Cu、Ni、Pt、Pd、Ir、Rh、W、Al等の金属、Cd、Znの金属硫化物、Fe、Ti、Si、Ge、Si、Zr、Baなどの酸化物、ハロゲン化銀の微粒子又は分散性ナノ粒子に相当する。また、導電性材料として前記金属や化合物の混合物を用いてもよい。また、透明導電膜として用いられるインジウム錫酸化物(ITO)、インジウム錫酸化物と酸化珪素からなるITSO、有機インジウム、有機スズ、酸化亜鉛、窒化チタン等に相当する。但し、吐出口から吐出する組成物は、比抵抗値を考慮して、金、銀、銅のいずれかの材料を溶媒に溶解又は分散させたものを用いることが好適であり、より好適には、低抵抗な銀、銅を用いるとよい。但し、銀、銅を用いる場合には、不純物対策のため、合わせてバリア膜を設けるとよい。バリア膜としては、窒化珪素膜やニッケルボロン(NiB)を用いるとことができる。

20

#### 【0018】

また、導電性材料の周りに他の導電性材料がコーティングされ、複数の層になっている粒子でも良い。例えば、銅の周りにニッケルボロン(NiB)がコーティングされ、その周囲に銀がコーティングされている3層構造の粒子などを用いても良い。溶媒は、酢酸ブチル、酢酸エチル等のエステル類、イソプロピルアルコール、エチルアルコール等のアルコール類、メチルエチルケトン、アセトン等の有機溶剤等を用いる。組成物の粘度は20mPa·s(cPs)以下が好適であり、これは、乾燥が起こることを防止したり、吐出口から組成物を円滑に吐出できるようにしたりするためである。また、組成物の表面張力は、40mN/m以下が好適である。但し、用いる溶媒や、用途に合わせて、組成物の粘度等は適宜調整するとよい。一例として、ITOや、有機インジウム、有機スズを溶媒に溶解又は分散させた組成物の粘度は5~20mPa·s、銀を溶媒に溶解又は分散させた組成物の粘度は5~20mPa·s、金を溶媒に溶解又は分散させた組成物の粘度は5~20mPa·sに設定するとよい。

30

#### 【0019】

本発明では、表示装置を構成する導電層のうち、ゲート線やソース線、他の引き回し配線など比較的広い線幅で形成する導電層(バスラインとも呼ばれる)を、絶縁層に埋め込むように液滴吐出法によって形成する。一方、画素部内のゲート電極やソース、ドレン電極、他の配線などの比較的細い線幅の導電層は、液滴吐出法により直接描画し、形成する。本発明によりゲート配線の線幅は10~40μm、ゲート電極の線幅は5~20μm、ゲート配線の線幅がゲート電極の線幅の約2倍となるような配線が形成できる。本発明により、配線への大電流を効率よく、高速で流すための低抵抗化と、電極への断線のないパターンの微細化という要求が、両方満たすことができる。絶縁層間へ埋め込みで形成

40

50

する幅広の配線と、微細な導電層の形成は、他工程で行ってもよいし、同時に行ってもよい。それぞれその配線に要求される役割と、表示装置の構成の違いによって、微細パターンを先に行っても、後から形成してもよく、その順序には限定されない。

#### 【0020】

本発明の薄膜トランジスタの一は、開口部を有する絶縁層と、開口部に設けられた第1の導電層と、絶縁層と第1の導電層とに接して、設けられた第2の導電層とを有し、第1の導電層は、第2の導電層より、幅が広くかつ厚いことを特徴とする。

#### 【0021】

本発明の薄膜トランジスタの一は、開口部を有する絶縁層と、開口部に設けられた第1の導電層と、絶縁層と第1の導電層とに接して、設けられた第2の導電層とを有し、第1の導電層は、第2の導電層より、幅が広くかつ厚く、第2の導電層は導電性材料を有する液滴を噴出して形成されることを特徴とする。

10

#### 【0022】

本発明の表示装置の一は、開口部を有する絶縁層と、開口部に設けられた第1の導電層と、絶縁層と第1の導電層とに接して、設けられた第2の導電層と、第2の導電層上にゲート絶縁膜を介して設けられた半導体層と、半導体層上に設けられた一対の第3の導電層と、一方の第3の導電層上に設けられた第1の電極と、第1の電極上に設けられた電界発光層と、電界発光層上に設けられた第2の電極とを有し、第1の導電層は、第2の導電層より、幅が広くかつ厚いことを特徴とする。

#### 【0023】

20

本発明の表示装置の一は、開口部を有する絶縁層と、開口部に設けられた第1の導電層と、絶縁層と第1の導電層とに接して、設けられた第2の導電層と、第2の導電層上にゲート絶縁膜を介して設けられた半導体層と、半導体層上に設けられた一対の第3の導電層と、一方の第3の導電層上に設けられた第1の電極と、第1の電極上に設けられた電界発光層と、電界発光層上に設けられた第2の電極とを有し、第1の導電層は、第2の導電層より、幅が広くかつ厚く、第2の導電層は導電性材料を有する液滴を噴出して形成されることを特徴とする。

#### 【0024】

本発明の表示装置の一は、開口部を有する絶縁層と、開口部に設けられた第1の導電層と、絶縁層と第1の導電層とに接して、設けられた第2の導電層と、第2の導電層上にゲート絶縁膜を介して設けられた半導体層と、半導体層上に設けられた一対の第3の導電層と、一方の第3の導電層上に設けられた第1の電極と、他方の第3の導電層上に設けられた開口部を有する第2の絶縁層と、開口部に設けられた第4の導電層と、第1の電極上に設けられた電界発光層と、電界発光層上に設けられた第2の電極とを有し、第1の導電層は、第2の導電層より、幅が広くかつ厚く、第4の導電層は、第3の導電層より、幅が広くかつ厚いことを特徴とする。

30

#### 【0025】

本発明の表示装置の一は、開口部を有する絶縁層と、開口部に設けられた第1の導電層と、絶縁層と第1の導電層とに接して、設けられた第2の導電層と、第2の導電層上にゲート絶縁膜を介して設けられた半導体層と、半導体層上に設けられた一対の第3の導電層と、一方の第3の導電層上に設けられた第1の電極と、他方の第3の導電層上に設けられた開口部を有する第2の絶縁層と、開口部に設けられた第4の導電層と、第1の電極上に設けられた電界発光層と、電界発光層上に設けられた第2の電極とを有し、第1の導電層は、第2の導電層より、幅が広くかつ厚く、第4の導電層は、第3の導電層より、幅が広くかつ厚く、第2の導電層及び第3の導電層は導電性材料を有する液滴を噴出して形成されることを特徴とする。

40

#### 【0026】

本発明において、第1の導電層、第2の導電層、ゲート電極、ソース電極、ドレイン電極、第1の電極、第2の電極は前述の導電体を形成する材料によって、液滴吐出法によって形成することができる。

50

## 【0027】

本発明の表示装置の一は、開口部を有する絶縁層と、開口部に設けられた第1の導電層と、絶縁層及び第1の導電層上に、設けられた第2の導電層を有し、第1の導電層は、第2の導電層より、幅が広くかつ厚いことを特徴とする。

## 【0028】

本発明の表示装置の一は、開口部を有する絶縁層と、開口部に設けられた第1の導電層と、絶縁層及び第1の導電層上に、設けられた第2の導電層を有し、第1の導電層は、第2の導電層より、幅が広くかつ厚く、第2の導電層は導電性材料を有する液滴を噴出して形成されることを特徴とする。

## 【0029】

本発明の表示装置の一は、開口部を有する絶縁層と、開口部に設けられた第1の導電層と、絶縁層と第1の導電層とに接して、設けられた第2の導電層と、第2の導電層上にゲート絶縁膜を介して設けられた半導体層と、半導体層上に設けられた第3の導電層と、第3の導電層上に設けられた開口部を有する第2の絶縁層と、開口部に設けられた第4の導電層とを有し、第1の導電層は、第2の導電層より、幅が広くかつ厚く、第4の導電層は、第3の導電層より、幅が広くかつ厚いことを特徴とする。

## 【0030】

本発明の表示装置の一は、開口部を有する絶縁層と、開口部に設けられた第1の導電層と、絶縁層と第1の導電層とに接して、設けられた第2の導電層と、第2の導電層上にゲート絶縁膜を介して設けられた半導体層と、半導体層上に設けられた第3の導電層と、第3の導電層上に設けられた開口部を有する第2の絶縁層と、開口部に設けられた第4の導電層とを有し、第1の導電層は、第2の導電層より、幅が広くかつ厚く、第4の導電層は、第3の導電層より、幅が広くかつ厚く、第2の導電層及び第3の導電層は導電性材料を有する液滴を噴出して形成されることを特徴とする。

## 【0031】

上記構成において、液滴吐出法により形成された第1の導電層、第2の導電層、ゲート電極、ソース電極またはドレイン電極の線幅は、5 μm以上100 μm以下であることが好ましい。液滴吐出法により、液量を0.1 p1以上40 p1吐出し、パターンを形成することができる。

## 【0032】

上記構成において、半導体層が、水素とハロゲン元素を含み、結晶構造を含むセミアモルファス半導体であってもよい。水素とハロゲン元素を含む非単結晶半導体、水素とハロゲン元素を含む多結晶半導体であってもよい。半導体層のチャネルの長さは5 μm以上100 μm以下であると好ましい。また、上記構成の表示装置で、表示画面を構成したことを特徴とするテレビジョン装置を作製することができる。

## 【0033】

本発明の表示装置の作製方法の一は、開口部を有する絶縁層を形成し、開口部に第1の導電層を形成し、導電性材料を有する液滴を噴出することにより、絶縁層及び第1の導電層に接して第2の導電層を形成し、第2の導電層上にゲート絶縁膜を介して半導体層を形成し、半導体層上に、導電性材料を有する液滴を噴出することにより第3の導電層を形成し、第3の導電層上に第1の電極を形成し、第1の電極上に電界発光層を形成し、電界発光層上に第2の電極を形成し、第1の導電層は、第2の導電層より、幅が広くかつ厚くなるように形成することを特徴とする。

## 【0034】

本発明の表示装置の作製方法の一は、開口部を有する絶縁層を形成し、開口部に第1の導電層を形成し、導電性材料を有する液滴を噴出することにより、絶縁層及び第1の導電層に接して第2の導電層を形成し、第2の導電層上にゲート絶縁膜を介して半導体層を形成し、半導体層上に、導電性材料を有する液滴を噴出することにより一対の第3の導電層を形成し、一方の第3の導電層上に第1の電極を形成し、他方の第3の導電層上に第2の絶縁層及び第4の導電層を形成し、第1の電極上に電界発光層を形成し、電界発光層上に

10

20

30

40

50

第2の電極を形成し、第1の導電層は、第2の導電層より、幅が広くかつ厚くなるように形成することを特徴とする。

#### 【0035】

本発明の表示装置の作製方法の一は、開口部を有する絶縁層を形成し、開口部に第1の導電層を形成し、導電性材料を有する液滴を噴出することにより、絶縁層及び第1の導電層に接して第2の導電層を形成し、第2の導電層上にゲート絶縁膜を介して半導体層を形成し、半導体層上に、導電性材料を有する液滴を噴出することにより第3の導電層を形成し、第3の導電層上に第1の電極を形成し、第1の電極上に電界発光層を形成し、電界発光層上に第2の電極を形成し、第1の導電層は、第2の導電層より、幅が広くかつ厚くなるように形成する。

10

#### 【0036】

本発明の表示装置の作製方法の一は、開口部を有する絶縁層を形成し、開口部に第1の導電層を形成し、導電性材料を有する液滴を噴出することにより、絶縁層及び第1の導電層に接して第2の導電層を形成し、第2の導電層上にゲート絶縁膜を介して半導体層を形成し、半導体層上に、導電性材料を有する液滴を噴出することにより一対の第3の導電層を形成し、一方の第3の導電層上に第1の電極を形成し、他方の第3の導電層上に第2の絶縁層及び第4の導電層を形成し、第1の電極上に電界発光層を形成し、電界発光層上に第2の電極を形成し、第1の導電層は、第2の導電層より、幅が広くかつ厚くなるように形成する。

#### 【0037】

20

ゲート絶縁膜は、第1の窒化珪素膜、酸化珪素膜及び第2の窒化珪素膜を順次積層して形成することで、ゲート電極の酸化を防止出来、かつ、ゲート絶縁膜の上層側に形成する半導体層と良好な界面を形成することが出来る。

#### 【0038】

本発明は、ゲート電極層や配線層、及びパターニングの時に利用するマスクを形成する際に液滴吐出法により行うことを特徴としているが、表示装置を作製するために必要なパターンのうち、少なくとも一つ若しくはそれ以上を、選択的にパターンを形成可能な方法により形成して、表示装置を製造することでその目的は達成される。

#### 【0039】

また、第1の絶縁層及び第2の絶縁層は、有機材料、無機材料又は珪素と酸素との結合で骨格構造が形成された材料で形成してもよい。有機材料は、その平坦性が優れているため、後に導電体を成膜した際にも、段差部で膜厚が極端に薄くなったり、断線が起こったりすることがなく、好適である。また、有機材料は、誘電率が低い。そのため、複数の配線の層間絶縁体として用いると、配線容量が低減し、多層配線を形成することが可能となり、高性能化及び高機能化が実現される。

30

#### 【0040】

一方、珪素と酸素との結合で骨格構造が形成された材料としては、シロキサン系ポリマーが代表例として挙げられ、詳しくは、珪素と酸素との結合で骨格構造が構成され置換基に少なくとも水素を含む材料、又は、置換基にフッ素、アルキル基、または芳香族炭化水素のうち少なくとも1種を有する材料である。この材料も平坦性に優れており、また透明性や耐熱性をも有し、シロキサンポリマーからなる絶縁体を形成後に300度～600度程度以下の温度で加熱処理を行うことができる。

40

#### 【発明の効果】

#### 【0041】

本発明により、導電層のパターンをその線幅によって作り分けることが出来るので、表示装置を構成する配線のうち、太い幅の低抵抗な配線と、画素部などに用いられる微細な配線の両方とを、その役割によって要求される機能を満たすように形成することができる。

#### 【0042】

50

本発明によれば、液滴吐出法により、配線層やマスクのパターニングを直接行うことが

できるので、材料の利用効率を向上させて、かつ、作製工程を簡略化した TFT 及びそれを用いた信頼性の高い表示装置を得ることができる。

【発明を実施するための最良の形態】

【0043】

本発明の実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々なに変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。

10

【0044】

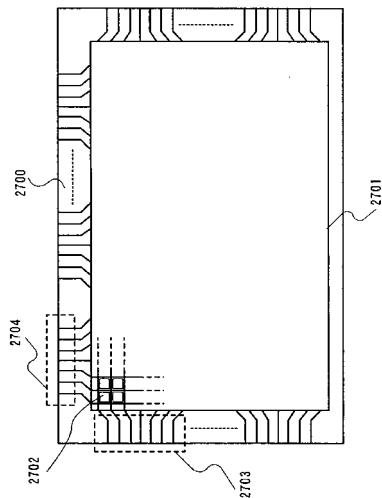

図38は本発明に係る表示パネルの構成を示す上面図であり、絶縁表面を有する基板2700上に画素2702をマトリクス上に配列させた画素部2701、走査線側入力端子2703、信号線側入力端子2704が形成されている。画素数は種々の規格に従って設ければ良く、XGAであれば $1024 \times 768 \times 3$ (RGB)、UXGAであれば $1600 \times 1200 \times 3$ (RGB)、フルスペックハイビジョンに対応させるのであれば $1920 \times 1080 \times 3$ (RGB)とすれば良い。

【0045】

画素2702は、走査線側入力端子2703から延在する走査線と、信号線側入力端子2704から延在する信号線とが交差することで、マトリクス状に配設される。画素2702のそれぞれには、スイッチング素子とそれに接続する画素電極が備えられている。スイッチング素子の代表的な一例はTFTであり、TFTのゲート電極側が走査線と、ソース若しくはドレイン側が信号線と接続されることにより、個々の画素を外部から入力する信号によって独立して制御可能としている。

20

【0046】

TFTは、その主要な構成要素として、半導体層、ゲート絶縁層及びゲート電極層が挙げられ、半導体層に形成されるソース及びドレイン領域に接続する配線層がそれに付随する。構造的には基板側から半導体層、ゲート絶縁層及びゲート電極層を配設したトップゲート型と、基板側からゲート電極層、ゲート絶縁層及び半導体層を配設したボトムゲート型などが代表的に知られているが、本発明においてはそれらの構造のどのようなものを用いても良い。

30

【0047】

半導体層を形成する材料は、シリコンやゲルマンに代表される半導体材料ガスを用いて気相成長法やスパッタリング法で作製されるアモルファス半導体(以下「AS」ともいう。)、該非晶質半導体を光エネルギーや熱エネルギーを利用して結晶化させた多結晶半導体、或いはセミアモルファス(微結晶若しくはマイクロクリスタルとも呼ばれる。以下「SAS」ともいう。)半導体などを用いることができる。

【0048】

SASは、非晶質と結晶構造(単結晶、多結晶を含む)の中間的な構造を有し、自由エネルギー的に安定な第3の状態を有する半導体であって、短距離秩序を持ち格子歪みを有する結晶質な領域を含んでいる。少なくとも膜中の一部の領域には、 $0.5 \sim 20 \text{ nm}$ の結晶領域を観測することが出来、珪素を主成分とする場合にはラマンスペクトルが $520 \text{ cm}^{-1}$ よりも低波数側にシフトしている。X線回折では珪素結晶格子に由来するとされる(111)、(220)の回折ピークが観測される。未結合手(ダンギングボンド)の中和剤として水素またはハロゲンを少なくとも1原子%またはそれ以上含ませている。SASは、珪化物気体をグロー放電分解(プラズマCVD)して形成する。珪化物気体としては、 $\text{SiH}_4$ 、その他にも $\text{Si}_2\text{H}_6$ 、 $\text{SiH}_2\text{Cl}_2$ 、 $\text{SiHCl}_3$ 、 $\text{SiCl}_4$ 、 $\text{SiF}_4$ などを用いることが可能である。また $\text{GeF}_4$ を混合させても良い。この珪化物気体を $\text{H}_2$ 、又は、 $\text{H}_2$ と $\text{He}$ 、 $\text{Ar}$ 、 $\text{Kr}$ 、 $\text{Ne}$ から選ばれた一種または複数種の希ガス元素で希釈しても良い。希釈率は2~1000倍の範囲。圧力は概略 $0.1 \text{ Pa} \sim 133 \text{ Pa}$ の範

40

50

囲、電源周波数は1MHz～120MHz、好ましくは13MHz～60MHz、基板加熱温度は300以下でよい。膜中の不純物元素として、酸素、窒素、炭素などの大気成分の不純物は $1 \times 10^{20}$ atoms/cm<sup>3</sup>以下とすることが望ましく、特に、酸素濃度は $5 \times 10^{19}$ atoms/cm<sup>3</sup>以下、好ましくは $1 \times 10^{19}$ atoms/cm<sup>3</sup>以下とする。

#### 【0049】

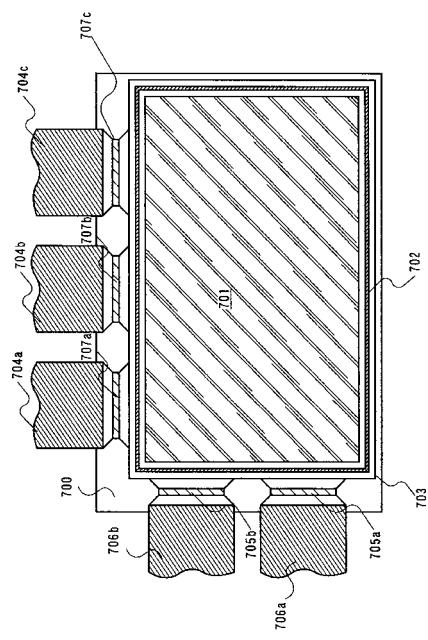

図38は、走査線及び信号線へ入力する信号を、外付けの駆動回路により制御する表示パネルの構成を示しているが、図27に示すように、COG(Chip on Glass)によりドライバICを基板700上に実装しても良い。ドライバICは単結晶半導体基板に形成されたものでも良いし、ガラス基板上にTFTで回路を形成したものであっても良い。

#### 【0050】

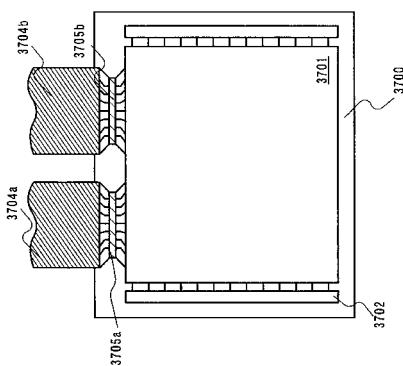

また、画素に設けるTFTをSASで形成する場合には、図11に示すように走査線側の駆動回路3702を基板3700上に形成し一体化することも出来る。図11において、3701は画素領域であり、信号線側駆動回路は、COGによりドライバIC3705a、3705bを実装し、FPC3704a、3704bに接続している。

#### 【0051】

##### (実施の形態1)

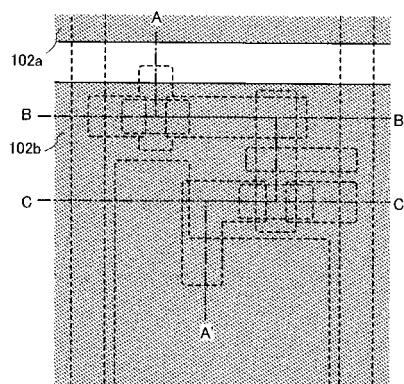

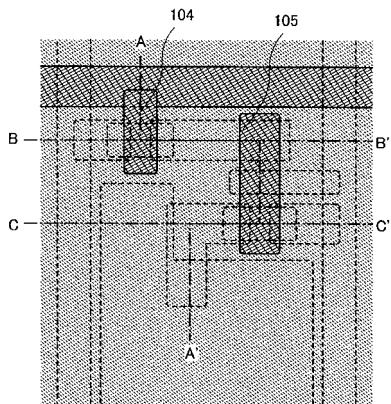

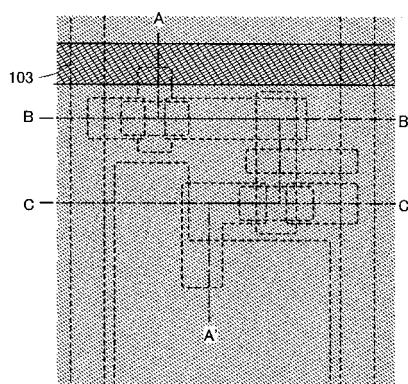

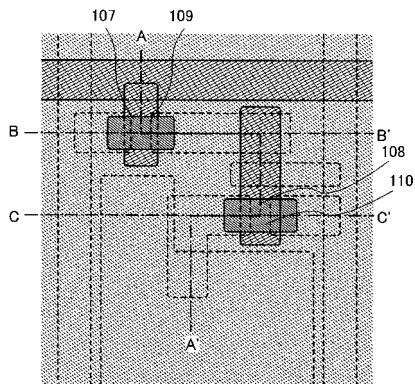

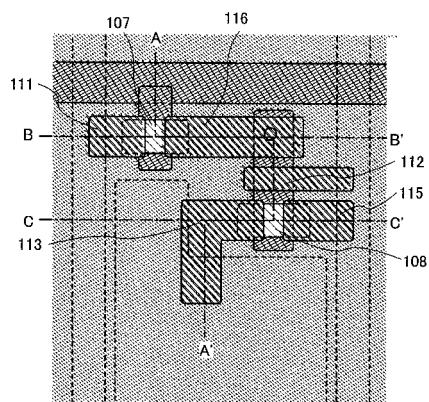

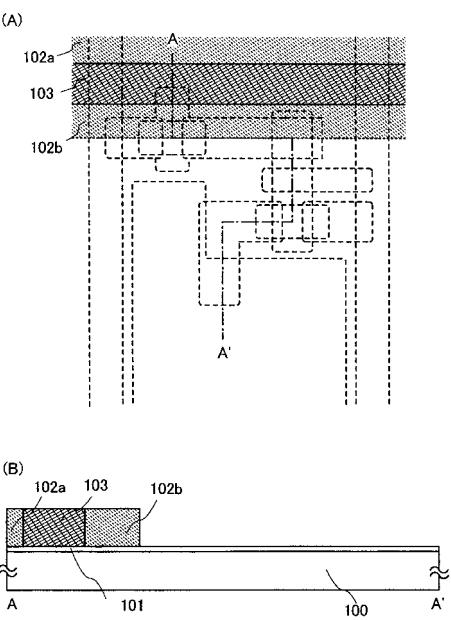

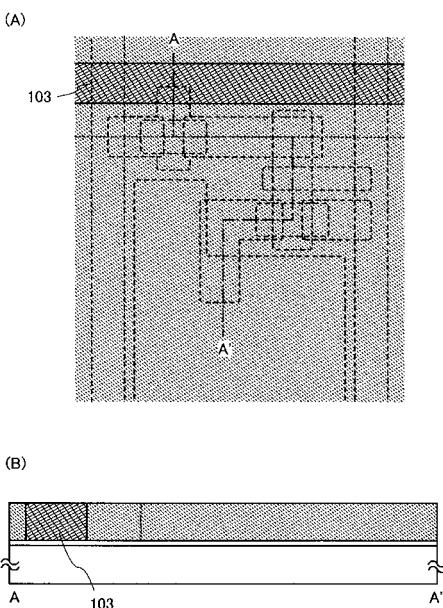

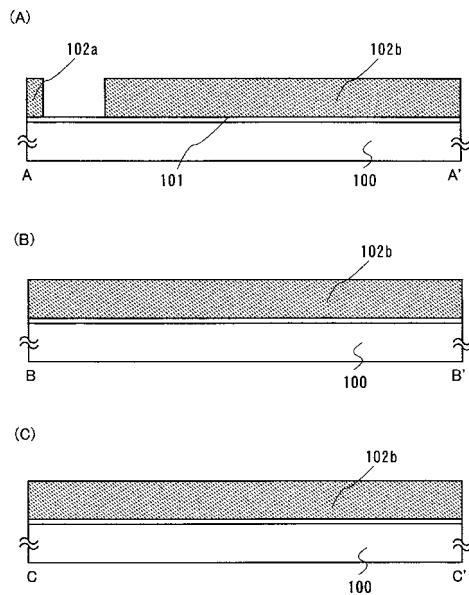

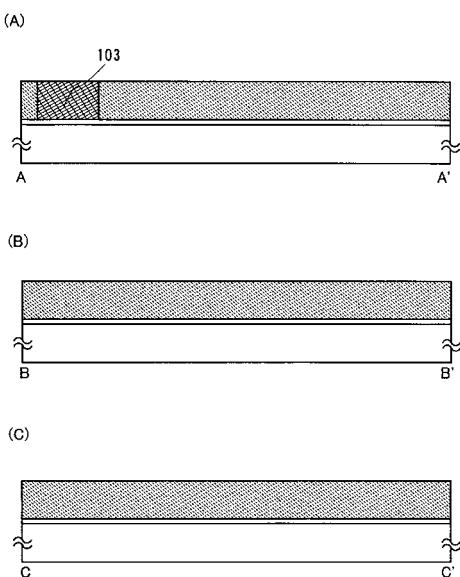

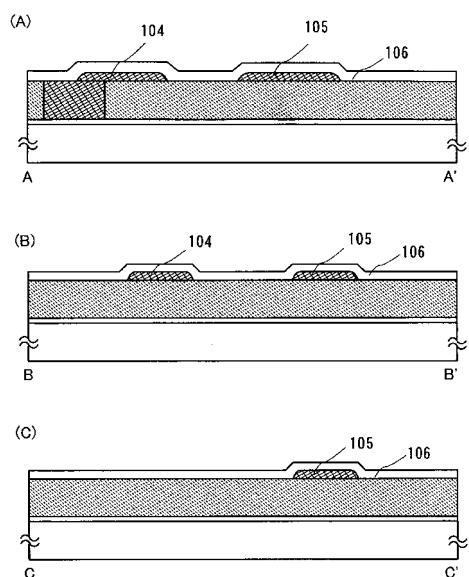

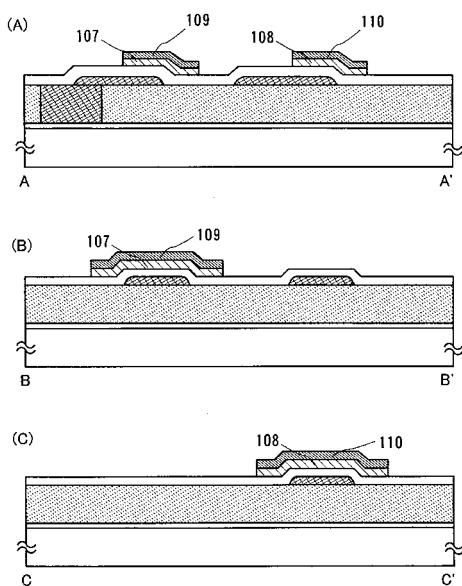

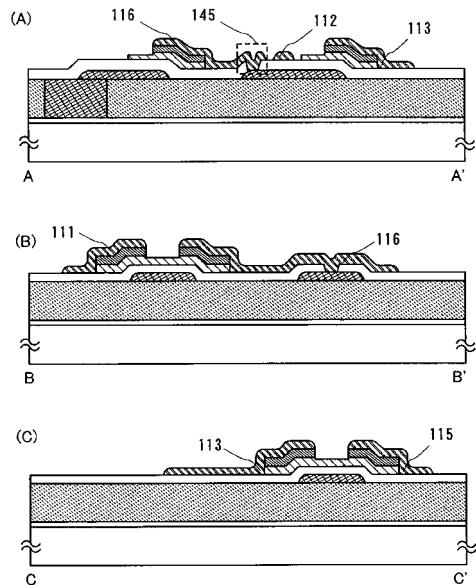

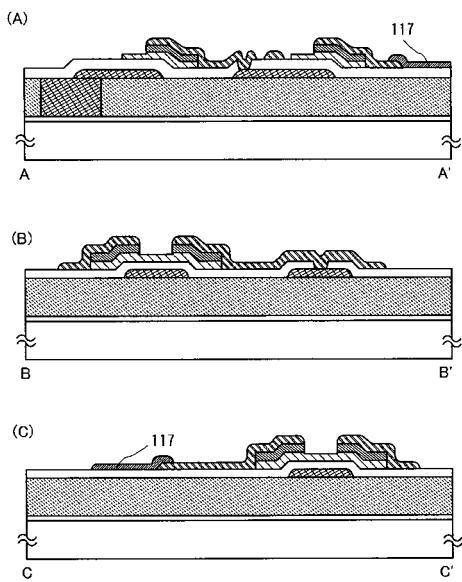

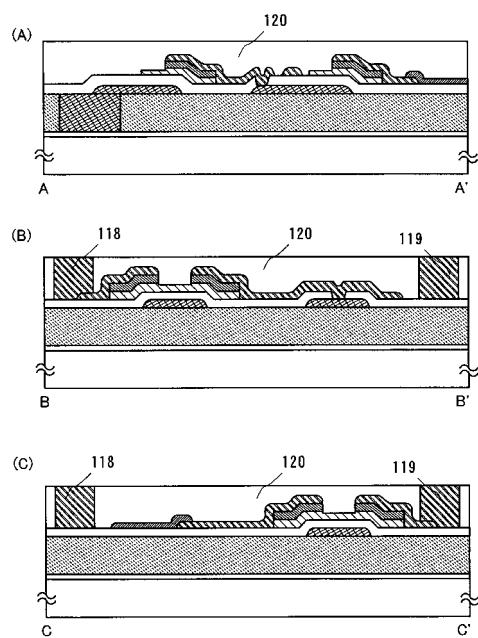

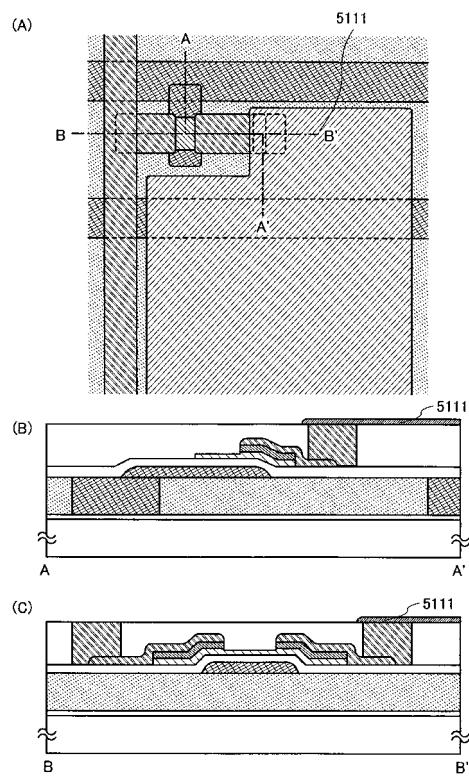

本発明の実施の形態について、図1～図7、図16～図23を用いて説明する。より詳しくは、本発明を適用した表示装置の作製方法について説明する。まず、本発明を適用した、チャネルエッチ型の薄膜トランジスタを有する表示装置の作製方法について説明する。図1～図7はそれぞれ図16～図22に対応しており、図1～図7は表示装置画素部の上面図であり、図16～図22の(A)は、図1～図7における線A-A'による断面図、(B)は線B-B'による断面図、(C)は線C-C'による断面図である。

#### 【0052】

基板100の上に、下地前処理として密着性を向上させる下地膜101を形成し、図1及び図16(A)、(B)及び(C)のように、絶縁層102a、102bを選択的に形成する。基板100は、バリウムホウケイ酸ガラス、アルミニウムホウケイ酸ガラス等からなるガラス基板、石英基板、シリコン基板、金属基板、ステンレス基板又は本作製工程の処理温度に耐えうる耐熱性を有するプラスチック基板を用いる。また、基板100の表面が平坦化されるようにCMP法などによって、研磨しても良い。なお、基板100上に、絶縁層を形成してもよい。絶縁層は、CVD法、プラズマCVD法、スピッタリング法、スピノコート法等の公知の方法により、珪素を含む酸化物材料、窒化物材料を用いて、単層又は積層して形成される。この絶縁層は、形成しなくても良いが、基板100からの汚染物質などを遮断する効果がある。ガラス基板よりの汚染を防ぐための絶縁層を形成する場合は、その上に液滴吐出法によって形成するゲート配線層103の下地前処理として下地膜101を形成する。

#### 【0053】

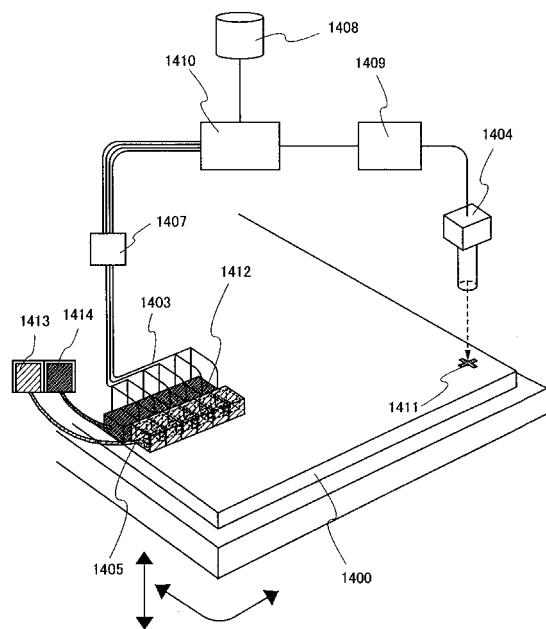

パターンの形成に用いる液滴吐出装置の一態様は図37に示されている。液滴吐出手段1403の個々のヘッド1405は制御手段1407に接続され、それがコンピュータ1410で制御することにより予めプログラミングされたパターンを描画することができる。描画するタイミングは、例えば、基板1400上に形成されたマーカー1411を基準に行えば良い。或いは、基板1400の縁を基準にして基準点を確定させても良い。これをCCDなどの撮像手段1404で検出し、画像処理手段1409にてデジタル信号に変換したものをコンピュータ1410で認識して制御信号を発生させて制御手段1407に送る。勿論、基板1400上に形成されるべきパターンの情報は記憶媒体1408に格納されたものであり、この情報を基にして制御手段1407に制御信号を送り、液滴吐出手段1403の個々のヘッド1405、1412を個別に制御することができる。吐出する材料は、材料供給源1413、材料供給源1414より配管を通してヘッド1405、ヘッド1412にそれぞれ供給される。

#### 【0054】

ヘッド1405と1412のノズルのサイズは異なっており、異なる材料を異なる幅

10

20

30

40

50

で同時に描画することができる。一つのヘッドで、導電材料や有機、無機材料などをそれぞれ吐出し、描画することができ、層間膜のような広領域に描画する場合は、スループットを向上させるため複数のノズルより同材料を同時に吐出し、描画することができる。大型基板を用いる場合、ヘッド 1405 は基板上を、矢印の方向に自在に走査し、描画する領域を自由に設定することができ、同じパターンを一枚の基板に複数描画することができる。

#### 【0055】

本実施の形態で下地前処理として形成する下地膜 101 は、ゾルゲル法のディップコーティング法、スピンドルコーティング法、液滴吐出法、イオンプレーティング法、イオンビーム法、CVD法、スパッタリング法、RFマグネットロンスパッタリング法、プラズマ溶射法、プラズマスプレー法、又は陽極酸化法により形成することができる。また下地膜を形成する物質は、その形成方法により膜としての連続性を有さなくても良い。ディップコーティング法、スピンドルコーティング法等の塗布法により形成する場合、溶媒を除去する必要があるとき、焼成したり、乾燥すればよい。

10

#### 【0056】

本実施の形態では、下地膜 101 として、スパッタリング法により所定の結晶構造を有する  $TiO_x$  (代表としては  $TiO_2$ ) 結晶を形成する場合を説明する。ターゲットには金属チタンチューブを用い、アルゴンガスと酸素を用いてスパッタリングを行う。更に He ガスを導入してもよい。成膜室又は処理物が設けられた基板を加熱しながら  $TiO_x$  を形成してもよい。

20

#### 【0057】

このように形成される  $TiO_x$  は非常に薄膜 (1 nm 程度) であってもよい。

#### 【0058】

また、スパッタリング法や蒸着法などの方法により、Ti (チタン)、W (タンゲステン)、Cr (クロム)、Ta (タンタル)、Ni (ニッケル)、Mo (モリブデン) などの金属材料若しくはその酸化物で形成される下地膜 101 を形成してもよい。

#### 【0059】

下地膜 101 は 0.01 ~ 10 nm の厚さで形成すれば良いが、極薄く形成すれば良いので、必ずしも層構造を持っていなくても良い。下地膜として、高融点金属材料や、3d 遷移元素を用いて、下地膜が導電性を有している場合、導電層形成領域以外の下地膜においては、下記の 2 つの方法を行うことが望ましい。

30

#### 【0060】

第 1 の方法としては、ゲート配線層 103 と重ならない下地膜 101 を絶縁化して、絶縁体層を形成する。つまり、ゲート配線層 103 と重ならない下地膜 101 を酸化して絶縁化する。このように、下地膜 101 を酸化して絶縁化する場合には、当該下地膜 101 を 0.01 ~ 10 nm の厚さで形成しておくことが好適であり、そうすると容易に酸化させることができる。なお、酸化する方法としては、酸素雰囲気下に晒す方法を用いてよいし、熱処理を行う方法を用いてよい。

#### 【0061】

第 2 の方法としては、ゲート配線層 103 の形成領域 (導電性材料を含む組成物と吐出領域) に選択的に形成する。下地膜 101 は、液滴吐出法などを用いるか、絶縁層 102a、102b をマスクとして用いるなどして、基板上に選択的に形成してもよいし、全面に形成した後、選択的に下地膜 101 をエッチングして除去してもよい。この工程を用いる場合には下地膜 101 の厚さに制約はない。

40

#### 【0062】

また、下地前処理の他の方法として、形成領域 (被形成面) に対してプラズマ処理を行う方法がある。プラズマ処理の条件は、空気、酸素又は窒素を処理ガスとして用い、圧力を数十 Torr ~ 1000 Torr (133000 Pa)、好ましくは 100 (13300 Pa) ~ 1000 Torr (133000 Pa)、より好ましくは 700 Torr (93100 Pa) ~ 800 Torr (106400 Pa)、つまり大気圧又は大気圧近傍の

50

圧力となる状態で、パルス電圧を印加する。このとき、プラズマ密度は、 $1 \times 10^{10} \sim 1 \times 10^{14} \text{ m}^{-3}$ 、所謂コロナ放電やグロー放電の状態となるようとする。空気、酸素又は窒素の処理ガスを用いプラズマ処理を用いることにより、材質依存性なく、表面改質を行うことができる。その結果、あらゆる材料に対して表面改質を行うことができる。

#### 【0063】

また、他の方法として、液滴吐出法によるパターンのその形成領域との密着性を上げるために、接着材として機能するような有機材料系の物質を形成してもよい。有機材料（有機樹脂材料）（ポリイミド、アクリル）やシリコン（Si）と酸素（O）との結合で骨格構造が構成され、置換基に少なくとも水素を含む材料、もしくは置換基にフッ素、アルキル基、または芳香族炭化水素のうち少なくとも1種を有する材料を用いてもよい。

#### 【0064】

絶縁層102a、102bを形成する。絶縁層102a、102bは、スピンドルコート法やディップ法により全面に絶縁層を形成した後、エッチング加工によって図1、図16に示すようにパターニングし、形成する。エッチングは、プラズマを利用したドライエッチングを用いても良いし、ウェットエッチングを用いてもよい。また、液滴吐出法により絶縁層102a、102bを形成すれば、エッチング加工は必ずしも必要ない。液滴吐出法を用いて、絶縁層など広領域に形成する場合、液滴吐出装置のノズル吐出口の径が大きなものを用いるか、複数のノズル吐出口から組成物を吐出し、複数の線が重なるように描画し形成すると、スループットが向上する。

#### 【0065】

絶縁層102a、102bは、酸化珪素、窒化珪素、酸化窒化珪素、酸化アルミニウム、窒化アルミニウム、酸化窒化アルミニウムその他の無機絶縁性材料、又はアクリル酸、メタクリル酸及びこれらの誘導体、又はポリイミド(polyimide)、芳香族ポリアミド、ポリベンゾイミダゾール(polybenzimidazole)などの耐熱性高分子、又はシロキサン系材料を出発材料として形成された珪素、酸素、水素からなる化合物のうちSi-O-Si結合を含む無機シロキサン、珪素上の水素がメチルやフェニルのような有機基によって置換された有機シロキサン系の絶縁材料で形成することができる。アクリル、ポリイミド等の感光性、非感光性の材料を用いて形成してもよい。感光性の材料を用いると、レジストによるマスクを用いることなくパターニングができる。本実施の形態では、感光性有機樹脂材料を用いる。

#### 【0066】

絶縁層102a、102bを形成した後、液滴吐出法によりゲート配線層103を、絶縁層102a、102b間に埋め込むように形成する（図2、図17参照。）。先に形成した絶縁層102a、102bを焼成した後でもよく、完全には焼成しない仮焼成でとどめておいて、ゲート配線層103を形成して同時に完全に焼成しても良い。本発明は、表示装置を構成する導電層のうち、画素間を跨ぎ、比較的太い線幅で形成されるゲート配線層や、容量配線層と、各画素内に比較的細線で形成されるゲート電極層、などの電極層を作り分ける。先にゲート配線層や容量配線層などの太い線幅を有する導電層を、絶縁層間に埋め込むように形成することにより、断線等がなく信頼性の高い、かつ低抵抗なゲート配線層、容量配線層を形成することができる。

#### 【0067】

図1、図2のように、絶縁層を先に選択的に形成し、その間に導電層を形成してもよいが、液滴吐出法を用いる場合、絶縁層を形成するための絶縁層有する組成物と、導電層を形成するための導電性材料を含む組成物を同時に吐出してもよい。同時に組成物を吐出することで、お互いがお互いの隔壁として機能するので、横に広がることなく、パターンが制御よく形成できる。その場合、それぞれの吐出口は、その形成する領域に応じて、選択すればよい。例えば、図2に示すように、絶縁層の方が導電層より広い領域形成する場合は、絶縁層を吐出するノズルの吐出口は、導電層を吐出するノズルの吐出口より大きなものを用いるとよい。また図12に示すように、絶縁層の形成領域が比較的広範囲な場合、まず、導電層を縁取るようにその周囲に同時に描画し、その後、残りの領域に絶縁層を吐

10

20

30

40

50

出して形成することができる。図12においては、ゲート配線層103を縁取るように絶縁層102a、102bの一部分が同時に形成される。次に、図13に示すように、絶縁層102bの残りの部分が液滴吐出法により形成される。図13における残りの部分の絶縁層は導電層のパターンより比較的広範囲なので、大きな径のノズルの吐出口を用いるとスループットを向上する事ができる。このように、所定の物質のパターンの構成によって、吐出口の大きさや、描画回数を設計することによって、スループットを向上することができる。

#### 【0068】

ゲート配線層103の形成は、液滴吐出手段を用いて行う。液滴吐出手段とは、組成物の吐出口を有するノズルや、1つ又は複数のノズルを具備したヘッド等の液滴を吐出する手段を有するものの総称とする。液滴吐出手段が具備するノズルの径は、0.02~100 $\mu\text{m}$  (好適には30 $\mu\text{m}$ 以下) に設定し、該ノズルから吐出される組成物の吐出量は0.001 $\text{p l}$ ~100 $\text{p l}$  (好適には0.1 $\text{p l}$ 以上40 $\text{p l}$ 以下、より好ましくは10 $\text{p l}$ 以下) に設定する。吐出量は、ノズルの径の大きさに比例して増加する。また、被処理物とノズルの吐出口との距離は、所望の箇所に滴下するために、出来る限り近づけておくことが好ましく、好適には0.1~3mm (好適には1mm以下) 程度に設定する。

#### 【0069】

吐出口から吐出する組成物は、導電性材料を溶媒に溶解又は分散させたものを用いる。導電性材料とは、Ag、Au、Cu、Ni、Pt、Pd、Ir、Rh、W、Al等の金属、Cd、Znの金属硫化物、Fe、Ti、Si、Ge、Si、Zr、Baなどの酸化物、ハロゲン化銀の微粒子又は分散性ナノ粒子に相当する。また、透明導電膜として用いられるインジウム錫酸化物(ITO)、インジウム錫酸化物と酸化珪素からなるITSO、有機インジウム、有機スズ、酸化亜鉛、窒化チタン等に相当する。但し、吐出口から吐出する組成物は、比抵抗値を考慮して、金、銀、銅のいずれかの材料を溶媒に溶解又は分散させたものを用いることが好適であり、より好適には、低抵抗な銀、銅を用いるとよい。但し、銀、銅を用いる場合には、不純物対策のため、合わせてバリア膜を設けるとよい。バリア膜としては、窒化珪素膜やニッケルボロン(NiB)を用いることができる。

#### 【0070】

また、導電性材料の周りに他の導電性材料がコーティングされ、複数の層になっている粒子でも良い。例えば、銅の周りにニッケルボロン(NiB)がコーティングされ、その周囲に銀がコーティングされている3層構造の粒子などを用いても良い。溶媒は、酢酸ブチル、酢酸エチル等のエステル類、イソプロピルアルコール、エチルアルコール等のアルコール類、メチルエチルケトン、アセトン等の有機溶剤等を用いる。組成物の粘度は20mPa·s以下が好適であり、これは、乾燥が起こることを防止したり、吐出口から組成物を円滑に吐出できるようにしたりするためである。また、組成物の表面張力は、40mN/m以下が好適である。但し、用いる溶媒や、用途に合わせて、組成物の粘度等は適宜調整するとよい。一例として、ITOや、有機インジウム、有機スズを溶媒に溶解又は分散させた組成物の粘度は5~20mPa·s、銀を溶媒に溶解又は分散させた組成物の粘度は5~20mPa·sに設定するとよい。

#### 【0071】

また、導電層は、複数の導電性材料を積層しても良い。また、始めに導電性材料として銀を用いて、液滴吐出法で導電層を形成した後、銅などでめっきを行ってもよい。めっきは電気めっきや化学(無電界)めっき法で行えばよい。めっきは、めっきの材料を有する溶液を満たした容器に基板表面を浸してもよいが、基板を斜め(または垂直)に立てて設置し、めっきする材料を有する溶液を、基板表面に流すように塗布してもよい。基板を立てて溶液を塗布するようにめっきを行うと、工程装置が小型化する利点がある。

#### 【0072】

各ノズルの径や所望のパターン形状などに依存するが、ノズルの目詰まり防止や高精細なパターンの作製のため、導電体の粒子の径はなるべく小さい方が好ましく、好適には粒

10

20

30

40

50

径 0 . 1  $\mu\text{m}$  以下が好ましい。組成物は、電解法、アトマイズ法又は湿式還元法等の公知の方法で形成されるものであり、その粒子サイズは、一般的に約 0 . 0 1 ~ 1 0  $\mu\text{m}$  である。但し、ガス中蒸発法で形成すると、分散剤で保護されたナノ粒子は約 7 nm と微細であり、またこのナノ粒子は、被覆剤を用いて各粒子の表面を覆うと、溶剤中に凝集がなく、室温で安定に分散し、液体とほぼ同じ挙動を示す。従って、被覆剤を用いることが好ましい。

#### 【 0 0 7 3 】

組成物を吐出する工程は、減圧下で行うと、組成物を吐出して被処理物に着弾するまでの間に、該組成物の溶媒が揮発し、後の乾燥と焼成の工程を省略することができる。また、減圧下で行うと、導電体の表面に酸化膜などが形成されないため好ましい。また、組成物を吐出後、乾燥と焼成の一方又は両方の工程を行う。乾燥と焼成の工程は、両工程とも加熱処理の工程であるが、例えば、乾燥は 1 0 0 度で 3 分間、焼成は 2 0 0 ~ 3 5 0 度で 1 5 分間 ~ 6 0 分間で行うもので、その目的、温度と時間が異なるものである。乾燥の工程、焼成の工程は、常圧下又は減圧下で、レーザ光の照射や瞬間熱アニール、加熱炉などにより行う。なお、この加熱処理を行うタイミングは特に限定されない。乾燥と焼成の工程を良好に行うためには、基板を加熱しておいてもよく、そのときの温度は、基板等の材質に依存するが、一般的には 1 0 0 ~ 8 0 0 度（好ましくは 2 0 0 ~ 3 5 0 度）とする。本工程により、組成物中の溶媒の揮発、又は化学的に分散剤を除去するとともに、周囲の樹脂が硬化収縮することで、ナノ粒子間を接触させ、融合と融着を加速する。

#### 【 0 0 7 4 】

レーザ光の照射は、連続発振またはパルス発振の気体レーザ又は固体レーザを用いれば良い。前者の気体レーザとしては、エキシマレーザ、YAGレーザ等が挙げられ、後者の固体レーザとしては、Cr、Nd等がドーピングされたYAG、YVO<sub>4</sub>等の結晶を使つたレーザ等が挙げられる。なお、レーザ光の吸収率の関係から、連続発振のレーザを用いることが好ましい。また、パルス発振と連続発振を組み合わせた所謂ハイブリッドのレーザ照射方法を用いてもよい。但し、基板 1 0 0 の耐熱性に依っては、レーザ光の照射による加熱処理は、該基板 1 0 0 が破壊しないように、数マイクロ秒から数十秒の間で瞬間的に行うとよい。瞬間熱アニール（RTA）は、不活性ガスの雰囲気下で、紫外光乃至赤外光を照射する赤外ランプやハロゲンランプなどを用いて、急激に温度を上昇させ、数分 ~ 数マイクロ秒の間で瞬間的に熱を加えて行う。この処理は瞬間的に行うために、実質的に最表面の薄膜のみを加熱することができ、下層の膜には影響を与えない。つまり、プラスチック基板等の耐熱性が弱い基板にも影響を与えない。

#### 【 0 0 7 5 】

液滴吐出法を用いて形成する導電層の下地前処理として、前述した下地膜 1 0 1 を形成する工程を行ったが、この処理工程は、ゲート配線層 1 0 3 を形成した後にも行っても良い。

#### 【 0 0 7 6 】

また、液滴吐出法により、絶縁層 1 0 2 a、1 0 2 b、ゲート配線層 1 0 3 を組成物を吐出し形成した後、その平坦性を高めるために表面を圧力によってプレスして平坦化してもよい。プレスの方法としては、ローラー状のものを表面に走査することによって、凹凸をならすように軽減したり、平坦な板状な物で表面を垂直にプレスしてもよい。プレスする時に、加熱工程を行っても良い。また溶剤等によって表面を軟化、または融解させエアナイフで表面の凹凸部を除去しても良い。また、CMP法を用いて研磨しても良い。この工程は、液滴吐出法によって凹凸が生じる場合に、その表面の平坦化する場合適用することができる。

#### 【 0 0 7 7 】

次に、ゲート電極層 1 0 4、ゲート電極層 1 0 5 を形成する。ゲート電極層 1 0 4 はゲート配線層 1 0 3 に接して形成する（図 3 参照。）。ゲート電極層 1 0 4 は、ゲート配線層 1 0 3 を形成した後、液滴吐出法によって、吐出口の径が小さなノズルを用いて微細に形成することができる。ゲート配線層 1 0 3 上のゲート電極層 1 0 4 の接する領域に下地

10

20

30

40

50

前処理として、下地膜101を形成したときのような処理をしてもよい。もちろん、ゲート電極層105を形成する領域にも前述の下地前処理を行っても良い。本実施の形態では、密着性を向上するための処理として、紫外線照射処理を行う。紫外線照射処理後、ゲート電極層104を形成する。本発明によりゲート配線層の線幅は10~40μm、ゲート電極層の線幅は5~20μm、ゲート配線層の線幅がゲート電極層の線幅の約2倍となるような配線が形成できる。

#### 【0078】

また、ゲート配線層103とゲート電極層104、105を同時に形成しても良い。その場合、液滴吐出装置のヘッドに径の大きさが異なるノズルを設置し、一回の走査でゲート配線層103とゲート電極層104、105を同時に形成する。例えば、ゲート配線層103を形成する領域には、径の比較的大きな吐出口のノズルが、ゲート電極層104、105を形成する領域には、径の比較的小さな吐出口のノズルが設置されたヘッドを走査する。ゲート配線層103を形成する吐出口からは連続的に導電性材料を吐出し、ゲート電極層104、105を形成する吐出口からは、その形成領域にヘッドが走査された時に、導電性材料を吐出する。このようにしても、線幅の異なるパターンを形成することができ、スループットを向上することができる。

#### 【0079】

次に、ゲート電極層104、105の上にゲート絶縁層106を形成する（図3、図18参照。）。ゲート絶縁層106としては、珪素の酸化物材料又は窒化物材料等の公知の材料で形成すればよく、積層でも単層でもよい。本実施の形態では、窒化珪素膜、酸化珪素膜、窒化珪素膜3層の積層を用いる。またそれらや、酸化窒化珪素膜の単層、2層からなる積層でも良い。好適には、緻密な膜質を有する窒化珪素膜を用いるとよい。また、液滴吐出法で形成される導電層に銀や銅などを用いる場合、その上にバリア膜として窒化珪素膜やNiB膜を形成すると、不純物の拡散を防ぎ、表面を平坦化する効果がある。なお、低い成膜温度でゲートリーク電流に少ない緻密な絶縁膜を形成するには、アルゴンなどの希ガス元素を反応ガスに含ませ、形成される絶縁膜中に混入させると良い。

#### 【0080】

次に半導体層を形成する。一導電性型を有する半導体層は必要に応じて形成すればよい。本実施の形態では、半導体層107、108と一導電型を有する半導体層としてN型半導体層109、110を積層する（図4、図19参照。）。またN型半導体層を形成し、Nチャネル型TFTのNMOS構造、P型半導体層を形成したPチャネル型TFTのPMOS構造、Nチャネル型TFTとPチャネル型TFTとのCMOS構造を作製することができる。また、導電性を付与するために、導電性を付与する元素をドーピングによって添加し、不純物領域を半導体層に形成することで、Nチャネル型TFT、Pチャネル型TFTを形成することもできる。

#### 【0081】

半導体層は公知の手段（スパッタ法、LPCVD法、またはプラズマCVD法等）により成膜すればよい。半導体層の材料に限定はないが、好ましくはシリコン又はシリコンゲルマニウム（SiGe）合金などで形成すると良い。

#### 【0082】

半導体層は、アモルファス半導体（代表的には水素化アモルファスシリコン）、結晶性半導体（代表的にはポリシリコン）を素材として用いている。ポリシリコンには、800以上のプロセス温度を経て形成される多結晶シリコンを主材料として用いた所謂高温ポリシリコンや、600以下のプロセス温度で形成される多結晶シリコンを主材料として用いた所謂低温ポリシリコン、また結晶化を促進する元素などを添加し結晶化させた結晶シリコンなどを含んでいる。

#### 【0083】

また、他の物質として、セミアモルファス半導体又は半導体層の一部に結晶相を含む半導体を用いることもできる。セミアモルファス半導体とは、非晶質と結晶構造（単結晶、多結晶を含む）の中間的な構造の半導体であり、自由エネルギー的に安定な第3の状態を

10

20

30

40

50

有する半導体であって、短距離秩序を持ち格子歪みを有する結晶質なものである。典型的にはシリコンを主成分として含み、格子歪みを伴って、ラマンスペクトルが  $520\text{ cm}^{-1}$  よりも低波数側にシフトしている半導体層である。また、未結合手（ダングリングボンド）の中和剤として水素またはハロゲンを少なくとも 1 原子%またはそれ以上含ませている。ここでは、このような半導体をセミアモルファス半導体（以下「S A S」とも呼ぶ。）と呼ぶ。この S A S は所謂微結晶（マイクロクリスタル）半導体（代表的には微結晶シリコン）とも呼ばれている。

#### 【0084】

この S A S は珪化物気体をグロー放電分解（プラズマ C V D）することにより得ることができる。代表的な珪化物気体としては、 $\text{SiH}_4$  であり、その他にも  $\text{Si}_2\text{H}_6$ 、 $\text{SiH}_2\text{Cl}_2$ 、 $\text{SiHCl}_3$ 、 $\text{SiCl}_4$ 、 $\text{SiF}_4$ などを用いることができる。また、 $\text{GeF}_4$ 、 $\text{F}_2$  を混合してもよい。この珪化物気体を水素、若しくは水素とヘリウム、アルゴン、クリプトン、ネオンから選ばれた一種又は複数種の希ガス元素で希釈して用いることで S A S の形成を容易なものとすることができます。珪化物気体に対する水素の希釈率は、例えば流量比で 2 倍～1000 倍とすることが好ましい。勿論、グロー放電分解による S A S の形成は、減圧下で行うことが好ましいが、大気圧における放電を利用して形成することができる。代表的には、 $0.1\text{ Pa} \sim 133\text{ Pa}$  の圧力範囲で行えば良い。グロー放電を形成するための電源周波数は  $1\text{ MHz} \sim 120\text{ MHz}$ 、好ましくは  $13\text{ MHz} \sim 60\text{ MHz}$  である。高周波電力は適宜設定すれば良い。基板加熱温度は 300 以下が好ましく、100～200 の基板加熱温度でも形成可能である。ここで、主に成膜時に取り込まれる不純物元素として、酸素、窒素、炭素などの大気成分に由来する不純物は  $1 \times 10^{20}\text{ cm}^{-3}$  以下とすることが望ましく、特に、酸素濃度は  $5 \times 10^{19}\text{ atoms/cm}^3$  以下、好ましくは  $1 \times 10^{19}\text{ atoms/cm}^3$  以下となるようにすることが好ましい。また、ヘリウム、アルゴン、クリプトン、ネオンなどの希ガス元素を含ませて格子歪みをさらに助長させることで安定性が増し良好な S A S が得られる。また半導体層としてフッ素系ガスより形成される S A S 層に水素系ガスより形成される S A S 層を積層してもよい。

#### 【0085】

半導体層に、結晶性半導体層を用いる場合、その結晶性半導体層の作製方法は、公知の方法（レーザー結晶化法、熱結晶化法、またはニッケルなどの結晶化を助長する元素を用いた熱結晶化法等）を用いれば良い。結晶化を助長する元素を導入しない場合は、非晶質珪素膜にレーザ光を照射する前に、窒素雰囲気下 500 で 1 時間加熱することによって非晶質珪素膜の含有水素濃度を  $1 \times 10^{20}\text{ atoms/cm}^3$  以下にまで放出させる。これは水素を多く含んだ非晶質珪素膜にレーザ光を照射すると膜が破壊されてしまうからである。

#### 【0086】

非晶質半導体層への金属元素の導入の仕方としては、当該金属元素を非晶質半導体層の表面又はその内部に存在させ得る手法であれば特に限定はなく、例えばスパッタ法、C V D 法、プラズマ処理法（プラズマ C V D 法も含む）、吸着法、金属塩の溶液を塗布する方法を使用することができる。このうち溶液を用いる方法は簡便であり、金属元素の濃度調整が容易であるという点で有用である。また、このとき非晶質半導体層の表面の濡れ性を改善し、非晶質半導体層の表面全体に水溶液を行き渡らせるため、酸素雰囲気中の U V 光の照射、熱酸化法、ヒドロキシラジカルを含むオゾン水又は過酸化水素による処理等により、酸化膜を成膜することが望ましい。

#### 【0087】

非晶質半導体層の結晶化は、熱処理とレーザ光照射による結晶化を組み合わせてもよく、熱処理やレーザ光照射を単独で、複数回行っても良い。

#### 【0088】

また、結晶性半導体層を、直接基板に線状プラズマ法により形成しても良い。また、線状プラズマ法を用いて、結晶性半導体層を選択的に基板に形成してもよい。

#### 【0089】

10

20

30

40

50

半導体として、有機材料を用いる有機半導体を用いてもよい。有機半導体としては、低分子材料、高分子材料などが用いられ、有機色素、導電性高分子材料などの材料も用いることが出来る。

【0090】

本実施の形態では、半導体として、非晶質半導体を用いる。半導体層を形成し、その後、プラズマCVD法等により一導電型を有する半導体層としてN型半導体層を形成する。

【0091】

続いて、レジストやポリイミド等の絶縁体からなるをマスクを用いて、半導体層、N型半導体層を同時にパターン加工し、半導体層107、108、N型半導体層109、110を形成する（図4、図19参照。）。マスクは組成物を選択的に吐出して形成することができる。マスクは、エポキシ樹脂、アクリル樹脂、フェノール樹脂、ノボラック樹脂、メラミン樹脂、ウレタン樹脂等の樹脂材料を用いる。また、ベンゾシクロブテン、パリレン、フレア、透過性を有するポリイミドなどの有機材料、シロキサン系ポリマー等の重合によってできた化合物材料、水溶性ホモポリマーと水溶性共重合体を含む組成物材料等を用いて液滴吐出法で形成する。或いは、感光剤を含む市販のレジスト材料を用いてもよく、例えば、代表的なポジ型レジストである、ノボラック樹脂と感光剤であるナフトキノンジアジド化合物、ネガ型レジストであるベース樹脂、ジフェニルシランジオール及び酸発生剤などを用いてもよい。いずれの材料を用いるとしても、その表面張力と粘度は、溶媒の濃度を調整したり、界面活性剤等を加えたりして適宜調整する。

【0092】

再び、レジストやポリイミド等の絶縁体からなるマスクを液滴吐出法を用いて形成し。そのマスクを用いて、エッティング加工によりゲート絶縁層106の一部に貫通孔145を形成して、その下層側に配置されているゲート電極層105の一部を露出させる。エッティング加工はプラズマエッティング（ドライエッティング）又はウェットエッティングのどちらを採用しても良いが、大面積基板を処理するにはプラズマエッティングが適している。エッティングガスとしては、 $CF_4$ 、 $NF_3$ 、 $Cl_2$ 、 $BCl_3$ 、などのフッ素系又は塩素系のガスを用い、HeやArなどの不活性ガスを適宜加えても良い。また、大気圧放電のエッティング加工を適用すれば、局所的な放電加工も可能であり、基板の全面にマスク層を形成する必要はない。

【0093】

マスクを除去した後、導電性材料を含む組成物を吐出して、ソース及びドレイン電極層111、113、115、116、導電層112を形成し、ソース及びドレイン電極層111、113、115、116をマスクとして、N型半導体層をパターン加工する（図5、図20参照。）。なお、図示しないが、ソース及びドレイン電極層111、113、115、116、導電層112を形成する前に、ソース及びドレイン電極層111、113、115、116、導電層112が形成する領域に選択的に $TiO_x$ 膜などを形成する、前述の下地前処理工程を行っても良い。そうすると、導電層は密着性よく形成できる。

【0094】

また、液滴吐出法を用いて形成する導電層の下地前処理として、前述した下地膜を形成する工程を行い、かつ、この処理工程は、導電層を形成した後にも行っても良い。この工程により、層間の密着性が向上するため、表示装置の信頼性も向上することができる。

【0095】

ゲート絶縁層106に形成した貫通孔145において、ソース及びドレイン電極層116とゲート電極層105とを電気的に接続させる。導電層112は容量素子を形成する。このソース及びドレイン電極層111、113、115、116、導電層112を形成する導電性材料としては、Ag（銀）、Au（金）、Cu（銅）、W（タンゲステン）、Al（アルミニウム）等の金属の粒子を主成分とした組成物を用いることができる。また、透光性を有するインジウム錫酸化物（ITO）、インジウム錫酸化物と酸化珪素からなるITO、有機インジウム、有機スズ、酸化亜鉛、窒化チタンなどを組み合わせても良い。

10

20

30

40

50

## 【0096】

ゲート絶縁層106の一部に貫通孔145を形成する工程を、ソース及びドレイン電極層111、113、115、116、導電層112形成後に、ソース及びドレイン電極層111、113、115、116、導電層112をマスクとして用いて貫通孔145を形成してもよい。そして貫通孔145に導電層を形成しソース及びドレイン電極層116とゲート電極層105を電気的に接続する。この場合、工程が簡略化する利点がある。

## 【0097】

続いて、ゲート絶縁層106上に選択的に、導電性材料を含む組成物を吐出して、第1の電極層117を形成する(図6、図21参照。)。第1の電極層117は、基板100側から光を放射する場合、または両面放射型の表示パネルを作製する場合には、インジウム錫酸化物(ITO)、酸化珪素を含むインジウム錡酸化物(ITSO)、酸化亜鉛(ZnO)、酸化スズ(SnO<sub>2</sub>)などを含む組成物により所定のパターンを形成し、焼成によって形成しても良い。

## 【0098】

また、好ましくは、スパッタリング法によりインジウム錡酸化物(ITO)、酸化珪素を含むインジウム錡酸化物(ITSO)、酸化亜鉛(ZnO)などで形成する。より好ましくは、ITOに酸化珪素が2~10重量%含まれたターゲットを用いてスパッタリング法で酸化珪素を含む酸化インジウムスズを用いる。この他、酸化珪素を含み酸化インジウムに2~20%の酸化亜鉛(ZnO)を混合した酸化物導電性材料を用いても良い。スパッタリング法で第1の電極層117を形成した後は、液滴吐出法を用いてマスク層を形成しエッチングにより、所望のパターンに形成すれば良い。本実施の形態では、第1の電極層117は、透光性を有する導電性材料により液滴吐出法を用いて形成し、具体的には、インジウム錡酸化物、ITOと酸化珪素から構成されるITSOを用いて形成する。図示しないが、第1の電極層117を形成する領域にゲート配線層103を形成する時と同様に、TiO<sub>x</sub>膜を形成し、下地前処理を行ってもよい。下地前処理によって、密着性が向上し、所望なパターンに第1の電極層117を形成する事ができる。

## 【0099】

本実施の形態では、ゲート絶縁層は窒化珪素からなる窒化珪素膜、酸化窒化珪素膜(酸化珪素膜)、窒化珪素膜の3層の例を前述した。好ましい構成として、酸化珪素を含む酸化インジウムスズで形成される第1の電極層117は、ゲート絶縁層106に含まれる窒化珪素からなる絶縁層と密接して形成され、それにより電界発光層で発光した光が外部に放射される割合を高めることが出来るという効果がある。また、ゲート絶縁層はゲート配線層や、ゲート電極層と、第1の電極層の間に介在し、容量素子として機能することもできる。

## 【0100】

また、発光した光を基板100側とは反対側に放射させる構造とする場合、上面放射型の表示パネルを作製する場合には、Ag(銀)、Au(金)、Cu(銅)、W(タンゲステン)、Al(アルミニウム)等の金属の粒子を主成分とした組成物を用いることができる。他の方法としては、スパッタリング法により透明導電膜若しくは光反射性の導電膜を形成して、液滴吐出法によりマスクパターンを形成し、エッチング加工を組み合わせて第1の電極層117を形成しても良い。

## 【0101】

第1の電極層117は、その表面が平坦化されるように、CMP法、ポリビニルアルコール系の多孔質体で拭净し、研磨しても良い。またCMP法を用いた研磨後に、第1の電極層117の表面に紫外線照射、酸素プラズマ処理などを行ってもよい。

## 【0102】

次に、第2の絶縁層となる絶縁層120を選択的に形成し、その間を埋めるようにソース配線層118、電源線119を液滴吐出法によって形成する(図7、図22参照。)。絶縁層120は、ソース配線層118、電源線119形成領域の他に、第1の電極層117上に開口部を有するように形成してもよい。本実施の形態では、絶縁層120を全面に

10

20

30

40

50

形成し、レジスト等のマスクによって、エッチングしパターニングする。この絶縁層120とソース配線層118、電源線119とを形成する工程も、前述した絶縁層102a、102bと、ゲート配線層103とを形成したときと同様に形成することができる。よって、先に絶縁層120を選択的に形成し、ソース配線層118、電源線119を後に形成する事もできるし、同時に形成することもできる。ソース配線層118、電源線119はソース、ドレイン電極層111、115とそれぞれ接して形成するため、その形成領域に前述のように下地前処理を行っても良い。

#### 【0103】

ソース配線層118、電源線119を形成する導電性材料としては、Ag(銀)、Au(金)、Cu(銅)、W(タンゲステン)、Al(アルミニウム)等の金属の粒子を主成分とした組成物を用いることができる。また、透光性を有するインジウム錫酸化物(ITO)、インジウム錫酸化物と酸化珪素からなるITO、有機インジウム、有機スズ、酸化亜鉛、窒化チタンなどを組み合わせても良い。

#### 【0104】

絶縁層120は、酸化珪素、窒化珪素、酸化窒化珪素、酸化アルミニウム、窒化アルミニウム、酸化窒化アルミニウムその他の無機絶縁性材料、又はアクリル酸、メタクリル酸及びこれらの誘導体、又はポリイミド(polyimide)、芳香族ポリアミド、ポリベンゾイミダゾール(polybenzimidazole)などの耐熱性高分子、又はシロキサン系材料を出発材料として形成された珪素、酸素、水素からなる化合物のうちSi-O-Si結合を含む無機シロキサン、珪素上の水素がメチルやフェニルのような有機基によって置換された有機シロキサン系の絶縁材料で形成することができる。アクリル、ポリイミド等の感光性、非感光性の材料を用いて形成してもよい。

#### 【0105】

また、液滴吐出法により、絶縁層120、ソース配線層118、電源線119を組成物を吐出し形成した後、その平坦性を高めるために表面を圧力によってプレスして平坦化してもよい。プレスの方法としては、ローラー状のものを表面に走査することによって、凹凸をならすように軽減したり、平坦な板状な物で表面を垂直にプレスしてもよい。また溶剤等によって表面を軟化、または融解させエアナイフで表面の凹凸部を除去しても良い。また、CMP法を用いて研磨しても良い。この工程は、液滴吐出法によって凹凸が生じる場合に、その表面の平坦化する場合適用することができる。この工程により平坦性が向上すると、表示パネルの表示ムラなどを防止することができ、高繊細な画像を表示することができる。

#### 【0106】

以上の工程により、基板100上にボトムゲート型(逆スタガ型ともいう。)のTFTと画素電極として機能する第1の電極層が接続された表示パネル用のTFTを有する基板100が完成する。また本実施の形態のTFTはチャネルエッチ型である。

#### 【0107】

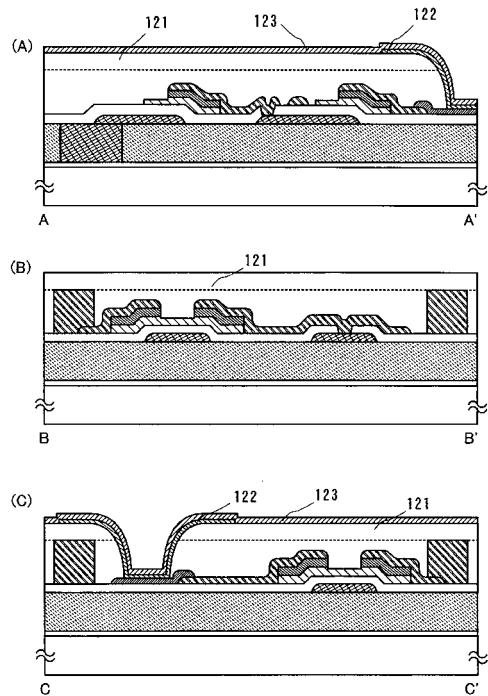

表示パネル用のTFTを有する基板100の上に、発光素子を形成する(図23参照)。ソース配線層118、電源線119を形成した後、絶縁層121を形成する。絶縁層121は絶縁層120と同様な材料で形成することができる。絶縁層121は、絶縁層120とともに、隔壁(土手ともよばれる)となる。

#### 【0108】

電界発光層122を形成する前に、大気圧中で200の熱処理を行い絶縁層120、121中若しくはその表面に吸着している水分を除去する。また、減圧下で200~400、好ましくは250~350に熱処理を行い、そのまま大気に晒さずに電界発光層122を真空蒸着法や、減圧下の液滴吐出法で形成することが好ましい。

#### 【0109】

電界発光層122として、赤色(R)、緑色(G)、青色(B)の発光を示す材料を、それぞれ蒸着マスクを用いた蒸着法等によって選択的に形成する。赤色(R)、緑色(G)、青色(B)の発光を示す材料はカラーフィルタ同様、液滴吐出法により形成すること

10

20

30

40

50

もでき（低分子または高分子材料など）、この場合マスクを用いずとも、RGBの塗り分けを行うことができるため好ましい。電界発光層122上に第2の電極層123を積層形成して、発光素子を用いた表示機能を有する表示装置（発光表示装置）が完成する（図23参照。）。

【0110】

図示しないが、第2の電極層123を覆うようにしてパッシベーション膜を設けることは有効である。パッシベーション膜としては、窒化珪素（SiN）、酸化珪素（SiO<sub>2</sub>）、酸化窒化珪素（SiON）、窒化酸化珪素（SiNO）、窒化アルミニウム（AlN）、酸化窒化アルミニウム（AlON）、窒素含有量が酸素含有量よりも多い窒化酸化アルミニウム（AlNO）または酸化アルミニウム、ダイアモンドライクカーボン（DLC）、窒素含有炭素膜（CN<sub>x</sub>）を含む絶縁膜からなり、該絶縁膜を単層もしくは組み合わせた積層を用いることができる。例えば窒素含有炭素膜（CN<sub>x</sub>）と窒化珪素（SiN）との積層、また有機材料を用いることも出来、スチレンポリマーなど高分子の積層でもよい。また、シリコン（Si）と酸素（O）との結合で骨格構造が構成され、置換基に少なくとも水素を含む材料、もしくは置換基にフッ素、アルキル基、または芳香族炭化水素のうち少なくとも1種を有する材料を用いてもよい。

【0111】

この際、カバーレッジの良い膜をパッシベーション膜として用いることが好ましく、炭素膜、特にDLC膜を用いることは有効である。DLC膜は室温から100以下の温度範囲で成膜可能であるため、耐熱性の低い電界発光層の上方にも容易に成膜することができる。DLC膜は、プラズマCVD法（代表的には、RFプラズマCVD法、マイクロ波CVD法、電子サイクロトロン共鳴（ECR）CVD法、熱フィラメントCVD法など）、燃焼炎法、スパッタ法、イオンビーム蒸着法、レーザー蒸着法などで形成することができる。成膜に用いる反応ガスは、水素ガスと、炭化水素系のガス（例えばCH<sub>4</sub>、C<sub>2</sub>H<sub>2</sub>、C<sub>6</sub>H<sub>6</sub>など）とを用い、グロー放電によりイオン化し、負の自己バイアスがかかったカソードにイオンを加速衝突させて成膜する。また、CN<sub>x</sub>膜は反応ガスとしてC<sub>2</sub>H<sub>4</sub>ガスとN<sub>2</sub>ガスとを用いて形成すればよい。DLC膜は酸素に対するプロッキング効果が高く、電界発光層の酸化を抑制することができる。そのため、この後に続く封止工程を行う間に電界発光層が酸化するといった問題を防止できる。

【0112】

続いて、シール材を形成し、封止基板を用いて封止する。その後、ゲート配線層103にフレキシブル配線基板を接続し、外部との電気的な接続をしても良い。これは、ソース配線層118も同様である。

【0113】

なお、本実施の形態では、ガラス基板で発光素子を封止した場合を示すが、封止の処理とは、発光素子を水分から保護するための処理であり、カバー材で機械的に封入する方法、熱硬化性樹脂又は紫外光硬化性樹脂で封入する方法、金属酸化物や窒化物等のバリア能力が高い薄膜により封止する方法のいずれかを用いる。カバー材としては、ガラス、セラミックス、プラスチックもしくは金属を用いることができるが、カバー材側に光を放射させる場合は透光性でなければならない。また、カバー材と上記発光素子が形成された基板とは熱硬化性樹脂又は紫外光硬化性樹脂等のシール材を用いて貼り合わせられ、熱処理又は紫外光照射処理によって樹脂を硬化させて密閉空間を形成する。この密閉空間の中に酸化バリウムに代表される吸湿材を設けることも有効である。この吸湿材は、シール材の上に接して設けても良いし、発光素子からの光を妨げないような、隔壁の上や周辺部に設けても良い。さらに、カバー材と発光素子の形成された基板との空間を熱硬化性樹脂若しくは紫外光硬化性樹脂で充填することも可能である。この場合、熱硬化性樹脂若しくは紫外光硬化性樹脂の中に酸化バリウムに代表される吸湿材を添加しておくことは有効である。

【0114】

本実施の形態では、スイッチング TFT はシングルゲート構造を示したが、ダブルゲート構造などのマルチゲート構造でもよい。図14にダブルゲート構造のスイッチング TFT

10

20

30

40

50

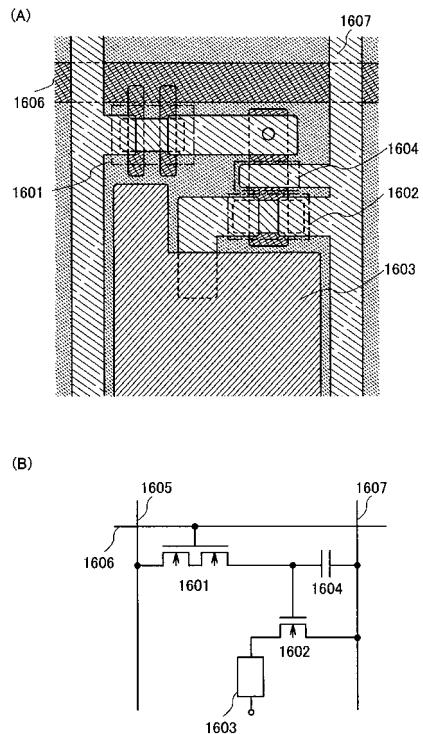

TとしてTFT1601を有する表示装置画素部の上面図を(A)に、回路図を(B)に示す。1601はTFT、1602はTFT、1603は発光素子、1604は容量、1605はソース配線層、1606はゲート配線層、1607は電源線である。TFT1601は信号線との接続状態を制御するトランジスタ(以下「スイッチング用トランジスタ」又は「スイッチング用TFT」ともいう。)であり、TFT1602は発光素子へ流れる電流を制御するトランジスタ(以下「駆動用トランジスタ」又は「駆動用TFT」ともいう。)であり、駆動用TFTが発光素子と直列に接続されている。容量1604はTFT1602のソース、ゲート間の電圧を保持する。

## 【0115】

以上示したように、本実施の形態では、フォトマスクを利用した光露光工程を用いないことにより、工程を省略することができる。また、液滴吐出法を用いて基板上に直接的に各種のパターンを形成することにより、1辺が1000mmを超える第5世代以降のガラス基板を用いても、容易にEL表示パネルを製造することができる。

## 【0116】

また、密着性が向上した信頼性の高いEL表示パネルを作製することができる。

## 【0117】

## (実施の形態2)

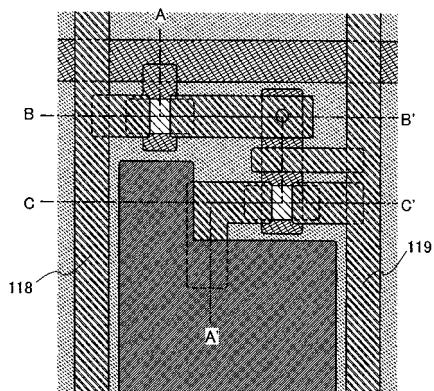

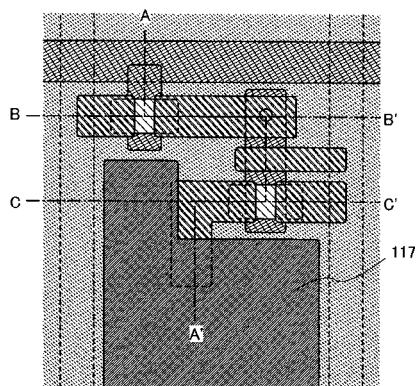

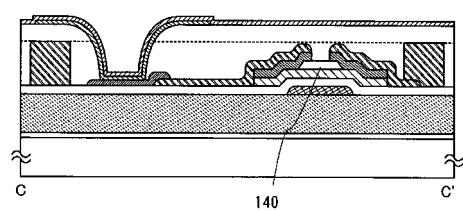

本発明の実施の形態として、図8を用いて説明する。本実施の形態は、実施の形態1において、薄膜トランジスタとしてチャネル保護型の薄膜トランジスタを用いるものである。よって、同一部分又は同様な機能を有する部分の繰り返しの説明は省略する。なお、図8は、図23の(C)のチャネルエッチ型の薄膜トランジスタとの断面図と対応している。

## 【0118】

基板100上に、絶縁層102bを形成し、導電性材料を含む組成物を液滴吐出法により吐出して、ゲート配線層103を形成する。ゲート配線層と接するようにゲート電極層105を、液滴吐出法により形成する。次に、プラズマCVD法やスパッタリング法を用いて、ゲート絶縁層106を単層又は積層構造で形成する。特に好ましい形態としては、窒化珪素からなる絶縁体層、酸化珪素からなる絶縁体層、窒化珪素からなる絶縁体層の3層の積層体がゲート絶縁層に相当する。さらに、活性層として機能する半導体層108まで形成する。以上の工程は第1の実施の形態と同様である。

## 【0119】

半導体層108を形成し、チャネル保護膜140を形成するため、例えば、プラズマCVD法により絶縁膜を形成し、所望の領域に、所望の形状となるようにパターニングする。このとき、ゲート電極をマスクとして基板の裏面から露光することにより、チャネル保護膜140を形成することができる。またチャネル保護膜140は、液滴吐出法を用いてポリイミド又はポリビニルアルコール等を滴下してもよい。その結果、露光工程を省略することができる。

## 【0120】

チャネル保護膜140としては、無機材料(酸化珪素、窒化珪素、酸化窒化珪素、窒化酸化珪素など)、感光性または非感光性の有機材料(有機樹脂材料)(ポリイミド、アクリル、ポリアミド、ポリイミドアミド、レジスト、ベンゾシクロブテンなど)、低誘電率であるLOW-k材料などの一種、もしくは複数種からなる膜、またはこれらの膜の積層などを用いることができる。また、シリコン(Si)と酸素(O)との結合で骨格構造が構成され、置換基に少なくとも水素を含む材料、もしくは置換基にフッ素、アルキル基、または芳香族炭化水素のうち少なくとも1種を有する材料を用いてもよい。作製法としては、プラズマCVD法や熱CVD法などの気相成長法やスパッタリング法を用いることができる。また、液滴吐出法や、印刷法(スクリーン印刷やオフセット印刷などパターンが形成される方法)を用いることもできる。塗布法で得られるTOF膜やSOG膜なども用いることができる。

## 【0121】

10

20

30

40

50

半導体層 108、チャネル保護膜 140 上に、N型半導体層 110 を形成する。次に、半導体層 108、N型半導体層 110 上に、組成物を選択的に吐出してマスクを形成する。続いて、マスクを利用して、半導体層 108 と N型半導体層 110 を同時にエッティングして、半導体層と N型半導体層を形成する。その後、半導体層 108 上に、導電性材料を含む組成物を吐出して、ソース及びドレイン電極層 113、115 を形成する。

【0122】

次に、ソース又はドレイン電極層 113、115 をマスクとして、N型半導体層 110 をエッティングする。次にソース又はドレイン電極層 113 に接して導電性材料を含む組成物を吐出して、第 1 の電極層 117 を形成する。続いて、絶縁層 120 を選択的に形成し、絶縁層 120 の開口部を埋めるようにソース配線層 118、電源線 119 を液滴吐出法により形成する。実施の形態 1 と同様に、絶縁層 120、ソース配線層 118、電源線 119 は同時に形成しても良く、その形成前と後に、前述の下地前処理を行っても良い。この後、プレス工程を行い、表面を平坦化しても良い。

10

【0123】

図 9 は、図 8 における EL 表示パネルと、第 1 の電極層 117 とソース及びドレイン電極層 113 との接続構造が異なる例である。図 9 においては、第 1 の電極層 117 をソース又はドレイン電極層 113 より先に形成し、後にソース又はドレイン電極層 113 を第 1 の電極層 117 と接するように形成する。

【0124】

その後、絶縁層 121 を形成し、第 1 の電極層 117 上に開口部を設けたのち、電界発光層 122、第 2 の電極層 123 を形成する。さらに、シール材を形成し、封止基板を用いて封止する。その後、ゲート配線層 103 にフレキシブル配線基板を接続しても良い。以上によって、表示機能を有する EL 表示パネルを作製することができる。

20

【0125】

以上、実施の形態 1、及び実施の形態 2 において逆スタガ型の薄膜トランジスタの例を示したが、本発明は、順スタガ型の薄膜トランジスタにも適用できる。順スタガ型の薄膜トランジスタの場合、ソース配線層がまず絶縁層中に埋め込むように形成され、液滴吐出法によって微細な画素部内のソース及びドレイン電極層がそのソース配線層に接して形成される。これにより、ソース配線層の低抵抗化と、電極層の微細化の両方が、逆スタガ型の薄膜トランジスタと同様、達成できる。

30

【0126】

(実施の形態 3)

本実施の形態は、実施の形態 1 で作成したチャネルエッチ型の薄膜トランジスタと、第 1 の電極層との接続構造が異なるものであり、図 15 を用いて説明する。

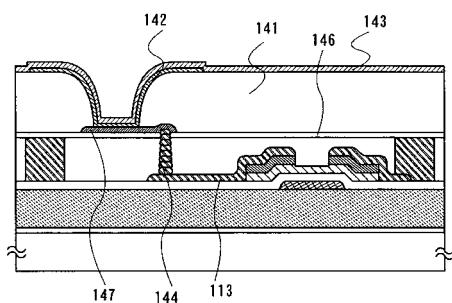

【0127】

ソース及びドレイン電極層 113 まで形成するのは実施の形態 1 と同一である。次にピラーとして機能する柱状の導電層 144 を形成する。本実施の形態では液滴吐出法を用いて導電層を積層して柱状の導電層 144 を形成する。柱状の導電層 144 は絶縁層 120 を形成する前に形成しても、後に形成してもよいが、絶縁層 120 を先に形成する場合、液滴吐出法により選択的に形成することによって、層間絶縁膜の形成と同時に柱状の導電層 144 が形成されるコンタクトホールの形成が可能となる。

40

【0128】

また、他の方法として、上層配線と下層配線の導通をとる箇所において、下層配線に、絶縁層 120 と撥液性を有する材料を液滴吐出法により吐出する。この撥液性を有する材料の撥液性により、絶縁層 120 は撥液性を有する材料が形成された領域には形成されない。よって、絶縁層 120 に開口部（コンタクトホール）が形成される。よってこの開口部に導電性材料を吐出し、柱状の導電層 144 を形成することもできる。絶縁層 120 上に絶縁層 146 を形成する。このとき、柱状の導電層 144 は絶縁層 146 に覆われてしまっていたら、エッティングし、柱状の導電層 144 を露出させる。絶縁層 146 はプラズマ CVD により窒化珪素膜などを用いるとよい。

50

## 【0129】

柱状の導電層 144 と接するように第 1 の電極層 147 を形成し、隔壁となる絶縁層 141 を形成する。第 1 の電極層 147 上に電界発光層 142 を形成し、第 2 の電極層 143 を形成する。さらに、シール材を形成し、封止基板を用いて封止する。その後、ゲート配線層にフレキシブル配線基板を接続しても良い。以上によって、表示機能を有する EL 表示パネルを作製することができる。

## 【0130】

## (実施の形態 4)

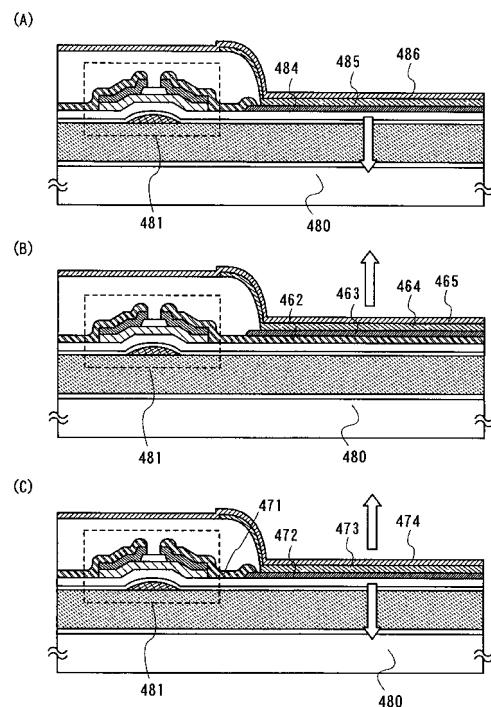

本発明を適用して薄膜トランジスタを形成し、該薄膜トランジスタを用いて表示装置(発光表示装置)を形成することができるが、発光素子を用いて、なおかつ、該発光素子を駆動するトランジスタとしてN型トランジスタを用いた場合、該発光素子から発せられる光は、下面放射、上面放射、両面放射のいずれかを行う。ここでは、いずれの場合に応じた発光素子の積層構造について、図10を用いて説明する。

10

## 【0131】

また、本実施の形態では、本発明を適用し、本実施の形態2で形成されるチャネル保護型の薄膜トランジスタであるトランジスタ481を用いる。

## 【0132】

まず、光が基板480側に放射する場合、つまり下面放射を行う場合について、図10(A)を用いて説明する。この場合、トランジスタ481に電気的に接続するように、ソース・ドレイン配線482、483、第1の電極484、電界発光層485、第2の電極486が順に積層される。次に、光が基板480と反対側に放射する場合、つまり上面放射を行う場合について、図10(B)を用いて説明する。トランジスタ481に電気的に接続するソース・ドレイン配線461、462、第1の電極463、電界発光層464、第2の電極465が順に積層される。上記構成により、第1の電極463において光が透過しても、該光は配線462において反射され、基板480と反対側に放射する。なお、本構成では、第1の電極463には透光性を有する材料を用いる必要はない。最後に、光が基板480側とその反対側の両側に放射する場合、つまり両面放射を行う場合について、図10(C)を用いて説明する。トランジスタ481に電気的に接続するソース・ドレイン配線470、471、第1の電極472、電界発光層473、第2の電極474が順に積層される。このとき、第1の電極472と第2の電極474のどちらも透光性を有する材料、又は光を透過できる厚さで形成すると、両面放射が実現する。

20

## 【0133】

発光素子は、電界発光層を第1の電極と第2の電極で挟んだ構成になっている。第1の電極及び第2の電極は仕事関数を考慮して材料を選択する必要があり、そして第1の電極及び第2の電極は、画素構成によりいずれも陽極、又は陰極となりうる。本実施の形態では、駆動用 TFT の極性がNチャネル型であるため、第1の電極を陰極、第2の電極を陽極とすると好ましい。また駆動用 TFT の極性がpチャネル型である場合、第1の電極を陽極、第2の電極を陰極とするとよい。

30

## 【0134】

また第1の電極が陽極であった場合、電界発光層は、第1の電極側から、HIL(ホール注入層)、HTL(ホール輸送層)、EML(発光層)、ETL(電子輸送層)、EIL(電子注入層)の順に積層するのが好ましい。また、第1の電極が陰極である場合はその逆にのとなり、第1の電極側からEIL(電子注入層)、ETL(電子輸送層)、EML(発光層)、HTL(ホール輸送層)、HIL(ホール注入層)、第2の電極である陽極の順に積層するのが好ましい。なお電界発光層は、積層構造以外に単層構造、又は混合構造をとることがある。

40

## 【0135】

また、電界発光層として、赤色(R)、緑色(G)、青色(B)の発光を示す材料を、それぞれ蒸着マスクを用いた蒸着法等によって選択的に形成する。赤色(R)、緑色(G)、青色(B)の発光を示す材料はカラーフィルタ同様、液滴吐出法により形成すること

50

もでき（低分子または高分子材料など）、この場合マスクを用いずとも、RGBの塗り分けを行うことができるため好ましい。

【0136】

具体的には、HILとしてCuPcやPEDOT、HTLとして-NPD、ETLとしてBCPやAlq<sub>3</sub>、EILとしてBCP:LiやCaF<sub>2</sub>、をそれぞれ用いる。また上面放射型の場合で、第2の電極に透光性を有するITOやITSOを用いる場合、ベンゾオキサゾール誘導体（BzOS）にLiを添加したBzOS-Liなどを用いることができる。また例えばEMLは、R、G、Bのそれぞれの発光色に対応したドーパント（Rの場合DCM等、Gの場合DMQD等）をドープしたAlq<sub>3</sub>を用いればよい。

【0137】

なお、電界発光層は上記材料に限定されない。例えば、CuPcやPEDOTの代わりに酸化モリブデン（MoO<sub>x</sub>:x=2~3）等の酸化物と-NPDやルブレンを共蒸着して形成し、ホール注入性を向上させることもできる。また電界発光層の材料は、有機材料（低分子又は高分子を含む）、又は有機材料と無機材料の複合材料として用いることができる。

【0138】

また、図10には図示していないが、基板480の対向基板にカラーフィルタを形成してもよい。カラーフィルタは液滴吐出法によって形成することができ、その場合、前述の下地前処理として光プラズマ処理などを適用することができる。本発明の下地膜により、所望なパターンに密着性よくカラーフィルタを形成することができる。カラーフィルターを用いると、高精細な表示を行うこともできる。カラーフィルターにより、各RGBの発光スペクトルにおいてプロードなピークを鋭くなるように補正できるからである。

【0139】

以上、各RGBの発光を示す材料を形成する場合を説明したが、単色の発光を示す材料を形成し、カラーフィルターや色変換層を組み合わせることによりフルカラー表示を行うことができる。例えば、白色又は橙色の発光を示す電界発光層を形成する場合、カラーフィルター、色変換層、又はカラーフィルターと色変換層とを組み合わせたものを別途設けることによってフルカラー表示ができる。カラーフィルターや色変換層は、例えば第2の基板（封止基板）に形成し、基板へ張り合わせればよい。また上述したように、単色の発光を示す材料、カラーフィルター、及び色変換層のいずれも液滴吐出法により形成することができる。

【0140】

もちろん単色発光の表示を行ってもよい。例えば、単色発光を用いてエリアカラータイプの表示装置を形成してもよい。エリアカラータイプは、パッシブマトリクス型の表示部が適しており、主に文字や記号を表示することができる。

【0141】

上記構成において、陰極としては、仕事関数が小さい材料を用いることが可能で、例えば、Ca、Al、CaF、MgAg、AlLi等が望ましい。電界発光層は、単層型、積層型、また層の界面がない混合型のいずれでもよく、またシングレット材料、トリプレット材料、又はそれらを組み合わせた材料や、低分子材料、高分子材料及び中分子材料を含む有機材料、電子注入性に優れる酸化モリブデン等に代表される無機材料、有機材料と無機材料の複合材料のいずれを用いてもよい。第1の電極484、472は光を透過する透明導電膜を用いて形成し、例えばITO、ITSOの他、酸化インジウムに2~20%の酸化亜鉛（ZnO）を混合した透明導電膜を用いる。なお、第1の電極484、463、472形成前に、酸素雰囲気中でのプラズマ処理や真空雰囲気下での加熱処理を行うとい。隔壁（土手ともいう）は、珪素を含む材料、有機材料及び化合物材料を用いて形成する。また、多孔質膜を用いても良い。但し、アクリル、ポリイミド等の感光性、非感光性の材料を用いて形成すると、その側面は曲率半径が連続的に変化する形状となり、上層の薄膜が段切れせずに形成されるため好ましい。本実施の形態は、上記の実施の形態と自由に組み合わせることが可能である。

## 【0142】

## (実施の形態5)

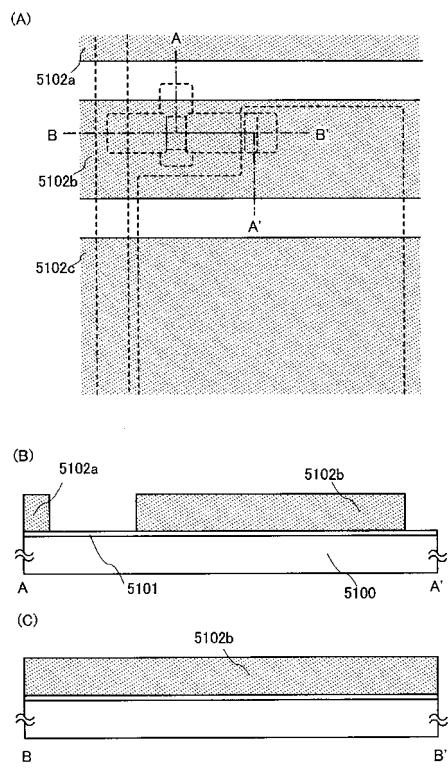

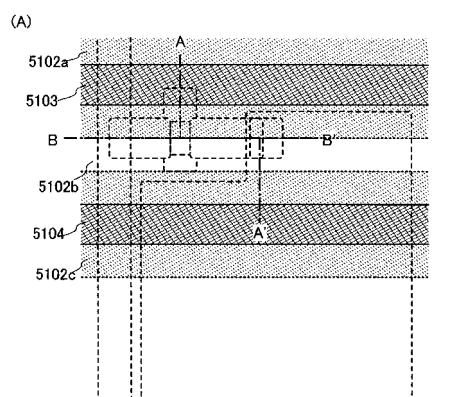

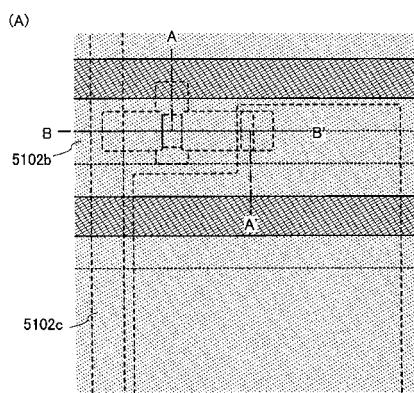

本発明の実施の形態について、図40～図46を用いて説明する。より詳しくは、本発明を適用した液晶表示装置の作製方法について説明する。まず、本発明を適用した、チャネル保護型の薄膜トランジスタを有する液晶表示装置の作製方法について説明する。また図40～図46において、(A)は液晶表示装置画素部の上面図であり、(B)は(A)における線A-A'による断面図、(C)は線B-B'による断面図である。

## 【0143】

基板5100の上に、下地前処理として密着性を向上させる下地膜5101を形成し、図40(A)、(B)及び(C)のように、絶縁層5102a、5102b、5102cを選択的に形成する。基板5100は、バリウムホウケイ酸ガラス、アルミニノホウケイ酸ガラス等からなるガラス基板、石英基板、シリコン基板、金属基板、ステンレス基板又は本作製工程の処理温度に耐えうる耐熱性を有するプラスチック基板を用いる。また、基板5100の表面が平坦化されるようにCMP法などによって、研磨しても良い。なお、基板5100上に、絶縁層を形成してもよい。絶縁層は、CVD法、プラズマCVD法、スパッタリング法、スピンドル法等の公知の方法により、珪素を含む酸化物材料、窒化物材料を用いて、単層又は積層して形成される。この絶縁層は、形成しなくても良いが、基板5100からの汚染物質などを遮断する効果がある。ガラス基板よりの汚染を防ぐための絶縁層を形成する場合は、その上に液滴吐出法によって形成する導電層の下地前処理として下地膜5101を形成する。

## 【0144】

本実施の形態で下地前処理として形成する下地膜5101は、ゾルゲル法のディップコーティング法、スピンドル法、液滴吐出法、イオンプレーティング法、イオンビーム法、CVD法、スパッタリング法、RFマグネットロンスパッタリング法、プラズマ溶射法、プラズマスプレー法、又は陽極酸化法により形成することができる。また物質は、その形成方法により膜としての連続性を有さなくても良い。ディップコーティング法、スピンドル法等の塗布法により形成する場合、溶媒を除去する必要があるとき、焼成したり、乾燥すればよい。

## 【0145】

本実施の形態では、下地膜5101として、スパッタリング法により所定の結晶構造を有するTiO<sub>x</sub>(代表としてはTiO<sub>2</sub>)結晶を形成する場合を説明する。ターゲットには金属チタンチューブを用い、アルゴンガスと酸素を用いてスパッタリングを行う。更にHeガスを導入してもよい。成膜室又は処理物が設けられた基板を加熱しながらTiO<sub>x</sub>を形成してもよい。

## 【0146】

また、スパッタリング法や蒸着法などの方法により、Ti(チタン)、W(タンゲステン)、Cr(クロム)、Ta(タンタル)、Ni(ニッケル)、Mo(モリブデン)などの金属材料若しくはその酸化物で形成される下地膜5101を形成してもよい。

## 【0147】

下地膜5101は0.01～10nmの厚さで形成すれば良いが、極薄く形成すれば良いので、必ずしも層構造を持っていなくても良い。下地膜として、高融点金属材料や、3d遷移元素を用いて、下地膜が導電性を有している場合、導電層形成領域以外の下地膜においては、下記の2つの方法を行うことが望ましい。

## 【0148】

第1の方法としては、ゲート配線層5103、容量配線層5104と重ならない下地膜5101を絶縁化して、絶縁体層を形成する。つまり、ゲート配線層5103、容量配線層5104と重ならない下地膜5101を酸化して絶縁化する。このように、下地膜5101を酸化して絶縁化する場合には、当該下地膜5101を0.01～10nmの厚さで形成しておくことが好適であり、そうすると容易に酸化させることができる。なお、酸化する方法としては、酸素雰囲気下に晒す方法を用いてもよいし、熱処理を行う方法を用い

10

20

30

40

50

てもよい。

【0149】

第2の方法としては、ゲート配線層5103、容量配線層5104の形成領域（導電性材料を含む組成物と吐出領域）に選択的に形成する。下地膜5101は、液滴吐出法などを用いるか、絶縁層5102a、5102b、5102cをマスクとして用いるかなどして、基板上に選択的に形成してもよいし、全面に形成した後、選択的に下地膜5101をエッティングして除去してもよい。この工程を用いる場合には下地膜5101の厚さに制約はない。

【0150】

また、下地前処理の他の方法として、形成領域（被形成面）に対してプラズマ処理を行う方法がある。プラズマ処理の条件は、空気、酸素又は窒素を処理ガスとして用い、圧力を数十Torr~1000Torr(133000Pa)、好ましくは100(13300Pa)~1000Torr(133000Pa)、より好ましくは700Torr(93100Pa)~800Torr(106400Pa)、つまり大気圧又は大気圧近傍の圧力となる状態で、パルス電圧を印加する。このとき、プラズマ密度は、 $1 \times 10^{10} \sim 1 \times 10^{14} \text{ m}^{-3}$ 、所謂コロナ放電やグロー放電の状態となるようにする。空気、酸素又は窒素の処理ガスを用いプラズマ処理を用いることにより、材質依存性なく、表面改質を行うことができる。その結果、あらゆる材料に対して表面改質を行うことができる。

【0151】

また、他の方法として、液滴吐出法によるパターンのその形成領域との密着性を上げるために、接着材として機能するような有機材料系の物質を形成してもよい。有機材料（有機樹脂材料）（ポリイミド、アクリル）やシリコン（Si）と酸素（O）との結合で骨格構造が構成され、置換基に少なくとも水素を含む材料、もしくは置換基にフッ素、アルキル基、または芳香族炭化水素のうち少なくとも1種を有する材料を用いてもよい。

【0152】

絶縁層5102a、5102b、5102cを形成する。絶縁層5102a、5102b、5102cは、スピンドルコート法やディップ法により全面に絶縁層を形成した後、エッティング加工によって図40に示すようにパターニングし、形成する。エッティングは、プラズマCVD法などのドライエッティングを用いても良いし、ウェットエッティングを用いてもよい。また、液滴吐出法により絶縁層5102a、5102b、5102cを形成すれば、エッティング加工は必ずしも必要ない。液滴吐出法を用いて、絶縁層など広領域に形成する場合、液滴吐出装置のノズル吐出口の径が大きなものを用いるか、複数のノズル吐出口から組成物を吐出し、複数の線が重なるように描画し形成すると、スループットが向上する。

【0153】

絶縁層5102a、5102b、5102cは、酸化珪素、窒化珪素、酸化窒化珪素、酸化アルミニウム、窒化アルミニウム、酸化窒化アルミニウムその他の無機絶縁性材料、又はアクリル酸、メタクリル酸及びこれらの誘導体、又はポリイミド(polyimide)、芳香族ポリアミド、ポリベンゾイミダゾール(polybenzimidazole)などの耐熱性高分子、又はシロキサン系材料を出発材料として形成された珪素、酸素、水素からなる化合物のうちSi-O-Si結合を含む無機シロキサン、珪素上の水素がメチルやフェニルのような有機基によって置換された有機シロキサン系の絶縁材料で形成することができる。アクリル、ポリイミド等の感光性、非感光性の材料を用いて形成してもよい。感光性の材料を用いると、レジストによるマスクを用いることなくパターニングができる。本実施の形態では、感光性有機樹脂材料を用いる。

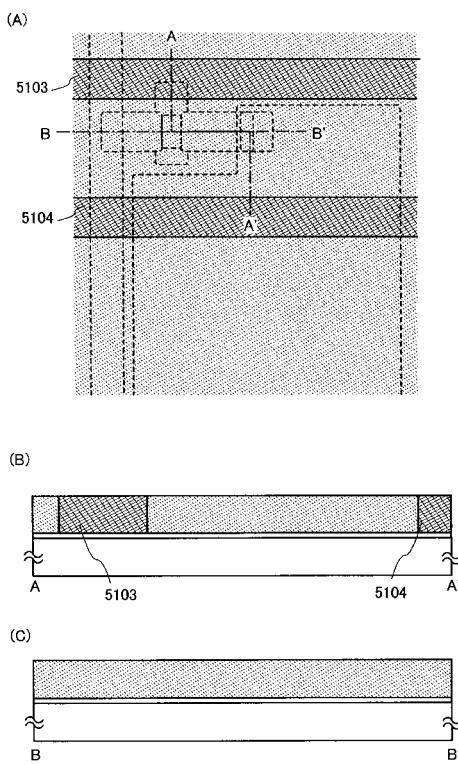

【0154】

絶縁層5102a、5102b、5102cを形成した後、液滴吐出法によりゲート配線層5103と容量配線層5104を、絶縁層5102a、5102b、5102c間を埋め込むように形成する。先に形成した絶縁層5102a、5102b、5102cを焼成した後でもよく、完全には焼成しない仮焼成でとどめておいて、ゲート配線層5103

10

20

30

40

50

、容量配線層 5104 を形成して同時に完全に焼成しても良い。本発明は、表示装置を構成する導電層のうち、画素間を跨ぎ、比較的太い線幅で形成されるゲート配線層や、容量配線層と、各画素内に比較的細線で形成されるゲート電極層、などの電極層を作り分ける。先にゲート配線層や容量配線層などの太い線幅を有する導電層を、絶縁層間に埋め込むように形成することにより、断線等がなく信頼性の高い、かつ低抵抗なゲート配線層、容量配線層を形成することができる。

【0155】

図40、図41のように、絶縁層を先に選択的に形成し、その間に導電層を形成してもよいが、液滴吐出法を用いる場合、絶縁層を形成するための絶縁層有する組成物と、導電層を形成するための導電性材料を含む組成物を同時に吐出してもよい。同時に組成物を吐出することで、お互いがお互いの隔壁として機能するので、横に広がることなく、パターンが制御よく形成できる。その場合、それぞれの吐出口は、その形成する領域に応じて、選択すればよい。例えば、図41に示すように、絶縁層の方が導電層より広い領域形成する場合は、絶縁層を吐出するノズルの吐出口は、導電層を吐出するノズルの吐出口より大きなものを用いるとよい。また図50に示すように、絶縁層の形成領域が比較的広範囲な場合、まず、導電層を縁取るようにその周囲に同時に描画し、その後、残りの領域に絶縁層を吐出して形成することができる。図50においては、ゲート配線層5103、容量配線層5104を縁取るように絶縁層5102a、5102b、5102cの一部分が同時に形成される。次に、図51に示すように、絶縁層5102b、5102cの残りの部分が液滴吐出法により形成される。図51における残りの部分の絶縁層は導電層のパターンより比較的広範囲なので、大きな径のノズルの吐出口を用いるとスループットを向上することができる。このように、所定の物質のパターンの構成によって、吐出口の大きさや、描画回数を設計することによって、スループットを向上することができる。

10

20

【0156】

このゲート配線層5103、容量配線層5104の形成は、液滴吐出手段を用いて行う。

【0157】

液滴吐出法を用いて形成する導電層の下地前処理として、前述した下地膜5101を形成する工程を行ったが、この処理工程は、ゲート配線層5103、容量配線層5104を形成した後にも行っても良い。

30

【0158】

また、液滴吐出法により、絶縁層5102a、5102b、5102c、ゲート配線層5103、及び容量配線層5104を組成物を吐出し形成した後、その平坦性を高めるために表面を圧力によってプレスして平坦化してもよい。プレスの方法としては、ローラー状のものを表面に走査することによって、凹凸をならすように軽減したり、平坦な板状な物で表面を垂直にプレスしてもよい。プレスする時に、加熱工程を行っても良い。また溶剤等によって表面を軟化、または融解させ、エアナイフで表面の凹凸部を除去しても良い。また、CMP法を用いて研磨しても良い。この工程は、液滴吐出法によって凹凸が生じる場合に、その表面の平坦化する場合適用することができる。

40

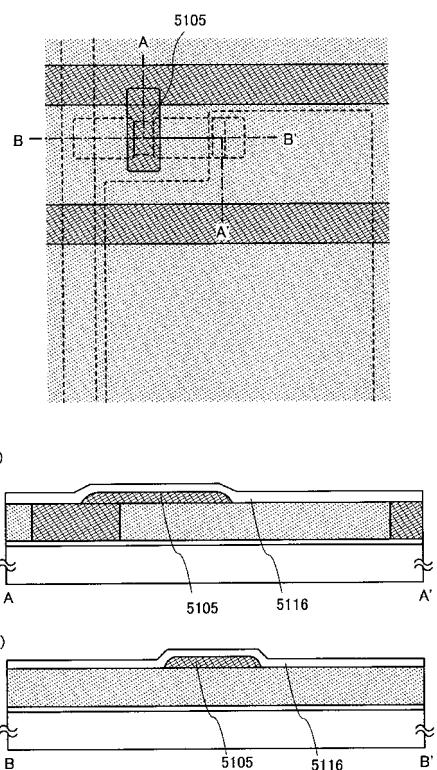

【0159】

次に、ゲート電極層5105をゲート配線層5103に接して形成する（図42参照）。ゲート電極層5105は、ゲート配線層5103を形成した後、液滴吐出法によって、吐出口の径が小さなノズルを用いて微細に形成することができる。ゲート配線層5103上のゲート電極層5105の接する領域に下地前処理として、下地膜5101を形成したときのような処理をしてもよい。本実施の形態では、密着性を向上するための処理として、紫外線照射処理を行う。紫外線照射処理後、ゲート電極層5105を形成する。本発明によりゲート配線の線幅は10～40μm、ゲート電極の線幅は5～20μm、ゲート配線の線幅がゲート電極の線幅の約2倍となるような配線が形成できる。

【0160】

また、ゲート配線層5103とゲート電極層5105を同時に形成しても良い。その場

50

合、液滴吐出装置のヘッドに径の大きさが異なるノズルを設置し、一回の走査でゲート配線層 5103 とゲート電極層 5105 を同時に形成する。例えば、ゲート配線層 5103 を形成する領域には、径の比較的大きな吐出口のノズルが、ゲート電極層 5105 を形成する領域には、径の比較的小さな吐出口のノズルが設置されたヘッドを走査する。ゲート配線層 5103 を形成する吐出口からは連続的に導電性材料を吐出し、ゲート電極層 5105 を形成する吐出口からは、その形成領域にヘッドが走査された時に、導電性材料を吐出する。このようにしても、線幅の異なるパターンを形成することができ、スループットを向上することができる。

#### 【0161】

次に、ゲート電極層 5105 の上にゲート絶縁層 5116 を形成する（図 42 参照。）10。ゲート絶縁層 5116 としては、珪素の酸化物材料又は窒化物材料等の公知の材料で形成すればよく、積層でも单層でもよい。本実施の形態では、窒化珪素膜、酸化珪素膜、窒化珪素膜 3 層の積層を用いる。またそれらや、酸化窒化珪素膜の单層、2 層からなる積層でも良い。好適には、緻密な膜質を有する窒化珪素膜を用いるとよい。また、液滴吐出法で形成される導電層に銀や銅などを用いる場合、その上にバリア膜として窒化珪素膜や NiB 膜を形成すると、不純物の拡散を防ぎ、表面を平坦化する効果がある。なお、低い成膜温度でゲートリーケ電流が少ない緻密な絶縁膜を形成するには、アルゴンなどの希ガス元素を反応ガスに含ませ、形成される絶縁膜中に混入させると良い。

#### 【0162】

次に半導体層を形成する。一導電性型を有する半導体層は必要に応じて形成すればよい。本実施の形態では、半導体層 5106 と一導電型を有する半導体層として N 型半導体層 5107 を積層する（図 43 参照。）。また N 型半導体層を形成し、N チャネル型 TFT の NMOS 構造、P 型半導体層を形成した P チャネル型 TFT の PMOS 構造、N チャネル型 TFT と P チャネル型 TFT との CMOS 構造を作製することができる。また、導電性を付与するために、導電性を付与する元素をドーピングによって添加し、不純物領域を半導体層に形成することで、N チャネル型 TFT、P チャネル型 TFT を形成することもできる。

#### 【0163】

本実施の形態では、半導体として、非晶質半導体を用いる。半導体層を形成し、その後、プラズマ CVD 法等により一導電型を有する半導体層として N 型半導体層を形成する。30

#### 【0164】

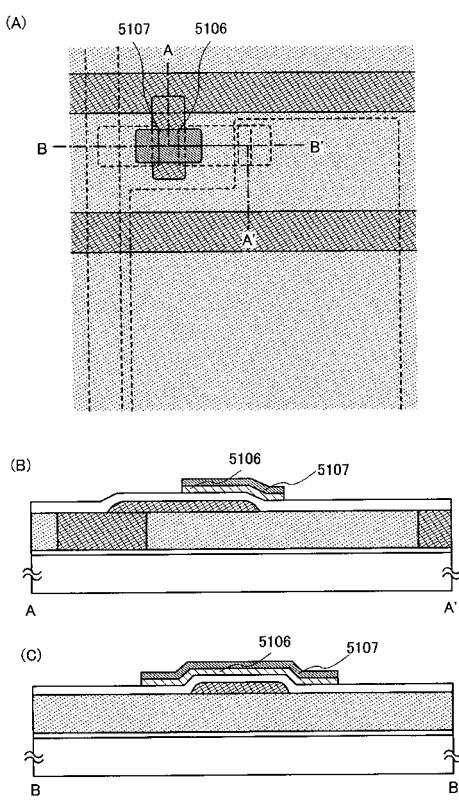

続いて、レジストやポリイミド等の絶縁体からなるをマスクを用いて、半導体層 5106、N 型半導体層 5107 を同時にパターン加工し、半導体層 5106、N 型半導体層 5107 を形成する（図 43 参照。）。マスクは組成物を選択的に吐出して形成することができる。マスクは、エポキシ樹脂、アクリル樹脂、フェノール樹脂、ノボラック樹脂、メラミン樹脂、ウレタン樹脂等の樹脂材料を用いる。また、ベンゾシクロブテン、パリレン、フレア、透過性を有するポリイミドなどの有機材料、シロキサン系ポリマー等の重合によってできた化合物材料、水溶性ホモポリマーと水溶性共重合体を含む組成物材料等を用いて液滴吐出法で形成する。或いは、感光剤を含む市販のレジスト材料を用いてもよく、例えば、代表的なポジ型レジストである、ノボラック樹脂と感光剤であるナフトキノンジアジド化合物、ネガ型レジストであるベース樹脂、ジフェニルシランジオール及び酸発生剤などを用いてもよい。いずれの材料を用いるとしても、その表面張力と粘度は、溶媒の濃度を調整したり、界面活性剤等を加えたりして適宜調整する。

#### 【0165】

導電性材料を含む組成物を吐出して、ソース、ドレイン電極層 5130、5108 を形成し、該ソース、ドレイン電極層 5130、5108 をマスクとして、半導体層 5106 及び N 型半導体層 5107 をパターン加工して、半導体層を露出させる（図 44 参照。）。なお、図示しないが、ソース、ドレイン電極層を形成する前に、ソース、ドレイン電極層が形成する領域に選択的に TiO<sub>x</sub> 膜などを形成する、前述の下地前処理工程を行ってもよい。そうすると、導電層は密着性よく形成できる。この処理工程は、導電層を形成し4050

た後にも行っても良い。この工程により、層間の密着性が向上するため、表示装置の信頼性も向上することができる。

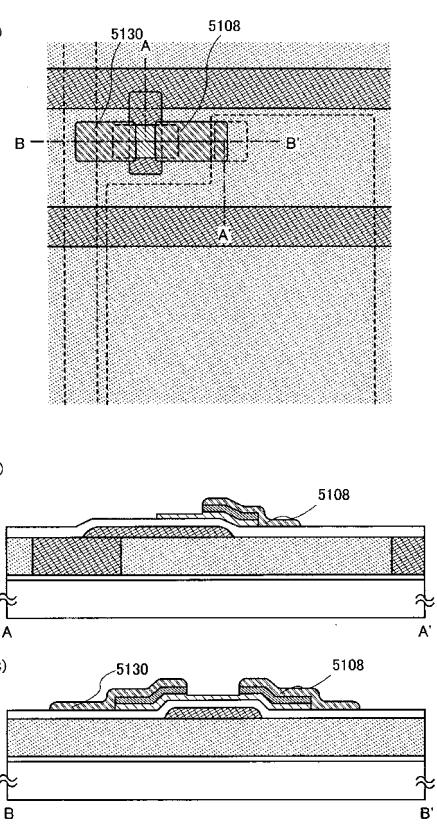

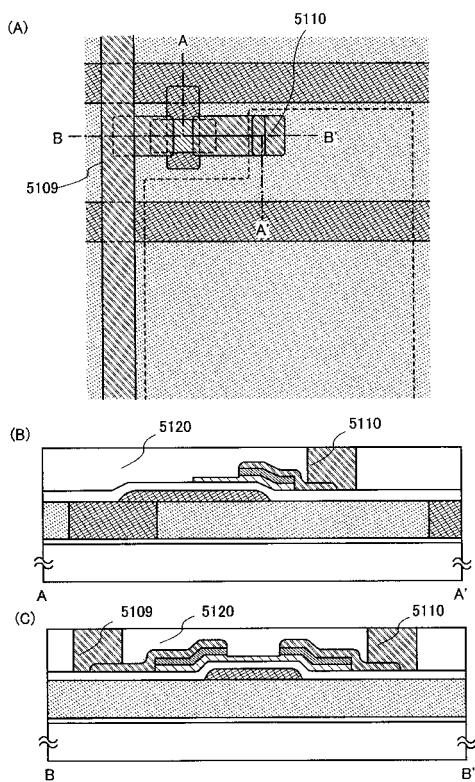

#### 【0166】

次に、第2の絶縁層となる絶縁層5120を選択的に形成し、その間を埋めるようにソース配線層5109、導電層5110を液滴吐出法によって形成する(図45参照。)。絶縁層5120は、ソース配線層5109形成領域の他に、ソース、ドレイン電極層5108と画素電極層5111とを接続するための導電層5110を形成するため、ソース、ドレイン電極層5108上に開口部を有するように形成される。この絶縁層5120とソース配線層5109、導電層5110とを形成する工程も、前述した絶縁層5102a、5102b、5102cと、ゲート配線層5103、容量配線層5104とを形成したときと同様に形成することができる。よって、先に絶縁層5120を選択的に形成し、ソース配線層5109、導電層5110を後に形成する事もできるし、同時に形成することもできる。ソース配線層5109、導電層5110はソース、ドレイン電極層5130、5108とそれぞれ接して形成するため、その形成領域に前述のように下地前処理を行っても良い。導電層5110はソース、ドレイン電極層5108と画素電極層5111とに接し、電気的に接続する機能を持つため、導電層5110の形成後にも下地前処理を行い、その上に画素電極層5111を形成することが好ましい。

#### 【0167】

ソース、ドレイン電極層5130、5108、ソース配線層5109、導電層5110を形成する導電性材料としては、Ag(銀)、Au(金)、Cu(銅)、W(タングステン)、Al(アルミニウム)等の金属の粒子を主成分とした組成物を用いることができる。また、透光性を有するインジウム錫酸化物(ITO)、インジウム錫酸化物と酸化珪素からなるITSO、有機インジウム、有機スズ、酸化亜鉛、窒化チタンなどを組み合わせても良い。

#### 【0168】

絶縁層5120は、酸化珪素、窒化珪素、酸化窒化珪素、酸化アルミニウム、窒化アルミニウム、酸化窒化アルミニウムその他の無機絶縁性材料、又はアクリル酸、メタクリル酸及びこれらの誘導体、又はポリイミド(polyimide)、芳香族ポリアミド、ポリベンゾイミダゾール(polybenzimidazole)などの耐熱性高分子、又はシロキサン系材料を出発材料として形成された珪素、酸素、水素からなる化合物のうちSi-O-Si結合を含む無機シロキサン、珪素上の水素がメチルやフェニルのような有機基によって置換された有機シロキサン系の絶縁材料で形成することができる。アクリル、ポリイミド等の感光性、非感光性の材料を用いて形成してもよい。

#### 【0169】

また、液滴吐出法により、絶縁層5120、ソース配線層5109、導電層5110を組成物を吐出し形成した後、その平坦性を高めるために表面を圧力によってプレスして平坦化してもよい。プレスの方法としては、ローラー状のものを表面に走査することによって、凹凸をならすように軽減したり、平坦な板状な物で表面を垂直にプレスしてもよい。また溶剤等によって表面を軟化、または融解させエアナイフで表面の凹凸部を除去しても良い。また、CMP法を用いて研磨しても良い。この工程は、液滴吐出法によって凹凸が生じる場合に、その表面の平坦化する場合適用することができる。この工程により平坦性が向上すると、表示パネルの表示ムラなどを防止することができ、高繊細な画像を表示することができる。

#### 【0170】

続いて、導電層5110と接するように、絶縁層5120上に選択的に、導電性材料を含む組成物を吐出して、画素電極層5111を形成する(図46参照。)。画素電極層5111は、透過型の液晶表示パネルを作製する場合には、インジウム錫酸化物(ITO)、酸化珪素を含むインジウム錡酸化物(ITSO)、酸化亜鉛(ZnO)、酸化スズ(SnO<sub>2</sub>)などを含む組成物により所定のパターンを形成し、焼成によって形成しても良い。

## 【0171】

また、好ましくは、スパッタリング法によりインジウム錫酸化物(ITO)、酸化珪素を含むインジウム錫酸化物(ITSO)、酸化亜鉛(ZnO)などで形成する。より好ましくは、ITOに酸化珪素が2~10重量%含まれたターゲットを用いてスパッタリング法で、酸化珪素を含む酸化インジウムスズ膜を形成する。この他、酸化珪素を含み酸化インジウムに2~20%の酸化亜鉛(ZnO)を混合した酸化物導電性材料を用いても良い。スパッタリング法で画素電極層5111を形成した後は、液滴吐出法を用いてマスク層を形成しエッ칭により、所望のパターンに形成すれば良い。本実施の形態では、画素電極層5111は、透光性を有する導電性材料により液滴吐出法を用いて形成し、具体的には、インジウム錫酸化物、ITOと酸化珪素から構成されるITSOを用いて形成する。

10

## 【0172】

また、反射型の液晶表示パネルを作製する場合には、Ag(銀)、Au(金)、Cu(銅)、W(タンゲステン)、Al(アルミニウム)等の金属の粒子を主成分とした組成物を用いることができる。他の方法としては、スパッタリング法により透明導電膜若しくは光反射性の導電膜を形成して、液滴吐出法によりマスクパターンを形成し、エッ칭加工を組み合わせて画素電極層5111を形成しても良い。

## 【0173】

画素電極層5111は、その表面が平坦化されるように、CMP法、ポリビニルアルコール系の多孔質体で拭淨し、研磨しても良い。またCMP法を用いた研磨後に、画素電極層5111の表面に紫外線照射、酸素プラズマ処理などを行ってもよい。

20

## 【0174】

以上の工程により、基板5100上にボトムゲート型(逆スタガ型ともいう。)のTFTと画素電極が接続された液晶表示パネル用のTFTを有する基板5100が完成する。また本実施の形態のTFTはチャネルエッチ型である。

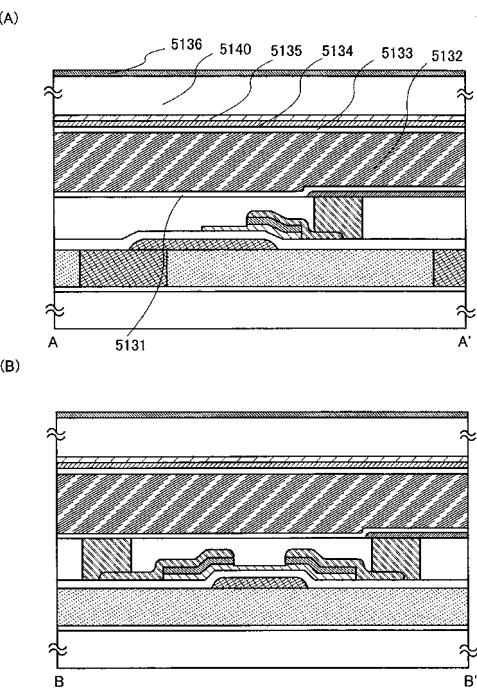

## 【0175】

次に、図48に示すように、画素電極層5111を覆うように、印刷法やスピンドルコート法により、配向膜と呼ばれる絶縁体層5131を形成する。図48の(A)は図40乃至46で示した上面図の線A-A'による断面図であり、図48(B)は、線B-B'による断面図であり、液晶表示パネルの完成図である。なお、絶縁体層5131は、スクリーン印刷法やオフセット印刷法を用いれば、選択的に形成することができる。その後、ラビングを行う。続いて、シール材を液滴吐出法により画素を形成した周辺の領域に形成する(図示せず。)。

30

## 【0176】

その後、配向膜として機能する絶縁体層5133、カラーフィルタとして機能する着色層5134、対向電極として機能する導電体層5135、偏光板5136が設けられた対向基板5140とTFTを有する基板5100とをスペーサを介して貼り合わせ、その隙間に液晶層5132を設けることにより液晶表示パネルを作製することができる(図48参照。)。シール材にはフィラーが混入されていても良く、さらに対向基板5140には、遮蔽膜(ブラックマトリクス)などが形成されていても良い。なお、液晶層5132を形成する方法として、ディスペンサ式(滴下式)や、対向基板5140を貼り合わせてから毛細管現象を用いて液晶を注入するディップ式(汲み上げ式)を用いることができる。

40

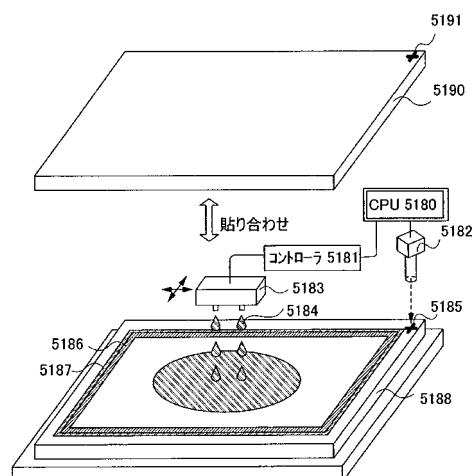

## 【0177】

ディスペンサ方式を採用した液晶滴下注入法を図52を用いて説明する。図52において、5180はCPU、5181はコントローラ、5182は撮像手段、5183はヘッド、5184は液晶、5185、5191はマーカー、5186はバリア層、5187はシール材、5188はTFT基板、5190は対向基板である。シール材5187で閉ループを形成し、その中にヘッド5183より液晶5184を1回若しくは複数回滴下する。そのとき、シール材5187と液晶5184とが反応することを防ぐため、バリア層5186を設ける。続いて、真空中で基板を貼り合わせ、その後紫外線硬化を行って、液晶

50

が充填された状態とする。

【0178】

以上の工程で形成された画素部と外部の配線基板を接続するために接続部を形成する。大気圧又は大気圧近傍下で、酸素ガスを用いたアッシング処理により、接続部の絶縁体層を除去する。この処理は、酸素ガスと、水素、 $\text{CF}_4$ 、 $\text{NF}_3$ 、 $\text{H}_2\text{O}$ 、 $\text{CHF}_3$ から選択された一つ又は複数とを用いて行う。本工程では、静電気による損傷や破壊を防止するために、対向基板を用いて封止した後に、アッシング処理を行っているが、静電気による影響が少ない場合には、どのタイミングで行っても構わない。

【0179】

続いて、異方性導電体層を介して、ゲート配線層5103が電気的に接続するように、接続用の配線基板を設ける。配線基板は、外部からの信号や電位を伝達する役目を担う。上記工程を経て、チャネルエッチ型のスイッチング用TFTと容量素子を含む液晶表示パネルが完成する。容量素子は、容量配線層5104とゲート絶縁層5116、絶縁層5120と画素電極層5111とで形成される。

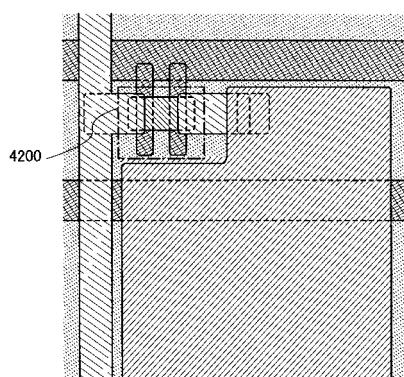

【0180】

本実施の形態では、スイッチングTFTはシングルゲート構造を示したが、ダブルゲート構造などのマルチゲート構造でもよい。図49にダブルゲート構造のスイッチングTFT4200を有する液晶表示装置の上面図を示す。

【0181】

以上示したように、本実施の形態では、フォトマスクを利用した光露光工程を用いないことにより、工程を省略することができる。また、液滴吐出法を用いて基板上に直接的に各種のパターンを形成することにより、1辺が1000mmを超える第5世代以降のガラス基板を用いても、容易に液晶表示パネルを製造することができる。

【0182】

また、密着性が向上した信頼性の高い液晶表示パネルを作製することができる。

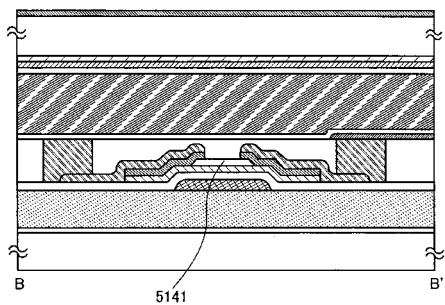

【0183】

(実施の形態6)

本発明の実施の形態として、図47を用いて説明する。本実施の形態は、実施の形態5において、薄膜トランジスタとしてチャネル保護型の薄膜トランジスタを用いるものである。よって、同一部分又は同様な機能を有する部分の繰り返しの説明は省略する。なお、図47は、図48の(B)のチャネルエッチ型の薄膜トランジスタとの断面図と対応している。

【0184】

基板5100上に、絶縁層5102cを形成し、導電性材料を含む組成物を液滴吐出法により吐出して、ゲート配線層、容量配線層を形成する。ゲート配線層と接するようにゲート電極層5105を、液滴吐出法により形成する。次に、プラズマCVD法やスパッタリング法を用いて、ゲート絶縁層5116を単層又は積層構造で形成する。特に好ましい形態としては、窒化珪素からなる絶縁体層、酸化珪素からなる絶縁体層、窒化珪素からなる絶縁体層の3層の積層体がゲート絶縁膜に相当する。さらに、活性層として機能する半導体層5106まで形成する。以上の工程は第5の実施の形態と同様である。

【0185】

半導体層5106を形成し、チャネル保護膜5141を形成するため、例えば、プラズマCVD法により絶縁膜を形成し、所望の領域に、所望の形状となるようにパターニングする。このとき、ゲート電極をマスクとして基板の裏面から露光することにより、チャネル保護膜5141を形成することができる。またチャネル保護膜は、液滴吐出法を用いてポリイミド又はポリビニルアルコール等を滴下してもよい。その結果、露光工程を省略することができる。

【0186】

チャネル保護膜としては、無機材料(酸化珪素、窒化珪素、酸化窒化珪素、窒化酸化珪素など)、感光性または非感光性の有機材料(有機樹脂材料)(ポリイミド、アクリル、

10

20

30

40

50

ポリアミド、ポリイミドアミド、レジスト、ベンゾシクロブテンなど)、低誘電率であるLow-k材料などの一種、もしくは複数種からなる膜、またはこれらの膜の積層などを用いることができる。また、シリコン(Si)と酸素(O)との結合で骨格構造が構成され、置換基に少なくとも水素を含む材料、もしくは置換基にフッ素、アルキル基、または芳香族炭化水素のうち少なくとも1種を有する材料を用いてもよい。作製法としては、プラズマCVD法や熱CVD法などの気相成長法やスパッタリング法を用いることができる。また、液滴吐出法や、印刷法(スクリーン印刷やオフセット印刷などパターンが形成される方法)を用いることもできる。塗布法で得られるTOF膜やSOG膜なども用いることができる。

## 【0187】

10

半導体層5106、チャネル保護膜5141上に、N型半導体層5107を形成する。次に、半導体層5106、N型半導体層5107上に、組成物を選択的に吐出してマスクを形成する。続いて、マスクを利用して、半導体層5106とN型半導体層5107を同時にエッティングして、半導体層とN型半導体層を形成する。その後、半導体層5106上に、導電性材料を含む組成物を吐出して、ソース及びドレイン電極層5130、5108を形成する。

## 【0188】

20

次に、ソース及びドレイン電極層5130、5108をマスクとして、N型半導体層5107をエッティングする。続いて、絶縁層5120を選択的に形成し、絶縁層5120の開口部を埋めるようにソース配線層5109、導電層5110を液滴吐出法により形成する。実施の形態5と同様に、絶縁層5120、ソース配線層5109、導電層5110は同時に形成しても良く、その形成前と後に、前述の下地前処理を行っても良い。ソース及びドレイン電極層5108と、導電層5110を介して電気的に接続するように、導電層5110に接して導電性材料を含む組成物を吐出して、画素電極層5111を形成する。この後、プレス工程を行い、表面を平坦化しても良い。

## 【0189】

次に、配向膜として機能する絶縁体層5131を形成する。続いて、シール材を形成し、該シール材を用いて、基板5100と、カラーフィルタ(着色層)5134と導電体層5135と絶縁体層5133が形成された対向基板5140を貼り合わせる。その後、基板5100と対向基板5140の間に液晶層5132を形成する。次に、接続端子を貼り付ける領域を大気圧又は大気圧近傍下でエッティングして露出させ、該接続端子を貼り付けたら、表示機能を有する液晶表示パネルを作製することができる(図47参照。)。

30

## 【0190】

以上、実施の形態5、及び実施の形態6において逆スタガ型の薄膜トランジスタの例を示したが、本発明は、順スタガ型の薄膜トランジスタにも適用できる。順スタガ型の薄膜トランジスタの場合、ソース配線層がまず絶縁層中に埋め込むように形成され、液滴吐出法によって微細な画素部内のソース及びドレイン電極層がそのソース配線層に接して形成される。これにより、ソース配線層の低抵抗化と、電極層の微細化の両方が、逆スタガ型の薄膜トランジスタと同様、達成できる。

## 【0191】

40

## (実施の形態7)

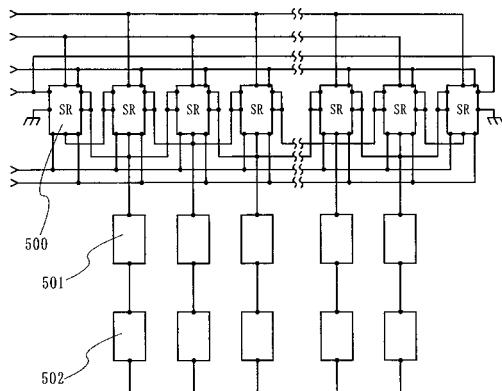

実施の形態1乃至6によって作製される表示パネル(EL表示パネル、液晶表示パネル)において、半導体層をSASで形成することによって、図11で説明したように、走査線側の駆動回路を基板3700上に形成することができる。

## 【0192】

図29は、 $1 \sim 15 \text{ cm}^2 / \text{V} \cdot \text{sec}$ の電界効果移動度が得られるSASを使ったnチャネル型のTFTで構成する走査線側駆動回路のブロック図を示している。

## 【0193】

図29において500で示すブロックが1段分のサンプリングパルスを出力するパルス出力回路に相当し、シフトレジスタはn個のパルス出力回路により構成される。501は

50

バッファ回路であり、その先に画素 502 が接続される。

【0194】

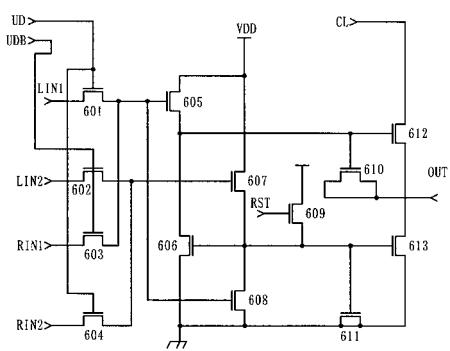

図 30 は、パルス出力回路 500 の具体的な構成を示したものであり、n チャネル型の TFT 601 ~ 612 で回路が構成されている。このとき、SAS を使った n チャネル型の TFT の動作特性を考慮して、TFT のサイズを決定すれば良い。例えば、チャネル長を 8  $\mu\text{m}$  とすると、チャネル幅は 10 ~ 80  $\mu\text{m}$  の範囲で設定することができる。

【0195】

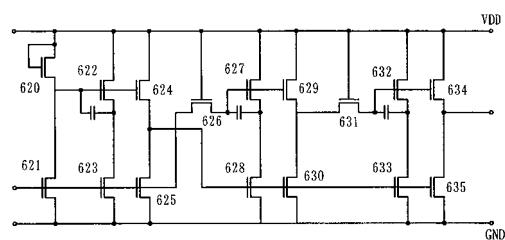

また、バッファ回路 501 の具体的な構成を図 31 に示す。バッファ回路も同様に n チャネル型の TFT 620 ~ 635 で構成されている。このとき、SAS を使った n チャネル型の TFT の動作特性を考慮して、TFT のサイズを決定すれば良い。例えば、チャネル長を 10  $\mu\text{m}$  とすると、チャネル幅は 10 ~ 1800  $\mu\text{m}$  の範囲で設定することとなる。

10

【0196】

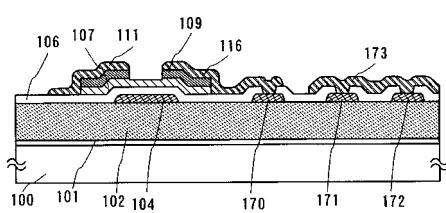

このような回路を実現するには、TFT 相互を配線によって接続する必要があり、その場合における配線の構成例を図 32 に示す。図 32 では、実施の形態 1 と同様に、ゲート電極層 104、ゲート絶縁層 106（窒化珪素からなる絶縁体層 106a、酸化珪素からなる絶縁体層 106b、窒化珪素からなる絶縁体層 106c の 3 層の積層体）、SAS で形成される半導体層 107、ソース及びドレインを形成する N 型半導体層 109、ソース及びドレイン電極層 111、116 が形成された状態を示している。この場合、基板 100 上には、ゲート電極層 104 と同じ工程で接続配線層 170、171、172 を形成しておく。そして、接続配線層 170、171、172 が露出するようにゲート絶縁層の一部をエッチング加工して、ソース及びドレイン電極層 111、116 及びそれと同じ工程で形成する接続配線層 173 により適宜 TFT を接続することにより様々な回路を実現することができる。

20

【0197】

(実施の形態 8)

次に、実施の形態 1 乃至 7 によって作製される EL 表示パネル、液晶表示パネルなどの表示パネルに駆動用のドライバ回路を実装する態様について説明する。

【0198】

まず、COG 方式を採用した表示装置について、図 11 を用いて説明する。基板 370 0 上には、文字や画像などの情報を表示する画素領域 3701、走査側の駆動回路 3702 が設けられる。複数の駆動回路が設けられた基板を、矩形状に分断し、分断後の駆動回路（以下ドライバ IC と表記）3705a、3705b は、基板 3700 上に実装される。図 11 は複数のドライバ IC 3705a、3705b、該ドライバ IC 3705a、3705b の先にテープ 3704 を実装する形態を示す。また、分割する大きさを画素部の信号線側の辺の長さとほぼ同じにし、単数のドライバ IC に、該ドライバ IC の先にテープを実装してもよい。

30

【0199】

また、TAB 方式を採用してもよく、その場合は、複数のテープを貼り付けて、該テープにドライバ IC を実装すればよい。COG 方式の場合と同様に、単数のテープに単数のドライバ IC を実装してもよく、この場合には、強度の問題から、ドライバ IC を固定する金属片等を一緒に貼り付けるとよい。

40

【0200】

これらの表示パネルに実装されるドライバ IC は、生産性を向上させる観点から、一辺が 300 mm から 1000 mm 以上の矩形状の基板上に複数個作り込むとよい。

【0201】

つまり、基板上に駆動回路部と入出力端子を一つのユニットとする回路パターンを複数個形成し、最後に分割して取り出せばよい。ドライバ IC の長辺の長さは、画素部の一辺の長さや画素ピッチを考慮して、長辺が 15 ~ 80 mm、短辺が 1 ~ 6 mm の矩形状に形成してもよいし、画素領域の一辺、又は画素部の一辺と各駆動回路の一辺とを足した長さ

50

に形成してもよい。

【0202】

ドライバICのICチップに対する外形寸法の優位性は長辺の長さにあり、長辺が15~80mmで形成されたドライバICを用いると、画素部に対応して実装するのに必要な数がICチップを用いる場合よりも少なくて済み、製造上の歩留まりを向上させることができる。また、ガラス基板上にドライバICを形成すると、母体として用いる基板の形状に限定されないので生産性を損なうことがない。これは、円形のシリコンウェハからICチップを取り出す場合と比較すると、大きな優位点である。

【0203】

図11において、画素領域3701の外側の領域には、駆動回路が形成されたドライバIC3705a、3705bが実装される。これらのドライバIC3705a、3705bは、信号線側の駆動回路である。RGBフルカラーに対応した画素領域を形成するためには、XGAクラスで信号線の本数が3072本必要であり、UXGAクラスでは4800本が必要となる。このような本数で形成された信号線は、画素領域3701の端部で数プロック毎に区分して引出線を形成し、ドライバIC3705a、3705bの出力端子のピッチに合わせて集められる。

【0204】

ドライバICは、基板上に形成された結晶質半導体により形成されることが好適であり、該結晶質半導体は連続発光のレーザ光を照射することで形成されることが好適である。従って、当該レーザ光を発生させる発振器としては、連続発光の固体レーザ又は気体レーザを用いる。連続発光のレーザを用いると、結晶欠陥が少なく、大粒径の多結晶半導体層を用いて、トランジスタを作成することが可能となる。また移動度や応答速度が良好なために高速駆動が可能で、従来よりも素子の動作周波数を向上させることができ、特性バラツキが少ないために高い信頼性を得ることができる。なお、さらなる動作周波数の向上を目的として、トランジスタのチャネル長方向とレーザ光の走査方向と一致させるとよい。これは、連続発光レーザによるレーザ結晶化工程では、トランジスタのチャネル長方向とレーザ光の基板に対する走査方向とが概ね並行（好ましくは-30°~30°）であるときに、最も高い移動度が得られるためである。なおチャネル長方向とは、チャネル形成領域において、電流が流れる方向、換言すると電荷が移動する方向と一致する。このように作製したトランジスタは、結晶粒がチャネル方向に延在する多結晶半導体層によって構成される活性層を有し、このことは結晶粒界が概ねチャネル方向に沿って形成されていることを意味する。

【0205】

レーザ結晶化を行うには、レーザ光の大幅な絞り込みを行うことが好ましく、そのビームスポットの幅は、ドライバICの短辺の同じ幅の1~3mm程度とすることがよい。また、被照射体に対して、十分に且つ効率的なエネルギー密度を確保するために、レーザ光の照射領域は、線状であることが好ましい。但し、ここでいう線状とは、厳密な意味で線を意味しているのではなく、アスペクト比の大きい長方形もしくは長楕円形を意味する。例えば、アスペクト比が2以上（好ましくは10~10000）のものを指す。このように、レーザ光のビームスポットの幅をドライバICの短辺と同じ長さとすることで、生産性を向上させた表示装置の作製方法を提供することができる。

【0206】

図11では、走査線駆動回路は画素部と共に一体形成し、信号線駆動回路としてドライバICを実装した形態を示した。しかしながら、本発明はこの形態に限定されず、走査線駆動回路及び信号線駆動回路の両方として、ドライバICを実装してもよい。その場合には、走査線側と信号線側で用いるドライバICの仕様を異なるものにするとよい。

【0207】

画素領域3701は、信号線と走査線が交差してマトリクスを形成し、各交差部に対応してトランジスタが配置される。本発明は、画素領域3701に配置されるトランジスタとして、非晶質半導体又はセミアモルファス半導体をチャネル部としたTFTを用いるこ

10

20

30

40

50

とを特徴とする。非晶質半導体は、プラズマCVD法やスパッタリング法等の方法により形成する。セミアモルファス半導体は、プラズマCVD法で300以下の温度で形成することが可能であり、例えば、外寸 $550 \times 650\text{ mm}$ の無アルカリガラス基板であっても、トランジスタを形成するのに必要な膜厚を短時間で形成するという特徴を有する。このような製造技術の特徴は、大画面の表示装置を作製する上で有効である。また、セミアモルファスTFTは、SASでチャネル形成領域を構成することにより $2 \sim 10\text{ cm}^2/\text{V}\cdot\text{sec}$ の電界効果移動度を得ることができる。従って、このTFTを画素のスイッチング用素子や、走査線側の駆動回路を構成する素子として用いることができる。従って、システムオンパネル化を実現した表示パネルを作製することができる。

## 【0208】

10

なお、図11では、半導体層をSASで形成したTFTを用いることにより、走査線側駆動回路も基板上に一体形成することを前提として示している。半導体層をASで形成したTFTを用いる場合には、走査線側駆動回路及び信号線側駆動回路の両方をドライバICを実装してもよい。

## 【0209】

その場合には、走査線側と信号線側で用いるドライバICの仕様を異なるものにすることが好適である。例えば、走査線側のドライバICを構成するトランジスタには30V程度の耐圧が要求されるものの、駆動周波数は100kHz以下であり、比較的高速動作は要求されない。従って、走査線側のドライバを構成するトランジスタのチャネル長(L)は十分大きく設定することが好適である。一方、信号線側のドライバICのトランジスタには、12V程度の耐圧があれば十分であるが、駆動周波数は3Vにて65MHz程度であり、高速動作が要求される。そのため、ドライバを構成するトランジスタのチャネル長などはミクロンルールで設定することが好適である。

20

## 【0210】

ドライバICの実装方法は、特に限定されるものではなく、公知のCOG方法やワイヤボンディング方法、或いはTAB方法を用いることができる。

## 【0211】

30

ドライバICの厚さは、対向基板と同じ厚さとすることで、両者の間の高さはほぼ同じものとなり、表示装置全体としての薄型化に寄与する。また、それぞれの基板を同じ材質のもので作製することにより、この表示装置に温度変化が生じても熱応力が発生することなく、TFTで作製された回路の特性を損なうことはない。その他にも、本実施形態で示すようにICチップよりも長尺のドライバICで駆動回路を実装することにより、1つの画素領域に対して、実装されるドライバICの個数を減らすことができる。

## 【0212】

以上のようにして、表示パネルに駆動回路を組み入れることができる。

## 【0213】

(実施の形態9)

本実施の形態で示すEL表示パネルの画素の構成について、図33に示す等価回路図を参照して説明する。

## 【0214】

40

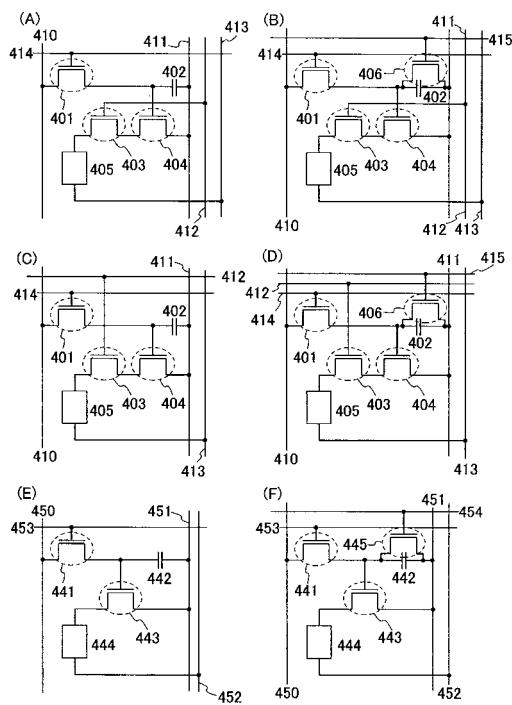

図33(A)に示す画素は、列方向に信号線410及び電源線411～413、行方向に走査線414が配置される。また、スイッチング用TFTであるTFT401、駆動用TFTであるTFT403、電流制御用TFTであるTFT404、容量素子402及び発光素子405を有する。

## 【0215】

図33(C)に示す画素は、TFT403のゲート電極が、行方向に配置された電源線412に接続される点が異なっており、それ以外は図33(A)に示す画素と同じ構成である。つまり、図33(A)(C)に示す両画素は、同じ等価回路図を示す。しかしながら、列方向に電源線412が配置される場合(図33(A))と、行方向に電源線412が配置される場合(図33(C))では、各電源線は異なるレイヤーの導電体層で形成さ

50

れる。ここでは、駆動用TFTであるTFT403のゲート電極が接続される配線に注目し、これらを作製するレイヤーが異なることを表すために、図33(A)(C)として分けて記載する。

【0216】

図33(A)(C)に示す画素の特徴として、画素内にTFT403、404が直列に接続されており、TFT403のチャネル長 $L_3$ 、チャネル幅 $W_3$ 、TFT404のチャネル長 $L_4$ 、チャネル幅 $W_4$ は、 $L_3 / W_3 : L_4 / W_4 = 5 \sim 6000 : 1$ を満たすように設定される点が挙げられる。6000:1を満たす場合の一例としては、 $L_3$ が500μm、 $W_3$ が3μm、 $L_4$ が3μm、 $W_4$ が100μmの場合がある。

【0217】

なお、TFT403は、飽和領域で動作し発光素子405に流れる電流値を制御する役目を有し、TFT404は線形領域で動作し発光素子405に対する電流の供給を制御する役目を有する。両TFTは同じ導電型を有していると作製工程上好ましい。またTFT403には、エンハンスマント型だけでなく、ディブリーション型のTFTを用いてもよい。上記構成を有する本発明は、TFT404が線形領域で動作するために、TFT404の $V_{GS}$ の僅かな変動は発光素子405の電流値に影響を及ぼさない。つまり、発光素子405の電流値は、飽和領域で動作するTFT403により決定される。上記構成を有する本発明は、TFTの特性バラツキに起因した発光素子の輝度ムラを改善して画質を向上させた表示装置を提供することができる。

【0218】

図33(A)～(D)に示す画素において、TFT401は、画素に対するビデオ信号の入力を制御するものであり、TFT401がオンして、画素内にビデオ信号が入力されると、容量素子402にそのビデオ信号が保持される。なお図33(A)～(D)には、容量素子402を設けた構成を示したが、本発明はこれに限定されず、ビデオ信号を保持する容量がゲート容量などでまかなることが可能な場合には、明示的に容量素子402を設けなくてもよい。

【0219】

発光素子405は、2つの電極間に電界発光層が挟まれた構造を有し、順バイアス方向の電圧が印加されるように、画素電極と対向電極の間(陽極と陰極の間)に電位差が設けられる。電界発光層は有機材料や無機材料等の広汎に渡る材料により構成され、この電界発光層におけるルミネッセンスには、一重項励起状態から基底状態に戻る際の発光(蛍光)と、三重項励起状態から基底状態に戻る際の発光(リン光)とが含まれる。

【0220】

図33(B)に示す画素は、TFT406と走査線415を追加している以外は、図33(A)に示す画素構成と同じである。同様に、図33(D)に示す画素は、TFT406と走査線415を追加している以外は、図33(C)に示す画素構成と同じである。

【0221】

TFT406は、新たに配置された走査線415によりオン又はオフが制御される。TFT406がオンになると、容量素子402に保持された電荷は放電し、TFT404がオフする。つまり、TFT406の配置により、強制的に発光素子405に電流が流れない状態を作ることができる。従って、図33(B)(D)の構成は、全ての画素に対する信号の書き込みを待つことなく、書き込み期間の開始と同時又は直後に点灯期間を開始することができるため、デューティ比を向上することが可能となる。

【0222】

図33(E)に示す画素は、列方向に信号線450、電源線451、452、行方向に走査線453が配置される。また、スイッチング用TFT441、駆動用TFT443、容量素子442及び発光素子444を有する。図33(F)に示す画素は、TFT445と走査線454を追加している以外は、図33(E)に示す画素構成と同じである。なお、図33(F)の構成も、TFT445の配置により、デューティ比を向上することが可能となる。

10

20

30

40

50

## 【0223】

## (実施の形態10)

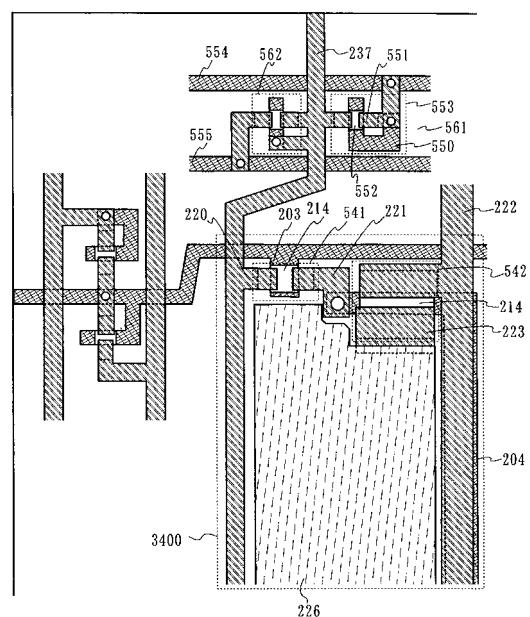

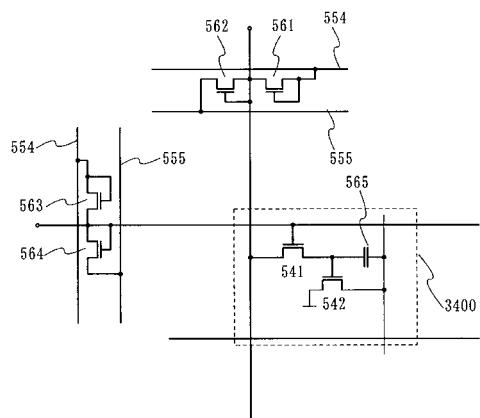

走査線側入力端子部と信号線側入力端子部とに保護ダイオードを設けた一態様について図34を参照して説明する。図34において画素3400にはTFT541、542が設けられている。このTFTは第1の実施の形態と同様な構成を有している。

## 【0224】

信号線側入力端子部には、保護ダイオード561と562が設けられている。この保護ダイオードは、TFT541若しくは542と同様な工程で作製され、ゲートとドレイン若しくはソースの一方とを接続することによりダイオードとして動作させている。図34で示す上面図の等価回路図を図39に示している。

10

## 【0225】

保護ダイオード561は、ゲート電極層550、半導体層551、チャネル保護用の絶縁層552、配線層553から成っている。保護ダイオード562も同様な構造である。この保護ダイオードと接続する共通電位線554、555はゲート電極層と同じ層で形成している。従って、配線層553と電気的に接続するには、ゲート絶縁層にコンタクトホールを形成する必要がある。

## 【0226】

ゲート絶縁層中のコンタクトホールは、液滴吐出法によりマスク層を形成し、エッチング加工すれば良い。この場合、大気圧放電のエッティング加工を適用すれば、局所的な放電加工も可能であり、基板の全面にマスク層を形成する必要はない。

20

## 【0227】

信号配線層237はTFT541におけるソース及びドレイン配線層と同じ層で形成され、それに接続している信号配線層237とソース又はドレイン側が接続する構造となっている。

## 【0228】

走査信号線側の入力端子部も同様な構成である。このように、本発明によれば、入力段に設けられる保護ダイオードを同時に形成することができる。なお、保護ダイオードを挿入する位置は、本実施の形態のみに限定されず、駆動回路と画素との間に設けることもできる。

## 【0229】

30

## (実施の形態11)

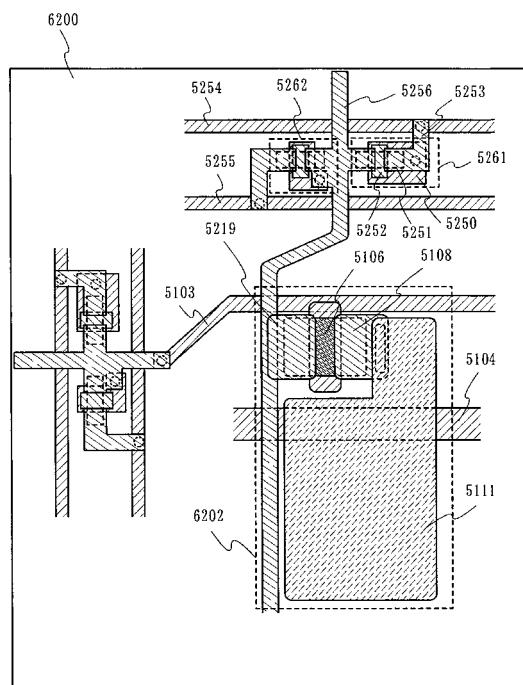

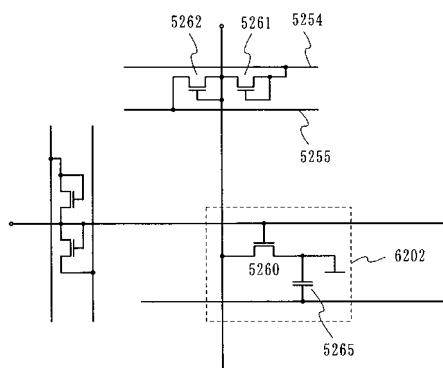

走査線側入力端子部と信号線側入力端子部とに保護ダイオードを設けた一態様について図53、図54を用いて説明する。図54において画素6202にはTFT260が設けられている。このTFTは第5の実施の形態と同様な構成を有している。

## 【0230】

信号線側入力端子部には、保護ダイオード5261と5262が設けられている。この保護ダイオードは、TFT5260と同様な工程で作製され、ゲートとドレイン若しくはソースの一方とを接続することによりダイオードとして動作させている。図53で示す上面図の等価回路図を図54に示している。

## 【0231】

40

基板6200上の保護ダイオード5261は、ゲート電極層5250、半導体層5251、チャネル保護用の絶縁層5252、配線層5253から成っている。保護ダイオード5262も同様な構造である。この保護ダイオードと接続する共通電位線5254、5255はゲート電極層5250と同じ層で形成している。従って、配線層5253と電気的に接続するには、ゲート絶縁層にコンタクトホールを形成する必要がある。

## 【0232】

ゲート絶縁層へのコンタクトホールは、液滴吐出法によりマスク層を形成し、エッティング加工すれば良い。この場合、大気圧放電のエッティング加工を適用すれば、局所的な放電加工も可能であり、基板の全面にマスク層を形成する必要はない。

## 【0233】

50

保護ダイオード 5261 若しくは 5262 は、TFT5260 におけるソース及びドレイン配線層 5219 と同じ層で形成され、それに接続している信号配線層 5256 とソース又はドレン側が接続する構造となっている。

【0234】

走査信号線側の入力端子部も同様な構成である。このように、本発明によれば、入力段に設けられる保護ダイオードを同時に形成することができる。なお、保護ダイオードを挿入する位置は、本実施の形態のみに限定されず、駆動回路と画素との間に設けることもできる。

【0235】

(実施の形態 12)

10

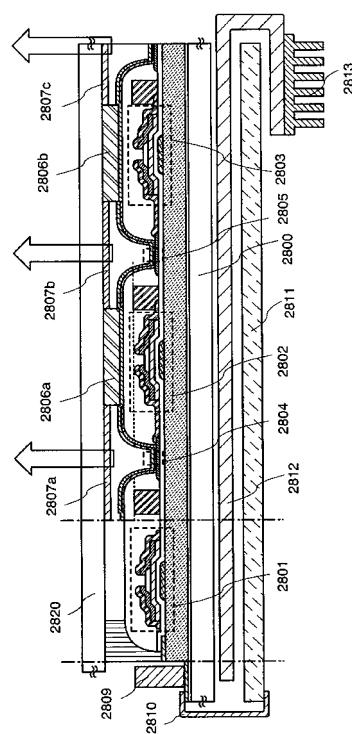

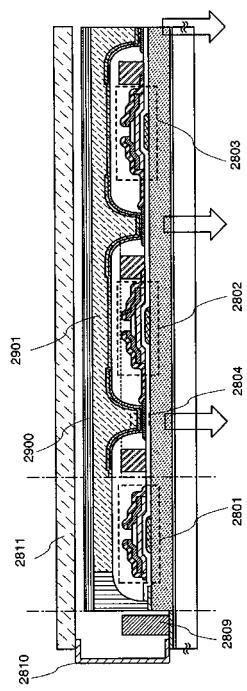

図 28 及び図 35 は、液滴吐出法により作製される TFT 基板 2800 を用いて EL 表示モジュールを構成する一例を示している。両図面において、TFT 基板 2800 上には、画素により構成された画素部が形成されている。

【0236】

図 28 では、画素部の外側であって、駆動回路と画素との間に、画素に形成されたものと同様な TFT 又はその TFT のゲートとソース若しくはドレンの一方とを接続してダイオードと同様に動作させた保護回路部 2801 が備えられている。駆動回路 2809 は、単結晶半導体で形成されたドライバ IC、ガラス基板上に多結晶半導体膜で形成されたスティックドライバ IC、若しくは SAS で形成された駆動回路などが適用されている。

【0237】

20

TFT 基板 2800 は、液滴吐出法で形成されたスペーサ 2806a、2806b を介して封止基板 2820 と固着されている。スペーサは、基板の厚さが薄く、また画素部の面積が大型化した場合にも、2 枚の基板の間隔を一定に保つために設けておくことが好ましい。発光素子 2804、2805 上であって、TFT 基板 2800 と封止基板 2820 との間にある空隙には透光性の樹脂材料を充填して固体化しても良いし、無水化した窒素若しくは不活性気体を充填させても良い。

【0238】

図 27 では発光素子 2804、2805 をトップエミッション型の構成とした場合を示し、図中に示す矢印の方向に光を放射する構成としている。各画素は、画素を赤色、緑色、青色として発光色を異らせておくことで、多色表示を行うことができる。また、このとき封止基板 2820 側に各色に対応した着色層 2807a、2807b、2807c を形成しておくことで、外部に放射される発光の色純度を高めることができる。また、画素を白色発光素子として着色層 2807a、2807b、2807c と組み合わせても良い。

30

【0239】

駆動回路 2809 は、TFT 基板 2800 の一端に設けられた走査線若しくは信号線接続端子と、配線基板 2810 で接続される。また、TFT 基板 2800 に接して若しくは近接させて、ヒートパイプ 2813 と放熱板 2812 を設け、放熱効果を高める構成としても良い。

【0240】

40

なお、図 28 では、トップエミッションの EL モジュールとしたが、発光素子の構成や外部回路基板の配置を変えてボトムエミッション構造としても良い。

【0241】

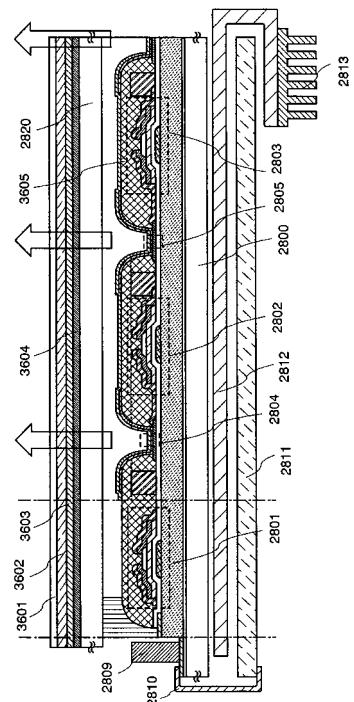

図 35 は、TFT 基板 2800 において、画素部が形成された側にシール材や接着性の樹脂 2901 を用いて樹脂フィルム 2900 を貼り付けて封止構造を形成した一例を示している。樹脂フィルム 2900 の表面には水蒸気の透過を防止するガスバリア膜を設けておくと良い。図 35 では、発光素子の光が基板を通して放射されるボトムエミッションの構成を示しているが、樹脂フィルム 2900 や接着性の樹脂 2901 を透光性とすることにより、トップエミッション構造とすることもできる。いずれにしても、フィルム封止構造とすることで、さらなる薄型化及び軽量化を図ることができる。

50

## 【0242】

## (実施の形態13)

本発明によって形成される表示装置によって、テレビジョン装置（ELテレビジョン装置、液晶テレビジョン装置）を完成させることができる。図26はテレビジョン装置の主要な構成を示すブロック図を示している。表示パネルには、図38で示すような構成として画素部のみが形成されて走査線側駆動回路と信号線側駆動回路とがT A B方式により実装される場合と、図27に示すような構成として画素部とその周辺に走査線側駆動回路と信号線側駆動回路とがC O G方式により実装される場合と、図11に示すようにS A SでTFTを形成し、画素部と走査線側駆動回路を基板上に一体形成し信号線側駆動回路を別途ドライバICとして実装する場合などがあるが、どのような形態としても良い。

10

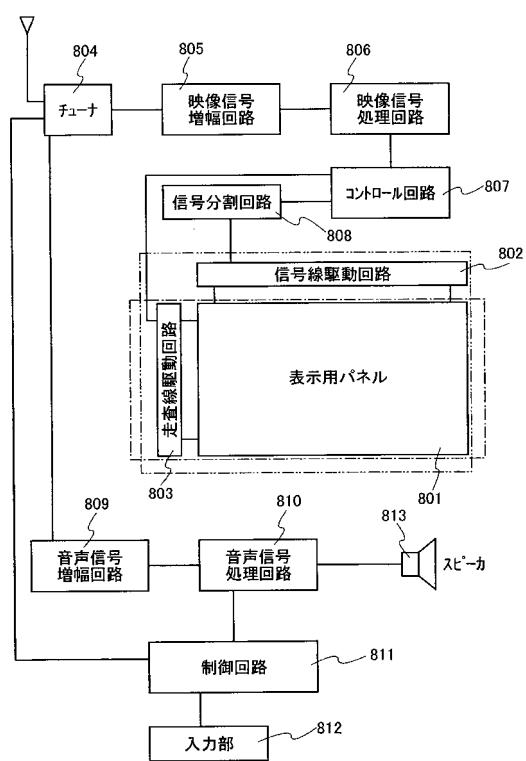

## 【0243】

その他の外部回路の構成として、映像信号の入力側では、チューナ804で受信した信号のうち、映像信号を増幅する映像信号增幅回路805と、そこから出力される信号を赤、緑、青の各色に対応した色信号に変換する映像信号処理回路806と、その映像信号をドライバICの入力仕様に変換するためのコントロール回路807などからなっている。コントロール回路807は、走査線側と信号線側にそれぞれ信号が出力する。デジタル駆動する場合には、信号線側に信号分割回路808を設け、入力デジタル信号をm個に分割して供給する構成としても良い。

## 【0244】

チューナ804で受信した信号のうち、音声信号は、音声信号增幅回路809に送られ、その出力は音声信号処理回路810を経てスピーカ813に供給される。制御回路811は受信局（受信周波数）や音量の制御情報を入力部812から受け、チューナ804や音声信号処理回路810に信号を送出する。

20

## 【0245】

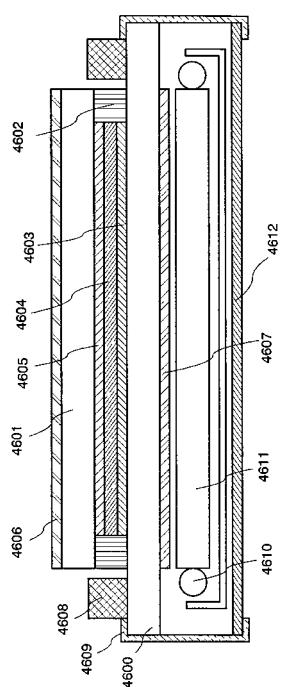

図55は液晶表示モジュールの一例であり、TFT基板4600と対向基板4601がシール材4602により固定され、その間に画素部4603と液晶層4604が設けられ表示領域を形成している。着色層4605はカラー表示を行う場合に必要であり、RGB方式の場合は、赤、緑、青の各色に対応した着色層が各画素に対応して設けられている。TFT基板4600と対向基板4601の外側には偏光板4606、4607が配設されている。光源は冷陰極管4610と導光板4611により構成され、回路基板4612は、フレキシブル配線基板4609によりTFT基板4600上の外部回路4608と接続され、コントロール回路や電源回路などの外部回路が組みこまれている。

30

## 【0246】

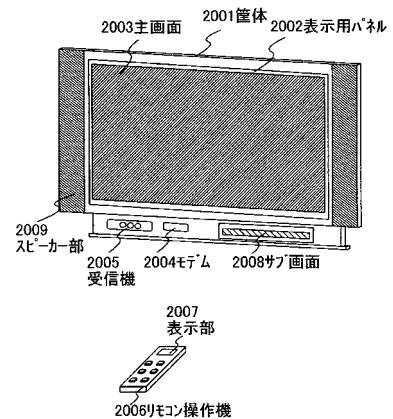

このELモジュール、液晶表示モジュールなどの表示モジュールを、図24に示すように、筐体2001に組みこんで、テレビジョン装置を完成させることができる。表示モジュールにより主画面2003が形成され、その他付属設備としてスピーカ部2009、操作スイッチなどが備えられている。このように、本発明によりテレビジョン装置を完成させることができる。

## 【0247】

また、図36に示すように、波長板や偏光板を用いて、外部から入射する光の反射光を遮断するようにしてもよい。図36はトップエミッション型の構成であり、隔壁となる絶縁層3605を着色しブラックマトリクスとして用いている。この隔壁は液滴吐出法により形成することができ、ポリイミドなどの樹脂材料に、カーボンブラック等を混合させてもよく、その積層でもよい。液滴吐出法によって、異なった材料を同領域に複数回吐出し、隔壁を形成してもよい。波長板3603、3604としては、/4、\/2を用い、光を制御できるように設計すればよい。構成としては、順にTFT基板2800、発光素子2804、封止基板（封止材）2820、波長板3603、3604（/4、\/2）、偏光板3602となり、発光素子から放射された光は、これらを通過し偏光板側より外部に放射される。この波長板や偏光板は光が放射される側に設置すればよく、両面放射される両面放射型の表示装置であれば両方に設置することもできる。また、偏光板の外側

40

50

に反射防止膜 3601 を有していても良い。これにより、より高繊細で精密な画像を表示することができる。

【0248】

筐体 2001 に表示素子を利用した表示用パネル 2002 が組みこまれ、受信機 2005 により一般のテレビ放送の受信をはじめ、モデム 2004 を介して有線又は無線による通信ネットワークに接続することにより一方向（送信者から受信者）又は双方向（送信者と受信者間、又は受信者間同士）の情報通信をすることもできる。テレビジョン装置の操作は、筐体に組みこまれたスイッチ又は別体のリモコン装置 2006 により行うことが可能であり、このリモコン装置にも出力する情報を表示する表示部 2007 が設けられても良い。

10

【0249】

また、テレビジョン装置にも、主画面 2003 の他にサブ画面 2008 を第 2 の表示用パネルで形成し、チャネルや音量などを表示する構成が付加されても良い。主画面 2003 を低消費電力で表示可能な液晶表示用パネルで形成し、サブ画面を視野角の優れた E L 表示用パネルで形成し、点滅可能とする構成としても良い。本発明を用いると、このような大型基板を用いて、多くの TFT や電子部品を用いても、信頼性の高い表示装置とすることもできる。

【0250】

勿論、本発明はテレビジョン装置に限定されず、パーソナルコンピュータのモニタをはじめ、鉄道の駅や空港などにおける情報表示盤や、街頭における広告表示盤など特に大面積の表示媒体として様々な用途に適用することができる。

20

【0251】

（実施の形態 14）

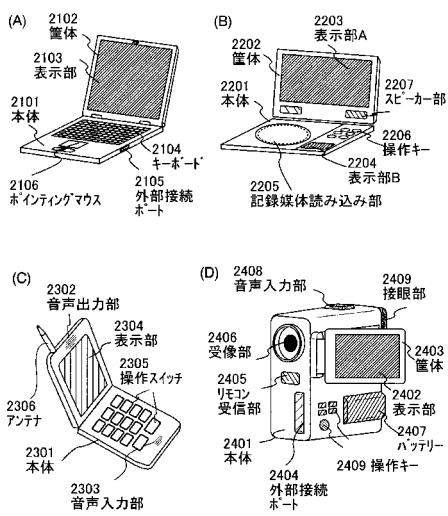

本発明を適用して、様々な表示装置を作製することができる。即ち、それら表示装置を表示部に組み込んだ様々な電子機器に本発明を適用できる。

【0252】

その様な電子機器としては、ビデオカメラ、デジタルカメラ、プロジェクター、ヘッドマウントディスプレイ（ゴーグル型ディスプレイ）、カーナビゲーション、カーステレオ、パーソナルコンピュータ、ゲーム機器、携帯情報端末（モバイルコンピュータ、携帯電話または電子書籍等）、記録媒体を備えた画像再生装置（具体的にはDigital Versatile Disc (DVD) 等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置）などが挙げられる。それらの例を図 25 に示す。

30

【0253】

図 25 (A) は、ノート型パーソナルコンピュータであり、本体 2101、筐体 2102、表示部 2103、キーボード 2104、外部接続ポート 2105、ポインティングマウス 2106 等を含む。本発明は、表示部 2103 の作製に適用される。本発明を用いると、小型化し、配線等が精密化しても、信頼性の高い高画質な画像を表示することができる。

【0254】

図 25 (B) は記録媒体を備えた画像再生装置（具体的にはDVD 再生装置）であり、本体 2201、筐体 2202、表示部 A 2203、表示部 B 2204、記録媒体 (DVD 等) 読み込み部 2205、操作キー 2206、スピーカー部 2207 等を含む。表示部 A 2203 は主として画像情報を表示し、表示部 B 2204 は主として文字情報を表示するが、本発明は、これら表示部 A、B 2203、2204 の作製に適用される。本発明を用いると、小型化し、配線等が精密化しても、信頼性の高い高画質な画像を表示することができる。

40

【0255】

図 25 (C) は携帯電話であり、本体 2301、音声出力部 2302、音声入力部 2303、表示部 2304、操作スイッチ 2305、アンテナ 2306 等を含む。本発明により作製される表示装置を表示部 2304 に適用することで、小型化し、配線等が精密化す

50

る携帯電話であっても、信頼性の高い高画質な画像を表示できる。

【0256】

図25(D)はビデオカメラであり、本体2401、表示部2402、筐体2403、外部接続ポート2404、リモコン受信部2405、受像部2406、バッテリー2407、音声入力部2408、操作キー2409、接眼部2410を含む。本発明は、表示部2402に適用することができる。本発明により作製される表示装置を表示部2304に適用することで、小型化し、配線等が精密化するビデオカメラであっても、信頼性の高い高画質な画像を表示できる。本実施の形態は、上記の実施の形態と自由に組み合わせることができる。

【図面の簡単な説明】

10

【0257】

【図1】本発明の表示装置の作製方法を説明する図。

【図2】本発明の表示装置の作製方法を説明する図。

【図3】本発明の表示装置の作製方法を説明する図。

【図4】本発明の表示装置の作製方法を説明する図。

【図5】本発明の表示装置の作製方法を説明する図。

【図6】本発明の表示装置の作製方法を説明する図。

【図7】本発明の表示装置の作製方法を説明する図。

【図8】本発明の表示装置の作製方法を説明する図。

【図9】本発明の表示装置の作製方法を説明する図。

20

【図10】本発明の表示装置を説明する図。

【図11】本発明の表示装置の上面図。

【図12】本発明の表示装置の作製方法を説明する図。

【図13】本発明の表示装置の作製方法を説明する図。

【図14】本発明の表示装置の作製方法を説明する図。

【図15】本発明の表示装置の作製方法を説明する図。

【図16】本発明の表示装置の画素回路の上面図。

【図17】本発明の表示装置の作製方法を説明する図。

【図18】本発明の表示装置の作製方法を説明する図。

30

【図19】本発明の表示装置の作製方法を説明する図。

【図20】本発明の表示装置の作製方法を説明する図。

【図21】本発明の表示装置の作製方法を説明する図。

【図22】本発明の表示装置の作製方法を説明する図。

【図23】本発明の表示装置の作製方法を説明する図。

【図24】本発明が適用される電子機器を示す図。

【図25】本発明が適用される電子機器を示す図。

【図26】本発明の電子機器の主要な構成を示すブロック図。

【図27】本発明の表示装置の上面図。

【図28】本発明のEL表示モジュールの構成例を説明する断面図。

【図29】本発明の表示パネルにおいて走査線側駆動回路をTFTで形成する場合の回路構成を説明する図。

40

【図30】本発明の表示パネルにおいて走査線側駆動回路をTFTで形成する場合の回路構成を説明する図(シフトレジスタ回路)。

【図31】本発明の表示パネルにおいて走査線側駆動回路をTFTで形成する場合の回路構成を説明する図(バッファ回路)。

【図32】本発明の表示装置の作製方法を説明する図。

【図33】本発明のEL表示パネルに適用できる画素の構成を説明する回路図。

【図34】本発明のEL表示パネルを説明する上面図である。

【図35】本発明のEL表示モジュールの構成例を説明する断面図。

【図36】本発明のEL表示モジュールの構成例を説明する断面図。

50

【図37】本発明に適用することができる液滴吐出装置の構成を説明する図。

【図38】本発明の表示装置の上面図。

【図39】図34で説明するEL表示パネルの等価回路図である。

【図40】本発明の液晶表示装置の作製方法を説明する図。

【図41】本発明の液晶表示装置の作製方法を説明する図。

【図42】本発明の液晶表示装置の作製方法を説明する図。

【図43】本発明の液晶表示装置の作製方法を説明する図。

【図44】本発明の液晶表示装置の作製方法を説明する図。

【図45】本発明の液晶表示装置の作製方法を説明する図。

【図46】本発明の液晶表示装置の作製方法を説明する図。

10

【図47】本発明の液晶表示装置の断面図。

【図48】本発明の液晶表示装置の作製方法を説明する図。

【図49】本発明の液晶表示装置の上面図。

【図50】本発明の液晶表示装置の作製方法を説明する図。

【図51】本発明の液晶表示装置の作製方法を説明する図。

【図52】本発明の液晶表示装置の作製方法を説明する図。

【図53】本発明の液晶表示パネルを説明する上面図。

【図54】図53で説明する液晶表示パネルの等価回路図。

【図55】本発明の液晶表示モジュールの構成を説明する図。

【図1】

【図3】

【図2】

【図4】

【図5】

【図7】

【図6】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図31】

【図30】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図39】

【図40】

【図41】

【図42】

【図43】

【図44】

【図45】

【図46】

【図47】

【図48】

【図49】

【図50】

【図51】

【図52】

【図 5 3】

【図 5 4】

【図 5 5】

---

フロントページの続き

(72)発明者 伊佐 敏行

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

審査官 綿引 隆

(56)参考文献 特開2003-318192(JP,A)

特開平10-209463(JP,A)

特開平03-085530(JP,A)

特開2003-318401(JP,A)

(58)調査した分野(Int.Cl., DB名)

G02F 1/1368

H01L 21/288

H01L 21/336

H01L 29/786

H01L 51/50