(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4771654号

(P4771654)

(45) 発行日 平成23年9月14日(2011.9.14)

(24) 登録日 平成23年7月1日(2011.7.1)

(51) Int.Cl.

G06F 12/06 (2006.01)

F 1

G06F 12/06 540C

G06F 12/06 550A

請求項の数 3 (全 17 頁)

(21) 出願番号 特願2003-379250 (P2003-379250)

(22) 出願日 平成15年11月10日 (2003.11.10)

(65) 公開番号 特開2004-164641 (P2004-164641A)

(43) 公開日 平成16年6月10日 (2004.6.10)

審査請求日 平成18年10月11日 (2006.10.11)

(31) 優先権主張番号 10/292,144

(32) 優先日 平成14年11月12日 (2002.11.12)

(33) 優先権主張国 米国(US)

(73) 特許権者 511076424

ヒューレット-パッカード デベロップメント カンパニー エル.ピー.

Hewlett-Packard Development Company, L.P.

アメリカ合衆国 テキサス州 77070

ヒューストン コンパック センタードライブ ウエスト 11445

(74) 代理人 110000246

特許業務法人O F H特許事務所

(74) 代理人 100081721

弁理士 岡田 次生

(74) 代理人 100105393

弁理士 伏見 直哉

最終頁に続く

(54) 【発明の名称】メモリバンクへのアドレスのマッピングをするメモリコントローラ

## (57) 【特許請求の範囲】

## 【請求項 1】

受信アドレスを複数のメモリバンクのメモリロケーションにマッピングするメモリコントローラであって、

前記受信アドレスを前記複数のバンクの数に基づく除数によって除算した際の剰余を計算する回路と、

前記剰余と、前記受信アドレスの少なくとも1ビットとの組合せについての条件に基づいて、前記複数のバンクのうちの特定のバンクを求める回路と、

前記受信アドレスの少なくとも一部を使用して前記特定のバンク内の前記メモリロケーションを求める回路と、

前記特定のバンクがビジーである場合、前記受信アドレスに係るメモリアクセス要求を保留し、ビジーでないバンクへの後着のメモリアクセス要求を発行する並び替えバッファと、

を有するメモリコントローラ。

## 【請求項 2】

アドレスを複数のメモリバンクのうちの特定のバンクにマップする方法であって、

前記アドレスを受け取るステップと、

前記複数のバンクの数に基づく除数によって前記アドレスを除算するステップと、

前記除算するステップの剰余と、前記アドレスの少なくとも1ビットとの組合せについての条件に基づいて、前記特定のバンクを求めるステップと、

10

20

前記特定のバンクがビジーである場合、前記受信アドレスに係るメモリアクセス要求を保留し、ビジーでないバンクへの後着のメモリアクセス要求を発行する並び替えステップと、

を含む方法。

【請求項 3】

複数のメモリバンクと、

アドレスを含むメモリアクセス要求を受け取り、前記アドレスの少なくとも 1 ビットと、前記複数のメモリバンクの数に関連付けられる数によって前記アドレスを除算した剰余との組合せについての条件に基づいて、前記アドレスを複数のメモリバンクのうちの特定のバンクにマップする、メモリコントローラと、

10

前記受け取ったアドレスの少なくとも一部を使用して、前記特定のバンク内の特定の口ケーションにアクセスする回路と、

前記特定のバンクがビジーである場合、前記アドレスに係るメモリアクセス要求を保留し、ビジーでないバンクへの後着のメモリアクセス要求を発行する並び替えバッファと、

を有するコンピュータシステム。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、包括的にはコンピュータメモリに関し、特に、競合を低減し帯域幅を増大させる、メモリバンクにアドレスをマッピングするシステムおよび方法に関する。

20

【背景技術】

【0002】

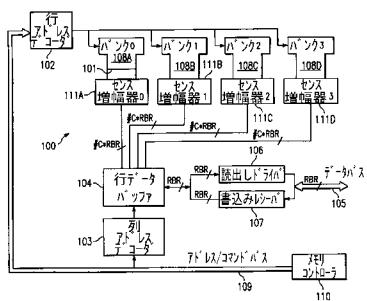

同期ダイナミックランダムアクセスメモリ (synchronous dynamic random access memory、 S D R A M ) またはダブルデータレートメモリ (double data rate memory、 D D R ) は、通常、複数のバンクを備える。たとえば、図 1 A に示すように、メモリ 100 は 4 つのバンク、すなわち 108 A、108 B、108 C および 108 D を備える。各バンクは、行と列とに配置される。各バンクは、そのそれぞれのセンス増幅器 (sense amplifier) 111 A、111 B、111 C および 111 D を有する。データがメモリから読出されるかメモリに書き込まれる時、メモリの特定のバンク (たとえば、108 A) における特定の行 101 が、コントローラ 110 からの、行アドレスデコーダ 102 によってデコードされる行およびバンクアドレスによって起動される。所望の行は、行データバッファ 104 にロードされる。特定の行がアクティブとなった後、列アドレスデコーダ 103 がコントローラ 110 からのアドレスを使用して、行データバッファ 104 内の起動された行の列を選択する。特定の列 / 行アドレスロケーションに入るかまたはそこから出るデータは、データバス 105 と、読み出しドライバ 106 と、書き込みレシーバ 107 と、によって処理される。コントローラ 110 により、アドレス / コマンドバス 109 が使用されることにより、アドレスおよびコマンドが行アドレスデコーダ 102 と列アドレスデコーダ 103 とに送られる。なお、ライン幅は、列の数 (# c) × トランザクションのバースト長 (R<sub>B R</sub>) であり、バースト長は、初期列アドレスから開始してアクセスされる連続的な列の数であることに留意されたい。

30

【0003】

メモリ 100 を、バーストメモリトランザクションを処理するようにプログラムしてよく、それにより、単一バンク内で複数のデータロケーションに同時にアクセスする (すなわち、そこから読出しかまたはそこに書込む) ことが可能になる。図 1 A のメモリの場合、バースト長が 4 とすると、1 つの列アドレスが 4 つの連続したアドレスとして解釈され、それにより 1 つの列アドレスのみで 4 つの列に同時にアクセスすることができる。各列 / 行ロケーションに対応するメモリロケーションが、データバスに連結される。このため、行が起動される毎に、合計 4 つのメモリロケーションにアクセスすることができる。

【0004】

40

50

この構成の1つの問題は、メモリバンクに対してセンス増幅器が1行しかないことである。したがって、メモリバンクの特定行に対してメモリロケーションがアクセスされた後、その行を、同じバンクの異なる行へのアクセスを可能にするために閉じるかまたはプリチャージする必要がある。このため、プリチャージが行われている間、メモリバンク内の他の行にアクセスすることができない。同じバンクにおける異なる行に対する起動間の最短時間は、行アドレスストローブ (row address strobe、R A S) サイクルタイムすなわち  $T_{R C}$  として知られている。

#### 【0005】

システムパフォーマンスを最大にするために、データバスは、可能な限りビジーに維持される必要があり、そうでなければ、C P U は、メモリからのデータを待つ間にアイドル状態となる可能性がある。データバス使用を最大にする1つの方法は、異なるバンクへの連続したメモリアクセスをインターリーブすることである。これにより、1つの特定バンクにアクセスした後、他のバンクは、理想的には  $T_{R C}$  が経過するまでアクセスされ、その後、その1つの特定バンクに再びアクセスすることができる。なお、帯域幅は、データがバスで転送されるクロックサイクルの数をクロックサイクルの合計数によって除算した数であることに留意されたい。そのため、データが常に転送される場合、帯域幅は 100 % である。データが 3 / 4 サイクルで転送される場合、帯域幅は 75 % である。そのため、帯域幅を最大化することは、データバスの使用を最大にすることを意味する。

#### 【0006】

図 1 B は、従来技術による図 1 A の 4 バンクメモリへのアドレスマッピングの例 150 を示す。この例では、簡単のために、4 つのバンクが合計 32 のアドレスロケーションを有するものと仮定する。このように、ストライド 1 でアドレス指定される、連続的にアドレス指定されるトランザクションは、異なるバンクにマッピングされる。これは、最下位ビットがバンクアドレスを確定するため、最下位ビット (L S B) インターリービングと呼ばれる。たとえば、2 進表記では、16、17、18 および 19 の 2 つの最下位ビットは、それぞれ 00、01、10 および 11 であり、そのためこれらのアドレスは、それぞれバンク 0、1、2 および 3 にマッピングされる。なお、0 ~ 31 より高いアドレスは、循環ロケーションにマッピングし、たとえば、アドレス 32 はロケーション 0 にマッピングし、アドレス 33 はロケーション 1 にマッピングする、等である。

#### 【0007】

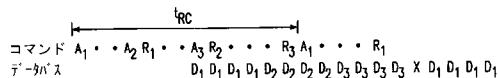

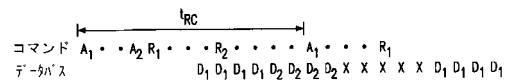

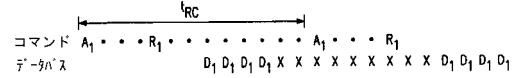

図 2 A ないし図 2 C は、インターリービングがいかにデータバスに影響を与えるかを示す。 $t_{R C}$  は 13 サイクルであり、バースト長は 4 サイクルであり、 $A_x$  はバンク X に対する起動コマンドであり、 $R_x$  はバンク X に対する読み出しコマンドであり、 $D_x$  はバンク X からのデータであるものとする。図 2 A は、図 1 A に示す構成の 4 バンクのうちの 3 バンクを使用するインターリービングの例を示す。図示するように、データバスは、13 サイクルのうちの 12 サイクルに対して使用される。図 2 B は、図 1 A に示す構成の 4 バンクのうちの 2 バンクを使用するインターリービングの例を示す。図示するように、データバスは、13 サイクルのうちの 8 サイクルに対して使用され、それは、図 2 A の構成の効率の 2 / 3 である。R 2 が発行された後、第 1 のバンクに対して R A S サイクルタイム ( $t_{R C}$ ) は完了していないため、第 1 のバンクに対する後続するアクセスは、R A S サイクルタイムが完了するまで待たなければならない。この追加の待ち時間により、データバス使用が低減する。図 2 C は、図 1 A に示す構成の 4 バンクのうちの 1 バンクを使用するインターリービングの例を示す。図示するように、データバスは、13 サイクルのうちの 4 サイクルに対して使用され、それは図 2 A の構成の効率の 1 / 3 である。1 つのバンクのみが使用されているため、次のアクセスを開始する前に、各アクセスに対してプリチャージが完了しなければならない。インターリービング例の効率を調べる別な方法は、3 つのバンクを使用することにより B の帯域幅効率が提供され (図 2 A)、2 つのバンクを使用することにより 2 B / 3 の効率が提供され (図 2 B)、1 つのバンクを使用することにより 1 B / 3 の効率が提供される (図 2 C)、と想定することである。

#### 【0008】

10

20

30

40

50

メモリコマンドは、アドレス / コマンドバス 109 を介して送られ、典型的には、アドレスとともに提供される 4 つの追加ビットを含む。コマンドビットは、典型的には、書込みイネーブル (write enable、WE) と、RAS と、列アドレスストローブ (column address strobe、CAS) と、チップ選択 (chip select、CS) と、を含む。たとえば、図 2A の A1 (起動コマンド) は、行 / バンクアドレスとともに送られ、R1 (読み出しコマンド) は、列 / バンクアドレスとともに送られる。このように、読み出し (または書き込み) 動作に対し、2 つの別々のコマンド、すなわち行アドレスによる起動とそれに続く列アドレスによる読み出し / 書込みとが使用される。

#### 【0009】

インターリービングを達成するために使用される第 1 の従来技術の方法は、連続するアクセスに対して異なるバンクが使用されるように、メモリアクセスを並び替える、というものである。複数のメモリアクセスが、メモリコントローラ 110 において待ち行列に入れられるかまたはバッファリングされる。そして、連続したメモリアクセスに対して異なるバンクが使用されるように、異なる順序でバッファからアクセスが発行される。この方法にはいくつかの問題がある。すなわち、この方法は、ランダムアドレスマッピングには適当に作用するが、アクセスにおけるアドレスが一定のストライドを有する場合は適当に作用しない。それは、並べ替えバッファが、ストライドパターンを壊すいかなるアドレスも含まないためである。一定のストライドアドレスは、1 つまたは 2 つのバンクにマッピングする傾向にある。このため、0、4、8、…のアドレスを有する 4 バンクメモリ (ストライドが 4) に対する一連のアクセス要求は、同じバンクにマッピングし、アドレス 0、2、4、6、…を有する (ストライドが 2) 一連のアクセス要求は、2 つのバンクにマッピングする。そのため、いかにアクセスがバッファリングされようとも、1 つまたは 2 つのバンクしか使用されない。上に示したように、1 つのバンクかまたは 2 つのバンクへの順次アクセスは、それぞれ 1B / 3 または 2B / 3 の効率を有する。なお、これは典型的には、プログラム全体を通して連続して発生せず、プログラム実行のいくつかのスポットにおいて発生する、ということに留意されたい。

#### 【0010】

従来技術でインターリービングを達成するために使用する第 2 の方法は、要求のアドレスの下位ビットにわたってインターリープすることである。たとえば、上の 4 バンク例を使用することにより、バンクを選択するためにアドレスの 2 つの最下位ビットが使用される。このため、00 はバンク 0 にアクセスし、01 はバンク 1 にアクセスし、10 はバンク 2 にアクセスし、11 はバンク 3 にアクセスする。ここでもまた、この方法は、ランダムアドレスかまたはストライドが 1 のアドレスには適当に作用するが、ストライドが  $2^N$ 、たとえば 2 または 4 のアドレスには適当に作用しない。1 のストライドは、4 つのバンクすべてにわたってインターリープする。2 のストライドにより、上記例の 4 バンクのうちの 2 つのバンクにわたってインターリープすることになる。たとえば、0、2、4、6、8、…のアドレスは、第 1 のバンク (0、4、8 はバンク 0 にマッピングする) と第 3 のバンク (2、6 はバンク 2 にマッピングする) とにわたってインターリープする。4 のストライドは、1 つのバンクにわたってインターリープする。たとえば、0、4、8、…のアドレスは、第 1 のバンク、バンク 0 にわたってインターリープする。4 バンク例によるこの方法の場合の平均帯域幅は、(B + 2 / 3B + B + 1 / 3B) / 4 であり、それは 3B / 4 に等しく、最悪の場合の帯域幅は 1 / 3B である。なお、平均帯域幅は、4 つのあり得るストライド帯域幅、すなわち、1 のストライド (B)、2 のストライド (2B / 3)、3 のストライド (B) および 4 のストライド (1B / 3) から計算される。この方法は、非特許文献 1 においてさらに説明されているので参照されたい。

#### 【0011】

従来技術でインターリービングを達成するために使用する第 3 の方法は、各々が  $2^X$  行および列を有する、素数のバンクを使用することである。バンクへのアドレスのマッピングを、アドレス mod バンク、すなわち、アドレスをバンクの数で除算した後の剰余を計算することによって行う。たとえば、3 つのバンクがある場合、6 mod 3 = 0、7 mod

10

20

30

40

50

$d_3 = 1$ 、 $8 \bmod 3 = 2$  および  $9 \bmod 3 = 0$  等である。このように、1 または 2 のストライドでは、順次アクセスが異なるバンクに向けられることになるが、3 のストライドでは、アクセスが同じバンクに向けられることになる。なお、 $n$  のストライドは、 $n \bmod 3$  のストライドと同じ振舞いをし、そのため、たとえば 4 のストライドは  $4 \bmod 3 = 1$  のストライドのように振舞う。このように、あり得るすべてのストライドに対して 3 バンクシステムの帯域幅を計算するためには、ストライド 1、2 および 3 の帯域幅を計算するだけでよい。3 バンクシステムでの素数方法の場合の平均帯域幅は、 $(B + B + 1B / 3) / 3 = 7B / 9$  であり、最悪の場合は、3 のストライドに対する  $1B / 3$  である。この方法は、非特許文献 2 においてさらに説明されているので参照されたい。この方法の問題は、メモリシステムが素数で利用可能ではないことである。メモリシステム、たとえば SDRAM は、通常、 $2^N$  のバンクにおいてのみ利用可能である。このため、この方法を使用するシステムは、メモリの一部、たとえば、4 バンクある場合の 1 バンクか、または 16 に最も近い素数が 13 であるため 16 バンクある場合の 3 バンクを使用しない。10

#### 【0012】

なお、帯域幅の上記論考は、メモリアクセス要求の連続的なストリームに対して一定のストライドで達成することができる最大帯域幅に対するものである。実際の実現される帯域幅は、一般的に、最大帯域幅より小さい。それは、実際のメモリアクセスパターンが、通常、連続した一定のストライドより複雑である、たとえば異なる時間長に対して異なるストライドであるかまたはまったくストライドがないためである。

【非特許文献 1】 "Techniques for Higher Bandwidth: Avoiding Memory Bank Conflicts", Computer Architecture: a Quantitative Approach (2nd edition), pp.435 ~ 437, Hennessey & Patterson 199620

【非特許文献 2】 Gao, "The Chinese Remainder Theorem and the Prime Memory System", 20th Annual Int'l Symposium on Computer Architecture ISCA '20, San Diego, May 16 ~ 19, 1993

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0013】

本発明の目的は、データバスを最大限使用してシステムパフォーマンスを最大とするような、メモリバンクにアドレスをマッピングするシステムおよび方法を提供するものである。30

#### 【課題を解決するための手段】

#### 【0014】

本発明の一実施形態は、受信アドレスを複数のメモリバンクのメモリロケーションにマッピングするメモリコントローラであって、受信アドレスを複数のバンクの数に基づく除数によって除算した際の剩余を計算する回路と、剩余と受信アドレスの少なくとも 1 ビットとに基づいて複数のバンクのうちの特定バンクを確定する回路と、受信アドレスの少なくとも一部を使用して特定バンクのメモリロケーションを確定する回路と、を備えるメモリコントローラである。40

#### 【0015】

本発明の別の実施形態は、アドレスを複数のメモリバンクのうちの特定バンクにマッピングする方法であって、アドレスを受取るステップ、アドレスを複数のバンクの数に基づく除数によって除算するステップ、除算するステップの剩余とアドレスの少なくとも 1 ビットとに基づいて特定バンクを確定するステップ、とを含む方法である。

#### 【0016】

本発明の別の実施形態は、アドレスを複数のメモリバンクのうちの特定バンクにマッピングするシステムであって、アドレスを複数のバンクの数に基づく除数によって除算し剩余を形成する手段と、剩余とアドレスの少なくとも 1 ビットとに基づいて特定バンクを確定する手段と、を備えるシステムである。

#### 【0017】

10

20

30

40

50

本発明の別の実施形態は、複数のメモリバンクと、アドレスを含むメモリアクセス要求を受取り、アドレスの少なくとも1つのビットと、アドレスを複数のメモリバンクの数に関連する数によって除算した場合の剰余とに基づいて、アドレスを複数のメモリバンクにおける特定のロケーションにマッピングするメモリコントローラと、受信アドレスの少なくとも一部を使用して特定のロケーションにアクセスする回路と、を備えるコンピュータシステムである。

【0018】

ここで、本発明のより完全な理解のために、添付図面とともに考慮する以下の説明を参考する。

【発明を実施するための最良の形態】

10

【0019】

本発明の実施形態は、メモリアドレス、たとえば物理アドレスを、 $2^N$  バンクを有するメモリシステムにマッピングするのが好ましい。 $2^N$  バンクの各々は、ほとんどの連続的なアドレスが異なるバンクにマッピングされるように $2^P$  メモリロケーションを有するのが好ましい。連続的なアドレスは、同じストライドに関するこを意味し、たとえば、ストライドが1である場合、連続的なアドレスは0、1、2、3、4等であり、ストライドが2である場合、連続的なアドレスは0、2、4、6、8等である。本発明の実施形態は、実施形態が1未満のクロックサイクルでマッピングを行うことができるようする組合せ回路を使用して実現されるのが好ましい。これにより、メモリ待ち時間が低く維持される。本発明の実施形態は、バンク競合なしに多くの異なるストライドに対して動作可能であり、そのためデータバスに対して高メモリ帯域幅を提供する。本発明の実施形態は、素数のメモリバンクを必要とせず、そのため市販のメモリシステムで動作し利用可能なメモリのすべてを使用する。

20

【0020】

なお、種々の実施態様において、メモリにアクセスするためにアドレスの最下位ビットを使用しない。本発明の実施形態の説明を簡略化するために、メインメモリにアクセスするためにアドレスのすべてのビットを使用する。しかしながら、当業者は、最下位ビットのいくつかは、キャッシュライン内のバイトを指定するため、メインメモリに対してアドレス指定するために必要のない場合があることを認めるであろう。さらなる情報を得るために、2002年6月11日に発行された、「METHOD AND APPARATUS FOR DETERMINING INTERLEAVING SCHEMES IN A COMPUTER SYSTEM THAT SUPPORTS MULTIPLE INTERLEAVING SCHEMES」と題された米国特許第6,405,286号と、2000年5月30日に発行された、「MAIN MEMORY BANK INDEXING SCHEME THAT OPTIMIZES CONSECUTIVE PAGE HITS BY LINKING MAIN MEMORY BANK ADDRESS ORGANIZATION TO CACHE MEMORY ADDRESS ORGANIZATION」と題された同第6,070,227号と、を参照のこと。

30

【0021】

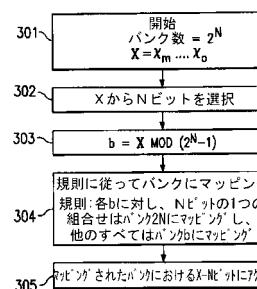

本発明の実施形態の動作に対する好ましい実施態様300を、図3に示す。本システムは、 $2^N$  バンクのSDRAMメモリを備え、ビットストリーム $X$ （ $X$ は、 $X_m, \dots, X_0$  からなる）を使用してシステム内のメモリロケーションにアドレス指定する。動作は301で開始し、メモリアドレス $X$ を含むメモリアクセス要求が受取られる。本発明の実施形態は、 $N$ ビット（ $N$ は、ビットストリームからの $2^N$  バンクの $N$ である）を読出す（302）。これらの $N$ ビットは、インターリーブビットとして既知であるのが好ましい。ビットストリームにおけるロケーションは、事前に確定されており、最下位ビットであるのが好ましい。しかしながら、他のビットを使用してもよい。さらに、 $N$ ビットは、ストリームに連続して位置していてもよく、あるいは互いに離れていてもよい。 $N$ ビットは、下位ビットであっても上位ビットであってもよく、もしくは幾つかの下位ビットと幾つかの上位ビットであってもよい。そして、本発明の実施形態は、 $X$ が $2^N - 1$ で除算された場合の剰余であるモジュラス(modulus)  $b$ を確定する（303）。これは、 $b = X \bmod 2^N - 1$ として表される。この演算を、ボックス302と並行して、それより前にまたは後に行ってもよい。そして、 $N$ ビットと $b$ とを使用して、アドレス $X$ がいずれのバンクにマッ

40

50

ピングされるかを確定する(304)。一般規則は、各  $b$  に対して、 $N$  ビットの 1 つの組合せがバンク  $2^N$  (または指定されたバンク) にマッピングし、他の組合せのすべてがバンク  $b$  にマッピングすることが好ましい。そして、読み出し、書き込みまたは他のメモリ動作のために、 $N$  ビットなしに  $X$  によって識別されるメモリロケーション(行および列アドレス)にアクセスすることができる(305)。なお、モジュラスは、2進数の場合 ( $X_m 2^m + \dots + X_0 2^0 \bmod 2^N - 1$ ) である。

#### 【0022】

図3の発明の実施形態の実施態様の例を、図4Aに示す。この実施例では、メモリシステムが4バンク、すなわちバンク0、バンク1、バンク2およびバンク3を有するものと仮定する。なお、バンクの数は、異なる数のバンクを使用することができるため、単に例示としてのものであることに留意されたい。このため、 $N = 2$  および  $b = X \bmod 3$  である。そして、 $b$  は、0、1および2のあり得る値の範囲を有する。インターリーブビットとして  $X$  の  $x_a$  および  $x_b$  を使用する。アドレス  $X$  をマッピングするために使用する規則は、以下の通りである。すなわち、1)  $b = 0$  でありかつ  $(x_a \ x_b) = (11)$  である場合、バンクはバンク3であり、2)  $b = 1$  でありかつ  $(x_a \ x_b) = (00)$  である場合、バンクはバンク3であり、3)  $b = 2$  でありかつ  $(x_a \ x_b) = (11)$  である場合、バンクはバンク3であり、4) それ以外のバンク = バンク  $b$  である。なお、他の規則を使用することができるため、これらの規則は単に例示としてのものであることに留意されたい。たとえば、バンク3がインターリーブビットの  $b = 0, 1, 2$  の特別な場合を受取る代りに、異なるバンク、たとえばバンク0を使用することができ、このため規則4は、それ以外のバンク = バンク  $b + 1$  となる。なお、 $b$  およびインターリーブビットの合計 12 の異なる場合または組合せがあり、各バンクは3つの異なる場合にマッピングされることに留意されたい。

#### 【0023】

図4Bは、図4Aの実施例が、合計32のメモリロケーションを有するメモリの4つのバンクでいかに動作するかを示す。ロケーションの数は、より多いロケーションも少ないロケーションも存在することができるため、単なる例示的なものである。典型的には、メモリシステムは、何千ものメモリロケーションを有する。したがって、メモリアドレスは、2進アドレス  $111111, 111110, \dots, 00001, 00000$  に対応する  $X = 31, 30, \dots, 1, 0$  である。なお、各2進アドレスは、 $x_4 x_3 x_2 x_1 x_0$  に対応する。インターリーブビットは、 $x_1 x_0$  であるように選択されるが、他のビット、たとえば  $x_3 x_2$  を使用することができるため、それらは単なる例として選択される。このため、 $X$  の残りのビット、すなわち  $x_4 x_3 x_2$  は、各バンクにおけるメモリロケーションアドレスに対して使用される。図4Cは、図4Bの実施例のレイアウトを示す。なお、各バンクは、7(111)から0(000)までのバンクアドレスを有し、ビット  $x_4 x_3 x_2$  は、各バンク内においてそのバンクアドレスを確定するために使用されることに留意されたい。さらに、バンク内のアドレスは、簡単のために複数の行を有する単一列として示すことも留意されたい。実際のメモリバンクは行および列のアレイからなり何千ものロケーションを有するため、アドレスビットは、行と列との両方の情報を有する。

#### 【0024】

図2Aないし図2Cを参照すると、ストライドが3バンクを使用する場合、Bの帯域幅があり、ストライドが2バンクを使用する場合、帯域幅は  $2B/3$  であり、ストライドが1バンクを使用する場合、帯域幅は  $B/3$  である。図2Aないし図2Cに示す例では、Bは  $12/13$  に等しい。図2Aにおいて、データバスにおけるD1までのサイクルは、第1の転送までの時間であるため、無視することができる。そして、データは、次の13サイクルのうちの12に対して転送され、このため帯域幅は  $12/13$  である。同様に、図2Bのストリームに対する帯域幅は  $8/13$  ( $2B/3$  である) であり、図2Cのストリームの場合は  $4/13$  ( $B/3$  である) である。このように、3または4バンクを使用して、最大(または略最大、 $12/13$ )を達成することができる。図4Aないし図4Cの実施例においてこれらの結果を使用することにより、1のストライドは4バンクにマッピ

10

20

30

40

50

ングし、2のストライドは3バンクにマッピングし、3のストライドは2バンクにマッピングし、4のストライドの1/4(たとえば、3、5、11、15、19、23)は、2バンクにマッピングする。4の残りのストライドは、3バンクにマッピングする。このため、図4Aないし図4Cに示す実施例に対する1~4のストライドの場合の平均帯域幅は、 $(B + B + 2B/3 + (1/4 \times 2B/3 + 3B/4)) / 4 = 43B/48 = .896B$ であり、最悪の場合は $2B/3$ である。なお、これらの計算は、たとえば4口ケーションのバッファを使用する、何らかの並べ替えを想定する。この並べ替えは、ランダムな連続的アクセスが同じバンクに向う機会を低減するために必要である。図2Aないし図2Cに示すストリームにより例証されるように、1または2バンクとは異なる3または4バンクを通してアクセスを循環させることがより適切である。

10

#### 【0025】

図4Cの帯域幅に対してさらに続けて説明する。1のストライドを、小さい並べ替えバッファを用いて、3つのバンクにマッピングすることができる。たとえば、0、1、2、3、4、5、6のアドレスストリームを考慮する。図4Cのマッピングを使用すると、メモリコントローラは、並べ替えなしに0、1、2、3をバンク0、1、2、3にマッピングする。しかしながら、アドレス4は、バンク3にマッピングし、バンク3はビジーである。このため、アドレス4がバッファリングされ、次のアドレス、すなわちアドレス5が考慮されるが、それもまたビジーである(この実施例の目的のために、ビジーバンクは、最近書込みがなされた2つのバンクである)。このため、アドレス5がバッファリングされ、次のアドレス、すなわちバンク0にマッピングされるビジーではないアドレス6が考慮される。ここで、バンク2はもはやビジーではないため、アドレス5がバンク2に送られる。次に、バンク3はもはやビジーではないため、アドレス4がバンク3に送られる。このように、受取られる順序は、0、1、2、3、4、5、6であり、送られる順序は、バンク0、1、2、3、0、2、3に対応する0、1、2、3、6、5、4である。少なくとも3バンクが使用中であるため、帯域幅は1のストライドの場合はBである。

20

#### 【0026】

2のストライドを有するストリーム、たとえばアドレス0、2、4、6、8、10のストリームを想定する。これは、並び替えなしにバンク0、2、3、0、2、1にマッピングする。少なくとも3つのバンクが使用中であるため、帯域幅は2のストライドの場合はBである。

30

#### 【0027】

3のストライドを有するストリーム、たとえばアドレス0、3、6、9、12、15、18、21、24、27等のストリームを想定する。これらは、バンク0、3、0、0、0、3、0、0、3に直接マッピングする。並び替えバッファを用いて、アドレスは、バンク0、3、0、3、0、3、0、3に対応する順序0、3、6、15、9、27、12等で発行される。2バンクが使用中であるため、帯域幅は、3のストライドの場合は $2/3B$ であり、それは図2Bのストリームの帯域幅と同様である。なお、パターンを並び替えることができる時間は、並び替えバッファの深さによって決まることに留意されたい。この実施例では、たとえば18、21および24を格納するために3の深さが必要である。さらに、一定のストライドは、典型的には長くは続かないことにも留意されたい。

40

#### 【0028】

4のストライドを有するストリーム、たとえばアドレス0、4、8、12のストリームが、バンク0、3、2、0にマッピングする(3バンクマッピング)ものとする。しかしながら、最悪の場合のストライド4ストリームは、たとえばアドレスシーケンス3、7、11、15、19、23である。このストリームは、バンク3、1、3、3、1、3にマッピングする。2バンクが使用中であるため、最悪の場合の帯域幅は、4のストライドに対して $2/3B$ である。

#### 【0029】

なお、本発明の実施形態に対する帯域幅の論考は、一定のストライドでのメモリアクセス要求の連続的なストリームに対して達成することができる最大帯域幅に対するものであ

50

る。本発明の実施形態を使用する実際に実現される帯域幅は、典型的には最大帯域幅より小さくなる。それは、実際のメモリアクセスパターンが、典型的には、連続的な一定のストライドより複雑であり、たとえば異なる長さの時間に対する異なるストライドかまたはストライドがまったくないためである。

【0030】

図5Aは、図4Aのものと同様の、本発明の実施形態の実施例を示し、図4Aのものとはわずかに異なる規則を有する。なお、アドレスXをマッピングするために使用する規則は、次のとおりである。すなわち、1)  $b = 0, 1$ または $2$ でありかつ $(x_a \times x_b) = (11)$ である場合、バンクはバンク $3$ であり、2) それ以外のバンク = バンク $b$ である。図5Bおよび図5Cに示すように、この変更により、図4Bおよび図4Cに示すものとは異なるマッピングとなる。これは正当なマッピングであるが、帯域幅は図4Aないし図4Cのものほど高くはない。図5Aないし図5Cのマッピングの場合、1~4のストライドに対する帯域幅は、 $((B + B + 2B / 3 + (1 / 4 \times B / 3 + 3 / 4 \times B)) / 4 = 42 / 48 = 0.875$  Bであり、最悪の場合のパフォーマンスは、単一バンク $3$ にマッピングするように、ストライド4アドレスシーケンス $3, 7, 11, 15, 19, 23, 27, 31$ に対する $1 / 3$  Bである。しかしながら、このマッピングは、従来技術より高い帯域幅を有する。図1BのLSBインターリービングの場合ストライド1~4の帯域幅は、ストライド1の場合はBであり(ストライド1は4バンクすべてを使用するため)、ストライド2の場合は $2B / 3$ であり(ストライド2は2つのバンクを使用するため、たとえば $0, 2, 4, 6, 8$ はバンク $0$ および $2$ を使用する)、ストライド3の場合はBであり(ストライド3は並び替えにより4つのバンクをすべて使用するため)、ストライド4の場合は $B / 3$ である(ストライド4は1つのバンクしか使用しないため)。このため、平均は、 $((B + 2B / 3 + B + B / 3) / 4 = 3 / 4 B = 0.75$  Bであり、最悪の場合は $B / 3$ である。

【0031】

なお、他の規則を使用することができるため、図4Aおよび図5Aに示す規則は単なる例示的なものであることに留意されたい。さらに、バンク内のアドレスは、簡単のために複数の行を有する单一列として示すことも留意されたい。実際のメモリバンクは行および列のアレイから構成され何千ものロケーションを有するため、アドレスビットは、行および列の両方の情報を有する。

【0032】

上述したように、本発明の実施形態は、異なる数、たとえば4以外のバンクを有するメモリシステムで動作することができる。8バンクのメモリ、すなわちバンク $0, 1, 2, 3, 4, 5, 6$ およびバンク $7$ を有する発明の実施形態の実施態様の例を、図6に示す。このため、 $N = 3$ および $b = X \bmod 7$ である。そして、 $b$ は、 $0 \sim 6$ のあり得る値の範囲を有する。インターリーブビットとして $X$ のビット $x_a \times x_b \times x_c$ が使用される。アドレスXをマッピングするために使用する規則は、次のとおりである。すなわち、1)  $b = 0, 2, 4$ または $6$ でありかつ $(x_a \times x_b \times x_c) = (111)$ である場合、バンクはバンク $7$ であり、2)  $b = 1, 3$ または $5$ でありかつ $(x_a \times x_b \times x_c) = (000)$ である場合、バンクはバンク $7$ であり、3) それ以外のバンク = バンク $b$ である。なお、 $b$ およびインターリーブビットには合計56の異なる場合または組合せがあり、各バンクは7つの異なる場合にマッピングされることに留意されたい。図6の場合のアドレスのバンクへのマッピングは、以下の通りである。

10

20

30

40

【表1】

| b 0 | b 1 | b 2 | b 3 | b 4 | b 5 | b 6 | b 7 |    |

|-----|-----|-----|-----|-----|-----|-----|-----|----|

| 0   | 1   | 2   | 3   | 4   | 5   | 6   | 7   |    |

| 1 4 | 1 5 | 9   | 1 0 | 1 1 | 1 2 | 1 3 | 8   |    |

| 2 1 | 2 2 | 1 6 | 1 7 | 1 8 | 1 9 | 2 0 | 2 3 |    |

| 2 8 | 2 9 | 3 0 | 3 1 | 2 5 | 2 6 | 2 7 | 2 4 |    |

| 3 5 | 3 6 | 3 7 | 3 8 | 3 2 | 3 3 | 3 4 | 3 9 |    |

| 4 2 | 4 3 | 4 4 | 4 5 | 4 6 | 4 7 | 4 1 | 4 0 |    |

| 4 9 | 5 0 | 5 1 | 5 2 | 5 3 | 5 4 | 4 8 | 5 5 |    |

| 5 6 | 5 7 | 5 8 | 5 9 | 6 0 | 6 1 | 6 2 | 6 3 | 10 |

| 7 0 | 7 1 | 6 5 | 6 6 | 6 7 | 6 8 | 6 9 | 6 4 |    |

## 【0033】

ストライド1～8のすべてに対して、アドレスは3つ以上のバンクにわたって分配される。ストライド7の場合、同じバンクに対して7つの連続したアクセスがある。たとえば、アドレスシーケンス14、21、28、35、42、49、56はすべて、バンク0にマッピングする。シーケンスにおける次のアドレス(63)は、異なるバンクにマッピングするが、シーケンスにおける続く7つのアドレスは、再びバンク0にマッピングする。ストライド7のシーケンスに対する帯域幅がB/3であるという控えめな想定を使用すると、最初の8ストライドにわたる平均帯域幅は、(7×B+B/3)/8=91.7%である。

20

## 【0034】

図7は、16バンクのメモリを用いる本発明の実施形態の実施態様の例を示す。この実施例では、N=4およびb=X mod 15である。そして、bは0～14のあり得る値の範囲を有する。インターリーブビットとしてXのビット $x_a \times b \times c \times d$ が使用される。アドレスXをマッピングするために使用される規則は、次の通りである。すなわち、1) b=0、…13または14でありかつ( $x_a \times b \times c \times d$ )=(1111)である場合、バンクはバンク15であり、それ以外のバンク=バンクbである。なお、bおよびインターリーブビットには合計240の異なる場合または組合せがあり、各バンクは、15の異なる場合に対してマッピングされることに留意されたい。

30

## 【0035】

なお、図7に示す実施例では、15(N=4)は素数ではなく、3および5の除数を有する合成数であることに留意されたい。 $2^N - 1$ のほとんどの低い値の数は素数であり、たとえば3(N=2)、7(N=3)、31(N=5)および127(N=7)は素数である。しかしながら、63(N=6)もまた素数ではなく、21、9、7および3の除数を有する合成数である。同様に、255(N=8)、511(N=9)、1023(N=10)、2047(N=11、23×89=2047)および4095(N=12)は、素数ではない。8191(N=13)は素数である。最初の26個の素数は、2、3、5、7、11、13、17、19、23、29、31、37、41、43、47、53、59、61、67、71、73、79、83、89、97、101である。より大きい数は、目下、2つの理由で重要ではない。第1に、現標準メモリは、典型的には4または8バンクを使用するためである。第2に、3より大きいNに対し、翻訳をクロックサイクル内で行うことは目下困難であるためである。

40

## 【0036】

$\bmod$ 式における除数は、素数、たとえば3または7であるのが好ましい。そうでない場合、因数、同様に因数の倍数に等しいストライドで、バンク競合が発生する。このため、15の場合、3、5と同様に6、9、12等(3の倍数)および10、15等(5の倍数)のストライドでバンク競合が発生する。これにより、本発明の実施形態のパフォーマンスが図1Bの構成のパフォーマンスまで低減する。これは許容可能でないため、バンクを合せてグループ化することにより少ない数の「より大きい」バンクを形成することができる。言換れば、たとえば、16バンクを対で合せてグループ化することにより、8つ

50

の等しいサイズのより大きいバンクを形成することができる。これにより、バンクの数が、 $2^N - 1$  が素数であるように、すなわち  $n = 3$  または  $m \bmod 7$  であるようなレベルまで低減する。この低減はまた、他の非素数のいずれをも素数まで低減するように作用する。そして、追加のビットを使用して、各大きいバンク内の特定の小さいバンクを選択することができる。この構成の実施例を図 8 に示す。なお、バンク 0 および 1、2 および 3、4 および 5、6 および 7、8 および 9、10 および 11、12 および 13 ならびに 14 および 15 は、互いに対にされることにより、その対の両バンクに同じモジュラス  $b$  が適用されるようにされている。ビットシーケンスにおける第 1 のビット 801 を使用して、バンクの対のバンク間で選択がなされる。代替的に、バンクを 8 バンクからなる 2 つのグループに分割することができ、ビットを使用して 2 つのグループ間で選択することができる。なお、16 もまた 4 からなる 4 つのグループに分割してもよく、2 つのビットを使用してそれらの間で検出してもよく、たとえば、 $n = 2$  または  $m \bmod 3$  であることに留意されたい。

10

### 【0037】

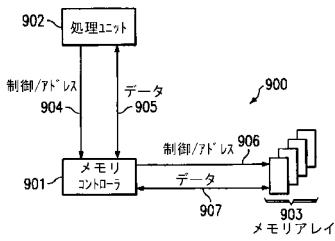

図 9 は、本発明の実施形態を有するメモリコントローラ 901 の実施例を示す。メモリコントローラ 901 は、コマンドバス 904 を介してプロセッサユニット 902 からメモリアクセス要求を受取る。なお、コンピュータシステム 900 は複数のプロセッサユニットを含んでもよいことに留意されたい。メモリアクセス要求は、アドレスおよび制御情報を含む。制御情報は、アクセス要求が読み出し動作、書き込み動作、それらの組合せまたは他のメモリ機能に対するものであることを指定してもよい。アクセスがメモリ 903 に対するデータの書き込みを含む場合、プロセッサは、データバス 905 にデータを送出してもよい。メモリコントローラ 901 は、上述した発明および図 3 ないし図 8 に示す発明の実施形態に従って、要求におけるアドレスを SDRAM メモリバンク 903 内のメモリロケーションにマッピングする。メモリコントローラは、制御情報とマッピングされたアドレスとをコマンドバス 906 を介してメモリバンク 903 に転送し、書き込み動作のためのデータがある場合、そのデータはデータバス 907 を介してメモリバンク 903 に提供される。そして、メモリバンク 903 は、マッピングされたメモリロケーションによって指定される制御情報を処理する。アクセスが読み出し動作を含む場合、マッピングされたメモリロケーションからデータが読み出され、それが、データバス 907、コントローラ 901 およびデータバス 905 を介して処理ユニット 902 に再び提供される。1 処理ユニットしかない場合、データバス 907 は、処理ユニット 902 に直接連結してもよい。多重処理ユニットシステムでは、メモリコントローラ（または別の構造）は、要求側処理ユニットに戻るデータの流れを制御する。なお、メモリコントローラ 901 は、図 9 に示すような別々のユニットではなくプロセッサユニット 902 の一部であってもよいことに留意されたい。

20

30

### 【0038】

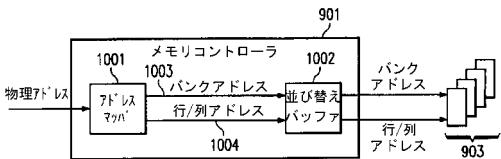

図 10 は、図 9 のメモリコントローラ 901 の構成の実施例を示す。メモリコントローラは、アドレス、たとえば物理アドレスを受取りその物理アドレスをメモリバンク 903 にマッピングするアドレスマッパー（address mapper）1001 を有する。アドレスマッパー 1001 は、行／列アドレスとして表してもよいバンクアドレス 1003 とメモリロケーションアドレス 1004 とを提供する。メモリコントローラは、別の保留中のメモリアクセス要求と競合するアドレス情報に対する並び替えバッファ 1002 を含むのが好ましい。並び替えバッファは、同じバンクにマッピングするストライドの短いバーストからの、同じバンクへのランダムな連続的アドレスから発生する帯域幅損失を低減する。競合が取除かれると、アドレス情報がリリースされるかまたはメモリバンクに対して発行される。

40

### 【0039】

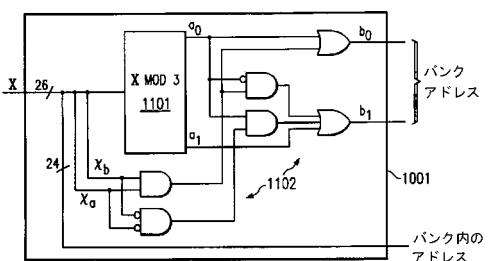

図 11A は、図 10 のアドレスマッパー 1001 の構成の実施例を示す。アドレスマッパー 1001 は、アドレス X に対しモジュラス関数を実行するロジックまたは回路 1101 と、回路 1101 の結果とアドレス X の一部とに基づいてバンクアドレスを確定するロジックまたは回路 1102 と、を含む。アドレスマッパー 1001 は、アドレス X から、バンク

50

内のロケーションアドレスであるメモリロケーションアドレスを形成する。メモリロケーションアドレスは、行／列アドレスの形態であってもよい。図11Bは、回路1102の出力を示す表である。回路1102は、図4Aにおいて提供する規則に従って動作するよう設定される。 $a_1 a_0 = 00$ 、 $01$ および $10$ の行は、それぞれ $0$ 、 $1$ および $2$ の剩余に対応する。このため、 $a_1 a_0 = 00$ を意味する $b = 0$ およびビット $x_a \times b = 11$ の場合、バンク3が選択され、そのため出力 $b_0 b_1 = 11$ （3に対応）となる。なお、図11Bに示すものと同じ規則かまたは異なる規則を形成するために他の回路を使用することができるため、この回路は単なる例示的なものであることに留意されたい。

#### 【0040】

なお、従来技術において、 $n = 2^m - 1$ である場合（ $n$ が $2^n$ の累乗でない場合）、 $X \bmod n$ の計算がより容易であることは既知である。ブロック1101は、 $n = 2^m - 1$ 、たとえば $n = 3$ である場合の $X \bmod n$ を計算する。なお、 $1) 2^0 \bmod 3 = 1$ 、 $2^1 \bmod 3 = 2$ 、 $2^2 \bmod 3 = 1$ 、 $2^3 \bmod 3 = 2$ 等であることに留意されたい。 $2) X = x_0 \times 2^0 + x_1 \times 2^1 + x_2 \times 2^2 + \dots + x_p \times 2^p$ であることに留意されたい。 $(a + b) \bmod c = (a \bmod c) + (b \bmod c)$ であるため、 $2)$ および $3)$ から、 $X \bmod n = (x_0 \times 2^0 \bmod n) + (x_1 \times 2^1 \bmod n) + (x_2 \times 2^2 \bmod n) + \dots + (x_p \times 2^p \bmod n)$ であり、それは、 $1)$ から、 $X \bmod 3 = ((x_0 + x_2 + x_4 + \dots) \times 1 + (x_1 + x_3 + x_5 + \dots) \times 2) \bmod 3$ に等しいことに留意されたい。 $X$ が32ビット、すなわち $x_0 \sim x_{31}$ を有するものと仮定する。そして、先の式から、Aが $0 \sim 16$ の数であり、Bが32までの偶数である場合、 $X \bmod n = A + B \bmod 3$ である。そのため、Cが $0 \sim 48$ の範囲であり、 $C = x_0 + x_2 + \dots + x_{30} + 2 \times (x_1 + x_3 + \dots + x_{31})$ である場合、 $X \bmod 3 = C \bmod n$ である。数 $0 \sim 48$ を表すために6つの2進数、すなわち $c_0 \sim c_5$ のみを要するため、Cに対して同じ手続きを繰返すことができる。すなわち、 $X \bmod 3 = c_0 + c_2 + c_4) \bmod 3 + (c_1 + c_3 + c_5) \times 2 \bmod 3$ である。これを、ハードウェアで直接計算することができる。

#### 【0041】

なお、その実施例で剩余は $0 \sim 2$ の範囲をとるため、3の剩余に対応する $a_1 a_0 = 11$ に対するデータの行はないことに留意されたい。さらに、 $a_1 a_0 = 11$ はブロック1101の正当な出力ではないため、図11Bにおいて、表におけるこれらのエントリをドントケア（d.c.）として使用することにより、 $b_0$ および $b_1$ に対する式を低減することができることに留意されたい。図示する式は、これらのドントケア行における $b_1$ および $b_0$ に対してすべて1を選択することに対応する。

#### 【0042】

本発明の実施形態を、SDRAMメモリに関して上に説明した。しかしながら、本発明の他の実施形態は、DRAMメモリ、RAMメモリ、ROMメモリ、DDRメモリ、RAMBUSメモリ、キャッシュメモリもしくはブロックまたはバンクに編成される他の任意のタイプのメモリで作用してもよい。

#### 【0043】

また、本発明の実施形態を、メモリに関して上に説明した。しかしながら、本発明の他の実施形態は、ブロックに編成される他の任意のデバイスで作用してもよい。たとえば、大規模コンピュータシステムにおいて、アービトレータは、異なる処理ユニット間でタスクを分割する際に本発明の実施形態を使用することができ、それによりレイテンシを低減しシステムにおける帯域幅を増大させることができる。

#### 【0044】

本発明の実施形態は、好ましくは、チップに形成されるロジックおよび／または回路として実装され、本明細書で説明した本発明の実施形態の要素を行うように設計される。しかしながら、本発明の他の実施形態を、ソフトウェアで実装してもよい。ソフトウェアで実装される場合、本発明の実施形態の要素は、本質的に、必要なタスクを実行するコードセグメントである。プログラムまたはコードセグメントを、プロセッサ読取可能媒体に格

納するか、あるいは搬送波で具体化されるコンピュータデータ信号かまたは搬送波で変調される信号により、伝送媒体を介して伝送することができる。「プロセッサ読取可能媒体」は、情報を格納するかまたは転送することができるいかなる媒体も含んでよい。プロセッサ読取可能媒体の例には、電子回路、半導体メモリデバイス、ROM、フラッシュメモリ、消去可能ROM(EROM)、フロッピーディスク、コンパクトディスクCD-ROM、光ディスク、ハードディスク、光ファイバ媒体、無線周波数(RF)リンク等が含まれる。コンピュータデータ信号には、電子ネットワークチャネル、光ファイバ、空気、電磁気、RFリンク等の伝送媒体によって伝播することができるいかなる信号も含まれてよい。コードセグメントを、インターネット、イントラネット等のコンピュータネットワークを介してダウンロードしてもよい。

10

## 【図面の簡単な説明】

## 【0045】

【図1A】SDRAMの従来技術の構成の図。

【図1B】SDRAMの従来技術の構成の図。

【図2A】データバスに対するインターリービングの効果を示す一連のタイミング図。

【図2B】データバスに対するインターリービングの効果を示す一連のタイミング図。

【図2C】データバスに対するインターリービングの効果を示す一連のタイミング図。

【図3】本発明の実施形態のフローチャートの例。

【図4A】4バンクメモリシステムによる本発明の実施形態の例の図。

20

【図4B】4バンクメモリシステムによる本発明の実施形態の例の図。

【図4C】4バンクメモリシステムによる本発明の実施形態の例の図。

【図5A】図4Aないし図4Cの発明の代替実施形態の図。

【図5B】図4Aないし図4Cの発明の代替実施形態の図。

【図5C】図4Aないし図4Cの発明の代替実施形態の図。

【図6】8バンクメモリシステムによる本発明の実施形態の例の図。

【図7】16バンクメモリシステムによる本発明の実施形態の例の図。

【図8】16バンクメモリシステムによる本発明の異なる実施形態の例の図。

【図9】本発明の実施形態を使用するメモリコントローラの例の図。

【図10】図9のメモリコントローラの例の図。

30

【図11A】図10のメモリコントローラにあるアドレスマッパーの例の図。

【図11B】図10のメモリコントローラにあるアドレスマッパーの例の図。

## 【符号の説明】

## 【0046】

## 901 メモリコントローラ

1001 受信アドレスの少なくとも一部を使用して特定バンク内のメモリロケーションを確定する回路

## 1002 並び替えバッファ

1101 受信アドレスを、バンクの数に基づく除数によって除算した際の剰余を計算する回路

1102 剰余と受信アドレスの少なくとも1ビットとにに基づいて複数のバンクのうち特定バンクを確定する回路

40

【図 1 A】

【図1B】

| パンク 0 | パンク 1 | パンク 2 | パンク 3 |

|-------|-------|-------|-------|

| 0     | 1     | 2     | 3     |

| 4     | 5     | 6     | 7     |

| 8     | 9     | 10    | 11    |

| 12    | 13    | 14    | 15    |

| 16    | 17    | 18    | 19    |

| 20    | 21    | 22    | 23    |

| 24    | 25    | 26    | 27    |

| 28    | 29    | 30    | 31    |

## 【図2A】

## 【図2B】

### 【図2C】

### 【圖 3】

【図 4 A】

| <u>BANK 0</u> | <u>BANK 1</u> | <u>BANK 2</u> | <u>BANK 3</u> |

|---------------|---------------|---------------|---------------|

| b=0 (00)      | b=1 (01)      | b=2 (00)      | b=0 (11)      |

| b=0 (01)      | b=1 (10)      | b=2 (01)      | b=1 (00)      |

| b=0 (10)      | b=1 (11)      | b=2 (10)      | b=2 (11)      |

b = X MOD 3

NUMBER BANKS =  $2^N = 4$

$X = X_m \dots X_0$

$(X_a, X_b) \Sigma X$

**RULES:**

IF b=0 AND  $(X_a, X_b) = (1,1)$  THEN BANK = BANK 3

IF b=1 AND  $(X_a, X_b) = (0,0)$  THEN BANK = BANK 3

IF b=2 AND  $(X_a, X_b) = (1,1)$  THEN BANK = BANK 3

ELSE BANK = BANK b

〔図4B〕

| アドレス | 2進アドレス<br>$X_4X_3X_2X_1X_0$ | MOD | パンク | パンクアドレス<br>$X_4X_3X_2$ |

|------|-----------------------------|-----|-----|------------------------|

| 0    | 00000                       | 0   | 0   | 0                      |

| 1    | 00001                       | 1   | 1   | 0                      |

| 2    | 00010                       | 2   | 2   | 0                      |

| 3    | 00011                       | 0   | 3   | 0                      |

| 4    | 00100                       | 1   | 3   | 1                      |

| 5    | 00101                       | 2   | 2   | 1                      |

| 6    | 00110                       | 0   | 0   | 1                      |

| 7    | 00111                       | 1   | 1   | 1                      |

| 8    | 01000                       | 2   | 2   | 2                      |

| 9    | 01001                       | 0   | 0   | 2                      |

| 10   | 01010                       | 1   | 1   | 2                      |

| 11   | 01011                       | 2   | 3   | 2                      |

| 12   | 01100                       | 0   | 0   | 3                      |

| 13   | 01101                       | 1   | 1   | 3                      |

| 14   | 01110                       | 2   | 2   | 3                      |

| 15   | 01111                       | 0   | 3   | 3                      |

| 16   | 10000                       | 1   | 3   | 4                      |

| 17   | 10001                       | 2   | 2   | 4                      |

| 18   | 10010                       | 0   | 0   | 4                      |

| 19   | 10011                       | 1   | 1   | 4                      |

| 20   | 10100                       | 2   | 2   | 5                      |

| 21   | 10101                       | 0   | 0   | 5                      |

| 22   | 10110                       | 1   | 1   | 5                      |

| 23   | 10111                       | 2   | 3   | 5                      |

| 24   | 11000                       | 0   | 0   | 6                      |

| 25   | 11001                       | 1   | 1   | 6                      |

| 26   | 11010                       | 2   | 2   | 6                      |

| 27   | 11011                       | 0   | 3   | 6                      |

| 28   | 11100                       | 1   | 3   | 7                      |

| 29   | 11101                       | 2   | 2   | 7                      |

| 30   | 11110                       | 0   | 0   | 7                      |

| 31   | 11111                       | 1   | 1   | 7                      |

【図4C】

| バンクアドレス | バンク0 | バンク1 | バンク2 | バンク3 |

|---------|------|------|------|------|

| 0       | 0    | 1    | 2    | 3    |

| 1       | 6    | 7    | 5    | 4    |

| 2       | 9    | 10   | 8    | 11   |

| 3       | 12   | 13   | 14   | 15   |

| 4       | 18   | 19   | 17   | 16   |

| 5       | 21   | 22   | 20   | 23   |

| 6       | 24   | 25   | 26   | 27   |

| 7       | 30   | 31   | 29   | 28   |

【図5A】

| BANK 0                                                 | BANK 1   | BANK 2   | BANK 3   |

|--------------------------------------------------------|----------|----------|----------|

| b=0 (00)                                               | b=1 (00) | b=2 (00) | b=0 (11) |

| b=0 (01)                                               | b=1 (01) | b=2 (01) | b=1 (11) |

| b=0 (10)                                               | b=1 (10) | b=2 (10) | b=2 (11) |

| b = X MOD 3                                            |          |          |          |

| NUMBER BANKS = $2^N = 4$                               |          |          |          |

| X = $X_m \dots X_0$                                    |          |          |          |

| $(X_a, X_b) \Sigma X$                                  |          |          |          |

| RULES:                                                 |          |          |          |

| IF b=0,1,2 AND $(X_a, X_b) = (1,1)$ THEN BANK = BANK 3 |          |          |          |

| ELSE BANK = BANK b                                     |          |          |          |

【図5B】

| アドレス | 2進トレス X <sub>4</sub> X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub> | MOD | バンク X <sub>4</sub> X <sub>3</sub> X <sub>2</sub> |

|------|----------------------------------------------------------------------------------|-----|--------------------------------------------------|

| 0    | 00000                                                                            | 0   | 0                                                |

| 1    | 00001                                                                            | 1   | 1                                                |

| 2    | 00010                                                                            | 2   | 2                                                |

| 3    | 00011                                                                            | 0   | 3                                                |

| 4    | 00100                                                                            | 1   | 1                                                |

| 5    | 00101                                                                            | 2   | 2                                                |

| 6    | 00110                                                                            | 0   | 0                                                |

| 7    | 00111                                                                            | 1   | 3                                                |

| 8    | 01000                                                                            | 2   | 2                                                |

| 9    | 01001                                                                            | 0   | 0                                                |

| 10   | 01010                                                                            | 1   | 1                                                |

| 11   | 01011                                                                            | 2   | 3                                                |

| 12   | 01100                                                                            | 0   | 0                                                |

| 13   | 01101                                                                            | 1   | 1                                                |

| 14   | 01110                                                                            | 2   | 2                                                |

| 15   | 01111                                                                            | 0   | 3                                                |

| 16   | 10000                                                                            | 1   | 1                                                |

| 17   | 10001                                                                            | 2   | 2                                                |

| 18   | 10010                                                                            | 0   | 0                                                |

| 19   | 10011                                                                            | 1   | 3                                                |

| 20   | 10100                                                                            | 2   | 2                                                |

| 21   | 10101                                                                            | 0   | 0                                                |

| 22   | 10110                                                                            | 1   | 1                                                |

| 23   | 10111                                                                            | 2   | 3                                                |

| 24   | 11000                                                                            | 0   | 0                                                |

| 25   | 11001                                                                            | 1   | 1                                                |

| 26   | 11010                                                                            | 2   | 2                                                |

| 27   | 11011                                                                            | 0   | 3                                                |

| 28   | 11100                                                                            | 1   | 1                                                |

| 29   | 11101                                                                            | 2   | 2                                                |

| 30   | 11110                                                                            | 0   | 0                                                |

| 31   | 11111                                                                            | 1   | 3                                                |

【図5C】

| バンクアドレス | バンク0 | バンク1 | バンク2 | バンク3 |

|---------|------|------|------|------|

| 0       | 0    | 1    | 2    | 3    |

| 1       | 6    | 4    | 5    | 7    |

| 2       | 9    | 10   | 8    | 11   |

| 3       | 12   | 13   | 14   | 15   |

| 4       | 18   | 16   | 17   | 19   |

| 5       | 21   | 22   | 20   | 23   |

| 6       | 24   | 25   | 26   | 27   |

| 7       | 30   | 28   | 29   | 31   |

【図6】

| BANK 0                                                              | BANK 1    | BANK 2    | BANK 3    |

|---------------------------------------------------------------------|-----------|-----------|-----------|

| b=0 (000)                                                           | b=1 (001) | b=2 (000) | b=3 (001) |

| b=0 (001)                                                           | b=1 (010) | b=2 (001) | b=3 (010) |

| b=0 (010)                                                           | b=1 (011) | b=2 (010) | b=3 (011) |

| b=0 (011)                                                           | b=1 (100) | b=2 (011) | b=3 (100) |

| b=0 (100)                                                           | b=1 (101) | b=2 (100) | b=3 (101) |

| b=0 (101)                                                           | b=1 (110) | b=2 (101) | b=3 (110) |

| b=0 (110)                                                           | b=1 (111) | b=2 (110) | b=3 (111) |

| BANK 4                                                              |           |           |           |

| b=4 (000)                                                           | b=5 (001) | b=6 (000) | b=0 (111) |

| b=4 (001)                                                           | b=5 (010) | b=6 (001) | b=1 (000) |

| b=4 (010)                                                           | b=5 (011) | b=6 (010) | b=2 (111) |

| b=4 (011)                                                           | b=5 (100) | b=6 (011) | b=3 (000) |

| b=4 (100)                                                           | b=5 (101) | b=6 (100) | b=4 (111) |

| b=4 (101)                                                           | b=5 (110) | b=6 (101) | b=5 (000) |

| b=4 (110)                                                           | b=5 (111) | b=6 (110) | b=6 (111) |

| b = X MOD 7                                                         |           |           |           |

| NUMBER BANKS = $2^N = 8$                                            |           |           |           |

| X = $X_m \dots X_0$                                                 |           |           |           |

| $(X_a, X_b, X_c) \Sigma X$                                          |           |           |           |

| RULES:                                                              |           |           |           |

| IF b=0, 2, 4, OR 6 AND $(X_a, X_b, X_c) = (111)$ THEN BANK = BANK 7 |           |           |           |

| IF b=1, 3, OR 5 AND $(X_a, X_b, X_c) = (000)$ THEN BANK = BANK 7    |           |           |           |

| ELSE BANK = BANK b                                                  |           |           |           |

【図7】

| BANK 7    | BANK 5    | BANK 6     | BANK 7     |

|-----------|-----------|------------|------------|

| b=7 00000 | b=6 00000 | b=7 00000  | b=7 00000  |

| b=7 00001 | b=6 00001 | b=7 00001  | b=7 00001  |

| b=7 00010 | b=6 00010 | b=7 00010  | b=7 00010  |

| b=7 00011 | b=6 00011 | b=7 00011  | b=7 00011  |

| b=7 00100 | b=6 00100 | b=7 00100  | b=7 00100  |

| b=7 00101 | b=6 00101 | b=7 00101  | b=7 00101  |

| b=7 00110 | b=6 00110 | b=7 00110  | b=7 00110  |

| b=7 00111 | b=6 00111 | b=7 00111  | b=7 00111  |

| b=7 01000 | b=6 01000 | b=7 01000  | b=7 01000  |

| b=7 01001 | b=6 01001 | b=7 01001  | b=7 01001  |

| b=7 01010 | b=6 01010 | b=7 01010  | b=7 01010  |

| b=7 01011 | b=6 01011 | b=7 01011  | b=7 01011  |

| b=7 01100 | b=6 01100 | b=7 01100  | b=7 01100  |

| b=7 01101 | b=6 01101 | b=7 01101  | b=7 01101  |

| b=7 01110 | b=6 01110 | b=7 01110  | b=7 01110  |

| b=7 01111 | b=6 01111 | b=7 01111  | b=7 01111  |

| b=7 10000 | b=6 10000 | b=7 10000  | b=7 10000  |

| b=7 10001 | b=6 10001 | b=7 10001  | b=7 10001  |

| b=7 10010 | b=6 10010 | b=7 10010  | b=7 10010  |

| b=7 10011 | b=6 10011 | b=7 10011  | b=7 10011  |

| b=7 10100 | b=6 10100 | b=7 10100  | b=7 10100  |

| b=7 10101 | b=6 10101 | b=7 10101  | b=7 10101  |

| b=7 10110 | b=6 10110 | b=7 10110  | b=7 10110  |

| b=7 10111 | b=6 10111 | b=7 10111  | b=7 10111  |

| b=7 11000 | b=6 11000 | b=7 11000  | b=7 11000  |

| b=7 11001 | b=6 11001 | b=7 11001  | b=7 11001  |

| b=7 11010 | b=6 11010 | b=7 11010  | b=7 11010  |

| b=7 11011 | b=6 11011 | b=7 11011  | b=7 11011  |

| b=7 11100 | b=6 11100 | b=7 11100  | b=7 11100  |

| b=7 11101 | b=6 11101 | b=7 11101  | b=7 11101  |

| b=7 11110 | b=6 11110 | b=7 11110  | b=7 11110  |

| b=7 11111 | b=6 11111 | b=7 11111  | b=7 11111  |

| b=8 00000 | b=9 00000 | b=10 00000 | b=11 00000 |

| b=8 00001 | b=9 00001 | b=10 00001 | b=11 00001 |

| b=8 00010 | b=9 00010 | b=10 00010 | b=11 00010 |

| b=8 00011 | b=9 00011 | b=10 00011 | b=11 00011 |

| b=8 00100 | b=9 00100 | b=10 00100 | b=11 00100 |

| b=8 00101 | b=9 00101 | b=10 00101 | b=11 00101 |

| b=8 00110 | b=9 00110 | b=10 00110 | b=11 00110 |

| b=8 00111 | b=9 00111 | b=10 00111 | b=11 00111 |

| b=8 01000 | b=9 01000 | b=10 01000 | b=11 01000 |

| b=8 01001 | b=9 01001 | b=10 01001 | b=11 01001 |

| b=8 01010 | b=9 01010 | b=10 01010 | b=11 01010 |

| b=8 01011 | b=9 01011 | b=10 01011 | b=11 01011 |

| b=8 01100 | b=9 01100 | b=10 01100 | b=11 01100 |

| b=8 01101 | b=9 01101 | b=10 01101 | b=11 01101 |

| b=8 01110 | b=9 01110 | b=10 01110 | b=11 01110 |

| b=8 01111 | b=9 01111 | b=10 01111 | b=11 01111 |

| b=8 10000 | b=9 10000 | b=10 10000 | b=11 10000 |

| b=8 10001 | b=9 10001 | b=10 10001 | b=11 10001 |

| b=8 10010 | b=9 10010 | b=10 10010 | b=11 10010 |

| b=8 10011 | b=9 10011 | b=10 10011 | b=11 10011 |

| b=8 10100 | b=9 10100 | b=10 10100 | b=11 10100 |

| b=8 10101 | b=9 10101 | b=10 10101 | b=11 10101 |

| b=8 10110 | b=9 10110 | b=10 10110 | b=11 10110 |

| b=8 10111 | b=9 10111 | b=10 10111 | b=11 10111 |

| b=8 11000 | b=9 11000 | b=10 11000 | b=11 11000 |

| b=8 11001 | b=9 11001 | b=10 11001 | b=11 11001 |

| b=8 11010 | b=9 11010 | b=10 11010 | b=11 11010 |

| b=8 11011 | b=9 11011 | b=10 11011 | b=11 11011 |

| b=8 11100 | b=9 11100 | b=10 11100 | b=11 11100 |

| b=8 11101 | b=9 11101 | b=10 11101 | b=11 11101 |

| b=8 11110 | b=9 11110 | b=10 11110 | b=11 11110 |

| b=8 11111 | b=9 11111 | b=10 11111 | b=11 11111 |

【図8】

| BANK 1 |           | BANK 2      |             | BANK 3      |             | BANK 4      |             | BANK 5      |             | BANK 6      |             | BANK 7      |             |             |

|--------|-----------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| b=0    | 0 0 0 0 0 | b=0 1 0 0 0 | b=1 0 0 0 0 | b=1 1 0 0 0 | b=2 0 0 0 0 | b=2 1 0 0 0 | b=3 0 0 0 0 | b=3 1 0 0 0 | b=3 0 0 0 1 | b=3 1 0 0 1 | b=3 0 0 1 0 | b=3 1 0 1 0 | b=3 0 0 1 1 | b=3 1 0 1 1 |

| b=0    | 0 0 0 0 1 | b=0 1 0 0 1 | b=1 0 0 0 1 | b=1 1 0 0 1 | b=2 0 0 0 1 | b=2 1 0 0 1 | b=3 0 0 0 1 | b=3 1 0 0 1 | b=3 0 0 1 0 | b=3 1 0 1 0 | b=3 0 0 1 1 | b=3 1 0 1 1 | b=3 0 1 0 1 | b=3 1 1 0 1 |

| b=0    | 0 0 0 1 0 | b=0 1 0 1 0 | b=1 0 0 1 0 | b=1 1 0 1 0 | b=2 0 0 1 0 | b=2 1 0 1 0 | b=3 0 0 1 0 | b=3 1 0 1 0 | b=3 0 1 0 0 | b=3 1 1 0 0 | b=3 0 1 0 1 | b=3 1 1 0 1 | b=3 0 1 1 0 | b=3 1 1 1 0 |

| b=0    | 0 0 0 1 1 | b=0 1 0 1 1 | b=1 0 0 1 1 | b=1 1 0 1 1 | b=2 0 0 1 1 | b=2 1 0 1 1 | b=3 0 0 1 1 | b=3 1 0 1 1 | b=3 0 1 0 1 | b=3 1 1 0 1 | b=3 0 1 1 0 | b=3 1 1 1 0 | b=3 0 1 1 1 | b=3 1 1 1 1 |

| b=0    | 0 0 1 0 0 | b=0 1 1 0 0 | b=1 0 1 0 0 | b=1 1 1 0 0 | b=2 0 1 0 0 | b=2 1 1 0 0 | b=3 0 1 0 0 | b=3 1 1 0 0 | b=3 0 1 0 1 | b=3 1 1 0 1 | b=3 0 1 1 0 | b=3 1 1 1 0 | b=3 0 1 1 1 | b=3 1 1 1 1 |

| b=0    | 0 0 1 0 1 | b=0 1 1 0 1 | b=1 0 1 0 1 | b=1 1 1 0 1 | b=2 0 1 0 1 | b=2 1 1 0 1 | b=3 0 1 0 1 | b=3 1 1 0 1 | b=3 0 1 1 0 | b=3 1 1 1 0 | b=3 0 1 1 1 | b=3 1 1 1 1 | b=3 0 1 1 0 | b=3 1 1 1 0 |

| b=0    | 0 0 1 1 0 | b=0 1 1 1 0 | b=1 0 1 1 0 | b=1 1 1 1 0 | b=2 0 1 1 0 | b=2 1 1 1 0 | b=3 0 1 1 0 | b=3 1 1 1 0 | b=3 0 1 1 1 | b=3 1 1 1 1 | b=3 0 1 1 0 | b=3 1 1 1 0 | b=3 0 1 1 1 | b=3 1 1 1 1 |

| b=0    | 0 0 1 1 1 | b=0 1 1 1 1 | b=1 0 1 1 1 | b=1 1 1 1 1 | b=2 0 1 1 1 | b=2 1 1 1 1 | b=3 0 1 1 1 | b=3 1 1 1 1 | b=3 0 1 1 0 | b=3 1 1 1 0 | b=3 0 1 1 1 | b=3 1 1 1 1 | b=3 0 1 1 0 | b=3 1 1 1 0 |

| b=1    | 1 1 1 1 1 | 1 1 1 1 1   | 1 1 1 1 1   | 1 1 1 1 1   | 1 1 1 1 1   | 1 1 1 1 1   | 1 1 1 1 1   | 1 1 1 1 1   | 1 1 1 1 1   | 1 1 1 1 1   | 1 1 1 1 1   | 1 1 1 1 1   | 1 1 1 1 1   | 1 1 1 1 1   |

【図11B】

| a <sub>1</sub> a <sub>0</sub> |             | X <sub>a</sub> X <sub>b</sub> |             | a <sub>1</sub> a <sub>0</sub> |             | X <sub>a</sub> X <sub>b</sub> |             |

|-------------------------------|-------------|-------------------------------|-------------|-------------------------------|-------------|-------------------------------|-------------|

| 00                            | 0 0 1 1 1 0 | 00                            | 0 0 1 0 0 0 | 00                            | 0 0 1 1 1 0 | 00                            | 0 0 1 0 0 0 |

| 01                            | 1 0 0 0 0 0 | 01                            | 1 1 1 1 1 1 | 01                            | 1 1 1 1 1 1 | 01                            | 1 1 1 1 1 1 |

| 11                            | dc dc dc dc |

| 10                            | 1 1 1 1     | 10                            | 0 0 1 1 0 0 | 10                            | 0 0 1 1 0 0 | 10                            | 0 0 1 1 0 0 |

b<sub>1</sub> = a<sub>1</sub> + a<sub>0</sub>X<sub>b</sub>'X<sub>a</sub>' + a<sub>0</sub>'X<sub>b</sub>X<sub>a</sub>

b<sub>0</sub> = a<sub>0</sub> + X<sub>b</sub>X<sub>a</sub>

【図9】

【図10】

【図11A】

---

フロントページの続き

(74)代理人 100111969

弁理士 平野 ゆかり

(72)発明者 マーク・エイ・ヒーブ

アメリカ合衆国 9 4 0 8 7 カリフォルニア州サンーヴェール、マネット・テラス 561

審査官 多賀 実

(56)参考文献 特開昭60-176153 (JP, A)

特開平05-210579 (JP, A)

特開昭62-065148 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 12 / 06

G 11 C 7 / 00