(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5528662号

(P5528662)

(45) 発行日 平成26年6月25日(2014.6.25)

(24) 登録日 平成26年4月25日(2014.4.25)

|               |              |

|---------------|--------------|

| (51) Int.Cl.  | F 1          |

| HO 1 L 21/822 | (2006.01)    |

| HO 1 L 27/04  | (2006.01)    |

| HO 1 L 21/82  | (2006.01)    |

|               | HO 1 L 27/04 |

|               | HO 1 L 21/82 |

|               | HO 1 L 21/82 |

請求項の数 13 (全 23 頁)

|           |                               |           |                                                       |

|-----------|-------------------------------|-----------|-------------------------------------------------------|

| (21) 出願番号 | 特願2007-241517 (P2007-241517)  | (73) 特許権者 | 000002185<br>ソニー株式会社<br>東京都港区港南1丁目7番1号                |

| (22) 出願日  | 平成19年9月18日 (2007.9.18)        | (74) 代理人  | 100094053<br>弁理士 佐藤 隆久                                |

| (65) 公開番号 | 特開2009-76501 (P2009-76501A)   | (72) 発明者  | 緒方 博美<br>神奈川県横浜市保土ヶ谷区神戸町134番地<br>ソニー・エルエスアイ・デザイン株式会社内 |

| (43) 公開日  | 平成21年4月9日 (2009.4.9)          |           |                                                       |

| 審査請求日     | 平成22年3月15日 (2010.3.15)        |           |                                                       |

| 審判番号      | 不服2013-24583 (P2013-24583/J1) |           |                                                       |

| 審判請求日     | 平成25年12月13日 (2013.12.13)      |           |                                                       |

最終頁に続く

(54) 【発明の名称】半導体集積回路

## (57) 【特許請求の範囲】

## 【請求項 1】

格子状に配置された複数の内部電圧線を備える回路ブロックと、

前記回路ブロックの周囲で閉じた環状線を形成し、電源電圧または基準電圧が印加される第1環状線と、

前記第1環状線と前記回路ブロックとの間で閉じた環状線を形成し、複数箇所で前記複数の内部電圧線と電気的に接続されている第2環状線と、

前記回路ブロックの周囲に配置され、それぞれが矩形の外形を備える複数のスイッチブロックと、

を有し、

各スイッチブロックが、当該スイッチブロック内で互いに並行な前記第1環状線と前記第2環状線との間に電気的に接続された複数のスイッチトランジスタを備え、

前記複数のスイッチトランジスタの一部が、前記各スイッチブロック内において前記第1環状線と前記第2環状線の下層領域に配置され、

前記各スイッチブロックの外周の4辺のうち前記回路ブロックに近い内側辺から前記第1環状線までの距離が前記複数のスイッチブロックで等しく、かつ、前記内側辺から前記第2環状線までの距離が前記複数のスイッチブロックで等しい、

半導体集積回路。

## 【請求項 2】

前記複数のスイッチブロックは、同一サイズを有し、前記回路ブロックの辺ごとに異なる

10

20

る少なくとも 4 種類のスイッチブロックを有する、

請求項 1 に記載の半導体集積回路。

【請求項 3】

前記各スイッチブロックにおいて、前記第 1 環状線および第 2 環状線のスイッチブロック内部分である 2 つの電圧線セグメントと前記複数のスイッチトランジスタが内部接続され、

前記各スイッチブロックのブロック枠の対向する 2 辺における、前記 2 つの電圧線セグメントの端辺の位置関係が、前記複数のスイッチブロックで同じに設定されている、

請求項 2 に記載の半導体集積回路。

【請求項 4】

10

前記回路ブロックは少なくとも 2 組の互いに対向する 2 辺を含む外周を備え、

前記対向する 2 辺の側に配置された前記スイッチブロックが、ミラー対称または 180 度回転対称のパターンを有する、

請求項 1 から 3 の何れか一項に記載の半導体集積回路。

【請求項 5】

前記回路ブロックは少なくとも 2 組の互いに対向する 2 辺を含む外周を備え、

少なくとも 1 組の前記対向する 2 辺において、一方の辺側と他方の辺側で前記スイッチブロックの配置数が異なる、

請求項 1 から 3 の何れか一項に記載の半導体集積回路。

【請求項 6】

20

前記回路ブロックの外周の各辺からみた、当該回路ブロックへ電源電圧または基準電圧を供給する配線のインピーダンスが小さいほど数多くなるように、前記回路ブロックの辺ごとに前記スイッチブロックの配置数が決められている、

請求項 5 に記載の半導体集積回路。

【請求項 7】

前記複数のスイッチブロック内で、前記スイッチトランジスタは、ゲート電極の長手方向が同じ方向に揃えられている、

請求項 1 から 3 の何れか一項に記載の半導体集積回路。

【請求項 8】

30

前記スイッチブロック内の異なるスイッチトランジスタを各々が制御する複数のスイッチ制御線を有する、

請求項 1 から 3 の何れか一項に記載の半導体集積回路。

【請求項 9】

前記複数のスイッチ制御線の各々に対し、バッファ回路が接続されている、

請求項 8 に記載の半導体集積回路。

【請求項 10】

複数の前記バッファ回路が、前記第 2 環状線に対し、前記回路ブロックと反対の側に配置されている、

請求項 9 に記載の半導体集積回路。

【請求項 11】

40

前記各スイッチブロックにおいて、

前記複数のスイッチトランジスタの配置領域と交差または近接して、前記第 1 環状線および第 2 環状線のスイッチブロック内部分である 2 つの電圧線セグメントが配置され、

前記複数のスイッチトランジスタの配置領域および前記 2 つの電圧線セグメントに対し前記回路ブロックと反対の側に、前記第 1 環状線の電圧線セグメントから電圧供給を受けて動作する前記バッファ回路が配置され、

前記バッファ回路の入力側に、制御線を介して制御信号が入力される第 1 制御線セグメントが配置され、

前記バッファ回路の出力側に、前記スイッチトランジスタの制御ノードに電気的に接続される第 2 制御線セグメントが配置されている、

50

請求項 10 に記載の半導体集積回路。

【請求項 12】

格子状の前記複数の内部電圧線は、第1方向の内部電圧線と、前記第1方向と直交する第2方向の内部電圧線とが異なる階層の配線層から形成されている。\_

請求項 1 から 3 の何れか一項に記載の半導体集積回路。

【請求項 13】

前記第2環状線は、第1方向の配線層と、前記第1方向と直交する第2方向に配線され前記第1方向の配線層と異なる階層の第2方向の配線層とから形成されている。\_

請求項 12 に記載の半導体集積回路。

【発明の詳細な説明】

10

【技術分野】

【0001】

本発明は、回路ブロックの内部電圧線と、電源電圧または基準電圧が印加される配線との接続と非接続をスイッチにより制御する半導体集積回路に関する。

【背景技術】

【0002】

回路に対しスイッチにより電源供給の遮断とその解除を制御するものとして、M T C M O S (Multi-threshold Complementary Metal Oxide Semiconductor) 技術が知られている。

一般的に、電源電圧低下や素子微細化に付随して信号遅延が発生しないように、論理回路等のトランジスタの閾値電圧を設計値として下げる必要がある。論理回路等のトランジスタの閾値電圧が小さいとリーク電流が大きい。M T C M O S 技術は、停止状態の回路に対し、論理回路等のトランジスタに比べ、より大きな閾値電圧のトランジスタ（電源スイッチ）によって、リーク電流経路を遮断して、その消費電力の浪費を防ぐものである。

【0003】

M T C M O S 技術の回路ブロックへの適用では、いわゆる仮想 V D D 線、仮想 G N D 線と称される、回路ブロック内に設けられた内部電圧線を設ける。内部電圧線は、回路ブロックの外部でブロック間接続を行うグローバルな実電源線（実 V D D 線）や実基準電圧線（実 V S S 線）に対して、電源遮断とその解除のための電源スイッチを介して接続される。

電源スイッチを設ける箇所は、起動と停止が繰り返される機能回路と実 V D D 線との間、機能回路と実 V S S 線との間、その両方の 3 通りがあり、スイッチとしては通常、V D D 側では P M O S トランジスタ、V S S 線側では N M O S トランジスタを用いる。

【0004】

M T C M O S 適用ブロックの機能回路の起動と停止は、半導体集積回路が起動された後は常時、実 V D D 線と実 V S S 線からの電源供給を受けて動作状態におかれる M T C M O S 非適用ブロック内の回路によって制御される。あるいは、M T C M O S 適用ブロックの機能回路の起動と停止を制御する制御信号を、半導体集積回路の外部端子から入力可能な構成が採用されることもある。

【0005】

ところで、電源スイッチは、M T C M O S 適用ブロック内セルにより実現されることがある。より詳細には M T C M O S 適用ブロック内において、インバータ、N A N D 回路、N O R 回路等の各論理回路セル内に、あるいは、幾つかの論理回路で実現される機能回路セル内に電源スイッチを設ける場合と、論理回路や機能回路を有しない専用の電源スイッチセルを設ける場合がある。以下、このタイプのスイッチ配置を「内部スイッチ（S W）配置」、当該配置が採られた半導体集積回路を「内部 S W 配置型 I C」と称する。

【0006】

内部 S W 配置型 I C に対して、電源供給制御対象の回路ブロックの周囲に電源スイッチを配置した半導体集積回路が知られている（例えば、特許文献 1、特許文献 2 参照）。このタイプのスイッチ配置を「外部 S W 配置」、当該配置が採られた半導体集積回路を「外

20

30

40

50

部 SW 配置型 IC」と称する。

外部 SW 配置は、いわゆる「マクロ」と称される汎用的な回路（例えばメモリや CPU 等）を一部または全部とする回路ブロックと組み合わせて好適に用いられる。

#### 【0007】

上記特許文献 2 には、回路ブロックの 3 辺又は 4 辺に対し、長手方向が各辺に沿う形状のトランジスタセル（スイッチ）が配置され、当該スイッチ内のトランジスタゲートラインの配置方向が上記長手方向と同一な構成が開示されている。

この構成において、トランジスタセル配置領域の反回路ブロック側（外側）に、回路ブロックの周囲を環状に囲む環状線として VDD 供給リングおよび VSS 供給リングが配置されている。VDD 供給リングと、スイッチトランジスタのドレインとが、VDD 供給リングと異なる階層のメタル配線層により接続されている。VSS 供給リングと、回路ブロック内の VSS 線とが、VSS 供給リングと異なる階層のメタル配線層により接続されている。また、スイッチトランジスタのソースと、回路ブロック内の仮想 VSS 線とが、VSS 供給リングと異なる階層のメタル配線層により接続されている。

【特許文献 1】特開 2003-289245 号公報

【特許文献 2】特開 2003-158189 号公報

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0008】

上記特許文献 1 に記載の半導体集積回路は、VDD 電圧の供給線が回路ブロック（内部回路）の周囲に環状に配置されていないため、VDD 電圧の供給元から遠い VDD 電圧の供給線箇所で電圧ドロップが生じ、その結果、他と同じサイズのスイッチトランジスタを同じ時間だけオンまたはオフしても、内部回路の内部電圧線を充放電する能力に差が生じる。このため、VDD 電圧の供給元から遠い箇所ほどスイッチトランジスタのサイズを大きくするか、トランジスタ数を増やすなどの工夫が必要となる。その結果、内部回路の停止状態においてスイッチトランジスタを介したリーク電流が増大するという不利益が生じる。

スイッチトランジスタの閾値電圧は、内部回路のトランジスタの閾値電圧より大きく設定され、相対的にリーク電流は小さい。しかし、停止期間が長いと、スイッチトランジスタのサイズや数の増大による無駄な電力消費は無視できなくなる。

#### 【0009】

上記特許文献 2 に記載の半導体集積回路は、VDD 電圧や VSS 電圧の供給線が供給リングとして環状配置されているため、供給リングがない上記特許文献 1 に記載の半導体集積回路と比べると、電圧の供給元から各スイッチトランジスタまでの電圧ドロップが均一化されている。よって、上記リーク電流の増大は比較的抑制される。

#### 【0010】

しかしながら、上記特許文献 2 に記載の半導体集積回路は、環状線（供給リング）が、スイッチトランジスタと別々に配置されているため、スイッチトランジスタと供給リング（VDD 供給リングおよび VSS 供給リング）を接続する配線が複雑である。

#### 【0011】

VDD 供給リングや VSS 供給リングは電圧ドロップを均一化する目的で設けられるが、その電位は、周辺の動作回路の影響を受けて完全に均一でないことがある。勿論、これらの供給リングの配線抵抗を減らすことにより、より均一になるが、頻繁に大きな振幅で動作する周辺回路の付近では、その影響を受けて、例えば VSS 供給リングの電位が基準電位（例えば 0 [V]）から持ち上ることがある。しかし、周辺回路の動作を完全に見積もることは困難であるため、周辺回路の影響を回避してスイッチトランジスタの動作の安定化を図るには、設計中に、スイッチトランジスタの位置をずらし、あるいは、サイズを変更する必要が生じ、接続配線をやり直す設計負担が大きい。

#### 【0012】

つまり、特許文献 2 に記載のスイッチトランジスタ（当該特許文献では「マクロ」と称

10

20

30

40

50

している)の構成は、そのような設計変更に対応した構造を有していない。

なお、スイッチトランジスタの位置やサイズが重要であることは、特許文献2においてスイッチトランジスタのサイズを変更し、あるいは、スイッチトランジスタを2重に設けるなどの様々な変更例が示されていることからも明らかである。

【課題を解決するための手段】

【0013】

本発明の一形態に關わる半導体集積回路は、格子状に配置された複数の内部電圧線を備える回路ブロックと、前記回路ブロックの周囲で閉じた環状線を形成し、電源電圧または基準電圧が印加される第1環状線と、前記第1環状線と前記回路ブロックとの間で閉じた環状線を形成し、複数箇所で前記複数の内部電圧線と電気的に接続されている第2環状線と、前記回路ブロックの周囲に配置され、それぞれが矩形の外形を備える複数のスイッチブロックと、を有し、各スイッチブロックが、当該スイッチブロック内で互いに並行な前記第1環状線と前記第2環状線との間に電気的に接続された複数のスイッチトランジスタを備え、前記複数のスイッチトランジスタの一部が、前記各スイッチブロック内において前記第1環状線と前記第2環状線の下層領域に配置され、前記各スイッチブロックの外周の4辺のうち前記回路ブロックに近い内側辺から前記第1環状線までの距離が前記複数のスイッチブロックで等しく、かつ、前記内側辺から前記第2環状線までの距離が前記複数のスイッチブロックで等しい。

好適に、前記複数のスイッチブロックは、同一サイズを有し、前記回路ブロックの辺ごとに異なる少なくとも4種類のスイッチブロックを有する。

さらに好適に、前記各スイッチブロックにおいて、前記第1環状線および第2環状線のスイッチブロック内部分である2つの電圧線セグメントと前記複数のスイッチトランジスタが内部接続され、前記各スイッチブロックのブロック枠の対向する2辺における、前記2つの電圧線セグメントの端辺の位置関係が、前記複数のスイッチブロックで同じに設定されている。

【0014】

好適に、前記回路ブロックは少なくとも2組の互いに對向する2辺を含む外周を備え、前記對向する2辺の側に配置された前記スイッチブロックが、ミラー対称または180度回転対称のパターンを有する。

【0015】

好適に、前記回路ブロックは少なくとも2組の互いに對向する2辺を含む外周を備え、少なくとも1組の前記對向する2辺において、一方の辺側と他方の辺側で前記スイッチブロックの配置数が異なる。

さらに好適に、前記回路ブロックの外周の各辺からみた、当該回路ブロックへ電源電圧または基準電圧を供給する配線のインピーダンスが小さいほど数多くなるように、前記回路ブロックの辺ごとに前記スイッチブロックの配置数が決められている。

【0016】

好適に、前記複数のスイッチブロック内で、前記スイッチトランジスタは、ゲート電極の長手方向が同じ方向に揃えられている。

【0017】

好適に、前記スイッチブロック内の異なるスイッチトランジスタを各々が制御する複数のスイッチ制御線を有する。

さらに好適に、前記複数のスイッチ制御線の各々に対し、バッファ回路が接続されている。

さらに好適に、複数の前記バッファ回路が、前記第2環状線に対し、前記回路ブロックと反対の側に配置されている。

さらに好適に、前記各スイッチブロックにおいて、前記複数のスイッチトランジスタの配置領域と交差または近接して、前記第1環状線および第2環状線のスイッチブロック内部分である2つの電圧線セグメントが配置され、前記複数のスイッチトランジスタの配置領域および前記2つの電圧線セグメントに対し前記回路ブロックと反対の側に、前記第1

10

20

30

40

50

環状線の電圧線セグメントから電圧供給を受けて動作する前記バッファ回路が配置され、前記バッファ回路の入力側に、制御線を介して制御信号が入力される第1制御線セグメントが配置され、前記バッファ回路の出力側に、前記スイッチトランジスタの制御ノードに電気的に接続される第2制御線セグメントが配置されている。

【0018】

前述した一形態の構成によれば、環状線が、第1および第2環状線と称する2本形成される。

このため、複数のスイッチブロックの各々において、第1環状線の一部と、第2環状線の一部とを備え、これらスイッチブロック内の第1および第2環状線にスイッチトランジスタが接続されている。また、複数のスイッチブロックにおいて、第1および第2環状線から回路ブロックまでの距離が一定である。

したがって、スイッチブロック同士を隣接させて、第1環状線（のブロック内セグメント）同士、第2環状線（のブロック内セグメント）同士をつなぐか、あるいは、距離が離れている場合には、対応する第1または第2環状線（のブロック内セグメント）同士の間を配線でつなぐことによって、回路ブロックの周囲で閉じた2本の環状線が形成される。

【0019】

スイッチブロックの位置を動かす場合は、移動対象スイッチブロックの第1および第2環状線以外の構成要素を所望の位置に動かし、その移動させた位置で当該構成要素を第1および第2環状線に接続させる。

このとき上記一形態では、第1および第2環状線をスイッチブロックごとに有しているため、回路ブロックとの接続変更も不要である。このため、第1および第2環状線それぞれに対し、スイッチブロックの第1および第2環状線以外の構成要素を移動させるだけで、自由にスイッチブロックを移動できる。

【0020】

以上はスイッチトランジスタの移動における作用説明であるが、スイッチトランジスタを挿入し、あるいは、削除する場合も、同様に、スイッチブロックの第1および第2環状線以外の構成要素を必要な数だけ必要な場所に挿入、削除するだけでよい。

【発明の効果】

【0021】

本発明によれば、スイッチの移動、数の変更などに際し、主に、スイッチブロックの電圧線セグメント以外の構成要素変更で済むため、設計変更が容易で、スイッチの位置や数の最適化を行うことが簡単であるという利益が得られる。より詳細には、電源電圧または基準電圧の供給線がスイッチと離れて互いの位置関係に統一性がない場合に、スイッチ移動やスイッチの挿入、削除などの設計変更に際し、異なる階層のメタル配線層を接続し直す必要があるが、本発明では、そのような環状レール線以外の配線を一々やり直す手間が不要である。

【発明を実施するための最良の形態】

【0022】

以下、本発明の実施形態を、図面を参照して説明する。

【0023】

<全体構成>

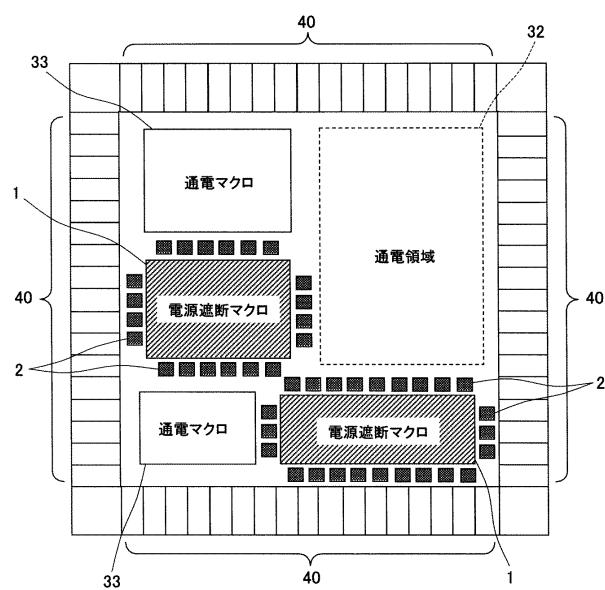

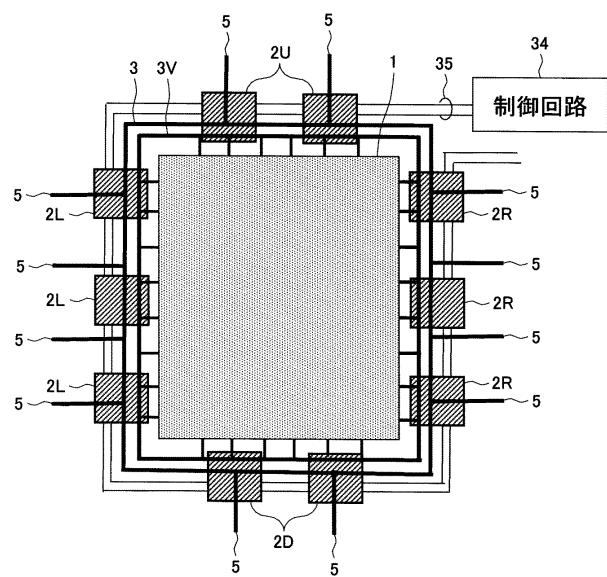

図1に、本発明の実施形態に関わる半導体集積回路の全体構成を示す。

図1において、半導体集積回路が形成される矩形半導体チップの4つの辺に沿って、それぞれ複数の入出力セル40が列をなして配列されている。

【0024】

図1に示す入出力セル40に四方を囲まれた回路配置のためのチップエリアに、いくつかの回路ブロックが配置されている。図1に示す例では、「通電領域」と称される、半導体集積回路のベーシックな構成、例えば、CPU、レジスタ、メモリ、電源回路などを含む通電回路ブロック32がチップエリアに配置されている。通電回路ブロック32は、MTCMOS技術の非適用回路ブロックに対応し、当該半導体集積回路が起動後は常時、電

10

20

30

40

50

源電圧 V D D と基準電圧 V S S の供給を受けて動作する。

回路配置のためのチップエリアには、さらに、「マクロ」と称され、他の半導体集積回路で流用可能に個別設計される汎用的な回路を一部または全部に含む回路ブロックが多数配置されている。「マクロ」は、外部委託による設計が可能であり、また I P (Intellectual Property) として他社から購入することも可能である。

#### 【 0 0 2 5 】

「マクロ」としての回路ブロックは、通電回路ブロック 3 2 と同様に、当該半導体集積回路が起動後は常時、電源電圧 V D D と基準電圧 V S S の供給を受けて動作する「通電マクロ」と称される M T C M O S 技術が非適用の非適用回路ブロック 3 3 と、「電源遮断マクロ」と称され、M T C M O S 技術が適用されて、必要に応じて適宜電源遮断が行われる電源遮断対象の回路ブロック 1 と、に大別できる。

なお、入出力セル 4 0 に囲まれたチップエリアに配置された通電回路ブロック 3 2 、非適用回路ブロック 3 3 および電源遮断対象の回路ブロック 1 は、図 1 では図示を省略しているが、実 V D D 線と実 V S S 線が対をなして配置され、これにより電源供給を受ける。より詳細には、入出力セル 4 0 の幾つかが電源供給のために割り当てられており、当該電源供給のための入出力セル 4 0 から、チップエリア内のロウ (行) 方向とカラム (列) 方向にそれぞれ実電源線対が配線され、これにより、通電回路ブロック 3 2 、非適用回路ブロック 3 3 および電源遮断対象の回路ブロック 1 の電源供給配線がなされている。

#### 【 0 0 2 6 】

電源遮断対象の回路ブロック 1 は、電源遮断と接続を制御するスイッチが電源遮断対象の回路ブロック 1 の周囲に配置されている、いわゆる「外部 S W 配置型」である。図 1 に示すように、スイッチを含むスイッチブロック 2 が、電源遮断対象の回路ブロック 1 の周囲に所定数配置されている。

そして、図 1 では図示を省略しているが、電源電圧 V D D または基準電圧 V S S が印加される環状レール線が、電源遮断対象の回路ブロック 1 周囲に配置された複数のスイッチブロック 2 に重ねて配置されている。環状レール線は最低 1 本、望ましくは 2 本設けられる。以下、図面を参照して環状レール線とスイッチブロック 2 との配置関係を説明する。

#### 【 0 0 2 7 】

前述したように M T C M O S 技術において、スイッチトランジスタを設ける箇所は、起動と停止が繰り返される機能回路と実 V D D 線との間、機能回路と実 V S S 線との間、その両方の 3 通りがあり、スイッチとしては通常、V D D 側では P M O S トランジスタ、V S S 線側では N M O S トランジスタを用いる。

本実施形態でスイッチトランジスタを設ける箇所は、上記 3 通りのいずれでもよい。ただし、V D D 側と V S S 側の両方にスイッチトランジスタを設けると効果の割に占有面積増大の不利益が大きいため、好ましくは、V D D 側と V S S 側の片側にスイッチトランジスタを設ける。また、N M O S トランジスタは P M O S トランジスタより単位ゲート幅あたりの駆動能力が高いため、V S S 側にスイッチトランジスタを設けることが、さらに望ましい。

よって、以下の説明では V S S 側にスイッチ (トランジスタ) を設けることを前提とする。

#### 【 0 0 2 8 】

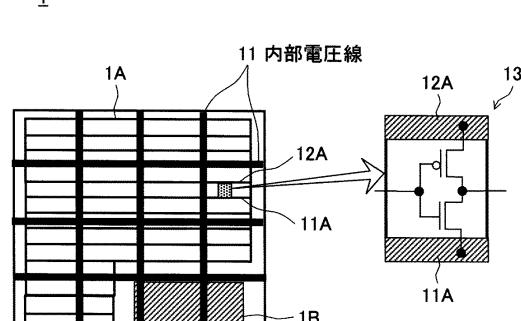

図 2 に、電源遮断対象の回路ブロック 1 の内部構成例を示す。

図解した構成例では、回路ブロック 1 内が、スタンダードセルにより機能回路が実現される標準セル配置領域 1 A と、例えば R A M 等のマクロセル領域 1 B とに区分されている。なお、本発明の適用に関して、電源遮断制御対象の「回路ブロック」は「マクロ」を有している必要はなく、標準セル配置領域 1 A のみの構成でもよい。

標準セル配置領域 1 A とマクロセル領域 1 B 上に、いわゆる「仮想 V S S 線」と称され基準電圧 V S S が印加される内部電圧線 1 1 が、行 (ロウ) 方向と列 (カラム) 方向それぞれ平行配置されている。ロウ方向の内部電圧線 1 1 とカラム方向の内部電圧線 1 1 は、セルより上層階層の配線層により形成され、その交差箇所で相互接続されている。

10

20

30

40

50

一方、煩雑化を避けるため図示を省略しているが、いわゆる「実VDD線」と称され電源電圧VDDが印加される電源線、さらには、基準電圧VSSが印加される電源線も、同様にして格子状に配置されている。

【0029】

標準セル配置領域1Aにおいて、「仮想VSS線」としての内部電圧線11のカラム方向幹配線から、所定間隔で複数の分岐線11Aが口ウ方向に延びている。また、標準セル配置領域1Aにおいて、不図示の「実VDD線」としての電圧供給線のカラム方向幹配線から、所定間隔で複数の分岐線12Aが口ウ方向に延びている。

図2では、スタンダードセルを代表して1つのインバータセル13を拡大して示している。インバータセル13は、分岐線11Aの一部となるVSS線セグメントと、分岐線12Aの一部となるVDD線セグメントとを有し、その2つのセグメント間にPMOSトランジスタとNMOSトランジスタとを直列接続させている。PMOSトランジスタとNMOSトランジスタのゲートは共に入力信号線に接続されている。PMOSトランジスタとNMOSトランジスタ間のノードは出力信号線に接続されている。入力信号線と出力信号線は、インバータセル13および隣接セル内部の信号線セグメントにより形成される。ただし、標準セル配置領域1A全体の入出力線は、上層の配線層(不図示)により形成される。

【0030】

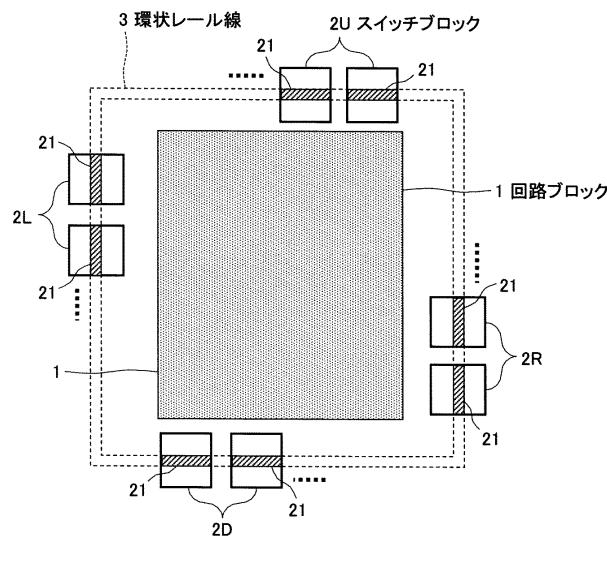

<レール配置例1>

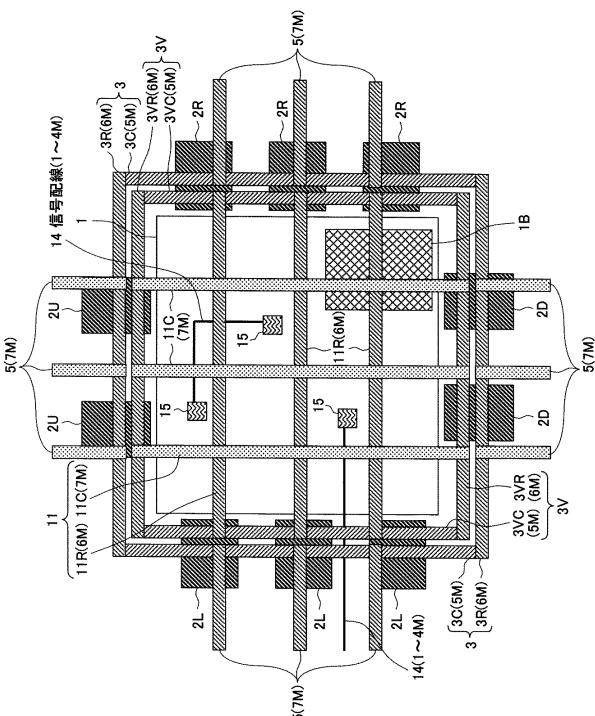

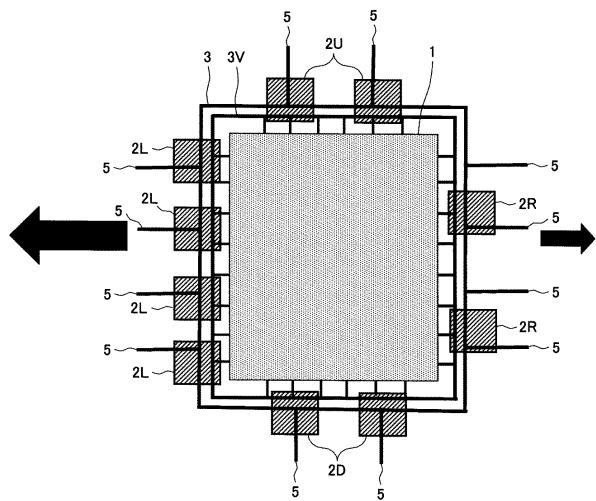

図3に、レール配置例1を示す。

図3に図解するように、電源遮断対象の回路ブロック1の4辺に近接して、当該回路ブロック1を囲むように複数のスイッチブロック2が配置されている。ここで便宜上、スイッチブロック2を、電源遮断対象の回路ブロック1の辺ごとに、上部スイッチブロック2U、下部スイッチブロック2D、右側スイッチブロック2R、左側スイッチブロック2Lに分類する。上部スイッチブロック2U同士、下部スイッチブロック2D同士、右側スイッチブロック2R同士、左側スイッチブロック2L同士は、それぞれ同じ構成を有する。

【0031】

4種類のスイッチブロック2U, 2D, 2R, 2Lは、それぞれ、電圧線セグメント21と、不図示のスイッチとを備える。

電圧線セグメント21は、図3に破線で示し、電源遮断対象の回路ブロック1の周囲に閉じた環状線を形成する環状レール線3の一部となる配線部分である。

配置配線の設計段階では、スイッチを配置した後の配線段階で環状レール線3がスイッチ等に対して配置接続される。一旦、配置接続された後は、スイッチブロック2U, 2D, 2R, 2L単位で、電圧線セグメント21以外の構成要素(スイッチを含む)を移動させて、その移動後の位置で、環状レール線3へスイッチ等を接続させる。なお、この図3では、電源遮断対象の回路ブロック1内の内部電圧線11(図2参照)とスイッチの接続配線は、スイッチブロック移動のたびに変更する必要がある。ただし、環状レール線3に関しては、スイッチとの接続配線を変更する手間がなく、その分、スイッチの移動が容易である。

【0032】

スイッチブロックを挿入する場合は、同様にして、スイッチブロック内の電圧線セグメント21以外の構成要素を単位として、これを必要数、必要な場所に挿入し、その場所における環状レール線3にスイッチ等を接続する。

スイッチを削除する場合も同様であり、スイッチブロック内の電圧線セグメント21以外の構成要素を単位として削除する。

スイッチの挿入、削除においても、環状レール線3に関しては、スイッチとの接続配線を変更する手間がなく、その分、スイッチの移動が容易である。

【0033】

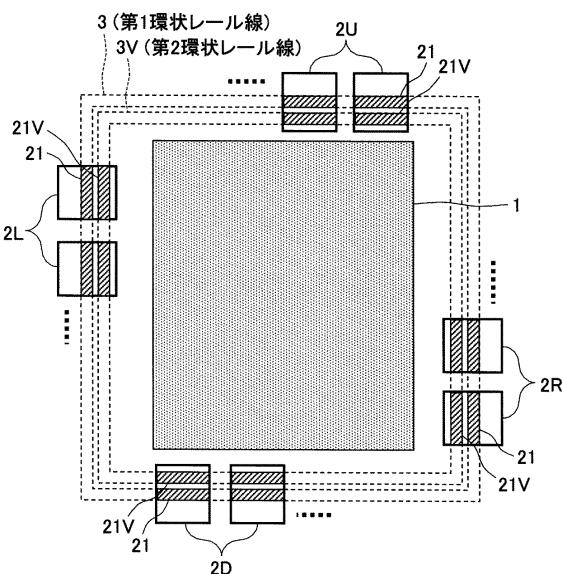

<レール配置例2>

図4に、レール配置例2を示す。

10

20

30

40

50

図4に示す配置例が図3と異なる第1の点として、「第1環状レール線」としての環状レール線3に加えて、「第2環状レール線」としての仮想環状レール線3Vが設けられている。

仮想環状レール線3Vは、環状レール線3と電源遮断対象の回路ブロック1との間に、環状レール線3と並行に配置される。仮想環状レール線3Vは、電源遮断対象の回路ブロック1内の内部電圧線11(図2参照)に対し、所定の箇所、例えば図2の場合、内部電圧線11の各端部(ロウ方向3箇所、カラム方向4箇所)に接続されている。

スイッチブロック2U, 2D, 2R, 2Lの各々において、環状レール線3(電圧線セグメント21)と仮想環状レール線3V(仮想電圧線セグメント21V)間に、不図示のスイッチが接続されている。

10

#### 【0034】

第2の相違点として、スイッチブロック2U, 2D, 2R, 2Lの各々に、「第1電圧線セグメント」としての電圧線セグメント21と並行に、「第2電圧線セグメント」としての仮想電圧線セグメント21Vを備える。

その他の、スイッチブロック2U, 2D, 2R, 2Lの電源遮断対象の回路ブロック1に対する配置自体は、図3と共通する。

#### 【0035】

レール配置例2においても、レール配置例1と同様に、スイッチブロックの電圧線セグメント21および仮想電圧線セグメント21Vを除く構成要素を移動、挿入、削除するだけで、環状レール線3に関しては、スイッチとの接続配線を変更する手間がなく、その分、スイッチの移動が容易である。

20

さらに、レール配置例2においては、仮想環状レール線3Vが、例えば内部電圧線11の各端部(ロウ方向3箇所、カラム方向4箇所)と接続されているが、この接続箇所に変更を加えることなく、仮想環状レール線3Vに関しても、スイッチとの接続配線を変更する手間がなく、その分、スイッチの移動が容易である。

#### 【0036】

上述したレール配置例1(図3)およびレール配置例2(図4)において、上述したスイッチブロックの電圧線セグメント21(および仮想電圧線セグメント21V)を除く構成要素を環状レール線3(および仮想環状レール線3V)に沿って移動、挿入、削除するだけで自由にスイッチブロックの位置や数の変更が可能であることは既に述べた。

30

この自由な設計変更を可能とするためには、スイッチブロック2U, 2D, 2R, 2Lのサイズが同じであり、そのブロック枠の、環状レール線3(および仮想環状レール線3V)が横切る各対向2辺において、電圧線セグメント21(および仮想電圧線セグメント21V)の端辺位置が規格化されている(一定となっている)ことが必要である。

#### 【0037】

なお、端辺位置が規格化されていない場合、スイッチブロックの電圧線セグメント21(および仮想電圧線セグメント21V)を除く構成要素を環状レール線3(および仮想環状レール線3V)に沿って移動、挿入、削除した後に、隣り合うスイッチブロック間で端辺同士を結ぶように電圧線セグメント21(および仮想環状レール線3V)のパターンを修正する必要がある。ただし、この作業は端辺を結ぶ簡単な作業であるため自動化が可能である。よって、スイッチ配置後に、スイッチより外側に配置されている環状線と手作業で他の階層の配線層を用いて接続配線をやり直す場合に比べると、各段にスイッチ配置変更が容易である。

40

#### 【0038】

##### <スイッチ制御線>

図3および図4では図示を省略しているが、スイッチの制御線は、同時制御するスイッチ群の個数により、複数配線されることがある。

#### 【0039】

図5は、制御線が2本の場合における、制御線の配線例を示す図である。ここで、環状レール線については、レール配置例2(図4)が採用されている。

50

図5に示す制御回路34は、例えば、図1における通電回路ブロック32や非適用回路ブロック33などの、MTCMOS非適用回路ブロックに設けられることにより、当該半導体集積回路の起動後は常時、電源供給を受けて動作可能な回路である。制御回路34からの制御線35は、上部スイッチブロック2U、左側スイッチブロック2L、下部スイッチブロック2D、右側スイッチブロック2Rの順に配線され、制御信号が、この順で印加される。制御信号により、各スイッチブロック内のスイッチの導通と非導通が制御される。

#### 【0040】

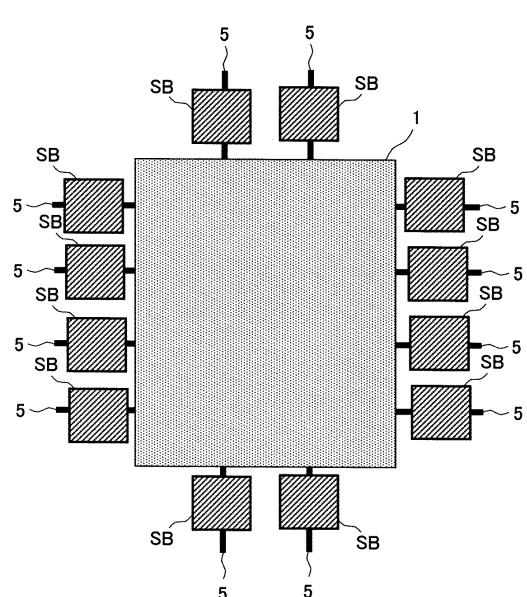

なお、図5に示す構成は、図6に示す環状レール線を有しない構成と置き換えて使用可能とするために、環状レール線3の所定箇所に実VSS配線の分岐が設けられている。

10

図6に示す、本発明が非適用の外部SW配置構成は、格子状に設けられたグローバルな各実VSS配線5を、スイッチブロックSBを介して電源遮断対象の回路ブロック1に接続させている。

図5に示す環状レール線3は、格子状配置の実VSS配線5と、ロウ方向2箇所、カラム方向4箇所で接続されている。

一方、仮想環状レール線3Vは、電源遮断対象の回路ブロック1と、ロウ方向6箇所、カラム方向8箇所で接続されている。

これらの接続箇所は、スイッチブロック2U, 2D, 2R, 2Lを移動、挿入、削除する際に全く変更する必要がない。

#### 【0041】

20

つぎに、2本の制御線35によりスイッチ制御される場合を例として、より詳細なスイッチ構成を、図面を参照して説明する。

#### 【0042】

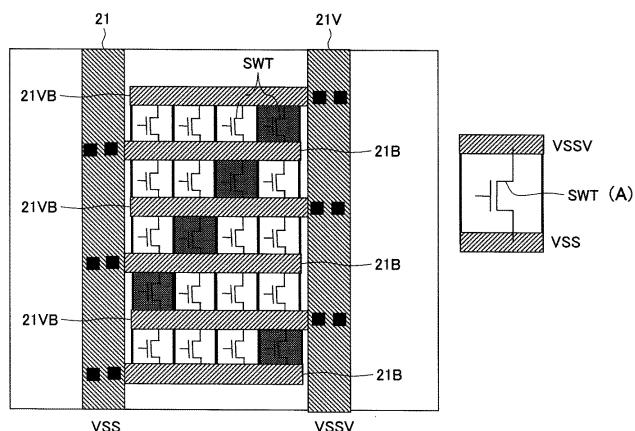

##### <スイッチ構成例>

図7は、基準電圧VSS(例えば0[V])が印加される電圧線セグメント21と、仮想基準電圧VSSVで保持される仮想電圧線セグメント21V間のスイッチトランジスタの配置を模式的に示す、スイッチブロックの構成図である。

図7において、電圧線セグメント21に3本の分岐線21Bが設けられており、仮想電圧線セグメント21Vに3本の分岐線21VBが設けられている。分岐線21Bと分岐線21VBは交互に配置されている。1本の分岐線21Bと、隣接する1本の分岐線21VBとの間に4個のスイッチトランジスタSWTが並列に接続されている。このスイッチトランジスタ列は5段設けられ、全体で $4 \times 5 = 20$ 個のスイッチトランジスタSWTがマトリクス配置されている。

30

#### 【0043】

20個のスイッチトランジスタSWTのうち、各段1つずつ、合計5個のスイッチトランジスタSWTが、不図示の1本の制御線により導通と非導通が制御される。この5個のスイッチトランジスタSWTの回路記号部分を、図7では暗いメッシュを施して示している。メッシュが施されていない他の15個のスイッチトランジスタSWTは、他の制御線により同時制御される。

#### 【0044】

40

このように一部のスイッチと、他のスイッチを分けて制御するのは、電源遮断対象の回路ブロック1(図1～図5参照)の電源供給を遮断した停止状態から、電源供給を開始して動作状態に復帰する際に、急激なスイッチングによる電圧線セグメント21(環状レール線3)の電位変動を抑制するためである。したがって、少ない個数、ここでは5個のスイッチトランジスタSWTを先にオンして、比較的高いオン抵抗である程度、仮想電圧線セグメント21V(電源遮断対象の回路ブロック1内の内部電圧線11)の電位を下げてから、安定したら、残りの15個のスイッチトランジスタSWTをオンする制御が行われる。これにより、環状レール線3から実VSS配線5に伝達する基準電圧VSSの電位上昇(電源ノイズ)のピーク値を、他の常時動作中の回路に影響がない程度に抑圧する。

#### 【0045】

50

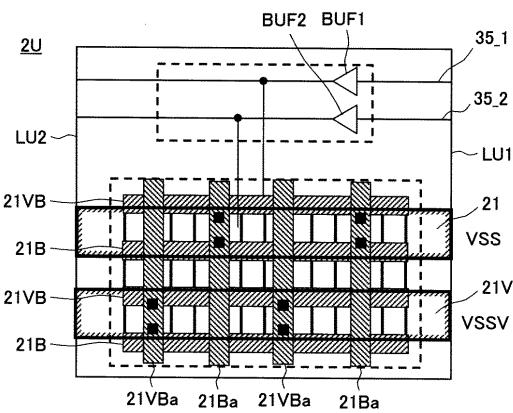

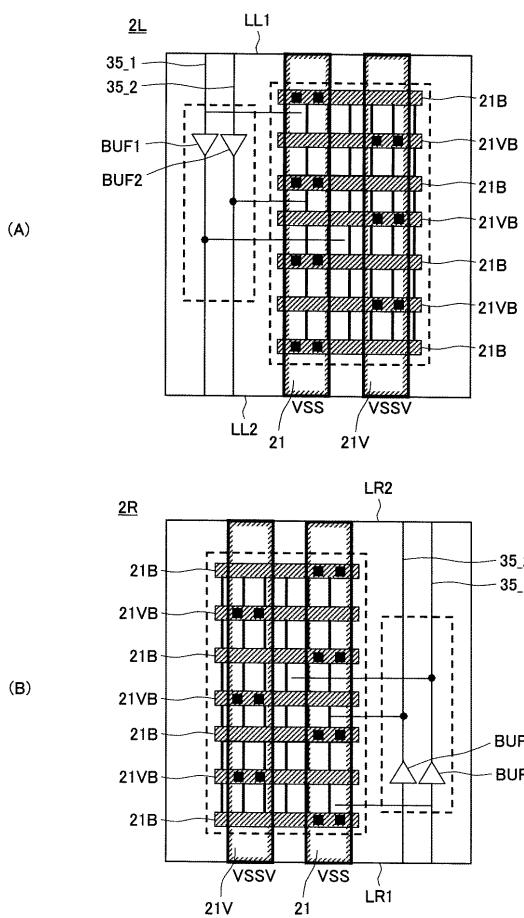

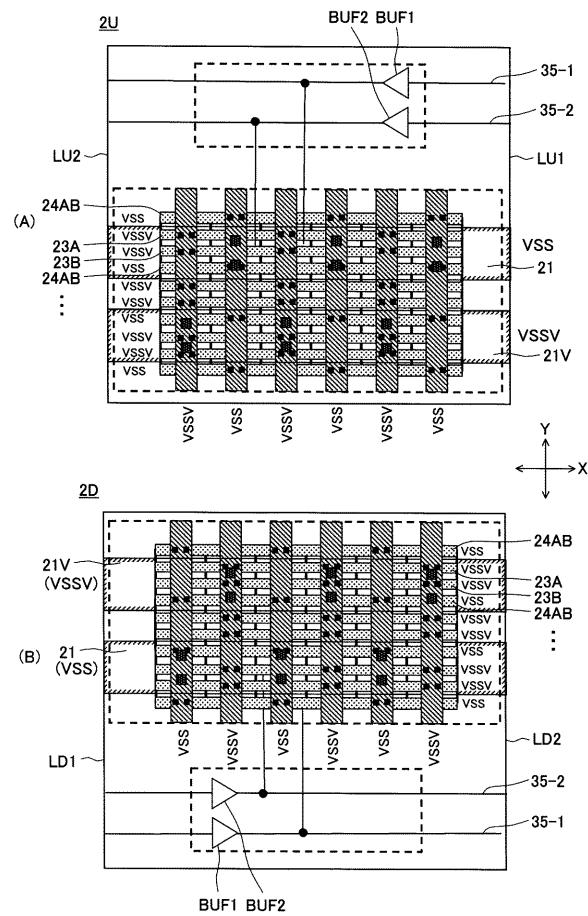

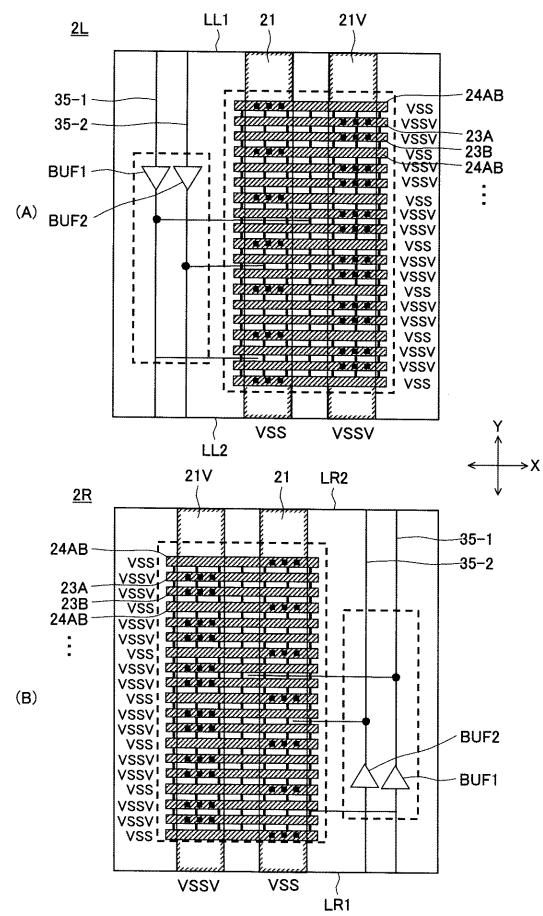

図8(A)～図9(B)に、実際のスイッチブロック内配置例を示す。ここで図3および図4との対応関係で言うと、図8(A)は上部スイッチブロック2U、図8(B)は下部スイッチブロック2D、図9(A)は左側スイッチブロック2L、図9(B)は右側スイッチブロック2Rを、それぞれ示す。

4種類のスイッチブロック2U, 2D, 2R, 2Lは同じサイズを有する。ここで、基準電圧VSS、仮想基準電圧VSSVおよび制御信号が入出力するブロック枠の辺(以下、接続辺という)、すなわち、図8(A)の辺LU1とLU2、図8(B)の辺LD1とLD2、図9(A)の辺LL1とLL2、ならびに、図9(B)の辺LR1とLR2は、同じ長さに設定されている。また、これらの接続辺における、電圧線セグメント21、仮想電圧線セグメント21V、第1スイッチ制御線35\_1、第2スイッチ制御線35\_2の各端辺は、どの接続辺でも同じ位置に規格化されている。 10

#### 【0046】

ここで第1スイッチ制御線35\_1は、図7と同様に先に制御される数個のスイッチトランジスタSWTを制御し、第2スイッチ制御線35\_2は、残りの数個のスイッチトランジスタSWTを制御するものである。

#### 【0047】

図8および図9に示すスイッチブロック2U, 2D, 2R, 2Lは、図7と異なり、破線で囲むスイッチ配置領域の上方に重ねて電圧線セグメント21および仮想電圧線セグメント21Vを並行配置している。これによりブロックの占有面積を小さくできる利点がある。ただし、図7のように、スイッチ配置領域に電圧線セグメント21および仮想電圧線セグメント21Vを重ねない配置も採用可能である。 20

スイッチ配置領域の上方に重ねて電圧線セグメント21および仮想電圧線セグメント21Vを並行配置する場合、限られた多層配線構造の階層数では、第1および第2スイッチ制御線35\_1, 35\_2を、スイッチ配置領域に配置することができない。よって、本例では、電源遮断対象の回路ブロック1に対する外寄りのスイッチ配置領域の外部に、第1および第2スイッチ制御線35\_1, 35\_2を配置している。

#### 【0048】

図9に示す左側スイッチブロック2Lと右側スイッチブロック2Rにおいては、図7に示すスイッチセルを、X方向(図の左右の方向)に6個、Y方向(図の上下の方向)に6個の合計36個、配置している。 30

これに対し、図8に示す上部スイッチブロック2Uと下部スイッチブロック2Dでは、スイッチセルの合計数は36個と図9の場合と同じであるが、X方向の配置数が12個、Y方向の配置数が3個となっている。

その理由は、スイッチセルはY方向のサイズがX方向に比べて大きいこと、ゲート電極の長手方向を図8と図9でY方向に揃える必要があることに対応して、同じサイズを有するスイッチブロック内に収容するスイッチ配置領域の縦横比を、図8と図9で入れ替わっているスイッチブロックの縦と横のサイズに適合させるためである。

#### 【0049】

図9の場合、分岐線21Bと21VBの全てに対し、電圧線セグメント21と仮想電圧線セグメント21Vの各々が交差している。このため、電圧線セグメント21は、下層の全ての分岐線21Bと21VBにコンタクトを介して接続することができ、また、仮想電圧線セグメント21Vは、下層の全ての分岐線21Bと21VBにコンタクトを介して接続することができる。 40

これに対し、図8の場合、電圧線セグメント21と仮想電圧線セグメント21Vは、コンタクトをとるべき下層配線(分岐線21Bと21VB)全てに交差していない。よって、図8に示すように、上部スイッチブロック2Uおよび下部スイッチブロック2Dにおいては、電圧線セグメント21から分岐線21Bまでのアクセス経路に、電圧線セグメント21および分岐線21Bと直交するアクセス分岐線21Baを設ける必要がある。アクセス分岐線21Baは、電圧線セグメント21より下層で、分岐線21Bより上層の配線層から形成される。よって、電圧線セグメント21の分岐線がアクセス分岐線21Ba 50

であり、さらに、アクセス分岐線 2 1 B a から分岐線 2 1 B が分岐する 2 段階分岐構造が採用されている。

同様に、仮想電圧線セグメント 2 1 V から、これと直交するアクセス分岐線 2 1 V B a が分岐し、さらにアクセス分岐線 2 1 V B a から、これと直交する分岐線 2 1 V B が分岐することによって、2 段階分岐構造が採用されている。

#### 【0050】

第 1 スイッチ制御線 3 5 \_ 1 が制御する数個のスイッチトランジスタ SWT の総ゲート幅（長手方向のトータルの長さ）が、図 8 と図 9 では同じに設定されている。同様に、第 2 スイッチ制御線 3 5 \_ 2 が制御する残りの数個のスイッチトランジスタ SWT についても、その総ゲート幅が図 8 と図 9 では同じに設定されている。

10

#### 【0051】

スイッチブロック 2 U, 2 D, 2 R, 2 L の各々は、スイッチ配置領域の回路ブロック 1 と反対の側（外側）に、第 1 スイッチ制御線 3 5 \_ 1 の途中に設けられているバッファ回路 BUF 1 と、第 2 スイッチ制御線 3 5 \_ 2 の途中に設けられているバッファ回路 BUF 2 を備える。

バッファ回路 BUF 1, BUF 2 は、不図示の実 VDD 線と電圧線セグメント 2 1 に接続されることにより、伝送途中で減衰した制御信号を電源電圧 VDD 振幅のパルス信号に波形整形する役目がある。このため、破線により示すバッファ回路の配置領域はスイッチ配置領域より外側に設けられている。

#### 【0052】

バッファ回路 BUF 1, BUF 2 の各出力からは、スイッチ制御のための配線がそれぞれスイッチ配置領域に延び、対応するスイッチトランジスタ群のゲートに接続されている。

20

なお、この配線、ならびに、第 1 スイッチ制御線 3 5 \_ 1 および第 2 スイッチ制御線 3 5 \_ 2 は、図 8 および図 9 ではラインで示しているが、実際には、電圧線セグメント 2 1 等と同様な幅を有する配線層で形成されている。

第 1 スイッチ制御線 3 5 \_ 1 および第 2 スイッチ制御線 3 5 \_ 2 は、それぞれ、スイッチブロック内において、対応するバッファ回路 BUF 1, BUF 2 の入力側に設けられ、制御信号が入力される「第 1 制御線セグメント」と、出力側に設けられ、波形整形された制御信号が出力される「第 2 制御線セグメント」を有して構成されている。

30

#### 【0053】

##### <配線構造>

図 10 に、多層配線構造における各階層の配線層の使用例を示す。ここでは、多層配線構造において、下層から順に積層された第 1 階層の配線層（第 1 配線層（1 M））～第 7 階層の配線層（第 7 配線層（7 M））を利用して、各配線を形成している。

#### 【0054】

具体的には、電源遮断対象の回路ブロック 1 内のインバータセル 1 3（図 2）等の標準セル 15 間を第 1 配線層（1 M）～第 4 配線層（4 M）から形成している。また、ある標準セル 15 から外部へ引き出す信号線も、第 1 配線層（1 M）～第 4 配線層（4 M）で形成している。

40

#### 【0055】

環状レール線 3 のカラム方向の配線 3 C を、第 5 配線層（5 M）から形成している。環状レール線 3 の口ウ方向の配線 3 R を、カラム方向の配線 3 C の両端に接続された 1 階層上の第 6 配線層（6 M）により形成している。

同様に、仮想環状レール線 3 V のカラム方向の配線 3 VC を、第 5 配線層（5 M）から形成している。仮想環状レール線 3 V の口ウ方向の配線 3 VR を、カラム方向の配線 3 VC の両端に接続された 1 階層上の第 6 配線層（6 M）により形成している。

#### 【0056】

一方、内部電圧線 1 1 の口ウ方向の配線 1 1 R は、第 5 配線層（5 M）により形成された仮想環状レール線 3 V のカラム方向の配線 3 VC に接続するために、それより 1 階層上

50

の第6配線層(6M)により形成している。さらに、6Mにより形成された当該内部電圧線11のロウ方向の配線11Rは、それよりさらに1階層上の第7配線層(7M)により形成された、内部電圧線11のカラム方向の配線11Cと、交差箇所で接続されている。

なお、実VSS配線5も第7配線層(7M)により形成されている。

#### 【0057】

このように、カラム方向の配線を、ロウ方向の1階層下の配線から形成し、そのルールを適用しながら配線間接続を上手に達成している。

#### 【0058】

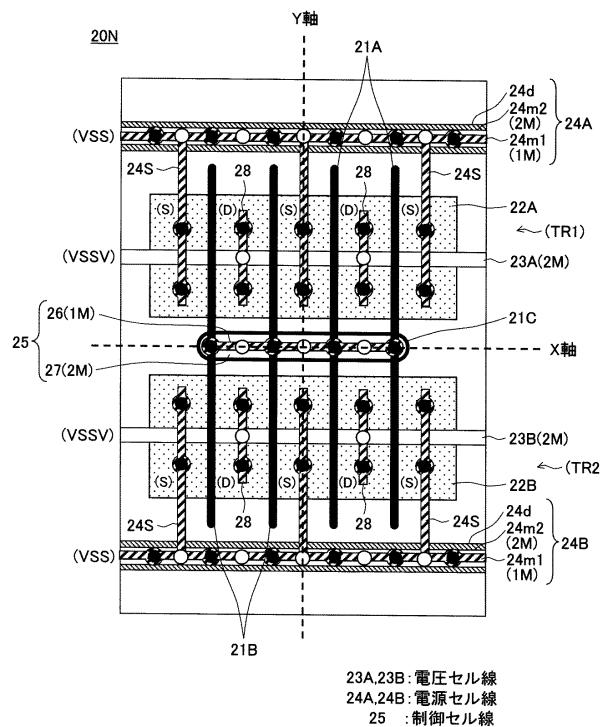

以上の説明では、スイッチセルのパターンについては任意であり言及しなかったが、次に、望ましい具体例として、2軸対称パターンを有するスイッチセルについて説明する。

10

図11に、1つのスイッチセルの概略的なレイアウト図を示す。なお、図11は、パターンの寸法等が実際のものと等しい訳ではなく、パターンの大まかな配置と接続関係を模式的に示すに過ぎない。

#### 【0059】

図11に示すスイッチセル20Nは、1つのNMOStランジスタをスタンダードセル化したものであり、セル中心を通るX軸とY軸それぞれに対し、軸対称な配置となっている。以下、この対称性を「2軸対称」という。

#### 【0060】

図11に図解するスイッチセル20Nの全領域がPウェルの一部となっている。

X軸に沿ってセル中心を通るゲート電極の連結部21Cが形成されている。連結部21Cのセル中心からの長さは、Y軸を境に同じ(対称)である。つまり、連結部21Cは2軸対称のパターンを有する。

20

連結部21Cから、その幅方向の一方側に同じ長さの4本のゲート電極21Aが延び、他方側に同じ長さの4本のゲート電極21Bが延びている。4本のゲート電極21Aは、X軸方向において等間隔に配置され、4本のゲート電極21Bは、同様にX軸方向において等間隔に配置され、全て同じ長さと太さを有するためY軸対称となっている。ゲート電極21Aと21Bは、連結部21Cからの分岐箇所が同じであるため、X軸対称となっている。連結部21C、ゲート電極21Aと21Bは、同じ導電材料を加工して一体として形成されている。

#### 【0061】

30

X軸から等距離で、同じサイズの2つのN型活性領域22Aと22Bが、Pウェルに形成されている。N型活性領域22Aは4本の4ゲート電極21Aに交差する位置に形成され、N型活性領域22Bは4本のゲート電極21Bに交差する位置に形成されている。N型活性領域22Aと22Bは、ゲート電極21Aと21Bを形成後に、これらのゲート電極をマスクとしてN型不純物を選択的にPウェルに導入することにより形成される。

N型活性領域22Aと22Bは、それぞれ、ゲート電極部分で分断され、交互にソース(S)とドレイン(D)として機能する5つの領域から構成されている。

これにより、N型活性領域22Aの分離部分をチャネルとする第1単位トランジスタ(TR1)と、N型活性領域22Bの分離部分をチャネルとする第2単位トランジスタ(TR2)の、2軸対称性を有する基本構造が形成されている。

40

#### 【0062】

第1単位トランジスタ(TR1)の配置領域において、第2配線層(2M)から形成されている電圧セル線23Aが、4本のゲート電極21Aと直交して配置されている。同様に、第2単位トランジスタ(TR2)の配置領域において、第2配線層(2M)から形成されている電圧セル線23Bが、4本のゲート電極21Bと直交して配置されている。

2本の電圧セル線23Aと23Bは、それぞれ、より上層の仮想電圧線セグメント21V(図7参照)によって、回路ブロック1内の内部電圧線11(図2参照)と、電気的に接続されるセル内部線である。つまり、図7との対応関係で言うと、図11の2本の電圧セル線23Aと23Bが、図7の1本の分岐線21VBに対応する。

#### 【0063】

50

N型活性領域22Aと22Bの夫々において、2つのドレイン(D)の各々に対し1s<sub>t</sub>コンタクト(1C)を介して接続する、2つのドレイン線28が設けられている。N型活性領域22Aと22Bで2つずつ、合計4つのドレイン線28は、第1配線層(1M)により形成されている。

N型活性領域22A上の2つのドレイン線28に、2ndコンタクト(2C)を介して電圧セル線23Aが接続されている。同様に、N型活性領域22B上の2つのドレイン線28に、2ndコンタクト(2C)を介して電圧セル線23Bが接続されている。

2本の電圧セル線23Aと23Bは、互いに平行で、かつ、X軸から等距離に配置されている。

#### 【0064】

4本のゲート電極21Aの先端側に、電圧セル線23Aと平行な電源セル線24Aが配置されている。同様に、4本のゲート電極21Bの先端側に、電圧セル線23Bと平行な電源セル線24Bが配置されている。

2本の電源セル線24Aと24Bは、それぞれ、より上層の実VDD線(図7の電圧線セグメント21)と、電気的に接続されるセル内部線である。つまり、このため、2本の電源セル線24Aと24Bは、図7との対応関係で言うと、図11の2本の電源セル線24Aと24Bが、図7の1本の分岐線21Bに対応する。

#### 【0065】

2本の電源セル線24Aと24Bは、それぞれ、不図示のP型活性領域等と同時形成される配線領域24dと、第1配線層(1M)から形成されている第1裏打配線24m1と、第2配線層(2M)から形成されている第2裏打配線24m2とを含んで構成されている。

2本の電源セル線24Aと24Bの夫々において、配線領域24dと第1裏打配線24m1は1s<sub>t</sub>コンタクト(1C)により等間隔で短絡され、第1裏打配線24m1と第2裏打配線24m2は2ndコンタクト(2C)により等間隔で短絡されている。

電源セル線24Aを構成する第1裏打配線24m1は、N型活性領域22Aの2つのソース(S)側に延びる、2本のソース線24Sと一緒に形成されている。同様に、電源セル線24Bを構成する第1裏打配線24m1は、N型活性領域22Bの2つのソース(S)側に延びる、2本のソース線24Sと一緒に形成されている。

そして、各ソース(S)が、ソース線24Sと1s<sub>t</sub>コンタクト(1C)を介して接続されている。

#### 【0066】

ここで、最初に説明したゲート電極の連結部21Cは省略可能で、4つのコンタクトパッド部で代替可能である。

何れの場合でも、全体として、Y軸と平行なゲート電極21Aと21Bからなる4本のゲート電極が、それより上層の配線層で短絡されている。このゲート電極を短絡するセル内部配線を「制御セル線」と称する。

本例の制御セル線25は、第1配線層(1M)からなる第1制御セル線26と、第2配線層(2M)からなる第2制御セル線27を重ねて形成されている。連結部21C(または4つのコンタクトパッド部)と第1制御セル線26が1s<sub>t</sub>コンタクト(1C)により接続され、第1制御セル線26と第2制御セル線27が2ndコンタクト(2C)により接続されている。

制御セル線25が、その幅方向と長さ方向の中心をセル中心に一致させて、X軸に沿って配置されている。

よって、制御セル線25は、2本の電圧セル線23Aと23B、2本の電源セル線24Aと24Bの夫々に対し並行配置されている。

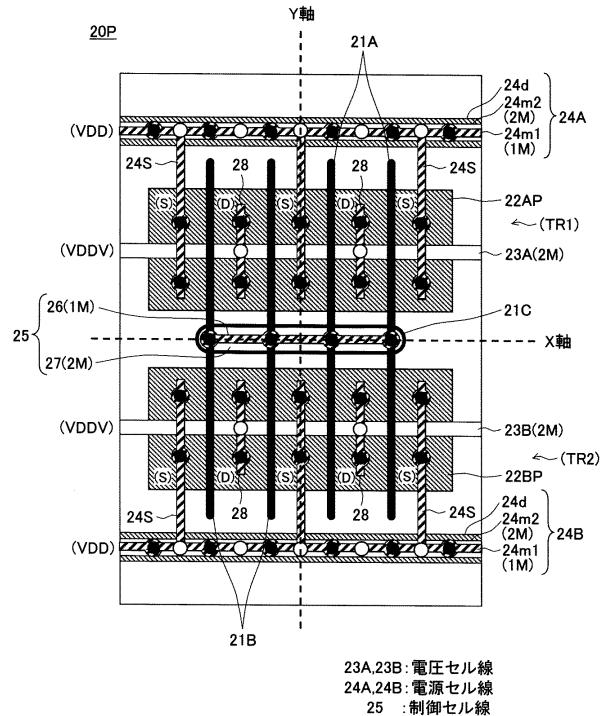

#### 【0067】

図12に、PMOSトランジスタのスイッチセル20Pを示す。

図12に図解するスイッチセル20Pが、図11のスイッチセル20Nと異なる点は、全体がNウェルに形成され、Nウェルに形成されている第1単位トランジスタ(TR1)

10

20

30

40

50

と第2単位トランジスタ( TR2 )の活性領域が、P型のN型活性領域22APと22BPであることである。その他の構成は、図5と同じであるため、同一符号を付して、説明を省略する。

#### 【0068】

図13(A)と図13(B)に、図12のNMOSトランジスタ構成のスイッチセル20Nを利用する、上部スイッチブロック2Uと下部スイッチブロック2Dの構成図を示す。また、図14(A)と図14(B)に、同様にスイッチセル20Nを利用する、左側スイッチブロック2Lと右側スイッチブロック2Rの構成図を示す。

図13および図14を、図8および図9と比較すると、図8および図9の分岐線21Bに対応する電源セル線24ABが、分岐線21Bの2倍の密度で形成され、図8および図9の分岐線21Bに対応する電圧セル線23Aと23Bが、分岐線21VBの2倍の密度で形成されていることが分かる。ここで電源セル線24ABは、図11における電源セル線24Aと、Y方向に隣接する他のセルの電源セル線24Bと共有させたものである。

他の構成は共通するため、ここでの説明を省略する。

#### 【0069】

図13および図14では図示を省略しているが、第1および第2スイッチ制御線35\_1, 35\_2の各々に対し、所定の数で、所定の位置のスイッチセル20Nを接続するためにも、多層配線構造が利用される。配線層を多層化すれば、スイッチ制御線のブロック中心に対する対称配置も可能であるが、このためだけに配線構造を複雑化して製造コストを上げるのは望ましくない。また、本例ではバッファ回路BUF1, BUF2を配置する必要から、スイッチブロックの中心に対し、第1および第2スイッチ制御線35\_1, 35\_2を非対称配置せざるを得ない。

#### 【0070】

つぎに、このようにスイッチ制御線をブロック中心に対称配置できない場合における、スイッチセルの配線対称構造の利点を述べる。

#### 【0071】

第1の利点として、スイッチブロックの設計が容易であることを説明する。

本実施形態で好ましいスイッチの配置配線方法(スイッチブロック設計手法)は、スイッチセル20Nのレイアウト対称性を利用し、以下の手順をとる。

第1ステップ：トランジスタを配置し、内部電圧線11とそれぞれが電気的に接続される2本の電圧セル線23A, 23Bと、電源電圧VDD(スイッチセル20Pの場合)または基準電圧VSS(スイッチセル20Nの場合)が印加される第2電源線に対しそれぞれが電気的に接続される2本の電源セル線24A, 24B(または、2本の共有された電源セル線24AB)と、スイッチ制御線29A～29Cに対し電気的に接続される制御セル線25との各々を、セル中心を通るX軸およびY軸それぞれに対して軸対称に配置し、かつ、トランジスタに対し接続することにより、スイッチセル20Nあるいは20P(またはその両方)を形成する。

第2ステップ：形成されたスイッチセル20Nあるいは20P(またはその両方)を行列状に配置し、複数のスイッチ制御線29A～29Cの各々に対し、所定のスイッチセル20Nあるいは20P(またはその両方)を接続してスイッチブロック20を形成する。

第3ステップ：スイッチブロック2の作成済みデータを、X軸またはY軸と平行なラインを軸としてミラー反転し、または、セル中心を軸として180度回転(180度反転)することにより、反転スイッチブロックを形成する。

第4ステップ：配置されたスイッチブロックおよび反転スイッチブロック間で複数のスイッチ制御線29A～29Cおよび第2電源線を接続し、電圧セル線23A, 23Bを回路ブロック1の内部電圧線11と接続する。

#### 【0072】

重複するが、より具体的に説明すると、制御セル線25、電圧セル線23Aと23B、および、電源セル線24Aと24B(または、2つの電源セル線24AB)が、X軸とY軸のそれぞれに対して対称である。このため、スイッチセル20NをX軸またはY軸に沿

10

20

30

40

50

ったラインを反転軸としてミラー反転し、あるいは、セル中心を軸として180度回転しても、上記5本のセル線の位置関係は元のままである。

とくにトランジスタまで2軸対称配置されている図5の場合は、あるスイッチブロック2を、例えば図4のようにスイッチ制御線まで設計した段階で、ブロックごとミラー反転または180度回転しても、行列状のスイッチセル群において、図11に示す、各スイッチセル20Nの基本パターンに何ら変化はない。変化があるのは、ブロック内で対称配置されていない、第3配線層(3M)以上の配線層により形成された、スイッチ制御線29A~29Cとその接続線である。

#### 【0073】

回路ブロック1から第1および第2スイッチ制御線35\_1, 35\_2の各々の距離が同じであると、ブロック間配線が容易である。また、トランジスタのゲートの向き(長手方向)は、特性を揃えるため集積回路内で同じとする制約があることが多い。このような場合、回路ブロック1の4辺に配置するスイッチブロックは、辺ごとに異なるパターンとなる。

しかしながら、図11に示すような、5本のセル線、即ち電圧セル線23Aと23B、電源セル線24Aと24B、および、制御セル線25が2軸対称性を有するスイッチセルを用いると、前述した第1~第5ステップの手順を有する方法によって、簡単にスイッチブロックの設計が可能になる。

#### 【0074】

この5本のセル線の関係が、ミラー反転または180度回転の前後で変化せず、それより上層の配線が変化することを利用すると、第1および第2ステップで、回路ブロック1の対向する2辺のうち、一方の辺側に配置すべき1つのスイッチブロック2を設計後に、設計後のスイッチブロック2のデータを、上記2辺と平行なラインを軸としてミラー反転する、あるいは、180度回転することにより、他の辺側に配置すべきもう片方のスイッチブロック2のデータを、容易に作成できる(第3ステップ)。

同様にして、他の2辺においても、その1つの辺側に配置すべきスイッチブロック2を第1および第2ステップで設計後に、設計後のデータをミラー反転または180度回転することにより(第3ステップ)、他の1つの辺側に配置すべきスイッチブロック2のデータを容易に作成できる。

このようにして作成された4種類のスイッチブロック(2U, 2D, 2L, 2R)は、それらのスイッチ制御線29A~29Cそれぞれの、回路ブロック1までの距離が、4種類のスイッチブロックで同じであるため、第4ステップにおけるスイッチ制御線のブロック間接続が容易である。また、このことは、スイッチブロック間接続すべき他の配線についても言える。

#### 【0075】

次に、第2の利点として、スイッチセルの設計自体が容易であることを説明する。

5本のセル線の対称性に加え、図11や図12のように、トランジスタのパターンまで2軸対称であると、X軸とY軸で区画される第1~第4象限のパターン(以下、4分割パターンという)は、その1つの4分割パターンを設計し、後は、設計後のパターンデータをコピーし、ミラー反転、あるいは、ミラー反転と180度回転を組み合わせながらペーストするだけで、残りの3つの4分割パターンが形成され、スイッチセルの設計が完結する。

よって、スイッチセルの設計が非常に容易である。また、4分割パターンを最初に設計する段階で、最大限のゲート幅が確保できるように高密度設計すると、無駄がないスイッチセルの設計ができる。

#### 【0076】

本実施形態によれば、以下の利益が得られる。

電源遮断対象の回路ブロック1の周囲に複数配置されるスイッチブロックが、電源電圧または基準電圧が印加される環状レール線の一部となる電圧線セグメントとスイッチを備える。このため、当該電圧線セグメントとスイッチ間の位置関係が固定された状態でスイ

10

20

30

40

50

ツチブロックを移動、挿入、削除するだけで、あたかも、環状線レールに沿ってスイッチセグメントを自由に移動し、新たに挿入し、あるいは削除することが容易に行える。

#### 【0077】

特に、図15に示すように、電源遮断対象の回路ブロック1の4辺の各辺からみた、当該回路ブロック1への電源電圧または基準電圧を供給する配線（本実施形態の説明においては、具体的には実VSS配線5および環状レール線3）の配線のインピーダンスが小さいほどスイッチブロック数を増やすように、複数のスイッチブロックが配置されている。

図15では、太い矢印で示す側のインピーダンスが、細い矢印で示す側より低い。つまり、太い矢印の側には図1に示す入出力セル40が配置されているため、外部からの基準電圧が0[V]にほぼ近い値をとる。これに対し、細い矢印で示す側には常時動作する他の回路ブロック（例えば通電回路ブロック32）が配置されているため、実VDD線の電位が、時間平均をとると0[V]より高い状態となる。

#### 【0078】

このような場合、スイッチブロックを基準電圧が0[V]に固定されている側で多く配置すると、同じスイッチオンの時間内に、より効率的に内部電圧線11の放電が進む。これとは逆に、基準電圧が0[V]より高い側にスイッチを多く配置すると、同じ放電効果を得るにはスイッチブロック数を多くしなければならないため、無駄が多い。

#### 【0079】

本実施形態では、このような効果的なスイッチブロックの配置が容易に行えるという効果がある。

具体的には、設計の後半での消費電力確定時での対応ができ、従来よりも使用するスイッチブロック数を削減できる。スイッチブロック数を減らして、スイッチトランジスタの総ゲート幅を削減すると、リーク電流が、その分減り、電力削減効果がある。また、入出力セル40側は動作している回路ブロックが存在しないため、放電による電源ノイズの影響が小さく、他の回路ブロックへの動作スピードへの悪影響を抑えることができる。

また、電源電圧や基準電圧が印加される環状線を、スイッチと重ねて配置できるため、面積削減効果も大きい。

#### 【0080】

また、2軸対称パターンを有するスイッチセルを用いた場合に、前述した第1の利点（スイッチブロックの設計が容易）と第2の利点（スイッチセルの設計自体が容易）が得られる。

#### 【図面の簡単な説明】

#### 【0081】

【図1】本発明の実施形態に関わる半導体集積回路の全体構成を示すブロック図である。

【図2】実施形態に関わる、電源遮断対象の回路ブロックの内部構成図である。

【図3】実施形態のレール配置例1を示す図である。

【図4】実施形態のレール配置例2を示す図である。

【図5】実施形態において、回路ブロックとその周囲のスイッチブロックに対する、制御線の配線を示す図である。

【図6】環状レール線を有しない構成を示すブロック図である。

【図7】実施形態において、スイッチトランジスタの配置を模式的に示す図である。

【図8】実施形態に関わり、（A）は上部スイッチブロックの構成図、（B）は下部スイッチブロックの構成図である。

【図9】実施形態に関わり、（A）は左側スイッチブロックの構成図、（B）は右側スイッチブロックの構成図である。

【図10】多層配線構造における各階層の配線層の使用状況を1M～7Mの符号により示す図である。

【図11】実施形態に関わるスイッチセルの概略的なレイアウト図である。

【図12】実施形態に関わる他のスイッチセルの概略的なレイアウト図である。

【図13】実施形態に関わり、（A）は図11のスイッチセルを用いて形成した上部スイ

10

20

30

40

50

ツチブロックの構成図、(B)は下部ツチブロックの構成図である。

【図14】実施形態に関わり、(A)は図11のツチセルを用いて形成した左側ツチブロックの構成図、(B)は右側ツチブロックの構成図である。

【図15】実施形態において、ツチブロック数の適正配置を示す図である。

【符号の説明】

【0082】

1...電源遮断対象の回路ブロック、2...ツチブロック、2U...上部ツチブロック、2D...下部ツチブロック、2L...左側ツチブロック、2R...右側ツチブロック、3...環状レール線、3V...仮想環状レール線、5...実VSS配線、11...内部電圧線、21...電圧線セグメント、21A, 21B...ゲート電極、21C...連結部、21V...仮想電圧線セグメント、22A, 22B...N型活性領域、22AP, 22BP...、P型活性領域、23A, 23B...電圧セル線、24A, 24B...電源セル線、24S...ソース線、25...制御セル線、28...ドレイン線、34...制御回路、35...制御線、35\_1...第1ツチ制御線、35\_2...第2ツチ制御線、BUF1, BUF2...バッファ回路、SWT...ツチトランジスタ

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【 8 】

【 図 9 】

【図10】

【図11】

【 図 1 2 】

【図13】

【図14】

【図15】

---

フロントページの続き

(56)参考文献 特開2007-158035(JP, A)

国際公開第2006/114875(WO, A1)

(58)調査した分野(Int.Cl., DB名)

H01L27/04

H01L21/82