(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7566708号**

**(P7566708)**

(45)発行日 令和6年10月15日(2024.10.15)

(24)登録日 令和6年10月4日(2024.10.4)

(51)国際特許分類

H 01 L 31/12 (2006.01)

F I

H 01 L 31/12

H 01 L 31/12C

F

請求項の数 6 (全11頁)

(21)出願番号 特願2021-152824(P2021-152824)

(22)出願日 令和3年9月21日(2021.9.21)

(65)公開番号 特開2023-44783(P2023-44783A)

(43)公開日 令和5年4月3日(2023.4.3)

審査請求日 令和5年9月19日(2023.9.19)

|          |                                                 |

|----------|-------------------------------------------------|

| (73)特許権者 | 000003078<br>株式会社東芝<br>東京都港区芝浦一丁目1番1号           |

| (73)特許権者 | 317011920<br>東芝デバイス＆ストレージ株式会社<br>東京都港区芝浦一丁目1番1号 |

| (74)代理人  | 110003708<br>弁理士法人鈴榮特許総合事務所                     |

| (72)発明者  | 劉 佳<br>東京都港区芝浦一丁目1番1号 東芝デバイス＆ストレージ株式会社内         |

| (72)発明者  | 堀 将彦<br>東京都港区芝浦一丁目1番1号 東芝デバイス＆ストレージ株式会社内        |

| 審査官      | 桂城 厚                                            |

最終頁に続く

(54)【発明の名称】 半導体装置

**(57)【特許請求の範囲】****【請求項1】**

第1方向及び第2方向に延伸する第1面を有する基板と、

前記基板の前記第1面上に設けられ、前記第1方向及び前記第2方向と交差する第3方向を向いた第2面を有し、前記第2面上に設けられた第1電極及び第2電極を含む第1のMOSFETと、

前記基板の前記第1面上に設けられ、前記第3方向に延伸する支持台と、

前記支持台の前記第1方向を向いた第3面に接し、前記第1方向を向いた第4面を有し、前記第4面上に設けられた第3電極及び第4電極を含む受光素子と、

前記受光素子の前記第4面に接する発光素子と、

前記第1電極と前記第3電極とに接続される第1配線と、

前記第2電極と前記第4電極とに接続される第2配線と

を備える半導体装置。

**【請求項2】**

前記第3面及び前記第4面は、前記第1方向の前記第1のMOSFETが配置されている側を向いている、

請求項1に記載の半導体装置。

**【請求項3】**

前記受光素子の受光面は、前記第4面上に設けられ、

前記発光素子の照射面は、前記受光面と向かい合う、

請求項 1 または 2 に記載の半導体装置。

**【請求項 4】**

前記第 1 面に設けられた第 2 の M O S F E T を更に備え、

前記第 1 の M O S F E T のソースと、前記第 2 の M O S F E T のソースとが電気的に接続される、

請求項 1 乃至 3 のいずれか一項に記載の半導体装置。

**【請求項 5】**

前記第 1 面に設けられた第 5 電極を更に備え、

前記発光素子は、前記第 1 方向を向いた第 5 面に設けられた第 6 電極を含み、

前記第 5 電極と前記第 6 電極とは電気的に接続される、

請求項 1 乃至 4 のいずれか一項に記載の半導体装置。

**【請求項 6】**

前記第 5 電極と前記第 6 電極とに接続され、前記第 5 電極との接続位置から前記第 3 方向に延伸する部分と、前記第 6 電極との接続位置から前記第 1 方向に延伸して折れ曲がる部分とを含む第 3 配線を更に備える、

請求項 5 に記載の半導体装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明の実施形態は、半導体装置に関する。

20

**【背景技術】**

**【0002】**

半導体装置として、フォトリレー装置が知られている。フォトリレー装置は、発光素子及び受光素子を含む半導体リレー装置である。フォトリレー装置は、無接点のリレーであり、交流信号または直流信号の伝送に用いられる。

**【先行技術文献】**

**【特許文献】**

**【0003】**

【文献】特許第 5 9 8 5 4 5 2 号公報

【文献】特開 2 0 0 3 - 8 4 1 7 3 号公報

30

【文献】特開 2 0 0 5 - 1 2 3 2 7 4 号公報

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0004】**

高周波信号の伝送特性を改善できる半導体装置を提供する。

**【課題を解決するための手段】**

**【0005】**

実施形態に係る半導体装置は、第 1 方向及び第 2 方向に延伸する第 1 面を有する基板と、基板の第 1 面に設けられ、第 1 方向及び第 2 方向と交差する第 3 方向を向いた第 2 面を有し、第 2 面に設けられた第 1 電極及び第 2 電極を含む第 1 の M O S F E T と、基板の第 1 面の上方に設けられ、第 3 方向に延伸する支持台と、支持台の第 1 方向を向いた第 3 面に接し、第 1 方向を向いた第 4 面を有し、第 4 面に設けられた第 3 電極及び第 4 電極を含む受光素子と、受光素子の第 4 面に接する発光素子と、第 1 電極と第 3 電極とに接続される第 1 配線と、第 2 電極と第 4 電極とに接続される第 2 配線とを含む。

40

**【図面の簡単な説明】**

**【0006】**

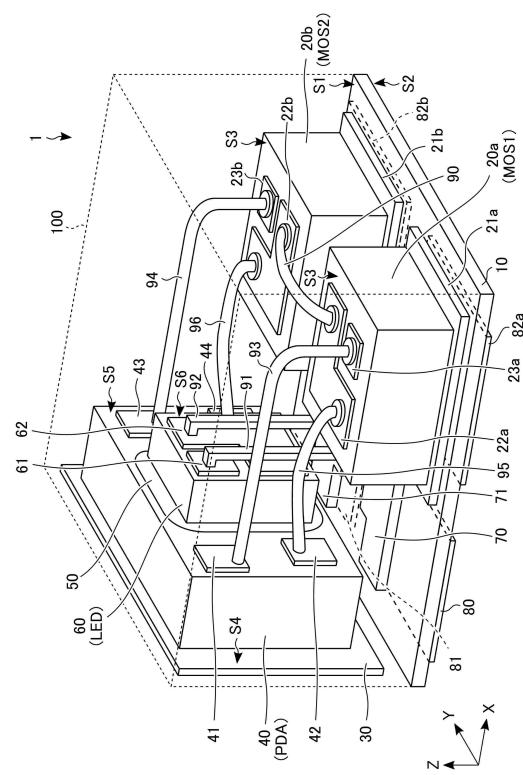

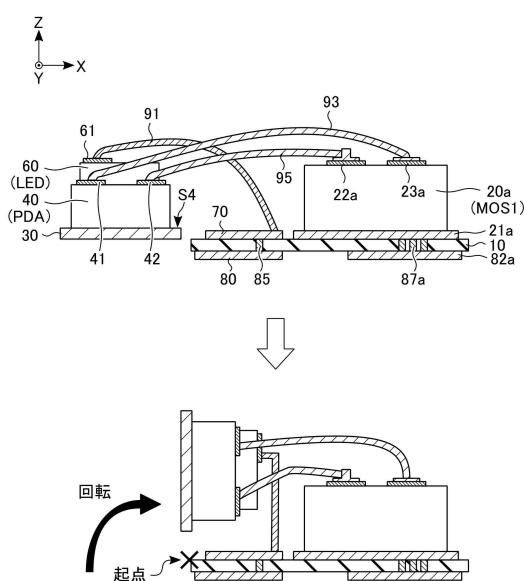

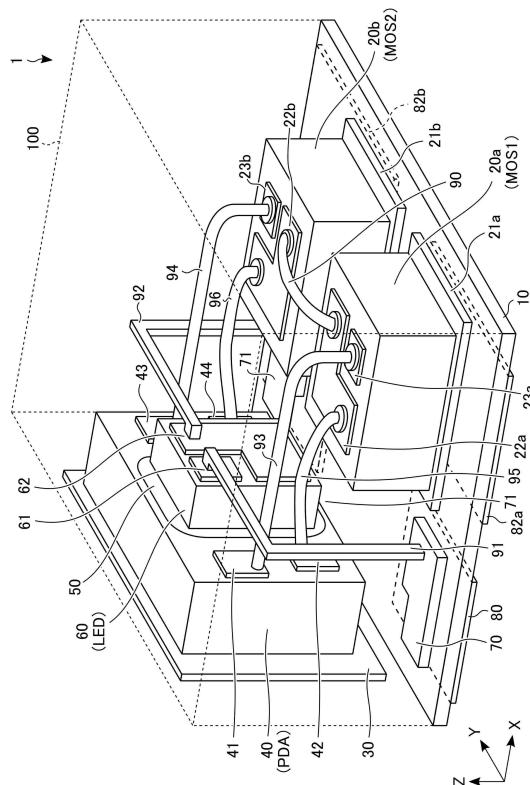

【図 1】図 1 は、第 1 実施形態に係るフォトリレー装置の斜視図である。

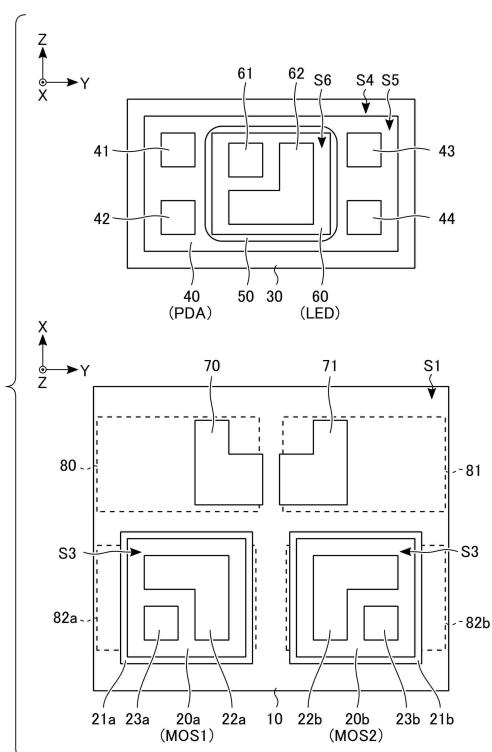

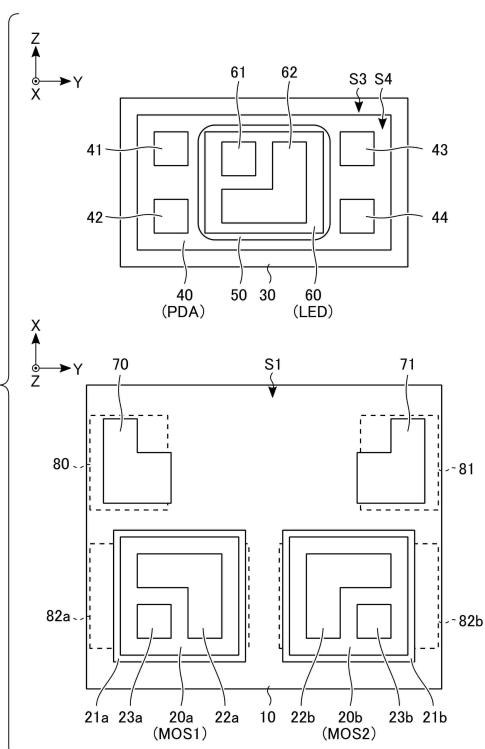

【図 2】図 2 は、第 1 実施形態に係るフォトリレー装置の基板の平面及び支持台の平面を示す図である。

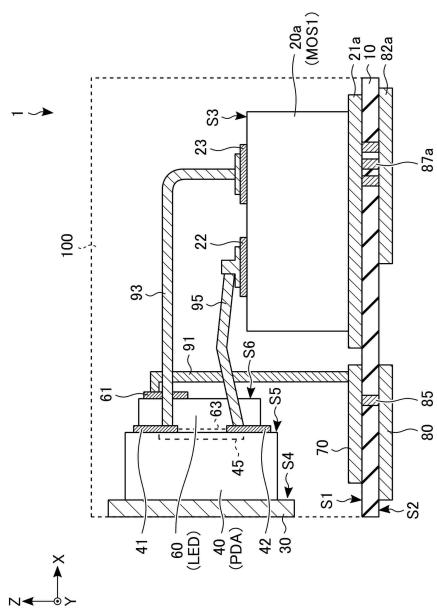

【図 3】図 3 は、第 1 実施形態に係るフォトリレー装置の断面図である。

50

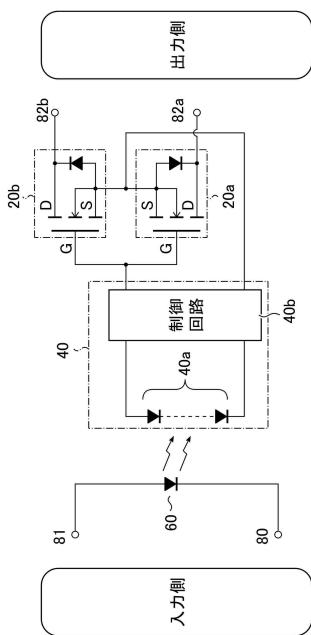

【図4】図4は、第1実施形態に係るフォトリレー装置の回路図である。

【図5】図5は、第1実施形態に係るフォトリレー装置における受光素子及び発光素子を縦方向に配置する工程を示す図である。

【図6】図6は、第2実施形態に係るフォトリレー装置の斜視図である。

【図7】図7は、第2実施形態に係るフォトリレー装置の基板の平面及び支持台の平面を示す図である。

#### 【発明を実施するための形態】

##### 【0007】

以下に実施形態が図面を参照して記述される。以下の記述において、略同一の機能及び構成を有する構成要素は同一符号を付され、繰り返しの説明は省略される場合がある。また、ある実施形態についての記述は全て、明示的に又は自明的に排除されない限り、別の実施形態の記述としても当てはまる。

10

##### 【0008】

本明細書及び特許請求の範囲において、ある第1要素が別の第2要素に「接続されている」とは、第1要素が直接的又は常時あるいは選択的に導電性となる要素を介して第2要素に接続されていることを含む。

20

##### 【0009】

###### 1. 第1実施形態

第1実施形態について、説明する。本実施形態では、半導体装置の例として、フォトリレー装置について説明する。

##### 【0010】

###### 1.1 全体構成

まず、図1及び図2を参照して、フォトリレー装置1の全体構成の一例について説明する。図1は、フォトリレー装置1の斜視図である。図2は、フォトリレー装置1の基板10の平面及び支持台30の平面を示す図である。以下の説明では、フォトリレー装置1の基板10に平行な方向をX方向とする。基板10に平行であり、X方向と交差する方向をY方向とする。基板10に垂直であり（基板10と交差し）、X方向及びY方向に交差する方向をZ方向（または「縦方向」と表記する）とする。なお、図2では、説明を簡略化するためは、電極間を接続する配線は省略されている。

30

##### 【0011】

図1及び図2に示すように、フォトリレー装置1は、基板10、2つのMOSFET（Metal Oxide Semiconductor Field Effect Transistor）20a及び20b、支持台30、受光素子40、発光素子60、電極70及び71、入力端子80及び81、出力端子82a及び82b、配線90～96、並びに封止樹脂100を含む。

##### 【0012】

基板10は、例えば、ポリイミドを用いたフレキシブル基板（FPC：Flexible Printed Circuits）である。なお、基板10は、フレキシブル基板に限定されない。基板10は、例えば、X方向及びY方向に延伸する板状の形状を有する。

40

##### 【0013】

MOSFET20a及び20bは、例えばエンハンスマント型のnチャネルMOSトランジスタである。MOSFET20a及び20bは、伝送する交流信号または直流信号の制御に用いられる。MOSFET20a及び20bがオン状態の場合、フォトリレー装置1は、信号を伝送し、MOSFET20a及び20bがオフ状態の場合、フォトリレー装置1は、信号を伝送しない。

##### 【0014】

MOSFET20a（以下、「MOS1」とも表記する）は、電極21a、22a、及び23aを含む。電極21aは、MOSFET20aのドレイン電極として機能する。電極22aは、MOSFET20aのソース電極として機能する。電極23aは、MOSFET20aのゲート電極として機能する。電極21aは、基板10のZ方向を向いた面S1上に設けられる。すなわち、電極21aは、基板10の面S1上に設けられたダイバッ

50

ドとも呼べる。電極 21a 上に、MOSFET 20a が設けられている。MOSFET 20a の電極 21a と接する面と対向する Z 方向を向いた面 S3 には、電極 22a 及び電極 23a が設けられている。

#### 【0015】

MOSFET 20b (以下、「MOS 2」とも表記する) は、MOSFET 20a と同じ構造を有する。例えば、MOSFET 20b は、基板 10 の面 S1 の上方において、MOSFET 20a と、Y 方向に並んで配置されている。なお、MOSFET 20a 及び MOSFET 20b の配置は任意である。

#### 【0016】

MOSFET 20b は、電極 21b、22b、及び 23b を含む。電極 21b は、MOSFET 20b のドレイン電極として機能する。電極 22b は、MOSFET 20b のソース電極として機能する。電極 23b は、MOSFET 20b のゲート電極として機能する。電極 21b は、基板 10 の Z 方向を向いた面 S1 上に設けられる。すなわち、電極 21b は、基板 10 の面 S1 上に設けられたダイパッドとも呼べる。電極 21b 上に、MOSFET 20b が設けられている。MOSFET 20b の電極 21b と接する面と対向する Z 方向を向いた面 S3 には、電極 22b 及び電極 23b が設けられている。図 2 の例では、電極 22b 及び電極 23b は、MOSFET 20a の電極 22a 及び電極 23a と、X 方向を中心軸として、対称となるように配置されている。

#### 【0017】

MOSFET 20a の電極 22a と MOSFET 20b の電極 22b とは、配線 90 により共通に接続されている。すなわち、MOSFET 20a のソースと MOSFET 20b のソースが共通に接続されている。なお、配線 90 の本数は、1 本以上であればよい。

#### 【0018】

支持台 30 は、受光素子 40 及び発光素子 60 を支持する。支持台 30 は、導電体であってもよいし、絶縁体であってもよい。支持台 30 は、Y 方向及び Z 方向に延伸する板状の形状を有する。支持台 30 は、例えば、基板 10 の面 S1 に対して、縦方向 (垂直、または Z 方向) に配置される。

#### 【0019】

受光素子 40 は、PDA (Photo Diode Array)、またはフォトトランジスタ等である。以下では、受光素子 40 が PDA である場合について説明する。受光素子 40 は、X 方向を向いた支持台 30 の面 S4 に接する。より具体的には、支持台 30 の面 S4 は、X 方向の MOSFET 20a 及び 20b が配置されている側を向いている。受光素子 40 は、基板 10 に対して縦方向に配置される。受光素子 40 は、支持台 30 に接する面と対向する X 方向を向いた面 S5 に、受光面を有する。換言すれば、受光素子 40 の面 S5 は、X 方向の MOSFET 20a 及び 20b が配置されている側を向いている。受光素子 40 は、電極 41 ~ 44 を含む。電極 41 ~ 44 は、受光素子 40 の支持台 30 に接する面と対向する X 方向を向いた面 S5 上に、設けられている。例えば、電極 41 及び 43 は、受光素子 40 内において共通に接続されている。例えば、電極 42 及び 44 は、受光素子 40 内において共通に接続されている。電極 41 は、配線 93 を介して、MOSFET 20a の電極 22a に接続される。電極 42 は、配線 95 を介して、MOSFET 20a の電極 23a に接続される。電極 43 は、配線 94 を介して、MOSFET 20b の電極 22b に接続される。電極 44 は、配線 96 を介して、MOSFET 20b の電極 23b に接続される。

#### 【0020】

発光素子 60 は、例えば、LED (Light Emitting Diode) である。発光素子 60 は、接着層 50 を介して、受光素子 40 の面 S5 上に配置される。発光素子 60 は、基板 10 に対して縦方向に配置される。なお、接着層 50 には、透光性を有する絶縁材料が用いられる。発光素子 60 の光の照射面は、受光素子 40 の受光面、すなわち、受光素子 40 の面 S5 と向かい合う。発光素子 60 は、電極 61 及び 62 を含む。電極 61 及び 62 は、発光素子 60 の受光素子 40 と接する面と対向する X 方向を向いた面 S6 上に設けられ

10

20

30

40

50

る。換言すれば、発光素子 6 0 の面 S 6 は、X 方向の M O S F E T 2 0 a 及び 2 0 b が配置されている側を向いている。電極 6 1 及び 6 2 は、いずれか一方が発光素子 6 0 のアノード電極であり、他方が発光素子 6 0 のカソード電極である。

#### 【 0 0 2 1 】

電極 7 0 及び 7 1 は、基板 1 0 の面 S 1 上に設けられる。電極 7 0 は、配線 9 1 を介して、発光素子 6 0 の電極 6 1 に接続される。電極 7 1 は、配線 9 2 を介して、発光素子 6 0 の電極 6 2 に接続される。配線 9 1 は、例えば、Z 方向に延伸し、一端が電極 6 1 に接続され、他端が、電極 7 0 に接続される。同様に、配線 9 2 は、例えば、Z 方向に延伸し、一端が電極 6 2 に接続され、他端が、電極 7 1 に接続される。

#### 【 0 0 2 2 】

入力端子 8 0 及び 8 1 、並びに出力端子 8 2 a 及び 8 2 b は、基板 1 0 の面 S 1 と対向する面 S 2 上に設けられる。

#### 【 0 0 2 3 】

入力端子 8 0 及び 8 1 は、外部に設けられた図示せぬ直流電源に接続される。入力端子 8 0 及び 8 1 には、フォトリレー装置 1 を制御するための電圧が印加される。入力端子 8 0 は、基板 1 0 を貫通する図示せぬ導電体を介して電極 7 0 に電気的に接続される。入力端子 8 1 は、基板 1 0 を貫通する図示せぬ導電体を介して電極 7 1 に電気的に接続される。

#### 【 0 0 2 4 】

出力端子 8 2 a 及び 8 2 b は、外部に設けられた回路等にそれぞれ接続される。出力端子 8 2 a は、基板 1 0 を貫通する導電体を介して M O S F E T 2 0 a の電極 2 1 a に電気的に接続される。出力端子 8 2 b は、基板 1 0 を貫通する導電体を介して M O S F E T 2 0 b の電極 2 1 b に電気的に接続される。M O S F E T 2 0 a 及び 2 0 b がオン状態の場合、出力端子 8 2 a 及び 8 2 b は電気的に接続される。これにより、フォトリレー装置 1 を介して交流または直流信号が伝送される。

#### 【 0 0 2 5 】

配線 9 0 ~ 9 6 は、導電材料により構成される。なお、配線 9 1 ~ 9 6 は、ワイヤボンディングにより形成されたワイヤであってもよいし、フレキシブル基板の配線であってもよい。

#### 【 0 0 2 6 】

封止樹脂 1 0 0 は、基板 1 0 の面 S 1 の上方に配置された、M O S F E T 2 0 a 及び 2 0 b 、受光素子 4 0 、発光素子 6 0 、並びに配線 9 0 ~ 9 6 を覆い保護する。また、封止樹脂 1 0 0 は、縦方向に配置された支持台 3 0 、受光素子 4 0 、及び発光素子 6 0 の位置を固定する。なお、封止樹脂 1 0 0 は、複数の樹脂材を含んでいてもよい。例えば、封止樹脂 1 0 0 は、発光素子 6 0 を被覆する第 1 封止樹脂と基板 1 0 の面 S 1 の上方全体を被覆する第 2 封止樹脂により構成されていてもよい。

#### 【 0 0 2 7 】

##### 1 . 2 フォトリレー装置の断面構成

次に、図 3 を参照して、フォトリレー装置 1 の断面構成の一例について説明する。図 3 は、Y 方向を向いた側面から見たフォトリレー装置の断面図である。

#### 【 0 0 2 8 】

図 3 に示すように、X 方向に向かって支持台 3 0 の面 S 3 上に受光素子 4 0 及び発光素子 6 0 が積層されている。支持台 3 0 、受光素子 4 0 、及び発光素子 6 0 の積層構造体は、基板 1 0 の面 S 1 の上方に配置されている。そして、支持台 3 0 の面 S 4 、受光素子 4 0 の面 S 5 、及び発光素子 6 0 の面 S 6 は、X 方向の M O S F E T 2 0 a 及び 2 0 b が配置されている側を向いている。支持台 3 0 、受光素子 4 0 、及び発光素子 6 0 の積層構造体は、基板 1 0 及び M O S F E T 2 0 a 及び 2 0 b に対して、縦方向に配置されている。

#### 【 0 0 2 9 】

受光素子 4 0 の受光面 4 5 は、受光素子 4 0 の面 S 5 に設けられている。発光素子 6 0 の光の照射面 6 3 は、受光素子 4 0 の受光面、すなわち、受光素子 4 0 の面 S 5 と向かい合う。

10

20

30

40

50

**【 0 0 3 0 】**

電極 7 0 は、入力端子 8 0 と、基板 1 0 を関する導電体 8 5 を介して電気的に接続されている。電極 7 1 と、入力端子 8 1 との接続も同様である。

**【 0 0 3 1 】**

MOSFET 20a の電極 21a は、出力端子 82a と、基板 1 0 を関する導電体 87a を介して電気的に接続されている。なお、図 3 の例では、3 つの導電体 87a が設けられているが、導電体 87a は、1 つ以上あればよい。MOSFET 20b の電極 21b と、出力端子 82b との接続も同様である。

**【 0 0 3 2 】**

受光素子 40 及び発光素子 60 を縦方向に配置することにより、受光素子 40 の電極 41 ~ 44 と、MOSFET 20a 及び 20b の電極 22a、22b、23a、及び 23b との距離を、受光素子 40 及び発光素子 60 を MOSFET 20a 及び 20b の横に配置した場合よりも、短くすることができる。すなわち、配線 93 ~ 96 の長さを比較的短くできる。同様に、発光素子 60 の電極 61 及び 62 と、基板 1 0 上に設けられた電極 70 及び 71 と接続する配線 91 及び 92 の長さを比較的短くできる。

10

**【 0 0 3 3 】**

なお、図 3 の例では、支持台 3 0 は、基板 1 0 の面 S 1 の上方に設けられ、基板 1 0 と接していないが、Z 方向に延伸して、基板 1 0 と接してもよい。

**【 0 0 3 4 】****1 . 3 フォトリレー装置の回路構成**

20

次に、図 4 を参照して、フォトリレー装置 1 の回路構成の一例について説明する。図 4 は、フォトリレー装置 1 の回路図である。

**【 0 0 3 5 】**

図 4 に示すように、発光素子 60 は入力端子 80 及び 81 に接続される。入力端子 80 及び 81 には、フォトリレー装置 1 を制御するための入力電圧が印加される。

**【 0 0 3 6 】**

受光素子 40 は、例えば、制御回路 40a と、直列に接続された数個～数十個のフォトダイオード 40b とを含むフォトダイオードアレイである。直列接続された複数のフォトダイオード 40b の両端は、制御回路 40a に接続される。

30

**【 0 0 3 7 】**

MOSFET 20a 及び 20b のゲートは、受光素子 40 のアノードに共通に接続される。MOSFET 20a 及び 20b のソースは、受光素子 40 のカソードに共通に接続される。MOSFET 20a のドレインは、出力端子 82a に接続される。MOSFET 20b のドレインは、出力端子 82b に接続される。

40

**【 0 0 3 8 】**

入力側の発光素子 60 がオン状態（発光状態）になると、MOSFET 20a 及び 20b を駆動する受光素子 40 は、発光素子 60 から受光して、例えば、7V ~ 10 数 V の電圧を発生させる。これにより、MOSFET 20a 及び 20b がオン状態とされ、出力端子 82a 及び 82b が電気的に接続される。また、発光素子 60 がオフ状態となると、MOSFET 20a 及び 20b はオフ状態とされ、出力端子 82a 及び 82b は、電気的に非接続状態とされる。

**【 0 0 3 9 】****1 . 4 製造方法**

次に、図 5 を参照してフォトリレー装置 1 の製造方法の一例について説明する。本実施形態では、受光素子 40 及び発光素子 60 を縦方向に配置する工程に着目して説明する。図 5 は、受光素子 40 及び発光素子 60 を縦方向に配置する工程を示す図である。

**【 0 0 4 0 】**

図 5 に示すように、例えば、支持台 3 0 の面 S 4 が Z 方向を向いた状態で、支持台 3 0 、受光素子 40 、及び発光素子 60 の積層構造体が、基板 1 0 と隣り合って配置されている。この状態で、各電極が電気的に接続される。例えば、図 5 の例では、MOSFET 2

50

0 a の電極 2 2 a と、受光素子 4 0 の電極 4 2 とが、配線 9 5 を介して電気的に接続される。MOSFET 2 0 a の電極 2 3 a と、受光素子 4 0 の電極 4 1 とが、配線 9 3 を介して電気的に接続される。発光素子 6 0 の電極 6 1 と、電極 7 0 とが、配線 9 1 を介して電気的に接続される。他の電極も同様である。

#### 【0041】

次に、例えば、支持台 3 0 、受光素子 4 0 、及び発光素子 6 0 の積層構造体は、基板 1 0 の X 方向の端部を起点として、90 度回転されて、縦方向の配置とされる。その後、封止樹脂 1 0 0 により、MOSFET 2 0 a 及び 2 0 b 、受光素子 4 0 、並びに発光素子 6 0 が覆われる。なお、受光素子 4 0 及び発光素子 6 0 を縦方向に配置する方法はこれに限定されない。

10

#### 【0042】

##### 1.5 本実施形態に係る効果

本実施形態に係る構成であれば、例えば、1 GHz 以上の高周波信号の伝送特性を改善できる。本効果につき、詳述する。

#### 【0043】

例えば、フォトリレー装置において、受光素子及び発光素子を、MOSFET（出力端子）と、電極（入力端子）との間に配置することがある。この場合、受光素子と入力端子との間、及び受光素子と出力端子との間で結合容量が生じる。この結合容量の影響により、例えば 1 GHz 以上の高周波伝送特性が劣化することがある。また、例えば、受光素子と MOSFET とを接続する配線の長さが長くなるとオープンスタブの影響により、より低い周波数領域で、伝送特性が劣化する。

20

#### 【0044】

これに対し、本実施形態に係る構成であれば、フォトリレー装置 1 は、受光素子 4 0 及び発光素子 6 0 を縦方向に配置できる。これにより、受光素子 4 0 と入力端子 8 0 及び 8 1 との間、及び受光素子 4 0 と出力端子 8 2 a 及び 8 2 b との間で生じる結合容量を低減できる。更に、入力端子 8 0 と入力端子 8 1 との間で生じる結合容量を低減できる。また、受光素子 4 0 及び発光素子 6 0 を縦方向に配置することにより、受光素子 4 0 の電極と、MOSFET 2 0 a 及び 2 0 b の電極とを接続する配線の長さを比較的短くできる。同様に、発光素子 6 0 の電極 6 1 及び 6 2 と、基板 1 0 上に設けられた電極 7 0 及び 7 1 と接続する配線の長さを比較的短くできる。したがって、オープンスタブの影響をより高周波領域にシフトさせることができる。従って、半導体装置の高周波信号の伝送特性を改善できる。

30

#### 【0045】

更に、本実施形態に係る構成であれば、受光素子 4 0 及び発光素子 6 0 を縦方向に配置することにより、フォトリレー装置 1 の設置面積を低減できる。すなわち、フォトリレー装置 1 を小型化できる。

#### 【0046】

##### 2. 第 2 実施形態

次に、第 2 実施形態について説明する。第 2 実施形態では、第 1 実施形態と異なるフォトリレー装置 1 の構成について説明する。以下、第 1 実施形態と異なる点を中心に説明する。

40

#### 【0047】

##### 2.1 全体構成

図 6 及び図 7 を参照して、フォトリレー装置 1 の全体構成の一例について説明する。図 6 は、フォトリレー装置 1 の斜視図である。図 7 は、フォトリレー装置 1 の基板 1 0 の平面及び支持台 3 0 の平面を示す図である。なお、図 7 では、説明を簡略化するため、電極間を接続する配線は省略されている。

#### 【0048】

図 6 及び図 7 に示すように、本実施形態のフォトリレー装置 1 の MOSFET 2 0 a 及び 2 0 b 、受光素子 4 0 、並びに発光素子 6 0 の配置は、第 1 実施形態の図 1 と同様であ

50

る。

#### 【0049】

本実施形態の電極70は、例えば、Y方向において、MOSFET20aよりも基板10の端部に配置されている。同様に、電極71は、例えば、Y方向において、MOSFET20bよりも基板10の端部に配置されている。

#### 【0050】

配線91及び92は、第1実施形態と配線レイアウトが異なる。配線91は、例えば、電極61との接続位置からY方向に延伸して、電極70の上方において、電極70に向かって折れ曲がっている。そして、配線91は、Z方向に延伸して電極70に接続されている。同様に、配線92は、例えば、電極62との接続位置からY方向に延伸して、電極71の上方において、電極71に向かって折れ曲がっている。そして、配線92は、Z方向に延伸して電極71に接続されている。これにより、Y方向において、配線91と配線92との間に、X方向に延伸する配線93～94が配置されている。10

#### 【0051】

##### 2.2 本実施形態に係る効果

本実施形態に係る構成であれば、第1実施形態と同様の効果が得られる。

#### 【0052】

更に、本実施形態に係る構成であれば、配線91及び92と、配線93～96との距離を比較的大きくできる。これにより、配線間の電磁干渉を低減できる。

#### 【0053】

##### 3.その他

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。20

#### 【符号の説明】

#### 【0054】

1…フォトリレー装置、20a、20b…MOSFET、21a、21b、22a、22b、23a、23b、41～44、61、62、70、71…電極、30…支持台、40…受光素子、40a…制御回路、40b…フォトダイオード、45…受光面、50…接着層、60…発光素子、63…照射面、80、81…入力端子、82a、82b…出力端子、85、87a…導電体、90～96…配線、100…封止樹脂30

【义面】

【 句 1 】

【 図 2 】

【 四 3 】

### 【図4】

10

20

30

40

50

【図5】

【 四 6 】

〔 四 7 〕

10

20

30

40

50

---

フロントページの続き

- (56)参考文献

- 特開平11-274548 (JP, A)

特開2021-089971 (JP, A)

特開2015-056531 (JP, A)

特開2015-050281 (JP, A)

国際公開第2015/129178 (WO, A1)

特開2002-134823 (JP, A)

特開2003-084173 (JP, A)

特開2005-294494 (JP, A)

特開2005-123274 (JP, A)

米国特許第05654559 (US, A)

- (58)調査した分野 (Int.Cl., DB名)

- H01L 31/00 - 31/0392

H01L 31/08 - 31/20