(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 698 37 674 T2 2008.01.10

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 1 021 827 B1

(51) Int Cl.<sup>8</sup>: H01L 21/768 (2006.01)

(21) Deutsches Aktenzeichen: 698 37 674.9

(86) PCT-Aktenzeichen: PCT/US98/17010

(96) Europäisches Aktenzeichen: 98 939 967.0

(87) PCT-Veröffentlichungs-Nr.: WO 1999/009593

(86) PCT-Anmeldetag: 17.08.1998

(87) Veröffentlichungstag

der PCT-Anmeldung: 25.02.1999

(97) Erstveröffentlichung durch das EPA: 26.07.2000

(97) Veröffentlichungstag

der Patenterteilung beim EPA: 25.04.2007

(47) Veröffentlichungstag im Patentblatt: 10.01.2008

(30) Unionspriorität:

914521 19.08.1997 US

(84) Benannte Vertragsstaaten:

BE, DE, GB, NL

(73) Patentinhaber:

Applied Materials, Inc., Santa Clara, Calif., US

(72) Erfinder:

CHEN, Liang-Yuh, San Jose, CA 95131, US; TAO, Rong, San Jose, CA 95129, US; GUO, Ted, Palo Alto, CA 94303, US; MOSELY, Roderick Craig, Pleasanton, CA 94588, US

(54) Bezeichnung: DOPPELDAMASZEN-METALLISIERUNG

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

**Beschreibung****HINTERGRUND DER ERFINDUNG****Gebiet der Erfindung**

**[0001]** Die vorliegende Erfindung bezieht sich auf ein Metallisierungsverfahren zur Herstellung von Halbleiterbauelementen. Insbesondere bezieht sich die vorliegende Erfindung auf eine Metallisierung von Doppeldamaszen-Umgrenzungen für Kontaktloch und Leiter in einer dielektrischen Schicht zur Bildung von Metallzwischenverbindungen und Metallkontaktlochverschlüssen.

**Hintergrund der verwandten Technik**

**[0002]** Die Vielniveau-Metallisierung im Bereich unter einem halben  $\mu\text{m}$  ist eine der Schlüsseltechnologien für die nächste Generation mit sehr hohem Integrationsgrad (VLSI – Very Large Scale Integration). Die Vielniveau-Zwischenverbindungen, die das Wesen dieser Technologie sind, erfordern eine Planarisierung der in Öffnungen mit hohem Seitenverhältnis ausgebildeten Zwischenverbindungsstrukturen, zu denen Kontakte, Durchgangslöcher, Leiter oder andere Strukturen gehören. Eine zuverlässige Ausbildung dieser Zwischenverbindungsstrukturen ist für den Erfolg des VLSI und für die fortgesetzte Anstrengung sehr wichtig, die Schaltungsdichte und Qualität an einzelnen Substraten und Chips zu steigern.

**[0003]** Wenn die Schaltungsdichten erhöht werden, müssen die Breiten von Durchgangslöchern, Kontakten und anderen Strukturen sowie der dielektrischen Materialien zwischen ihnen kleiner werden, was für die Strukturen ein größeres Seitenverhältnis ergibt. Deshalb nehmen die Anstrengungen zu, die sich auf die Ausbildung von hohlraumfreien Strukturen mit hohen Seitenverhältnissen richten, bei denen das Verhältnis von Strukturbreite zu Strukturhöhe 4:1 oder größer ist. Ein solches Verfahren umfasst die selektive chemische Gasphasenabscheidung (CVD – Chemical Vapor Deposition) von Material nur auf expanierten Keimbildungsoberflächen, wie sie an der Substratoberfläche vorgesehen sind. Zu einer selektiven CVD gehört die Abscheidung einer Filmschicht bei Kontakt einer Komponente der chemischen Gasphase mit einem leitenden Substrat. Die Komponente bildet Keime auf einem solchen Substrat und erzeugt eine Metalloberfläche, auf der die weitere Abscheidung weitergeht.

**[0004]** Eine selektive CVD-Metallabscheidung basiert auf der Tatsache, dass die Zersetzung eines CVD-Metallvorläufegases gewöhnlich eine Quelle von Elektronen aus einem leitenden Keimbildungsfilm erfordert. Bei einem herkömmlichen Prozess der selektiven CVD-Metallabscheidung soll das Metall im Boden einer Öffnung wachsen, wo entweder ein Me-

tallfilm oder dotiertes Silicium oder Metallsilicid aus der darunter liegenden leitenden Schicht freigelegt worden ist, sollte aber auf dielektrischen Flächen, beispielsweise den Ebenen- und Öffnungswänden, nicht wachsen. Die darunter liegenden Metallfilme oder das dotierte Silicium sind im Gegensatz zu der dielektrischen Ebene und den Öffnungswänden elektrisch leitend und sorgen für die Elektronen, die für die Zersetzung des Metallvorläufegases und die sich ergebende Zersetzung des Metalls erforderlich sind. Das durch eine selektive Abscheidung erhaltene Ergebnis ist ein epitaxiales Wachstum "vom Boden aus" des CVD-Metalls in den Öffnungen, die in der Lage sind, Kontaktlöcher oder Kontaktöffnungen mit sehr kleiner Abmessung ( $< 0,25 \mu\text{m}$ ) und hohem Seitenverhältnis ( $> 5:1$ ) zu füllen.

**[0005]** Elementares Aluminium (Al) und seine Legierungen waren die traditionellen Metalle, die wegen des niedrigen spezifischen Widerstands des Aluminiums, der überlegenen Haftung an Siliciumdioxid ( $\text{SiO}_2$ ), der leichten Strukturbildung und der hohen Reinheit zur Bildung von Leitern und Zapfen bei der Halbleiterbehandlung verwendet wurden. Darüber hinaus sind Aluminiumvorläufegase verfügbar, die den vorstehend beschriebenen selektiven CVD-Prozess erleichtern. Aluminium hat jedoch einen höheren spezifischen Widerstand und Probleme mit der Elektromigration. Die Elektromigration ist ein Phänomen, das in einer Metallschaltung, wenn sie in Betrieb ist, im Gegensatz zu einem während der Herstellung auftretenden Defekt auftritt. Die Elektromigration wird durch die Diffusion des Metalls in dem elektrischen Feld verursacht, das in der Schaltung gebildet wird. Das Metall wird von einem Ende zum anderen nach Stunden des Betriebs transportiert und führt schließlich zu einer vollständigen Trennung, was ein Öffnen der Schaltung verursacht. Dieses Problem wird manchmal durch Cu-Dotierung und eine Texturverbesserung überwunden. Die Elektromigration ist jedoch ein Problem, das schlimmer wird, wenn die Stromdichte zunimmt.

**[0006]** Andererseits haben Kupfer und seine Legierungen noch niedrigere spezifische Widerstände als Aluminium und einen beträchtlich höheren Elektromigrationswiderstand. Diese Eigenschaften sind wesentlich für das Halten von höheren Stromdichten, die sich bei hohen Integrationsniveaus ergeben, und erhöhen die Bauelementgeschwindigkeit. Die Hauptprobleme beim Integrieren von Kupfermetall in Vielniveau-Metallisierungssysteme sind jedoch (1) die Schwierigkeit der Strukturbildung aus dem Metall unter Verwendung von Ätztechniken und (2) die Schwierigkeit beim Füllen kleiner Durchgangslöcher unter Verwendung von PVD, wenn eine Nachbehandlung durch CVD-Prozesse fehlt. Für Bauelemente mit minimaler Strukturgröße unter einem  $\mu\text{m}$  sind Nassätztechniken für Kupferstrukturen aufgrund der Flüssigkeitsoberflächenspannung, des isotropen

Ätzprofils und der Schwierigkeit bei einer Überätzsteuerung nicht akzeptabel, und ein zuverlässiger Trockenätzprozess steht nicht zur Verfügung.

**[0007]** Zur Herstellung von strukturierten Kupferzwischenverbindungen wurden mehrere Verfahren vorgeschlagen, zu denen ein selektives stromloses Plattieren, eine selektive chemische Gasphasenabscheidung, eine reaktive Ionenätzung bei hoher Temperatur und eine Abhebebehandlung gehören. Das stromlose Plattieren erfordert, dass der Boden einer Zwischenverbindung geimpft wird, um den Boden leitend zu machen. Der leitende Boden kann dann geladen werden, um Kupfer aus einer Lösung oder aus einem Bad anzuziehen.

**[0008]** Zur selektiven chemischen Gasphasenabscheidung gehört gewöhnlich die Zersetzung eines Metallvorläufergases an einer elektrisch leitenden Fläche. Jedoch steht ein zuverlässiger und ausgereifter Prozess für selektives CVD-Kupfer nicht zur Verfügung.

**[0009]** Reaktives Ionenätzen (RIE – Reaktiv Ion Etching) bei hoher Temperatur oder Zerstäubungsätszen wurde ebenfalls zur Strukturierung einer Kupferschicht verwendet. Außerdem kann RIE in Verbindung mit Abhebebehandlungen verwendet werden, bei denen Überschussmetall von den Strukturen durch eine Trennschicht abgehoben wird, um eine planare Oberfläche zu belassen, in der eine Kupferstruktur ausgebildet ist.

**[0010]** Eine andere Technik zur Metallverdrahtung von Kupfer weist die Strukturierung und das Ätzen eines Grabens und/oder eines Kontaktes in einer Dickschicht aus Isoliermaterial, wie  $\text{SiO}_2$ , auf. Danach kann eine dünne Schicht aus einem Sperrmetall, wie Ti, TiW oder TiN auf der Oberseite der Isolierschicht und innerhalb des Grabens und/oder Kontakts vorgesehen werden, um als Diffusionssperre zu wirken und um eine Interdiffusion von nachher abscheidendem Metall in das Silicium und zwischen einem solchen Metall und dem Oxid zu verhindern. Nach dem Abscheiden des Sperrmetalls wird eine Kupferschicht abgelegt, um den Graben vollständig zu füllen.

**[0011]** Eine bekannte Metallisiertechnik besteht aus einem Verfahren zur Ausbildung einer Doppeldamaszen-Zwischenverbindung in einer dielektrischen Schicht, die Doppeldamaszen-Umgrenzungen für Kontaktloch und Leiter aufweist, wobei das Kontaktloch einen Boden hat, der eine darunter liegende Schicht freilegt. Zu dem Verfahren gehört die physikalische Gasphasenabscheidung einer Sperrsicht, die physikalische Gasphasenabscheidung eines leitenden Metalls, vorzugsweise Kupfer, und dann das Elektroplattieren des leitenden Metalls, um die Kontaktlöcher und Gräben auszufüllen. Abschließend

werden die abgeschiedenen Schichten und die dielektrischen Schichten planarisiert, beispielsweise durch chemisches-mechanisches Polieren, um einen Leiter zu bilden.

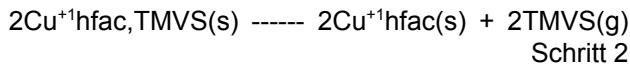

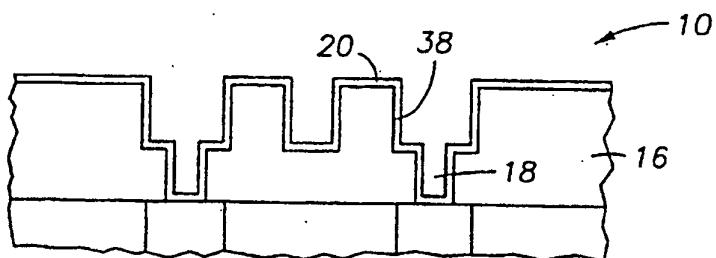

**[0012]** In [Fig. 1A](#) bis [Fig. 1E](#) ist eine Querschnittsdarstellung eines Schichtaufbaus **10** mit einer dielektrischen Schicht **16** gezeigt, die über einer darunter liegenden Schicht **14** ausgebildet ist, die elektrisch leitende Strukturen **15** enthält. Die darunter liegende Schicht **14** kann die Form eines dotierten Siliciumsubstrats haben oder kann eine erste oder darauf folgende leitende Schicht sein, die auf einem Substrat ausgebildet ist. Die dielektrische Schicht **16** wird über der darunter liegenden Schicht **14** nach bekannten Vorgängen als Teil der gesamten integrierten Schaltung ausgebildet. Wenn die dielektrische Schicht **16** abgeschieden ist, wird sie geätzt, um eine Doppeldamaszen-Umgrenzung von Kontaktloch und Leiter zu bilden, wobei das Kontaktloch einen Boden **30** hat, der einen kleinen Teil der leitenden Struktur **15** exponiert. Das Ätzen der dielektrischen Schicht **16** wird mit einem dielektrischen Ätzprozess erreicht, zu dem das Plasmaätzen gehört. Spezielle Techniken zum Ätzen von Siliciumdioxid und organischen Materialien können solche Verbindungen aufweisen, wie gepufferte Fluorwasserstoffsäure bzw. Aceton oder EKC. Die Strukturierung kann jedoch unter Verwendung irgendeines bekannten Verfahrens erzielt werden.

**[0013]** In [Fig. 1A](#) ist eine Schnittansicht einer Doppeldamaszen-Umgrenzung von Kontaktloch und Leiter gezeigt, die in der dielektrischen Schicht **16** ausgebildet ist. Die Kontaktloch- und -leiter-Umgrenzung erleichtert das Ablegen einer leitenden Zwischenverbindung, die eine elektrische Verbindung mit der darunter liegenden leitenden Struktur **15** bildet. Die Umgrenzung sieht Kontaktlöcher **32** mit Kontaktlochwänden **34** und einem Boden **30** vor, der wenigstens einen Teil der leitenden Struktur **15** exponiert, sowie Gräben **17** mit Grabenwänden **38**.

**[0014]** Gemäß [Fig. 1B](#) wird eine Sperrsicht **20** aus PVD-TaN auf der Umgrenzung für Kontaktloch und Draht abgeschieden, die in den Kontaktlöchern **32** Löcher **18** belässt. Die Sperrsicht wird vorzugsweise von Titan, Titannitrid, Tantal oder Tantalnitrid gebildet. Der verwendete Prozess kann zur Verbesserung der Textur und Filmeigenschaft PVD, CVD oder kombiniert CVD/PVD sein. Die Sperrsicht begrenzt die Diffusion des Kupfers und erhöht die Zuverlässigkeit der Zwischenverbindung extrem. Bevorzugt hat die Sperrsicht eine Dicke zwischen etwa 25 und etwa 300 Å (1 Å = 0,1 nm), besonders bevorzugt etwa 100 Å.

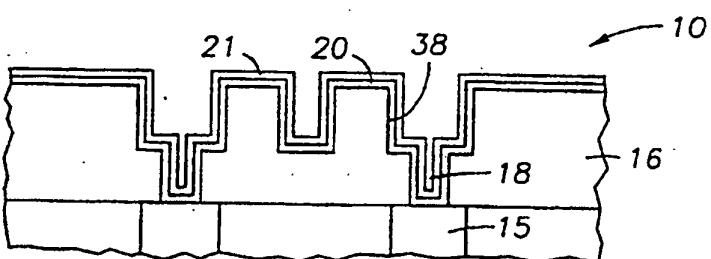

**[0015]** Gemäß [Fig. 1C](#) wird eine PVD-Kupferschicht **21** auf der Sperrsicht über den Wänden **34**, **48** und dem Boden **30** der Leiterumgrenzung abge-

schieden. Das verwendete Metall kann auch Aluminium oder Wolfram sein. Die PVD-Kupferschicht **21** sorgt für eine gute Haftung für zusätzliche Metallschichten.

**[0016]** Gemäß [Fig. 1D](#) wird Kupfer **22** über der PVD-Kupferschicht **21** elektroplattiert, um das Durchgangsloch **32** mit einem Kupferstopfen **19** zu füllen. Das Elektroplattieren gehört zum Stand der Technik und kann durch eine Vielzahl von Techniken erreicht werden.

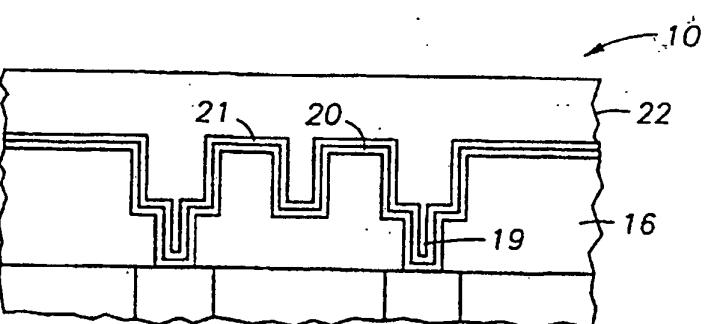

**[0017]** Gemäß [Fig. 1E](#) wird dann der obere Teil der Struktur **10** planarisiert, vorzugsweise durch chemisches mechanisches Polieren (CMP – Chemical Mechanical Polishing). Während des Planarisiervorgangs werden Teile der Kupferschichten **21**, **22**, der Sperrsicht **20** und des Dielektriks **16** von der Oberseite der Struktur entfernt, so dass eine vollständig planare Oberfläche mit Leitern **39** verbleibt, die in den Gräben in ihr ausgebildet sind.

**[0018]** Im Vergleich zur PVD-Kupferabscheidung sind Dünnfilme, die während eines Decken-CVD-Prozesses abgeschieden werden, üblicherweise konform und geben eine hervorragende Stufenabdeckung, d.h. eine gleichförmige Dicke der Schichten an den Seiten und der Basis einer in dem Substrat ausgebildeten Öffnung, auch bei sehr kleinen Öffnungsgeometrien. Deshalb ist die Decken-CVD ein übliches Verfahren, das zum Füllen von Öffnungen verwendet wird. Den Decken-CVD-Prozessen sind jedoch zwei Haupt Schwierigkeiten zugeordnet. Zuerst wachsen die Decken-CVD-Filme von allen Seiten in eine Öffnung, was gewöhnlich einen Hohlraum in der gefüllten Öffnung ergibt, da die abgeschiedene Schicht nach oben und nach außen an den oberen Ecken der Öffnung wächst und an der oberen Fläche die Öffnung überbrückt, bevor die Öffnung vollständig gefüllt worden ist (d.h. Brücken- oder Kronenbildung). Ferner verringert eine fortlaufende Keimbildungsschicht, d.h. eine fortlaufende Filmschicht zur Gewährleistung der Keimbildung über allen Flächen des Substrats, die auf den Öffnungswänden abgeschieden wird, um eine Abscheidung der CVD-Schicht darauf zu gewährleisten, die Breite der Öffnung weiterhin, wodurch die Schwierigkeit zunimmt, die Öffnung ohne Hohlräume zu füllen. Zweitens tendieren durch Decken-CVD abgeschiedene Filme zu einer Konformierung mit der Topographie der Oberfläche, auf der die Filme abgeschieden werden, was einen Film ergeben kann, der eine willkürlich ausgerichtete Kristallstruktur und daraus resultierende geringere Reflexionseigenschaften sowie eine schlechte Elektromigration hat, wenn die Topographie nicht orientiert oder willkürlich ist.

**[0019]** Ein selektives CVD basiert auf der Tatsache, dass die Zersetzung des CVD-Vorläufergases zur

Bildung eines Abscheidefilms gewöhnlich eine Elektronenquelle aus einem leitenden Keimbildungsfilm erfordert. Bei einem herkömmlichen selektiven CVD-Prozess sollte die Abscheidung in dem Boden einer Öffnung vor sich gehen, wo entweder ein leitender Film oder ein dotiertes Silicium aus der darunter liegenden Schicht freigelegt worden ist, sie sollte jedoch nicht auf dem Isolierbereich oder den Isolieröffnungswänden wachsen, wo keine Keimbildungsstellen vorgesehen sind. Diese leitenden Filme und/oder das dotierte Silicium, das an der Basis der Öffnungen freigelegt ist, sorgt im Gegensatz zu dielektrischen Oberflächen für die Elektronen, die für die Zersetzung des Vorläufergases und der daraus resultierenden Abscheidung der Filmschicht erforderlich sind. Das durch die selektive Abscheidung erhaltene Ergebnis ist ein Wachstum des Films in den Öffnungen "vom Boden nach oben", wodurch Kontaktlöcher oder Kontakte mit sehr kleinen Abmessungen ( $< 0,25 \mu\text{m}$ ) und hohem Seitenverhältnis ( $> 5,1$ ) gefüllt werden können. In selektiven CVD-Prozessen bilden sich jedoch auf der Ebene, wo Defekte in dieser Oberfläche vorhanden sind, unerwünschte Knoten.

**[0020]** Andererseits ermöglichen PVD-Prozesse eine Abscheidung von in hohem Maße ausgerichteten Filmen mit verbessertem Reflexionsvermögen, haben jedoch kein gutes Öffnungsfüllen oder keine gute Stufenabdeckung bei Anwendungen mit hohem Seitenverhältnis. Das physikalische Zerstäuben von Target-Material ergibt Teilchen, die sich in spitzen Winkeln bezüglich der Substratoberfläche bewegen. Als Folge neigen beim Füllen von Öffnungen mit hohem Seitenverhältnis zerstäubte Teilchen zur Abscheidung an den oberen Wandflächen und zur Abdeckung ihrer Mündung, bevor die Öffnung vollständig mit Abscheidematerial gefüllt wird. Die sich ergebende Struktur weist typischerweise Hohlräume in sich auf, die die Integrität der auf dem Substrat ausgebildeten Bauelemente gefährden.

**[0021]** Öffnungen mit großem Seitenverhältnis können unter Verwendung von PVD-Prozessen dadurch gefüllt werden, dass der Film bei erhöhten Temperaturen abgeschieden wird. Beispielsweise kann Aluminium bei  $400^\circ\text{C}$  oder mehr abgeschieden werden, um den Fluss des Aluminiums auf die Oberfläche und durch die Öffnung zu steigern. Man hat gefunden, dass dieses heiße Al-Verfahren eine verbesserte Stufenabdeckung ergibt. Es zeigt sich jedoch, dass das heiße Al-Verfahren eine unzuverlässige Kontaktlochfüllung, hohe Abscheidetemperaturen und lange Füllzeiten sowie ein schlechtes Filmreflexionsvermögen aufweist.

**[0022]** Trotz der Verfügbarkeit dieser technischen Maßnahmen besteht ein Bedürfnis nach einem Metallisierprozess zur Herstellung von Doppeldamassen-Zwischenverbindungen und Kontaktlöchern, die Böden mit irgendeinem Abscheidematerial haben.

Solche hochintegrierten Zwischenverbindungen müssen hohlraumfreie Kontaktlöcher, insbesondere mit großem Seitenverhältnis, sowie zur Bildung von Kontakten und Kontaktlöchern Öffnungen haben, die unter einem Viertel  $\mu\text{m}$  groß sind. Weiterhin besteht ein Bedürfnis für ein Verfahren zur Bereitstellung einer Schaltung mit höherer elektrischer Leitfähigkeit und verbessertem Elektromigrationswiderstand. Man wünscht sich ein einfaches Verfahren, das weniger Behandlungsschritte erfordert, um Metallstopfen in Kontaktlöchern und Leiter in den Gräben zu bilden. Ferner ist erwünscht, dass mit dem Verfahren dies alles erreicht werden kann, ohne Metallätztechniken zu verwenden.

#### ZUSAMMENFASSUNG DER ERFINDUNG

**[0023]** Die vorliegende Erfindung betrifft ein Verfahren zur Ausbildung einer Doppeldamaszen-Zwischenverbindung in einer dielektrischen Schicht mit einer Doppeldamaszen-Umgrenzung für Kontaktloch und Leiter, bei welchem

- a) auf exponierten Oberflächen der dielektrischen Schicht eine Sperrsicht abgelegt wird,

- b) auf der Sperrsicht durch chemische Gasphasenabscheidung oder Elektroplattieren ein leitendes Metall aufgebracht wird,

- c) das leitende Metall nach der chemischen Gasphasenabscheidung oder dem Elektroplattieren zum Füllen der Kontaktlochumgrenzung wärmebehandelt wird,

- d) nach der Wärmebehandlung das leitende Metall zum Füllen der Leiterumgrenzung durch physikalische Gasphasenabscheidung aufgebracht wird, und

- e) das leitende Metall, die Sperrsicht und die dielektrische Schicht zur Bildung eines Leiterdrahts planarisiert werden.

#### KURZBESCHREIBUNG DER ZEICHNUNGEN

**[0024]** Damit die Art und Weise, in der die vorstehend erwähnten Merkmale, Vorteile und Ziele der vorliegenden Erfindung erreicht werden können, im Einzelnen verstanden werden kann, folgt eine speziellere Beschreibung der Erfindung, wie sie vorstehend kurz zusammengefasst ist, unter Bezugnahme auf Ausführungsformen von ihr, die in den beiliegenden Zeichnungen dargestellt sind.

**[0025]** Es ist jedoch zu vermerken, dass die beiliegenden Zeichnungen nur typische Ausführungsformen dieser Erfindung veranschaulichen und deshalb nicht als Begrenzung ihres Umfangs anzusehen sind, da die Erfindung Zugang zu anderen, gleich wirksamen Ausführungsformen haben kann.

**[0026]** [Fig. 1A](#) bis [Fig. 1E](#) (Stand der Technik) zeigen eine Doppeldamaszen-Kontaktloch- und -Leiterumgrenzung und die Schritte nach dem Stand der

Technik zur Bereitstellung einer metallischen Zwischenverbindung unter Verwendung einer Sperrsicht, einer PVD-Metallabscheidung und einer Metallektroplattierung.

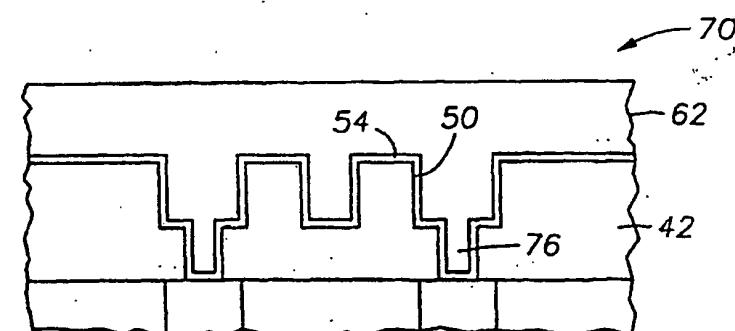

**[0027]** [Fig. 2A](#) bis [Fig. 2E](#) dienen lediglich als Hintergrundinformation und zeigen eine Doppeldamaszen-Umgrenzung für Kontaktloch und Leiter sowie die Abscheidung einer Sperrsicht vor dem Füllen der Umgrenzung für Kontaktloch und Leiter mit einem leitenden Metall.

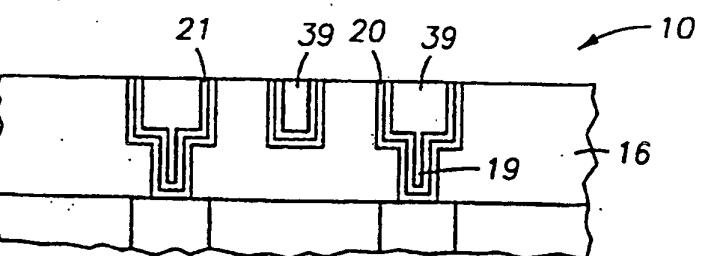

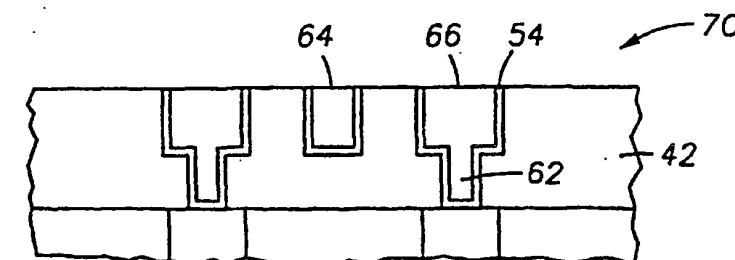

**[0028]** [Fig. 3A](#) bis [Fig. 3E](#) zeigen eine Doppeldamaszen-Umgrenzung für Kontaktloch und Leiter mit einer Sperrsicht sowie Schritte zur Abscheidung eines leitenden Metalls gemäß einer Ausführungsform der Erfindung.

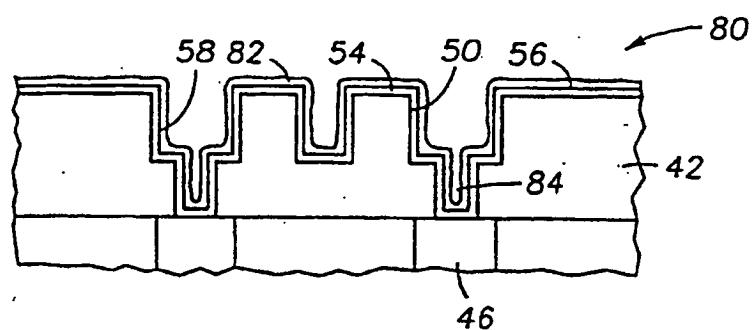

**[0029]** [Fig. 4A](#) bis [Fig. 4E](#) zeigen eine Doppeldamaszen-Umgrenzung für Kontaktloch und Leiter mit einer Sperrsicht sowie Schritte zur Abscheidung eines leitenden Metalls gemäß einer zweiten Ausführungsform der vorliegenden Erfindung.

**[0030]** [Fig. 5A](#) bis [Fig. 5E](#) dienen nur als Hintergrundinformation und zeigen eine Doppeldamaszen-Umgrenzung mit Kontaktloch und Leiter, die eine Sperrsicht aufweist, sowie Schritte zur Ablage eines leitenden Metalls.

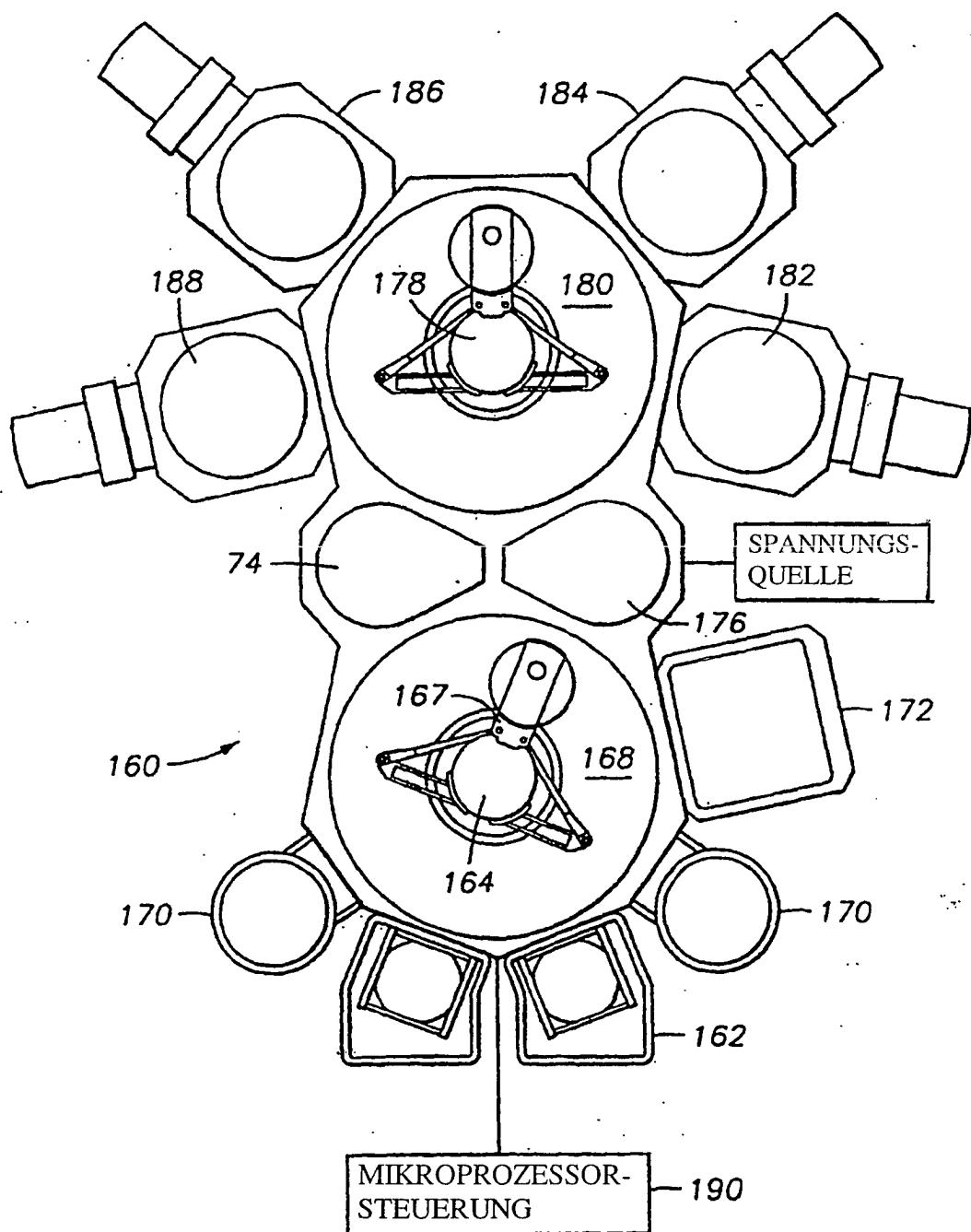

**[0031]** [Fig. 6](#) ist ein integriertes Behandlungssystem für eine sequenzielle Metallisierung gemäß einer bevorzugten Ausführungsform der vorliegenden Erfindung.

#### INS EINZELNE GEHENDE BESCHREIBUNG EINER BEVORZUGTEN AUSFÜHRUNGSFORM

**[0032]** Die vorliegende Erfindung stellt insgesamt ein In-situ-Metallisierungsverfahren für eine Zwischenverbindung in einer hochintegrierten Struktur bereit, die einen reduzierten Zwischenverbundungswiderstand und eine verbesserte Elektromigrationsleistung hat. Insbesondere stellt die vorliegende Erfindung ein Verfahren zur Ausbildung einer Doppeldamaszen-Zwischenverbindung, die eine Sperrsicht an exponierten Oberflächen einer Umgrenzung von Kontaktloch und Leiter aufweist, sowie Abscheidungstechniken zum Füllen der Umgrenzung der Kontaktlochs – teilweise – und des Leiters bereit, die durch einen Glühbehandlungsschritt zum Füllen des Kontaktlochs getrennt sind. In einem integrierten Behandlungssystem können bevorzugte Abscheidungstechniken kombiniert werden, obwohl nicht integrierte Techniken geeignete Metallzwischenverbindungen und Metallkontaktlochstopfen bereitstellen.

**[0033]** Zur Klarstellung wird die vorliegende Erfindung nachstehend unter Bezug auf Kupferabscheidetechniken beschrieben. Es können jedoch auch

andere Metallprozesse, wie PVD-Aluminium oder AUCu verwendet werden, um die Vorteile der vorliegenden Erfindung zu erreichen.

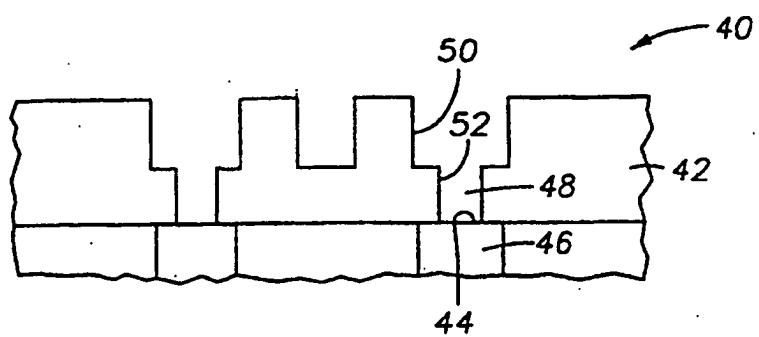

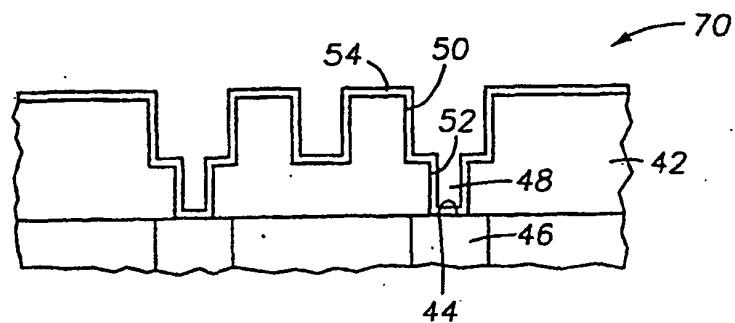

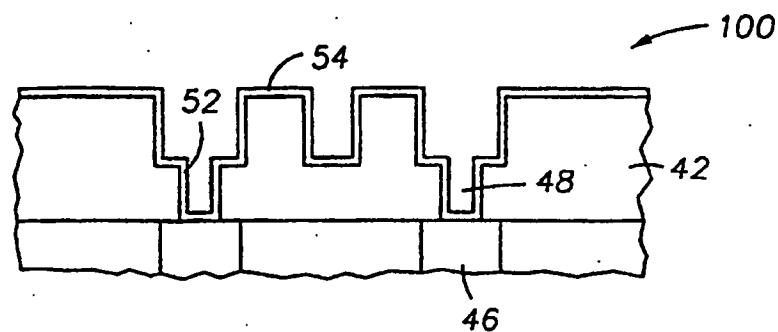

**[0034]** Gemäß [Fig. 2A](#) wird zur Ausbildung einer außerhalb der Erfindung liegenden IC-Struktur **40** eine dielektrische Schicht **42** nach herkömmlichen Techniken über einer Oberfläche **44** einer leitenden Schicht oder eines leitenden Bereichs **46** einer strukturierten Schicht ausgebildet. Die dielektrische Schicht kann so dick sein wie etwa die doppelte Dicke einer einzigen Metallisierungsschicht, wenn eine Doppeldamaszen-Umgrenzung für Kontaktloch und Leiter hindurchgeätzt wird. Es kann jedes dielektrische Material, ob es gegenwärtig bekannt ist oder noch nicht entdeckt ist, verwendet werden und liegt innerhalb des Rahmens der vorliegenden Erfindung, einschließlich gering dielektrische Materialien, wie Kohlenstoff-fluoriertes SiO<sub>2</sub>, organische Polymere, usw. Die dielektrische Schicht kann auf jedem geeigneten, die Abscheidung begünstigenden Material abgeschieden werden, jedoch gehören zu den bevorzugten, die Abscheidung begünstigenden Materialien leitende Metalle und dotiertes Silicium.

**[0035]** Wenn die dielektrische Schicht abgeschieden ist, wird sie zur Bildung einer Doppeldamaszen-Umgrenzung für Kontaktloch und Draht geätzt, wobei das Kontaktloch **48** den unteren leitenden Bereich **46** mit einem Graben **50** verbindet, der einen Leiter oder eine Zwischenverbindung bildet, wenn er gefüllt ist. Das Kontaktloch hat gewöhnlich ein großes Seitenverhältnis mit steilen Seitenwänden **52**. Das Ätzen der dielektrischen Schicht **42** kann mit jedem dielektrischen Ätzprozess einschließlich Plasmaätzen erreicht werden. Zu speziellen Techniken zum Ätzen von Siliciumdioxid und organischen Materialien können solche Verbindungen gehören, wie gepufferter Fluorwasserstoffsäure bzw. Aceton oder EKC. Eine Strukturierung kann jedoch unter Verwendung jedes bekannten Verfahrens erreicht werden.

**[0036]** Gemäß [Fig. 2B](#) ist eine Sperrsicht **54** auf exponierten Oberflächen abgeschieden, zu denen die Oberflächen in den Umgrenzungen des Kontaktlochs **48** und des Leiters **50** gehören. Zu bevorzugten Sperr-/Benetzungsschichten gehören Schichten aus beispielsweise hitzebeständigem Material (wie Wolfram (W)), Wolframatnitrid (WN), Niob (Nb), Aluminiumsilicate, usw.), Tantal (Ta), Tantalanitrid (TaN), Titanitrid (TiN), PVD-Ti/N<sub>2</sub>-gefüllt, eine ternäre Verbindung (wie TiSiN, WSiN, usw.) oder eine Kombination dieser Schichten. Zu bevorzugten Sperrmaterialien gehören Titan, Titannitrid, Titansiliciumnitrid, Wolframatnitrid, Wolframsiliciumnitrid, Tantal, Tantalanitrid, Tantalsiliciumnitrid, dotiertes Silicium, Aluminium und Aluminiumoxide. Die besonders bevorzugten Sperr-Benetzungsmaterialien sind Ta und TaN, die gewöhnlich als PVD-Schicht mit einer Dicke zwischen etwa 50 und etwa 1000 Å bereitgestellt werden. Umgekehrt

hat eine CVD-, TiN- oder eine WN-Sperr-Benetzungsschicht gewöhnlich eine Dicke zwischen etwa 100 und etwa 400 Å. Die Sperr-Benetzungsschicht wird abgeschieden, um eine im Wesentlichen durchgehende Kappe über der dielektrischen Schicht zu bilden, und kann mit Stickstoff behandelt werden. Alternativ können exponierte Oberflächen von Siliciumoxid mit Stickstoff behandelt werden, um eine Si<sub>x</sub>O<sub>y</sub>N<sub>2</sub>-Schicht zu bilden, die als Sperrsicht für Kupfer wirksam ist.

**[0037]** Durch abwechselnde Prozessgasströme kann eine Kombination von Sperr-Benetzungsschichten hergestellt werden, um eine bessere Adhäsion für CVD-Cu zu bilden. Beispielsweise gibt eine CVD-Abscheidung von WN durch Reaktion von WF<sub>6</sub>, N<sub>2</sub>, H<sub>2</sub> und SiH<sub>4</sub> eine hervorragende Haftung für die dielektrische Schicht. Die Unterbrechung des Stickstoffstroms während des Abscheidens führt zu einer abschließenden Sperr-Benetzungsschicht von CVD-W, die an der CVD-WN-Schicht und der darauf folgenden CVD-Cu-Schicht haftet. Auf ähnliche Weise kann eine TaN-Schicht mit einer Ta-Schicht kombiniert werden oder es kann eine TiN-Schicht mit einer Ti-Schicht durch Unterbrechen des Stickstoffstroms kombiniert werden. Die kombinierten Schichten verbessern die Haftung an dem CVD-Cu, das eine bessere Textur für das Material gibt, das in dem Kontaktloch oder Graben abgeschieden wird. Alternativ können WN-, TaN- oder TiN-Sperr-Benetzungsschichten mit H<sub>2</sub>-, Ar- oder He-Plasma vorbehandelt werden, um die CVD-Cu-Schicht mit Keimstellen zu versehen und für eine bessere Haftung zu sorgen.

#### CVD/PVD-Füllen

**[0038]** Bei einer Ausführung **40**, die lediglich als Hintergrundinformation eingeführt wird, wie weiter in [Fig. 2C](#), [Fig. 2E](#) gezeigt ist, wird ein Verfahren zur Ausbildung von Doppeldamaszen-Stopfen und -Zwischenverbindungen vorgesehen, die einen niedrigeren spezifischen Widerstand und einen größeren Elektromigrationswiderstand haben. Das Kontaktloch unter einem halben µm wird ohne Hohlräume durch konformes CVD-Cu gefüllt, wonach der Graben mit PVD-Cu gefüllt wird, das vorzugsweise Zinn als Dotierung aufweist. Nach dem Abscheiden wandert das Dotiermittel in die CVD-Cu-Schicht und verbessert den Elektromigrationswiderstand. Die Leiter werden durch Planarisierung der Struktur vervollständigt.

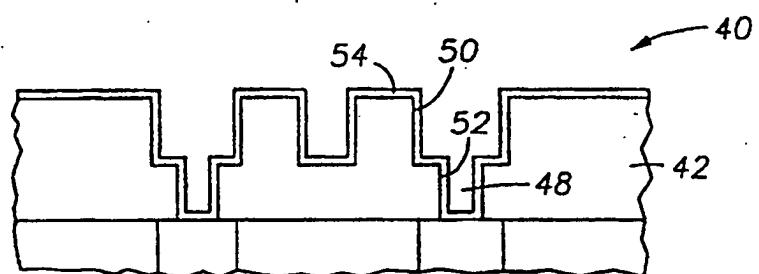

**[0039]** Die im Querschnitt in [Fig. 2C](#) gezeigte Doppeldamaszen-Umgrenzung für Kontaktloch und Leiter, die die konforme Sperrsicht **54** aufweist, hat eine konforme CVD-Cu-Schicht **55**, die gleichförmig auf Feldbereich **56** und Seitenwänden **58** abgeschieden ist, bis das Kontaktloch vollständig durch einen Kupferstopfen **60** gefüllt ist.

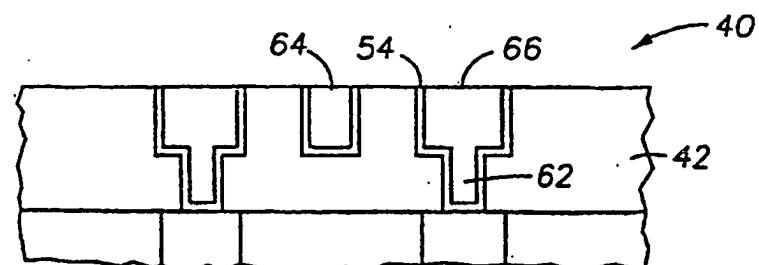

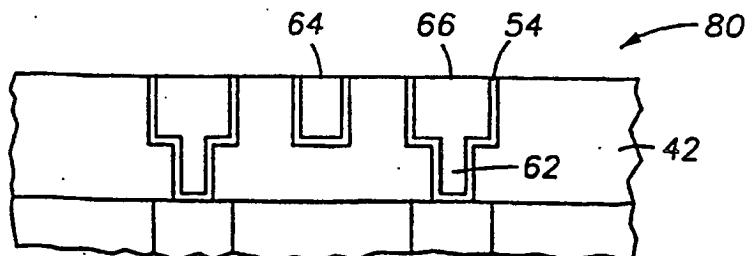

[0040] Gemäß [Fig. 2D](#) ist eine Kupferschicht **62** über der CVD-Cu-Schicht durch physikalische Gasphasenabscheidung abgeschieden, um die Leiterumgrenzung **50** zu füllen. Zum Füllen der Leiterumgrenzung tritt im Allgemeinen ein, dass das gesamte Feld der Struktur mit dem PVD-Cu bedeckt wird.

[0041] Gemäß [Fig. 2E](#) wird dann der obere Teil der Struktur **40** planarisiert, vorzugsweise durch chemisches-mechanisches Polieren (CMP) (beispielsweise durch ein Mirra™-System, lieferbar von Applied Materials, Santa Clara, Cal.). Während des Planarisierungsprozesses werden Teile des Kupfers **62**, des Sperrmaterials **54** und des Dielektrikums **42** von der Oberseite der Struktur entfernt, so dass eine volle planare Oberfläche mit darin ausgebildeten Leiterdrähten **64**, **66** verbleibt.

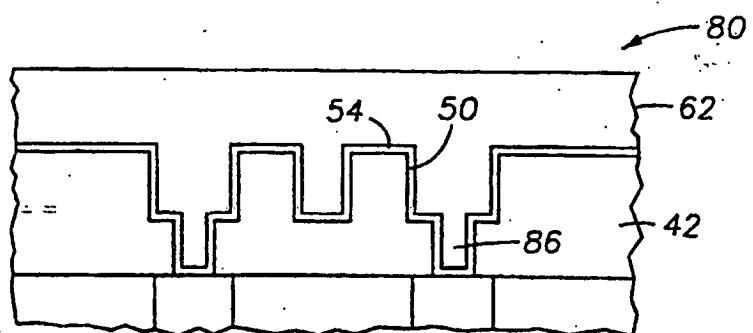

CVD/Glühbehandeln/PVD-Füllen

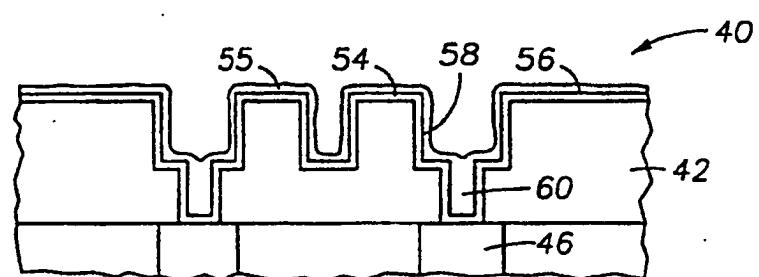

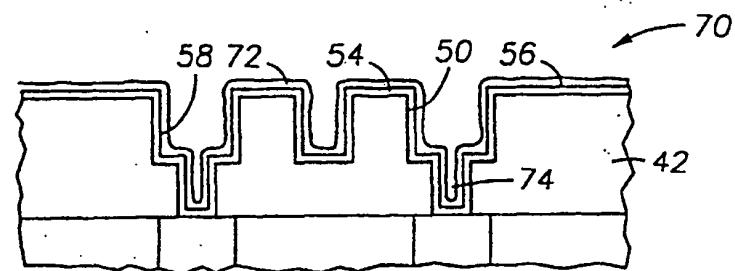

[0042] Bei einer Ausführungsform **70** der Erfindung, die in [Fig. 3A](#) bis [Fig. 3E](#) gezeigt ist, wird das Kontaktloch mit unter einem halben µm teilweise mit dem konformen CVD-Cu gefüllt und dann zum Füllen des Kontaktlochs glühbehandelt. Dann wird der Graben mit PVD-Cu, wie vorher beschrieben, gefüllt. Wenn ein Graben eine zu geringe Breite hat, kann der Glühbehandlungsschritt den Graben auch füllen. Die Gräben können die gleiche Breite wie das Kontaktloch haben, das den Graben mit einer darunter liegenden Schicht verbindet. Der PVD-Cu-Schritt kann noch verwendet werden, um Dotiermittel bereitzustellen oder um eine ausreichende Filmdicke zur Planarisierung der Struktur vorzusehen.

[0043] [Fig. 3A](#) zeigt ein strukturiertes Dielektrikum mit einer darauf ausgebildeten Sperrsicht **54** ähnlich wie sie in [Fig. 2B](#) gezeigt ist. Gemäß [Fig. 3B](#) hat eine Querschnittsansicht des Doppeldamasen-Umrisses für Kontaktloch und Draht mit der konformen Sperrsicht **54** eine konforme CVD-Cu-Schicht **72**, die gleichförmig auf Feldbereichen **56** und Seitenwänden **58** abgeschieden ist, bis das Kontaktloch teilweise gefüllt ist und ein Loch **74** verbleibt. Gemäß [Fig. 3C](#) wird dann die CVD-Cu-Schicht glühbehandelt, indem der Wafer auf eine Temperatur von etwa 300°C bis etwa 450°C erhitzt wird, um das Kupfer in das Loch **74** aufzuschmelzen und einen Kupferstopfen **76** zu bilden.

[0044] Gemäß [Fig. 3D](#) wird eine Kupferschicht **62** über der CVD-Cu-Schicht durch physikalische Gasphasenabscheidung abgeschieden, um die Leiterumgrenzung **50** zu füllen. Zum Füllen der Leiterumgrenzung tritt gewöhnlich ein, dass das gesamte Feld der Struktur mit dem PVD-Cu bedeckt wird.

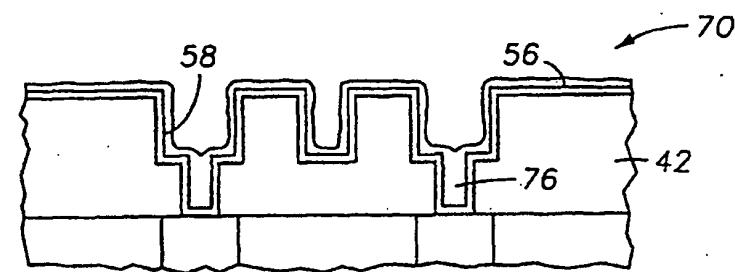

[0045] Gemäß [Fig. 3E](#) wird dann der obere Teil der Struktur **70** planarisiert, vorzugsweise durch chemisches mechanisches Polieren (CMP). Während des

Planarisierprozesses werden Teile des Kupfers **62**, des Sperrmaterials **54** und des Dielektrikums **42** von der Oberseite der Struktur entfernt, so dass eine vollständig planare Oberfläche mit darin ausgebildeten Leiterdrähten **64**, **66** verbleibt.

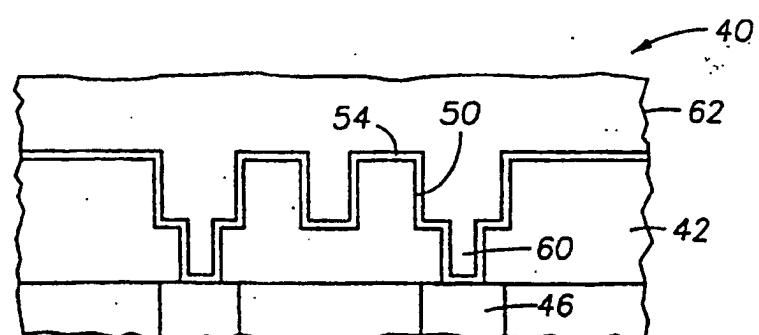

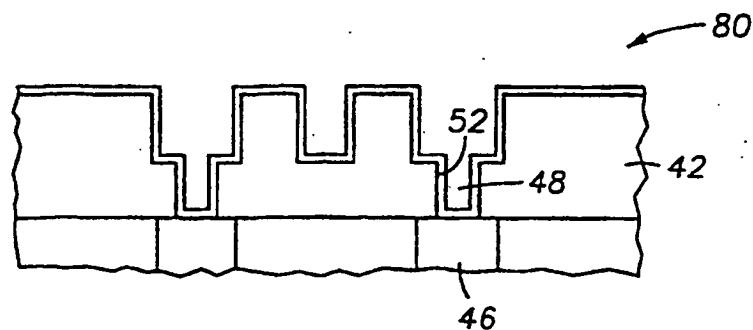

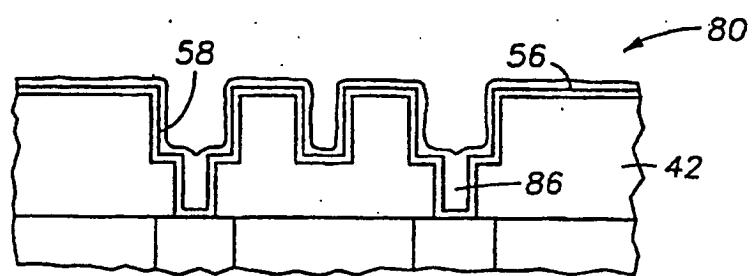

Elektroplattieren/PVD oder CVD/PVD-Füllen

[0046] Bei einer weiteren Ausführungsform **80** der Erfindung, wie sie in den [Fig. 4A](#) bis [Fig. 4E](#) gezeigt ist, wird das Kontaktloch mit unter einem halben µm teilweise durch Cu-Elektroplattieren oder durch konformes CVD-Cu gefüllt. Dann kann der Graben in einem nicht integrierten System mit PVD-Cu, wie vorher beschrieben, gefüllt werden. Wenn man dem Cu-Elektroplattieren folgt, ist das PVD-Cu vollständig dotiert, um die Elektromigration zu verbessern. Die Drähte werden durch Planarisierung der Struktur fertig gestellt.

[0047] [Fig. 4A](#) zeigt ein strukturiertes Dielektrikum mit einer darauf ausgebildeten Sperrsicht **54** ähnlich wie in [Fig. 2B](#). Gemäß [Fig. 4B](#) hat ein Querschnitt der Doppeldamasen-Umgrenzung für Kontaktloch und Leiter mit der konformen Sperrsicht **43** eine konforme Cu-elektroplattierte Schicht **82**, die gleichförmig auf den Feldbereich **56** und Seitenwänden **58** abgeschieden ist, bis das Kontaktloch teilweise gefüllt ist, so dass ein Loch **84** verbleibt. Gemäß [Fig. 4C](#) wird dann die Cu-elektroplattierte Schicht durch Erhitzen des Wafers auf eine Temperatur von etwa 300°C bis etwa 450°C glühbehandelt, um das Kupfer in dem Loch **84** aufzuschmelzen und einen Kupferstopfen **86** zu bilden.

[0048] Gemäß [Fig. 4D](#) wird über der Cu-elektroplattierten Schicht eine Kupferschicht **62** durch physikalische Gasphasenabscheidung abgeschieden, um die Leiterumgrenzung **50** zu füllen. Beim Füllen der Leiterumgrenzung tritt gewöhnlich ein, dass das gesamte Feld der Struktur mit dem PVD-Cu abgedeckt wird.

[0049] Gemäß [Fig. 4E](#) wird dann der obere Teil der Struktur **80** planarisiert, vorzugsweise durch chemisches mechanisches Polieren (CMP). Während des Planarisierungsprozesses werden Teile des Kupfers **62**, des Sperrmaterials **54** und des Dielektrikums **42** von der Oberseite der Struktur entfernt, so dass eine vollständig planare Oberfläche mit darin ausgebildeten Leiterdrähten **64**, **66** verbleibt.

CVD/Glühbehandeln/CVD/Glühbehandeln Füllen

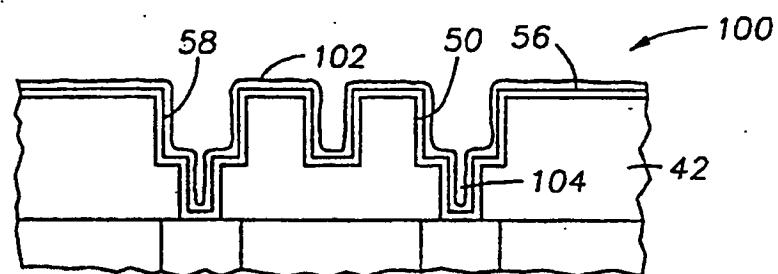

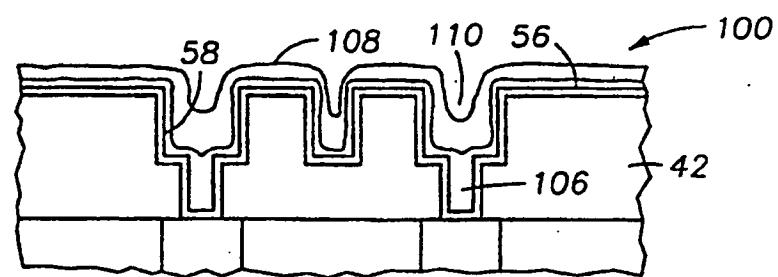

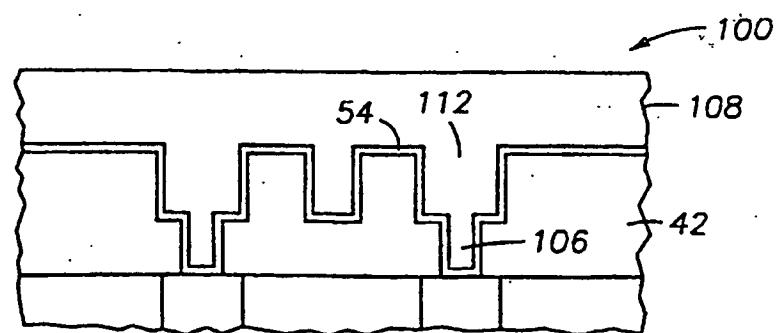

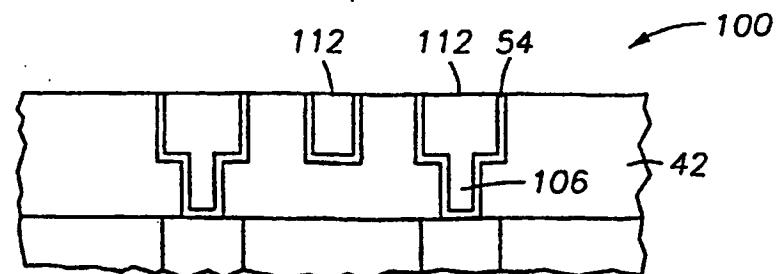

[0050] Bei einer Ausgestaltung **100**, die lediglich zur Hintergrundinformation aufgenommen wird und in [Fig. 5A](#) bis [Fig. 5E](#) gezeigt ist, wird das Kontaktloch mit unter einem halben µm mit konformem CVD-Cu gefüllt und dann glühbehandelt, um das Kontaktloch zu füllen. Anschließend wird der Graben mit CVD-Cu gefüllt und dann glühbehandelt, wie für das Kontakt-

loch beschrieben. Die Drähte werden durch Planarisieren der Struktur gebildet.

[0051] [Fig. 5A](#) zeigt ein strukturiertes Dielektrikum mit einer darauf ausgebildeten Sperrsicht **54** ähnlich wie in [Fig. 2B](#) gezeigt. Gemäß [Fig. 5B](#) hat ein Querschnitt einer Doppeldamaszen-Umgrenzung für Kontaktloch und Leiter die konforme Sperrsicht **54**, eine konforme CVD-Cu-Schicht **102**, die gleichförmig auf Feldbereichen **56** und Seitenwänden **58** abgeschieden ist, bis das Kontaktloch teilweise gefüllt ist, wodurch ein Loch **104** verbleibt. Gemäß [Fig. 5C](#) wird dann die CVD-Cu-Schicht durch Erhitzen des Wafers auf eine Temperatur von etwa 300°C bis etwa 450°C glühbehandelt, um das Kupfer in dem Loch **104** aufzuschmelzen und einen Kupferstopfen **106** zu bilden. Dann wird eine zweite konforme CVD-Cu-Schicht **108** gleichmäßig auf der glühbehandelten CVD-Schicht abgeschieden, bis die Gräben teilweise gefüllt sind, so dass ein Loch **110** verbleibt. Gemäß [Fig. 5D](#) wird dann die zweite CVD-Cu-Schicht **108** durch Erhitzen des Wafers auf eine Temperatur von etwa 300°C bis etwa 450°C glühbehandelt, um das Kupfer in das Grabenloch **110** aufzuschmelzen und um einen Kupferdraht **112** zu bilden. Gemäß [Fig. 5E](#) wird dann der Kupferdraht **112** durch Planarisieren, wie vorher beschrieben, fertig gestellt.

#### Integriertes Behandlungssystem

[0052] In [Fig. 6](#) ist schematisch ein integriertes Behandlungssystem **160** gezeigt, das sowohl PCV- als CVD-Kammern aufweist, in denen die vorstehend beschriebenen integrierten Prozesse ausgeführt werden können. Gewöhnlich werden Substrate in das Behandlungssystem **160** durch eine Kassettenladeschleuse **162** eingeführt und daraus abgeführt. In dem Behandlungssystem **160** ist ein Roboter **164** mit einem Blatt **167** angeordnet, um die Substrate durch das System **160** zu bewegen. Ein Roboter **164** ist gewöhnlich in einer Pufferkammer **168** angeordnet, um Substrate zwischen der Kassettenladeschleuse **162**, einer Entgasungs-Waferausrichtkammer **170**, einer Vorreinigungskammer **172**, einer PVD-TiN-Kammer **174** und einer Abkühlkammer **176** zu überführen. In einer Überführungskammer **180** ist ein zweiter Roboter **178** angeordnet, um Substrate zu der Abkühlkammer **176**, einer kohärenten Ti-Kammer **162**, einer CVD-Zinn-Kammer **184**, einer CVD-Cu-Kammer **186** und einer PVD-IMP-Cu-Behandlungskammer **188** hin und daraus heraus zu überführen. Die Überführungskammer **180** in dem integrierten System wird vorzugsweise auf einem niedrigen Druck oder einem hohen Vakuum im Bereich von  $10^{-3}$  bis  $10^{-8}$  Torr gehalten. Diese spezielle Ausgestaltung der Kammern in [Fig. 6](#) hat ein integriertes Behandlungssystem, das sowohl CVD- als auch PVD-Prozesse in einem einzigen Gruppengerät ausführen kann. Diese spezielle Kammerausgestaltung oder -anordnung dient nur der Veranschaulichung, die vorliegende Erfindung sieht

auch mehrere Ausgestaltungen von PVD- und CVD-Prozessen in Betracht.

[0053] Gewöhnlich wird ein in dem Behandlungssystem **160** behandeltes Substrat aus der Kassettenladeschleuse **162** zu der Pufferkammer **168** geführt, wo der Roboter **164** das Substrat zuerst in eine Entgasungskammer **170** bewegt. Das Substrat wird dann in eine Vorreinigungskammer **172**, eine PVD-TiN-Kammer **174** und dann in eine Abkühlkammer **176** überführt. Aus der Abkühlkammer **176** bewegt der Roboter **178** das Substrat gewöhnlich in und zwischen einer oder mehreren Behandlungskammern, bevor er das Substrat zurück zu der Abkühlkammer **178** führt. Das Substrat kann in einer oder mehreren Kammern beliebig oft in jeder Reihenfolge behandelt oder gekühlt werden, um die Fertigung einer gewünschten Struktur auf dem Substrat zu erreichen. Das Substrat wird nach der Behandlung aus dem Behandlungssystem **160** über die Pufferkammer **168** und dann die Ladeschleuse **162** entfernt. Eine Mikroprozessorsteuerung **190** steuert die Abfolge und Ausbildung der Schichten auf den Substraten.

[0054] Das Behandlungssystem **160** führt ein Substrat durch die Ladeschleuse **162** in die Entgasungskammer **170**, in die das Substrat eingeführt wird, um Verunreinigungen auszugasen. Dann wird das Substrat in eine Vorreinigungskammer **172** bewegt, wo die Oberfläche des Substrats gereinigt wird, um alle Verunreinigungen darauf zu entfernen. Anschließend wird das Substrat in der CVD-TiN-Kammer **175** behandelt, um eine Sperrsicht auf der dielektrischen Schicht abzuscheiden. Anschließend überführt der Roboter **178** das Substrat zu einer CVD-Cu-Kammer **174**. Das Substrat erhält zwei oder mehr Metallschichten, um den Metallstopfen und die Zwischenverbindung auszubilden. Eine Glühbehandlung kann in jeder erhitzen Kammer erfolgen. Wenn die Metallschicht voll abgeschieden ist, wird das Substrat zur Planarisierungseinheit geschickt.

[0055] Ein Waferbehandlungssystem mit Stufenvakuum ist in dem US-Patent 5,186,718 mit dem Titel "Staged-Vacuum Wafer Processing Systems and Method" (System und Verfahren zur Waferbehandlung mit abgestuftem Vakuum), Tepman et al., ausgetragen am 16. Februar 1993, offenbart. Dieses System wurde für die Aufnahme einer CVD-Kammer modifiziert.

[0056] Unter Verwendung irgendeines bekannten CVD-Cu-Prozess- oder -Vorläufergases, wozu Kupfer<sup>+2</sup>(hfac)<sub>2</sub> und Cu<sup>2</sup>(fod)<sub>2</sub> (fod ist die Abkürzung für Heptafluordimethyloctandien) gehören, kann eine CVD-Cu-Schicht abgeschieden werden, ein bevorzugter Prozess verwendet jedoch einen flüchtigen flüssigen Komplex Kupfer<sup>+1</sup>hfac-TMVS (hfac ist die Abkürzung für das Hexafluoracetylacetonat-Anion und TMVS ist die Abkürzung für Trimethylvinylsilan)

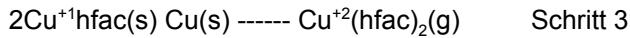

mit Argon als Trägergas. Da dieser Komplex unter Umgebungsbedingungen eine Flüssigkeit ist, kann es in Standard-CVD-Blasenbildner-Vorläuferabgabesystemen verwendet werden, die gegenwärtig bei der Halbleiterherstellung genutzt werden. Sowohl TMVS als auch Kupfer<sup>+2</sup>(hfac)<sub>2</sub> sind flüchtige Nebenprodukte der Abscheidungsreaktion, die aus der Kammer abgeführt werden. Man nimmt an, dass die Abscheidungsreaktion nach den folgenden Mechanismen abläuft, in denen (s) die Interaktion mit einer Oberfläche und (g) die Gasphase bezeichnet.

**[0057]** Im Schritt 1 wird der Komplex aus der Gasphase aus einer metallischen Oberfläche adsorbiert. Im Schritt 2 dissoziiert das koordinierte Olefin (in diesem speziellen Fall TMVS) aus dem Komplex als ein freies Gas, das als instabile Verbindung Cu<sup>+1</sup>hfac hinterlässt. Im Schritt 3 dissoziiert das Cu<sup>+1</sup>hfac und ergibt Kupfermetall und flüchtiges Cu<sup>+2</sup>(hfac)<sub>2</sub>. Die Dissoziation bei CVD-Temperaturen scheint durch metallische oder elektrisch leitende Oberflächen stark katalysiert zu werden. Bei einer alternativen Reaktion kann der organometallische Kupferkomplex zu Wasserstoff reduziert werden, um metallisches Kupfer zu ergeben.

**[0058]** Der flüchtige flüssige Komplex Cu<sup>+1</sup>hfac, TMVS kann dazu verwendet werden, Cu entweder über einen thermischen oder einen Prozess auf Plasmabasis abzuscheiden, wobei der thermische Prozess stärker bevorzugt wird. Die Substrattemperatur für den plasmagestützten Prozess liegt vorzugsweise zwischen etwa 100 und etwa 400°C, während die für den thermischen Prozess zwischen etwa 50 und etwa 300°C, besonders bevorzugt bei etwa 170°C liegt. Anschließend an jeden dieser Prozesse kann eine CVD-Cu-Benetzungsschicht über einer Keimbildungsschicht vorgesehen werden. Alternativ kann elektroplattiertes Kupfer in Kombination mit oder als Ersatz der CVD-Cu-Benetzungsschicht verwendet werden.

**[0059]** Nach dem Abscheiden einer CVD-Cu-Schicht wird das Substrat in eine PVD-Cu-Kammer gebracht, um PVD-Cu unter der Schmelzpunkttemperatur von CVD-Cu und PVD-Cu abzuscheiden. Wenn das Weichmetall Kupfer ist, wird bevorzugt, dass das PVD-Cu bei einer Wafer-temperatur unter etwa 550°C, vorzugsweise etwa unter 400°C abgeschieden wird. Die Kupferschichten beginnen während des PVD-Abscheidungsprozesses bei über 200°C zu fließen, während die Tan-

tal-Sperr-Benetzungsschicht als massive Metallschicht fest an Ort und Stelle bleibt. Da Tantal eine gute Benetzung mit Kupfer hat, wird das CVD-Cu davon abgehalten, das Tantal bei etwa 400°C zu entnetzen, so dass Wafertemperaturen über dem Schmelzpunkt von Aluminium (> 660°C), wie es der CVD-Prozess nach dem Stand der Technik lehrt, nicht erforderlich sind. Deshalb ermöglicht die Verwendung einer dünnen Tantalschicht das Erreichen einer Planarisierung des Kupfers bei Temperaturen weit unter dem Schmelzpunkt von Kupfer.

**[0060]** Bei jedem Aspekt der Erfindung können abgeschiedene Cu-Schichten mit H<sub>2</sub> glühbehandelt werden, um die Schichten gegen die Bildung von CuO widerstandsfähiger zu machen.

**[0061]** Das Kupferplattieren ist viel billiger als PVD- oder CVD-Prozesse, kann jedoch nicht in dem integrierten Behandlungssystem ausgeführt werden. Glücklicherweise hat das Aussetzen des Substrats an Luft beim Überführen zwischen verschiedenen Prozessanordnungen keine merkliche Trennfläche in der Metallschicht gebildet. Es können Kupfer-Tar-gets, die von etwa 0,5 Gew.-% bis etwa 2 Gew.-% Sn enthalten, durch Gasphasenabscheidung abgeschie-den oder unter Verwendung eines dualen Elektronenkanonensystems unter einem Vakuum von 10<sup>-7</sup> Torr (1 Torr = 1,33 Pa) und bei einer Substrattempe-ratur von 150°C elektroplattiert werden.

**[0062]** Während die vorstehenden Ausführungen sich auf die bevorzugte Ausgestaltung der vorliegen-den Erfindung richten, sind andere und weitere Ausführungsformen der Erfindung möglich, ohne von ih-rem Grundgedanken abzuweichen. Der Umfang der Erfindung wird durch die nachstehenden Ansprüche bestimmt.

### Patentansprüche

1. Verfahren zur Ausbildung einer Doppeldamaszen-Zwischenverbindung in einer dielektrischen Schicht mit einer Doppeldamaszen-Umgrenzung für Kontaktloch und Leiter, bei welchem

- a) auf exponierten Oberflächen der dielektrischen Schicht eine Sperrschiicht abgelegt wird,

- b) auf der Sperrschiicht durch chemische Gaspha-senabscheidung oder Elektroplattieren ein leitendes Metall aufgebracht wird,

- c) das leitende Metall nach der chemischen Gaspha-senabscheidung oder dem Elektroplattieren zum Füllen der Kontaktlochumgrenzung wärmebehandelt wird,

- d) nach der Wärmebehandlung das leitende Metall zum Füllen der Leiterumgrenzung durch physikalische Gasphasenabscheidung aufgebracht wird und

- e) das leitende Metall, die Sperrschiicht und die dielektrische Schicht zur Bildung eines Leiterdrahts planarisiert werden.

2. Verfahren nach Anspruch 1, bei welchem das leitende Metall aus der Gruppe ausgewählt wird, die aus Kupfer, Aluminium, dotiertem Kupfer, dotiertem Aluminium und Mischungen davon besteht.

3. Verfahren nach Anspruch 1, bei welchem die Schritte (a) und (b) in einem integrierten Behandlungssystem ausgeführt werden.

4. Verfahren nach Anspruch 1, bei welchem der Schritt der Planarisierung durch chemisches-mechanisches Polieren ausgeführt wird.

5. Verfahren nach Anspruch 1, bei welchem die Sperrsicht ein Material aufweist, das aus der Gruppe ausgewählt wird, die aus Titan, Titannitrid, Titansiliciumnitrid, Wolframnitrid, Wolframsiliciumnitrid, Tantal, Tantalnitrid, Tantsiliciumnitrid, dotiertem Silicium, Aluminium und Aluminiumoxiden besteht.

6. Verfahren nach Anspruch 1, bei welchem das leitende Metall Kupfer oder dotiertes Kupfer ist.

7. Verfahren nach Anspruch 1, bei welchem der Schritt b) eine chemische Gasphasenabscheidung aufweist.

8. Verfahren nach Anspruch 1, bei welchem der Schritt b) das Elektroplattieren aufweist.

Es folgen 6 Blatt Zeichnungen

## Anhängende Zeichnungen

**FIG. 1A**

(STAND DER TECHNIK)

**FIG. 1B**

(STAND DER TECHNIK)

**FIG. 1C**

(STAND DER TECHNIK)

**FIG. 1D**

(STAND DER TECHNIK)

**FIG. 1E**

(STAND DER TECHNIK)

*FIG. 2A*

*FIG. 2B*

*FIG. 2C*

*FIG. 2D*

*FIG. 2E*

FIG. 3A

FIG. 3B

FIG. 3C

FIG. 3D

FIG. 3E

*FIG. 4A*

*FIG. 4B*

*FIG. 4C*

*FIG. 4D*

*FIG. 4E*

*FIG. 5A*

*FIG. 5B*

*FIG. 5C*

*FIG. 5D*

*FIG. 5E*

*FIG. 6*