(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4848366号

(P4848366)

(45) 発行日 平成23年12月28日(2011.12.28)

(24) 登録日 平成23年10月21日(2011.10.21)

(51) Int.Cl.

F 1

**H01L 21/8238 (2006.01)**

**H01L 27/092 (2006.01)**

**H01L 29/423 (2006.01)**

**H01L 29/49 (2006.01)**

**H01L 27/08** 321D

**H01L 29/58** G

請求項の数 6 (全 11 頁)

(21) 出願番号 特願2007-513157 (P2007-513157)

(86) (22) 出願日 平成17年4月18日 (2005.4.18)

(65) 公表番号 特表2007-537595 (P2007-537595A)

(43) 公表日 平成19年12月20日 (2007.12.20)

(86) 國際出願番号 PCT/US2005/013076

(87) 國際公開番号 WO2005/114718

(87) 國際公開日 平成17年12月1日 (2005.12.1)

審査請求日 平成20年4月11日 (2008.4.11)

(31) 優先権主張番号 10/843,850

(32) 優先日 平成16年5月12日 (2004.5.12)

(33) 優先権主張国 米国(US)

(73) 特許権者 504199127

フリースケール セミコンダクター イン

コーポレイテッド

アメリカ合衆国 78729 テキサス州

オースティン ダブリュー パーマー

レーン 7700

(74) 代理人 100116322

弁理士 桑垣 衡

(72) 発明者 アデトゥトゥ、オルビンミ オー。

アメリカ合衆国 78729 テキサス州

オースティン パートリッジ ベンド

ドライブ 12919

最終頁に続く

(54) 【発明の名称】 2種類の金属酸化物ゲート誘電体に1種類の金属ゲート電極が設けられる半導体プロセス及び集積回路

## (57) 【特許請求の範囲】

## 【請求項1】

半導体基板上にN型のトランジスタが形成される第1の領域とP型のトランジスタが形成される第2の領域とを有する半導体デバイスの製造方法において、

前記第1の領域と第2の領域の両方の上方に、酸化ランタンを含有する第1の高K材料からなる第1ゲート誘電体を形成する工程と、

前記第1の領域と第2の領域の両方の上方に、第1ゲート電極膜を形成する工程と、

前記第2の領域から前記第1ゲート誘電体及び前記第1ゲート電極膜を除去する工程と

前記第1の領域と第2の領域の両方の上方に、前記第1の高K材料とは異なる第2の高K材料からなる第2ゲート誘電体を形成する工程と、

前記第1の領域と第2の領域の両方の上方に、第2ゲート電極膜を形成する工程と、

前記第1の領域から前記第2ゲート誘電体及び前記第2ゲート誘電体を除去する工程とを備え、前記第1ゲート電極膜を含んで前記第1の領域に形成される第1ゲート積層構造は前記第2ゲート電極膜を含んで前記第2の領域に形成される第2ゲート積層構造と同一の組成及び膜厚を有する、半導体デバイスの製造方法。

## 【請求項2】

前記第2の高K材料は酸化アルミニウムである、請求項1記載の製造方法。

## 【請求項3】

第1及び第2ゲート電極はタンタル含有層を、前記第1及び第2ゲート誘電体のそれぞれ

10

20

の上に、かつ前記第1及び第2ゲート誘電体のそれぞれとコンタクトする形で含む、請求項2記載の製造方法。

【請求項4】

前記タンタル含有層はTaCから成る、請求項3記載の製造方法。

【請求項5】

前記タンタル含有層はTaSiNから成る、請求項3記載の製造方法。

【請求項6】

第1及び第2ゲート電極は導電層を、前記タンタル含有層の上に、かつタンタル含有層とコンタクトする形で含み、前記導電層はポリシリコン及びタンゲステンから成るグループから選択される、請求項3記載の製造方法。

10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体形成プロセスの分野に関し、特に相補型金属酸化膜半導体(CMOS)の半導体プロセスの分野に関する。

【背景技術】

【0002】

従来のCMOS形成プロセスはこれまで、PMOSトランジスタ及びNMOSトランジスタの両方に関して1種類のゲート誘電体を使用してきた。従来のゲート誘電体はSiO<sub>2</sub>, SiON, 及びSi<sub>3</sub>N<sub>4</sub>を含む。これらの誘電体の膜厚(T<sub>x</sub>)が徐々に小さくなつて、より小さな素子を形成することができるようになるにつれて、直接トンネルによるゲートリーク電流が大きくなっている。更に、薄い酸化膜を有するトランジスタのポリシリコンの空乏化によりゲート容量が非常に大きくなつて望ましくない。

20

【0003】

高い誘電率を有する材料(高K材料)を使用して薄いゲート誘電体に関連する問題の幾つかを解決してきた。高K誘電体を有するトランジスタは相対的に厚いゲート誘電体を使用して形成することができるとともに、相対的に薄いゲート誘電体を有する従来のトランジスタと同じ容量の効果を実現する。最も広く用いられてきた高K材料は、酸化ハフニウム(例えば、HfO<sub>2</sub>)、酸化アルミニウム(例えば、Al<sub>2</sub>O<sub>3</sub>)、及びこれらの化合物の誘導体のような金属酸化物系化合物を含む。

30

【発明の開示】

【発明が解決しようとする課題】

【0004】

高K材料によって誘電体の膜厚問題を解決することができるので有利であるが、高K材料はNMOSトランジスタ及びPMOSトランジスタの閾値電圧に不所望かつ非対称の影響を及ぼすことが判明している。酸化ハフニウムから成る金属酸化物ゲート誘電体は、ゲート電極の仕事関数をバンドギャップの中程に固定(ピニング)するように作用し、この現象が閾値電圧及び駆動電流を含むデバイスパラメータに悪い影響を与えることが理論的に判明している。更に、酸化ハフニウムのような金属酸化物系ゲート化合物に関するフェルミピニングは、不純物ドープポリシリコンをゲート電極として使用する場合に特に、NMOSトランジスタよりもPMOSトランジスタにおいて顕著である(すなわち、PMOSトランジスタのデバイスパラメータの方がNMOSトランジスタのデバイスパラメータよりも大きな影響を受ける)。高K材料を取り入れたプロセスを用いて、非常に薄いゲート誘電体に関連する問題を解決し、同時に高Kゲート誘電体を1種類だけ使用する場合に観察される素子特性の非対称なずれの問題も解決することが望ましい。更に、用いるプロセスが、プロセスフローを簡単にするためにゲート電極材料を1種類だけ使用することができれば望ましい。

40

【課題を解決するための手段】

【0005】

要約すると、本発明は、ゲート電極を1種類のみ設けた構造の2つの異なるゲート誘電

50

体を使用して集積化を行なうC M O S形成プロセスである。異なるゲート誘電体によって、ゲート電極材料の差を補償するとともに、1種類のゲート電極のみを使用することによりプロセスフローを簡単にし、かつプロセスコストを下げる。2つの異なる特定のプロセスフローまたは集積化方法について明示的に記載する。

**【発明を実施するための最良の形態】**

**【0 0 0 6】**

本発明は例を通して示され、そして添付の図によって制限されるものではなく、これらの図では、同様の参照記号は同様の構成要素を指す。

当業者であれば、これらの図における構成要素が説明を簡単かつ明瞭にするために示され、そして必ずしも寸法通りには描かれていないことが分かるであろう。例えば、これらの図における幾つかの構成要素の寸法を他の構成要素に対して誇張して描いて本発明の実施形態を理解し易くしている。10

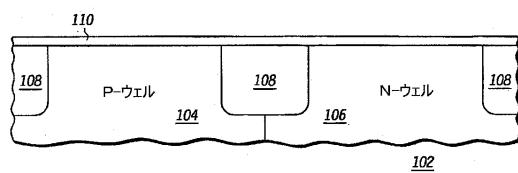

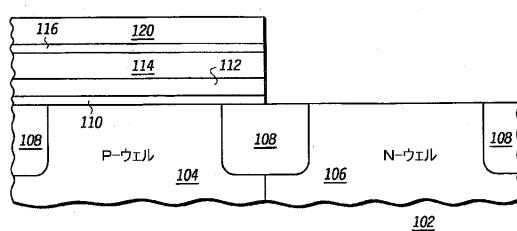

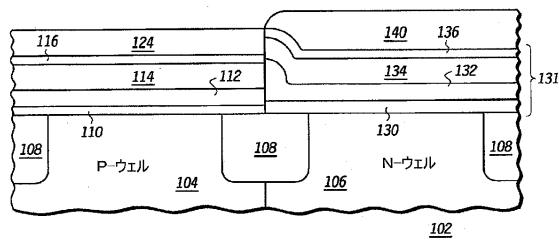

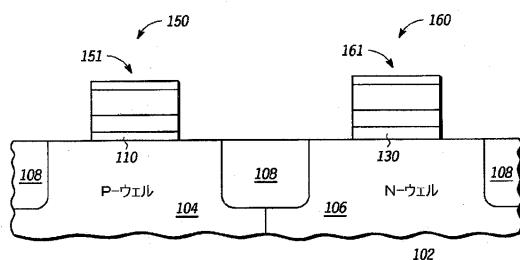

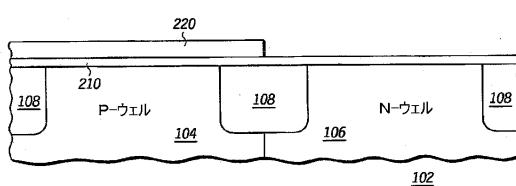

**【0 0 0 7】**

次に、図1を参照すると、プロセスフローの中間工程における半導体ウェハ102の部分断面図が示される。図示の実施形態では、ウェハ102は、第1ウェル領域104(第1ウェル104とも呼ぶ)、及び第2ウェル領域106(第2ウェル106とも呼ぶ)を含み、これらのウェル領域は互いにに対して横方向にずれて配置される。第1ウェル104及び第2ウェル106は逆導電型の不純物を含み、これらのウェルの一方がp型ウェルとなり、そしてこれらのウェルのもう一方がn型ウェルとなる。記載の実施形態では、第1ウェル104がp型ウェル(pウェル)であり、このウェルには、N M O Sトランジスタが形成され、そして第2ウェル106がn型ウェル(nウェル)であり、このウェルには、p M O Sトランジスタが形成される。20

**【0 0 0 8】**

誘電体分離トレンチ108がウェハ102内部に形成されている。トレンチの名前が示すとおり、誘電体分離トレンチ108は隣接素子(トランジスタ)の間の電気的絶縁及び物理的絶縁を実現するように機能する。誘電体分離トレンチ108はシリコン酸化物(または他の誘電体)系化合物により構成されることが好ましく、このシリコン酸化物系化合物は、エッティングによりトレンチをウェハ102内部に形成し、トレンチに誘電体を堆積させることにより充填し、そしてウェハを研磨する、またはエッティングして不要の誘電体を除去することにより形成される。別の方法として、誘電体分離トレンチ108は従来のL O C O S法を使用して形成することができ、このL O C O S法では、シリコン窒化膜を堆積させ、そしてパターニングして絶縁領域を画定し、その後ウェハ102の露出シリコンを熱酸化して絶縁誘電体を形成する。30

**【0 0 0 9】**

ウェル104及び106、及び分離トレンチ108を形成した後、第1ゲート誘電体110をプランケット堆積法によりウェハ102全体を覆って堆積させる。第1誘電体は第1タイプのトランジスタのゲート誘電体として機能する。図示の実施形態では、第1誘電体110は、複数のトランジスタの内、第1ウェル104の上に形成されるゲート誘電体として機能する。第1ウェル104がpウェルである実施形態では、第1ゲート誘電体110はN M O Sトランジスタに使用されるゲート誘電体である。このような一の実施形態では、第1ゲート誘電体110は化学気相成長により形成される金属酸化物系化合物である。第1誘電体110としての使用に適する金属酸化物系化合物は酸化ランタン(好適には、La<sub>2</sub>O<sub>3</sub>)である。第1ゲート誘電体の通常の膜厚は0.5~1.0ナノメートルの範囲である。40

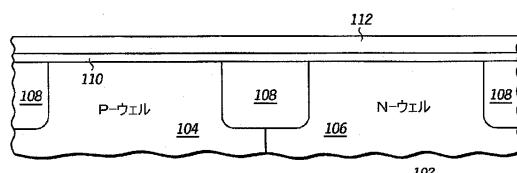

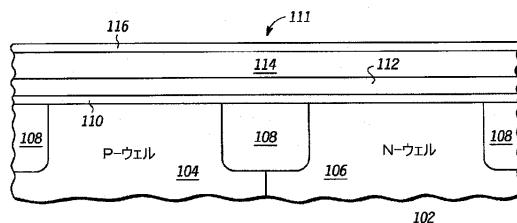

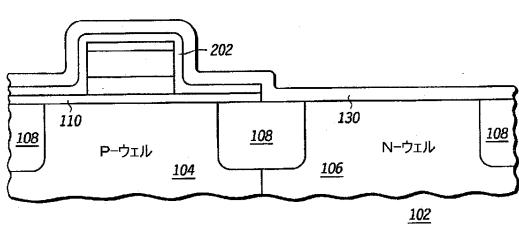

**【0 0 1 0】**

次に、図2及び図3によれば、第1誘電体110形成した後、第1ゲート積層構造111が、ゲート電極層112、導電層114、及び反射防止コーティング(A R C)116を連続して第1誘電体110を覆うように堆積せることにより形成される。一の実施形態では、ゲート電極層112はT a S i N層であり、この層は1~2.0ナノメートルの範囲の膜厚を有することが好ましい。別の実施形態では、ゲート電極層112はT a C層で50

あり、この層は 1 ~ 20 ナノメートルの範囲の膜厚を有する。

#### 【0011】

導電層 114 は、設けるかどうかは任意の層であり、この層を使用して、例えば集積化を簡単に行なうことができる。導電層 114 は高不純物濃度ポリシリコン、タングステン、または別の適切な導電材料であることが好ましく、これらの材料は約 10 ~ 100 ナノメートルの範囲の膜厚を有する。反射防止コーティング(ARC)116 は非常に薄い層であり、この層を使用して、半導体形成の分野で公知のように、後続のフォトリソグラフィ工程を容易に行なうことができるようとする。ARC116 は  $\text{Si}_x\text{N}_y$ 、またはフォトリソグラフィ技術における露光波長で高い吸光率を有するポリマーにより構成することができる。

10

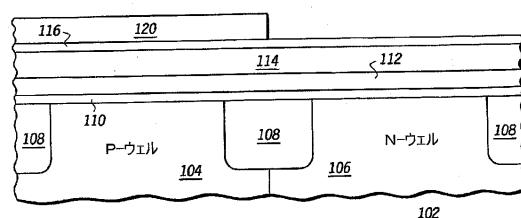

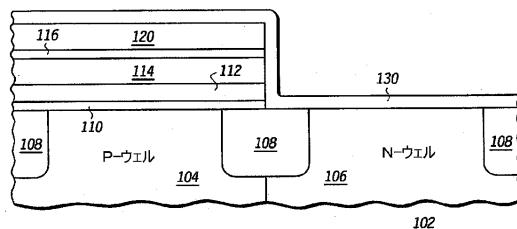

#### 【0012】

次に、図 4 によれば、ARC116 を形成した後、ハードマスク 120 を、第 1 ウェル領域 104 上方の ARC116 の上に選択的に形成する。ハードマスク 120 は CVD により形成される酸化シリコン層であることが好ましい。ハードマスク 120 は、第 1 ウェル領域 104 上方の第 1 ゲート積層構造 111 を、同様のゲート構造を第 2 ウェル領域 106 上方に形成している間に保護するように機能する。

#### 【0013】

次に、図 5 によれば、ハードマスク 120 をパターニングした後、ゲート積層構造 111 の露出部分を除去する。ゲート積層構造 111 の露出部分は、ゲート積層構造の内、第 2 ウェル領域 106 上方の部分を含む。ゲート積層構造の内、第 2 ウェル領域 106 上方の部分を除去することにより、ゲート積層構造 111 の内、第 1 ウェル領域 104 上方の部分の上の保護コーティングを残しながら、ウェハ 106 の内、第 2 ウェル領域 106 上方の上側表面を露出させる。

20

#### 【0014】

次に、図 6 によれば、第 2 ゲート誘電体 130 をウェハ 102 の上に非選択的に堆積させる。第 2 ゲート誘電体 130 は第 1 ゲート誘電体 110 とは異なる材料であり、そして第 2 ウェル領域 106 上の第 2 ゲート誘電体 130 の膜厚は第 1 ウェル領域 104 上の第 1 ゲート誘電体 110 の膜厚とは異ならせることができる。本発明の一の実施形態では、第 1 ゲート誘電体 110 及び第 2 ゲート誘電体 130 は共に、高 K 誘電体であることが重要である。本開示の目的を達成するために、高 K 誘電体は、 $\text{SiO}_2$  の誘電率の少なくとも 1.5 倍の誘電率を有する誘電体である。タンタル系ゲート電極を有する PMOS ランジスタに関連する形での使用に適するこのような一の実施形態では、第 2 ゲート誘電体 130 は、堆積法により形成され、かつ 0.5 ~ 10 ナノメートルの範囲の膜厚を有する酸化アルミニウム膜を含む。

30

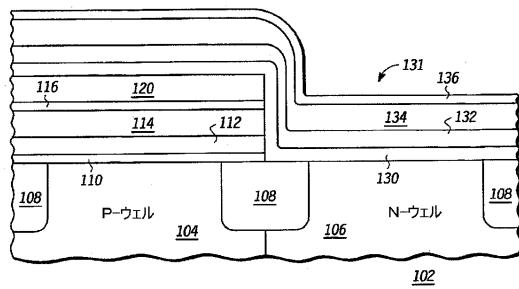

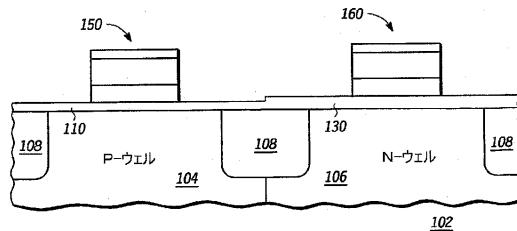

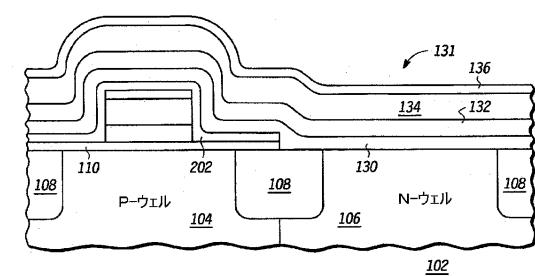

#### 【0015】

図 7 では、第 2 ゲート積層構造 131 は、第 2 ゲート誘電体膜 132 を第 2 ゲート誘電体 130 上に、第 2 導電膜 134 を第 2 ゲート電極 132 上に、そして第 2 ARC 膜 136 を第 2 導電膜 134 上に連続して堆積させることにより形成される。一の実施形態では、第 2 ゲート積層構造 131 は第 1 ゲート積層構造 111 に、第 2 ゲート電極 132 が第 1 ゲート電極膜 112 と同じ組成及び膜厚を有し、第 2 導電膜 134 が第 1 導電膜 114 と同じ組成及び膜厚を有し、そして第 2 ARC 136 が第 1 ARC 116 と同じ組成及び膜厚を有するという点で同等である。設けるかどうかが任意の第 1 導電層 114 を設けない実施形態では、第 2 導電層 134 を第 2 ゲート積層構造 131 には設けないとするので、第 1 ゲート積層構造 111 及び第 2 ゲート積層構造 131 は組成及び寸法(膜厚)に関してほぼ同じになる。

40

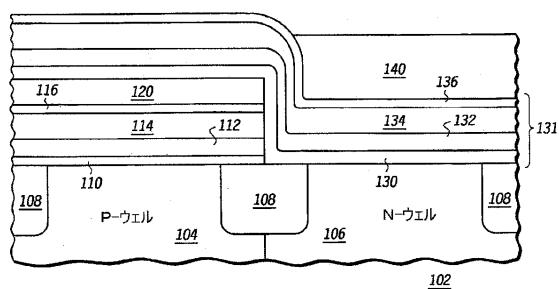

#### 【0016】

図 8 及び図 9 では、フォトレジストマスク 140 をパターニングして、第 2 ウェル領域 106 上の第 2 ゲート積層構造 131 の上に残す。次に、第 2 ゲート積層構造 131 の露出部分(第 2 ウェル領域 106 上に位置しない部分)が、第 1 ゲート積層構造 111 の一部分を除去するために使用するエッチング手順とほぼ同じエッチング手順を使用して除去

50

される。第2ゲート積層構造131の露出部分を除去した後、図9に示すフォトレジスト層140の残りの部分だけでなく、図9に示すハードマスク120の残りの部分を、更に別の処理を継続する前に除去する。

#### 【0017】

図10では、従来のゲート電極エッチング手順を実施して第1トランジスタ150及び第2トランジスタ160を、第1ウェル領域104及び第2ウェル領域106の上にそれぞれ形成する。第1トランジスタ150及び第2トランジスタ160を逆の導電型とし、例えば第1トランジスタ150がN MOSトランジスタとなり、第2トランジスタ160がP MOSトランジスタとなるようにすることが好ましい。第1トランジスタ150及び第2トランジスタ160のゲート誘電体は組成が異なる。上に記載したように、例えば第1ゲート誘電体110を酸化ランタンのような第1材料により構成し、そして第2ゲート誘電体130を酸化アルミニウムのような第2材料により構成することができる。更に、第1トランジスタ150及び第2トランジスタ160が異なる導電型であり、かつ異なるゲート誘電体を有するが、両方のトランジスタのゲート電極は組成及び膜厚の両方に關してほぼ同じである。10

#### 【0018】

半導体製造における当業者であれば、更に別の従来の処理工程（図示せず）を実行して第1トランジスタ150及び第2トランジスタ160を完成させることができると分かるであろう。例えば、一つ以上のエクステンションイオン注入工程、ハロイオン注入工程、スペーサ形成工程、及びソース／ドレインイオン注入工程を実行してトランジスタを完成させることができる。更に統いて、多層配線を通常含む従来の後工程処理（図示せず）が、トランジスタを所望の方法で接続して所望の機能を実現するために必要になる。20

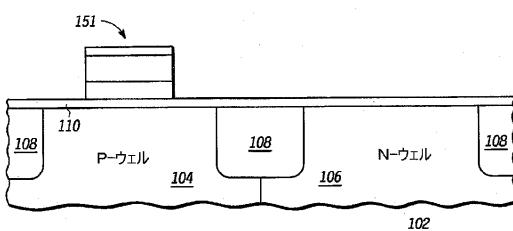

#### 【0019】

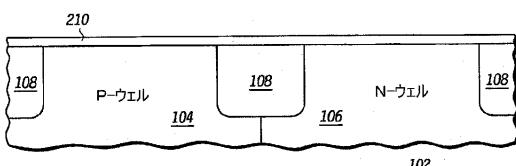

図11～15には、本発明による形成プロセスの第2の実施形態の関連部分が示される。この第2の実施形態の図11の前に、図1～3に関して示し、そして説明した処理手順を実行する。しかしながらその後の処理手順は図4～10に示す手順とは異なる。

#### 【0020】

図11によれば、第1ゲート積層構造111を第1ゲート誘電体110の上に図3に示すように形成した後、第1ウェル領域104上のゲート電極151を第1ゲート積層構造111により、従来のゲート電極形成手順を使用して形成する。詳細には、ゲート電極151は、第1ゲート積層構造111上のフォトレジスト層をパターニングして、所望のゲート電極151が形成される予定の領域を除くゲート積層構造111を露出させることにより形成される。その後、第1ゲート積層構造111を、従来のゲート電極エッチング処理手順を使用してエッティングする。30

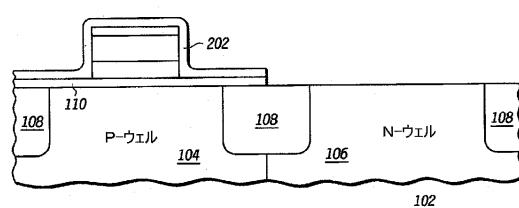

#### 【0021】

図12では、窒化シリコンにより形成されことが好ましいハードマスク202をウェハ102上に堆積させ、そして選択的にエッティングしてハードマスクの内、第2ウェル領域106上の部分を除去して第2ウェル領域106の上側表面を露出させる。次に、第2ゲート誘電体130を図13に示すように堆積させる。

#### 【0022】

図14では、第2ゲート積層構造131をウェハ102上に形成するが、この場合、第2ゲート積層構造131は、第1ゲート電極151を形成するために使用した第1ゲート積層構造111の組成及び膜厚と同じ組成及び膜厚を有する。図15では、第2ゲート電極161が、フォトレジスト層をP MOSゲートマスクを使用してパターニングし、その後、第2ゲート積層構造131の露出部分をエッティングすることにより形成されている。更に、ハードマスク202がウェハから適切なエッティングプロセスを使用して除去されている。

#### 【0023】

本発明の一の実施形態では2層のゲート誘電体を使用する。この実施形態の2つの変形例は第1変形例及び第2変形例を含み、第1変形例では、第1ウェル及び第2ウェルの両4050

方の上のゲート誘電体が2層構造になっており、第2変形例では、これらのウェル内の第1ウェルの上のゲート誘電体が1層構造誘電体であり、第2ウェルの上のゲート誘電体が2層構造誘電体である。好ましくは5～10オングストロームの膜厚を有する第1誘電体層は、N MOS側及びP MOS側の両方で同じにすることができる。好ましくは5～20オングストロームの膜厚を有する第2層は、第1ウェル上で第1組成を有し、そして第2ウェル上で第2組成を有して、異なるゲート電極仕事関数を実現する。この第2層は基本的に仕事関数設定用の誘電体層である。

#### 【0024】

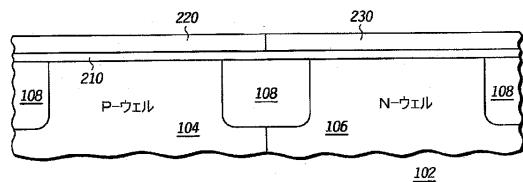

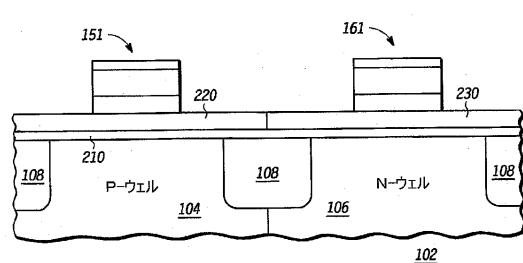

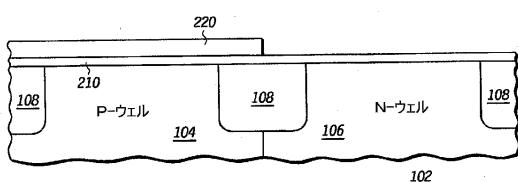

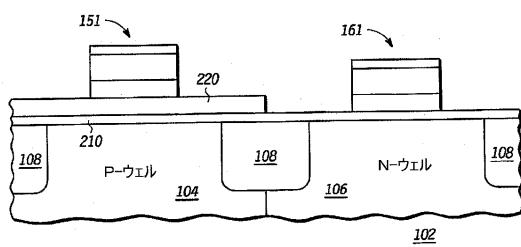

次に、図16～19を参照すると、本発明の或る実施形態が示され、この実施形態では、第1ゲート誘電体（すなわち、第1ウェル104上に形成されるゲート誘電体）は第2誘電体膜220を第1誘電体膜210上に含み、第1誘電体膜210は第1ウェル104上に設けられる。第2ゲート誘電体（すなわち、第2ウェル106上に形成されるゲート誘電体）は第3誘電体膜230を第1誘電体膜210上に含む。この実施形態は、N MOSトランジスタ及びP MOSトランジスタがほぼ同じ組成のゲート電極を使用する構成において、異なるゲート誘電体をN MOSトランジスタ及びP MOSトランジスタに関して設けるというコンセプトを含むが、異なるゲート誘電体は共通の誘電体膜を含む。詳細には、図16によれば、第1誘電体膜210は第1ウェル104及び第2ウェル106の上に形成される。一の実施形態では、第1誘電体膜210はSiO<sub>2</sub>、酸化ハフニウム、または約5～100オングストロームの範囲の膜厚を有する別の高K誘電体である。第1誘電体膜210は、原子層堆積法（ALD）、CVD、またはPVDにより堆積させることができる。次に、第2誘電体膜220を堆積させ、そして図17に示すようにパターニングして、第2誘電体膜220が第1ウェル104上に残るが、第2ウェル106の上から除去されるようとする。次に、第3誘電体膜230を堆積させ、そして図18に示すようにパターニングして、第3誘電体膜230が第2ウェル106上に残るが、第1ウェル104の上から除去されるようとする。第2誘電体膜220が5～20オングストロームの厚さの酸化ランタンまたはLaAlO<sub>3</sub>であり、第3誘電体膜230が5～20オングストロームの厚さの酸化アルミニウムであることが好ましい。第1誘電体膜210と同じように、第2誘電体膜220及び第3誘電体膜230は、ALD、CVD、またはPVDにより堆積させることができる。図19において、第1ゲート積層構造151及び第2ゲート積層構造161は第1ウェル104及び第2ウェル106の上にそれぞれ形成される。

#### 【0025】

図20及び図21を参照すると、前の段落で説明した手順の変形例が示され、この変形例では、第1ウェル104上に形成されるゲート誘電体が第2誘電体膜220を第1誘電体膜210上に含み、第2ウェル106上に形成されるゲート誘電体が第1誘電体膜210を基板（すなわち第2ウェル領域106）上に含む。この実施形態は、第1誘電体膜210を堆積させ、その後、第2誘電体膜220を堆積させ、そしてパターニングして第2誘電体膜220の内、第2ウェル106領域上の部分を除去することにより得られる。図21において、ゲート積層構造151及び161は、それぞれ第1ゲート誘電体及び第2ゲート誘電体の上に形成される。一の実施形態では、第1誘電体膜210はSiO<sub>2</sub>、酸化ハフニウム、または酸化アルミニウムにより構成することができ、第2誘電体膜220は酸化ランタンである。

#### 【0026】

これまでの明細書では、本発明について特定の実施形態を参考しながら記載してきた。しかしながら、この技術分野の当業者であれば、種々の変形及び変更を、以下の請求項に示す本発明の技術範囲から逸脱しない範囲において加え得ることが分かるであろう。例えば、図1に示す素子構造に関する別の構造では、第1ウェル104をn型ウェルとし、第2ウェル106をp型ウェルとする。また、第1及び第2ゲート電極層（112, 132）、及び第1及び第2導電層（114, 134）は開示した材料とは異なる材料とすることができる。更に、記載の層の膜厚は開示した膜厚値とは異なるようにすることができる。従って、明細書及び図は、本発明を制限するものとしてではなく例示として捉えられる

10

20

30

40

50

べきであり、そしてこのような変更の全てが本発明の技術範囲に含まれるべきものである。

【0027】

効果、他の利点、及び技術的問題に対する解決法について、特定の実施形態に関して上に記載してきた。しかしながら、効果、利点、及び問題解決法、及びいずれかの効果、利点、または問題解決法をもたらし、またはさらに顕著にし得る全ての要素（群）が、いずれかの請求項または全ての請求項の必須の、必要な、または基本的な特徴または要素であると解釈されるべきではない。本明細書で使用されるように、「compromise」、「comprising」という用語、または他の全てのこれらの変形は包括的な意味で適用されるものであり、一連の要素を備えるプロセス、方法、製品、または装置がこれらの要素のみを含むのではなく、明らかには列挙されていない、またはそのようなプロセス、方法、製品、または装置に固有の他の要素も含むことができる。10

【図面の簡単な説明】

【0028】

【図1】半導体ウェハの部分断面図であり、このウェハでは、第1ゲート誘電体層がウェハを覆って形成される。

【図2】ゲート電極層を第1ゲート誘電体層を覆うように形成する、図1に続く処理を示す部分断面図。

【図3】導電層及び反射防止コーティングをゲート電極層を覆うように形成する、図2に続く処理を示す部分断面図。20

【図4】ハードマスクを反射防止コーティングの第1部分を覆うように形成する、図3に続く処理を示す部分断面図。

【図5】反射防止コーティング、導電層、及びゲート電極層の露出部分を除去する、図4に続く処理を示す部分断面図。

【図6】第2ゲート誘電体をウェハの第2部分を覆うように形成する、図5に続く処理を示す部分断面図。

【図7】第2ゲート電極層、導電層、及び反射防止コーティングを第2ゲート誘電体を覆うように形成する、図6に続く処理を示す部分断面図。

【図8】フォトレジストマスクをウェハの第2部分を覆うように形成する、図7に続く処理を示す部分断面図。30

【図9】第2反射防止コーティング、導電層、及びゲート電極層の露出部分を除去する、図8に続く処理を示す部分断面図。

【図10】第1及び第2ゲート電極をウェハの第1及び第2部分を覆うように形成する、図9に続く処理を示す部分断面図。

【図11】第1ゲート電極をウェハの第1部分を覆うように形成する、本発明の第2の実施形態による図3に続く処理を示す部分断面図。

【図12】ハードマスクを第1ゲート電極を覆うように形成する、図11に続く処理を示す部分断面図。

【図13】第2ゲート誘電体をウェハの第2部分を覆うように形成する、図12に続く処理を示す部分断面図。40

【図14】第2ゲート電極層、導電層、及び反射防止コーティングをウェハを覆うように形成する、図13に続く処理を示す部分断面図。

【図15】第2ゲート電極をウェハの第2部分を覆うように形成する、図14に続く処理を示す部分断面図。

【図16】半導体ウェハの部分断面図であり、このウェハでは、第1ゲート誘電体層がウェハを覆うように形成される部分断面図。

【図17】第2ゲート誘電体層をウェハの第1部分を覆うように形成する、図16に続く処理を示す部分断面図。

【図18】第3ゲート誘電体層をウェハの第2部分を覆うように形成する、図17に続く処理を示す部分断面図。50

【図19】第1及び第2ゲート電極をウェハの第1及び第2部分を覆うように形成する、図18に続く処理を示す部分断面図。

【図20】第2ゲート電極層をウェハの第1部分を覆うように形成する、別の実施形態による図16に続く処理を示す部分断面図。

【図21】第1及び第2ゲート電極をウェハの第1及び第2部分覆うように形成する、図20に続く処理を示す部分断面図。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図15】

【図13】

【図16】

【図14】

【図17】

【図18】

【図19】

【図20】

【図21】

---

フロントページの続き

(72)発明者 サマベダム、スリカンス ピー .

アメリカ合衆国 7 8 7 2 8 テキサス州 オースティン ベルナーディーノ コープ 2 9 1 3

(72)発明者 ホワイト、ブルース イー .

アメリカ合衆国 7 8 6 6 4 テキサス州 ラウンド ロック ブルーベル ベンド コープ 3

2 0 4

審査官 宇多川 勉

(56)参考文献 特開平03-184368 (JP, A)

特開2002-359295 (JP, A)

特開2002-280461 (JP, A)

特開2001-024188 (JP, A)

特開2004-289061 (JP, A)

特開2004-134753 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/8238

H01L 27/092

H01L 29/423

H01L 29/49