(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2010-0134593

(43) 공개일자 2010년12월23일

(51) Int. Cl.

H01L 33/24 (2010.01) H01L 29/45 (2006.01)

(21) 출원번호 10-2010-7020377

(22) 출원일자(국제출원일자) 2009년03월13일

심사청구일자 없음

(85) 번역문제출일자 2010년09월13일

(86) 국제출원번호 PCT/DE2009/000354

(87) 국제공개번호 WO 2009/121319

국제공개일자 2009년10월08일

(30) 우선권주장

10 2008 016 524.7 2008년03월31일 독일(DE)

10 2008 032 318.7 2008년07월09일 독일(DE)

(71) 출원인

오스람 옵토 세미컨덕터스 게엠베하

독일 레겐스부르크 라이브니츠슈트라쎄 4 (우:93055)

(72) 별명자

엔글, 칼

독일, 93051 레겐스부르그, 젤트루드-본-레-포트

-스트라쎄 5

호펠, 루츠

독일, 93087 엘테글로프셰임, 래씽스트라베 1

(뒷면에 계속)

(74) 대리인

허용록

전체 청구항 수 : 총 15 항

(54) 광전 반도체칩 및 그 제조 방법

### (57) 요 약

광전 반도체칩이 기술된다. 반도체칩은 제1전도성 타입의 층(21)과 제2전도성 타입의 층(22) 사이에서 복사 생성을 위해 제공된 활성층(23)을 구비한 반도체층 시퀀스(2)를 포함한다. 제1전도성 타입의 층(21)은 반도체층 시퀀스(2)의 전방측(110)에 인접한다. 반도체층 시퀀스(2)는 적어도 하나의 리세스(3)를 포함하고, 상기 리세스는 상기 전방측(110)에 대향된 반도체층 시퀀스(2)의 후방측으로부터 활성층(23)을 관통하여 제1전도성 타입의 층(21)까지 연장된다. 제1전도성 타입의 층(21)은 제1전기 연결층(5)을 이용하여 리세스(3)를 관통하여 전기적으로 연결된다. 상기 제1전기 연결층은 반도체층 시퀀스(2)의 후방측(120)을 적어도 부분적으로 덮는다. 반도체칩은 리세스(3)의 영역에서 접합층(20)을 포함하고, 상기 접합층은 제1전도성 타입의 층(21)의 물질 및 제1전기 연결층(5)의 물질로 구성된 물질 조성물을 포함한다. 또한, 이러한 반도체칩의 제조 방법도 기술된다.

**대 표 도** - 도1

(72) 발명자

로드, 패트릭

독일, 93051 레겐스부르그, 멜쿠르스트라베 24

사바틸, 마티아스

독일, 93059 레겐스부르그, 암 프로첸웨이어 21 비

---

## 특허청구의 범위

### 청구항 1

제1전도성 타입의 층(21)과 제2전도성 타입의 층(22) 사이에 복사 생성을 위해 제공된 활성층(23)을 포함하는 반도체층 시퀀스(2)를 구비한 광전 반도체칩에 있어서,

상기 제1전도성 타입의 층(21)은 상기 반도체층 시퀀스(2)의 전방측(110)에 인접하고;

상기 반도체층 시퀀스(2)는 상기 전방측(110)에 대향된 상기 반도체층 시퀀스(2)의 후방측(120)으로부터 상기 활성층(23)을 관통하여 상기 제1전도성 타입의 층(21)까지 연장되는 적어도 하나의 리세스(3)를 포함하고;

상기 제1전도성 타입의 층(21)은 상기 반도체층 시퀀스(2)의 후방측(120)을 적어도 국부적으로 덮는 제1전기 연결층(5)을 이용하여 상기 리세스(3)를 관통하여 전기적으로 연결되며; 그리고

상기 반도체칩은 상기 리세스(3)의 영역에서 접합층(20)을 포함하고, 상기 접합층은 상기 제1전도성 타입의 층(21)의 물질 및 제1전기 연결층(5)의 물질로 구성된 물질 조성물을 포함하는 것을 특징으로 하는 광전 반도체칩.

### 청구항 2

제 1항에 있어서,

상기 광전 반도체칩은 복수 개의 리세스(3)를 포함하고, 상기 리세스는 상호간  $75 \mu\text{m}$  내지  $125 \mu\text{m}$ 의 횡 간격(D5)을 가지는 것을 특징으로 하는 광전 반도체칩.

### 청구항 3

제 1항 또는 제 2항에 있어서,

상기 리세스(3)의 전체면(F)은 상기 후방측(120)의 배면도 상에서 상기 반도체층 시퀀스(2)의 면의 5% 이하, 특히 2% 이하인 것을 특징으로 하는 광전 반도체칩.

### 청구항 4

제 1항 내지 제 3항 중 어느 한 항에 있어서,

상기 광전 반도체칩은 상기 반도체층 시퀀스(2)의 후방측(120)에서 전기 절연 거울층(6) 및 제2전기 연결층(7)을 포함하며, 상기 제2전기 연결층(7)은 상기 반도체층 시퀀스(2)의 후방측(120)을 적어도 국부적으로 덮고, 전기적 분리층(4)을 이용하여 상기 제1전기 연결층(5)으로부터 전기적으로 절연되며, 상기 제1전기 연결층(5), 제2전기 연결층(7) 및 전기적 분리층(4)은 횡 방향으로 겹치고, 상기 절연 거울층(6)은 복수 개의 개구부(60)를 포함하고, 상기 제2전도성 타입의 층(22)은 상기 개구부(60)를 관통하여 상기 제2전기 연결층(7)을 이용하여 전기적으로 연결되는 것을 특징으로 하는 광전 반도체칩.

### 청구항 5

제 4항에 있어서,

상기 광전 반도체칩은 제2전기 연결층(7)과 제2전도성 타입의 층(22) 사이에서 다른 접합층(20')을 포함하고, 상기 다른 접합층은 상기 제2전도성 타입의 층(22)의 물질 및 제2전기 연결층(7)의 물질로 구성된 물질 조성물을 포함하는 것을 특징으로 하는 광전 반도체칩.

### 청구항 6

제 4항 또는 제 5항에 있어서,

상기 개구부(60)는 상호 간에  $5 \mu\text{m}$  이하의 횡 간격(D7)을 가지는 것을 특징으로 하는 광전 반도체칩.

### 청구항 7

**청구항 4** 내지 청구항 6 중 어느 한 항에 있어서,

인접한 2개의 개구부(60) 사이의 간격(D7)과 하나의 개구부(60)의 최대 래터럴 치수간의 비율은 10이하인 것을 특징으로 하는 광전 반도체칩.

### **청구항 8**

제 1항 내지 제 7항 중 어느 한 항에 있어서,

상기 접합층(20) 및/또는 다른 접합층(20')은 5 nm 이상의 층 두께를 가지는 것을 특징으로 하는 광전 반도체칩.

### **청구항 9**

제 1항 내지 제 8항 중 어느 한 항에 있어서,

상기 제1 및/또는 제2전기 연결층(5, 7)은 Au, Ag, Al, Cr, Cu, Ti, Pt, Ru, NiAu 중 적어도 하나의 물질을 포함하는 것을 특징으로 하는 광전 반도체칩.

### **청구항 10**

제 9항에 있어서,

상기 제1 및/또는 제2전기 연결층(5, 7)은 상기 반도체층 시퀀스를 향해 구비되며 Cr, Ti, Pt, Ru 및/또는 NiAu를 함유한 층(71) 및 상기 반도체층 시퀀스와 반대 방향이며 Al, Ag, Au 및/또는 Cu를 함유한 층(72)을 구비한 다층 구조를 포함하는 것을 특징으로 하는 광전 반도체칩.

### **청구항 11**

제 1항 내지 제 9항 중 어느 한 항에 있어서,

상기 광전 반도체칩은 성장 기판을 포함하지 않으며, 성장 기판과 다른 캐리어판(9)을 포함하는 것을 특징으로 하는 광전 반도체칩.

### **청구항 12**

제 1항 내지 제 11항 중 어느 한 항에 따른 광전 반도체칩을 제조하는 방법에 있어서,

리세스(3)를 구비한 반도체층 시퀀스(2)를 제공하는 단계;

상기 리세스(3)의 표면의 적어도 부분 영역 상에 상기 제1전기 연결층(5) 또는 상기 제1전기 연결층의 일부를 증착하는 단계; 및

상기 반도체층 시퀀스(2) 및 상기 제1전기 연결층(5) 또는 제1전기 연결층의 일부를 가열하여, 상기 제1전기 연결층(5)의 물질이 접합층(20)의 형성을 위해 상기 리세스(3)의 표면을 통해 상기 반도체층 시퀀스(2) 안으로 삽입되도록 하는 단계를 포함하는 것을 특징으로 하는 광전 반도체칩 제조 방법.

### **청구항 13**

제 12항에 있어서,

상기 전기 연결층(5) 또는 전기 연결층의 일부를 350°C 이상의 온도, 특히 800°C 이하의 온도로 가열하는 것을 특징으로 하는 광전 반도체칩 제조 방법.

### **청구항 14**

제 11항 또는 제 12항에 있어서,

제 4항 내지 제 10항 중 어느 한 항에 따른 광전 반도체칩을 제조하기 위해 상기 반도체층 시퀀스(2)의 후방측(120) 상에 개구부(60)를 구비한 전기 절연 거울층(6)을 도포하는 단계, 상기 제2전기 연결층(7) 또는 제2전기 연결층의 일부를 상기 반도체층 시퀀스(2) 상에서 적어도 상기 개구부(60)의 영역에 증착하는 단계 및 상기 반도체층 시퀀스(2) 및 상기 제2전기 연결층(7) 또는 제2전기 연결층의 일부를 가열하여, 상기 제2전기 연결층(7)의 물질이 다른 접합층(20')의 형성을 위해 상기 개구부(60)의 영역에서 상기 반도체층 시퀀스(2) 안으로 삽입되도록 하는 단계를 포함하는 것을 특징으로 하는 광전 반도체칩 제조 방법.

입되도록 하는 단계를 더 포함하는 것을 특징으로 하는 광전 반도체칩 제조 방법.

## 청구항 15

제 12항 내지 제 14항 중 어느 한 항에 있어서,

상기 제공된 반도체층 시퀀스는 성장 기판을 포함하고, 상기 성장 기판은 이후의 단계에서 제거되며, 상기 성장 기판의 제거 이전 또는 이후에 상기 반도체층 시퀀스(2)는 캐리어판(9)에 고정되는 것을 특징으로 하는 광전 반도체칩 제조 방법.

## 명세서

### 기술 분야

[0001]

본 출원은 광전 반도체칩 및 광전 반도체칩의 제조 방법에 관한 것이다.

### 발명의 내용

#### 해결하려는 과제

[0002]

본 발명은 전기 광학적 층 효율이 개선된 광전 반도체칩을 제공하는 것을 목적으로 한다.

#### 과제의 해결 수단

[0003]

이러한 목적은 독립항에 따른 광전 반도체칩 및 광전 반도체칩의 제조 방법에 의하여 해결된다. 본 반도체칩 및 방법의 실시예는 각각 종속항에 기술된다. 특히 청구 범위의 공개 내용은 명백하게 참조로 상세한 설명에 포함된다.

[0004]

반도체층 시퀀스를 구비한 광전 반도체칩이 기술되며, 상기 반도체층 시퀀스는 제1 전도성 타입의 층과 제2전도성 타입의 층 사이에서 복사 생성을 위해 제공된 활성층을 포함한다.

[0005]

예컨대, 제1전도성 타입의 층은 n형 층을 가리킨다. 이 경우, 제2전도성 타입의 층은 p형 층을 가리킨다. 또는, 제1전도성 타입의 층이 p형 층이고 제2전도성 타입의 층이 n형 층을 가리킬 수 있다.

[0006]

바람직하게, 활성층은 복사 생성을 위해 pn 접합, 이중 이종 구조, 단일 양자 우물(SQW, single quantum well) 또는 다중 양자 우물 구조(MQW, multiple quantum well)를 포함한다. 양자 우물 구조란 명칭은 양자화의 차원성과 관련한 의미를 전개하지 않는다. 상기 명칭은 특히 양자상자, 양자선, 양자점 및 이들 구조의 각 조합을 포함한다. MQW 구조에 대한 예는 문현 WO 2001/39282, US 5,831,277, US 6,172,382 B1 및 US 5,684,309에 기술되어 있고, 그 공개 내용은 참조로 포함된다.

[0007]

제1전도성 타입의 층은 반도체층 시퀀스의 전방측에 인접한다. 제2전도성 타입의 층은, 특히, 반도체층 시퀀스의 후방측에 인접한다. 반도체층 시퀀스의 후방측은 상기 전방측에 대향되어 배치된다. 특히, 반도체칩은 활성 층으로부터 생성된 전자기 복사를 상기 반도체칩의 전방측으로부터 방출하도록 제공된다.

[0008]

적어도 일 실시예에 따르면, 반도체층 시퀀스는 상기 반도체층 시퀀스의 후방측으로부터 활성층을 관통하여 제1 전도성 타입의 층까지 연장되는 적어도 하나의 리세스를 포함한다.

[0009]

리세스는 후방측으로부터 전방측의 방향으로 반도체층 시퀀스 안으로 연장되는 함몰부를 나타낸다. 일 실시예에서, 함몰부는 블라인드 홀의 형태를 가진다. 리세스는 예컨대 반도체층 시퀀스의 주 연장면에 대해 수직이거나 경사진 중심축을 포함한다. 적합하게, 리세스는 제2전도성 타입의 층 및 활성층을 관통하여 연장된다. 리세스는, 특히, 후방측으로부터 제1전도성 타입의 층 안으로 연장되며, 바람직하게 제1전도성 타입의 층의 중앙 영역에서 종결된다.

[0010]

이러한 실시예에서, 제1전도성 타입의 층은 제1전기 연결층을 이용하여 리세스를 관통하여 전기적으로 연결된다. 상기 제1전기 연결층은 반도체층 시퀀스의 후방측을 적어도 국부적으로 덮는다. 적합하게, 제1전기 연결층은 리세스에서 전기적 분리층을 이용하여 활성층 및 제2전도성 타입의 층에 대해 전기적으로 절연된다.

[0011]

본 명세서에서, 제1전기 연결층이 반도체층 시퀀스의 후방측을 적어도 국부적으로 덮는다는 것은, 제1전기 연결층의 적어도 일부가 전방측으로부터 후방측을 향한 방향에서 반도체층 시퀀스보다 뒤에 위치한다는 것을 의미한다. 그러나, 전체의 제1전기 연결층이 후방측에 배치될 필요는 없다. 오히려, 제1전기 연결층의 부분 영역은 후

방측으로부터 리세스 안으로, 제1전도성 타입의 층에 이르기까지 연장된다. 특히, 제1전기 연결층은 리세스의 영역에서 반도체층 시퀀스에 인접한다. 제1전기 연결층은 예컨대 금속층이며, 즉 상기 제1전기 연결층은 하나 이상의 금속을 포함하거나 그것으로 구성된다. 상기 연결층은 반도체층 시퀀스에 전기적 구동 전류를 공급하기 위해 제공된다.

[0012] 제1전도성 타입의 층이 중앙 영역을 포함하면, 이러한 중앙 영역은 예컨대 전류 분포층을 나타낸다. 이를 위해, 상기 영역은 예컨대 도핑 농도가 증가할 수 있다. 예컨대, 중앙층에서 제1전도성 타입의 도편트의 농도는, 전방 측의 방향 및/또는 후방측의 방향에서 중앙 영역에 인접하는 제1전도성 타입의 층의 부분 영역에 비해, 5배이고, 특히 10배이다. 대안적 또는 부가적으로, 중앙 영역은 교대로 구비되는 층들의 초격자(superlattice)를 포함할 수 있다. 이러한 초격자에서, 층들, 예컨대 교대로 구비되는 GaN 및 AlGaN 층들은 일 실시예에서 10 nm이하의 층 두께, 바람직하게 5 nm 이하, 특히 2 nm 이하의 층 두께를 가진다. 교대로 구비된 층들 각각이 제1 전도성 타입의 도편트로 도핑되고 다른 층은 명목상 도핑되지 않는 경우도 고려될 수 있다.

[0013] 이러한 실시예에서, 반도체칩은 리세스의 영역에서 접합층을 포함하고, 상기 접합층은 제1전도성 타입의 층의 물질 및 제1전기 연결층의 물질로 구성된 물질 조성을 포함한다. 특히, 리세스 및 접합층은 횡방향으로 겹친다.

[0014] 본 명세서와 관련하여, 접합층이 제1전도성 타입의 층의 물질 및 제1전기 연결층의 물질로 구성된 물질 조성을 포함한다는 것은, 특히, 제1전도성 타입의 층의 물질 및 제1전기 연결층의 물질이 서로 혼합되어 있음을 의미한다. 바람직하게, 접합층은 제1전도성 타입의 층의 물질과 제1전기 연결층의 물질 사이에서 단일의 물질 조성물 - 예컨대 합금의 방식으로 - 을 포함한다. 이 때, 제1전기 연결층의 물질 비율은 후방측으로부터 전방측을 향하여 진행하면서 접합층의 층두께에 의해 연속적으로 또는 단계적으로 감소할 수 있다. 예컨대, 제1전기 연결층의 물질은 제1전도성 타입의 층의 물질에 삽입 확산된다.

[0015] 접합층을 이용하면, 유리하게도 제1전기 연결층과 제1전도성 타입의 층 사이에 전기 접촉 저항이 매우 낮게 얻어진다. 바람직하게는, 접촉 저항은  $2 \times 10^{-5} \text{ Ohm/cm}^2$  이하, 예컨대 약  $2 \times 10^{-6} \text{ Ohm/cm}^2$  이다. 낮은 접촉 저항은, 특히, 약 1 A 이상, 예컨대 1.4 A 이상의 높은 구동 전류로 반도체칩이 구동할 때 유리하다. 구동 전류가 높으면, 접촉 저항은 반도체칩의 특성선에 큰 영향을 줄 수 있다.

[0016] 이러한 실시형태의 실시예에서, 리세스의 최대 횡방향 치수는 10  $\mu\text{m}$  이상이다. 다른 실시예에서, 리세스의 최대 횡방향 치수는 30  $\mu\text{m}$  이하이다.

[0017] 다른 실시예에서, 반도체칩은 복수 개의 리세스를 포함하고, 상기 리세스는 서로 간에 75  $\mu\text{m}$  이상의 횡 간격을 가진다. 다른 실시예에서, 횡 간격은 125  $\mu\text{m}$  이하이다. 바람직하게 상기 횡 간격의 값은 75  $\mu\text{m}$  내지 125  $\mu\text{m}$  이다. 리세스의 상호간 횡 간격은 측면에서 연속한 각 2개의 리세스 사이의 간격이다.

[0018] 일 실시예에서, 후방측의 배면도 상에서 리세스의 전체면은 반도체층 시퀀스의 후방측의 주요면의 5% 이하, 특히 2% 이하이다. 후방측의 주요면은 후방측을 향해 구비되는 반도체층 시퀀스의 표면의 부분이다.

[0019] 따라서, 이와 같이 작은 전체면을 가진 리세스는 반도체칩의 광학적 효율을 위해 유리하다. 종래의 반도체칩은 반도체층 시퀀스의 주요면의 10% 이상을 덮는 전기 연결면을 포함하는 경우가 많다. 본 명세서에서, 제1전도성 타입의 층의 전기 연결부의 면은 리세스의 면에 의해 정해진다. 이러한 방식으로, 제1전도성 타입의 층의 전기 연결부에 의한 활성면의 손실이 매우 낮다. 접합층을 이용하면, 이와 같이 낮은 작은 연결면에도 불구하고 반도체층 시퀀스와 제1전기 연결층 사이에 비교적 낮은 전기 접촉 저항이 달성될 수 있다.

[0020] 다른 실시예에서, 광전 반도체칩은 제1전기 연결층에 대해 대안적 또는 부가적으로 제2전기 연결층을 포함하고, 상기 제2전기 연결층은 반도체층 시퀀스의 후방측을 적어도 국부적으로 덮는다. 상기 제1연결층을 이용하여 제1 전도성 타입의 층이 리세스를 관통하여 연결된다. 제2전기 연결층을 이용하면, 제2전도성 타입의 층이 전기적으로 연결된다.

[0021] 제1전기 연결층 및 제2전기 연결층은, 특히, 전기적 분리층에 의해 쌍방간 전기적으로 절연된다. 바람직한 실시 예에서, 제1전기 연결층, 제2전기 연결층 및 전기적 분리층은 반도체칩의 후방측에서 횡방향으로 겹친다.

[0022] 이러한 실시예에서, 예컨대 반도체칩의 광 방출 전방측은 본딩 패드와 같은 전기 접촉부를 포함하지 않는다. 이러한 방식으로, 구동 시 활성층으로부터 방출된 전자기 복사의 일부가 전기 접촉부에 의해 차폐되거나 차폐되고 흡수될 위험이 감소할 수 있다.

[0023] 이러한 실시형태의 실시예에서, 반도체칩은 반도체층 시퀀스의 후방측에서 전기 절연 거울층을 포함한다. 전기

절연 거울층은 복수 개의 개구부를 포함하고, 상기 개구부를 관통하여 제2전도성 타입의 층이 제2전기 연결층을 이용하여 전기적으로 연결된다. 특히, 전기 절연 거울층은 적어도 국부적으로, 반도체층 시퀀스와 제1 및/또는 제2전기 연결층 사이에 배치된다. 전기 절연 거울층 대신 반도체 거울층이 고려될 수 있다.

[0024] 예컨대, 거울층의 굴절률은, 반도체층 시퀀스에서 전방측을 향한 방향으로 상기 거울층보다 뒤에 배치되며 특히 상기 거울층에 인접하는 층의 굴절률보다 1이상만큼 차이가 난다. 일 실시예에서, 거울층은  $\text{SiO}_2$  또는 규소질화물( $\text{SiN}_x$ )와 같은 유전체를 포함한다. 일 실시예에서, 전기 절연 거울층은 분포 브래그 반사체(DBR, distributed bragg reflector)를 포함하고, 상기 반사체는 교대로 높고 낮은 굴절률을 가진 층들로 구성되는 적어도 하나의 쌍을 포함한다. 브래그 반사체의 층은 예컨대 규소이산화물, 탄탈륨이산화물 및/또는 티타늄이산화물을 포함한다.

[0025] 전기 절연 거울층은 - 예컨대 굴절률의 변화에 의해 - 매우 큰 반사 계수를 포함하여, 상기 거울층은 활성층으로부터 후방측의 방향으로 방출되는 전자기 복사를 전방측의 방향으로 매우 효율적으로 재귀 반사한다.

[0026] 일 실시예에서, 전기 절연 거울층은 적어도 하나의 저굴절성 물질을 포함한다. 저굴절성 물질은, 본 명세서에서, 굴절률이 1.38 이하이고, 바람직하게 1.25이하인 물질을 의미한다.

[0027] 이러한 저굴절성 물질은 예컨대 매트릭스 물질을 포함하고, 상기 매트릭스 물질에 기공이 포함된다. 매트릭스 물질은 예컨대 규소이산화물을 가리킬 수 있다. 기공은 특히 가스 - 가령 공기 - 로 채워진다. 매트릭스 물질은 예컨대 가스의 굴절률보다 큰 굴절률을 가진다. 기공에 의해, 저굴절성 물질의 유효 굴절률이 매트릭스 물질의 굴절률 미만으로 감소한다. 기공은 특히 나노미터 범위의 치수를 가지며, 예컨대 8 nm 이하이고, 바람직하게는 3 nm 이하이다.

[0028] 저굴절성 물질을 이용하면, 유리하게, 전반사를 위한 매우 큰 한계각이 얻어진다. 전기 절연성 거울층에 비교적 경사져서 도달하는 광빔은 저굴절성 물질을 이용하여 전반사된다.

[0029] 일 실시예에서, 저굴절성 물질의 유전 상수는 3.9 이하, 바람직하게 2.7 이하이다. 예컨대, 유전 상수가 3.9 이하이고, 특히 2.7 이하인 저굴절성 물질은, 층 두께가 수 100 나노미터에 이르는 범위를 가질 때 비교적 적은 전자기 복사만을 흡수한다. 바람직하게, 전기 절연성 거울층의 흡수 계수는  $10^{-3}$ 이하이다.

[0030] 기공 대신, 또는 기공에 대해 부가적으로, 저굴절성 물질은 하나 이상의 첨가물을 포함할 수 있다. 예컨대, 규소이산화물을 위해 불소, 염소 또는 C-H 적합한 첨가물이 있다. 특히, 이러한 물질은 규소에서 결합 위치를 차지하여, 규소이산화물로부터 완결정 구조(full-crystalline network)망이 형성되는 경우를 방지한다.

[0031] 기공을 포함한 저굴절성 물질은 예컨대, 이러한 첨가물이 적합한 공정, 예컨대 가열에 의해 다시 매트릭스 물질로부터 빠져나오면서 제조될 수 있다. 규소이산화물의 경우, 이러한 방식으로 예컨대 약 1.14의 굴절률을 가진 저굴절성 물질이 얻어질 수 있다.

[0032] 일 실시예에서, 전기 절연 거울층은 반도체층 시퀀스의 후방측의 주요면의 적어도 50%를 덮는다. 바람직하게, 전기 절연 거울층은 상기 거울층에 도달하는 광의 적어도 96%를 전방측의 방향으로 재귀 반사한다.

[0033] 전기 절연 거울층은 -소정의 주파수 범위를 위해- 1보다 작은 굴절률을 가지고 더욱이 0보다 작은 굴절률을 가질 수 있다. 이와 같은 거울층은 예컨대 광 결정을 이용하여 구현될 수 있다. 3차원 광 결정을 이용하여, 예컨대, 활성층으로부터 방출된 전자기 복사의 전반사가 전기 절연 거울층 상에의 입사각과 무관하게 달성될 수 있다. 3차원 광 결정의 주기는 예컨대 활성층의 방출 최대 파장의 1/4이다.

[0034] 유리한 실시예에서, 전기 절연 거울층은 전방측으로부터 후방측을 향하는 방향으로 우선 저굴절성 물질을 함유한 층을 포함하고, 이어서 브래그 반사체를 포함한다. 저굴절성 물질을 포함한 층을 이용하면, 활성층으로부터 방출되어 비교적 평각으로 거울층에 도달하는 전자기 복사가 전반사에 의해 전방측을 향해 재귀 반사된다. 활성층으로부터 방출되어 거울층에 경사각으로, 예컨대 수직으로 도달하는 전자기 복사는 저굴절성 물질을 포함한 층을 투과하여, 특히 경사지게 도달하는 전자기 복사에 대해 높은 반사 계수를 가지는 브래그 반사체로부터 전방측을 향하여 재귀 반사된다.

[0035] 다른 유리한 실시예에서, 광전 반도체칩은 제2전기 연결층과 제2전도성 타입의 층 사이에서 다른 접합층을 포함하고, 상기 다른 접합층은 제2전도성 타입의 층의 물질 및 제2전기 연결층의 물질로 구성된 물질 조성을 포함한다.

- [0036] 반도체칩의 실시예에서, 제2전도성 타입의 층은 제2전기 연결층을 이용하여 간접적으로 전기적 연결된다. 특히, 이러한 실시예에서, 제2전도성 타입의 층, 경우에 따라서 다른 접합층 및 제2전기 연결층이 간접적으로 연속한다. 이러한 실시예에서, 반도체층 시퀀스는 터널 접합 및 다른 제1전도성 타입의 층을 포함하고, 상기 층들은 이러한 순서로 후방측을 향하여 제2전도성 타입의 층 다음에 배치된다. 가령 npn 반도체층 시퀀스와 같은 이러한 반도체층 시퀀스에 대한 예는 문현 WO 2007/012327 A1에 기술되어 있고, 그 공개 내용은 참조로 포함된다. 다른 접합층을 포함하는 이러한 실시예에 따른 반도체칩에서, 상기 다른 접합층은 제2전도성 타입의 층의 물질 대신 다른 제1전도성 타입의 층을 포함한다.

- [0037] 반도체칩의 다른 실시예에서, 전기 절연 거울층의 개구부의 최대 횡 방향 치수 - 즉 예컨대 동심원형 홀일 때 직경 또는 직사각형 홀일 때는 대각선 - 는  $1 \mu\text{m}$  이하이다. 측면에서 연속하는 개구부는 예컨대  $5 \mu\text{m}$  이하의 횡 간격을 포함한다.

- [0038] 특히, p형층인 제2전도성 타입의 층과 제2전기 연결층 사이에 다른 접합층이 위치한 경우, 이러한 방식으로 구동 전류가 p형층에 매우 균일하게 주입될 수 있다. 2개의 인접한 개구부들간의 간격과 개구부들 또는 개구부들 중 적어도 하나의 최대 횡 방향 치수간의 비율이 10 이하일 때 매우 유리하다.

- [0039] 일 실시예에서, 접합층 및/또는 다른 접합층은 층 두께 - 본 명세서에서 특히 후방측으로부터 전방측을 향한 방향으로의 치수 - 는  $5 \text{ nm}$  이상이고, 예컨대  $10 \text{ nm}$  이상이다.

- [0040] 제1 및/또는 제2전기 연결층은 예컨대 Au, Ag, Al, Cr, Cu, Ti, Pt, Ru, NiAu 중 적어도 하나의 물질을 포함한다.

- [0041] 일 실시예에서, 제1 및/또는 제2전기 연결층은 다층 구조를 포함한다. 일 실시예에서, 다층 구조는 반도체층 시퀀스를 향한 층을 포함하고, 상기 층은 Cr, Ti, Pt, Ru 및/또는 NiAu를 포함한다. 반도체층 시퀀스와 반대 방향인 다층 구조의 층은 예컨대 Al, Ag, Au 및/또는 Cu를 포함할 수 있다.

- [0042] 반도체층 시퀀스를 향한 층을 이용하여, 예컨대 제1 또는 제2전기 연결층이 반도체층 시퀀스 및/또는 전기 절연 거울층에 매우 양호하게 부착될 수 있다. 반도체층 시퀀스와 반대 방향인 층은 예컨대 매우 양호한 전기 전도도 및/또는 매우 높은 반사 계수를 포함한다.

- [0043] 유리한 실시예에서, 반도체층 시퀀스를 향한 다층 구조의 층은 투광성이다. 예컨대, 상기 층은 NiAu를 포함한다. NiAu는 특히 산소를 함유한 대기에서 가열에 의해 투광성이 된다. 대안적 또는 부가적으로, 반도체층 시퀀스를 향한 다층 구조의 층은 그 층 두께에 의해서도 투광성일 수 있다. 반도체층 시퀀스를 향한, 다층 구조의 투광성층은, 특히, 반도체층 시퀀스와 반대 방향인 다층 구조의 층이 매우 높은 반사 계수를 가지는 경우에 유리하다.

- [0044] 일 실시예에서, 접합층은 반도체층 시퀀스를 향한 층의 물질, 즉 Ti, Pt 및/또는 NiAu를 포함한다. 대안적 또는 부가적으로, 접합층은 반도체층 시퀀스와 반대 방향인 층의 물질, 즉 예컨대 Al, Ag 및/또는 Au를 포함할 수 있다. 반도체층과 반대 방향인 다층 구조의 층의 물질은 광전 반도체칩의 제조 시 예컨대 반도체층 시퀀스를 향한 층을 관통하여 접합층에 도달할 수 있다.

- [0045] 다른 실시예에서, 광전 반도체칩은 박막 발광다이오드칩이다. 특히, 반도체칩은 상기 반도체칩의 후방측에서 캐리어판을 포함한다. 일 실시예에서, 제1 및 제2전기 연결층은 적어도 국부적으로 반도체층 시퀀스와 캐리어 기판 사이에 배치된다.

- [0046] 박막 발광다이오드칩은 이하의 특징적 특성을 중 적어도 하나를 특징으로 한다:

- [0047] - 복사 생성 반도체층 시퀀스, 특히 복사 생성 에피택시 층시퀀스에서 캐리어 부재, 특히 캐리어판을 향한 주요 면에는 반사층이 도포되거나 형성되고, 상기 반사층은 반도체층 시퀀스에서 생성된 전자기 복사의 적어도 일부를 상기 반도체층 시퀀스에 재귀 반사함. 이러한 반사층의 적어도 일부 영역은 예컨대 전기 절연 거울층 및/또는 제1 및/또는 제2전기 연결층으로 형성됨;

- [0048] - 박막 발광다이오드칩은 캐리어 부재를 포함하고, 상기 캐리어 부재는 반도체층 시퀀스가 에피택시얼 성장되었던 성장 기판이 아니라, 차후에 반도체층 시퀀스에 고정되는 별도의 캐리어 부재를 가리킴;

- [0049] - 반도체층 시퀀스의 두께는  $20 \mu\text{m}$  이하의 범위, 특히  $10 \mu\text{m}$  이하의 범위를 가짐;

- [0050] - 반도체층 시퀀스는 성장 기판을 포함하지 않음. 여기서 "성장 기판을 포함하지 않음"이란, 경우에 따라서 성장을 위해 사용된 성장 기판이 반도체층 시퀀스로부터 제거되거나 적어도 상당히 얇아져있음을 의미함. 특히,

상기 성장 기판이 그 자체로 또는 에피택시 층시퀀스와 함께만으로는 자체 지지력을 가지지 못할만큼 얇아져있음. 상당히 얇아진 성장 기판의 잔류한 나머지는 특히 성장 기판의 기능을 하기 위한 것으로서는 부적합함; 그리고

[0051] - 반도체층 시퀀스는 혼합 구조를 가진 적어도 하나의 면을 구비한 적어도 하나의 반도체층을 포함하고, 상기 혼합 구조는 이상적인 경우 반도체층 시퀀스에서 광이 거의 에르고딕으로 분포하도록 유도하며, 즉 상기 혼합 구조는 가능한 한 에르고딕한 확률적 산란 거동을 포함함.

[0052] 박막 발광다이오드칩의 기본 원리는 예컨대 문헌 I.Schnitzer et al., Appl. Phys. Lett. 63(16) 1993.10.18, 2174-2176쪽에 기술되어 있고, 그 공개 내용은 참조로 포함된다. 박막 발광 다이오드칩에 대한 예는 문헌 EP0905797 A2 및 WO 02/13281 A1에 기술되어 있고, 그 공개 내용도 마찬가지로 참조로 포함된다.

[0053] 박막 발광 다이오드칩은 거의 람베르시안 표면 이미터에 가깝고, 예컨대 투광기, 가령 자동차 전조등에 사용되기에 적합하다.

[0054] 광전 반도체칩의 제조 방법에서, 일 실시예에 따르면, 리세스를 포함한 반도체층 시퀀스가 제공된다. 이후, 제1전기 연결층은 리세스 표면의 적어도 일부 영역상에 증착된다. 또는, 우선 제1전기 연결층의 일부분만 리세스 표면의 적어도 하나의 부분 영역 상에 증착될 수 있다. 예컨대 다층 구조를 가진 제1전기 연결층의 경우에, 층들 중 하나만 - 완성된 반도체칩에서 반도체층 시퀀스를 향해있는 층을 나타냄 - 이 증착될 수 있다. 증착은 예컨대 기화 방법을 이용하여 수행될 수 있다.

[0055] 본 방법에서, 제1전기 연결층 또는 제1전기 연결층의 일부의 증착과 동시에 또는 상기 증착 이후에, 반도체층 시퀀스 및 제1전기 연결층 또는 제1전기 연결층의 일부는 가열되며, 제1전기 연결층의 물질이 접합층의 형성을 위해 리세스 표면을 통해 반도체층 시퀀스 안으로 삽입되도록 가열된다. 예컨대, 상기 가열은 소결 공정을 나타낸다. 제1전기 연결층의 물질은 예컨대 확산을 이용하여 반도체층 시퀀스 안으로 삽입될 수 있다.

[0056] 일 실시예에서, 제1전기 연결층의 물질은 공용물(eutectic)이다. 공용물은 유리하게도 융점이 매우 낮다. 방법의 실시예에서, 상기 가열 시 제1전기 연결층의 물질은 적어도 국부적으로 용융된다.

[0057] 일 실시예에서, 반도체층 시퀀스 및 제1전기 연결층 또는 제1전기 연결층의 일부는 350°C 이상의 온도에서, 특히 400°C 이상의 온도에서 가열된다. 바람직하게, 상기 온도는 800°C 이하, 특히 500°C 이하이다. 일 실시예에서, 제1전기 연결층 또는 제1전기 연결층의 일부는 산소 가스 또는 산소를 함유한 가스 혼합물에서 가열된다.

[0058] 방법의 다른 실시예에서, 제2전기 연결층 또는 제2전기 연결층의 일부는 반도체층 시퀀스 상에 증착된다. 제2전기 연결층의 증착은 제1전기 연결층의 증착과 동시에, 제1전기 연결층의 증착 이전에 또는 제1전기 연결층의 증착 이후에 수행될 수 있다.

[0059] 이러한 실시예에서, 제2전기 연결층의 증착 이전에 개구부를 구비한 전기 절연 거울층이 반도체층 시퀀스의 후방측에 도포된다. 적합하게, 제2전기 연결층 또는 제2전기 연결층의 일부는 적어도 반도체층 시퀀스의 개구부의 영역에서 증착된다.

[0060] 이어서, 반도체층 시퀀스 및 제2전기 연결층 또는 제2전기 연결층의 일부는 가열되며, 상기 제2전기 연결층의 물질이 접합층의 형성을 위해 특히 전기 절연 거울층의 개구부의 영역에서 반도체층 시퀀스 안으로 삽입되도록 가열된다.

[0061] 제2전기 연결층의 가열은 제1전기 연결층 또는 제1전기 연결층의 일부의 가열과 동시에, 그 이전에 또는 그 이후에 수행될 수 있다. 바람직하게, 온도는 다시 350°C 이상, 특히 400°C 이상 및/또는 800°C 이하, 특히 600°C 이하이다. 가열은 산소 가스 또는 산소를 함유한 가스 혼합물에서 수행될 수 있다.

[0062] 방법의 실시예에서, 제1전기 연결층 또는 제1전기 연결층의 일부는 증착되고 제1온도로 가열된다. 그 이전 또는 이후에, 제2전기 연결층 또는 제2전기 연결층의 일부가 증착되고 제2온도로 가열되며, 이 때 제2온도는 제1온도와 상이하다. 이러한 실시예에서, 바람직하게, 본 방법은, 우선, 두 온도 중 더 높은 온도로 가열되는 전기 연결층이 증착되고 가열되도록 수행된다.

[0063] 방법의 다른 실시예에서, 제공된 반도체층 시퀀스는 성장 기판을 포함하고, 상기 성장 기판은 방법의 이후 단계에서 - 즉 제1 및/또는 제2전기 연결층을 포함한 반도체층 시퀀스의 가열 이후에 수반되는 단계에서 - 제거된다. 이러한 실시예에서, 반도체층 시퀀스가 성장 기판의 제거 이전 또는 이후에 캐리어판에 고정되는 경우가 고려될 수 있다. 이는 예컨대 공용 본딩 단계, 땜납 결합 및/또는 접착 결합을 이용하여 수행될 수 있다.

[0064] 상기 방법의 실시예에서, 제1전기 연결층 및/또는 제2전기 연결층은 캐리어판과 반도체층 시퀀스가 결합하기 전에 제조된다. 이러한 방식으로, 전기 연결층의 제조 시 반도체칩은, 접합층(들)의 형성을 위해 필요하면서 반도체층 시퀀스와 캐리어판간의 결합이 안정적으로 유지될 때까지의 온도보다 높은 온도로 가열될 수 있다.

### 도면의 간단한 설명

[0065] 다른 이점, 유리한 실시예는 도면과 관련하여 기술된 이하의 실시예로부터 도출된다.

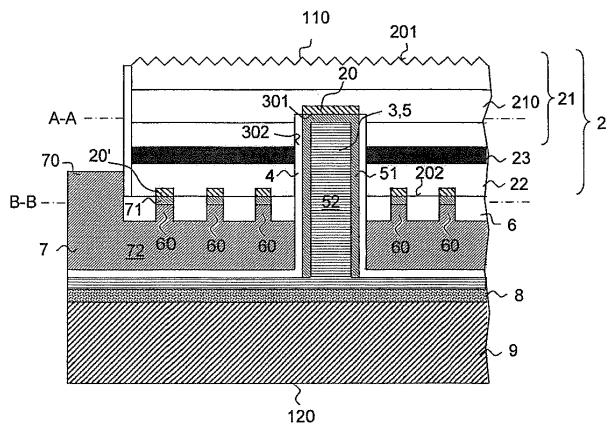

도 1은 일 실시예에 따른 광전 반도체칩의 개략적 횡단면도이다.

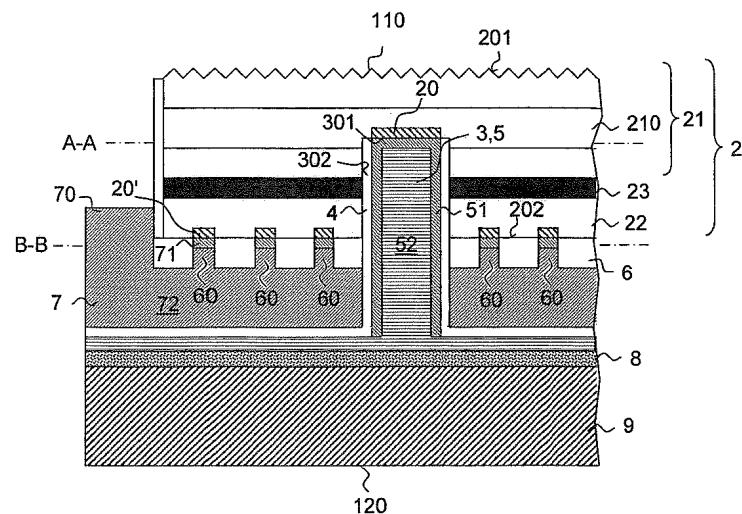

도 2는 일 실시예에 따른 전기 절연 거울층의 개략적 횡단면도이다.

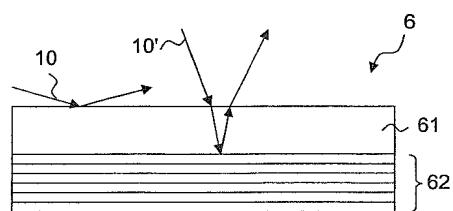

도 3은 복수 개의 리세스를 포함한 광전 반도체칩의 전기 광학적 총 효율을 리세스의 전체면 및 간격에 의존하여 나타낸 도면이다.

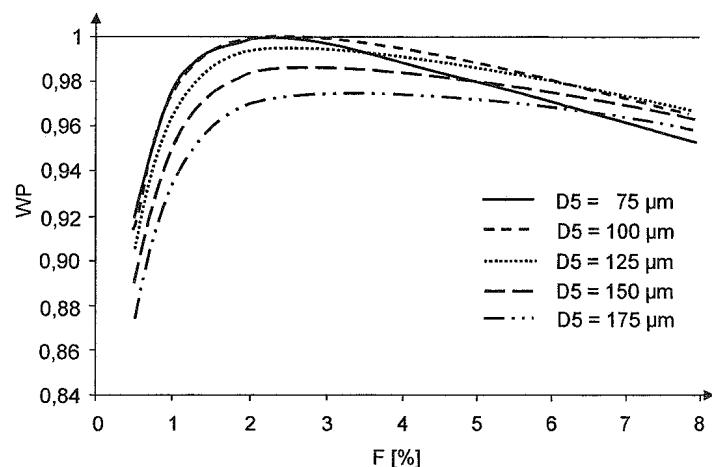

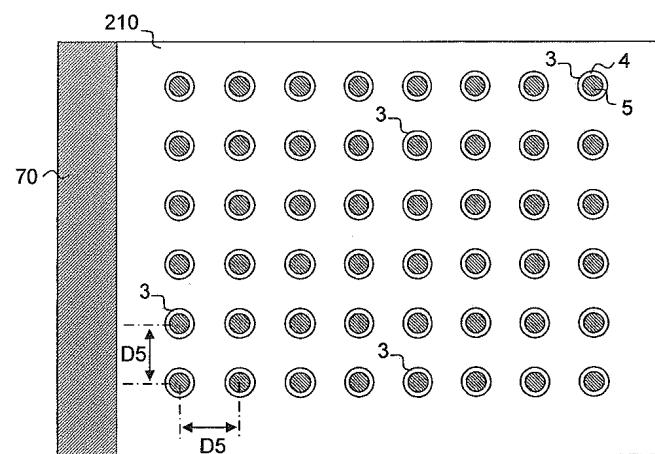

도 4a는 도 1에서 A-A 평면상의 반도체칩의 개략적 단면도이다.

도 4b는 도 1에서 B-B 평면상의 반도체 봄체의 개략적 단면도이다.

### 발명을 실시하기 위한 구체적인 내용

[0066] 도면 및 실시예에서 동일하거나 동일한 종류이거나 동일한 기능의 요소는 동일한 참조번호를 가진다. 도면 및 도면에 도시된 요소들간의 크기비는 치수가 정확하게 기술된 경우를 제외하고 축척에 맞는 것으로 볼 수 없다. 오히려, 가령 층들과 같은 개별 요소는 더 나은 이해 및/또는 더 나은 표현을 위해 과장되어 크게 도시되어 있을 수 있다.

[0067] 도 1은 일 실시예에 따른 광전 반도체 봄체의 개략적 횡단면을 도시한다. 반도체 봄체는 반도체층 시퀀스(2)를 포함한다. 예컨대, 반도체층 시퀀스(2)는 III-V 화합물 반도체 물질계 또는 II-VI 화합물 반도체 물질계이다. 본 명세서에서, 반도체층 시퀀스(2)는 성장 기판을 포함하지 않으며, 그 두께가 5 내지 7  $\mu\text{m}$ 이다.

[0068] III/V 화합물 반도체 물질은 적어도, 예컨대, B, Al, Ga, In 과 같은 제3족의 원소 및 예컨대 N, P, As와 같은 제5족의 원소를 포함한다. 특히, "III/V 화합물 반도체 물질"이란 개념은, 2성분, 3성분 또는 4성분 화합물군을 포함하고, 이러한 화합물군은 제3족의 적어도 하나의 원소 및 제5족의 적어도 하나의 원소를 포함하며, 예컨대 질화물- 및 인화물 화합물 반도체가 있다. 이러한 2성분, 3성분 또는 4성분 화합물은 예컨대 하나 이상의 도편트 및 부가 성분을 포함할 수 있다.

[0069] 이에 상응하여, II-VI 화합물 반도체 물질은, 적어도, 예컨대 Be, Mg, Ca, Sr과 같은 제2족의 원소 및 예컨대 O, S, Se와 같은 제6족의 원소를 포함한다. 특히, II/VI 화합물 반도체 물질은 2성분, 3성분 또는 4성분 화합물을 포함하고, 상기 화합물은 제2주족의 적어도 하나의 원소 및 제6주족의 적어도 하나의 원소를 포함한다. 이러한 2성분, 3성분 또는 4성분 화합물은 예컨대 하나 이상의 도편트 및 부가 성분을 포함할 수 있다. 예컨대, II/VI 화합물 반도체 물질에는 ZnO, ZnMgO, CdS, ZnCdS, MgBeO가 속한다.

[0070] 반도체층 시퀀스(2)는 제1전도성 타입의 층(21)을 포함하고, 본 명세서에서 상기층은 n형층(21)이다. 반도체칩의 전방측(110)으로부터 후방측(120)으로 가는 방향에서 n형층(21) 상에 우선 활성층(23) 및 이후 제2전도성 타입의 층이 후속하며, 본 명세서에서 제2전도성 타입의 층은 p형층(22)이다. 활성층(23)은 예컨대 복사 생성을 위해 다중 양자 우물 구조를 포함한다.

[0071] 반도체층 시퀀스는 npn 층시퀀스로서 형성될 수 있고, 이때 후방측(120)을 향한 방향에서 상기 p형층(22) 다음에 다른 n형층이 배치된다(도면에 미도시됨).

[0072] 반도체층 시퀀스(2)에 함몰부(3)가 형성되고, 상기 함몰부는 반도체층 시퀀스(2)의 후방측 주요면(202)으로부터 p형층(22) 및 활성층(23)을 관통하여 전방측(110)의 방향으로 연장된다. 함몰부(3)는 n형층(21) 안으로 삽입 연장되고, 그 바닥면(301)이 n형층(21)의 중앙 영역(210)에서 종결된다.

[0073] 본 명세서에서, 반도체층 시퀀스(2)의 전방측의 주요면(201)은 구조화부 및/또는 거칠기를 포함하고, 이는 특히 반도체층 시퀀스(2)로부터의 광아웃커플링을 개선하기 위해 제공된다. 바람직하게, 구조화 및/또는 거칠기는 반도체층 시퀀스(2)에서 전자기 복사가 거의 에르고딕으로 분포하도록 유도한다.

[0074] 함몰부(3)는 예컨대 원형 실린더형 또는 타원 실린더형, 직육면체형, 원뿔형 또는 원뿔대형, 피라미드형 또는 각뿔대형이다. 또는, 함몰부(3)는 트렌치로서 형성될 수 있다. 이 경우, 바람직하게, 트렌치는 실질적으로 평편

한 바닥면을 포함한다. 일 실시예에서, 트렌치의 횡단면은 전방측(110)으로부터 후방측(120)을 향한 방향으로 확대된다. 이러한 형상의 리세스(3)는 반도체칩의 모든 실시예를 위해 적합하다.

[0075] 함몰부(3)의 표면의 일부에 전기적 분리층(4)이 형성된다. 본 명세서에서, 분리층(4)은 함몰부(3)의 측벽 또는 원주형 측벽(302)을 덮는다. 전기적 분리층(4)은 전기 절연성으로 형성되고, 예컨대  $\text{SiO}_2$ ,  $\text{SiN}_x$  또는 규소질산화물과 같은 유전체를 포함하거나 그것으로 구성된다.

[0076] 제1전기 연결층(5)의 부분 영역은 함몰부에 배치되고, 특히 함몰부(3)를 완전히 채운다. n형층(21)은 금속의 제1전기 연결층(5)을 이용하여 전기적으로 연결된다. 전기적 분리층(4)은 제1전기 연결층을 활성층(23) 및 p형층(22)에 대하여 절연시킨다.

[0077] n형층(21)의 중앙 영역(210)은 예컨대 전류 확산층을 나타낸다. 특히, 중앙 영역(210)에서의 n형 도편트 농도는 전방측(110)을 향한 방향 및 후방측(120)을 향한 방향에서 상기 중앙 영역(210)에 인접하는 n형층(21)의 영역에 비해 크다 - 특히 5배 이상만큼, 바람직하게는 10배 이상만큼 크다-

[0078] 대안적 또는 부가적으로, 중앙 영역(210)은 교대로 구비되는 층들의 초격자로서 형성된 전류 확산층을 나타낼 수 있다(도면에 미도시). 예컨대, 초격자는 교대로 구비된 GaN층 및 AlGaN층을 포함한다. 초격자의 층은 예컨대 10 nm 이하, 바람직하게 5 nm 이하, 더욱 바람직하게 2 nm 이하의 층 두께를 가진다. 예컨대, 층쌍의 각 하나의 층, 예컨대 AlGaN층은 n형 도핑되고, 층쌍의 제2층은 도핑되지 않거나, 적어도 낮은 도편트 농도로 n형 도핑된다.

[0079] 본 명세서에서, 반도체층 시퀀스(2)의 후방측 주요면(202)에 전기 절연 거울층(6)이 인접한다. 전기 절연 거울층(6)은 개구부(60)를 포함한다. 제2전기 연결층(7)은 전기 절연 거울층(6)을 적어도 국부적으로 덮고, 전기 절연 거울층(6)의 개구부(60)를 관통하여 반도체층 시퀀스(2)까지 연장된다. 본 명세서에서, 상기 층은 p형층(22)에 인접한다.

[0080] 제2전기 연결층(7)을 이용하면, p형층(22)은 전기적으로 연결된다. 이러한 방식으로, 제1전기 연결층(5) 및 제2전기 연결층(7)을 이용하면 반도체층 시퀀스로 구동 전압이 주입될 수 있다.

[0081] 본 명세서에서, 적합하게, 전기적 분리층(4)은 함몰부(3)의 측면(302)에 대해 부가적으로 제2전기 연결층(7)의 표면의 부분 영역을 덮는다. 특히, 상기 층은 제2전기 연결층(7)의 표면에서 제1전기 연결층(5)을 향해있는 부분 영역을 덮는다. 이러한 방식으로, 제1 및 제2 전기 연결층(5, 7)은 쌍방간 전기적으로 절연된다. 제1전기 연결층(5), 제2전기 연결층(7) 및 전기적 분리층(4)은 반도체칩의 후방측(120)에서 횡 방향으로 겹친다.

[0082] 전기 연결층(5, 7)을 포함한 반도체층 시퀀스(2)는 뼈납층 또는 접착제층(8)을 이용하여 캐리어판(9) 상에 고정된다. 상기 고정은 뼈납층 또는 접착제층(8) 없이 - 예컨대 공용 본딩 공정을 이용하여 - 수행될 수 있다.

[0083] 본 명세서에서, 반도체칩은 제1전기 연결층을 이용하여 상기 반도체칩의 후방측(120)으로부터 전기적 연결되도록 제공된다. 뼈납층 또는 접착제층(8) 및 캐리어판(9)은 전기 전도성이고, 제1전기 연결층과 전기 전도적으로 연결된다.

[0084] 본 명세서에서, 제2전기 연결층(7)은 반도체칩의 전방측으로부터 반도체칩을 전기적으로 연결하기 위해 제공된다. 이를 위해, 상기 연결층은 반도체층 시퀀스(2)의 측면에서 전기 연결 영역(70)을 포함한다.

[0085] 또는, 제2전기 연결층(7)은 후방측(120)으로부터의 전기적 연결을 위해 제공되거나/제공되고 제1전기 연결층(5)은 - 예컨대 반도체층 시퀀스(2)의 옆의 측면에 배치된 접촉 영역을 이용하여 - 반도체칩의 전방측(110)으로부터의 반도체칩의 전기적 연결을 위해 제공될 수 있다.

[0086] 리세스(3)의 영역에서 반도체층 시퀀스(2)는 제1전기 연결층에 인접한 접합층(20)을 포함한다. 본 명세서에서, 반도체층 시퀀스는 전기 절연 거울층(6)의 개구부(60)의 영역에서도 제2전기 연결층(7)에 인접한 접합층(20')을 포함한다.

[0087] 접합층(20) 및 다른 접합층(20')은 각각 반도체층 시퀀스(2)의 물질 및 각 전기 연결층의 물질을 포함하며, 상기 전기 연결층은 접합층(20 또는 20')에 인접한다. 본 명세서에서, 접합층(20)은 n형층(21)의 중앙 영역(210)의 물질 및 제1전기 연결층의 물질을 포함한다. 다른 접합층(20')은 p형층(22)의 물질 및 제2전기 연결층(7)의 물질을 포함한다.

[0088] 본 명세서에서, 제1 및 제2전기 연결층(5, 7)은 다층 구조를 포함한다. 제1전기 연결층(5)은 반도체층 시퀀스(2) 및 전기적 분리층(4)에 인접한 부착 증진층(51)을 포함하고, 제2전기 연결층(7)은 반도체층 시퀀스(2) 및

전기 절연 거울층(6)에 인접한 부착 증진층(71)을 포함한다.

[0089] 부착 증진층(51, 71)의 두께는 예컨대 2 nm 이하, 바람직하게 1 nm 이하이다. 본 명세서에서, 제1 또는 제2전기 연결층(5, 7)의 부착 증진층(51, 71)은 각각 약 1 nm의 총 두께를 가진다. 부착 증진층(51, 71) 상에 각각 하나의 반사체층(52 또는 72)이 도포된다.

[0090] 제1 및/또는 제2전기 연결층(5, 7)의 다층 구조는 별도의 전류 분포층을 더 포함할 수 있고, 상기 전류 분포층은 후방측(120)을 향한 방향에서 반사체층(52, 72)뒤에 적어도 국부적으로 배치된다.

[0091] 부착 증진층(51, 71)을 위해 예컨대 금속 Ti, Pt 및/또는 NiAu가 적합하다. 본 명세서에서, 부착 증진층(51, 71)은 티타늄을 포함한다. 본 명세서에서, 반사체층은 알루미늄을 포함한다. 접합층(20, 20')은 부착증진층(51 또는 71)의 물질 및/또는 반사체층(52 또는 72)의 물질을 포함할 수 있다.

[0092] 본 발명자는 실험을 통해, 접합층(20, 20')과 관련하여 이와 같은 전기 연결층(5, 7)을 이용하면 매우 낮은 전기 접촉 저항이 달성된다는 것을 도출하였다. 예컨대, 반도체층 시퀀스에 대한 제1전기 연결층(5)의 접촉 비저항(specific contact resistance)은 본 반도체칩에서  $1 \times 10^{-4}$  Ohm/cm<sup>2</sup> 이하이다. 예컨대, 상기 접촉 비저항의 값은  $2 \times 10^{-5}$  Ohm/cm<sup>2</sup> 이다. 이 때, 상기 접촉 저항은 접합층(20)에 의해 매우 낮다. 접합층(20)없이 동일한 전기 연결층(5)을 포함한 반도체칩에서, 상기 접촉 저항은 예컨대 접합층(20)을 포함한 경우에 비해 5배 이상만큼 크다.

[0093] 접합층(20) 또는 다른 접합층(20')의 영역에서 반도체칩의 후방측에서의 반사도는 접합층(20, 20')을 포함하지 않은 반도체층 시퀀스에 비해 감소한다. 따라서, 낮은 접촉 저항에 의해 반도체칩의 전기적 효율이 증가하긴 한다. 그러나, 광학적 효율은 리세스(3) 및/또는 개구부(60)의 영역에서 반사도의 감소에 의해 낮아질 수 있다. 예컨대, 리세스(3)의 영역에서의 반사도는 절연 거울층(6)에 의해 덮이는 영역의 경우에 비해 약 20%만큼 더 낮다.

[0094] 양호한 반사도를 위해, 가능한 한 큰 면적의 전기 절연 거울층(6)이 유리할 수 있다. 가능한 한 낮은 접촉 저항을 위해, 가능한 한 큰 면적의 리세스(3) 및 개구부(60)가 유리하다. 가능한 한 큰 전기 광학적 총 효율 - "월 플러그 효율(wall plug efficiency)"라고도 함 - 을 얻기 위해, 리세스(3)의 전체면은 매우 높은 전기 광학적 총 효율을 내도록 최적화되는 것이 유리하다.

[0095] 도 3은 이를 위해 본 발명자가 수행한 모의 실험 결과를 도시한다.

[0096] 반도체칩은 복수 개의 리세스(3)를 구비한 반도체층 시퀀스(2)를 포함한다. 이는 도 4a에서 A-A 평면을 따른 개략적 단면도로 개략적으로 도시되어 있다. 본 명세서에서, 리세스의 직경은 10 내지 30 μm이다. 본 명세서에서, 리세스는 균일한 그리드형으로 배치된다. 그리드의 행 또는 열을 따라 연속하는 리세스(3)는 서로 간의 간격(D5)을 포함한다. 바람직하게는, 상기 간격은 인접한 리세스들(3)의 중심으로부터 중심까지 측정된다.

[0097] 도 3은 리세스(3)의 간격(D5) 및 전체면(F)에 대한 상대적 전기 광학적 총 효율(WP)의 종속도를 도시한다. 리세스(3)의 전체면은 가령 전체 접촉면 - 즉 전기적 전체 연결면 - 에 상응하고, 이는 도 3에서 F로 표시되어 있다.

[0098] 도 3에 도시된 결과는 구동 전류가 1.4 A일 때, 티타늄으로 구성되며 총 두께가 1nm인 부착 증진층(51) 및 알루미늄 소재의 반사체층(52)을 포함한 제1전기 연결층(5)과 관련한다.

[0099] 전체 접촉면(F)이 5% 이하, 특히 3% 이하이며 1% 이상 - 예컨대 전체 접촉면(F)이 2% - 일 때가 매우 유리한 것으로 확인되었다. 리세스(3)의 간격(D5)이 75내지 125 μm일 때 매우 높은 전기 광학적 총 효율(WP)이 얻어진다.

[0100] 도 4b는 전기 절연 거울층(6)의 개구부(60)를 관통하여 연장되는 B-B 평면(도 1 참조)에서 반도체칩의 개략적 단면도를 도시한다.

[0101] 본 명세서에서, 제2전기 연결층(7)의 일부 영역으로 채워지는 개구부(60)는 리세스(3)와 마찬가지로 그리드형으로 배치된다.

[0102] 그리드의 행 또는 열에서 각각 인접한 개구부(60)는 상호간 간격(D7)을 포함한다. 간격(D7)을 위해, 5 μm이하의 값이 유리한 것으로 확인되었다. 개구부(60)의 직경은 바람직하게 1 μm 이하이며, 예컨대 500 nm 이하이다. 본 명세서에서, 개구부의 직경은 약 200 나노미터이다. 2개의 연속한 개구부(60)사이의 간격(D7)은 바람직하게 개구부(60)의 최대 횡 방향 치수의 10배 이하이고, 이 때 최대 횡 방향 치수는 예컨대 개구부(60)의 직경 또는 대각선이다. 이러한 방식으로, p형층(22)의 비교적 낮은 횡전도도에 의해 활성층(23)으로의 전류 주입 균일도가

저하될 위험이 감소한다.

- [0103] 도 2는 광전 반도체칩을 위한 전기 절연 거울층(6)의 유리한 실시예를 개략적 획단면도로 도시한다. 상기 실시 예에 따르면, 전기 절연 거울층(6)은 저굴절성 물질로 구성되며 전방측(110)을 향해있는 층(61), 및 후방측(120)을 향해있는 브래그 반사체(62)를 포함한다.

- [0104] 저굴절성 물질의 층(61)은 예컨대 규소이산화물층을 가리키며, 상기 층은 공기로 채워진 기공을 포함하고, 상기 기공의 직경은 8 nm 이하이고, 예컨대 약 3 nm이다. 불규칙하게 형성된 기공에서, 직경은 특히 상기 기공을 완전히 포함하는 최소의 구의 직경이다.

- [0105] 저굴절층(61)의 굴절률은, 반도체층 시퀀스(2)에서 상기 층에 인접하는 층의 굴절률, 본 명세서의 경우 p형층(22)의 굴절률보다 작다. 저굴절층(61)상에 비교적 평평하게 입사된 광빔(10)은 상기 층에서 전반사를 이용하여 전방측(110)으로 재귀반사된다. 저굴절 물질을 이용하면, 전반사를 위해 매우 큰 한계각이 얻어진다.

- [0106] 전기 절연 거울층(6)에 경사지게 도달하여 저굴절층(61)에서 전반사되지 않는 다른 광빔(10')은 상기 저굴절층을 투과하여 브래그 반사체(62)로부터 반사된다. 이를 위해 유리하게는, 브래그 반사체(62)는 활성층(23)으로부터 방출된 전자기 복사에 동조된다.

- [0107] 저굴절층(61) 및 브래그 반사체(62)를 포함한 전기 절연 거울층(6)을 이용하면, 거울층에 평평하게 도달하는 복사(10)뿐만 아니라 거울층(6)에 경사지게 도달하는 복사(10')를 위해서도 높은 반사도가 얻어진다. 상기 반사는 전반사 또는 간섭을 이용하여 수행되므로, 상기 도달한 전자기 복사의 매우 적은 비율만 흡수되어, 거울층(6)의 효율이 매우 높다.

- [0108] 도 1의 실시예에 따른 반도체칩의 제조 시, 예컨대 우선 제2전기 연결층(7)이 반도체층 시퀀스(2) 및 전기 절연 거울층(6) 상에 증착되고, 가령 물리적 또는 화학적 기화 공정(PVD, physical vapour deposition; CVD, chemical vapour deposition)과 같은 기화 방법을 이용한다.

- [0109] 제2전기 연결층(7)을 포함한 반도체층 시퀀스(2)가 노(furnace)에서 - 바람직하게는 불활성 가스 환경 하에 - 가열되고, 예컨대 600°C의 온도로 가열된다. 이 때, 제2전기 연결층의 물질이 p형층(22) 안으로 삽입되고, 다른 접합층(20')을 형성한다.

- [0110] 일 실시예에서, 상기 가열 이전에, 제2전기 연결층(7)의 일부분만 증착되고, 예컨대 부착 증진층(72)이 증착된다. 이 경우, 이후 상기 제2전기 연결층(7)은 가열로 완성된다.

- [0111] 이러한 실시예의 실시예에서, 리소그래피 마스크를 이용하여 거울층(6)에 개구부(60)가 제조된다. 이 때, 제2전기 연결층(7)의 일부가 개구부(60)안에, 그리고 상기 리소그래피 마스크상에 증착될 수 있다. 이후, - 아직 가열되기 전에 - 리소그래피 마스크가 제거된다. 이와 동시에, 리소그래피 마스크 상에 증착된 제2전기 연결층(7)의 물질도 제거된다.

- [0112] 이후, 제1전기 연결층(5)은 반도체칩의 후방측(120)으로부터 제2전기 연결층(7)상의 분리층(4)상에, 그리고 리세스(3)에 증착된다. 증착은 예컨대 마찬가지로 기화 방법을 이용하여 수행될 수 있다.

- [0113] 이후, 제1 및 제2전기 연결층(5, 7)을 포함한 반도체층 시퀀스(2)가 다시 가열되고, 예컨대 500°C의 온도로 가열된다. 이 때, 제2전기 연결층(5)의 물질이 접합층(20')의 형성을 위해 n형층(21)의 중앙 영역(210)으로 삽입된다.

- [0114] 방법의 실시예에서, 접합층(20, 20')의 형성을 위한 제1 및 제2전기 연결층(5, 7)의 가열은 동일한 단계에서 수행될 수 있다. 제2연결층(7)보다 먼저 제1연결층(5)이 제조되는 경우도 고려될 수 있다. 2개의 별도 가열 단계가 수행될 경우, 우선 더 높은 온도로의 가열 단계 및 그 이후 더 낮은 온도로의 가열 단계가 수행되는 것이 유리하다.

- [0115] 다층 구조(51, 52 또는 71, 72)를 포함한 연결층(5, 7)의 가열 시, 예컨대 반사체층(52, 72)의 물질이 부착 증진층(51 또는 71)을 관통하여 반도체층 시퀀스(2)안으로 삽입되는 경우가 고려될 수 있다.

- [0116] 이와 같이 제조된 접합층(20, 20')은 예컨대 5 nm 이상의 층 두께를 가지고, 일 실시예에서 10 nm 이상의 층 두께를 가진다.

- [0117] 방법의 바람직한 실시예에서, 반도체층 시퀀스(2)는 가열 단계 동안 또는 가열 단계 동안 반도체층 시퀀스의 전방측(110)에서 성장 기판을 포함하고, 상기 성장 기판상에 반도체층 시퀀스(2)가 에피택시얼 성장되어 있다. 성

장 기판은 제1 및 제2전기 연결층(5, 7)의 가열된 후 반도체층 시퀀스(2)로부터 제거된다. 바람직하게, 남은 반도체층 시퀀스는 10  $\mu\text{m}$ 이하의 층 두께를 가진다.

[0118] 도 1의 실시예에 따른 반도체칩의 제조 방법에서, 성장 기판의 제거 이전 또는 이후에 반도체층 시퀀스(2)가 캐리어판(9)가 결합한다.

[0119] 통상적 실시예에서, 예컨대 접착제층 또는 땀납층(8)을 이용하는 캐리어판(9)과 반도체층 시퀀스(2)의 결합은 300°C 이하의 온도까지 안정적이다. 따라서, 캐리어판(9)과 반도체층 시퀀스(2)의 결합은 접합층(20, 20')을 형성하기 위한 상기 반도체층 시퀀스(2) 및 전기 연결층(5, 7)의 가열 이후에 수행된다. 제조 공정 동안 반도체칩의 안정성을 보장하기 위해, 반도체층 시퀀스(2)가 접합층(20, 20')의 제조를 위한 가열 동안 여전히 성장 기판과 결합되어 있는 것이 유리하다. 이는 유리하게도 n형측 및 p형측의 접촉이 반도체칩의 후방측(120)으로부터 수행됨으로써 가능해진다.

[0120] 본 발명은 실시예에 의거한 설명에 의하여 상기 실시예에 한정되지 않는다. 오히려 각 새로운 특징 및 특징들의 각 조합을 포함한다. 이는 특히 특히 청구 범위에서의 특징들의 각 조합을 포함하며, 비록 이러한 특징 또는 이러한 조합이 그자체로 명백하게 특히 청구 범위 또는 실시예에 기술되지 않더라도 그러하다.

[0121] 본 특허 출원은 독일 특허 출원 10 2008 016524.7 및 10 2008 032318.7을 기초로 우선권을 주장하고, 그 공개 내용은 참조로 포함된다.

### 부호의 설명

|                   |                   |

|-------------------|-------------------|

| 2: 반도체층 시퀀스       | 21: 제 1 전도성 타입의 층 |

| 22: 제 2 전도성 타입의 층 | 23: 활성층           |

| 3: 리세스            | 4: 전기적 분리층        |

| 5: 제 1 전기 연결층     | 6: 전기 절연 거울층      |

| 7: 제 2 전기 연결층     |                   |

### 도면

#### 도면1

## 도면2

## 도면3

## 도면4a

도면4b